## **Product data sheet**

# LH75401/LH75411 System-on-Chip

### DESCRIPTION

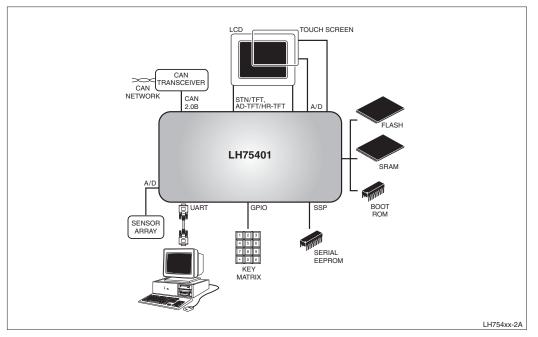

The NXP BlueStreak LH75401/LH75411 family consists of two low-cost 16/32-bit System-on-Chip (SoC) devices.

- LH75401 contains the superset of features.

- LH75411 similar to LH75401, without CAN 2.0B.

### **COMMON FEATURES**

- Highly Integrated System-on-Chip

- ARM7TDMI-S™ Core

- High Performance (84 MHz CPU Speed)

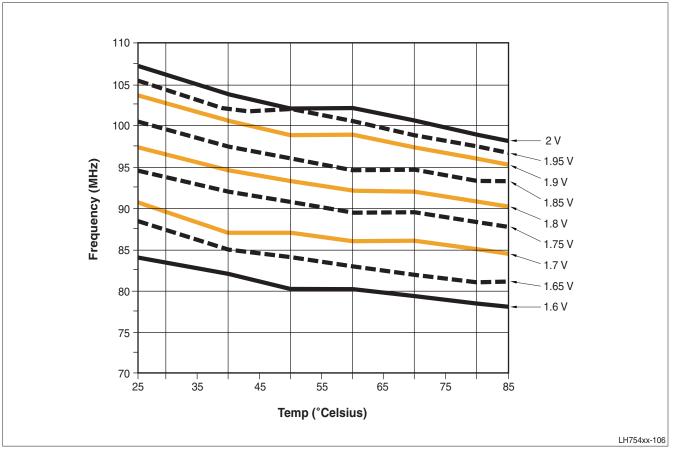

- Internal PLL Driven or External Clock Driven

- Crystal Oscillator/Internal PLL Can Operate with Input Frequency Range of 14 MHz to 20 MHz

- 32 kB On-chip SRAM

- 16 kB Tightly Coupled Memory (TCM) SRAM

- 16 kB Internal SRAM

- Clock and Power Management

Low Power Modes: Standby, Sleep, Stop

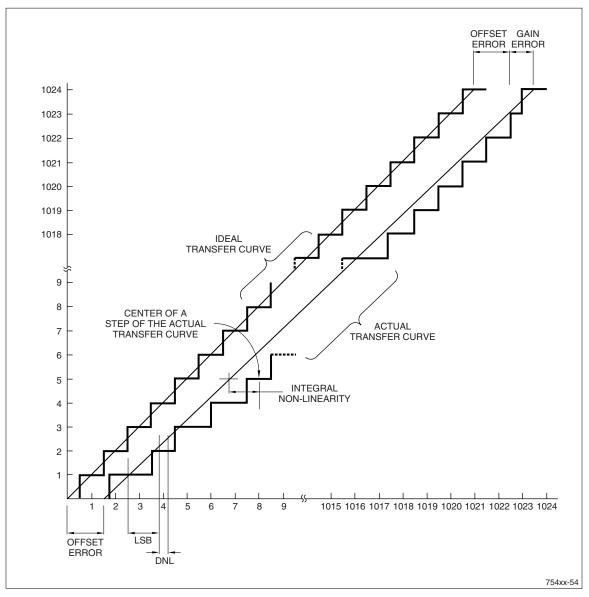

- Eight Channel, 10-bit Analog-to-Digital Converter

- Integrated Touch Screen Controller

- Serial interfaces

- Two 16C550-type UARTs supporting baud rates up to 921,600 baud (requires crystal frequency of 14.756 MHz).

- One 82510-type UART supporting baud rates up to 3,225,600 baud (requires a system clock of 70 MHz).

- Synchronous Serial Port

- Motorola SPI™

- National Semiconductor Microwire<sup>™</sup>

- Texas Instruments SSI

- Real-Time Clock (RTC)

- Three Counter/Timers

- Capture/Compare/PWM Compatibility

- Watchdog Timer (WDT)

- Low-Voltage Detector

- JTAG Debug Interface and Boundary Scan

- Single 3.3 V Supply

- 5 V Tolerant Digital I/O

XTALIN and XTAL32IN inputs are 1.8 V ± 10 %

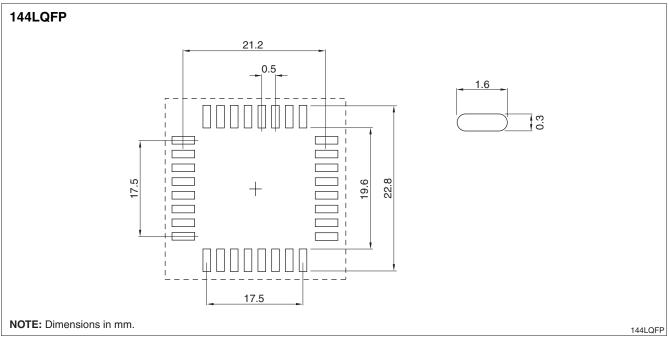

- 144-pin LQFP Package

- -40°C to +85°C Operating Temperature

### **Unique Features of the LH75401**

- Color and Grayscale Liquid Crystal Display (LCD) Controller

- 12-bit (4,096) Direct Mode Color, up to VGA

- 8-bit (256) Direct or Palettized Color, up to SVGA

- 4-bit (16) Direct Mode Color/Grayscale, up to XGA

- 12-bit Video Bus

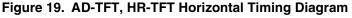

- Supports STN, TFT, HR-TFT, and AD-TFT Displays.

- CAN Controller that supports CAN version 2.0B.

### Unique Features of the LH75411

- Color and Grayscale LCD Controller (LCDC)

- 12-bit (4,096) Direct Mode Color, up to VGA

- 8-bit (256) Direct or Palettized Color, up to SVGA

4-bit (16) Direct Mode Color/Grayscale, up to XGA

- 12-bit Video Bus

- Supports STN, TFT, HR-TFT, and AD-TFT Displays.

### **ORDERING INFORMATION**

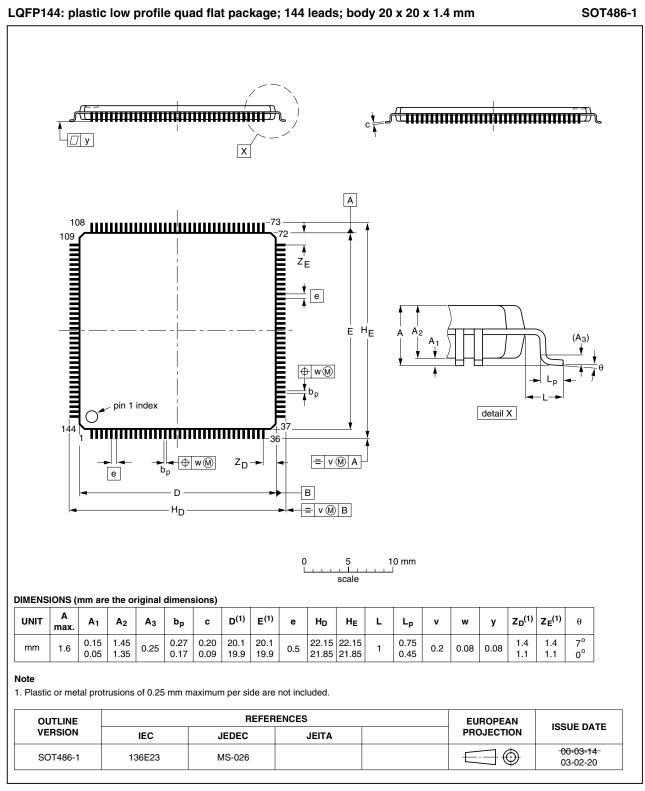

| Table 1 | 1. | Ordering | information |

|---------|----|----------|-------------|

|---------|----|----------|-------------|

|                 |         | Version                                                                    |          |

|-----------------|---------|----------------------------------------------------------------------------|----------|

| Type number     | Name    | me Description                                                             |          |

| LH75401N0Q100C0 | LQFP144 | plastic low profile quad flat package; 144 leads;<br>body 20 x 20 x 1.4 mm | SOT486-1 |

| LH75411N0Q100C0 | LQFP144 | plastic low profile quad flat package; 144 leads;<br>body 20 x 20 x 1.4 mm | SOT486-1 |

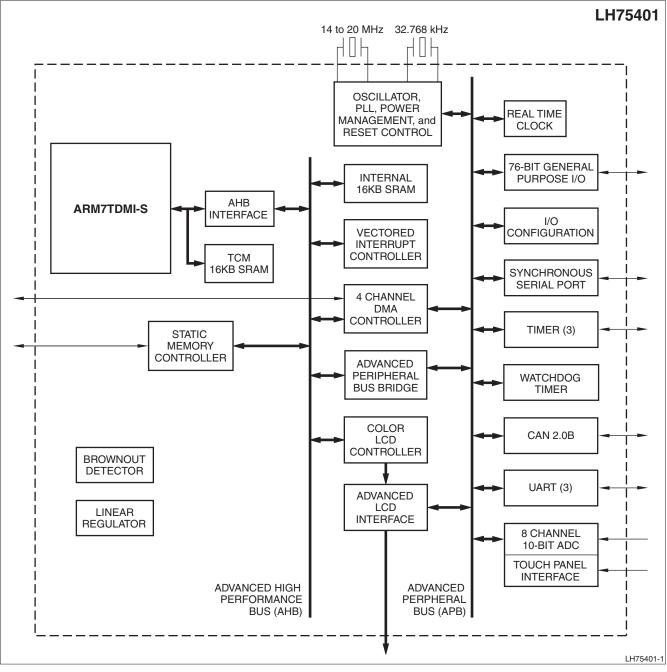

### LH75401 BLOCK DIAGRAM

Figure 1. LH75401 Block Diagram

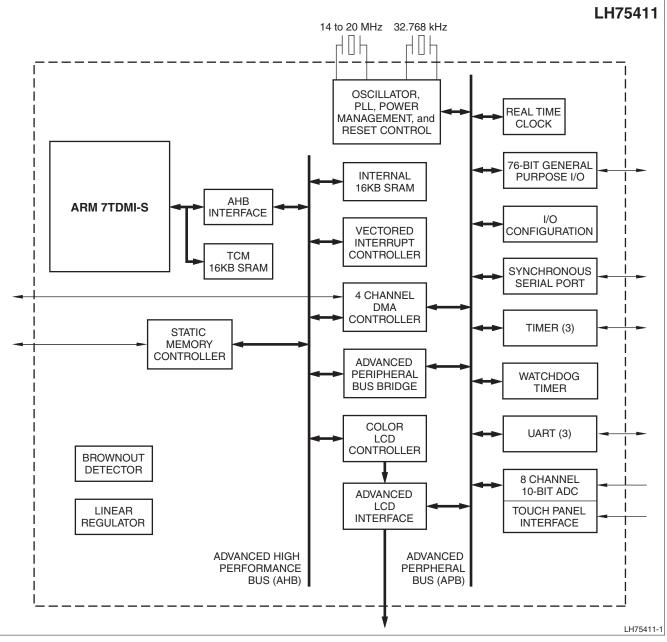

### LH75411 BLOCK DIAGRAM

Figure 2. LH75411 Block Diagram

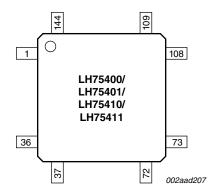

### **PIN CONFIGURATION**

Figure 3. LH75401/LH75411 pin configuration

## LH75401 Numerical Pin Listing

| PIN<br>NO. | FUNCTION<br>AT RESET | FUNCTION 2 | FUNCTION 3 | FUNCTION<br>TYPE | OUTPUT<br>DRIVE | BUFFER<br>TYPE | BEHAVIOR DURING<br>RESET | NOTES |

|------------|----------------------|------------|------------|------------------|-----------------|----------------|--------------------------|-------|

| 1          | PA7                  | D15        |            | I/O              | 8 mA            | Bidirectional  | Pull-up                  | 1     |

| 2          | PA6                  | D14        |            | I/O              | 8 mA            | Bidirectional  | Pull-up                  | 1     |

| 3          | VDD                  |            |            | Power            | None            |                |                          |       |

| 4          | PA5                  | D13        |            | I/O              | 8 mA            | Bidirectional  | Pull-up                  | 1     |

| 5          | PA4                  | D12        |            | I/O              | 8 mA            | Bidirectional  | Pull-up                  | 1     |

| 6          | PA3                  | D11        |            | I/O              | 8 mA            | Bidirectional  | Pull-up                  | 1     |

| 7          | PA2                  | D10        |            | I/O              | 8 mA            | Bidirectional  | Pull-up                  | 1     |

| 8          | VSS                  |            |            | Ground           | None            |                |                          |       |

| 9          | PA1                  | D9         |            | I/O              | 8 mA            | Bidirectional  | Pull-up                  | 1     |

| 10         | PA0                  | D8         |            | I/O              | 8 mA            | Bidirectional  | Pull-up                  | 1     |

| 11         | VDDC                 |            |            | Power            | None            |                |                          |       |

| 12         | D7                   |            |            | I/O              | 8 mA            | Bidirectional  | Pull-up                  |       |

| 13         | D6                   |            |            | I/O              | 8 mA            | Bidirectional  | Pull-up                  |       |

| 14         | VSSC                 |            |            | Ground           | None            |                |                          |       |

| 15         | D5                   |            |            | I/O              | 8 mA            | Bidirectional  | Pull-up                  |       |

| 16         | D4                   |            |            | I/O              | 8 mA            | Bidirectional  | Pull-up                  |       |

| 17         | VDD                  |            |            | Power            | None            |                |                          |       |

| 18         | D3                   |            |            | I/O              | 8 mA            | Bidirectional  | Pull-up                  |       |

| 19         | D2                   |            |            | I/O              | 8 mA            | Bidirectional  | Pull-up                  |       |

| 20         | D1                   |            |            | I/O              | 8 mA            | Bidirectional  | Pull-up                  |       |

| 21         | D0                   |            |            | I/O              | 8 mA            | Bidirectional  | Pull-up                  |       |

| 22         | nWE                  |            |            |                  | 8 mA            | Output         | HIGH                     | 3     |

| 23         | nOE                  |            |            |                  | 8 mA            | Output         | HIGH                     | 3     |

| 24         | PB5                  | nWAIT      |            |                  | 8 mA            | Bidirectional  | Pull-up                  | 1, 3  |

| 25         | PB4                  | nBLE1      |            |                  | 8 mA            | Bidirectional  | Pull-up                  | 1, 3  |

| 26         | VSS                  |            |            | Ground           | None            |                |                          |       |

| 27         | PB3                  | nBLE0      |            |                  | 8 mA            | Bidirectional  | Pull-up                  | 1, 3  |

| 28         | PB2                  | nCS3       |            |                  | 8 mA            | Bidirectional  | Pull-up                  | 1, 3  |

| 29         | PB1                  | nCS2       |            |                  | 8 mA            | Bidirectional  | Pull-up                  | 1, 3  |

| 30         | PB0                  | nCS1       |            |                  | 8 mA            | Bidirectional  | Pull-up                  | 1, 3  |

| 31         | nCS0                 |            |            |                  | 8 mA            | Output         | Pull-up                  | 3     |

| 32         | PC7                  | A23        |            |                  | 8 mA            | Bidirectional  | Pull-down                | 1     |

| 33         | PC6                  | A22        |            |                  | 8 mA            | Bidirectional  | Pull-down                | 1     |

| 34         | VDD                  |            |            | Power            | None            |                |                          |       |

| 35         | PC5                  | A21        |            |                  | 8 mA            | Bidirectional  | Pull-down                | 1     |

| 36         | PC4                  | A20        |            |                  | 8 mA            | Bidirectional  | Pull-down                | 1     |

| 37         | PC3                  | A19        |            |                  | 8 mA            | Bidirectional  | Pull-down                | 1     |

| 38         | PC2                  | A18        |            |                  | 8 mA            | Bidirectional  | Pull-down                | 1     |

| PIN<br>NO. | FUNCTION<br>AT RESET | FUNCTION 2 | FUNCTION 3 | FUNCTION<br>TYPE | OUTPUT<br>DRIVE | BUFFER<br>TYPE | BEHAVIOR DURING<br>RESET | NOTES |

|------------|----------------------|------------|------------|------------------|-----------------|----------------|--------------------------|-------|

| 39         | PC1                  | A17        |            |                  | 8 mA            | Bidirectional  | Pull-down                | 1     |

| 40         | PC0                  | A16        |            |                  | 8 mA            | Bidirectional  | Pull-down                | 1     |

| 41         | VSS                  |            |            | Ground           | None            |                |                          |       |

| 42         | VDD                  |            |            | Power            | None            |                |                          |       |

| 43         | A15                  |            |            |                  | 8 mA            | Output         | LOW                      |       |

| 44         | A14                  |            |            |                  | 8 mA            | Output         | LOW                      |       |

| 45         | A13                  |            |            |                  | 8 mA            | Output         | LOW                      |       |

| 46         | A12                  |            |            |                  | 8 mA            | Output         | LOW                      |       |

| 47         | A11                  |            |            |                  | 8 mA            | Output         | LOW                      |       |

| 48         | VSS                  |            |            | Ground           | None            |                |                          |       |

| 49         | A10                  |            |            |                  | 8 mA            | Output         | LOW                      |       |

| 50         | A9                   |            |            |                  | 8 mA            | Output         | LOW                      |       |

| 51         | A8                   |            |            |                  | 8 mA            | Output         | LOW                      |       |

| 52         | A7                   |            |            |                  | 8 mA            | Output         | LOW                      |       |

| 53         | A6                   |            |            |                  | 8 mA            | Output         | LOW                      |       |

| 54         | VDD                  |            |            | Power            | None            |                |                          |       |

| 55         | A5                   |            |            |                  | 8 mA            | Output         | LOW                      |       |

| 56         | A4                   |            |            |                  | 8 mA            | Output         | LOW                      |       |

| 57         | A3                   |            |            |                  | 8 mA            | Output         | LOW                      |       |

| 58         | A2                   |            |            |                  | 8 mA            | Output         | LOW                      |       |

| 59         | VSS                  |            |            | Ground           | None            |                |                          |       |

| 60         | A1                   |            |            |                  | 8 mA            | Output         | LOW                      |       |

| 61         | A0                   |            |            |                  | 8 mA            | Output         | LOW                      |       |

| 62         | nRESETIN             |            |            |                  | None            | Input          | Pull-up                  | 2, 3  |

| 63         | TEST2                |            |            |                  | None            | Input          | Pull-up                  | 2     |

| 64         | TEST1                |            |            |                  | None            | Input          | Pull-up                  | 2     |

| 65         | TMS                  |            |            |                  | None            | Input          | Pull-up                  | 2     |

| 66         | RTCK                 |            |            |                  | 8 mA            | Output         |                          |       |

| 67         | ТСК                  |            |            |                  | None            | Input          |                          |       |

| 68         | TDI                  |            |            |                  | None            | Input          | Pull-up                  | 2     |

| 69         | TDO                  |            |            |                  | 4 mA            | Output         |                          |       |

| 70         | LINREGEN             |            |            |                  | None            | Input          |                          | 5     |

| 71         | nRESETOUT            |            |            |                  | 8 mA            | Output         |                          | 3     |

| 72         | PD6                  | INT6       | DREQ       |                  | 6 mA            | Bidirectional  | Pull-down                | 1     |

| 73         | PD5                  | INT5       | DACK       |                  | 6 mA            | Bidirectional  |                          | 1, 2  |

| 74         | PD4                  | INT4       | UARTRX1    |                  | 8 mA            | Bidirectional  | Pull-up                  | 1     |

| 75         | VDDC                 |            |            | Power            | None            |                |                          |       |

| 76         | PD3                  | INT3       | UARTTX1    |                  | 8 mA            | Bidirectional  | Pull-up                  | 1     |

| 77         | PD2                  | INT2       |            |                  | 2 mA            | Bidirectional  | Pull-up                  | 1     |

| 78         | PD1                  | INT1       |            |                  | 6 mA            | Bidirectional  |                          | 1, 2  |

| 79         | PD0                  | INT0       |            |                  | 2 mA            | Bidirectional  |                          | 1     |

| 80         | VSSC                 |            |            | Ground           | None            |                |                          |       |

### Table 2. LH75401 Numerical Pin List (Cont'd)

Downloaded from  $\underline{\text{Elcodis.com}}$  electronic components distributor

| PIN<br>NO. | FUNCTION<br>AT RESET | FUNCTION 2 | FUNCTION 3 | FUNCTION<br>TYPE | OUTPUT<br>DRIVE | BUFFER<br>TYPE | BEHAVIOR DURING<br>RESET | NOTES |

|------------|----------------------|------------|------------|------------------|-----------------|----------------|--------------------------|-------|

| 81         | nPOR                 |            |            |                  | None            | Input          | Pull-up                  | 2, 3  |

| 82         | XTAL32IN             |            |            |                  | None            | Input          |                          | 4     |

| 83         | XTAL32OUT            |            |            |                  | None            | Output         |                          |       |

| 84         | VSSA_PLL             |            |            | Ground           | None            |                |                          |       |

| 85         | VDDA_PLL             |            |            | Power            | None            |                |                          |       |

| 86         | XTALIN               |            |            |                  | None            | Input          |                          | 4     |

| 87         | XTALOUT              |            |            |                  | None            | Output         |                          |       |

| 88         | VSSA_ADC             |            |            | Ground           | None            |                |                          |       |

| 89         | AN3 (LR/Y-)          | PJ7        |            |                  | None            | Input          |                          |       |

| 90         | AN4 (Wiper)          | PJ6        |            |                  | None            | Input          |                          |       |

| 91         | AN9                  | PJ5        |            |                  | None            | Input          |                          |       |

| 92         | AN2 (LL/Y+)          | PJ4        |            |                  | None            | Input          |                          |       |

| 93         | AN8                  | PJ3        |            |                  | None            | Input          |                          |       |

| 94         | AN1 (UR/X-)          | PJ2        |            |                  | None            | Input          |                          |       |

| 95         | AN6                  | PJ1        |            |                  | None            | Input          |                          |       |

| 96         | AN0 (UL/X+)          | PJ0        |            |                  | None            | Input          |                          |       |

| 97         | VDDA_ADC             |            |            | Power            | None            |                |                          |       |

| 98         | VDD                  |            |            | Power            | None            |                |                          |       |

| 99         | PE7                  | SSPFRM     |            |                  | 4 mA            | Bidirectional  | Pull-up                  | 1     |

| 100        | PE6                  | SSPCLK     |            |                  | 4 mA            | Bidirectional  | Pull-down                | 1     |

| 101        | PE5                  | SSPRX      |            |                  | 4 mA            | Bidirectional  | Pull-up                  | 1     |

| 102        | PE4                  | SSPTX      |            |                  | 4 mA            | Bidirectional  | Pull-down                | 1     |

| 103        | PE3                  | CANTX      | UARTTX0    |                  | 8 mA            | Bidirectional  | Pull-up                  | 1     |

| 104        | PE2                  | CANRX      | UARTRX0    |                  | 2 mA            | Bidirectional  | Pull-up                  | 1     |

| 105        | PE1                  | UARTTX2    |            |                  | 4 mA            | Bidirectional  | Pull-up                  | 1     |

| 106        | VSS                  |            |            | Ground           | None            |                |                          |       |

| 107        | PE0                  | UARTRX2    |            |                  | 4 mA            | Bidirectional  | Pull-up                  | 1     |

| 108        | PF6                  | CTCAP2B    | CTCMP2B    |                  | 4 mA            | Bidirectional  |                          | 2     |

| 109        | PF5                  | CTCAP2A    | CTCMP2A    |                  | 4 mA            | Bidirectional  |                          |       |

| 110        | PF4                  | CTCAP1B    | CACMP1B    |                  | 4 mA            | Bidirectional  |                          | 2     |

| 111        | PF3                  | CTCAP1A    | CTCMP1A    |                  | 4 mA            | Bidirectional  |                          |       |

| 112        | VDD                  |            |            | Power            | None            |                |                          |       |

| 113        | PF2                  | CTCAP0E    |            |                  | 4 mA            | Bidirectional  |                          | 2     |

| 114        | PF1                  | CTCAP0D    |            |                  | 4 mA            | Bidirectional  |                          |       |

| 115        | PF0                  | CTCAP0C    |            |                  | 4 mA            | Bidirectional  |                          | 2     |

| 116        | PG7                  | CTCAP0B    | CTCMP0B    |                  | 4 mA            | Bidirectional  |                          |       |

| 117        | PG6                  | CTCAP0A    | CTCMP0A    |                  | 4 mA            | Bidirectional  |                          | 2     |

| 118        | PG5                  | CTCLK      |            |                  | 4 mA            | Bidirectional  |                          |       |

| 119        | VSS                  |            |            | Ground           | None            |                |                          |       |

| 120        | PG4                  | LCDVEEEN   | LCDMOD     |                  | 8 mA            | Bidirectional  |                          |       |

| 121        | PG3                  | LCDVDDEN   |            |                  | 8 mA            | Bidirectional  |                          |       |

| 122        | PG2                  | LCDDSPLEN  | LCDREV     |                  | 8 mA            | Bidirectional  |                          |       |

### Table 2. LH75401 Numerical Pin List (Cont'd)

| PIN<br>NO. | FUNCTION<br>AT RESET | FUNCTION 2 | FUNCTION 3 | FUNCTION<br>TYPE | OUTPUT<br>DRIVE | BUFFER<br>TYPE | BEHAVIOR DURING<br>RESET | NOTES |

|------------|----------------------|------------|------------|------------------|-----------------|----------------|--------------------------|-------|

| 123        | PG1                  | LCDCLS     |            |                  | 8 mA            | Bidirectional  |                          |       |

| 124        | PG0                  | LCDPS      |            |                  | 8 mA            | Bidirectional  |                          |       |

| 125        | PH7                  | LCDDCLK    |            |                  | 8 mA            | Bidirectional  |                          |       |

| 126        | VDD                  |            |            | Power            | None            |                |                          |       |

| 127        | VSS                  |            |            | Ground           | None            |                |                          |       |

| 128        | PH6                  | LCDLP      | LCDHRLP    |                  | 8 mA            | Bidirectional  |                          |       |

| 129        | PH5                  | LCDFP      | LCDSPS     |                  | 8 mA            | Bidirectional  |                          |       |

| 130        | PH4                  | LCDEN      | LCDSPL     |                  | 8 mA            | Bidirectional  |                          |       |

| 131        | PH3                  | LCDVD11    |            |                  | 8 mA            | Bidirectional  |                          |       |

| 132        | PH2                  | LCDVD10    |            |                  | 8 mA            | Bidirectional  |                          |       |

| 133        | PH1                  | LCDVD9     |            |                  | 8 mA            | Bidirectional  |                          |       |

| 134        | VDD                  |            |            | Power            | None            |                |                          |       |

| 135        | PH0                  | LCDVD8     |            |                  | 8 mA            | Bidirectional  |                          |       |

| 136        | PI7                  | LCDVD7     |            |                  | 8 mA            | Bidirectional  |                          |       |

| 137        | Pl6                  | LCDVD6     |            |                  | 8 mA            | Bidirectional  |                          |       |

| 138        | PI5                  | LCDVD5     |            |                  | 8 mA            | Bidirectional  |                          |       |

| 139        | PI4                  | LCDVD4     |            |                  | 8 mA            | Bidirectional  |                          |       |

| 140        | VSS                  |            |            | Ground           | None            |                |                          |       |

| 141        | PI3                  | LCDVD3     |            |                  | 8 mA            | Bidirectional  |                          |       |

| 142        | Pl2                  | LCDVD2     |            |                  | 8 mA            | Bidirectional  |                          |       |

| 143        | PI1                  | LCDVD1     |            |                  | 8 mA            | Bidirectional  |                          |       |

| 144        | PI0                  | LCDVD0     |            |                  | 8 mA            | Bidirectional  |                          |       |

| Table 2. LH7540 | 1 Numerical Pi | n List (Cont'd) |

|-----------------|----------------|-----------------|

|-----------------|----------------|-----------------|

#### NOTES:

1. Signal is selectable as pull-up, pull-down, or no pull-up/pull-down via the I/O Configuration peripheral.

2. CMOS Schmitt trigger input.

3. Signals preceded with 'n' are active LOW.

4. Crystal Oscillator Inputs should be driven to 1.8 V  $\pm$ 10 % (MAX.)

5. LINREGEN activation requires a 0  $\Omega$  pull-up to VDD.

## LH75401 Signal Descriptions

| PIN NO.                                                                                                                                      | SIGNAL NAME | TYPE   | DESCRIPTION                                    | NOTES |

|----------------------------------------------------------------------------------------------------------------------------------------------|-------------|--------|------------------------------------------------|-------|

|                                                                                                                                              |             |        | MEMORY INTERFACE (MI)                          |       |

| 1<br>2<br>4<br>5<br>6<br>7<br>9<br>10<br>12<br>13<br>15<br>16<br>18<br>19<br>20<br>21                                                        | D[15:0]     |        | Data Input/Output Signals                      | 1     |

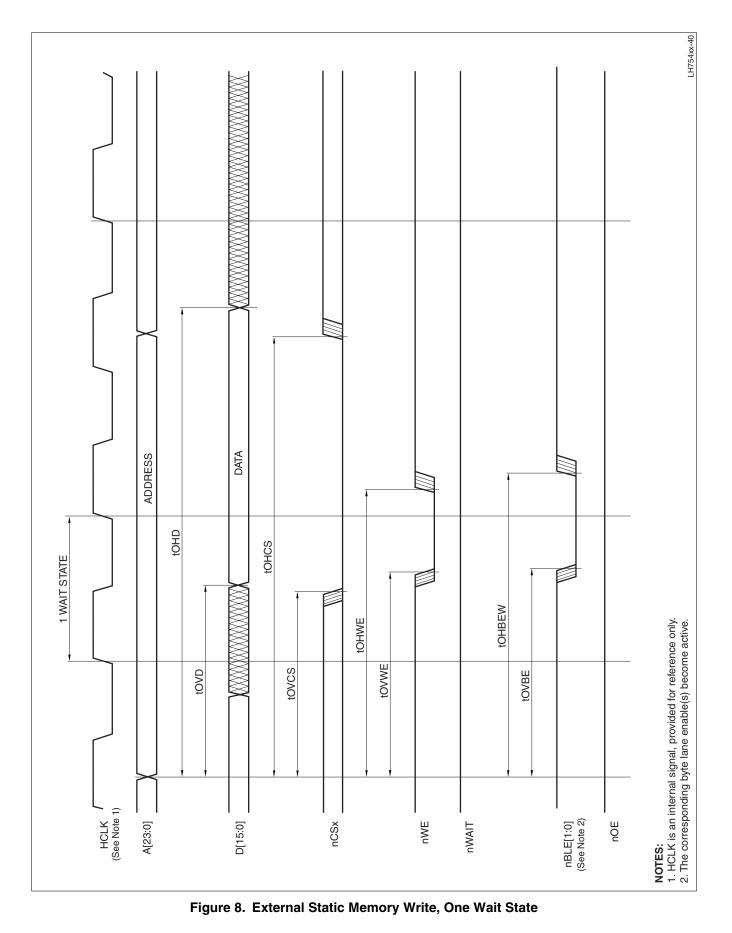

| 22                                                                                                                                           | nWE         | Output | Static Memory Controller Write Enable          | 2     |

| 23                                                                                                                                           | nOE         | Output | Static Memory Controller Output Enable         | 2     |

| 24                                                                                                                                           | nWAIT       | Input  | Static Memory Controller External Wait Control | 1, 2  |

| 25                                                                                                                                           | nBLE1       | Output | Static Memory Controller Byte Lane Strobe      | 1, 2  |

| 27                                                                                                                                           | nBLE0       | Output | Static Memory Controller Byte Lane Strobe      | 1, 2  |

| 28                                                                                                                                           | nCS3        | Output | Static Memory Controller Chip Select           | 1, 2  |

| 29                                                                                                                                           | nCS2        | Output | Static Memory Controller Chip Select           | 1, 2  |

| 30                                                                                                                                           | nCS1        | Output | Static Memory Controller Chip Select           | 1, 2  |

| 31                                                                                                                                           | nCS0        | Output | Static Memory Controller Chip Select           | 2     |

| 32<br>33<br>35<br>36<br>37<br>38<br>39<br>40<br>43<br>44<br>45<br>46<br>47<br>49<br>50<br>51<br>52<br>53<br>55<br>56<br>57<br>58<br>60<br>61 | A[23:0]     | Output | Address Signals                                | 1     |

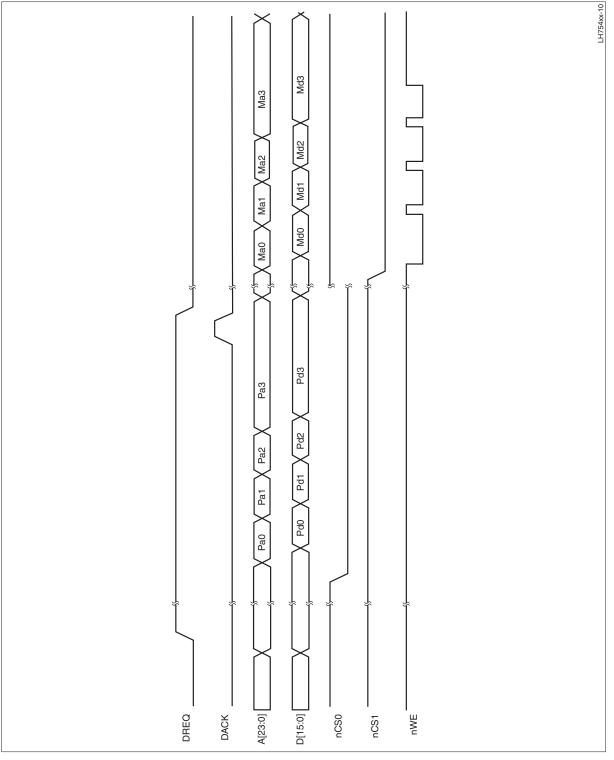

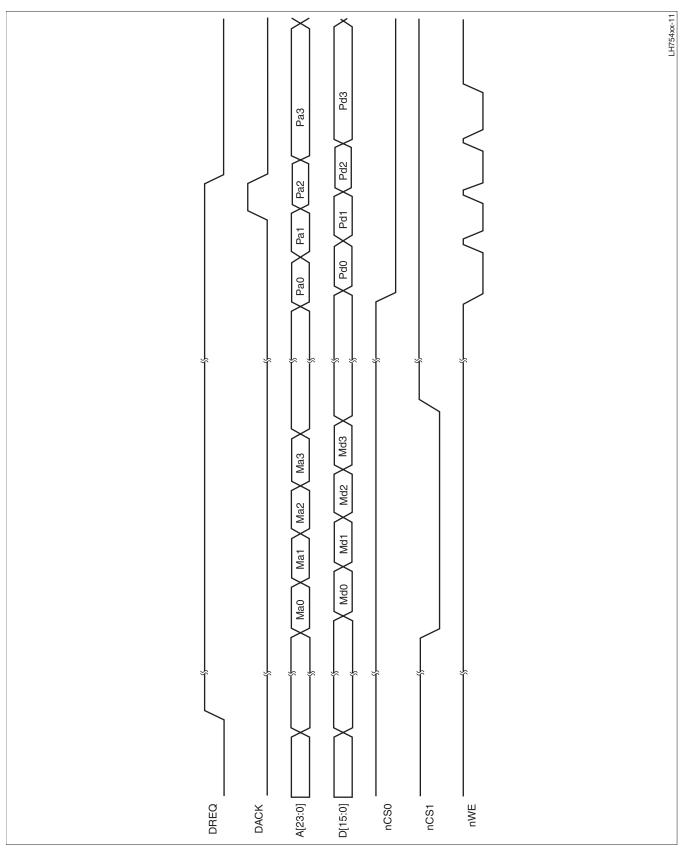

| 72                                                                                                                                           | DREQ        | Incut  | DMA CONTROLLER (DMAC)                          | 4     |

|                                                                                                                                              |             | Input  | DMA Request                                    | 1     |

| 73                                                                                                                                           | DACK        | Output | DMA Acknowledge                                | 1     |

| PIN NO.                                                                                                                       | SIGNAL NAME | TYPE      | DESCRIPTION                                                              | NOTES |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------|-------------|-----------|--------------------------------------------------------------------------|-------|--|--|--|

| COLOR LCD CONTROLLER (CLCDC)                                                                                                  |             |           |                                                                          |       |  |  |  |

| 120                                                                                                                           | LCDMOD      | Output    | Signal Used by the Row Driver (AD-TFT, HR-TFT only)                      | 1     |  |  |  |

| 120                                                                                                                           | LCDVEEEN    | Output    | Analog Supply Enable (AC Bias SIgnal)                                    | 1     |  |  |  |

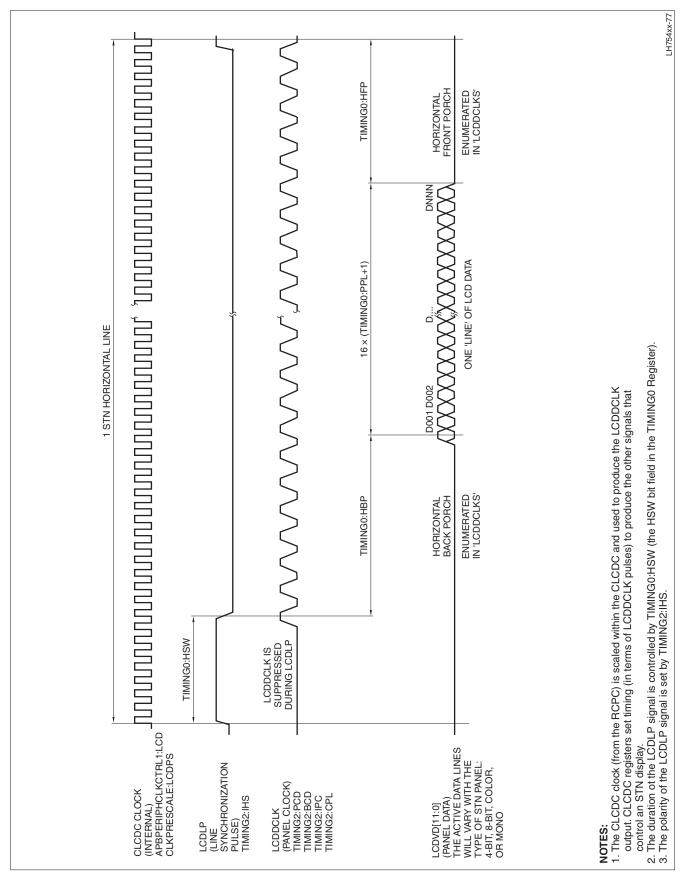

| 121                                                                                                                           | LCDVDDEN    | Output    | Digital Supply Enable                                                    | 1     |  |  |  |

| 122                                                                                                                           | LCDDSPLEN   | Output    | LCD Panel Power Enable                                                   | 1     |  |  |  |

| 122                                                                                                                           | LCDREV      | Output    | Reverse Signal (AD-TFT, HR-TFT only)                                     | 1     |  |  |  |

| 123                                                                                                                           | LCDCLS      | Output    | Clock to the Row Drivers (AD-TFT, HR-TFT only)                           | 1     |  |  |  |

| 124                                                                                                                           | LCDPS       | Output    | Power Save (AD-TFT, HR-TFT only)                                         | 1     |  |  |  |

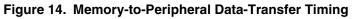

| 125                                                                                                                           | LCDDCLK     | Output    | LCD Panel Clock                                                          | 1     |  |  |  |

| 128                                                                                                                           | LCDLP       | Output    | Line Synchronization Pulse (STN), Horizontal Synchronization Pulse (TFT) | 1     |  |  |  |

| 128                                                                                                                           | LCDHRLP     | Output    | Latch Pulse (AD-TFT, HR-TFT only)                                        | 1     |  |  |  |

| 129                                                                                                                           | LCDFP       | Output    | Frame Pulse (STN), Vertical Synchronization Pulse (TFT)                  | 1     |  |  |  |

| 129                                                                                                                           | LCDSPS      | Output    | Row Driver Counter Reset Signal (AD-TFT, HR-TFT only)                    | 1     |  |  |  |

| 130                                                                                                                           | LCDEN       | Output    | LCD Data Enable                                                          | 1     |  |  |  |

| 130                                                                                                                           | LCDSPL      | Output    | Start Pulse Left (AD-TFT, HR-TFT only)                                   | 1     |  |  |  |

| 132<br>133<br>135<br>136<br>137<br>138<br>139<br>141<br>142<br>143<br>144                                                     | LCDVD[11:0] | Output    | LCD Panel Data bus                                                       | 1     |  |  |  |

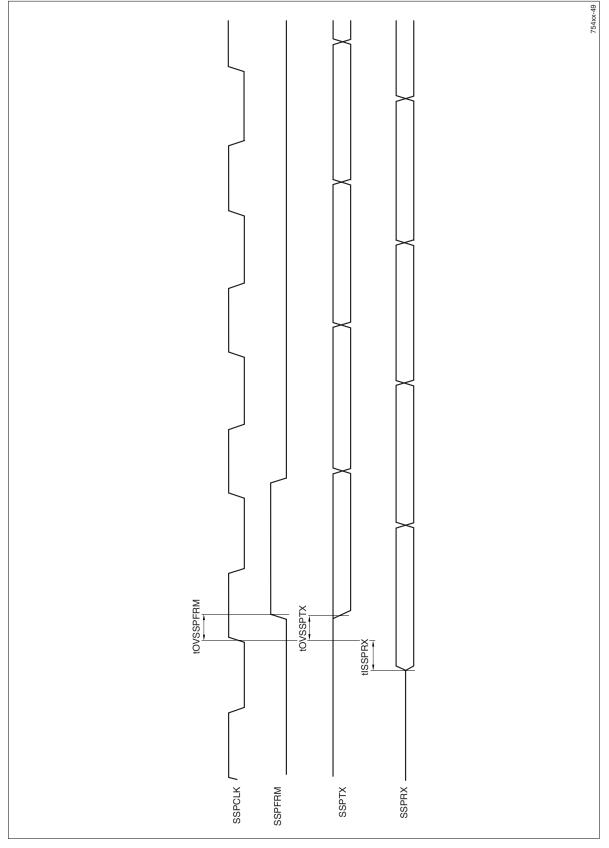

|                                                                                                                               | 1           |           | SYNCHRONOUS SERIAL PORT (SSP)                                            | 1     |  |  |  |

| 99                                                                                                                            | SSPFRM      | Output    | SSP Serial Frame                                                         | 1     |  |  |  |

| 100                                                                                                                           | SSPCLK      | Output    | SSP Clock                                                                | 1     |  |  |  |

| 101                                                                                                                           | SSPRX       | Input     | SSP RXD                                                                  | 1     |  |  |  |

| 102                                                                                                                           | SSPTX       | Output    | SSP TXD                                                                  | 1     |  |  |  |

|                                                                                                                               |             | <u> </u>  |                                                                          |       |  |  |  |

| 103                                                                                                                           | UARTTX0     | -         | UARTO Transmitted Serial Data Output                                     | 1     |  |  |  |

| 104                                                                                                                           | UARTRX0     | Input     | UARTO Received Serial Data Input                                         | 1     |  |  |  |

| 74                                                                                                                            |             | la a d    | UART1 (U1)                                                               |       |  |  |  |

| 74                                                                                                                            | UARTRX1     | Input     | UART1 Received Serial Data Input                                         | 1     |  |  |  |

| 76                                                                                                                            | UARTTX1     | Output    | UART1 Transmitted Serial Data Output                                     | 1     |  |  |  |

| 105                                                                                                                           |             | Outra : + | UART2 (U2)                                                               | 4     |  |  |  |

| 105                                                                                                                           | UARTTX2     | Output    | UART2 Transmitted Serial Data Output                                     | 1     |  |  |  |

| 107                                                                                                                           | UARTRX2     | Input     |                                                                          | 1     |  |  |  |

| CONTROLLER AREA NETWORK (CAN)           103         CANTX         Output         CAN Transmitted Serial Data Output         1 |             |           |                                                                          |       |  |  |  |

| 103                                                                                                                           | CANRX       | •         | CAN Received Serial Data Input                                           | 1     |  |  |  |

| 104                                                                                                                           |             | Input     | טרוע הפטפועפע ספוומו שמומ וווµענ                                         |       |  |  |  |

#### Table 3. LH75401 Signal Descriptions (Cont'd)

| Table 3. | LH75401 | Signal | Descriptions | (Cont'd) |

|----------|---------|--------|--------------|----------|

|----------|---------|--------|--------------|----------|

| PIN NO.                                      | SIGNAL NAME                                                                                  | TYPE         | DESCRIPTION                          | NOTES |

|----------------------------------------------|----------------------------------------------------------------------------------------------|--------------|--------------------------------------|-------|

|                                              |                                                                                              | Α            | NALOG-TO-DIGITAL CONVERTER (ADC)     |       |

| 89<br>90<br>91<br>92<br>93<br>94<br>95<br>96 | AN3 (LR/Y-)<br>AN4 (Wiper)<br>AN9<br>AN2 (LL/Y+)<br>AN8<br>AN1 (UR/X-)<br>AN6<br>AN0 (UL/X+) | Input        | ADC Inputs                           | 1     |

|                                              |                                                                                              |              | TIMER 0                              |       |

| 117<br>116<br>115<br>114<br>113              | CTCAP0[A:E]                                                                                  | Input        | Timer 0 Capture Inputs               | 1     |

| 117<br>116                                   | CTCMP0[A:B]                                                                                  | Output       | Timer 0 Compare Outputs              | 1     |

| 118                                          | CTCLK                                                                                        | Input        | Common External Clock                | 1     |

|                                              |                                                                                              |              | TIMER 1                              |       |

| 111<br>110                                   | CTCAP1[A:B]                                                                                  | Input        | Timer 1 Capture Inputs               | 1     |

| 111<br>110                                   | CTCMP1[A:B]                                                                                  | Output       | Timer 1 Compare Outputs              | 1     |

| 118                                          | CTCLK                                                                                        | Input        | Common External Clock                | 1     |

|                                              |                                                                                              |              | TIMER 2                              |       |

| 109<br>108                                   | CTCAP2[A:B]                                                                                  | Input        | Timer 2 Capture Inputs               | 1     |

| 109<br>108                                   | CTCMP2[A:B]                                                                                  | Input        | Timer 2 Compare Outputs              | 1     |

| 118                                          | CTCLK                                                                                        | Input        | Common External Clock                | 1     |

|                                              | 1                                                                                            | GE           | NERAL PURPOSE INPUT/OUTPUT (GPIO)    |       |

| 1<br>2<br>4<br>5<br>6<br>7<br>9<br>10        | PA7<br>PA6<br>PA5<br>PA4<br>PA3<br>PA2<br>PA1<br>PA0                                         | Input/Output | General Purpose I/O Signals - Port A | 1     |

| 24<br>25<br>27<br>28<br>29<br>30             | PB5<br>PB4<br>PB3<br>PB2<br>PB1<br>PB0                                                       | Input/Output | General Purpose I/O Signals - Port B | 1     |

| 32<br>33<br>35<br>36<br>37<br>38<br>39<br>40 | PC7<br>PC6<br>PC5<br>PC4<br>PC3<br>PC2<br>PC1<br>PC0                                         | Input/Output | General Purpose I/O Signals - Port C | 1     |

| PIN NO.                                              | SIGNAL NAME                                          | TYPE            | DESCRIPTION                                       | NOTES |

|------------------------------------------------------|------------------------------------------------------|-----------------|---------------------------------------------------|-------|

| 72<br>73<br>74<br>76<br>77<br>78<br>79               | PD6<br>PD5<br>PD4<br>PD3<br>PD2<br>PD1<br>PD0        | Input/Output    | General Purpose I/O Signals - Port D              | 1     |

| 89<br>90<br>91<br>92<br>93<br>94<br>95<br>96         | PJ7<br>PJ6<br>PJ5<br>PJ4<br>PJ3<br>PJ2<br>PJ1<br>PJ0 | Input           | General Purpose I/O Signals - Port J              | 1     |

| 99<br>100<br>101<br>102<br>103<br>104<br>105<br>107  | PE7<br>PE6<br>PE5<br>PE4<br>PE3<br>PE2<br>PE1<br>PE0 | Input/Output    | General Purpose I/O Signals - Port E              | 1     |

| 108<br>109<br>110<br>111<br>113<br>114<br>115        | PF6<br>PF5<br>PF4<br>PF3<br>PF2<br>PF1<br>PF0        | Input/Output    | General Purpose I/O Signals - Port F              | 1     |

| 116<br>117<br>118<br>120<br>121<br>122<br>123<br>124 | PG7<br>PG6<br>PG5<br>PG4<br>PG3<br>PG2<br>PG1<br>PG0 | Input/Output    | General Purpose I/O Signals - Port G              | 1     |

| 125<br>128<br>129<br>130<br>131<br>132<br>133<br>135 | PH7<br>PH6<br>PH5<br>PH4<br>PH3<br>PH2<br>PH1<br>PH0 | Input/Output    | General Purpose I/O Signals - Port H              | 1     |

| 136<br>137<br>138<br>139<br>141<br>142<br>143<br>144 | PI7<br>PI6<br>PI5<br>PI4<br>PI3<br>PI2<br>PI1<br>PI0 | Input/Output    | General Purpose I/O Signals - Port I              | 1     |

|                                                      |                                                      |                 | , CLOCK, AND POWER CONTROLLER (RCPC)              | 1     |

| 62                                                   | nRESETIN                                             | Input           | User Reset Input                                  | 2     |

| 71<br>72                                             | nRESETOUT                                            | Output<br>Input | System Reset Output<br>External Interrupt Input 6 | 2     |

| 12                                                   |                                                      | input           |                                                   |       |

Table 3. LH75401 Signal Descriptions (Cont'd)

| Table 3. LH | I75401 Signal | Descriptions | (Cont'd) |

|-------------|---------------|--------------|----------|

|-------------|---------------|--------------|----------|

| PIN NO.                                               | SIGNAL NAME | TYPE   | DESCRIPTION                                                           | NOTES |

|-------------------------------------------------------|-------------|--------|-----------------------------------------------------------------------|-------|

| 73                                                    | INT5        | Input  | External Interrupt Input 5                                            | 1     |

| 74                                                    | INT4        | Input  | External Interrupt Input 4                                            | 1     |

| 76                                                    | INT3        | Input  | External Interrupt Input 3                                            | 1     |

| 77                                                    | INT2        | Input  | External Interrupt Input 2                                            | 1     |

| 78                                                    | INT1        | Input  | External Interrupt Input 1                                            | 1     |

| 79                                                    | INT0        | Input  | External Interrupt Input 0                                            | 1     |

| 81                                                    | nPOR        | Input  | Power-on Reset Input                                                  | 2     |

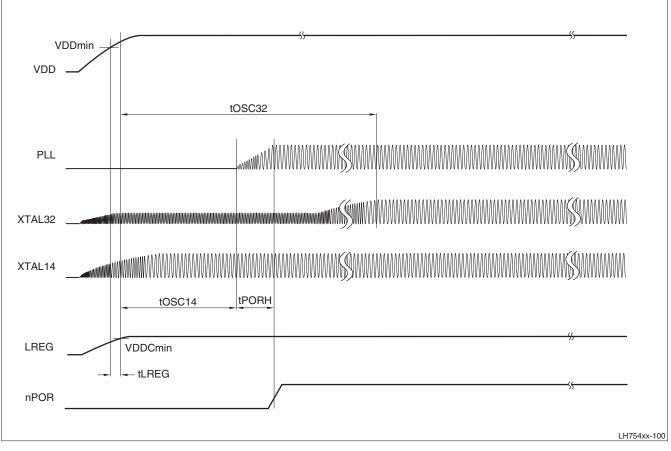

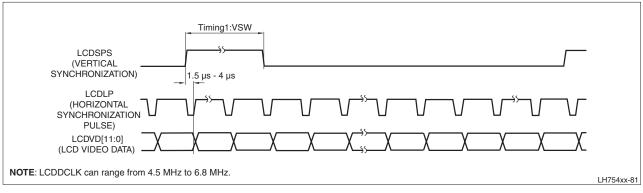

| 82                                                    | XTAL32IN    | Input  | 32.768 kHz Crystal Clock Input                                        |       |

| 83                                                    | XTAL32OUT   | Output | 32.768 kHz Crystal Clock Output                                       |       |

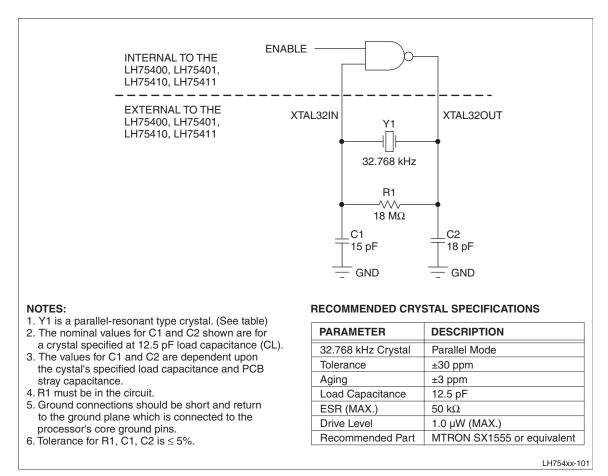

| 86                                                    | XTALIN      | Input  | Crystal Clock Input                                                   |       |

| 87                                                    | XTALOUT     | Output | Crystal Clock Output                                                  |       |

|                                                       |             |        | TEST INTERFACE                                                        |       |

| 63                                                    | TEST2       | Input  | Test Mode Pin 2                                                       |       |

| 64                                                    | TEST1       | Input  | Test Mode Pin 1                                                       |       |

| 65                                                    | TMS         | Input  | JTAG Test Mode Select Input                                           |       |

| 66                                                    | RTCK        | Output | Returned JTAG Test Clock Output                                       |       |

| 67                                                    | ТСК         | Input  | JTAG Test Clock Input                                                 |       |

| 68                                                    | TDI         | Input  | JTAG Test Serial Data Input                                           |       |

| 69                                                    | TDO         | Output | JTAG Test Data Serial Output                                          |       |

|                                                       |             |        | POWER AND GROUND (GND)                                                |       |

| 3<br>17<br>34<br>42<br>54<br>98<br>112<br>126<br>134  | VDD         | Power  | I/O Ring VDD                                                          |       |

| 8<br>26<br>41<br>48<br>59<br>106<br>119<br>127<br>140 | VSS         | Power  | I/O Ring VSS                                                          |       |

| 11<br>75                                              | VDDC        | Power  | Core VDD supply (Output if Linear Regulator Enabled, Otherwise Input) |       |

| 14<br>80                                              | VSSC        | Power  | Core VSS                                                              |       |

| 70                                                    | LINREGEN    | Input  | Linear Regulator Enable                                               |       |

| 84                                                    | VSSA_PLL    | Power  | PLL Analog VSS                                                        |       |

| 85                                                    | VDDA_PLL    | Power  | PLL Analog VDD Supply                                                 |       |

| 88                                                    | VSSA_ADC    | Power  | A-to-D converter Analog VSS                                           |       |

| 97                                                    | VDDA_ADC    | Power  | A-to-D converter Analog VDD Supply                                    |       |

#### NOTES:

These pin numbers have multiplexed functions.

Signals preceded with 'n' are active LOW.

## LH75411 Numerical Pin Listing

| Table 4. LITT STIT NUMERICAL FILLES | Table 4. | LH75411 | <b>Numerical Pin List</b> |

|-------------------------------------|----------|---------|---------------------------|

|-------------------------------------|----------|---------|---------------------------|

| PIN<br>NO. | FUNCTION<br>AT RESET | FUNCTION 2 | FUNCTION 3 | FUNCTION<br>TYPE | OUTPUT<br>DRIVE | BUFFER<br>TYPE | BEHAVIOR DURING<br>RESET | NOTES |

|------------|----------------------|------------|------------|------------------|-----------------|----------------|--------------------------|-------|

| 1          | PA7                  | D15        |            | I/O              | 8 mA            | Bidirectional  | Pull-up                  | 1     |

| 2          | PA6                  | D14        |            | I/O              | 8 mA            | Bidirectional  | Pull-up                  | 1     |

| 3          | VDD                  |            |            | Power            | None            |                |                          |       |

| 4          | PA5                  | D13        |            | I/O              | 8 mA            | Bidirectional  | Pull-up                  | 1     |

| 5          | PA4                  | D12        |            | I/O              | 8 mA            | Bidirectional  | Pull-up                  | 1     |

| 6          | PA3                  | D11        |            | I/O              | 8 mA            | Bidirectional  | Pull-up                  | 1     |

| 7          | PA2                  | D10        |            | I/O              | 8 mA            | Bidirectional  | Pull-up                  | 1     |

| 8          | VSS                  |            |            | Ground           | None            |                |                          |       |

| 9          | PA1                  | D9         |            | I/O              | 8 mA            | Bidirectional  | Pull-up                  | 1     |

| 10         | PA0                  | D8         |            | I/O              | 8 mA            | Bidirectional  | Pull-up                  | 1     |

| 11         | VDDC                 |            |            | Power            | None            |                |                          |       |

| 12         | D7                   |            |            | I/O              | 8 mA            | Bidirectional  | Pull-up                  |       |

| 13         | D6                   |            |            | I/O              | 8 mA            | Bidirectional  | Pull-up                  |       |

| 14         | VSSC                 |            |            | Ground           | None            |                |                          |       |

| 15         | D5                   |            |            | I/O              | 8 mA            | Bidirectional  | Pull-up                  |       |

| 16         | D4                   |            |            | I/O              | 8 mA            | Bidirectional  | Pull-up                  |       |

| 17         | VDD                  |            |            | Power            | None            |                |                          |       |

| 18         | D3                   |            |            | I/O              | 8 mA            | Bidirectional  | Pull-up                  |       |

| 19         | D2                   |            |            | I/O              | 8 mA            | Bidirectional  | Pull-up                  |       |

| 20         | D1                   |            |            | I/O              | 8 mA            | Bidirectional  | Pull-up                  |       |

| 21         | D0                   |            |            | I/O              | 8 mA            | Bidirectional  | Pull-up                  |       |

| 22         | nWE                  |            |            |                  | 8 mA            | Output         | HIGH                     | 3     |

| 23         | nOE                  |            |            |                  | 8 mA            | Output         | HIGH                     | 3     |

| 24         | PB5                  | nWAIT      |            |                  | 8 mA            | Bidirectional  | Pull-up                  | 1, 3  |

| 25         | PB4                  | nBLE1      |            |                  | 8 mA            | Bidirectional  | Pull-up                  | 1, 3  |

| 26         | VSS                  |            |            | Ground           | None            |                |                          |       |

| 27         | PB3                  | nBLE0      |            |                  | 8 mA            | Bidirectional  | Pull-up                  | 1, 3  |

| 28         | PB2                  | nCS3       |            |                  | 8 mA            | Bidirectional  | Pull-up                  | 1, 3  |

| 29         | PB1                  | nCS2       |            |                  | 8 mA            | Bidirectional  | Pull-up                  | 1, 3  |

| 30         | PB0                  | nCS1       |            |                  | 8 mA            | Bidirectional  | Pull-up                  | 1, 3  |

| 31         | nCS0                 |            |            |                  | 8 mA            | Output         | Pull-up                  | 3     |

| 32         | PC7                  | A23        |            |                  | 8 mA            | Bidirectional  | Pull-down                | 1     |

| 33         | PC6                  | A22        |            |                  | 8 mA            | Bidirectional  | Pull-down                | 1     |

| 34         | VDD                  |            |            | Power            | None            |                |                          |       |

| 35         | PC5                  | A21        |            |                  | 8 mA            | Bidirectional  | Pull-down                | 1     |

| 36         | PC4                  | A20        |            |                  | 8 mA            | Bidirectional  | Pull-down                | 1     |

| 37         | PC3                  | A19        |            |                  | 8 mA            | Bidirectional  | Pull-down                | 1     |

| 38         | PC2                  | A18        |            |                  | 8 mA            | Bidirectional  | Pull-down                | 1     |

| 39         | PC1                  | A17        |            |                  | 8 mA            | Bidirectional  | Pull-down                | 1     |

| 40         | PC0                  | A16        |            |                  | 8 mA            | Bidirectional  | Pull-down                | 1     |

| 41         | VSS                  |            |            | Ground           | None            |                |                          |       |

| PIN<br>NO. | FUNCTION<br>AT RESET | FUNCTION 2 | FUNCTION 3 | FUNCTION<br>TYPE | OUTPUT<br>DRIVE | BUFFER<br>TYPE | BEHAVIOR DURING<br>RESET | NOTES |

|------------|----------------------|------------|------------|------------------|-----------------|----------------|--------------------------|-------|

| 42         | VDD                  |            |            | Power            | None            |                |                          |       |

| 43         | A15                  |            |            |                  | 8 mA            | Output         | LOW                      |       |

| 44         | A14                  |            |            |                  | 8 mA            | Output         | LOW                      |       |

| 45         | A13                  |            |            |                  | 8 mA            | Output         | LOW                      |       |

| 46         | A12                  |            |            |                  | 8 mA            | Output         | LOW                      |       |

| 47         | A11                  |            |            |                  | 8 mA            | Output         | LOW                      |       |

| 48         | VSS                  |            |            | Ground           | None            |                |                          |       |

| 49         | A10                  |            |            |                  | 8 mA            | Output         | LOW                      |       |

| 50         | A9                   |            |            |                  | 8 mA            | Output         | LOW                      |       |

| 51         | A8                   |            |            |                  | 8 mA            | Output         | LOW                      |       |

| 52         | A7                   |            |            |                  | 8 mA            | Output         | LOW                      |       |

| 53         | A6                   |            |            |                  | 8 mA            | Output         | LOW                      |       |

| 54         | VDD                  |            |            | Power            | None            |                |                          |       |

| 55         | A5                   |            |            |                  | 8 mA            | Output         | LOW                      |       |

| 56         | A4                   |            |            |                  | 8 mA            | Output         | LOW                      |       |

| 57         | A3                   |            |            |                  | 8 mA            | Output         | LOW                      |       |

| 58         | A2                   |            |            |                  | 8 mA            | Output         | LOW                      |       |

| 59         | VSS                  |            |            | Ground           | None            |                |                          |       |

| 60         | A1                   |            |            |                  | 8 mA            | Output         | LOW                      |       |

| 61         | A0                   |            |            |                  | 8 mA            | Output         | LOW                      |       |

| 62         | nRESETIN             |            |            |                  | None            | Input          | Pull-up                  | 2, 3  |

| 63         | TEST2                |            |            |                  | None            | Input          | Pull-up                  | 2     |

| 64         | TEST1                |            |            |                  | None            | Input          | Pull-up                  | 2     |

| 65         | TMS                  |            |            |                  | None            | Input          | Pull-up                  | 2     |

| 66         | RTCK                 |            |            |                  | 8 mA            | Output         |                          |       |

| 67         | ТСК                  |            |            |                  | None            | Input          |                          |       |

| 68         | TDI                  |            |            |                  | None            | Input          | Pull-up                  | 2     |

| 69         | TDO                  |            |            |                  | 4 mA            | Output         |                          |       |

| 70         | LINREGEN             |            |            |                  | None            | Input          |                          | 5     |

| 71         | nRESETOUT            |            |            |                  | 8 mA            | Output         |                          | 3     |

| 72         | PD6                  | INT6       | DREQ       |                  | 6 mA            | Bidirectional  | Pull-down                | 1     |

| 73         | PD5                  | INT5       | DACK       |                  | 6 mA            | Bidirectional  |                          | 1, 2  |

| 74         | PD4                  | INT4       | UARTRX1    |                  | 8 mA            | Bidirectional  | Pull-up                  | 1     |

| 75         | VDDC                 |            |            | Power            | None            |                |                          |       |

| 76         | PD3                  | INT3       | UARTTX1    |                  | 8 mA            | Bidirectional  | Pull-up                  | 1     |

| 77         | PD2                  | INT2       |            |                  | 2 mA            | Bidirectional  | Pull-up                  | 1     |

| 78         | PD1                  | INT1       |            |                  | 6 mA            | Bidirectional  |                          | 1, 2  |

| 79         | PD0                  | INT0       |            |                  | 2 mA            | Bidirectional  |                          | 1     |

| 80         | VSSC                 |            |            | Ground           | None            |                |                          |       |

| 81         | nPOR                 |            |            |                  | None            | Input          | Pull-up                  | 2, 3  |

| 82         | XTAL32IN             |            |            |                  | None            | Input          |                          | 4     |

| 83         | XTAL32OUT            |            |            |                  | None            | Output         |                          |       |

### Table 4. LH75411 Numerical Pin List (Cont'd)

| PIN<br>NO. | FUNCTION<br>AT RESET | FUNCTION 2 | FUNCTION 3 | FUNCTION<br>TYPE | OUTPUT<br>DRIVE | BUFFER<br>TYPE | BEHAVIOR DURING<br>RESET | NOTES |

|------------|----------------------|------------|------------|------------------|-----------------|----------------|--------------------------|-------|

| 84         | VSSA_PLL             |            |            | Ground           | None            |                |                          |       |

| 85         | VDDA_PLL             |            |            | Power            | None            |                |                          |       |

| 86         | XTALIN               |            |            |                  | None            | Input          |                          | 4     |

| 87         | XTALOUT              |            |            |                  | None            | Output         |                          |       |

| 88         | VSSA_ADC             |            |            | Ground           | None            |                |                          |       |

| 89         | AN3 (LR/Y-)          | PJ7        |            |                  | None            | Input          |                          |       |

| 90         | AN4 (Wiper)          | PJ6        |            |                  | None            | Input          |                          |       |

| 91         | AN9                  | PJ5        |            |                  | None            | Input          |                          |       |

| 92         | AN2 (LL/Y+)          | PJ4        |            |                  | None            | Input          |                          |       |

| 93         | AN8                  | PJ3        |            |                  | None            | Input          |                          |       |

| 94         | AN1 (UR/X-)          | PJ2        |            |                  | None            | Input          |                          |       |

| 95         | AN6                  | PJ1        |            |                  | None            | Input          |                          |       |

| 96         | AN0 (UL/X+)          | PJ0        |            |                  | None            | Input          |                          |       |

| 97         | VDDA_ADC             |            |            | Power            | None            |                |                          |       |

| 98         | VDD                  |            |            | Power            | None            |                |                          |       |

| 99         | PE7                  | SSPFRM     |            |                  | 4 mA            | Bidirectional  | Pull-up                  | 1     |

| 100        | PE6                  | SSPCLK     |            |                  | 4 mA            | Bidirectional  | Pull-down                | 1     |

| 101        | PE5                  | SSPRX      |            |                  | 4 mA            | Bidirectional  | Pull-up                  | 1     |

| 102        | PE4                  | SSPTX      |            |                  | 4 mA            | Bidirectional  | Pull-down                | 1     |

| 103        | PE3                  | UARTTX0    |            |                  | 8 mA            | Bidirectional  | Pull-up                  | 1     |

| 104        | PE2                  | UARTRX0    |            |                  | 2 mA            | Bidirectional  | Pull-up                  | 1     |

| 105        | PE1                  | UARTTX2    |            |                  | 4 mA            | Bidirectional  | Pull-up                  | 1     |

| 106        | VSS                  |            |            | Ground           | None            |                |                          |       |

| 107        | PE0                  | UARTRX2    |            |                  | 4 mA            | Bidirectional  | Pull-up                  | 1     |

| 108        | PF6                  | CTCAP2B    | CTCMP2B    |                  | 4 mA            | Bidirectional  |                          | 2     |

| 109        | PF5                  | CTCAP2A    | CTCMP2A    |                  | 4 mA            | Bidirectional  |                          |       |

| 110        | PF4                  | CTCAP1B    | CACMP1B    |                  | 4 mA            | Bidirectional  |                          | 2     |

| 111        | PF3                  | CTCAP1A    | CTCMP1A    |                  | 4 mA            | Bidirectional  |                          |       |

| 112        | VDD                  |            |            | Power            | None            |                |                          |       |

| 113        | PF2                  | CTCAP0E    |            |                  | 4 mA            | Bidirectional  |                          | 2     |

| 114        | PF1                  | CTCAP0D    |            |                  | 4 mA            | Bidirectional  |                          |       |

| 115        | PF0                  | CTCAP0C    |            |                  | 4 mA            | Bidirectional  |                          | 2     |

| 116        | PG7                  | CTCAP0B    | CTCMP0B    |                  | 4 mA            | Bidirectional  |                          |       |

| 117        | PG6                  | CTCAP0A    | CTCMP0A    |                  | 4 mA            | Bidirectional  |                          | 2     |

| 118        | PG5                  | CTCLK      |            |                  | 4 mA            | Bidirectional  |                          |       |

| 119        | VSS                  |            |            | Ground           | None            |                |                          |       |

| 120        | PG4                  | LCDVEEEN   | LCDMOD     |                  | 8 mA            | Bidirectional  |                          |       |

| 121        | PG3                  | LCDVDDEN   |            |                  | 8 mA            | Bidirectional  |                          |       |

| 122        | PG2                  | LCDDSPLEN  | LCDREV     |                  | 8 mA            | Bidirectional  |                          |       |

| 123        | PG1                  | LCDCLS     |            |                  | 8 mA            | Bidirectional  |                          |       |

| 124        | PG0                  | LCDPS      |            |                  | 8 mA            | Bidirectional  |                          |       |

| 125        | PH7                  | LCDDCLK    |            |                  | 8 mA            | Bidirectional  |                          |       |

### Table 4. LH75411 Numerical Pin List (Cont'd)

Downloaded from  $\underline{\text{Elcodis.com}}$  electronic components distributor

| PIN<br>NO. | FUNCTION<br>AT RESET | FUNCTION 2 | FUNCTION 3 | FUNCTION<br>TYPE | OUTPUT<br>DRIVE | BUFFER<br>TYPE | BEHAVIOR DURING<br>RESET | NOTES |

|------------|----------------------|------------|------------|------------------|-----------------|----------------|--------------------------|-------|

| 126        | VDD                  |            |            | Power            | None            |                |                          |       |

| 127        | VSS                  |            |            | Ground           | None            |                |                          |       |

| 128        | PH6                  | LCDLP      | LCDHRLP    |                  | 8 mA            | Bidirectional  |                          |       |

| 129        | PH5                  | LCDFP      | LCDSPS     |                  | 8 mA            | Bidirectional  |                          |       |

| 130        | PH4                  | LCDEN      | LCDSPL     |                  | 8 mA            | Bidirectional  |                          |       |

| 131        | PH3                  | LCDVD11    |            |                  | 8 mA            | Bidirectional  |                          |       |

| 132        | PH2                  | LCDVD10    |            |                  | 8 mA            | Bidirectional  |                          |       |

| 133        | PH1                  | LCDVD9     |            |                  | 8 mA            | Bidirectional  |                          |       |

| 134        | VDD                  |            |            | Power            | None            |                |                          |       |

| 135        | PH0                  | LCDVD8     |            |                  | 8 mA            | Bidirectional  |                          |       |

| 136        | PI7                  | LCDVD7     |            |                  | 8 mA            | Bidirectional  |                          |       |

| 137        | PI6                  | LCDVD6     |            |                  | 8 mA            | Bidirectional  |                          |       |

| 138        | PI5                  | LCDVD5     |            |                  | 8 mA            | Bidirectional  |                          |       |

| 139        | Pl4                  | LCDVD4     |            |                  | 8 mA            | Bidirectional  |                          |       |

| 140        | VSS                  |            |            | Ground           | None            |                |                          |       |

| 141        | PI3                  | LCDVD3     |            |                  | 8 mA            | Bidirectional  |                          |       |

| 142        | Pl2                  | LCDVD2     |            |                  | 8 mA            | Bidirectional  |                          |       |

| 143        | Pl1                  | LCDVD1     |            |                  | 8 mA            | Bidirectional  |                          |       |

| 144        | PI0                  | LCDVD0     |            |                  | 8 mA            | Bidirectional  |                          |       |

#### Table 4. LH75411 Numerical Pin List (Cont'd)

#### NOTES:

1. Signal is selectable as pull-up, pull-down, or no pull-up/pull-down via the I/O Configuration peripheral.

2. CMOS Schmitt trigger input.

3. Signals preceded with 'n' are active LOW.

4. Crystal Oscillator Inputs should be driven to 1.8 V  $\pm$ 10 % (MAX.)

5. LINREGEN activation requires a 0  $\Omega$  pull-up to VDD.

18

## LH75411 Signal Descriptions

| Table 5. | LH75411 | Signal | Descriptions |

|----------|---------|--------|--------------|

|----------|---------|--------|--------------|

| PIN NO.                                                                                                                                                | SIGNAL NAME | TYPE         | DESCRIPTION                                    | NOTES |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--------------|------------------------------------------------|-------|--|--|

|                                                                                                                                                        |             |              | MEMORY INTERFACE (MI)                          |       |  |  |