### **SPEAR-09-H042**

SPEAr™ Head200

## ARM 926, 200 K customizable eASIC™ gates, large IP portfolio SoC

Data Brief

#### **Features**

- ARM926EJ-S f<sub>MAX</sub> 266 MHz, 32 KI - 16 KD cache, 8 KI - KD TCM, ETM9 and JTAG interfaces

- 200K customizable equivalent ASIC gates (16K LUT equivalent) with 8 channels internal DMA high speed accelerator function and 87 dedicated general purpose I/Os

- Multilayer AMBA 2.0 compliant bus with f<sub>MAX</sub> 133 MHz

- Programmable internal clock generator with enhanced PLL function, specially optimized for E.M.I. reduction

- 16 KB single port SRAM embedded

- Dynamic RAM interface: 8/16 bit DDR, 8/16 bit SDRAM

- SPI interface connecting serial ROM and Flash devices

- 2 USB 2.0 Host independent ports with integrated PHYs

- USB 2.0 device with integrated PHY

- Ethernet MAC 10/100 with MII management interface

- 1 independent UART up to 115 Kbps (software flow control mode)

- I<sup>2</sup>C master mode fast and slow speed

- 6 general purpose I/Os

- Real time clock

- WatchDog

- 4 general purpose timers

- Operating temperature: 40 to 85 °C

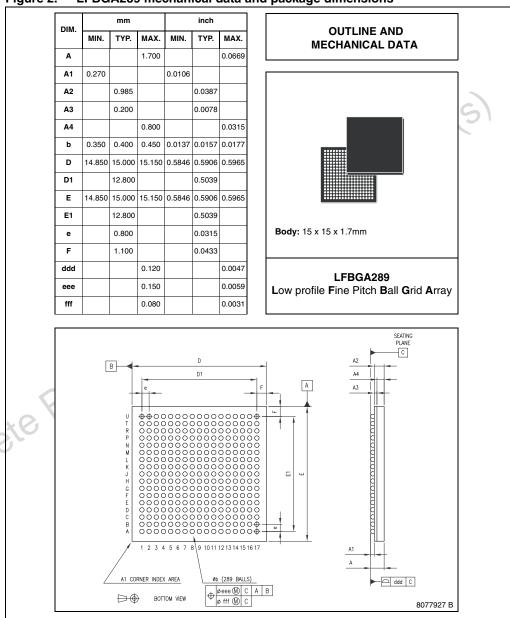

- Package: LF3GA289 (15x15x1.7mm pitch 0.8mm)

#### Description

SPEAr Head200 is a powerful digital engine belonging to SPEAr family, the innovative customizable system-on-chip.

The device integrates an ARM core with a large set of proven IPs (Intellectual Properties) and a configurable logic block that allows very fast customization of unique and/or proprietary solutions, with low effort and low investment.

Optimized for embedded applications.

Table 1. Device summary

| Order code    | Package                | Packing |

|---------------|------------------------|---------|

| SPEAR-09-H042 | LFBGA289 (15x15x1.7mm) | Tray    |

January 2008 Rev 1 1/16

Contents SPEAR-09-H042

### **Contents**

| 1   | Intro | duction 3                         |

|-----|-------|-----------------------------------|

| 2   | Feat  | ures modification                 |

|     | 2.1   | Analog to digital converter (ADC) |

|     | 2.2   | eASIC GPIOs                       |

|     | 2.3   | External FPGA emulation mode      |

|     | 2.4   | Dynamic RAM data path4            |

|     | 2.5   | UARTs 4                           |

| 3   | Pin o | description5                      |

|     | 3.1   | Interface signals                 |

|     | 3.2   | Power connections 11              |

|     | 3.3   | Ballout top view                  |

| 4   | Pack  | ade outline assembly              |

| 5   | Revi  | sion history                      |

| 005 | olete | Product(s)                        |

SPEAR-09-H042 Introduction

### 1 Introduction

This data brief describes the differences between SPEAr Head200 (SPEAR-09-H022) and the one packaged in LFBGA289 balls 0.8mm pitch (SPEAR-09-H042).

In this document the main package characteristics are described as well as the chip features modifications.

The reference specifications, for the SPEAR-09-H022 are available on the web at: www.st.com.

Features modification SPEAR-09-H042

#### 2 Features modification

To fit the new small package a number of features has been reduced or limited:

- Analog to digital converter (ADC)

- eASIC GPIOs

- External FPGA emulation mode

- Dynamic RAM data path

- UARTs

#### 2.1 Analog to digital converter (ADC)

ADC feature has been completely deleted so the 16 analog channels, the related test output, the power balls and the reference voltages have been removed.

#### 2.2 eASIC GPIOs

SPEAR-09-H022 features 112 GPIOs in the eASIC customizable part, some of these I/Os have been removed, but 87 are still available on SPEAR-09-H042.

Unusable hidden eASIC GPIOs (74, 76, 78, 80, 82, 84, 86, 88, 90, 92, 94, 96, 98, 100-111) must be configured as inputs.

### 2.3 External FPGA emulation mode

SPEAR-09-H022 has the capability to emulate the internal eASIC behavior with an external FPGA through the component GPIOs. This feature has been completely removed on SPEAR-09-H042 hence the development boards must use the 420 PBGA components.

#### 2.4 Dynamic RAM data path

The SPEAr component features a multi purpose memory controller to interface SDRAM or DDR memories able to work with different data path widths.

While SPEAR-09-H022 handles 8 and 16-bit DDRs or 8, 16 and 32-bit SDRAMs, on SPEAR-09-H042 to save 16 data balls and the related "data mask" balls, the SDRAM data path has been limited to 16-bit like the DDR one.

#### 2.5 UARTs

Two of the original UART interfaces have been removed, SPEAR-09-H042 features just the UART1 interface.

57

# 3 Pin description

Table 2 shows the component signals, grouped by function, and the relative ballout diagram.

# 3.1 Interface signals

Table 2. Interface signals

| Group | Signal Name    | Ball | Direction | Function                                                                  |

|-------|----------------|------|-----------|---------------------------------------------------------------------------|

|       | TEST0          | A14  |           |                                                                           |

|       | TEST1          | H14  |           |                                                                           |

| Debug | TEST2          | H13  | Input     | Test configuration port. For the functional mode they have to be set to 0 |

|       | TEST3          | H12  |           | 16                                                                        |

|       | PLL_BYPASS     | G1   | Input     | Enable / disable PLL bypass                                               |

| eASIC | eASICGP_IO[00] | G4   | I/O       | eASIC general purpose I/O                                                 |

|       | eASICGP_IO[01] | H7   |           | 00.0                                                                      |

|       | eASICGP_IO[02] | H6   |           | 010                                                                       |

|       | eASICGP_IO[03] | H5   | × (       | 2                                                                         |

|       | eASICGP_IO[04] | F3   | 16/       |                                                                           |

|       | eASICGP_IO[05] | E4   | CO,       |                                                                           |

|       | eASICGP_IO[06] | F5   |           |                                                                           |

|       | eASICGP_IO[07] | D2   |           |                                                                           |

|       | eASICGP_IO[08] | E3   |           |                                                                           |

|       | eASICGP_IO[09] | D3   |           |                                                                           |

|       | eASICGP_IO[10] | D1   |           |                                                                           |

|       | eASICGP_IO[11] | G6   |           |                                                                           |

| 01    | eASICGP_IO[12] | G7   |           |                                                                           |

| x6,   | eASICGP_IO[13] | D4   |           |                                                                           |

|       | eASICGP_IO[14] | C1   |           |                                                                           |

|       | eASICGP_IO[15] | E5   |           |                                                                           |

|       | eASICGP_IO[16] | F6   |           |                                                                           |

|       | eASICGP_IO[17] | B1   |           |                                                                           |

|       | eASICGP_IO[18] | E6   |           |                                                                           |

|       | eASICGP_IO[19] | B4   |           |                                                                           |

|       | eASICGP_IO[20] | F7   |           |                                                                           |

|       | eASICGP_IO[21] | A1   |           |                                                                           |

Pin description SPEAR-09-H042

Table 2. Interface signals (continued)

| Group | Signal Name    | Ball | Direction | Function     |

|-------|----------------|------|-----------|--------------|

|       | eASICGP_IO[22] | А3   |           |              |

|       | eASICGP_IO[23] | A4   |           |              |

|       | eASICGP_IO[24] | C2   |           |              |

|       | eASICGP_IO[25] | F4   |           |              |

|       | eASICGP_IO[26] | СЗ   |           |              |

|       | eASICGP_IO[27] | C5   |           |              |

|       | eASICGP_IO[28] | B5   |           |              |

|       | eASICGP_IO[29] | H8   |           |              |

|       | eASICGP_IO[30] | B2   |           |              |

|       | eASICGP_IO[31] | G5   |           |              |

|       | eASICGP_IO[32] | В3   |           |              |

|       | eASICGP_IO[33] | A2   |           | 4(5)         |

|       | eASICGP_IO[34] | C4   |           | IC!          |

|       | eASICGP_IO[35] | A5   |           | 20/0,        |

|       | eASICGP_IO[36] | H9   |           | 010          |

|       | eASICGP_IO[37] | C6   | . (       |              |

|       | eASICGP_IO[38] | G9   | 10.1      |              |

|       | eASICGP_IO[39] | C7   | ~O/O      | e Product(s) |

|       | eASICGP_IO[40] | D5   | 25        |              |

|       | eASICGP_IO[41] | B6   |           |              |

|       | eASICGP_IO[42] | A6   |           |              |

|       | eASICGP_IO[43] | G8   |           |              |

|       | eASICGP_IO[44] | E8   |           |              |

|       | eASICGP_IO[45] | E9   |           |              |

| 01    | eASICGP_IO[46] | D8   |           |              |

| .0.   | eASICGP_IO[47] | В7   |           |              |

|       | eASICGP_IO[48] | E7   |           |              |

|       | eASICGP_IO[49] | F8   |           |              |

|       | eASICGP_IO[50] | A7   |           |              |

|       | eASICGP_IO[51] | B8   |           |              |

|       | eASICGP_IO[52] | A8   |           |              |

|       | eASICGP_IO[53] | D9   |           |              |

|       | eASICGP_IO[54] | D6   |           |              |

|       | eASICGP_IO[55] | F9   |           |              |

|       | eASICGP_IO[56] | D7   |           |              |

Table 2. Interface signals (continued)

| Group    | Signal Name       | Ball | Direction | Function                          |

|----------|-------------------|------|-----------|-----------------------------------|

|          | eASICGP_IO[57]    | F10  |           |                                   |

|          | eASICGP_IO[58]    | C9   |           |                                   |

|          | eASICGP_IO[59]    | В9   |           |                                   |

|          | eASICGP_IO[60]    | A9   |           |                                   |

|          | eASICGP_IO[61]    | G10  |           |                                   |

|          | eASICGP_IO[62]    | C8   |           |                                   |

|          | eASICGP_IO[63]    | E10  |           |                                   |

|          | eASICGP_IO[64]    | D10  |           |                                   |

|          | eASICGP_IO[65]    | C10  |           |                                   |

|          | eASICGP_IO[66]    | B10  |           |                                   |

|          | eASICGP_IO[67]    | A10  |           |                                   |

|          | eASICGP_IO[68]    | G11  |           | ,(5)                              |

|          | eASICGP_IO[69]    | F11  |           | IC/                               |

|          | eASICGP_IO[70]    | E11  |           | 90,0                              |

|          | eASICGP_IO[71]    | D11  |           | 010                               |

|          | eASICGP_IO[72]    | C11  | . (       |                                   |

|          | eASICGP_IO[73-74] | B11  | 101       |                                   |

|          | eASICGP_IO[75-76] | A11  | ~O/O      | e Product(s)                      |

|          | eASICGP_IO[77-78] | A12  | 75        |                                   |

|          | eASICGP_IO[79-80] | B12  |           |                                   |

|          | eASICGP_IO[81-82] | C12  |           |                                   |

|          | eASICGP_IO[83-84] | D12  |           |                                   |

|          | eASICGP_IO[85-86] | E12  |           |                                   |

|          | eASICGP_IO[87-88] | A13  |           |                                   |

| 01       | eASICGP_IO[89-90] | B13  |           |                                   |

| W.C. Y   | eASICGP_IO[91-92] | C13  |           |                                   |

|          | eASICGP_IO[93-94] | D13  |           |                                   |

|          | eASICGP_IO[95-96] | E13  |           |                                   |

|          | eASICGP_IO[97-98] | C14  |           |                                   |

|          | eASICGP_IO[99]    | D14  |           |                                   |

|          | eASIC_EXT_CLOCK   | E14  |           |                                   |

|          | eASIC_PI_CLOCK    | K15  |           | eASIC program interface out clock |

| Ethernet | TX_CLK            | C15  | Input     | Ethernet input TX clock           |

|          | TXD[0]            | C16  |           | Ethernet TX output data           |

|          | TXD[1]            | C17  |           | Ethernet TX output data           |

Pin description SPEAR-09-H042

Table 2. Interface signals (continued)

| Group         Signal Name         Ball         Direction         Function           TXD[2]         D15         Output         Ethernet TX output data Ethernet TX output data Ethernet TX output data Ethernet TX enable           TX_EN         D17         Ethernet TX enable           CRS         E15         Input         Carrier sense input           COL         E16         Collision detection input           RX_CLK         E17         Input         Ethernet input RX clock           RXD[0]         F15         Input         Ethernet RX input data           RXD[1]         F16         Input         Data valid on RX           RX_D[2]         F17         Input         Data valid on RX           RX_D[3]         G15         Input         Data error detected           MDC         H15         Output         Output timing reference           MDIO         H16         I/O         I/O data to PHY | a a a a a a a a a a a a a a a a a a a |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|

| TXD[3] D16  TX_EN D17  CRS E15 Input Carrier sense input  COL E16  RX_CLK E17 Input Ethernet input RX clock  RXD[0] F15  RXD[1] F16 Input Ethernet RX input data  RXD[2] F17  RXD[3] G15  RX_DV G16 Input Data valid on RX  RX_ER G17 Input Data error detected  MDC H15 Output Output timing reference  MDIO H16 I/O I/O data to PHY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | ut<br>k                               |

| TX_EN D17  CRS E15 Input Carrier sense input COL E16 Collision detection input RX_CLK E17 Input Ethernet input RX clock RXD[0] F15 RXD[1] F16 Input Ethernet RX input data RXD[2] F17 RXD[3] G15 RX_DV G16 Input Data valid on RX RX_ER G17 Input Data error detected MDC H15 Output Output timing reference MDIO H16 I/O I/O data to PHY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ut<br>k                               |

| CRS E15 Input Carrier sense input COL E16 Collision detection input RX_CLK E17 Input Ethernet input RX clock RXD[0] F15 RXD[1] F16 Input Ethernet RX input data RXD[2] F17 RXD[3] G15 RX_DV G16 Input Data valid on RX RX_ER G17 Input Data error detected MDC H15 Output Output timing reference MDIO H16 I/O I/O data to PHY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | k                                     |

| COL E16 Collision detection input  RX_CLK E17 Input Ethernet input RX clock  RXD[0] F15  RXD[1] F16 Input Ethernet RX input data  RXD[2] F17  RXD[3] G15  RX_DV G16 Input Data valid on RX  RX_ER G17 Input Data error detected  MDC H15 Output Output timing reference  MDIO H16 I/O I/O data to PHY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | k                                     |

| RX_CLK E17 Input Ethernet input RX clock RXD[0] F15 RXD[1] F16 Input Ethernet RX input data RXD[2] F17 RXD[3] G15 RX_DV G16 Input Data valid on RX RX_ER G17 Input Data error detected MDC H15 Output Output timing reference MDIO H16 I/O I/O data to PHY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | k                                     |

| RXD[0] F15 RXD[1] F16 Input Ethernet RX input data RXD[2] F17 RXD[3] G15 RX_DV G16 Input Data valid on RX RX_ER G17 Input Data error detected MDC H15 Output Output timing reference MDIO H16 I/O I/O data to PHY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | (5)                                   |

| RXD[1] F16 Input Ethernet RX input data  RXD[2] F17  RXD[3] G15  RX_DV G16 Input Data valid on RX  RX_ER G17 Input Data error detected  MDC H15 Output Output timing reference  MDIO H16 I/O I/O data to PHY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | (6)                                   |

| RXD[2] F17 RXD[3] G15 RX_DV G16 Input Data valid on RX RX_ER G17 Input Data error detected MDC H15 Output Output timing reference MDIO H16 I/O I/O data to PHY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | (6)                                   |

| RXD[3] G15  RX_DV G16 Input Data valid on RX  RX_ER G17 Input Data error detected  MDC H15 Output Output timing reference  MDIO H16 I/O I/O data to PHY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | (5)                                   |

| RX_DV G16 Input Data valid on RX RX_ER G17 Input Data error detected  MDC H15 Output Output timing reference  MDIO H16 I/O I/O data to PHY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | (9)                                   |

| RX_ER G17 Input Data error detected  MDC H15 Output Output timing reference  MDIO H16 I/O I/O data to PHY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | (6)                                   |

| MDC H15 Output Output timing reference MDIO H16 I/O I/O data to PHY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 5                                     |

| MDIO H16 I/O I/O data to PHY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | . C P.4D10                            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | e for MDIO                            |

| OD IOIOI MAS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                       |

| GP_IO[0] M15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                       |

| GP_IO[1] L17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                       |

| GPI/Os GP_IO[2] L16 I/O General purpose I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                       |

| GP_IO[3] L15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                       |

| GP_IO[4] K17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                       |

| GP_IO[5] K16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                       |

| I2C SDA H17 I/O I2C serial data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                       |

| SCL J15 Output I2C clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                       |

| TDO F12 Output JTAG TDO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                       |

| TDI F13 Input JTAG TDI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                       |

| JTAG TMS F14 Input JTAG TMS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                       |

| RTCK G12 Output JTAG output clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                       |

| TCK G13 Input JTAG clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                       |

| nTRST G14 Output JTAG reset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                       |

| Master MCLK_in N1 Input 12MHz input crystal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                       |

| clock MCLK_out N2 Output 12MHz output crystal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                       |

| Master reset MRESET G3 Input Master reset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                       |

| MPMC MPMCDATA[00] T12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                       |

| MPMCDATA[01] R12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                       |

| MPMCDATA[02] T13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                       |

| MPMCDATA[03] R13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                       |

Table 2. Interface signals (continued)

| Group   Signal Name   Ball   Direction   Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |       | Signal Name     |      | r e       | Franchica                |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-----------------|------|-----------|--------------------------|

| MPMCDATA[05]         R14           MPMCDATA[06]         T15           MPMCDATA[07]         R15           MPMCDATA[08]         T17           MPMCDATA[09]         P16           MPMCDATA[10]         P17           MPMCDATA[11]         N15           MPMCDATA[12]         N16           MPMCDATA[13]         N17           MPMCADTA[14]         M16           MPMCADDROUT[00]         R6           MPMCADDROUT[01]         U7           MPMCADDROUT[02]         T7           MPMCADDROUT[03]         R7           MPMCADDROUT[04]         U8           MPMCADDROUT[05]         T8           MPMCADDROUT[06]         R8           MPMCADDROUT[07]         U9           MPMCADDROUT[08]         T9           MPMCADDROUT[10]         U10           MPMCADDROUT[10]         U10           MPMCADDROUT[11]         T10           MPMCADDROUT[12]         R10           MPMCADDROUT[13]         T11           MPMCADDROUT[14]         R11           nMPMCDYCSOUT[1]         T4           nMPMCDYCSOUT[2]         T5           nMPMCDYCSOUT[2]         T5           nMPMCCKEOUT[0]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Group | Signal Name     | Ball | Direction | Function                 |

| MPMCDATA[06]   T15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |       |                 |      |           |                          |

| MPMCDATA[07]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |       |                 | R14  |           |                          |

| MPMCDATA[08]   T17     MPMCDATA[09]   P16     MPMCDATA[10]   P17     MPMCDATA[11]   N15     MPMCDATA[12]   N16     MPMCDATA[13]   N17     MPMCDATA[14]   M16     MPMCDATA[15]   M17     MPMCDATA[15]   M17     MPMCDATA[15]   M17     MPMCADROUT[0]   R6     MPMCADROUT[0]   T7     MPMCADDROUT[03]   R7     MPMCADDROUT[04]   U8     MPMCADDROUT[05]   T8     MPMCADDROUT[06]   R8     MPMCADDROUT[07]   U9     MPMCADDROUT[08]   T9     MPMCADDROUT[08]   T9     MPMCADDROUT[10]   U10     MPMCADDROUT[11]   T10     MPMCADDROUT[12]   R10     MPMCADDROUT[13]   T11     MPMCADDROUT[14]   R11     nMPMCDYCSOUT[0]   U4     nMPMCDYCSOUT[0]   U4     nMPMCDYCSOUT[1]   T4     nMPMCDYCSOUT[2]   T5     nMPMCCKEOUT[0]   U11   Output     MPMCCKEOUT[0]   U12     MPMCCKEOUT[1]   U12     MPMCCKEOUT[1]   U12     MPMCCKEOUT[1]   U12     MPMCCKEOUT[1]   U16     MPMCCKEOU |       | MPMCDATA[06]    | T15  |           |                          |

| MPMCDATA[09]   P16     MPMCDATA[10]   P17     MPMCDATA[11]   N15     MPMCDATA[12]   N16     MPMCDATA[13]   N17     MPMCDATA[13]   N17     MPMCDATA[15]   M17     MPMCADROUT[00]   R6     MPMCADROUT[01]   U7     MPMCADROUT[02]   T7     MPMCADROUT[03]   R7     MPMCADROUT[04]   U8     MPMCADROUT[06]   R8     MPMCADROUT[06]   R8     MPMCADROUT[06]   R9     MPMCADROUT[08]   T9     MPMCADROUT[10]   U10     MPMCADROUT[10]   U10     MPMCADROUT[11]   T10     MPMCADROUT[12]   R10     MPMCADROUT[14]   R11     MPMCADROUT[14]   R11     MPMCADROUT[14]   R11     MPMCADROUT[15]   T5     MPMCCYCSOUT[0]   U4     MMPMCDYCSOUT[1]   T4     MMPMCDYCSOUT[2]   T5     MMPMCDYCSOUT[3]   R5     MPMCCKEOUT[0]   U11     MPMCCKEOUT[1]   U12     MPMCCKEOUT[1]   U12     MPMCCKEOUT[1]   U12     MPMCCKEOUT[1]   U16     M |       | MPMCDATA[07]    | R15  | I/O       | DDR / SDRAM data         |

| MPMCDATA[10]   P17     MPMCDATA[11]   N15     MPMCDATA[12]   N16     MPMCDATA[13]   N17     MPMCDATA[14]   M16     MPMCDATA[15]   M17     MPMCADDROUT[00]   R6     MPMCADDROUT[01]   U7     MPMCADDROUT[02]   T7     MPMCADDROUT[03]   R7     MPMCADDROUT[04]   U8     MPMCADDROUT[05]   T8     MPMCADDROUT[06]   R8     MPMCADDROUT[06]   R9     MPMCADDROUT[07]   U9     MPMCADDROUT[08]   T9     MPMCADDROUT[09]   R9     MPMCADDROUT[09]   R9     MPMCADDROUT[10]   U10     MPMCADDROUT[11]   T10     MPMCADDROUT[12]   R10     MPMCADDROUT[14]   R11     nMPMCDYCSOUT[0]   U4     nMPMCDYCSOUT[0]   U4     nMPMCDYCSOUT[1]   T4     nMPMCDYCSOUT[2]   T5     nMPMCCKEOUT[1]   U12     MPMCCKEOUT[1]   U12     MPMCCKEOUT[1]   U12     MPMCCKEOUT[1]   U12     MPMCCKEOUT[1]   U12     MPMCCKEOUT[0]   U16     DDR / SDRAM clock enable     DDR / SDRAM clock 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |       | MPMCDATA[08]    | T17  |           |                          |

| MPMCDATA[11]         N15           MPMCDATA[12]         N16           MPMCDATA[13]         N17           MPMCDATA[14]         M16           MPMCADDROUT[00]         R6           MPMCADDROUT[01]         U7           MPMCADDROUT[02]         T7           MPMCADDROUT[04]         U8           MPMCADDROUT[05]         T8           MPMCADDROUT[06]         R8           MPMCADDROUT[07]         U9           MPMCADDROUT[09]         T9           MPMCADDROUT[09]         R9           MPMCADDROUT[10]         U10           MPMCADDROUT[11]         T10           MPMCADDROUT[12]         R10           MPMCADDROUT[13]         T11           MPMCADDROUT[14]         R11           nMPMCDYCSOUT[0]         U4           nMPMCDYCSOUT[1]         T4           nMPMCDYCSOUT[2]         T5           nMPMCCKEOUT[0]         U11           MPMCCKEOUT[1]         U12           MPMCCKEOUT[0]         U16           DDR / SDRAM clock 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |       | MPMCDATA[09]    | P16  |           |                          |

| MPMCDATA[12]         N16           MPMCDATA[13]         N17           MPMCDATA[14]         M16           MPMCDATA[15]         M17           MPMCADDROUT[00]         R6           MPMCADDROUT[01]         U7           MPMCADDROUT[02]         T7           MPMCADDROUT[04]         U8           MPMCADDROUT[05]         T8           MPMCADDROUT[06]         R8           MPMCADDROUT[07]         U9           MPMCADDROUT[08]         T9           MPMCADDROUT[09]         R9           MPMCADDROUT[10]         U10           MPMCADDROUT[11]         T10           MPMCADDROUT[12]         R10           MPMCADDROUT[14]         R11           nMPMCDYCSOUT[0]         U4           nMPMCDYCSOUT[1]         T4           nMPMCDYCSOUT[2]         T5           nMPMCDYCSOUT[3]         R5           MPMCCKEOUT[0]         U11           MPMCCKEOUT[1]         U12           MPMCCLKOUT[0]         U16           DDR / SDRAM clock 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |       | MPMCDATA[10]    | P17  |           |                          |

| MPMCDATA[13]         N17           MPMCDATA[14]         M16           MPMCADDROUT[00]         R6           MPMCADDROUT[01]         U7           MPMCADDROUT[02]         T7           MPMCADDROUT[03]         R7           MPMCADDROUT[04]         U8           MPMCADDROUT[05]         T8           MPMCADDROUT[06]         R8           MPMCADDROUT[07]         U9           MPMCADDROUT[08]         T9           MPMCADDROUT[09]         R9           MPMCADDROUT[10]         U10           MPMCADDROUT[11]         T10           MPMCADDROUT[12]         R10           MPMCADDROUT[14]         R11           nMPMCDYCSOUT[1]         T4           nMPMCDYCSOUT[2]         T5           nMPMCDYCSOUT[2]         T5           nMPMCCYCSOUT[3]         R5           MPMCCKEOUT[0]         U11         Output         DDR / SDRAM clock enable           MPMCCKEOUT[1]         U16         DDR / SDRAM clock 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |       | MPMCDATA[11]    | N15  |           |                          |

| MPMCDATA[14]         M16           MPMCDATA[15]         M17           MPMCADDROUT[00]         R6           MPMCADDROUT[01]         U7           MPMCADDROUT[02]         T7           MPMCADDROUT[03]         R7           MPMCADDROUT[04]         U8           MPMCADDROUT[05]         T8           MPMCADDROUT[06]         R8           MPMCADDROUT[07]         U9           MPMCADDROUT[08]         T9           MPMCADDROUT[09]         R9           MPMCADDROUT[10]         U10           MPMCADDROUT[11]         T10           MPMCADDROUT[12]         R10           MPMCADDROUT[13]         T11           MPMCADDROUT[14]         R11           nMPMCDYCSOUT[1]         T4         Output         DDR / SDRAM chip select           nMPMCDYCSOUT[2]         T5         nMPMCDYCSOUT[3]         R5           MPMCCKEOUT[0]         U11         Output         DDR / SDRAM clock enable           MPMCCKEOUT[1]         U12         DDR / SDRAM clock 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |       | MPMCDATA[12]    | N16  |           |                          |

| MPMCADDROUT[00]         R6           MPMCADDROUT[01]         U7           MPMCADDROUT[02]         T7           MPMCADDROUT[03]         R7           MPMCADDROUT[04]         U8           MPMCADDROUT[05]         T8           MPMCADDROUT[06]         R8           MPMCADDROUT[07]         U9         Output           MPMCADDROUT[08]         T9           MPMCADDROUT[09]         R9           MPMCADDROUT[10]         U10           MPMCADDROUT[11]         T10           MPMCADDROUT[12]         R10           MPMCADDROUT[13]         T11           MPMCADDROUT[14]         R11           nMPMCDYCSOUT[0]         U4           nMPMCDYCSOUT[1]         T4         Output         DDR / SDRAM chip select           nMPMCCYCSOUT[3]         R5           MPMCCKEOUT[0]         U11         Output         DDR / SDRAM clock enable           MPMCCKEOUT[1]         U12         DDR / SDRAM clock 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |       | MPMCDATA[13]    | N17  |           |                          |

| MPMCADDROUT[00]         R6           MPMCADDROUT[01]         U7           MPMCADDROUT[02]         T7           MPMCADDROUT[03]         R7           MPMCADDROUT[04]         U8           MPMCADDROUT[05]         T8           MPMCADDROUT[06]         R8           MPMCADDROUT[07]         U9           MPMCADDROUT[08]         T9           MPMCADDROUT[10]         U10           MPMCADDROUT[10]         U10           MPMCADDROUT[11]         T10           MPMCADDROUT[12]         R10           MPMCADDROUT[14]         R11           nMPMCADDROUT[14]         R11           nMPMCDYCSOUT[0]         U4           nMPMCDYCSOUT[1]         T4           nMPMCDYCSOUT[2]         T5           nMPMCCKEOUT[0]         U11           MPMCCKEOUT[1]         U12           MPMCCKEOUT[1]         U12           MPMCCLKOUT[0]         U16    DDR / SDRAM clock 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |       | MPMCDATA[14]    | M16  |           |                          |