## **Data Sheet**

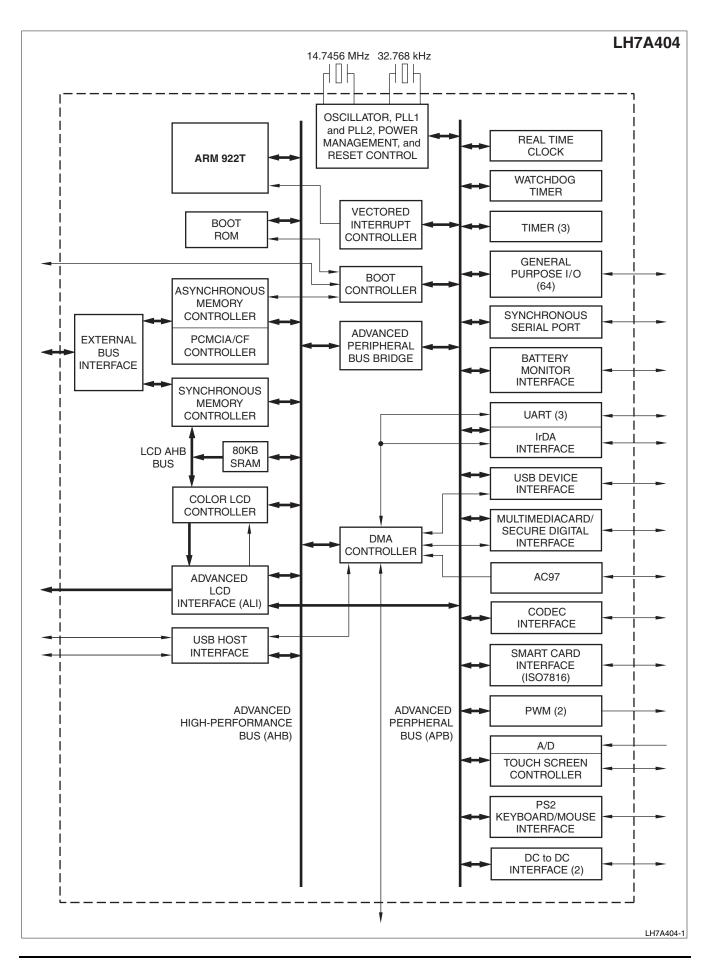

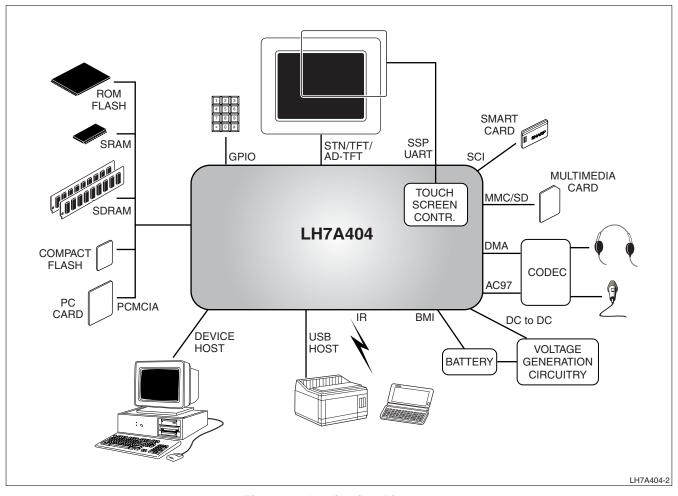

# LH7A404 32-Bit System-on-Chip

## **FEATURES**

- 32-bit ARM9TDMI™ RISC Core

- 16KB Cache: 8KB Instruction and 8KB Data Cache

- MMU (Windows CE<sup>™</sup> Enabled)

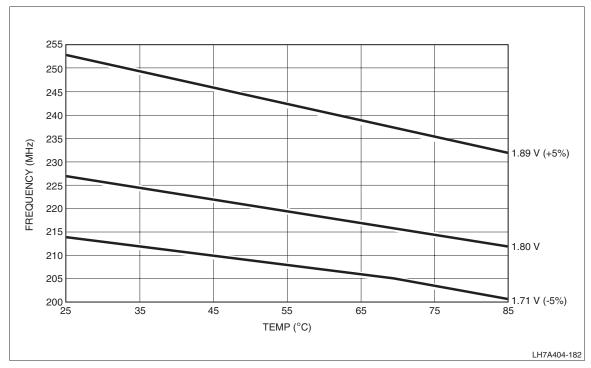

- Up to 266 MHz; See Table 1 for speed/temp options

- 80KB On-Chip Static RAM

- Vectored Interrupt Controller

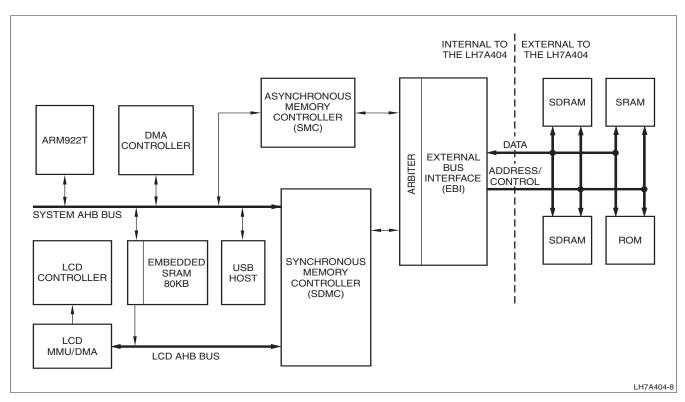

- · External Bus Interface

- Up to 133 MHz; See Table 1 for bus speed options

- Asynchronous and Synchronous interface RAM, Flash, PC Card and CompactFlash

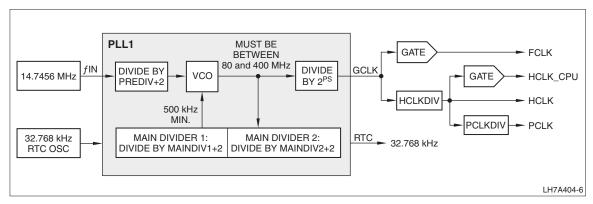

- · Clock and Power Management

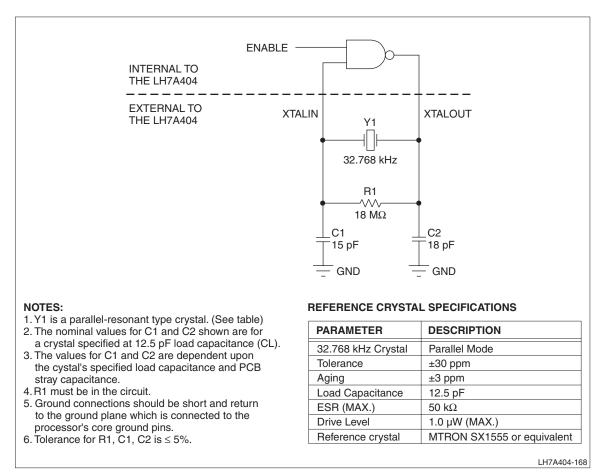

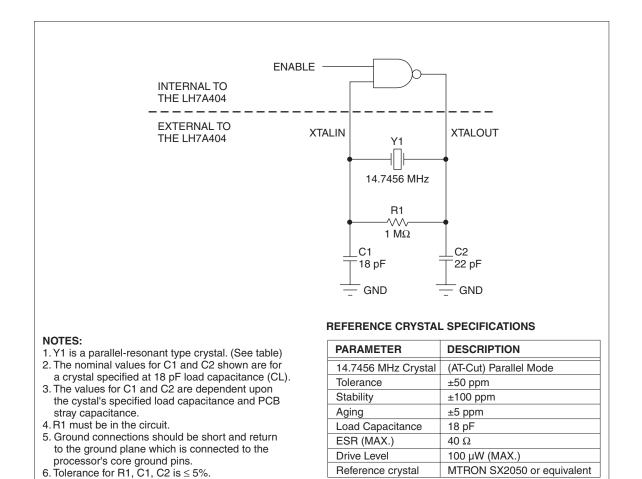

- 32.768 kHz and 14.7456 MHz Oscillators

- Programmable PLL

- Programmable LCD Controller

- Up to 1,024 × 768 Resolution

- Supports STN, Color STN, AD-TFT, HR-TFT, TFT

- Up to 64 K-Colors and 15 Gray Shades

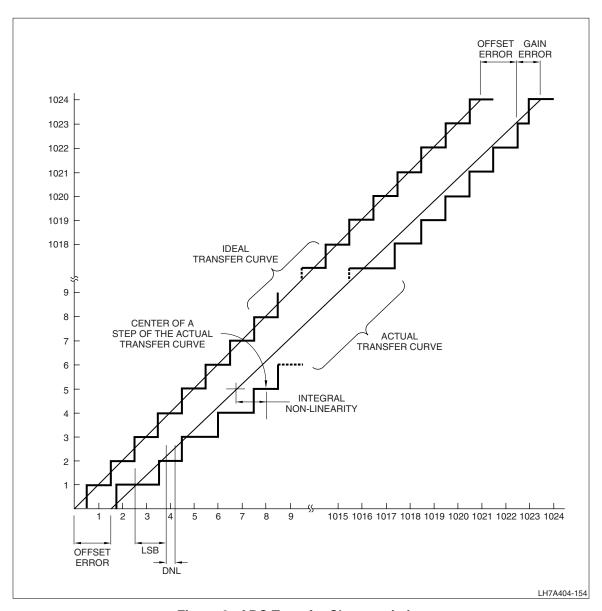

- 9 Channel, 10-bit A/D Converter

- Touch Screen Controller

- Brownout Detector

- DMA (12 Channels)

- External DMA Channels

- AC97

- MMC

- USB

- USB 2.0 Full Speed Host (two downstream ports)

- USB 2.0 Full Speed Device

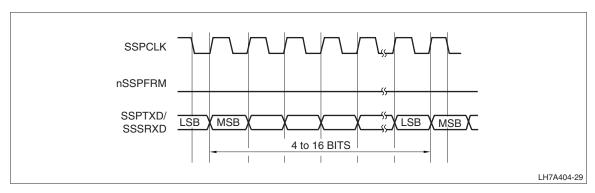

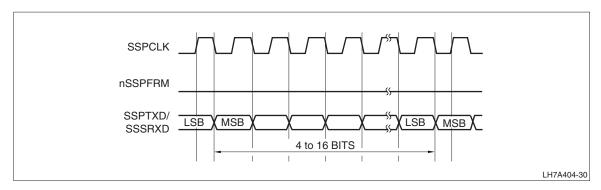

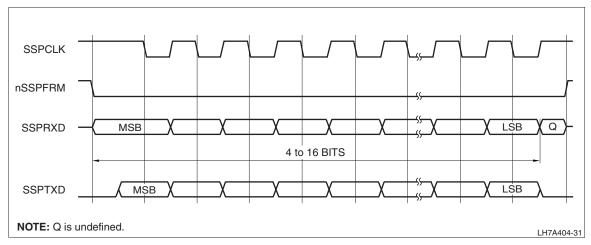

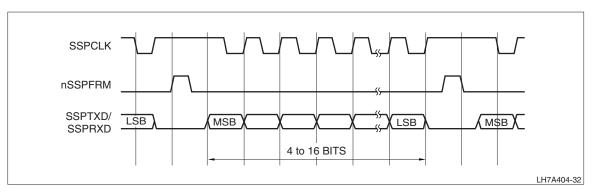

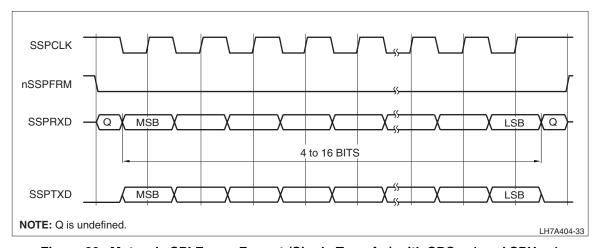

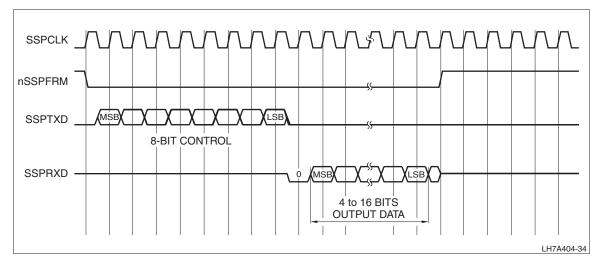

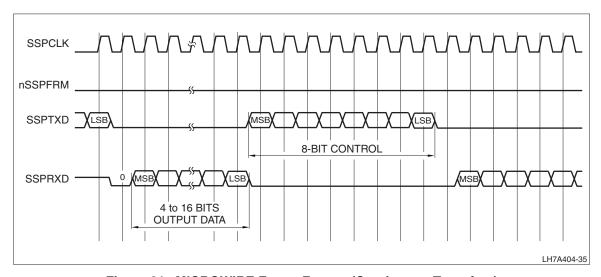

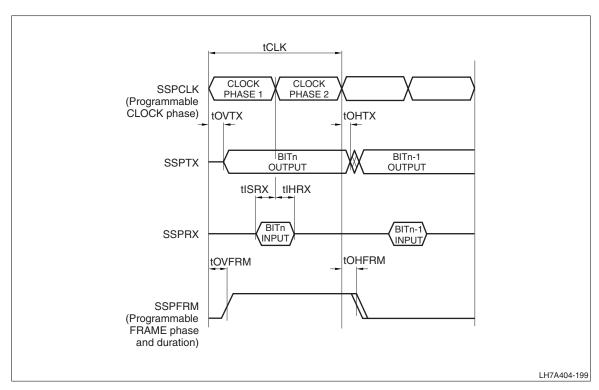

- · Synchronous Serial Port (SSP)

- Motorola SPI™, Texas Instruments SSI, National Semiconductor MICROWIRE™

- · On-board Boot ROM

- Variety of Boot Modes: external ROM, NAND Flash, Serial EEPROM, or XMODEM

- PS/2 Keyboard/Mouse Interface (KMI)

- Three Programmable Timers

- Three UARTs, one with Classic IrDA (115 kbit/s)

- Smart Card Interface (ISO7816)

- Four Pulse Width Modulators (PWMs)

- MultiMediaCard Interface with Secure Digital (MMC 2.11/SD 1.0)

- AC97 Codec Interface

- · Smart Battery Monitor Interface

- Real Time Clock (RTC)

- · Up to 64 General Purpose I/O Channels

- · Watchdog Timer

- JTAG Debug Interface and Boundary Scan

- · Operating Voltage

- 1.8 V (200 MHz), 2.1 V (266 MHz) Core

- 3.3 V Input/Output (Except XTALIN is 1.8 V)

- 5 V Tolerant Digital Inputs (excludes oscillator pins)

Oscillator pins T19, T20, Y18, Y19: 1.8 V ± 10%

- Operating Temperature: -40°C to +85°C

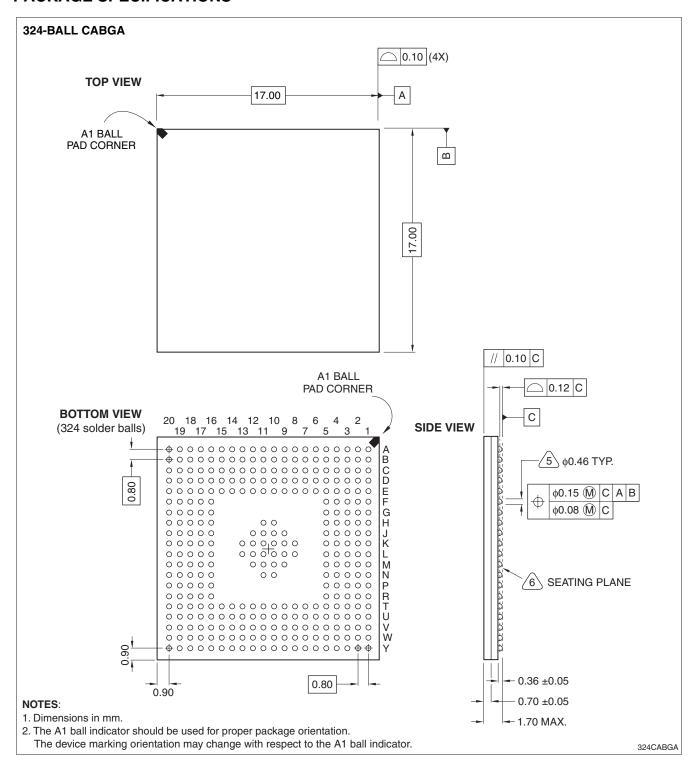

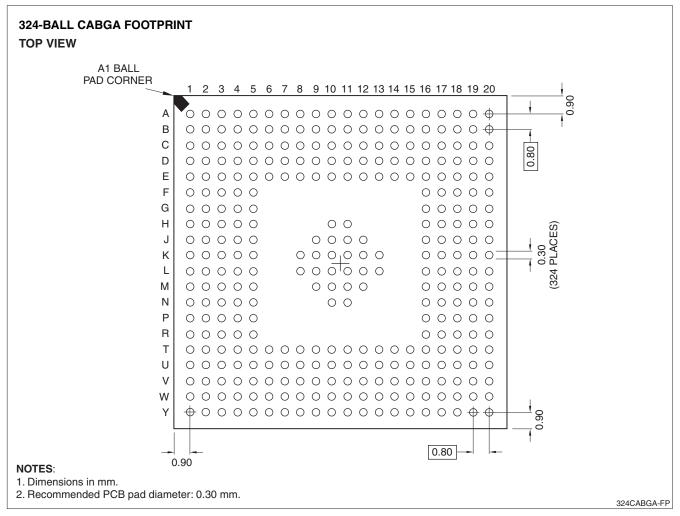

- 324-Ball CABGA Package

#### DESCRIPTION

The advent of 3G technology opens up a wide range of multimedia applications in mobile information appliances. The LH7A404 is designed from the ground up with a 32-bit ARM922 Core to provide high processing performance, low power consumption, and a high level of integration. Features include 80KB on-chip SRAM, fully static design, power management unit, low voltage (1.8 V Core, 3.3 V I/O) and on-chip PLL.

NOTE: Devices containing lead-free solder formulations have different reflow temperatures than leaded-solder formulations. When using both solder formulations on the same PC board, designers should consider the effect of different reflow temperatures on the overall PCB assembly process. (Refer to www.sharpmcu.com for an application note on recomended soldering practices).

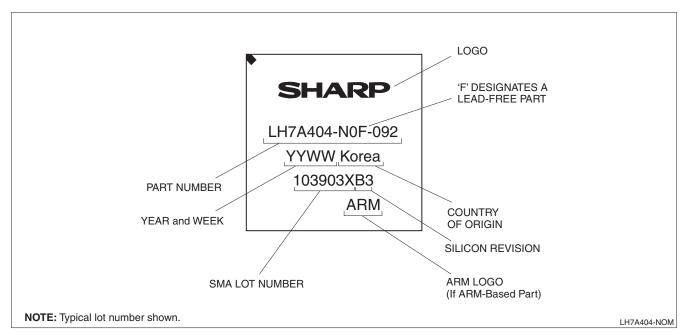

Table 1. LH7A404 Versions

| PART NUMBER <sup>1</sup>                              | CORE CLOCK | <b>BUS CLOCK</b> | LOW POWER CURRENT BY MODE                                            | TEMP. RANGE    |

|-------------------------------------------------------|------------|------------------|----------------------------------------------------------------------|----------------|

| LH7A404-N0E-092-xx<br>LH7A404-N0F-092-xx <sup>2</sup> | 266 MHz    | 133 MHz          | Run = 228 mA (Typ.); Halt = 60 mA (Typ.);<br>Standby = 200 μA (Typ.) | -40°C to +85°C |

| LH7A404-N0E-000-xx<br>LH7A404-N0F-000-xx <sup>2</sup> | 200 MHz    | 100 MHz          | Run = 147 mA (Typ.); Halt = 41 mA (Typ.);<br>Standby = 70 μA (Typ.)  | -40°C to +85°C |

#### NOTES:

Where 'xx' is a two digit revision number, e.g. B2; refer to www.sharpmcu.com for a list of all the active revisions

Lead-free part.

SPI is a trademark of Motorola, Inc.

MICROWIRE is a trademark of National Semiconductor Corporation.

ARM922T and ARM9TDMI are trademarks of Advanced RISC Machines Ltd.

Windows CE is a trademark of Microsoft Corporation.

## Table 2. LH7A404 Functional Pin List

| CABGA | SIGNAL | DESCRIPTION     | RESET<br>STATE | STANDBY<br>STATE | OUTPUT<br>DRIVE | I/O | NOTES |

|-------|--------|-----------------|----------------|------------------|-----------------|-----|-------|

| E10   |        |                 |                |                  |                 |     |       |

| E11   |        |                 |                |                  |                 |     |       |

| H10   |        |                 |                |                  |                 |     |       |

| H11   |        |                 |                |                  |                 |     |       |

| K5    |        |                 |                |                  |                 |     |       |

| K8    |        |                 |                |                  |                 |     |       |

| K13   |        |                 |                |                  |                 |     |       |

| K16   |        |                 |                |                  |                 |     |       |

| L5    | VDD    | I/O Ring Power  |                |                  |                 |     |       |

| L8    |        |                 |                |                  |                 |     |       |

| L13   |        |                 |                |                  |                 |     |       |

| L16   |        |                 |                |                  |                 |     |       |

| N10   |        |                 |                |                  |                 |     |       |

| N11   |        |                 |                |                  |                 |     |       |

| T10   |        |                 |                |                  |                 |     |       |

| T11   |        |                 |                |                  |                 |     |       |

| U18   |        |                 |                |                  |                 |     |       |

| J9    |        |                 |                |                  |                 |     |       |

| J10   |        |                 |                |                  |                 |     |       |

| J11   |        |                 |                |                  |                 |     |       |

| J12   |        |                 |                |                  |                 |     |       |

| K9    |        |                 |                |                  |                 |     |       |

| K10   |        |                 |                |                  |                 |     |       |

| K11   |        |                 |                |                  |                 |     |       |

| K12   |        |                 |                |                  |                 |     |       |

| L9    | VSS    | I/O Ring Ground |                |                  |                 |     |       |

| L10   |        |                 |                |                  |                 |     |       |

| L11   |        |                 |                |                  |                 |     |       |

| L12   |        |                 |                |                  |                 |     |       |

| M9    |        |                 |                |                  |                 |     |       |

| M10   |        |                 |                |                  |                 |     |       |

| M11   |        |                 |                |                  |                 |     |       |

| M12   |        |                 |                |                  |                 |     |       |

| T18   |        |                 |                |                  |                 |     |       |

| E7    |        |                 |                |                  |                 |     |       |

| E9    |        |                 |                |                  |                 |     |       |

| E14   |        |                 |                |                  |                 |     |       |

| G5    |        |                 |                |                  |                 |     |       |

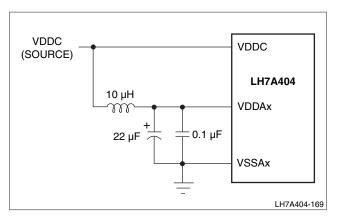

| G16   | VDDC   | Core Power      |                |                  |                 |     |       |

| P5    |        |                 |                |                  |                 |     |       |

| P16   |        |                 |                |                  |                 |     |       |

| T7    |        |                 |                |                  |                 |     |       |

| T12   |        |                 |                |                  |                 |     |       |

| T14   |        |                 |                |                  |                 |     |       |

# Table 2. LH7A404 Functional Pin List (Cont'd)

| CABGA | SIGNAL    | DESCRIPTION                                                                                                                                                                              | RESET<br>STATE | STANDBY<br>STATE | OUTPUT<br>DRIVE | I/O | NOTES |

|-------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|------------------|-----------------|-----|-------|

| E6    |           |                                                                                                                                                                                          |                |                  |                 |     |       |

| E15   |           |                                                                                                                                                                                          |                |                  |                 |     |       |

| F5    |           |                                                                                                                                                                                          |                |                  |                 |     |       |

| F16   |           |                                                                                                                                                                                          |                |                  |                 |     |       |

| J16   | V000      | Cana Cravind                                                                                                                                                                             |                |                  |                 |     |       |

| M5    | VSSC      | Core Ground                                                                                                                                                                              |                |                  |                 |     |       |

| R5    |           |                                                                                                                                                                                          |                |                  |                 |     |       |

| R16   | -         |                                                                                                                                                                                          |                |                  |                 |     |       |

| T6    |           |                                                                                                                                                                                          |                |                  |                 |     |       |

| T15   |           |                                                                                                                                                                                          |                |                  |                 |     |       |

| Y17   | VDDA      | Analan Dawar far Dili 4 and Dili 0                                                                                                                                                       |                |                  |                 |     |       |

| W17   | VDDA      | Analog Power for PLL1 and PLL2                                                                                                                                                           |                |                  |                 |     |       |

| V16   | VSSA      | Analog Cround for DLL1 and DLL0                                                                                                                                                          |                |                  |                 |     |       |

| U15   | - V55A    | Analog Ground for PLL1 and PLL2                                                                                                                                                          |                |                  |                 |     |       |

| W16   | VDDAD     | Analog Power for A/D, Touch Screen Controller                                                                                                                                            |                |                  |                 |     |       |

| V13   | VSSAD     | Analog Ground for A/D, Touch Screen Controller                                                                                                                                           |                |                  |                 |     |       |

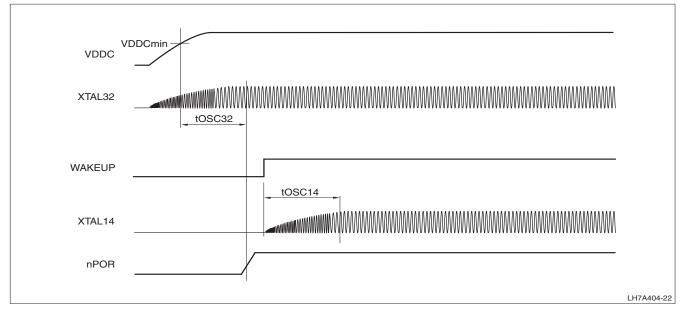

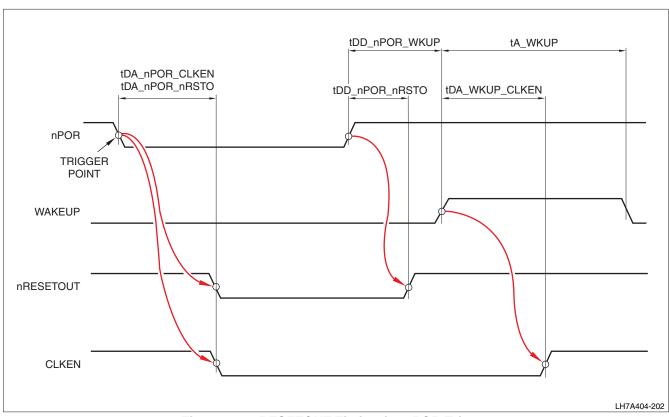

| D2    | nPOR      | Power on Reset                                                                                                                                                                           | Input          | Input            |                 | I   | 3     |

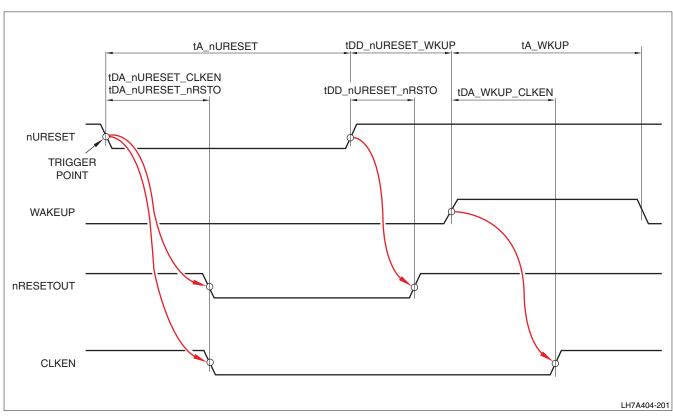

| E1    | nURESET   | User Reset                                                                                                                                                                               | Input          | Input            |                 | I   | 3     |

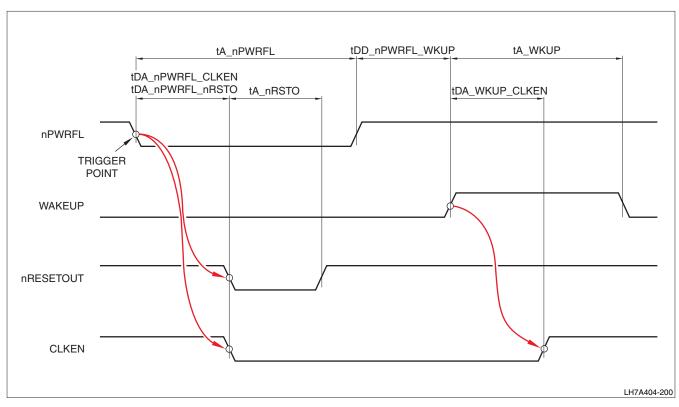

| F3    | WAKEUP    | Wake Up                                                                                                                                                                                  | Input          | Input            |                 | I   | 3     |

| F4    | nPWRFL    | Power Fail Signal                                                                                                                                                                        | Input          | Input            |                 | I   | 3     |

| C1    | nEXTPWR   | External Power                                                                                                                                                                           | Input          | Input            |                 | Ι   | 3     |

| C5    | nRESETOUT | Reset Output to external devices. This pin carries the same state as the internal SoC reset signal.                                                                                      | LOW            |                  | 12 mA           | 0   |       |

| Y18   | XTALIN    | 14.7456 MHz Crystal Oscillator pins. For an external                                                                                                                                     |                |                  |                 |     |       |

| Y19   | XTALOUT   | clock source, XTALIN can be used while XTALOUT is left unconnected. XTALIN voltage is 1.8 V nominal.                                                                                     |                |                  |                 |     |       |

| T19   | XTAL32IN  | 32.768 kHz Real Time Clock, Crystal Oscillator pins.                                                                                                                                     |                |                  |                 |     |       |

| T20   | XTAL32OUT | To drive the device from an external clock source, XTAL32IN can be used while XTAL32OUT is left unconnected.                                                                             |                |                  |                 |     |       |

| L2    | PGMCLK    | Programmable Clock (14.7456 MHz MAX.)                                                                                                                                                    | LOW            | LOW              | 8 mA            | 0   |       |

| T16   | CLKEN     | External Oscillator Enable Output                                                                                                                                                        | LOW            | LOW              | 8 mA            | I/O |       |

| Y13   | WIDTH0    | Boot Width Pins. Used with the MEDCHG and INT-BOOT bits for internal Boot ROM. On power up, the                                                                                          |                |                  |                 |     |       |

| W13   | WIDTH1    | values on these pins are latched to determine the width and type of Boot device. Boot width can be 8-, 16-, or 32-bit. The pins must be pulled HIGH with a 33 $\mbox{k}\Omega$ resistor. | Input          | Input            |                 | I   | 3     |

| E4    | MEDCHG    | Media Change bit; used at power on with INTBOOT and WIDTHx pins to determine boot device.                                                                                                | Input          | No Change        |                 | I   | 3     |

| Y20   | INTBOOT   | When LOW, boot device is selected according to the MEDCHG bit. When HIGH, the lower 64KB addresses are mapped to the internal Boot ROM.                                                  | Input          | No Change        |                 | I   |       |

Table 2. LH7A404 Functional Pin List (Cont'd)

| CABGA | SIGNAL | DESCRIPTION              | RESET<br>STATE | STANDBY<br>STATE | OUTPUT<br>DRIVE | I/O | NOTES |

|-------|--------|--------------------------|----------------|------------------|-----------------|-----|-------|

| N19   | D0     |                          |                |                  |                 |     |       |

| P20   | D1     |                          |                |                  |                 |     |       |

| N18   | D2     |                          |                |                  |                 |     |       |

| N20   | D3     |                          |                |                  |                 |     |       |

| M16   | D4     |                          |                |                  |                 |     |       |

| M18   | D5     |                          |                |                  |                 |     |       |

| L18   | D6     |                          |                |                  |                 |     |       |

| L17   | D7     |                          |                |                  |                 |     |       |

| L19   | D8     |                          |                |                  |                 |     |       |

| J19   | D9     |                          |                |                  |                 |     |       |

| K17   | D10    |                          |                |                  |                 |     |       |

| J18   | D11    |                          |                |                  |                 |     |       |

| H19   | D12    |                          |                |                  |                 |     |       |

| G20   | D13    |                          |                |                  |                 |     |       |

| G19   | D14    |                          |                |                  |                 |     |       |

| H17   | D15    | Data Bus                 | LOW            | LOW              | 12 mA           | I/O |       |

| F19   | D16    | Data Bus                 | LOVV           | LOW              | 12 IIIA         | 1/0 |       |

| E20   | D17    |                          |                |                  |                 |     |       |

| E19   | D18    |                          |                |                  |                 |     |       |

| D20   | D19    |                          |                |                  |                 |     |       |

| E18   | D20    |                          |                |                  |                 |     |       |

| C20   | D21    |                          |                |                  |                 |     |       |

| D18   | D22    |                          |                |                  |                 |     |       |

| B20   | D23    |                          |                |                  |                 |     |       |

| C18   | D24    |                          |                |                  |                 |     |       |

| A20   | D25    |                          |                |                  |                 |     |       |

| B18   | D26    |                          |                |                  |                 |     |       |

| C16   | D27    |                          |                |                  |                 |     |       |

| B17   | D28    |                          |                |                  |                 |     |       |

| A18   | D29    |                          |                |                  |                 |     |       |

| A17   | D30    |                          |                |                  |                 |     |       |

| B15   | D31    |                          |                |                  |                 |     |       |

| P17   | A0     | Asynchronous Address Bus | HIGH           | LOW              | 12 mA           | 0   |       |

| N16   | A1     | Augmoniona Audiosa Bus   | Than           | LOW              | 121117          |     |       |

Table 2. LH7A404 Functional Pin List (Cont'd)

| CABGA | SIGNAL   | DESCRIPTION                                                    | RESET<br>STATE | STANDBY<br>STATE | OUTPUT<br>DRIVE | I/O | NOTES |

|-------|----------|----------------------------------------------------------------|----------------|------------------|-----------------|-----|-------|

| N17   | A2/SA0   |                                                                |                |                  |                 |     |       |

| M19   | A3/SA1   |                                                                |                |                  |                 |     |       |

| M20   | A4/SA2   |                                                                |                |                  |                 |     |       |

| L20   | A5/SA3   |                                                                |                |                  |                 |     |       |

| M17   | A6/SA4   |                                                                |                |                  |                 |     |       |

| K18   | A7/SA5   |                                                                |                |                  |                 |     |       |

| K20   | A8/SA6   | Asynchronous Address Bus and                                   | LOW            | LOW              | 10 m A          | 0   |       |

| K19   | A9/SA7   | Synchronous Address Bus                                        | LOW            | LOW              | 12 mA           | U   |       |

| J20   | A10/SA8  |                                                                |                |                  |                 |     |       |

| H20   | A11/SA9  |                                                                |                |                  |                 |     |       |

| J17   | A12/SA10 |                                                                |                |                  |                 |     |       |

| H18   | A13/SA11 |                                                                |                |                  |                 |     |       |

| F20   | A14/SA12 |                                                                |                |                  |                 |     |       |

| G18   | A15/SA13 |                                                                |                |                  |                 |     |       |

| H16   | A16/SB0  | Asynchronous Address Bus     Synchronous Device Bank Address 0 | LOW            | LOW              | 12 mA           | 0   |       |

| F18   | A17/SB1  | Asynchronous Address Bus     Synchronous Device Bank Address 1 | LOW            | LOW              | 12 mA           | 0   |       |

| G17   | A18      |                                                                |                |                  |                 |     |       |

| F17   | A19      | Asynchronous Address Bus                                       | LOW            | LOW              | 12 mA           | 0   |       |

| D19   | A20      | Asynchronous Address Bus                                       | LOW            | LOW              | 12 mA           | 0   | 4     |

| E17   | A21      |                                                                | LOW            | LOW              | 121117          |     | 4     |

| C19   | A22      |                                                                |                |                  |                 |     |       |

| D17   | A23      |                                                                |                |                  |                 |     |       |

| B19   | A24      | Asynchronous Address Bus                                       | LOW            | LOW              | 12 mA           | 0   |       |

| A16   | A25      |                                                                | LOW            | 2011             | 121117          |     |       |

| D15   | A26      |                                                                |                |                  |                 |     |       |

| B14   | A27      |                                                                |                |                  |                 |     |       |

| V18   | nCS0     | Asynchronous Memory Chip Select 0                              | HIGH           | HIGH             | 12 mA           | 0   |       |

| R19   | nCS1     | Asynchronous Memory Chip Select 1                              | HIGH           | HIGH             | 12 mA           | 0   |       |

| R18   | nCS2     | Asynchronous Memory Chip Select 2                              | HIGH           | HIGH             | 12 mA           | 0   |       |

| P19   | nCS3     | Asynchronous Memory Chip Select 3                              | HIGH           | HIGH             | 12 mA           | 0   |       |

| R20   | nCS6     | Asynchronous Memory Chip Select 6                              | HIGH           | No Change        | 12 mA           | 0   |       |

| R17   | nCS7     | Asynchronous Memory Chip Select 7                              | HIGH           | No Change        | 12 mA           | 0   |       |

| C12   | nOE      | Asynchronous Memory Output Enable                              | HIGH           | HIGH             | 12 mA           | 0   | 4     |

| D12   | nWE      | Asynchronous Memory Write Enable                               | HIGH           | HIGH             | 12 mA           | 0   | 4     |

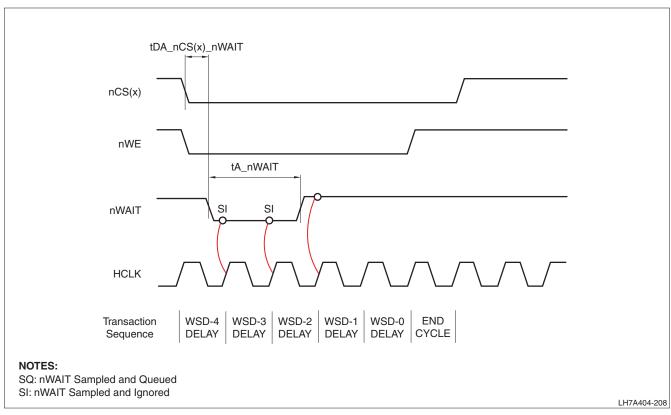

| P18   | nWAIT    | Asynchronous Memory Wait; pull HIGH if unused                  | Input          | No Change        |                 | ı   | 5     |

| C17   | nSCS0    | Synchronous Memory Chip Select 0                               | HIGH           | HIGH             | 12 mA           | I/O |       |

| A19   | nSCS1    | Synchronous Memory Chip Select 1                               | HIGH           | HIGH             | 12 mA           | I/O |       |

| D16   | nSCS2    | Synchronous Memory Chip Select 2                               | HIGH           | HIGH             | 12 mA           | I/O |       |

| E16   | nSCS3    | Synchronous Memory Chip Select 3                               | HIGH           | HIGH             | 12 mA           | I/O |       |

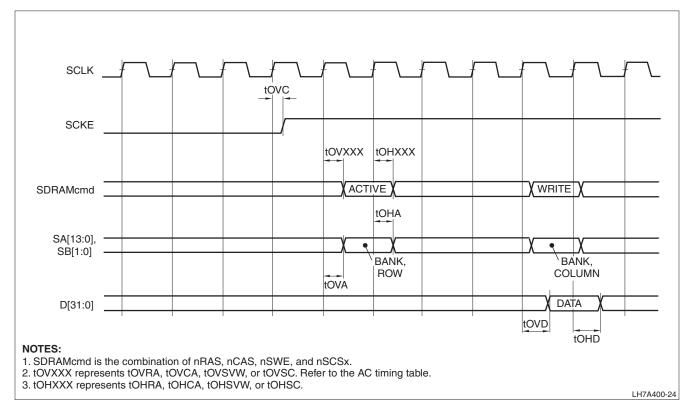

| B16   | nSWE     | Synchronous Memory Write Enable                                | HIGH           | HIGH             | 12 mA           | 0   |       |

| A14   | SCKE0    | Clock Enable 0 for Synchronous Memory                          | HIGH           | No Change        | 12 mA           | 0   |       |

| B13   | SCKE1_2  | Clock Enable 1 OR 2 for Synchronous Memory                     | HIGH           | No Change        | 12 mA           | 0   |       |

Table 2. LH7A404 Functional Pin List (Cont'd)

| CABGA | SIGNAL          | DESCRIPTION                                                                           | RESET<br>STATE       | STANDBY<br>STATE | OUTPUT<br>DRIVE | I/O | NOTES    |

|-------|-----------------|---------------------------------------------------------------------------------------|----------------------|------------------|-----------------|-----|----------|

| C14   | SCKE3           | Clock Enable 3 for Synchronous Memory                                                 | Depends on<br>MEDCHG | LOW              | 12 mA           | I/O |          |

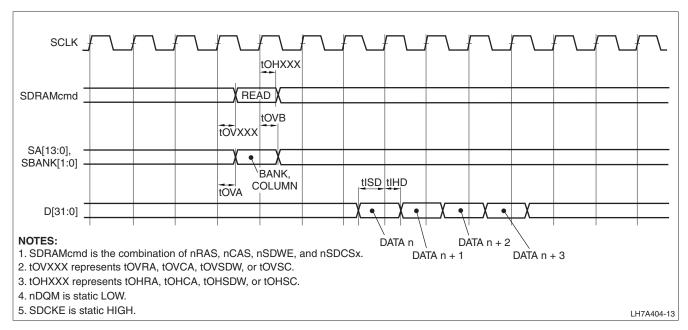

| D14   | SCLK            | Synchronous Memory Clock                                                              | LOW                  | No Change        | 20 mA           | I/O | 2        |

| A13   | nBLE0           | Byte Lane Enable 0                                                                    | HIGH                 | HIGH             | 12 mA           | I/O |          |

| U9    | nBLE1           | Byte Lane Enable 1                                                                    | HIGH                 | HIGH             | 12 mA           | 0   |          |

| Y7    | nBLE2           | Byte Lane Enable 2                                                                    | HIGH                 | HIGH             | 12 mA           | 0   |          |

| C13   | nBLE3           | Byte Lane Enable 3                                                                    | HIGH                 | HIGH             | 8 mA            | 0   |          |

| C15   | nCAS            | Synchronous Memory Column Address Strobe                                              | HIGH                 | HIGH             | 12 mA           | I/O |          |

| A15   | nRAS            | Synchronous Memory Row Address Strobe                                                 | HIGH                 | HIGH             | 12 mA           | I/O |          |

| D13   | DQM0            |                                                                                       |                      |                  |                 |     |          |

| E13   | DQM1            | Data Mask for Synchronous Memories                                                    | HIGH                 | No Change        | 12 mA           | 0   |          |

| B12   | DQM2            | - Data Mask for Synchronous Memories                                                  | півн                 | No Change        | 12 IIIA         | "   |          |

| A12   | DQM3            |                                                                                       |                      |                  |                 |     |          |

| M2    | PA0/<br>LCDVD16 | GPIO Port A0     LCD Data pin 16                                                      | PA0: Input           | No Change        | 8 mA            | I/O |          |

| L4    | PA1/<br>LCDVD17 | GPIO Port A1     LCD Data pin 17                                                      | PA1: Input           | No Change        | 8 mA            | I/O |          |

| МЗ    | PA2             |                                                                                       |                      |                  |                 |     |          |

| M4    | PA3             | 7                                                                                     |                      |                  |                 |     |          |

| M1    | PA4             | GPIO Port A[6:2]                                                                      | PAx: Input           | No Change        | 8 mA            | I/O |          |

| N3    | PA5             |                                                                                       |                      |                  |                 |     |          |

| N2    | PA6             | 7                                                                                     |                      |                  |                 |     |          |

| N1    | PA7             | GPIO Port A7     Boot Width Selection (See Table 6)                                   | PA7: Input           | No Change        | 8 mA            | I/O | 4        |

| N4    | PB0/UARTRX1     | GPIO Port B0     UART1 Receive Data Input                                             | PB0: Input           | No Change        | 8 mA            | I/O |          |

| P3    | PB1/UARTTX3     | GPIO Port B1     UART3 Transmit Data Out                                              | PB1: Input           | No Change        | 8 mA            | I/O |          |

| P2    | PB2/UARTRX3     | GPIO Port B2     UART3 Receive Data In                                                | PB2: Input           | No Change        | 8 mA            | I/O |          |

| P1    | PB3/UARTCTS3    | GPIO Port B3     UART3 Clear to Send                                                  | PB3: Input           | No Change        | 8 mA            | I/O |          |

| R3    | PB4/UARTDCD3    | GPIO Port B4     UART3 Data Carrier Detect                                            | PB4: Input           | No Change        | 8 mA            | I/O |          |

| N5    | PB5/UARTDSR3    | GPIO Port B5     UART3 Data Set Ready                                                 | PB5: Input           | No Change        | 8 mA            | I/O |          |

| R2    | PB6/SWID/SMBD   | <ul><li> GPIO Port B6</li><li> Single Wire Data</li><li> Smart Battery Data</li></ul> | PB6: Input           | No Change        | 8 mA            | I/O |          |

| R1    | PB7/SMBCLK      | GPIO Port B7     Smart Battery Clock                                                  | PB7: Input           | No Change        | 8 mA            | I/O |          |

| P4    | PC0/UARTTX1     | GPIO Port C0     UART1 Transmit Data Output                                           | PC0: LOW             | No Change        | 12 mA           | I/O |          |

| T1    | PC1             |                                                                                       |                      |                  |                 |     |          |

| T2    | PC2             |                                                                                       |                      |                  |                 |     |          |

| Т3    | PC3             | GPIO Port C[5:1]                                                                      | PCx: LOW             | No Change        | 12 mA           | I/O |          |

| R4    | PC4             |                                                                                       |                      |                  |                 |     |          |

| U1    | PC5             |                                                                                       |                      |                  |                 |     | <u> </u> |

| U2    | PC6             | GPIO Port C6                                                                          | PC6: LOW             | No Change        | 12 mA           | I/O | 4        |

Table 2. LH7A404 Functional Pin List (Cont'd)

| CABGA | SIGNAL                | DESCRIPTION                                                                                                        | RESET<br>STATE | STANDBY<br>STATE           | OUTPUT<br>DRIVE | I/O | NOTES |

|-------|-----------------------|--------------------------------------------------------------------------------------------------------------------|----------------|----------------------------|-----------------|-----|-------|

| V1    | PC7                   | GPIO Port C7                                                                                                       | PC7: LOW       | No Change                  | 12 mA           | I/O |       |

| Y11   | PD0/LCDVD8            |                                                                                                                    |                |                            |                 |     |       |

| U10   | PD1/LCDVD9            |                                                                                                                    |                |                            |                 |     |       |

| W12   | PD2/LCDVD10           |                                                                                                                    |                | LOW if                     |                 |     |       |

| V11   | PD3/LCDVD11           | GPIO Port D[7:0]                                                                                                   | PDx: LOW       | 8-bit LCD                  | 12 mA           | I/O |       |

| W11   | PD4/LCDVD12           | LCD Video Data Interface                                                                                           | I BX. LOVV     | enabled; else<br>No Change | 12117           | .,, |       |

| U11   | PD5/LCDVD13           |                                                                                                                    |                | No Change                  |                 |     |       |

| V12   | PD6/LCDVD14           |                                                                                                                    |                |                            |                 |     |       |

| Y12   | PD7/LCDVD15           |                                                                                                                    |                |                            |                 |     |       |

| Y9    | PE0/LCDVD4            |                                                                                                                    |                | LOW if                     |                 |     |       |

| W10   | PE1/LCDVD5            | • GPIO Port E[3:0]                                                                                                 | PEx: Output    | 8-bit LCD                  | 12 mA           | I/O |       |

| V10   | PE2/LCDVD6            | LCD Video Data Interface                                                                                           | 1 Ex. Output   | enabled; else<br>No Change | 121117          | 1,0 |       |

| Т9    | PE3/LCDVD7            |                                                                                                                    |                | No Change                  |                 |     |       |

| D4    | PE4/SCCLKIN           | GPIO Port E4     Smart Card Push-Pull Mode Clock Input                                                             | PE4: Output    | No Change                  | 12 mA           | I/O |       |

| СЗ    | PE5/SCCLKEN           | GPIO Port E5     Smart Card Push-Pull Mode External Clock     Buffer Enable                                        | PE5: Output    | No Change                  | 12 mA           | I/O |       |

| B2    | PE6/SCIN              | GPIO Port E6     Smart Card Push-Pull Mode Data Input                                                              | PE6: Output    | No Change                  | 12 mA           | I/O |       |

| A1    | PE7/SCDATEN           | GPIO Port E7     Smart Card Push-Pull Mode Data Out External     Buffer Enable                                     | PE7: Output    | No Change                  | 12 mA           | I/O |       |

| A9    | PF0/INT0              | GPIO Port F0     Interrupt 0                                                                                       | PF0: Input     | No Change                  | 8 mA            | I/O | 3     |

| D9    | PF1/INT1              | GPIO Port F1     Interrupt 1                                                                                       | PF1: Input     | No Change                  | 8 mA            | I/O | 3     |

| A8    | PF2/INT2              | GPIO Port F2     Interrupt 2                                                                                       | PF2: Input     | No Change                  | 8 mA            | I/O | 3     |

| C8    | PF3/INT3              | GPIO Port F3     Interrupt 3                                                                                       | PF3: Input     | No Change                  | 8 mA            | I/O | 3     |

| В8    | PF4/INT4              | • GPIO Port F4<br>• Interrupt 4                                                                                    | PF4: Input     | No Change                  | 8 mA            | I/O | 3     |

| D8    | PF5/INT5/<br>SCDETECT | <ul><li> GPIO Port F5</li><li> Interrupt 5</li><li> Smart Card Interface Card Detect Signal</li></ul>              | PF5: Input     | No Change                  | 8 mA            | I/O | 3     |

| A7    | PF6/INT6/<br>PCRDY1   | GPIO Port F6 Interrupt 6 Ready for Card 1 for PC Card (PCMCIA or CompactFlash) in Single or Dual Card mode         | PF6: Input     | No Change                  | 8 mA            | I/O | 3     |

| E8    | PF7/INT7/PCRDY2       | GPIO Port F7     Interrupt 7     Ready for Card 2 for PC Card (PCMCIA or CompactFlash) in Single or Dual Card mode | PF7: Input     | No Change                  | 8 mA            | I/O | 3     |

| Y2    | PG0/nPCOE             | GPIO Port G0     Output Enable for PC Card (PCMCIA or CompactFlash) in Single or Dual Card mode                    | LOW            | No Change                  | 8 mA            | I/O |       |

| W4    | PG1/nPCWE             | GPIO Port G1     Write Enable for PC Card (PCMCIA or CompactFlash) in Single or Dual Card mode                     | LOW            | No Change                  | 8 mA            | I/O |       |

Table 2. LH7A404 Functional Pin List (Cont'd)

| CABGA | SIGNAL                               | DESCRIPTION                                                                                                                                                                                                                                                                           | RESET<br>STATE | STANDBY<br>STATE | OUTPUT<br>DRIVE | I/O | NOTES |

|-------|--------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|------------------|-----------------|-----|-------|

| Y3    | PG2/nPCIOR                           | GPIO Port G2     I/O Read Strobe for PC Card (PCMCIA or CompactFlash) in Single or Dual Card mode                                                                                                                                                                                     | LOW            | No Change        | 8 mA            | I/O |       |

| U5    | PG3/nPCIOW                           | GPIO Port G3     I/O Write Strobe for PC Card (PCMCIA or CompactFlash) in Single or Dual Card mode                                                                                                                                                                                    | LOW            | No Change        | 8 mA            | I/O |       |

| T5    | PG4/nPCREG                           | GPIO Port G4     Register Memory Access for PC Card (PCMCIA or CompactFlash) in Single or Dual Card mode                                                                                                                                                                              | LOW            | No Change        | 8 mA            | I/O |       |

| W5    | PG5/nPCCE1                           | GPIO Port G5     Card Enable 1 for PC Card (PCMCIA or CompactFlash) in Single or Dual Card mode. This signal and nPCCE2 are used by the PC Card for decoding low and high byte accesses.                                                                                              | LOW            | No Change        | 8 mA            | I/O |       |

| Y4    | PG6/nPCCE2                           | GPIO Port G6     Card Enable 2 for PC Card (PCMCIA or CompactFlash) in Single or Dual Card mode. This signal and nPCCE1 are used by the PC Card for decoding low and high byte accesses.                                                                                              | LOW            | No Change        | 8 mA            | I/O |       |

| W6    | PG7/PCDIR                            | GPIO Port G7     Direction for PC Card (PCMCIA or CompactFlash) in Single or Dual Card mode                                                                                                                                                                                           | LOW            | No Change        | 8 mA            | I/O |       |

| V6    | PH0/PCRESET1                         | GPIO Port H0     Reset Card 1 for PC Card (PCMCIA or CompactFlash) in Single or Dual Card mode                                                                                                                                                                                        | PHx: Input     | No Change        | 8 mA            | I/O |       |

| Y5    | PH1/CFA8/<br>PCRESET2                | GPIO Port H1     Address Bit 8 for PC Card (CompactFlash) in Single Card mode     Reset Card 2 for PC Card (PCMCIA or CompactFlash) in Dual Card mode                                                                                                                                 | PHx: Input     | No Change        | 8 mA            | I/O |       |

| W7    | PH2/nPCSLOTE1                        | GPIO Port H2     Enable Card 1 for PC Card (PCMCIA or CompactFlash) in Single or Dual Card mode. This signal is used for gating other control signals to the appropriate PC Card.                                                                                                     | PHx: Input     | No Change        | 8 mA            | I/O |       |

| U6    | PH3/CFA9/<br>PCMCIAA25/<br>nPCSLOTE2 | GPIO Port H3     Address Bit 9 for PC Card (CompactFlash) in Single Card mode     Address Bit 25 for PC Card (PCMCIA) in Single Card mode     Enable Card 2 for PC Card (PCMCIA or CompactFlash) in Dual Card mode. Used for gating other control signals to the appropriate PC Card. | PHx: Input     | No Change        | 8 mA            | I/O |       |

| W8    | PH4/nPCWAIT1                         | GPIO Port H4     WAIT Signal for Card 1 for PC Card (PCMCIA or CompactFlash) in Single or Dual Card mode                                                                                                                                                                              | PHx: Input     | No Change        | 8 mA            | I/O |       |

| Y6    | PH5/CFA10/<br>PCMCIAA24/<br>nPCWAIT2 | GPIO Port H5     Address Bit 10 for PC Card (CompactFlash) in Single Card mode     Address Bit 24 for PC Card (PCMCIA) in Single Card mode     WAIT Signal for Card 2 for PC Card (PCMCIA or CompactFlash) in Dual Card mode                                                          | PHx: Input     | No Change        | 8 mA            | I/O |       |

| V7    | PH6/nAC97RESET                       | GPIO Port H6     AC97 Reset                                                                                                                                                                                                                                                           | PHx: Input     | No Change        | 8 mA            | I/O |       |

Table 2. LH7A404 Functional Pin List (Cont'd)

| CABGA | SIGNAL            | DESCRIPTION                                                                                                                                                                                                                                                                | RESET<br>STATE | STANDBY<br>STATE          | OUTPUT<br>DRIVE | I/O | NOTES |

|-------|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|---------------------------|-----------------|-----|-------|

| U7    | PH7/<br>nPCSTATRE | GPIO Port H7     Status Read Enable for PC Card (PCMCIA or CompactFlash) in Single or Dual Card mode                                                                                                                                                                       | PHx: Input     | No Change                 | 8 mA            | I/O |       |

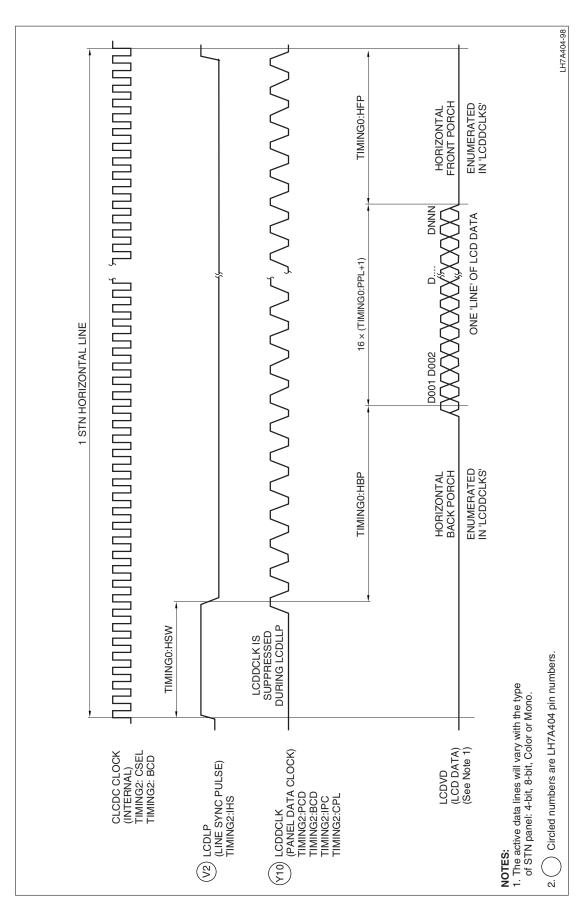

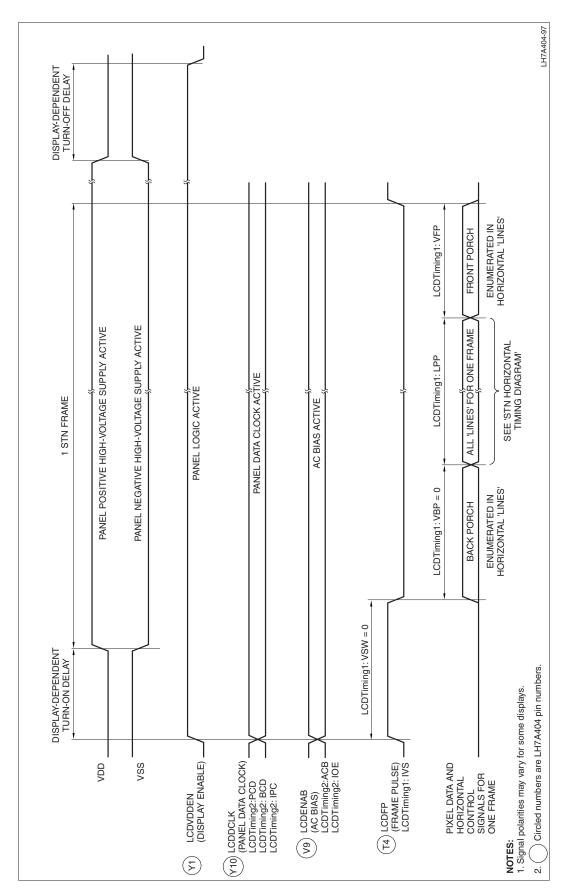

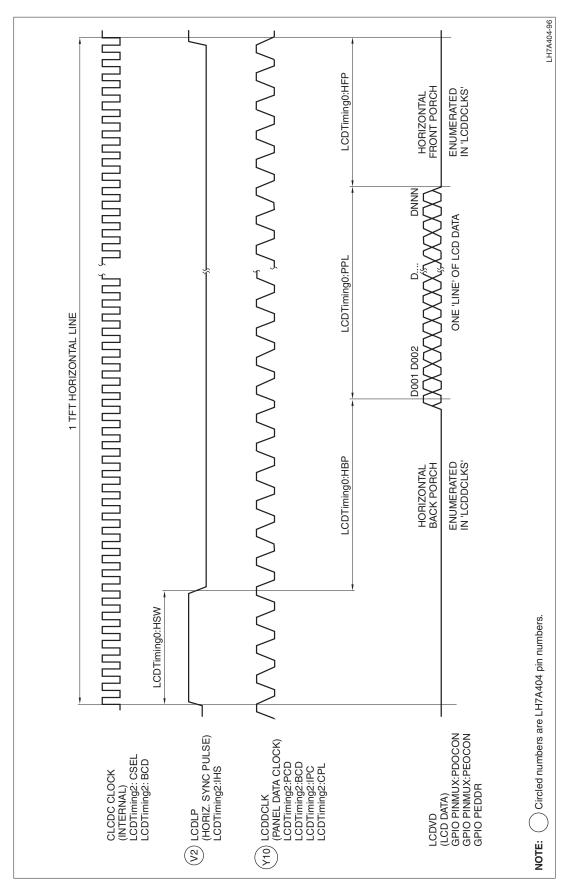

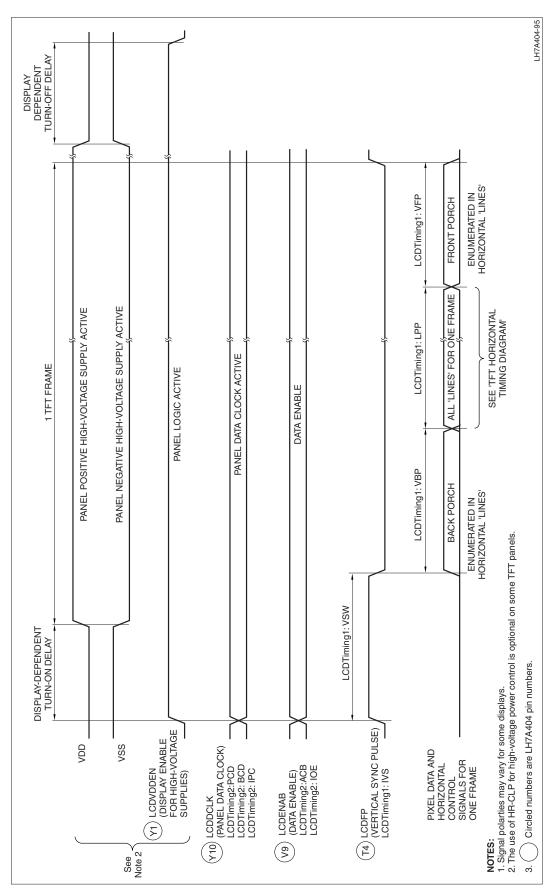

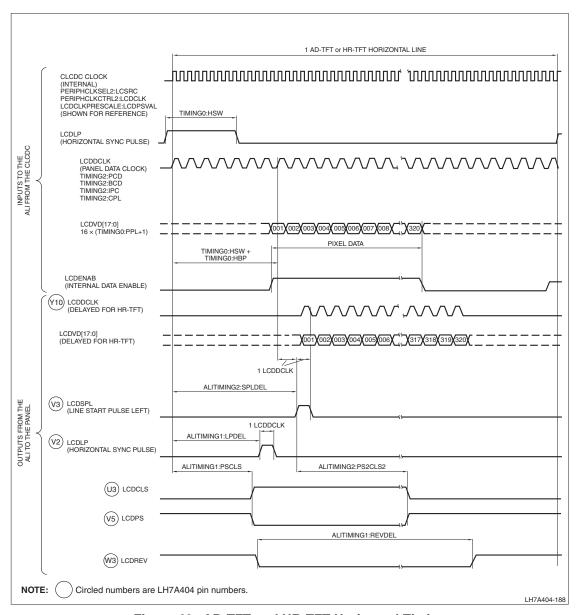

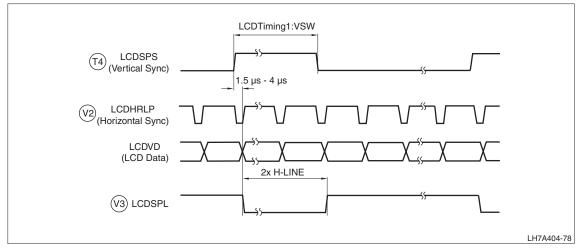

| T4    | LCDFP/LCDSPS      | LCD Frame Pulse     ALI Reset Row Driver Counter                                                                                                                                                                                                                           | LOW            | LOW if not in<br>ALI mode | 12 mA           | 0   |       |

| V2    | LCDLP/<br>LCDHRLP | LCD Linepulse     ALI Latch Pulse                                                                                                                                                                                                                                          | LOW            | LOW if not in<br>ALI mode | 12 mA           | 0   |       |

| U3    | LCDCLS            | ALI Clock for Row Drivers                                                                                                                                                                                                                                                  | LOW            | No Change                 | 12 mA           | 0   |       |

| V3    | LCDSPL            | ALI Start Pulse Left for reverse scanning                                                                                                                                                                                                                                  | LOW            | No Change                 | 12 mA           | 0   |       |

| U4    | LCDUBL            | ALI Up, Down signal for reverse scanning                                                                                                                                                                                                                                   | LOW            | No Change                 | 12 mA           | 0   |       |

| W1    | LCDSPR            | ALI Start Pulse Right for normal scanning                                                                                                                                                                                                                                  | LOW            | No Change                 | 12 mA           | 0   |       |

| V4    | LCDLBR            | ALI Output for reverse scanning                                                                                                                                                                                                                                            | HIGH           | No Change                 | 12 mA           | 0   |       |

| W2    | LCDMOD            | ALI MOD Signal used by the row driver                                                                                                                                                                                                                                      | LOW            | No Change                 | 12 mA           | 0   |       |

| V5    | LCDPS             | ALI Power Save                                                                                                                                                                                                                                                             | HIGH           | No Change                 | 12 mA           | 0   |       |

| Y1    | LCDVDDEN          | ALI Power Sequence Control                                                                                                                                                                                                                                                 | LOW            | No Change                 | 12 mA           | 0   |       |

| W3    | LCDREV            | ALI Reverse                                                                                                                                                                                                                                                                | HIGH           | No Change                 | 12 mA           | 0   |       |

| U8    | LCDCLKIN          | External Clock Input for LCD controller                                                                                                                                                                                                                                    | Input          | No Change                 |                 | ı   |       |

| V8    | LCDVD0            |                                                                                                                                                                                                                                                                            |                |                           |                 |     |       |

| T8    | LCDVD1            |                                                                                                                                                                                                                                                                            |                |                           |                 |     |       |

| W9    | LCDVD2            | LCD Video Data Interface                                                                                                                                                                                                                                                   | LOW            | LOW                       | 12 mA           | 0   |       |

| Y8    | LCDVD3            |                                                                                                                                                                                                                                                                            |                |                           |                 |     |       |

| V9    | LCDENAB/<br>LCDM  | LCD TFT Data Enable     LCD STN AC Bias                                                                                                                                                                                                                                    | LOW            | LOW                       | 12 mA           | 0   |       |

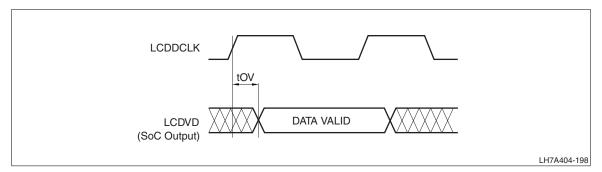

| Y10   | LCDDCLK           | LCD Pixel Clock                                                                                                                                                                                                                                                            | LOW            | LOW                       | 12 mA           | 0   |       |

| U17   | USBDCP            | USB Device Full Speed Pull-up Resistor Control                                                                                                                                                                                                                             | Input          | Input                     | 12 mA           | I   |       |

| U20   | USBDP             | USB Device Data Positive (Differential Pair)                                                                                                                                                                                                                               | Input          | Input                     | 12 mA           | I/O |       |

| U19   | USBDN             | USB Device Data Negative (Differential Pair)                                                                                                                                                                                                                               | Input          | Input                     | 12 mA           | I/O |       |

| W19   | USBHDP0           | USB Data Host Positive 0 (Differential Pair)                                                                                                                                                                                                                               | Input          | HIGH                      | 12 mA           | I/O |       |

| W20   | USBHDN0           | USB Data Host Negative 0 (Differential Pair)                                                                                                                                                                                                                               | Input          | LOW                       | 12 mA           | I/O |       |

| V19   | USBHDP1           | USB Data Host Positive 1 (Differential Pair)                                                                                                                                                                                                                               | Input          | Input                     | 12 mA           | I/O |       |

| V20   | USBHDN1           | USB Data Host Negative 1 (Differential Pair)                                                                                                                                                                                                                               | Input          | Input                     | 12 mA           | I/O |       |

| T17   | USBHPWR           | USB Host Power; This pin is connected to the remote USB Host Power Switch's Enable pin. In response to a fault contition, signalled on the nUSBHOVRCURR pin, the LH7A404 can assert this pin, which causes the power switch shut down.                                     | LOW            | No Change                 | 12 mA           | 0   |       |

| V17   | nUSBHOVRCURR      | USB Host Overcurrent; The overcurrent input is used to indicate to the host a fault has occurred, resulting in current limiting. The LH7A404 can be programmed to cause the remote power switch to shut off by asserting USBHPWR in response to an nUSBHOVRCURR assertion. | Input          | Input                     | 12 mA           | I   |       |

| D11   | nPWME0            | DC-DC Converter 0 PWM 0 Enable                                                                                                                                                                                                                                             | Input          | Input                     | 8 mA            | I/O |       |

| A10   | nPWME1            | DC-DC Converter 1 PWM 1 Enable                                                                                                                                                                                                                                             | Input          | Input                     | 8 mA            | I/O |       |

| C11   | PWM0              | DC-DC Converter 0 Output (Pulse Width Modulated)                                                                                                                                                                                                                           | LOW            | Input                     | 8 mA            | I/O |       |

| C10   | PWM1              | DC-DC Converter 1 Output (Pulse Width Modulated)                                                                                                                                                                                                                           | LOW            | Input                     | 8 mA            | I/O |       |

| B9    | PWM2              | PWM Output 2                                                                                                                                                                                                                                                               | LOW            | No Change                 | 8 mA            | 0   |       |

| D10   | PWM3              | PWM Output 3                                                                                                                                                                                                                                                               | LOW            | No Change                 |                 | 0   |       |

| C9    | PWMSYNC           | PWM Synchronizing Input for PWM2                                                                                                                                                                                                                                           | Input          | No Change                 | 8 mA            | I   |       |

Table 2. LH7A404 Functional Pin List (Cont'd)

| CABGA      | SIGNAL    | DESCRIPTION                                                                                                       | RESET<br>STATE | STANDBY<br>STATE | OUTPUT<br>DRIVE | I/O | NOTES |

|------------|-----------|-------------------------------------------------------------------------------------------------------------------|----------------|------------------|-----------------|-----|-------|

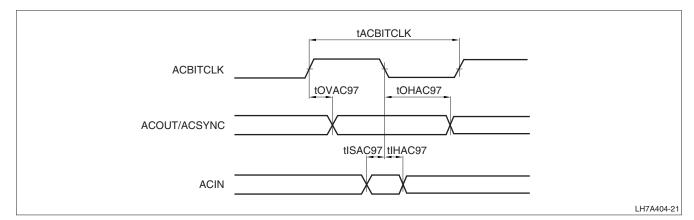

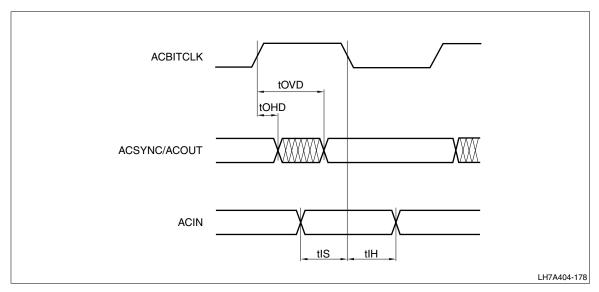

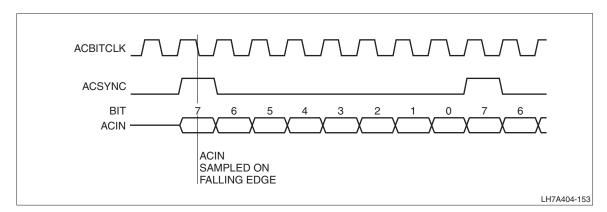

| C7         | ACBITCLK  | Audio Codec (AC97) Clock     Audio Codec (ACI) Clock                                                              | Input          | No Change        | 8 mA            | I/O |       |

| B7         | ACOUT     | Audio Codec (AC97) Output     Audio Codec (ACI) Output                                                            | LOW            | LOW              | 8 mA            | 0   |       |

| A6         | ACSYNC    | <ul><li>Audio Codec (AC97) Synchronization</li><li>Audio Codec (ACI) Synchronization</li></ul>                    | LOW            | LOW              | 8 mA            | 0   |       |

| В6         | ACIN      | <ul><li>Audio Codec (AC97) Input</li><li>Audio Codec (ACI) Input</li></ul>                                        | Input          | No Change        | 8 mA            | I/O |       |

| <b>A</b> 5 | MMCCLK    | MultiMediaCard Clock (20 MHz MAX.)                                                                                | LOW            | LOW              | 8 mA            | I/O |       |

| D7         | MMCCMD    | MultiMediaCard Command                                                                                            | Input          | Input            | 8 mA            | I/O |       |

| C6         | MMCDATA0  | MultiMediaCard Data 0                                                                                             | Input          | Input            | 8 mA            | I/O |       |

| B5         | MMCDATA1  | MultiMediaCard Data 1                                                                                             | Input          | Input            | 8 mA            | I/O |       |

| A4         | MMCDATA2  | MultiMediaCard Data 2                                                                                             | Input          | Input            | 8 mA            | I/O |       |

| B4         | MMCDATA3  | MultiMediaCard Data 3                                                                                             | Input          | Input            | 8 mA            | I/O |       |

| F2         | UARTCTS2  | UART2 Clear to Send Signal                                                                                        | Input          | Input            | 8 mA            | I/O |       |

| F1         | UARTDCD2  | UART2 Data Carrier Detect Signal                                                                                  | Input          | Input            | 8 mA            | I/O |       |

| G2         | UARTDSR2  | UART2 Data Set Ready Signal                                                                                       | Input          | Input            | 8 mA            | I/O |       |

| G3         | UARTIRTX1 | IrDA Transmit                                                                                                     | LOW            | No Change        | 8 mA            | I/O |       |

| G1         | UARTIRRX1 | IrDA Receive                                                                                                      | Input          | Input            | 8 mA            | I/O |       |

| H2         | UARTTX2   | UART2 Transmit Data Output                                                                                        | HIGH           | No Change        | 8 mA            | I/O |       |

| G4         | UARTRX2   | UART2 Receive Data Input                                                                                          | Input          | Input            | 8 mA            | I/O |       |

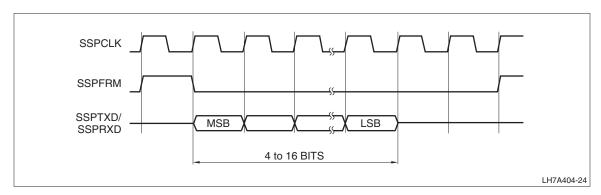

| K3         | SSPCLK    | Synchronous Serial Port Clock                                                                                     | LOW            | LOW              | 8 mA            | 0   |       |

| L1         | SSPRX     | Synchronous Serial Port Receive                                                                                   | Input          | Input            | 8 mA            | I/O |       |

| L3         | SSPTX     | Synchronous Serial Port Transmit                                                                                  | Input          | Input            | 8 mA            | I/O |       |

| K4         | SSPFRM    | Synchronous Serial Port Frame Sync                                                                                | HIGH           | HIGH             | 8 mA            | 0   |       |

| J2         | COL0      |                                                                                                                   |                |                  |                 |     |       |

| H4         | COL1      |                                                                                                                   |                |                  |                 |     |       |

| H5         | COL2      |                                                                                                                   |                |                  |                 |     |       |

| J1         | COL3      |                                                                                                                   |                |                  |                 |     |       |

| J3         | COL4      | Keyboard Interface                                                                                                | HIGH           | HIGH             | 8 mA            | I/O |       |

| J4         | COL5      |                                                                                                                   |                |                  |                 |     |       |

| J5         | COL6      |                                                                                                                   |                |                  |                 |     |       |

| K2         | COL7      |                                                                                                                   |                |                  |                 |     |       |

| E2         | ВАТОК     | Battery OK                                                                                                        | Input          | Input            |                 | ı   | 3     |

| D1         | nBATCHG   | Battery Change                                                                                                    | Input          | Input            |                 | ı   | 3     |

| U12        | BATCNTL   | Battery Control for A/D controller battery monitor                                                                | LOW            | No Change        | 12 mA           | 0   |       |

| H1         | KMIDAT    | Keyboard/Mouse Data                                                                                               | Input          | No Change        | 12 mA           | I/O |       |

| НЗ         | KMICLK    | Keyboard/Mouse Clock                                                                                              | Input          | No Change        | 12 mA           | I/O |       |

| K1         | TBUZ      | Timer Buzzer Output (254 kHz MAX.)                                                                                | LOW            | LOW              | 8 mA            | I/O |       |

| Y16        | AN0/UL/X+ | ADC channel 0     Touch Screen Controller Upper Left     Touch Screen Controller X-plus                           | Input          | Input            |                 | ı   |       |

| Y15        | AN1/UR/X- | ADC channel 1     Touch Screen Controller Upper Right     Touch Screen Controller X-minus                         | Input          | Input            |                 | ı   |       |

| W14        | AN2/LL/Y+ | <ul><li>ADC channel 2</li><li>Touch Screen Controller Lower Left</li><li>Touch Screen Controller Y-plus</li></ul> | Input          | Input            |                 | I   |       |

Table 2. LH7A404 Functional Pin List (Cont'd)

| CABGA | SIGNAL      | DESCRIPTION                                                                                                                                                  | RESET<br>STATE     | STANDBY<br>STATE   | OUTPUT<br>DRIVE | I/O | NOTES |

|-------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|--------------------|-----------------|-----|-------|

| U13   | AN3/LR/Y-   | ADC channel 3     Touch Screen Controller Lower Right     Touch Screen Controller Y-minus                                                                    | Input              | Input              |                 | ı   |       |

| V14   | AN4/WIPER   | ADC channel 4     Wiper input from 5-wire Touch Screen                                                                                                       | Input              | Input              |                 | ı   |       |

| U14   | VSS or VSSA | Connect pin to either VSS or VSSA                                                                                                                            | Input              | Input              |                 | I   |       |

| V15   | AN6         | ADC channel 6                                                                                                                                                | Input              | Input              |                 | I   |       |

| W15   | AN7         | ADC channel 7                                                                                                                                                | Input              | Input              |                 | I   |       |

| T13   | AN8         | ADC channel 8                                                                                                                                                | Input              | Input              |                 | I   |       |

| Y14   | AN9         | ADC channel 9                                                                                                                                                | Input              | Input              |                 | Ι   |       |

| E12   | SCIO        | Smart Card Interface I/O                                                                                                                                     | LOW                | LOW                | 12 mA           | I/O |       |

| A11   | SCCLK       | Smart Card Interface Clock                                                                                                                                   | LOW                | LOW                | 12 mA           | I/O |       |

| B11   | nSCRESET    | Smart Card Interface Reset                                                                                                                                   | LOW                | LOW                | 12 mA           | 0   |       |

| B10   | SCVCCEN     | Smart Card Interface VCC Enable                                                                                                                              | LOW                | No Change          | 12 mA           | 0   |       |

| D6    | CTCLKIN     | Counter Timer Clock Input                                                                                                                                    | Input              | No Change          |                 | I   |       |

| A3    | DREQ0       | DMA Request 0                                                                                                                                                | Input              | No Change          |                 | I   |       |

| D5    | DACK0       | DMA Acknowledge 0                                                                                                                                            | Input              | No Change          | 12 mA           | I/O |       |

| C4    | DEOT0       | DMA End of Transfer 0                                                                                                                                        | Input              | No Change          | 12 mA           | I/O |       |

| В3    | DREQ1       | DMA Request 1                                                                                                                                                | Input              | No Change          |                 | I   |       |

| A2    | DACK1       | DMA Acknowledge 1                                                                                                                                            | Input              | No Change          | 12 mA           | I/O |       |

| E5    | DEOT1       | DMA End of Transfer 1                                                                                                                                        | Input              | No Change          | 12 mA           | I/O |       |

| U16   | nTEST0      | Test Pin 0. Internal weak pull up to VDD. Status latched at nPOR going HIGH. Pull LOW for JTAG mode. Pull HIGH (or leave open) for Normal mode. See Table 3. | Input with pull-up | Input with pull-up |                 | I   |       |

| W18   | nTEST1      | Test Pin 1. Internal weak pull up to VDD. Status latched at nPOR going HIGH. Pull HIGH (or leave open) for both JTAG and Normal mode. See Table 3.           | Input with pull-up | Input with pull-up |                 | ı   |       |

| D3    | TDI         | JTAG Data In. Internal weak pull up to VDD.                                                                                                                  | Input              | No Change          |                 | I   |       |

| C2    | TCK         | JTAG Clock. Internal weak pull up to VDD.                                                                                                                    | Input              | No Change          |                 | I   | 3     |