# L6229Q

DMOS driver for three-phase brushless DC motor

## Features

- Operating supply voltage from 8 to 52 V

- 2.8 A output peak current (1.4 A RMS)

- $R_{DS(on)} 0.73 \Omega$  typ. value @  $T_J = 25 °C$

- Operating frequency up to 100 kHz

- Non dissipative overcurrent detection and protection

- Diagnostic output

- Constant t<sub>OFF</sub> PWM current controller

- Slow decay synchronous rectification

- 60° and 120° hall effect decoding logic

- Brake function

- Cross conduction protection

- Thermal shutdown

- Under voltage lockout

- Integrated fast free wheeling diodes

## Description

The L6229Q is a DMOS fully integrated threephase motor driver with overcurrent protection.

Realized in BCDmultipower technology, the device combines isolated DMOS power transistors with CMOS and bipolar circuits on the same chip.

The device includes all the circuitry needed to drive a three-phase BLDC motor including: a three-phase DMOS bridge, a constant off time PWM current controller and the decoding logic for single ended hall sensors that generates the required sequence for the power stage.

Available in VFQFPN-32 5 x 5 package, the L6229Q features a non-dissipative overcurrent protection on the high side power MOSFETs and thermal shutdown.

#### Table 1. Device summary

| Order codes | Package             | Packaging     |

|-------------|---------------------|---------------|

| L6229Q      | VFQFPN32 5x5x1.0 mm | Tube          |

| L6229QTR    |                     | Tape and reel |

www.st.com

# Contents

| 1 | Bloc  | Block diagram                                        |  |  |  |  |  |

|---|-------|------------------------------------------------------|--|--|--|--|--|

| 2 | Elec  | trical data                                          |  |  |  |  |  |

|   | 2.1   | Absolute maximum ratings 4                           |  |  |  |  |  |

|   | 2.2   | Recommended operating conditions 4                   |  |  |  |  |  |

|   | 2.3   | Thermal data                                         |  |  |  |  |  |

| 3 | Pin o | connection                                           |  |  |  |  |  |

| 4 | Elec  | trical characteristics8                              |  |  |  |  |  |

| 5 | Circ  | uit description                                      |  |  |  |  |  |

|   | 5.1   | Power stages and charge pump 11                      |  |  |  |  |  |

|   | 5.2   | Logic inputs                                         |  |  |  |  |  |

|   | 5.3   | PWM current control                                  |  |  |  |  |  |

|   | 5.4   | Slow decay mode                                      |  |  |  |  |  |

|   | 5.5   | Decoding logic                                       |  |  |  |  |  |

|   | 5.6   | Tacho                                                |  |  |  |  |  |

|   | 5.7   | Non-dissipative overcurrent detection and protection |  |  |  |  |  |

| 6 | Арр   | lication information                                 |  |  |  |  |  |

|   | 6.1   | Output current capability and ic power dissipation   |  |  |  |  |  |

|   | 6.2   | Thermal management 24                                |  |  |  |  |  |

| 7 | Pack  | age mechanical data 25                               |  |  |  |  |  |

| 8 | Revi  | sion history                                         |  |  |  |  |  |

# 1 Block diagram

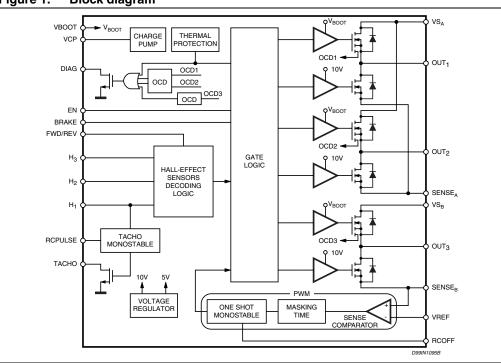

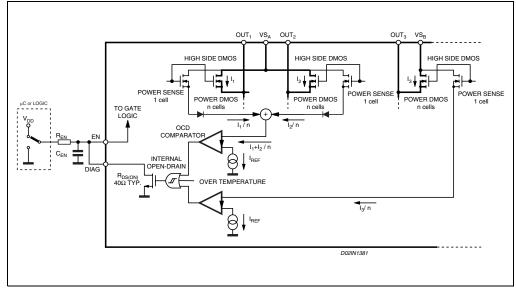

#### Figure 1. Block diagram

## 2 Electrical data

## 2.1 Absolute maximum ratings

| Symbol                             | Parameter                                                                                             | Parameter                                                                         | Value               | Unit |

|------------------------------------|-------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|---------------------|------|

| V <sub>S</sub>                     | Supply voltage                                                                                        | $V_{SA} = V_{SB} = V_S$                                                           | 60                  | V    |

| V <sub>OD</sub>                    | Differential voltage between: $VS_A$ , $OUT_1$ , $OUT_2$ , $SENSE_A$ and $VS_B$ , $OUT_3$ , $SENSE_B$ | $V_{SA} = V_{SB} = V_S = 60 V;$<br>$V_{SENSEA} = V_{SENSEB} =$<br>GND             | 60                  | v    |

| V <sub>BOOT</sub>                  | Bootstrap peak voltage                                                                                | $V_{SA} = V_{SB} = V_S$                                                           | V <sub>S</sub> + 10 | V    |

| V <sub>IN</sub> , V <sub>EN</sub>  | Logic inputs voltage range                                                                            |                                                                                   | -0.3 to +7          | V    |

| V <sub>REF</sub>                   | Voltage range at pin VREF                                                                             |                                                                                   | -0.3 to +7          | V    |

| V <sub>RCOFF</sub>                 | Voltage range at pin RCOFF                                                                            |                                                                                   | -0.3 to +7          | V    |

| V <sub>RCPULSE</sub>               | Voltage range at pin RCPULSE                                                                          |                                                                                   | -0.3 to +7          | V    |

| V <sub>SENSE</sub>                 | Voltage range at pins $SENSE_A$ and $SENSE_B$                                                         |                                                                                   | -1 to +4            | V    |

| I <sub>S(peak)</sub>               | Pulsed supply current (for each ${\rm V}_{\rm S}$ pin)                                                | V <sub>SA</sub> = V <sub>SB</sub> = V <sub>S</sub> ;<br>T <sub>PULSE</sub> < 1 ms | 3.55                | А    |

| ۱ <sub>S</sub>                     | RMS supply current (for each $V_S$ pin)                                                               | $V_{SA} = V_{SB} = V_S$                                                           | 1.4                 | А    |

| T <sub>stg</sub> , T <sub>OP</sub> | Storage and operating temperature range                                                               |                                                                                   | -40 to 150          | °C   |

#### Table 2. Absolute maximum ratings

## 2.2 Recommended operating conditions

| Table 3. | Recommended | operating | conditions |

|----------|-------------|-----------|------------|

|----------|-------------|-----------|------------|

| Symbol                                      | Parameter                                                                                                          | Parameter                                          | Min      | Max    | Unit   |

|---------------------------------------------|--------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|----------|--------|--------|

| V <sub>S</sub>                              | Supply voltage                                                                                                     | $V_{SA} = V_{SB} = V_S$                            | 8        | 52     | V      |

| V <sub>OD</sub>                             | Differential voltage between $VS_A$ , $OUT1_A$ , $OUT2_A$ , $SENSE_A$ and $VS_B$ , $OUT1_B$ , $OUT2_B$ , $SENSE_B$ |                                                    | 52       | V      |        |

| V <sub>REFA</sub> , V <sub>REFB</sub>       | Voltage range at pins $V_{REFA}$ and $V_{REFB}$                                                                    |                                                    | -0.1     | 5      | V      |

| V <sub>SENSEA,</sub><br>V <sub>SENSEB</sub> | Voltage range at pins $SENSE_A$ and $SENSE_B$                                                                      | (pulsed t <sub>W</sub> < t <sub>rr</sub> )<br>(DC) | -6<br>-1 | 6<br>1 | V<br>V |

| I <sub>OUT</sub>                            | RMS output current                                                                                                 |                                                    |          | 1.4    | А      |

| TJ                                          | Operating junction temperature                                                                                     |                                                    | -25      | +125   | °C     |

| f <sub>sw</sub>                             | Switching frequency                                                                                                |                                                    |          | 100    | kHz    |

## 2.3 Thermal data

#### Table 4. Thermal data

| Symbol              | Parameter                                    | Value | Unit |

|---------------------|----------------------------------------------|-------|------|

| R <sub>th(JA)</sub> | Thermal resistance junction-ambient max. (1) | 42    | °C/W |

Mounted on a double-layer FR4 PCB with a dissipating copper surface of 0.5 cm<sup>2</sup> on the top side plus 6 cm<sup>2</sup> ground layer connected through 18 via holes (9 below the IC).

## 3 Pin connection

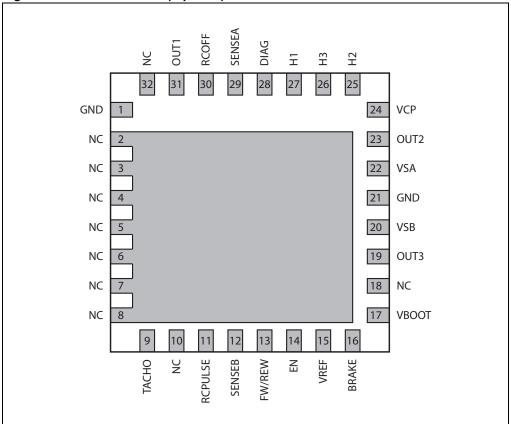

Figure 2. Pin connection (top view)

Note: 1 The pins 2 to 8 are connected to die PAD.

2 The die PAD must be connected to GND pin.

| Table 5. | Pin description    |                      |                                                                                                                                                                                                               |  |

|----------|--------------------|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| N°       | Pin                | Туре                 | Function                                                                                                                                                                                                      |  |

| 1, 21    | GND                | GND                  | Ground terminals.                                                                                                                                                                                             |  |

| 9        | TACHO              | Open drain<br>output | Frequency-to-voltage open drain output. Every pulse from pin $\rm H_1$ is shaped as a fixed and adjustable length pulse.                                                                                      |  |

| 11       | RCPULSE            | RC pin               | RC network pin. A parallel RC network connected between this pin and ground sets the duration of the monostable pulse used for the frequency-to-voltage converter.                                            |  |

| 12       | SENSE <sub>B</sub> | Power supply         | Half bridge 3 source Pin. This pin must be connected together with pin $SENSE_A$ to power ground through a sensing power resistor. At this pin also the Inverting Input of the sense comparator is connected. |  |

| 13       | FWD/REV            | Logic input          | Selects the direction of the rotation. HIGH logic level sets forward operation, whereas LOW logic level sets reverse operation.<br>If not used, it has to be connected to GND or +5 V.                        |  |

| 14       | EN                 | Logic input          | Chip enable. LOW logic level switches OFF all power MOSFETs.<br>If not used, it has to be connected to +5 V.                                                                                                  |  |

| 15       | VREF               | Logic input          | Current controller reference voltage.<br>Do not leave this pin open or connect to GND.                                                                                                                        |  |

| 16       | BRAKE              | Logic input          | Brake input pin. LOW logic level switches ON all high side power MOSFETs, implementing the brake function.<br>If not used, it has to be connected to +5 V.                                                    |  |

| 17       | VBOOT              | Supply<br>voltage    | Bootstrap voltage needed for driving the upper power MOSFETs.                                                                                                                                                 |  |

| 19       | OUT <sub>3</sub>   | Power output         | Output half bridge 3.                                                                                                                                                                                         |  |

| 20       | VS <sub>B</sub>    | Power supply         | Half bridge 3 power supply voltage. It must be connected to the supply voltage together with pin $VS_A$ .                                                                                                     |  |

| 22       | VS <sub>A</sub>    | Power supply         | Half bridge 1 and half bridge 2 power supply voltage. It must be connected to the supply voltage together with pin $\text{VS}_{\text{B}}$ .                                                                   |  |

| 23       | OUT <sub>2</sub>   | Power output         | Output half bridge 2.                                                                                                                                                                                         |  |

| 24       | VCP                | Output               | Charge pump oscillator output.                                                                                                                                                                                |  |

| 25       | H <sub>2</sub>     | Sensor input         | Single ended hall effect sensor input 2.                                                                                                                                                                      |  |

| 26       | H <sub>3</sub>     | Sensor input         | Single ended hall effect sensor input 3.                                                                                                                                                                      |  |

| 27       | H <sub>1</sub>     | Sensor input         | Single ended hall effect sensor input 1.                                                                                                                                                                      |  |

| 28       | DIAG               | Open drain<br>output | Overcurrent detection and thermal protection pin. An internal open drain transistor pulls to GND when an overcurrent on one of the high side MOSFETs is detected or during thermal protection.                |  |

| 29       | SENSEA             | Power supply         | Half bridge 1 and half bridge 2 source pin. This pin must be connected together with pin ${\sf SENSE}_{\sf B}$ to power ground through a sensing power resistor.                                              |  |

| 30       | RCOFF              | RC pin               | RC network pin. A parallel RC network connected between this pin and ground sets the current controller OFF-Time.                                                                                             |  |

| 31       | OUT <sub>1</sub>   | Power output         | Output half bridge 1.                                                                                                                                                                                         |  |

Table 5. Pin description

# 4 Electrical characteristics

#### Table 6. Electrical characteristics

( $V_S$  = 48 V,  $T_A$  = 25 °C, unless otherwise specified)

| Symbol                | Parameter Test condition                            |                                                                      | Min  | Тур  | Мах  | Unit |

|-----------------------|-----------------------------------------------------|----------------------------------------------------------------------|------|------|------|------|

| V <sub>Sth(ON)</sub>  | Turn-on threshold                                   |                                                                      | 5.8  | 6.3  | 6.8  | V    |

| V <sub>Sth(OFF)</sub> | Turn-off threshold                                  |                                                                      | 5    | 5.5  | 6    | V    |

| ۱ <sub>S</sub>        | Quiescent supply current                            | All bridges OFF;<br>T <sub>J</sub> = -25 °C to 125 °C <sup>(1)</sup> |      | 5    | 10   | mA   |

| T <sub>j(OFF)</sub>   | Thermal shutdown temperature                        |                                                                      |      | 165  |      | °C   |

| Output DM             | OS transistors                                      |                                                                      |      |      |      | I.   |

| _                     | High-side + low-side switch ON                      | T <sub>J</sub> = 25 °C                                               |      | 1.47 | 1.69 | Ω    |

| R <sub>DS(on)</sub>   | resistance                                          | $T_{\rm J} = 125  ^{\circ}{\rm C}^{(1)}$                             |      | 2.35 | 2.70 | Ω    |

|                       |                                                     | EN = Low; OUT = V <sub>S</sub>                                       |      |      | 2    | mA   |

| I <sub>DSS</sub>      | Leakage current                                     | EN = Low; OUT = GND                                                  | -0.3 |      |      | mA   |

| Source dra            | in diodes                                           |                                                                      |      |      |      |      |

| V <sub>SD</sub>       | Forward ON voltage                                  | I <sub>SD</sub> = 1.4 A, EN = LOW                                    |      | 1.15 | 1.3  | V    |

| t <sub>rr</sub>       | Reverse recovery time                               | I <sub>f</sub> = 1.4 A                                               |      | 300  |      | ns   |

| t <sub>fr</sub>       | Forward recovery time                               |                                                                      |      | 200  |      | ns   |

| Logic input           | s (EN, CONTROL, HALF/FULL, CLOCK                    | , RESET, CW/CCW)                                                     |      | I    |      |      |

| V <sub>IL</sub>       | Low level logic input voltage                       |                                                                      | -0.3 |      | 0.8  | V    |

| V <sub>IH</sub>       | High level logic input voltage                      |                                                                      | 2    |      | 7    | V    |

| IIL                   | Low level logic input current                       | GND logic input voltage                                              | -10  |      |      | μA   |

| I <sub>IH</sub>       | High level logic input current                      | 7 V logic input voltage                                              |      |      | 10   | μA   |

| V <sub>th(ON)</sub>   | Turn-on input threshold                             |                                                                      |      | 1.8  | 2.0  | V    |

| V <sub>th(OFF)</sub>  | Turn-off input threshold                            |                                                                      | 0.8  | 1.3  |      | V    |

| V <sub>th(HYS)</sub>  | Input threshold hysteresis                          |                                                                      | 0.25 | 0.5  |      | V    |

| Switching o           | characteristics                                     |                                                                      |      |      |      | I    |

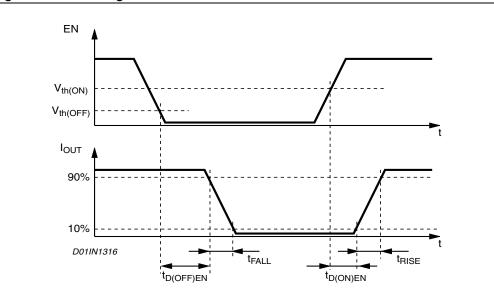

| t <sub>D(ON)EN</sub>  | Enable to output turn-on delay time $(2)$           |                                                                      | 500  | 650  | 800  | ns   |

| t <sub>D(OFF)EN</sub> | Enable to output turn-off delay time <sup>(2)</sup> |                                                                      | 500  |      | 1000 | ns   |

| t <sub>D(on)IN</sub>  | Other logic inputs to OUT turn-ON delay time        | I <sub>LOAD</sub> = 1.4 A, resistive load                            |      | 1.6  |      | μs   |

| t <sub>D(off)IN</sub> | Other logic inputs to OUT turn-OFF delay time       |                                                                      |      | 800  |      | ns   |

| t <sub>RISE</sub>     | Output rise time <sup>(2)</sup>                     |                                                                      | 40   |      | 250  | ns   |

| t <sub>FALL</sub>     | Output fall time <sup>(2)</sup>                     | 1                                                                    | 40   |      | 250  | ns   |

| t <sub>DT</sub>       | Dead time                                           |                                                                      | 0.5  | 1    |      | μs   |

|                       |                                                     |                                                                      |      | •    | •    |      |

#### Table 6. Electrical characteristics (continued)

$(V_S = 48 \text{ V}, T_A = 25 \text{ °C}, \text{ unless otherwise specified})$

|                       | $(v_{\rm S} = 48 v, T_{\rm A} = 25 °C, unless otherwise specified)$ |                                                      |     |     |      |      |  |

|-----------------------|---------------------------------------------------------------------|------------------------------------------------------|-----|-----|------|------|--|

| Symbol                | Parameter                                                           | Test condition                                       | Min | Тур | Max  | Unit |  |

| f <sub>CP</sub>       | Charge pump frequency                                               | $T_J$ = -25 °C to 125 °C <sup>(1)</sup>              |     | 0.6 | 1    | MHz  |  |

| PWM comp              | arator and monostable                                               |                                                      |     |     |      |      |  |

| I <sub>RCOFF</sub>    | Source current at pin RCOFF                                         | V <sub>RCOFF</sub> = 2.5 V                           | 3.5 | 5.5 |      | mA   |  |

| V <sub>OFFSET</sub>   | Offset voltage on sense comparator <sup>(3)</sup>                   | V <sub>ref</sub> = 0.5 V                             |     | ±5  |      | mV   |  |

| t <sub>prop</sub>     | Turn OFF propagation delay <sup>(4)</sup>                           | V <sub>ref</sub> = 0.5 V                             |     | 500 |      | ns   |  |

| t <sub>blank</sub>    | Internal blanking time on sense comparator                          |                                                      |     | 1   |      | μs   |  |

| t <sub>ON(min)</sub>  | Minimum on time                                                     |                                                      |     | 2.5 | 3    | μs   |  |

| +                     | PWM recirculation time                                              | $R_{OFF}$ = 20 kΩ; $C_{OFF}$ = 1 nF                  |     | 13  |      | μS   |  |

| t <sub>OFF</sub>      |                                                                     | $R_{OFF}$ = 100 k $\Omega$ ; $C_{OFF}$ = 1 nF        |     | 61  |      | μS   |  |

| I <sub>BIAS</sub>     | Input bias current at pin VREF                                      |                                                      |     |     | 10   | μA   |  |

| Tacho mon             | ostable                                                             |                                                      |     |     |      |      |  |

| IRCPULSE              | Source current at pin RCPULSE                                       | V <sub>RCPULSE</sub> = 2.5 V                         | 3.5 | 5.5 |      | mA   |  |

|                       | Manastable of time                                                  | $R_{PUL}$ = 20 k $\Omega$ ; $C_{PUL}$ = 1 nF         |     | 12  |      | μS   |  |

| t <sub>PULSE</sub>    | Monostable of time                                                  | $R_{PUL}$ = 100 k $\Omega$ ; $C_{PUL}$ = 1 nF        |     | 60  |      | μS   |  |

| R <sub>TACHO</sub>    | Open drain ON resistance                                            |                                                      |     | 40  | 60   | W    |  |

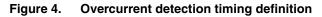

| Over currer           | nt detection and protection                                         |                                                      |     |     |      |      |  |

| I <sub>SOVER</sub>    | Supply overcurrent protection threshold                             | T <sub>J</sub> = -25 to 125 °C $^{(2)}$              | 2   | 2.8 | 3.55 | Α    |  |

| R <sub>OPDR</sub>     | Open drain ON resistance                                            | I <sub>DIAG</sub> = 4 mA                             |     | 40  | 60   | W    |  |

| I <sub>OH</sub>       | OCD high level leakage current                                      | V <sub>DIAG</sub> = 5 V                              |     | 1   |      | μA   |  |

| t <sub>OCD(ON)</sub>  | OCD turn-ON delay time <sup>(4)</sup>                               | $I_{DIAG} = 4 \text{ mA}; C_{DIAG} < 100 \text{ pF}$ |     | 200 |      | ns   |  |

| t <sub>OCD(OFF)</sub> | OCD turn-OFF delay time (4)                                         | I <sub>DIAG</sub> = 4 mA; C <sub>DIAG</sub> < 100 pF |     | 100 |      | ns   |  |

|                       |                                                                     |                                                      |     |     |      |      |  |

1. Tested at 25 °C in a restricted range and guaranteed by characterization

2. See Figure 3.

3. Measured applying a voltage of 1 V to pin SENSE and a voltage drop from 2 V to 0 V to pin VREF.

4. See Figure 4.

Figure 3. Switching characteristic definition

## 5 Circuit description

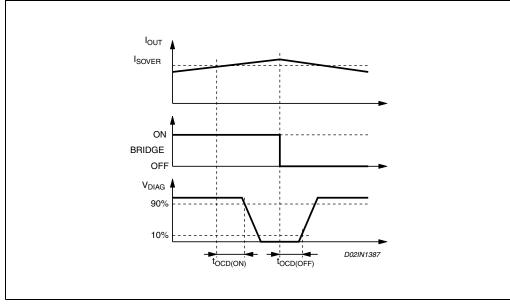

### 5.1 Power stages and charge pump

The L6229Q integrates a three-phase bridge, which consists of 6 power MOSFETs connected as shown on the block diagram (see *Figure 1*). each power MOS has an  $R_{DS(ON)} = 0.73 \ \Omega$  (typical value @ 25 °C) with intrinsic fast freewheeling diode. Switching patterns are generated by the PWM current controller and the hall effect sensor decoding logic (see relative paragraph 3.3 and 3.5). Cross conduction protection is implemented by using a dead time (t<sub>DT</sub> = 1 µs typical value) set by internal timing circuit between the turn off and turn on of two power MOSFETs in one leg of a bridge.

Pins  $VS_A$  and  $VS_B$  must be connected together to the supply voltage ( $V_S$ ).

Using N-channel power MOS for the upper transistors in the bridge requires a gate drive voltage above the power supply voltage. The bootstrapped supply ( $V_{BOOT}$ ) is obtained through an internal oscillator and few external components to realize a charge pump circuit as shown in *Figure 5*. The oscillator output (pin VCP) is a square wave at 600 kHz (typically) with 10 V amplitude. Recommended values/part numbers for the charge pump circuit are shown in *Table 7*.

| Component         | Value  |

|-------------------|--------|

| C <sub>BOOT</sub> | 220 nF |

| C <sub>P</sub>    | 10 nF  |

| D1                | 1N4148 |

| D2                | 1N4148 |

Table 7.

Charge pump external component values

57

### 5.2 Logic inputs

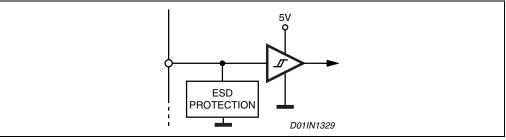

Pins FWD/REV, BRAKE, EN, H1, H2 and H3 are TTL/CMOS and microcontroller compatible logic inputs. The internal structure is shown in *Figure 6*. Typical value for turn-on and turn-off thresholds are respectively  $V_{th(ON)}$  = 1.8 V and  $V_{th(OFF)}$  = 1.3 V.

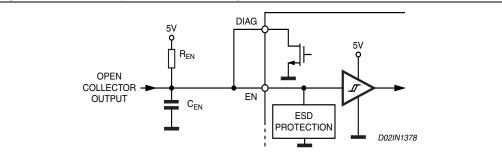

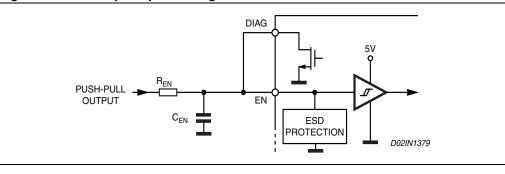

Pin EN (Enable) has identical input structure with the exception that the drain of the Overcurrent and thermal protection MOSFET is also connected to this pin. Due to this connection some care needs to be taken in driving this pin. The EN input may be driven in one of two configurations as shown in *Figure 10* or *Figure 11*. If driven by an open drain (collector) structure, a pull-up resistor R<sub>EN</sub> and a capacitor C<sub>EN</sub> are connected as shown in *Figure 10*. If the driver is a standard Push-Pull structure the resistor R<sub>EN</sub> and the capacitor C<sub>EN</sub> are connected as shown in *Figure 11*. The resistor R<sub>EN</sub> should be chosen in the range from 2.2 k $\Omega$  to 180 k $\Omega$ . Recommended values for R<sub>EN</sub> and C<sub>EN</sub> are respectively 10 k $\Omega$  and 5.6 nF. More information on selecting the values is found in the overcurrent protection section.

#### Figure 6. Logic inputs internal structure

#### Figure 7. Pin EN open collector driving

#### Figure 8. Pin EN push-pull driving

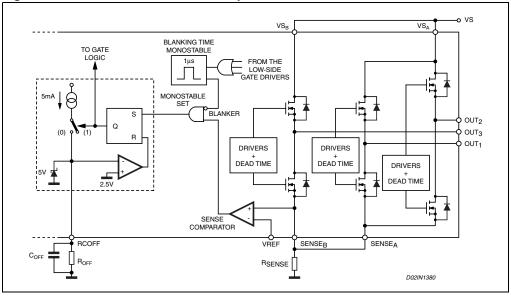

### 5.3 PWM current control

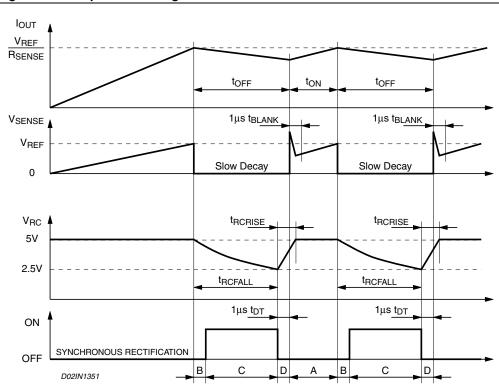

The L6229Q includes a constant off time PWM current controller. The current control circuit senses the bridge current by sensing the voltage drop across an external sense resistor connected between the source of the three lower power MOS transistors and ground, as shown in *Figure 9*. As the current in the motor increases the voltage across the sense resistor increases proportionally. When the voltage drop across the sense resistor becomes greater than the voltage at the reference input pin VREF the sense comparator triggers the monostable switching the bridge off. The power MOS remain off for the time set by the monostable and the motor current recirculates around the upper half of the bridge in slow decay mode as described in the next section. When the monostable times out, the bridge will again turn on. Since the internal dead time, used to prevent cross conduction in the bridge, delays the turn on of the power MOS, the effective off time t<sub>OFF</sub> is the sum of the monostable time plus the dead time.

*Figure 10* shows the typical operating waveforms of the output current, the voltage drop across the sensing resistor, the pin RC voltage and the status of the bridge. More details regarding the synchronous rectification and the output stage configuration are included in the next section.

Immediately after the power MOS turn on, a high peak current flows through the sense resistor due to the reverse recovery of the freewheeling diodes. The L6229Q provides a 1  $\mu$ s blanking time t<sub>BLANK</sub> that inhibits the comparator output so that the current spike cannot prematurely re trigger the monostable.

#### Figure 9. PWM current controller simplified schematic

Figure 10. Output current regulation waveforms

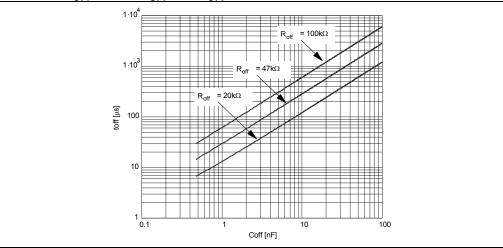

*Figure 11* shows the magnitude of the Off Time  $t_{OFF}$  versus  $C_{OFF}$  and  $R_{OFF}$  values. It can be approximately calculated from the equations:

$t_{RCFALL} = 0.6 \cdot R_{OFF} \cdot C_{OFF}$

$t_{OFF} = t_{RCFALL} + t_{DT} = 0.6 \cdot R_{OFF} \cdot C_{OFF} + t_{DT}$

where  $R_{OFF}$  and  $C_{OFF}$  are the external component values and  $t_{DT}$  is the internally generated Dead Time with:

$\begin{array}{l} 20 \text{ k}\Omega \leq R_{OFF} \leq 100 \text{ k}\Omega \\ 0.47 \text{ nF} \leq C_{OFF} \leq 100 \text{ nF} \\ t_{DT} = 1 \text{ } \mu \text{s} \text{ (typical value)} \end{array}$

Therefore:

$t_{OFF(MIN)} = 6.6 \ \mu s$  $t_{OFF(MAX)} = 6 \ m s$

These values allow a sufficient range of t<sub>OFF</sub> to implement the drive circuit for most motors.

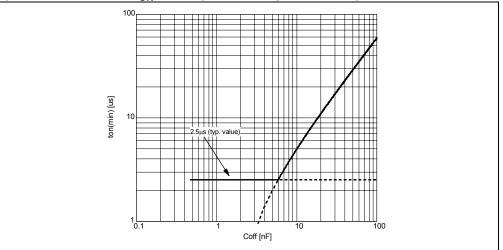

The capacitor value chosen for  $C_{OFF}$  also affects the Rise Time  $t_{RCRISE}$  of the voltage at the pin RCOFF. The rise time  $t_{RCRISE}$  will only be an issue if the capacitor is not completely charged before the next time the monostable is triggered. Therefore, the on time  $t_{ON}$ , which depends by motors and supply parameters, has to be bigger than  $t_{RCRISE}$  for allowing a good current regulation by the PWM stage. Furthermore, the on time  $t_{ON}$  can not be smaller than the minimum on time  $t_{ON(MIN)}$ .

$\begin{cases} t_{ON} > t_{ON(MIN)} = 2.5 \mu s & (typ. value) \\ t_{ON} > t_{RCRISE} - t_{DT} & \end{cases}$

$t_{\text{RCRISE}} = 600 \cdot C_{\text{OFF}}$

*Figure 12* shows the lower limit for the on time  $t_{ON}$  for having a good PWM current regulation capacity. It has to be said that  $t_{ON}$  is always bigger than  $t_{ON(MIN)}$  because the device imposes this condition, but it can be smaller than  $t_{RCRISE} - t_{DT}$ . In this last case the device continues to work but the off time  $t_{OFF}$  is not more constant.

So, small  $C_{OFF}$  value gives more flexibility for the applications (allows smaller on time and, therefore, higher switching frequency), but, the smaller is the value for  $C_{OFF}$  the more influential will be the noises on the circuit performance.

Figure 11. t<sub>OFF</sub> versus C<sub>OFF</sub> and R<sub>OFF</sub>

Figure 12. Area where t<sub>ON</sub> can vary maintaining the PWM regulation

### 5.4 Slow decay mode

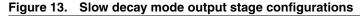

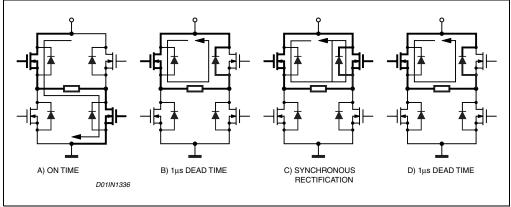

*Figure 13* shows the operation of the bridge in the slow decay mode during the off time. At any time only two legs of the three-phase bridge are active, therefore only the two active legs of the bridge are shown in the figure and the third leg will be off. At the start of the Off Time, the lower power MOS is switched off and the current recirculates around the upper half of the bridge. Since the voltage across the coil is low, the current decays slowly. After the dead time the upper power MOS is operated in the synchronous rectification mode reducing the impedance of the freewheeling diode and the related conducting losses. When the monostable times out, upper MOS that was operating the synchronous mode turns off and the lower power MOS is turned on again after some delay set by the dead time to prevent cross conduction.

## 5.5 Decoding logic

The decoding logic section is a combinatory logic that provides the appropriate driving of the three-phase bridge outputs according to the signals coming from the three hall sensors that detect rotor position in a 3-phase BLDC motor. This novel combinatory logic discriminates between the actual sensor positions for sensors spaced at 60, 120, 240 and 300 electrical degrees. This decoding method allows the implementation of a universal IC without dedicating pins to select the sensor configuration.

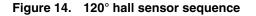

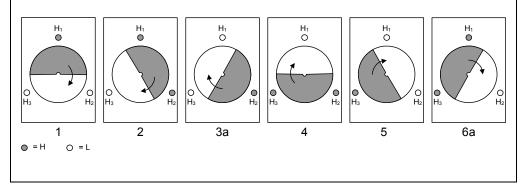

There are eight possible input combinations for three sensor inputs. Six combinations are valid for rotor positions with 120 electrical degrees sensor phasing (see *Figure 14*, positions 1, 2, 3a, 4, 5 and 6a) and six combinations are valid for rotor positions with 60 electrical degrees phasing (see *Figure 15*, positions 1, 2, 3b, 4, 5 and 6b). Four of them are in common (1, 2, 4 and 5) whereas there are two combinations used only in 120 electrical degrees sensor phasing (3a and 6a) and two combinations used only in 60 electrical degrees sensor phasing (3b and 6b).

The decoder can drive motors with different sensor configuration simply by following the *Table 8*. For any input configuration ( $H_1$ ,  $H_2$  and  $H_3$ ) there is one output configuration (OUT<sub>1</sub>, OUT<sub>2</sub> and OUT<sub>3</sub>). The output configuration 3a is the same than 3b and analogously output configuration 6a is the same than 6b.

The sequence of the Hall codes for 300 electrical degrees phasing is the reverse of 60 and the sequence of the Hall codes for 240 phasing is the reverse of 120. So, by decoding the 60

16/28

and the 120 codes it is possible to drive the motor with all the four conventions by changing the direction set.

| Hall 120°        | 1      | 2      | 3a     | -      | 4      | 5      | 6a     | -      |

|------------------|--------|--------|--------|--------|--------|--------|--------|--------|

| Hall 60°         | 1      | 2      | -      | 3b     | 4      | 5      | -      | 6b     |

| H <sub>1</sub>   | Н      | Н      | L      | Н      | L      | L      | Н      | L      |

| H <sub>2</sub>   | L      | Н      | Н      | Н      | Н      | L      | L      | L      |

| H <sub>3</sub>   | L      | L      | L      | Н      | Н      | Н      | Н      | L      |

| OUT <sub>1</sub> | Vs     | High Z | GND    | GND    | GND    | High Z | Vs     | Vs     |

| OUT <sub>2</sub> | High Z | Vs     | Vs     | Vs     | High Z | GND    | GND    | GND    |

| OUT <sub>3</sub> | GND    | GND    | High Z | High Z | Vs     | Vs     | High Z | High Z |

| Phasing          | 1->3   | 2->3   | 2->1   | 2->1   | 3->1   | 3->2   | 1->2   | 1->2   |

Table 8.

60 and 120 electrical degree decoding logic in forward direction

Figure 15. 60° hall sensor sequence

57

### 5.6 Tacho

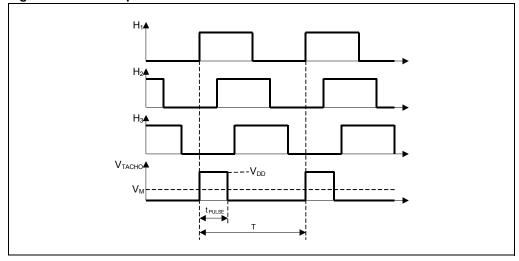

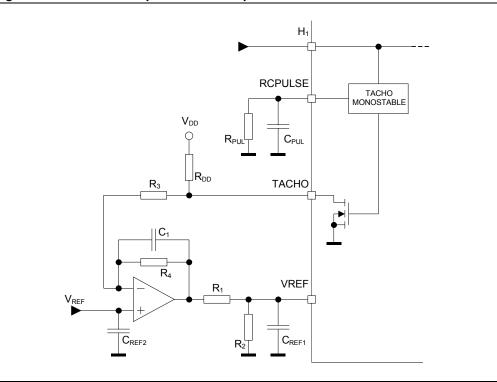

A tachometer function consists of a monostable, with constant off time  $(t_{PULSE})$ , whose input is one hall effect signal  $(H_1)$ . It allows developing an easy speed control loop by using an external op amp, as shown in *Figure 17*. For component values refer to Application Information section.

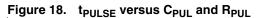

The monostable output drives an open drain output pin (TACHO). At each rising edge of the hall effect sensors  $H_1$ , the monostable is triggered and the MOSFET connected to pin TACHO is turned off for a constant time  $t_{PULSE}$  (see *Figure 16*). The off time  $t_{PULSE}$  can be set using the external RC network ( $R_{PUL}$ ,  $C_{PUL}$ ) connected to the pin RCPULSE. *Figure 18* gives the relation between  $t_{PULSE}$  and  $C_{PUL}$ ,  $R_{PUL}$ . We have approximately:

$t_{\text{PULSE}} = 0.6 \cdot R_{\text{PUL}} \cdot C_{\text{PUL}}$

where  $C_{PUL}$  should be chosen in the range 1 nF  $\dots$  100 nF and  $R_{PUL}$  in the range 20 k $\Omega$   $\dots$  100 k $\Omega$

By connecting the tachometer pin to an external pull-up resistor, the output signal average value  $V_M$  is proportional to the frequency of the hall effect signal and, therefore, to the motor speed. This realizes a simple frequency-to-voltage converter. An op amp, configured as an integrator, filters the signal and compares it with a reference voltage  $V_{REF}$  which sets the speed of the motor.

$$V_{M} = \frac{t_{PULSE}}{T} \cdot V_{DD}$$

#### Figure 16. Tacho operation waveforms

Figure 17. Tachometer speed control loop

### 5.7 Non-dissipative overcurrent detection and protection

The L6229Q integrates an overcurrent detection circuit (OCD) for full protection. This circuit provides output-to-output and output-to-ground short circuit protection as well. With this internal over current detection, the external current sense resistor normally used and its associated power dissipation are eliminated. *Figure 19* shows a simplified schematic for the overcurrent detection circuit.

To implement the over current detection, a sensing element that delivers a small but precise fraction of the output current is implemented with each high side power MOS. Since this current is a small fraction of the output current there is very little additional power dissipation. This current is compared with an internal reference current  $I_{REF}$  When the output current reaches the detection threshold (typically  $I_{SOVER} = 2.8$  A) the OCD comparator signals a fault condition. When a fault condition is detected, an internal open drain MOS with a pull down capability of 4 mA connected to pin DIAG is turned on.

The pin DIAG can be used to signal the fault condition to a  $\mu$ C or to shut down the threephase bridge simply by connecting it to pin EN and adding an external R-C (see R<sub>EN</sub>, C<sub>EN</sub>).

#### Figure 19. Overcurrent protection simplified schematic

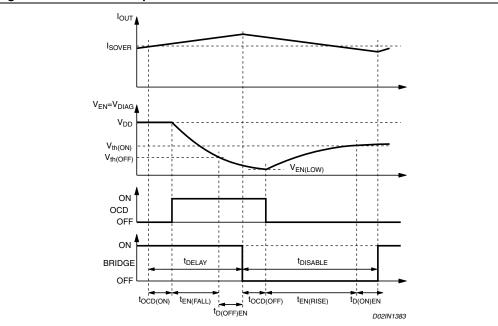

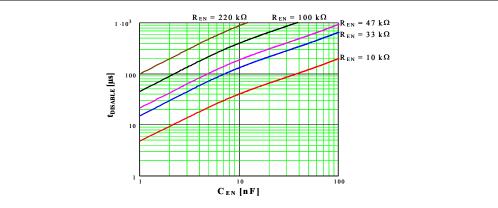

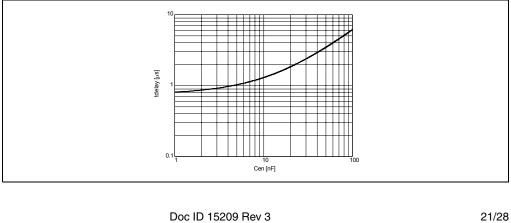

*Figure 20* shows the overcurrent detection operation. The disable time  $t_{DISABLE}$  before recovering normal operation can be easily programmed by means of the accurate thresholds of the logic inputs. It is affected whether by  $C_{EN}$  and  $R_{EN}$  values and its magnitude is reported in *Figure 21*. The delay time  $t_{DELAY}$  before turning off the bridge when an overcurrent has been detected depends only by  $C_{EN}$  value. Its magnitude is reported in *Figure 22*

$C_{EN}$  is also used for providing immunity to pin EN against fast transient noises. Therefore the value of  $C_{EN}$  should be chosen as big as possible according to the maximum tolerable delay time and the  $R_{EN}$  value should be chosen according to the desired disable time.

The resistor R<sub>EN</sub> should be chosen in the range from 2.2 k $\Omega$  to 180 k $\Omega$ . Recommended values for R<sub>EN</sub> and C<sub>EN</sub> are respectively 100 k $\Omega$  and 5.6 nF that allow obtaining 200  $\mu$ s disable time.

Figure 20. Overcurrent protection waveforms

### Figure 21. $t_{\text{DISABLE}}$ versus $C_{\text{EN}}$ and $R_{\text{EN}}$

57

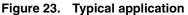

## 6 Application information

A typical application using L6229Q is shown in *Figure 23*. Typical component values for the application are shown in *Table 9*. A high quality ceramic capacitor (C<sub>2</sub>) in the range of 100 nF to 200 nF should be placed between the power pins VS<sub>A</sub> and VS<sub>B</sub> and ground near the L6229Q to improve the high frequency filtering on the power supply and reduce high frequency transients generated by the switching. The capacitor (C<sub>EN</sub>) connected from the EN input to ground sets the shut down time when an over current is detected (see overcurrent protection). The two current sensing inputs (SENSE<sub>A</sub> and SENSE<sub>B</sub>) should be connected to the sensing resistor R<sub>SENSE</sub> with a trace length as short as possible in the layout. The sense resistor should be non-inductive resistor to minimize the dl/dt transients across the resistor. To increase noise immunity, unused logic pins are best connected to keep power ground and signal ground separated on PCB.

| Component                                           | Value  |

|-----------------------------------------------------|--------|

| C <sub>1</sub>                                      | 100 μF |

| C <sub>2</sub>                                      | 100 nF |

| C <sub>3</sub>                                      | 220 nF |

| C <sub>BOOT</sub>                                   | 220 nF |

| C <sub>OFF</sub>                                    | 1 nF   |

| C <sub>PUL</sub>                                    | 10 nF  |

| C <sub>REF1</sub>                                   | 33 nF  |

| C <sub>REF2</sub>                                   | 100 nF |

| C <sub>EN</sub>                                     | 5.6 nF |

| C <sub>P</sub>                                      | 10 nF  |

| D <sub>1</sub>                                      | 1N4148 |

| D <sub>2</sub>                                      | 1N4148 |

| R <sub>1</sub>                                      | 5 k6Ω  |

| R <sub>2</sub>                                      | 1 k8Ω  |

| R <sub>3</sub>                                      | 4 k7Ω  |

| R <sub>4</sub>                                      | 1 MΩ   |

| R <sub>DD</sub>                                     | 1 kΩ   |

| R <sub>EN</sub>                                     | 100 kΩ |

| R <sub>SENSE</sub>                                  | 0.6 Ω  |

| R <sub>OFF</sub>                                    | 33 kΩ  |

| R <sub>PUL</sub>                                    | 47 kΩ  |

| R <sub>H1</sub> , R <sub>H2</sub> , R <sub>H3</sub> | 10 kΩ  |

| Table 9. | Component values for typical application |

|----------|------------------------------------------|

|----------|------------------------------------------|

22/28

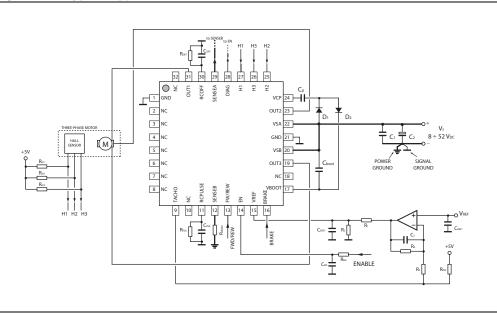

## 6.1 Output current capability and ic power dissipation

In *Figure 24* is shown the approximate relation between the output current and the IC power dissipation using PWM current control.

For a given output current the power dissipated by the IC can be easily evaluated, in order to establish which package should be used and how large must be the on-board copper dissipating area to guarantee a safe operating junction temperature (125 °C maximum).

Figure 24. IC power dissipation versus output power

57

## 6.2 Thermal management

In most applications the power dissipation in the IC is the main factor that sets the maximum current that can be delivered by the device in a safe operating condition. Therefore, it has to be taken into account very carefully. Besides the available space on the PCB, the right package should be chosen considering the power dissipation. Heat sinking can be achieved using copper on the PCB with proper area and thickness.

For instance, using a VFQFPN32L 5 x 5 package the typical  $R_{th(JA)}$  is about 42 °C/W when mounted on a double-layer FR4 PCB with a dissipating copper area of 0.5 cm<sup>2</sup> on the top side plus 6 cm<sup>2</sup> ground layer connected through 18 via holes (9 below the IC).

24/28

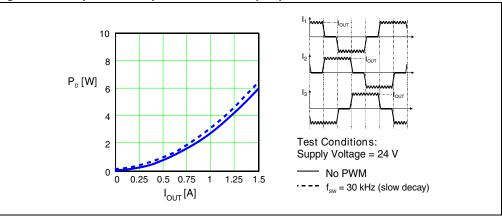

## 7 Package mechanical data

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK® packages, depending on their level of environmental compliance. ECOPACK® specifications, grade definitions and product status are available at: www.st.com. ECOPACK® is an ST trademark.

| Dim  | Databook (mm) |       |       |  |

|------|---------------|-------|-------|--|

| Dim. | Min           | Тур   | Мах   |  |

| А    | 0.80          | 0.85  | 0.95  |  |

| b    | 0.18          | 0.25  | 0.30  |  |

| b1   | 0.165         | 0.175 | 0.185 |  |

| D    | 4.85          | 5.00  | 5.15  |  |

| D2   | 3.00          | 3.10  | 3.20  |  |

| D3   | 1.10          | 1.20  | 1.30  |  |

| E    | 4.85          | 5.00  | 5.15  |  |

| E2   | 4.20          | 4.30  | 4.40  |  |

| E3   | 0.60          | 0.70  | 0.80  |  |

| е    |               | 0.50  |       |  |

| L    | 0.30          | 0.40  | 0.50  |  |

| ddd  |               |       | 0.08  |  |

Table 10. VFQFPN 5 x 5 x 1.0, 32 lead, pitch 0.50

Note:

VFQFPN stands for thermally enhanced very thin profile fine pitch quad flat package no lead. Very thin profile: 0.80 < A < 1.00 mm.

Details of terminal 1 are optional but must be located on the top surface of the package by using either a mold or marked features.

Figure 25. Package dimensions

26/28

# 8 Revision history

#### Table 11. Document revision history

| Date        | Revision | Changes                   |

|-------------|----------|---------------------------|

| 25-Nov-2008 | 1        | First release             |

| 26-Feb-2009 | 2        | Updated Table 4 on page 5 |

| 30-Aug-2010 | 3        | Updated Table 1 on page 1 |

#### Please Read Carefully:

Information in this document is provided solely in connection with ST products. STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, modifications or improvements, to this document, and the products and services described herein at any time, without notice.

All ST products are sold pursuant to ST's terms and conditions of sale.

Purchasers are solely responsible for the choice, selection and use of the ST products and services described herein, and ST assumes no liability whatsoever relating to the choice, selection or use of the ST products and services described herein.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted under this document. If any part of this document refers to any third party products or services it shall not be deemed a license grant by ST for the use of such third party products or services, or any intellectual property contained therein or considered as a warranty covering the use in any manner whatsoever of such third party products or services or services or any intellectual property contained therein.

UNLESS OTHERWISE SET FORTH IN ST'S TERMS AND CONDITIONS OF SALE ST DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY WITH RESPECT TO THE USE AND/OR SALE OF ST PRODUCTS INCLUDING WITHOUT LIMITATION IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION), OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

UNLESS EXPRESSLY APPROVED IN WRITING BY AN AUTHORIZED ST REPRESENTATIVE, ST PRODUCTS ARE NOT RECOMMENDED, AUTHORIZED OR WARRANTED FOR USE IN MILITARY, AIR CRAFT, SPACE, LIFE SAVING, OR LIFE SUSTAINING APPLICATIONS, NOR IN PRODUCTS OR SYSTEMS WHERE FAILURE OR MALFUNCTION MAY RESULT IN PERSONAL INJURY, DEATH, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE. ST PRODUCTS WHICH ARE NOT SPECIFIED AS "AUTOMOTIVE GRADE" MAY ONLY BE USED IN AUTOMOTIVE APPLICATIONS AT USER'S OWN RISK.

Resale of ST products with provisions different from the statements and/or technical features set forth in this document shall immediately void any warranty granted by ST for the ST product or service described herein and shall not create or extend in any manner whatsoever, any liability of ST.

ST and the ST logo are trademarks or registered trademarks of ST in various countries.

Information in this document supersedes and replaces all information previously supplied.

The ST logo is a registered trademark of STMicroelectronics. All other names are the property of their respective owners.

© 2010 STMicroelectronics - All rights reserved

STMicroelectronics group of companies

Australia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan -Malaysia - Malta - Morocco - Philippines - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States of America

www.st.com

28/28