# TECHNICAL MANUAL

# LSI53CF92A Fast SCSI Controller

April 2002 Version 2.1

This document contains proprietary information of LSI Logic Corporation. The information contained herein is not to be used by or disclosed to third parties without the express written permission of an officer of LSI Logic Corporation.

LSI Logic products are not intended for use in life-support appliances, devices, or systems. Use of any LSI Logic product in such applications without written consent of the appropriate LSI Logic officer is prohibited.

Document DB14-000094-02, Third Edition (April 2002)

This document describes the LSI Logic LSI53CF92A Fast SCSI Controller and will remain the official reference source for all revisions of this product until rescinded by an update.

LSI Logic Corporation reserves the right to make changes to any products herein at any time without notice. LSI Logic does not assume any responsibility or liability arising out of the application or use of any product described herein, except as expressly agreed to in writing by LSI Logic; nor does the purchase or use of a product from LSI Logic convey a license under any patent rights, copyrights, trademark rights, or any other of the intellectual property rights of LSI Logic or third parties.

Copyright © 1995–2002 by LSI Logic Corporation. All rights reserved.

#### TRADEMARK ACKNOWLEDGMENT

The LSI Logic logo design, SCRIPTS, SYM, and TolerANT are trademarks or registered trademarks of LSI Logic Corporation. All other brand and product names may be trademarks of their respective companies.

AP

To receive product literature, visit us at http://www.lsilogic.com.

For a current list of our distributors, sales offices, and design resource centers, view our web page located at

http://www.lsilogic.com/contacts/na\_salesoffices.html

# Preface

This book is the primary reference and technical manual for the LSI53CF92A Fast SCSI Controller. It contains a complete functional description and includes complete physical and electrical specifications.

#### Audience

This document assumes that you have some familiarity with current and proposed SCSI standards. The people who benefit from this book are:

- Engineers and managers who are evaluating the controller for possible use in a system

- Engineers who are designing the controller into a system

#### Organization

This document has the following chapters and appendixes:

- Chapter 1, Introduction

- Chapter 2, Functional Description

- Chapter 3, Signal Descriptions

- Chapter 4, Registers

- Chapter 5, Command Set

- Chapter 6, Electrical Specifications

- Appendix A, Register Map

- Appendix B, Wiring Diagram

#### **Related Publications**

#### ANSI

11 West 42nd Street New York, NY 10036 (212) 642-4900 Document No. X3.131-199X (SCSI-2)

#### **Global Engineering Documents**

15 Inverness Way East Englewood, CO 80112 (800) 854-7179 or (303) 397-7956 (outside U.S.) FAX (303) 397-2740 **ENDL Publications** 14426 Black Walnut Court Saratoga, CA 95070 (408) 867-6642 Document names: SCSI Bench Reference, SCSI Encyclopedia, SCSI Tutor

#### **Prentice Hall**

113 Sylvan Avenue

Englewood Cliffs, NJ 07632

(800) 947-7700

SCSI: Understanding the Small Computer System Interface,

ISBN 0-13-796855-8

#### LSI Logic World Wide Web Home Page

www.lsil.com

SCSI SCRIPTS<sup>™</sup> Processors Programming Guide, Order No. S14044.A

SCAM specification X3T9.2/93-109r5

#### **PCI Special Interest Group**

2575 N. E. Katherine Hillsboro, OR 97214 (800) 433-5177; (503) 693-6232 (International); FAX (503) 693-8344

#### **Conventions Used in This Manual**

The word *assert* means to drive a signal true or active. The word *deassert* means to drive a signal false or inactive.

Hexadecimal numbers are indicated by the prefix "0x" —for example, 0x32CF. Binary numbers are indicated by the prefix "0b" —for example, 0b0011.0010.1100.1111.

#### **Revision Record**

| Revision | Date  | Remarks                                                             |  |

|----------|-------|---------------------------------------------------------------------|--|

| 1.0      | 12/97 | st version.                                                         |  |

| 1.1      | 4/99  | Miscellaneous edits, reformat.                                      |  |

| 2.0      | 11/00 | All product names changed from SYM <sup>®</sup> to LSI.             |  |

| 2.1      | 12/01 | Updated Tables 6.7, 6.13, and 6.15 and Figures 6.9, 6.12, and 6.16. |  |

# Contents

| Chapter 1 | Intro | duction   |                                            |      |

|-----------|-------|-----------|--------------------------------------------|------|

|           | 1.1   | Genera    | al Description                             | 1-1  |

|           | 1.2   | SCSI-0    | Configured AutoMatically (SCAM) Capability | 1-2  |

|           | 1.3   |           | NT <sup>®</sup> Technology                 | 1-2  |

|           | 1.4   | Feature   |                                            | 1-3  |

| Chapter 2 | Fund  | ctional D | escription                                 |      |

|           | 2.1   | Typical   | SCSI Operation                             | 2-2  |

|           | 2.2   | Bus-Ini   | itiated Sequences                          | 2-3  |

|           |       | 2.2.1     | Bus-Initiated Selection                    | 2-4  |

|           |       | 2.2.2     | Bus-Initiated Reselection                  | 2-5  |

|           |       | 2.2.3     | Bus-Initiated Reset                        | 2-6  |

|           |       | 2.2.4     | Stacked Commands                           | 2-6  |

|           | 2.3   | Parity    | Checking and Generation                    | 2-6  |

|           | 2.4   | Host B    | us Configuration                           | 2-8  |

|           |       | 2.4.1     | Mode Description                           | 2-8  |

|           |       | 2.4.2     | Multiplexed Bus Configuration Mode         | 2-8  |

|           |       | 2.4.3     | Nonmultiplexed Bus Configuration Mode      | 2-9  |

|           | 2.5   | DMA C     | Operation                                  | 2-9  |

|           |       | 2.5.1     | DMA Threshold                              | 2-9  |

|           |       | 2.5.2     | Normal DMA Mode                            | 2-9  |

|           |       | 2.5.3     | Threshold Eight Mode                       | 2-10 |

|           |       | 2.5.4     | DMA Burst Mode                             | 2-11 |

|           |       | 2.5.5     | Single-Pin, SE SCSI                        | 2-13 |

|           | 2.6   | SCSI [    | Data Transfer Rates                        | 2-14 |

|           |       | 2.6.1     | Asynchronous Operation                     | 2-14 |

|           |       | 2.6.2     | Synchronous Operation                      | 2-14 |

|           | 2.7   | Chip R    | eset                                       | 2-15 |

|           |      | 2.7.1    | Hard Reset                          | 2-15 |

|-----------|------|----------|-------------------------------------|------|

|           |      | 2.7.2    | Soft Reset                          | 2-16 |

|           |      | 2.7.3    | Disconnect Reset                    | 2-17 |

|           | 2.8  | SCAM     | Capabilities                        | 2-17 |

|           |      | 2.8.1    | SCSI Low-Level Programming          | 2-18 |

|           |      | 2.8.2    | SCAM Operations                     | 2-18 |

| Chapter 3 | Sign | al Desci | riptions                            |      |

| Chapter 4 | Regi | isters   |                                     |      |

|           | 4.1  | Standa   | ard Register Set                    | 4-4  |

|           | 4.2  | SCAM     | Register Set                        | 4-36 |

| Chapter 5 | Com  | mand S   | et                                  |      |

|           | 5.1  | Illegal  | Commands                            | 5-3  |

|           |      | 5.1.1    | Stacked Commands                    | 5-3  |

|           | 5.2  | Miscel   | aneous Command Group                | 5-4  |

|           |      | 5.2.1    | No-Operation (NOP)                  | 5-4  |

|           |      | 5.2.2    | Flush FIFO                          | 5-4  |

|           |      | 5.2.3    | Reset Chip                          | 5-4  |

|           |      | 5.2.4    | Reset SCSI Bus                      | 5-5  |

|           |      | 5.2.5    | Disable Selection/Reselection       | 5-5  |

|           | 5.3  | Discon   | nected State Command Group          | 5-5  |

|           |      | 5.3.1    | Reselect Sequence                   | 5-6  |

|           |      | 5.3.2    | Select without ATN Sequence         | 5-6  |

|           |      | 5.3.3    | Select with ATN Sequence            | 5-7  |

|           |      | 5.3.4    | Select with ATN and Stop Sequence   | 5-7  |

|           |      | 5.3.5    | Enable Selection/Reselection        | 5-11 |

|           |      | 5.3.6    | Select with ATN3 Sequence           | 5-11 |

|           |      | 5.3.7    | Reselect3 Sequence                  | 5-12 |

|           | 5.4  | Initiato | r Command Group                     | 5-12 |

|           |      | 5.4.1    | Transfer Information                | 5-14 |

|           |      | 5.4.2    | Initiator Command Complete Sequence | 5-15 |

|           |      | 5.4.3    | Message Accepted                    | 5-15 |

|           |      | 5.4.4    | Transfer Pad                        | 5-16 |

|           |      | 5.4.5    | Set ATN                             | 5-16 |

|           |      | 5.4.6    | Reset ATN                           | 5-16 |

|           |      | 5.4.7    | Set ATN Immediate                   | 5-17 |

|            | Inde  | x          |                                                |      |

|------------|-------|------------|------------------------------------------------|------|

| Appendix B | Wiriı | ng Diagra  | ım                                             |      |

| Appendix A | Regi  | ster Map   |                                                |      |

|            | 6.5   | Packag     | e Drawings                                     | 6-29 |

|            | 6.4   |            | iming Diagrams                                 | 6-23 |

|            |       | 6.3.6      | Burst Mode DMA Interface (Nonmultiplexed Mode) |      |

|            |       | 6.3.5      | Burst Mode DMA Interface (Multiplexed Mode)    | 6-19 |

|            |       | 6.3.4      | DMA Interface (Multiplexed Mode Only)          | 6-17 |

|            |       | 6.3.3      | DMA Interface (Nonmultiplexed Mode Only)       | 6-15 |

|            |       | 6.3.2      | Register Interface, Multiplexed PAD Bus        | 6-13 |

|            |       | 6.3.1      | Register Interface, Nonmultiplexed PAD Bus     | 6-11 |

|            | 6.3   |            | ctrical Characteristics                        | 6-7  |

|            | 6.2   |            | IT Active Negation Technology Specifications   | 6-4  |

| -          | 6.1   |            | ctrical Characteristics                        | 6-1  |

| Chapter 6  | Elec  | trical Spe | ecifications                                   |      |

|            |       | 5.5.12     | Target Abort DMA                               | 5-22 |

|            |       | 5.5.11     | Receive Command Sequence                       | 5-21 |

|            |       | 5.5.10     | Receive Data                                   | 5-21 |

|            |       | 5.5.9      | Receive Command                                | 5-21 |

|            |       | 5.5.8      | Receive Message                                | 5-21 |

|            |       | 5.5.7      | Disconnect                                     | 5-20 |

|            |       | 5.5.6      | Target Command Complete Sequence               | 5-20 |

|            |       | 5.5.5      | Terminate Sequence                             | 5-19 |

|            |       | 5.5.4      | Disconnect Sequence                            | 5-19 |

|            |       | 5.5.3      | Send Data                                      | 5-18 |

|            |       | 5.5.2      | Send Status                                    | 5-18 |

|            | 0.0   | 5.5.1      | Send Message                                   | 5-18 |

|            | 5.5   | Target (   | Command Group                                  | 5-17 |

## Figures

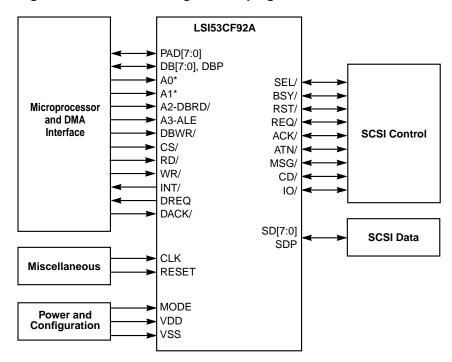

| 1.1  | Functional Block Diagram                            | 1-4  |

|------|-----------------------------------------------------|------|

| 1.2  | Bus Configuration, Multiplexed Mode (Dual Bus,      |      |

|      | 8-Bit DMA Bus and 8-Bit Multiplexed Processor       |      |

|      | Address/Data Bus)                                   | 1-5  |

| 1.3  | Bus Configuration, Nonmultiplexed Mode (Dual Bus,   |      |

|      | 8-Bit DMA Bus and 8-Bit Processor Bus)              | 1-5  |

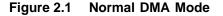

| 2.1  | Normal DMA Mode                                     | 2-10 |

| 2.2  | DMA Burst Mode (Multiplexed Mode and Nonmultiplexed |      |

|      | Mode Writes)                                        | 2-13 |

| 2.3  | DMA Burst Mode (Nonmultiplexed Mode Reads)          | 2-13 |

| 2.4  | SCAM Transfer Cycles                                | 2-23 |

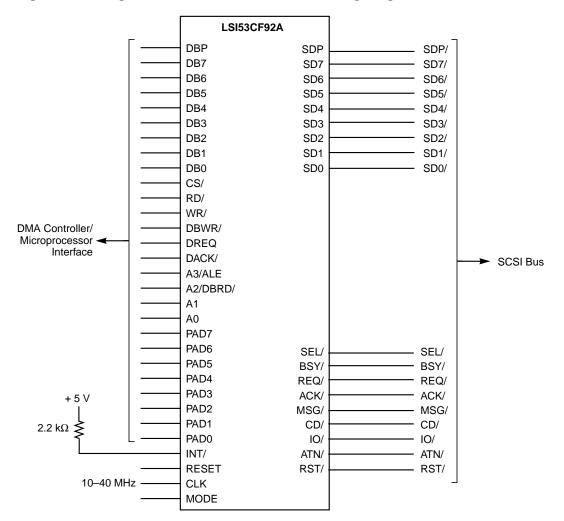

| 3.1  | Functional Signal Grouping                          | 3-1  |

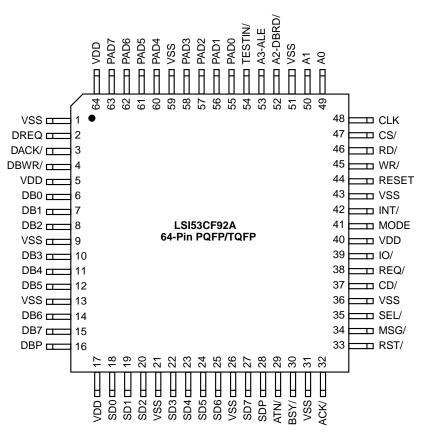

| 3.2  | LSI53CF92A 64-Pin Plastic QFP and Thin QFP Pin      |      |

|      | Configuration <sup>1</sup>                          | 3-6  |

| 4.1  | REQ/ ACK/ Deassertion Delay                         | 4-23 |

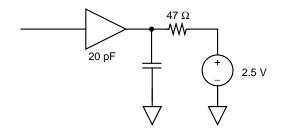

| 6.1  | Rise and Fall Time Test Conditions                  | 6-5  |

| 6.2  | SCSI Input Filtering                                | 6-5  |

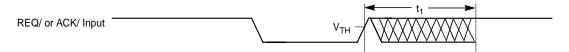

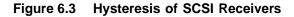

| 6.3  | Hysteresis of SCSI Receivers                        | 6-5  |

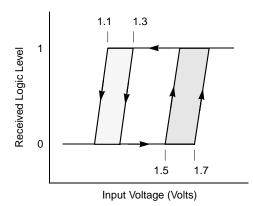

| 6.4  | Input Current as a Function of Input Voltage        | 6-6  |

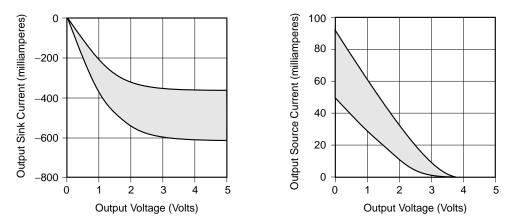

| 6.5  | Output Current as a Function of Output Voltage      | 6-6  |

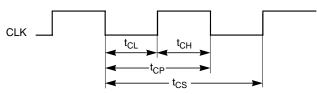

| 6.6  | Clock Input                                         | 6-8  |

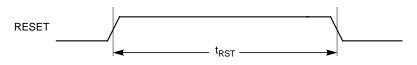

| 6.7  | Reset Input                                         | 6-9  |

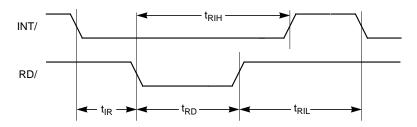

| 6.8  | Interrupt Output                                    | 6-10 |

| 6.9  | Register Read, Nonmultiplexed PAD Bus               | 6-11 |

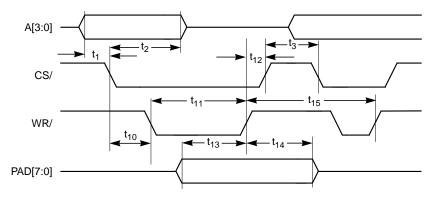

| 6.10 | Register Write, Nonmultiplexed PAD Bus              | 6-11 |

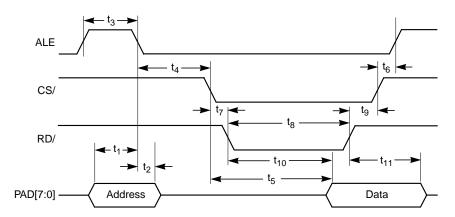

| 6.11 | Register Read, Multiplexed PAD Bus                  | 6-13 |

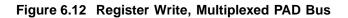

| 6.12 | Register Write, Multiplexed PAD Bus                 | 6-13 |

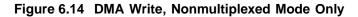

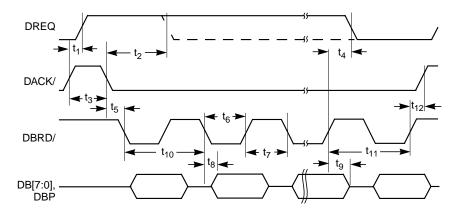

| 6.13 | DMA Read, Nonmultiplexed Mode Only                  | 6-15 |

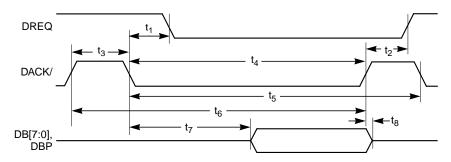

| 6.14 | DMA Write, Nonmultiplexed Mode Only                 | 6-15 |

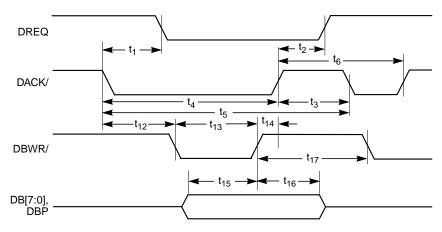

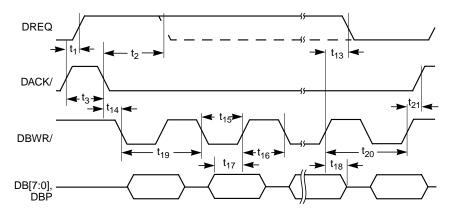

| 6.15 | DMA Read, Multiplexed Mode Only                     | 6-17 |

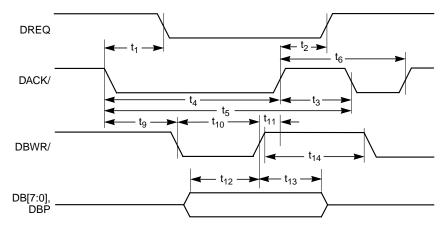

| 6.16 | DMA Write, Multiplexed Mode Only                    | 6-17 |

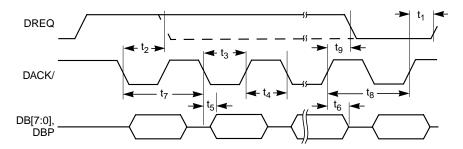

| 6.17 | Burst Mode DMA Read, Multiplexed Mode Only          | 6-19 |

| 6.18 | Burst Mode DMA Write, Multiplexed Mode Only         | 6-19 |

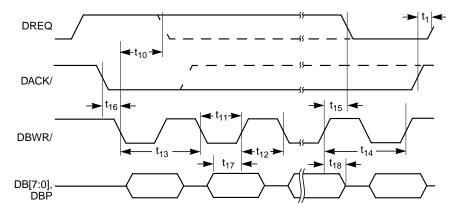

| 6.19 | Burst Mode DMA Read, Nonmultiplexed Mode Only       | 6-21 |

| 6.20 | Burst Mode DMA Write, Nonmultiplexed Mode Only      | 6-21 |

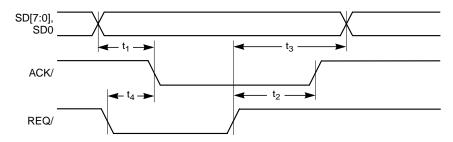

| 6.21 | Initiator Asynchronous Send                         | 6-23 |

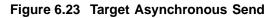

| 6.22 | Initiator Asynchronous Receive                   | 6-24 |

|------|--------------------------------------------------|------|

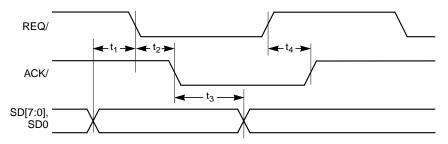

| 6.23 | Target Asynchronous Send                         | 6-25 |

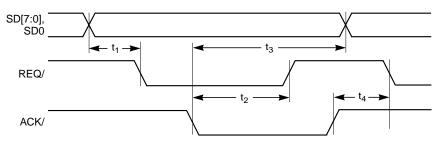

| 6.24 | Target Asynchronous Receive                      | 6-26 |

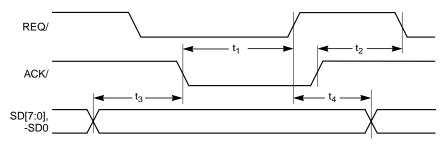

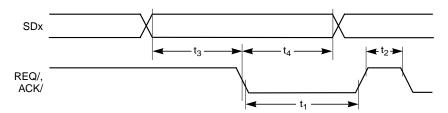

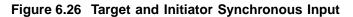

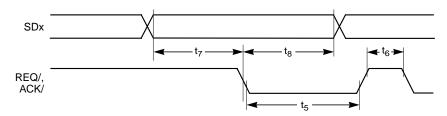

| 6.25 | Target and Initiator Synchronous Output          | 6-27 |

| 6.26 | Target and Initiator Synchronous Input           | 6-27 |

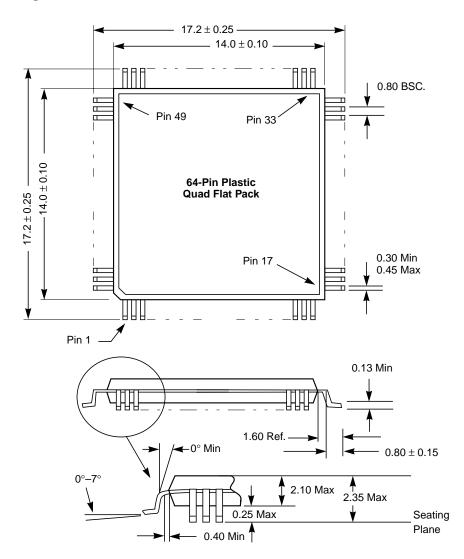

| 6.27 | 64-Pin Plastic Quad Flat Pack                    | 6-29 |

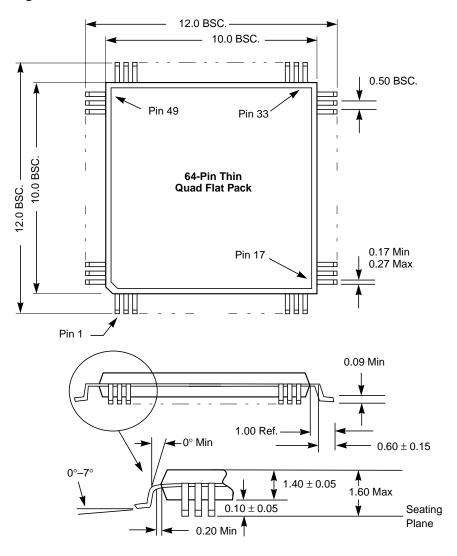

| 6.28 | 64-Pin Thin Quad Flat Pack                       | 6-30 |

| B.1  | Single-Pin, SE SCSI Bus Interface Wiring Diagram | B-1  |

|      |                                                  |      |

#### Tables

| 2.1  | Parity Control                                         | 2-7  |

|------|--------------------------------------------------------|------|

| 2.2  | Minimum Timing Requirements                            | 2-15 |

| 3.1  | Microprocessor and DMA Interface Signals               | 3-2  |

| 3.2  | SCSI Signals                                           | 3-4  |

| 3.3  | Configuration and Test Signals                         | 3-5  |

| 3.4  | Power and Ground Signals                               | 3-5  |

| 4.1  | Register Reset Values                                  | 4-2  |

| 4.2  | Register Set                                           | 4-3  |

| 4.3  | Transfer Rate with 40 MHz Clock (FASTCLK Bit Set)      | 4-19 |

| 4.4  | Transfer Rate with 25 MHz Clock (FASTCLK Bit Clear)    | 4-20 |

| 4.5  | REQ/ ACK/ Deassertion Delay Selection                  | 4-22 |

| 4.6  | REQ/ ACK/ Assertion Delay Selection                    | 4-22 |

| 4.7  | CLK Frequency vs. Clock Conversion Factor              | 4-26 |

| 4.8  | Synchronous Transfer Rate and Minimum Clocks/Byte      | 4-32 |

| 4.9  | DMA Modes                                              | 4-32 |

| 5.1  | Command Set                                            | 5-2  |

| 5.2  | Miscellaneous Commands                                 | 5-4  |

| 5.3  | Disconnected State Commands                            | 5-6  |

| 5.4  | Target Selected without ATN Sequence                   | 5-8  |

| 5.5  | Target Selected with ATN Sequence (SCSI-2 Bit Not Set) | 5-8  |

| 5.6  | Target Selected with ATN Sequence (SCSI-2 Bit or       |      |

|      | Queue Tag Enable Bit Set)                              | 5-9  |

| 5.7  | Initiator Select without ATN Sequence                  | 5-10 |

| 5.8  | Initiator Select with ATN Sequence                     | 5-10 |

| 5.9  | Initiator Select with ATN and Stop Sequence            | 5-11 |

| 5.10 | Initiator Select with ATN3 Sequence                    | 5-12 |

| 5.11 | Initiator Commands                                     | 5-14 |

| 5.12 | Target Commands                                        | 5-18 |

| 5.13 | Target Disconnect Sequence                             | 5-19 |

| 5.14 | Target Terminate Sequence                              | 5-20 |

| 5.15 | Target Command Complete Sequence                       | 5-20 |

| 5.16 | Target Receive Command Sequence                        | 5-22 |

| 6.1  | Absolute Maximum Stress Ratings                        | 6-1  |

| 6.2  | Recommended Operating Conditions                       | 6-2  |

| 6.3  | Inputs                                                 | 6-2  |

| 6.4  | Outputs                                                | 6-3  |

| Bidirectional Pins                             | 6-3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TolerANT Active Negation Technology Electrical |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Characteristics                                | 6-4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Pin Terminations                               | 6-7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Clock Timing (FASTCLK Bit Cleared)             | 6-8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Clock Timing (FASTCLK Bit Set)                 | 6-8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Reset Timing                                   | 6-9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Interrupt Timing                               | 6-10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Register Interface, Nonmultiplexed PAD Bus     | 6-12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Register Interface, Multiplexed PAD Bus        | 6-14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| DMA Interface (Nonmultiplexed Mode Only)       | 6-16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| DMA Interface (Multiplexed Mode Only)          | 6-18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Burst Mode DMA Interface (Multiplexed Mode)    | 6-20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Burst Mode DMA Interface (Nonmultiplexed Mode) | 6-22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Initiator Asynchronous Send Timings            | 6-23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Initiator Asynchronous Receive Timings         | 6-24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Target Asynchronous Send Timings               | 6-25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Target Asynchronous Receive Timings            | 6-26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| SCSI-1 SE Transfers (5 Mbytes/s)               | 6-28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Fast SCSI-2 SE Transfers (10 Mbytes/s)         | 6-28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Register Map                                   | A-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                                | TolerANT Active Negation Technology Electrical<br>Characteristics<br>Pin Terminations<br>Clock Timing (FASTCLK Bit Cleared)<br>Clock Timing (FASTCLK Bit Set)<br>Reset Timing<br>Interrupt Timing<br>Register Interface, Nonmultiplexed PAD Bus<br>Register Interface, Multiplexed PAD Bus<br>DMA Interface (Nonmultiplexed PAD Bus<br>DMA Interface (Nonmultiplexed Mode Only)<br>DMA Interface (Multiplexed Mode Only)<br>Burst Mode DMA Interface (Multiplexed Mode)<br>Burst Mode DMA Interface (Nonmultiplexed Mode)<br>Initiator Asynchronous Send Timings<br>Initiator Asynchronous Receive Timings<br>Target Asynchronous Receive Timings<br>SCSI-1 SE Transfers (5 Mbytes/s)<br>Fast SCSI-2 SE Transfers (10 Mbytes/s) |

# Chapter 1 Introduction

This chapter is divided into the following sections:

- Section 1.1, "General Description"

- Section 1.2, "SCSI-Configured AutoMatically (SCAM) Capability"

- Section 1.3, "TolerANT<sup>®</sup> Technology"

- Section 1.4, "Features"

# **1.1 General Description**

The LSI53CF92A Fast SCSI Controller (FSC) is a high performance CMOS device designed to maximize SCSI transfer rates. This device conforms to American National Standards Institute (ANSI) standards X3.131-1986 (SCSI-1) and X3.131-199X (SCSI-2). The FSC includes the basic functionality of earlier SCSI devices, plus additional features including Fast SCSI, a 24-bit transfer counter, a part-unique ID code, and SCSI-Configured AutoMatically (SCAM) Level 1 and 2 capability.

The LSI53CF92A is a second generation SCSI controller that reduces protocol overhead by performing common SCSI sequences in hardware, in response to a single command. The LSI53CF92A operates at sustained data transfer rates up to 10 Mbytes/s in synchronous mode and 5 Mbytes/s in asynchronous mode. The LSI53CF92A has on-chip 48 mA drivers for Single-Ended (SE) transmission and is offered in a 64-pin Plastic Quad Flat Pack (PQFP) or a 64-pin Thin Quad Flat Pack (TQFP) package.

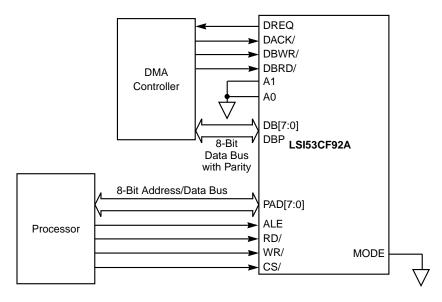

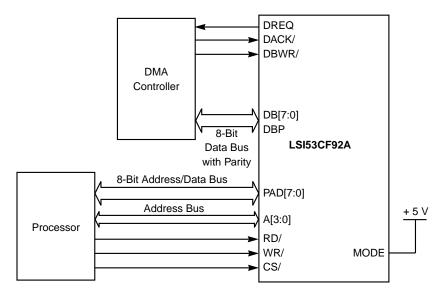

The microprocessor and DMA bus widths are eight bits. The FSC microprocessor bus can operate in either a multiplexed or nonmultiplexed mode, depending on the state of the MODE pin. See Figures 1.2 and 1.3 for more details.

# 1.2 SCSI-Configured AutoMatically (SCAM) Capability

The LSI53CF92A differs from other members of the 53Cx9x family in that SCAM capability has been incorporated into the device. SCAM requires the ability to manipulate the SCSI control and data lines individually. To provide this capability, a low-level SCSI programming mode has been added along with hardware assist for some SCAM operations. The LSI53CF92A now contains an additional register addressing mode, permitting access to two register banks, one for normal operation and one for SCAM operation. Refer to Section 2.8, "SCAM Capabilities," on page 2-17, for more information.

# **1.3 TolerANT<sup>®</sup> Technology**

The FSC features TolerANT technology, which includes active negation on the SCSI drivers and input signal filtering on the SCSI receivers. Active negation causes the SCSI REQ/, ACK/, Data, and Parity signals to be actively deasserted.

TolerANT receiver technology improves data integrity in unreliable cabling environments, where other devices would be subject to data corruption. TolerANT technology receivers filter the SCSI bus signal to eliminate unwanted transitions without the long signal delay associated with RC-type input filters. This improved driver and receiver technology helps to eliminate the double clocking of data, which is the single biggest data reliability issue with SCSI operations. The benefits of TolerANT technology include increased immunity to noise when the signal is going HIGH, increased performance due to balanced duty cycles, and improved Fast SCSI transfer rates. TolerANT technology is compatible with both the Alternative One and Alternative Two termination schemes proposed by the ANSI.

## 1.4 Features

- SCSI-2 compatible

- Ideal for target applications such as CD-ROMs

- Up to 5 Mbytes/s sustained asynchronous SCSI transfer rate

- Up to 10 Mbytes/s sustained synchronous SCSI transfer rate

- TolerANT technology provides:

- Active negation pad cells on the SCSI Data, Parity, REQ/, and ACK/ pins to improve Fast SCSI-2 performance

- Input signal conditioning on the REQ/ and ACK/ lines

- SCAM Level 1 and 2 capability

- On-chip 48 mA drivers

- Latch-up protection greater than 100 mA

- Typical 300 mV SCSI bus hysteresis

- Voltage feed-through protection

- A 24-bit transfer counter that eliminates intersector transfer delays and allows single transfers up to 16 Mbytes

- Up to 13.3 Mbytes/s DMA interface

- SCSI-2 tagged-queuing

- Single-pin, SE SCSI bus operation

- Combination commands implemented with on-chip sequential logic

- Host intervention minimized using combination commands

- Enhanced hot-plugability

- An 8-bit, split µP/DMA architecture

- Parity generation, optional checking

- Parity pass-through

- Supports clock frequencies from 10 to 40 MHz

- Low power CMOS

- Ordering Information:

- LSI53CF92A: 64-pin PQFP or TQFP

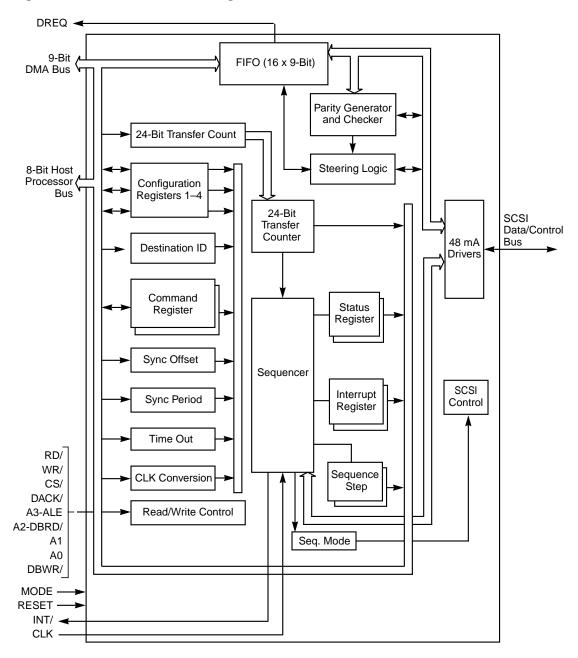

Figure 1.1 Functional Block Diagram

Figure 1.2 Bus Configuration, Multiplexed Mode (Dual Bus, 8-Bit DMA Bus and 8-Bit Multiplexed Processor Address/Data Bus)

Figure 1.3 Bus Configuration, Nonmultiplexed Mode (Dual Bus, 8-Bit DMA Bus and 8-Bit Processor Bus)

# Chapter 2 Functional Description

This chapter is divided into the following sections:

- Section 2.1, "Typical SCSI Operation"

- Section 2.2, "Bus-Initiated Sequences"

- Section 2.3, "Parity Checking and Generation"

- Section 2.4, "Host Bus Configuration"

- Section 2.5, "DMA Operation"

- Section 2.6, "SCSI Data Transfer Rates"

- Section 2.7, "Chip Reset"

- Section 2.8, "SCAM Capabilities"

The FSC has a command set that allows it to perform common SCSI sequences at hardware speed without host intervention. Its on-chip FIFO may be accessed simultaneously by the SCSI bus and either the microprocessor or the host DMA controller. All command, data, status, and message bytes pass through the FIFO on the way to or from the SCSI bus. Most FSC commands have two versions: DMA and non-DMA. When DMA instructions are used, data passes between memory and the SCSI bus with the FIFO acting as temporary storage when the DMA channel is temporarily shut down by a higher priority event, such as DRAM refresh.

The FIFO also helps speed execution during non-DMA transfers. For example, in initiator mode, the microprocessor loads the Command Descriptor Block (CDB) and optionally, one or three message bytes into the FIFO. It then issues one of several selection commands and wait for an interrupt. The FSC waits for bus free, arbitrates for the bus until it acquires it, sends the message bytes followed by the CDB, then generates an interrupt. Meanwhile, a multitasking host may continue with other tasks. The LSI53CF92A is the newest member of the LSI53C90 family, with additional features such as Fast SCSI transfer rates, single-pin SE SCSI, 8-bit DMA mode, and TolerANT Active Negation Technology.

## 2.1 Typical SCSI Operation

In target mode, the microprocessor enables selection and then waits for an interrupt. Eventually an initiator selects the FSC. It then automatically steps through the selection and command phases before generating an interrupt. When the interrupt occurs, the entire CDB is in the FIFO along with any message bytes sent by the initiator.

After the selection phase has been successfully completed, the FSC may transfer bytes in any SCSI information phase whether it is operating in initiator or target mode. The FSC supports disconnect/reselect in both initiator and target modes, making high performance multithreaded systems easy to implement.

The FSC may transfer data phase bytes across the bus synchronously, at speeds up to 10 Mbytes/s, or asynchronously, at speeds up to 5 Mbytes/s. Refer to Section 2.6, "SCSI Data Transfer Rates," on page 2-14, for more information. The difference between asynchronous and synchronous operation is transparent to the user except that the synchronous offset and the synchronous transfer period registers must be programmed prior to synchronous data transfer. The default, after hardware or software reset, is asynchronous transmission.

Data phase bytes are usually transferred using DMA. The microprocessor programs an external DMA controller, programs the FSC transfer count register, issues one of several FSC data transfer commands, then waits for an interrupt. The DMA controller and the FSC transfer all the data without microprocessor intervention.

To end the SCSI transaction, the FSC target places a status byte and a message byte in the FIFO. It then issues one of two single commands which causes the FSC first to assert Status phase, send the first byte, assert Message In phase, send the second byte, disconnect from the SCSI bus (after the initiator releases ACK/ [Acknowledge]) and interrupt the microprocessor.

The end of a SCSI transaction is similar for an FSC initiator except that it receives two bytes into its FIFO. The initiator prevents the target from disconnecting by holding ACK/ asserted on the bus while the microprocessor examines the status and message bytes. If both bytes are acceptable, the Message Accepted command instructs the FSC to release ACK/, which allows the target to disconnect and causes the initiator to interrupt its host and report the disconnect. If the status and message bytes are not acceptable, the host could first issue the Set ATN (Attention) command before issuing the Message Accepted command. This instructs the FSC to release to request Message Out phase rather than disconnect.

## 2.2 Bus-Initiated Sequences

- Selection

- Reselection

- SCSI bus reset

Selection or reselection sequences occur in the disconnected state when the FSC is selected or reselected by another initiator or target, if the Enable Selection or Reselection command has previously been received by the FSC.

In addition to responding to bus-initiated events, the FSC may initiate a bus event by using one of several selection or reselection commands. If one of these commands starts executing, the Enable Selection or Reselection command is cleared after another device has been selected, preventing the FSC from responding to a Select or Reselect command. Normally the microprocessor has 250 ms (ANSI recommended selection time-out period) after the chip disconnects from the bus to re-enable bus-initiated events. If the time-out period is exceeded, an initiator or target which is attempting to connect to the FSC may time-out and abort.

If, on the other hand, the bus-initiated event occurs before the command starts executing, the FIFO and command register is cleared and any further writes by the microprocessor are ignored until the Interrupt register is read. Because a selection or reselection command requires placing something in the FIFO, these bytes are lost, as is any command written to the Command register. The interrupt handler that services a selection or reselection command has to examine the bits in the Interrupt register

to determine if the FSC selected another device, or if it was selected by another device. The former case causes a Function Complete Interrupt, the latter case causes a Selection or Reselection interrupt.

### 2.2.1 Bus-Initiated Selection

When the FSC has been selected as a target, the following data is in its FIFO:

- Bus ID

- Identify message

- Optional two-byte command queuing message

- Command Descriptor Block (CDB)

The bus ID is always present and is always one byte. It is an unencoded version of the state of the bus during Selection phase. Any SCSI data bits that were true during Selection phase are set. The target ID must always be set. In arbitrating systems, the initiator ID must also be set. The initiator ID is optional in nonarbitrating systems. If parity checking is enabled, parity must be valid during the bus-initiated selection. If parity is not valid, the FSC does not respond to bus-initiated selection.

The identify message, if sent, is also be placed in the FIFO. The identify message is optional in SCSI-1 systems but is always one byte if it is used. In SCSI-2 systems a one or three byte message is sent, consisting of the one-byte identify message and an optional two-byte command queuing message. If the FSC is selected with ATN/ false, it stores a null byte (00) in the FIFO behind the bus ID, then begins requesting command phase bytes. A detected parity error causes the FSC to interrupt and stop, if parity checking is enabled.

If the FSC is selected with ATN/ true and the SCSI-2 bit is not set, it requests one message byte and places it in the FIFO behind the bus ID. Then it requests Command phase bytes unless the message byte is not a valid identify message, bit 7 in the Configuration 3 (Config 3) register is not set, or a parity error is detected, which causes the FSC to interrupt and stop. The Sequence Step register can then be examined to determine what events have been completed.

If the FSC is selected with ATN/ true and the SCSI-2 bit set, the FSC examines both the message byte and the ATN/ signal to determine how many bytes to request. If the first byte is a valid identify message and if ATN/ goes false after receiving the first byte, the FSC changes to Command phase. If the first byte is a valid identify message byte (0x80–0xFF) and ATN/ is still true, it requests two more message bytes. After requesting the message bytes, the FSC requests Command phase bytes unless one of the following situations occurs:

- The first byte is not a valid identify message

- A parity error is detected

- ATN/ goes false between the second and third bytes

- ATN/ remains true but the SCSI-2 bit is false.

All of these conditions cause the FSC to interrupt and stop.

To determine if one of these conditions has occurred, examine the Sequence Step register.

The CDB always begins at the third or fifth byte in the FIFO, assuming selection completed normally. The CDB may be 6, 10 or 12 bytes long. Thus, in SCSI-2, the entire FIFO may be filled if a tagged-queuing, 12-byte command is used.

#### 2.2.2 Bus-Initiated Reselection

The FSC allows itself to be reselected as an initiator by a target if it has previously received the Enable Selection/Reselection command. If the sequence completes normally, the FIFO has the following information:

- Bus ID

- Identify message

The bus ID is always present and is always one byte. It is an unencoded version of the state of the bus during Reselection phase.

The identify message is always present and is always one byte.

The FSC prevents the target from disconnecting by holding ACK/ asserted on the bus while the microprocessor examines the Bus ID and Identify message bytes. The Message Accept command causes the FSC to release ACK/. Any further message bytes can be received with the Transfer Information command.

Note: The settings of the SCSI-2 or Queue Tag Enable bits do not affect this operation.

#### 2.2.3 Bus-Initiated Reset

A SCSI bus-initiated reset is recognized by the FSC at any time. When SCSI RST/ pulses true, the FSC disconnects from the bus and resets its internal sequencer. If bit 6 in Configuration 1 (Config 1) register is not set, the FSC generates a SCSI reset-detected interrupt.

#### 2.2.4 Stacked Commands

The Command register is a two-deep, eight-bit read/write register that gives commands to the FSC. If DMA commands are to be stacked, the Transfer Count must be loaded prior to loading the respective command. Command stacking should only be used during Data In and Data Out. If stacked commands are used in Initiator mode, it is recommended that the Features Enable bit in the Configuration 2 (Config 2) register be set. This causes the SCSI phase lines to be latched at the end of a command.

## 2.3 Parity Checking and Generation

The FSC has three bits that control parity generation and checking. These three bits can be accessed by the user and are described in Table 2.1. If parity checking is disabled, the FSC does not check for parity errors. In this document, the word detected in conjunction with parity error should be understood to imply that parity checking has previously been enabled.

In Target role, detected parity errors set the Parity Error bit (bit 5 in the Status register) and clear the Command register without causing an interrupt. In Initiator role, detected parity errors set the Parity Error bit and, if receiving SCSI bytes, assert ATN/ (Attention) prior to releasing

ACK/ (Acknowledge). Parity errors occurring after a phase change to Synchronous Data In are handled differently in Initiator mode. Refer to Chapter 5, "Command Set," for more information on initiator commands.

| Control Bit                                              | Data Direction | Bit Set                                                           | Bit Not Set                                                                  |

|----------------------------------------------------------|----------------|-------------------------------------------------------------------|------------------------------------------------------------------------------|

| Parity Checking,<br>Configuration 1<br>(Config 1), bit 4 | SCSI to FIFO   | Enable parity checking and error reporting. SDP loaded into FIFO. | Disable parity checking<br>and error reporting.<br>Parity generator to FIFO. |

| Test parity,<br>Configuration 1                          | FIFO to SCSI   | SDP is a replica of SD7.                                          | FIFO to SDP.                                                                 |

| (Config 1), bit 5                                        | FIFO to memory | DBP is a replica of DB7.                                          | FIFO to DBP.                                                                 |

| DMA parity,<br>Configuration 2                           | DACK/ to FIFO  | DBP to FIFO.                                                      | Parity generator to FIFO.                                                    |

| (Config 2), bit 0                                        | FIFO to SCSI   | Enable parity checking and error reporting.                       | Disable parity checking and error reporting.                                 |

Configuration 2 (Config 2) register bit 2, the Target Bad Parity Abort bit, allows special handling for parity errors. When this bit is set, the chip aborts a Receive command or Receive Data command if bad parity is received from the SCSI bus. If a parity error occurs when the Target Bad Parity Abort bit is set, the Status register Parity Error bit (bit 5) is set, but no additional bits are set in the Interrupt or Status registers after bad parity is detected. The Transfer Counter and FIFO Flags registers contain a record of how many bytes were transferred before the command was aborted.

For additional information on the parity bits, refer to Chapter 4, "Registers."

The LSI53CF92A has one parity pin (DBP). In both the Multiplexed Bus Configuration mode and in the Nonmultiplexed Bus Configuration mode, the processor connects to the FIFO on an 8-bit bus only. In both of these modes, the internal parity generator creates parity to send to the SCSI bus.

When the DBP pin is enabled, parity may pass between the SCSI and host DMA bus without change or may be generated by the FSC from the data byte. Whether generated internally or externally, the parity bit is always loaded into the FIFO along with the data byte. From there on, it moves through the FIFO along with the data byte. The FIFO may be accessed by three buses: SCSI bus, microprocessor bus, or host DMA bus. If parity test mode is enabled during a DMA transfer, DBP is a duplicate of DB7. This is true both for data flowing from the FIFO to the SCSI Data Bus (SDB) pins or data flowing from the FIFO to the Host Data Bus (DB) pins.

The FSC flags parity errors as data comes into the FIFO from the SCSI bus, or as it leaves the FIFO on its way out to the SCSI bus.

## 2.4 Host Bus Configuration

The DMA and microprocessor buses may be configured in one of the two following ways.

### 2.4.1 Mode Description

Multiplexed Dual bus; 8-bit DMA bus and 8-bit multiplexed processor address/data bus.

Nonmultiplexed Dual bus; 8-bit DMA bus and 8-bit nonmultiplexed processor bus.

The operating mode is selected by the Mode strapping pin; refer to Chapter 3, "Signal Descriptions," for the setting of either mode. The two operating modes are labeled Multiplexed mode and Nonmultiplexed mode. Refer to Chapter 1, "Introduction," Figure 1.2, and Figure 1.3 for configuration diagrams. Both of these dual bus modes have separate data buses for DMA and microprocessor, which may be active simultaneously provided CS/ is not accessing the FIFO.

### 2.4.2 Multiplexed Bus Configuration Mode

In this dual-bus mode, 8-bit operations are supported by the DMA Data bus. The microprocessor interface is supported by the PAD bus. FIFO parity is not available for data transfers over the PAD bus. The direction of transfer is determined by the RD/ and WR/ lines. CS/ must be active during PAD bus accesses.

In the Multiplexed Bus Configuration mode, register addresses and register data are multiplexed on the PAD bus. The register address on the PAD[3:0] lines is latched into the chip on the HIGH to LOW transition of ALE (A3).

In this bus configuration mode, the Data bus configuration is for 8-bit DMA transfers. Pin A2 functions as the Data bus read signal (DBRD/), which drives the DMA read data. A1 and A0 must be tied to ground.

## 2.4.3 Nonmultiplexed Bus Configuration Mode

Like the Multiplexed Bus Configuration mode, this dual bus mode is configured for 8-bit transfers.

In this dual bus mode interface, DMA operations are supported by the DB bus, and the microprocessor interface is supported by the PAD bus. FIFO parity is not available for data transfers over the PAD bus. The direction of transfer is determined by the RD/ and WR/ lines. CS/ must be active during PAD bus accesses.

In the Nonmultiplexed Bus Configuration mode, transfers occur on the microprocessor interface over the PAD bus, which operates as a nonmultiplexed data only bus. The register address is carried by the A[3:0] lines and is latched into the chip on the HIGH to LOW transition of CS/.

# 2.5 DMA Operation

The FSC supports 8-bit DMA transfers. The on-chip FIFO allows the FSC to support normal and burst mode transfers. The DMA interface protocol runs asynchronous to the chip clock. The DMA Request signal (DREQ) is asserted when the DMA is ready for a transfer to or from the DMA channel. DREQ is asserted only when the DMA Acknowledge signal (DACK/) is inactive, and is released on the leading edge of DACK/. DREQ remains asserted until the chip receives as many DACK/s as it needs or can handle.

## 2.5.1 DMA Threshold

The threshold is the number of bytes in the FIFO that trigger DREQ. For DMA read, DREQ is asserted when the FIFO contains at least the threshold number of bytes. For DMA write, the FIFO must be able to accept this number of bytes. For 8-bit DMA operation the normal threshold is one byte.

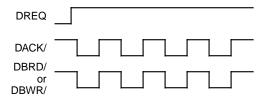

### 2.5.2 Normal DMA Mode

In normal operation, DREQ remains true until the FIFO empties or fills, depending on the direction of the transfer. Figure 2.1 illustrates the case where the threshold is always exceeded. This is typical of a DMA interface that is slower than the SCSI device to which the system is connected.

Normal DMA mode tends to monopolize the DMA bus, and slows the entire system down to the performance level of the SCSI device to which the chip is connected. In single-threaded systems, however, this remains the most efficient method of transferring data as long as important events, like DRAM refresh, can interrupt the DMA transfer.

## 2.5.3 Threshold Eight Mode

Threshold Eight mode causes the FSC to wait until eight bytes or more can be transferred before it requests service from the external DMA controller. Because the DMA bus can operate at speeds five to ten times greater than typical SCSI devices, this mode allows SCSI operations to run effectively in parallel with other processes.

The Threshold Eight bit in Configuration 3 (Config 3) register changes the threshold to eight bytes. Refer to the description for the Configuration 3 (Config 3) register in Chapter 4, "Registers." Threshold Eight mode is enabled by setting bit 0 in the Configuration 3 (Config 3) register and is valid in both bus configurations. Threshold Eight mode operates only during SCSI Data In or Data Out phase.

<u>Note:</u> When enabling this mode, the synchronous data offset can only be set to seven or less.

Threshold Eight mode causes DREQ to remain false until the FIFO can accommodate an eight-byte transfer. This improves DMA bus efficiency by keeping the chip off this bus until it can transfer at least eight bytes. With Threshold Eight enabled, the chip retains control of the DMA channel as long as one transfer can be accommodated. The transfer continues in normal mode whenever the Transfer Counter drops below eight bytes and the threshold drops to one transfer. The following conditions must be true for a DMA Threshold Eight transfer to occur:

- Threshold Eight mode is enabled.

- Transfer Counter indicates eight or more bytes.

- The FIFO can accommodate an 8-byte transfer as follows:

- The FIFO contains at least eight bytes of data to transfer to memory, or

- At least the top eight bytes of the FIFO are empty to receive the eight-byte transfer from memory.

Because the Threshold Eight mode is enabled during DMA burst mode, the DMA burst is limited to eight transfers. This feature forces the chip to periodically relinquish control of the DMA channel, allowing other devices to gain access to the bus to perform such operations as memory refresh.

### 2.5.4 DMA Burst Mode

Burst mode, or Alternate DMA mode, is a special mode devised to maximize data throughput using most DMA controllers. DMA burst mode is enabled by setting both the Threshold Eight and the Alternate DMA mode bits in the Configuration 3 (Config 3) register. Threshold Eight causes the FSC to delay assertion of DREQ until it can transfer eight bytes. Alternate DMA mode causes the FSC to deassert DREQ after the byte transfers, causing the DMA controller to relinquish the bus.

This regular surrendering of the DMA channel has benefits for two common DMA interface problems. For DMA controllers that do not recognize higher priority requests until the current device finishes, the FSC can periodically force DMA arbitration. This allows DRAM refresh and other operations to occur during SCSI operations. For DMA controllers that are much faster than the SCSI host or peripheral to which the system is connected, bus efficiency is improved by ensuring that the FSC has data to transfer while the DMA controller is controlling the bus.

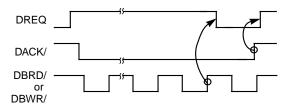

DMA Burst mode can be enabled in both bus configurations. DMA Burst mode affects the deassertion of DREQ and assertion of DACK/ for DMA reads and writes.

In the Multiplexed Bus Configuration mode, the FSC is designed to operate with a DMA controller that has timings similar to an 8237. Because many systems use one of the 8237 channels for DRAM refresh and because the 8237 does not recognize a higher priority request until it finishes its current transfer, Burst mode gives the best transfer rate without sacrificing memory integrity.

#### 2.5.4.1 Deassertion of DREQ

The FSC remains in Burst mode as long as more than eight bytes remain to be transferred. However, if the Transfer Counter drops below eight, then the FSC switches out of Burst mode for the last one to seven bytes. The last bytes are transferred in Normal DMA mode where DREQ goes true and stays true as long as the FIFO is able to transfer data; DACK/ cycles true then false for each transfer. Because DACK/ must cycle true then false for every DMA transfer in this mode, Normal mode is sometimes referred to as Single Transfer mode.

- Single Transfer Mode: DREQ goes true and stays true as long as the FIFO is able to transfer data. DACK/ cycles true then false for every transfer.

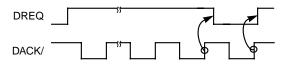

- Multiple DMA Transfers per DREQ: In the Multiplexed Bus Configuration mode, DREQ is deasserted after the trailing edge of DBWR/ or DBRD/. DACK/ remains asserted throughout multiple transfers. In the Nonmultiplexed Bus Configuration mode, DREQ is deasserted after the trailing edge of DACK/ of the next-to-last DMA transfer. In the Nonmultiplexed Bus Configuration mode, DACK/ toggles for each DMA read cycle.

#### 2.5.4.2 DMA Read

When DMA Burst mode is enabled, the method by which DMA read data is transferred to the system bus depends on the bus configuration mode. The DMA read data is enabled onto the DB bus by DACK/ and either the RD/ or DBRD/ input signal, as follows.

- Multiplexed Bus Configuration Mode: Data is enabled when both DBRD/ and DACK/ are true. For multiple DMA transfers, DACK/ remains asserted throughout the multiple transfers and DBRD/ toggles for each transfer.

- Nonmultiplexed Bus Configuration Mode: Data is enabled when DACK/ is true. DACK/ toggles for each DMA transfer.

#### 2.5.4.3 DMA Write

In DMA Burst mode, the functionality of DACK/ and DBWR/ is unchanged for single DMA transfers per DREQ. For multiple DMA transfers per DREQ, DACK/ remains asserted throughout the multiple transfers and DBWR/ toggles for each transfer.

Figure 2.2 illustrates the DMA Burst mode, Multiplexed mode and Nonmultiplexed mode writes.

# Figure 2.2 DMA Burst Mode (Multiplexed Mode and Nonmultiplexed Mode Writes)

Figure 2.3 illustrates the DMA Burst mode, Nonmultiplexed mode reads.

#### Figure 2.3 DMA Burst Mode (Nonmultiplexed Mode Reads)

### 2.5.5 Single-Pin, SE SCSI

The LSI53CF92A improves fast, SE SCSI performance by reducing capacitance of the SCSI input and output signals. Single pin SCSI provides the best performance for fast, SE SCSI, and reduces signal attenuation at SCSI-1 transfer rates.

# 2.6 SCSI Data Transfer Rates

Performance numbers for the FSC are based on SE connection to the SCSI bus with no external transceivers.

## 2.6.1 Asynchronous Operation

The asynchronous transmission rate varies with cable length and the CLK period. The FSC can reach sustained transfer rates of 5 Mbytes/s on short (1 foot) cables using typical devices operating at or near nominal voltage and temperature. The typical transfer rate on a 6-meter cable is 4 Mbytes/s using two typical FSCs talking to each other. The worst case asynchronous transmission rate, over voltage, temperature, and process variations is 3 Mbytes/s on a maximum length (6 meters), SE cable and 4 Mbytes/s on a 1-foot cable.

The asynchronous transmission rate is only slightly affected by the CLK frequency when sending data. The FSC drives the data bus for a minimum of one CLK period (plus any additional time required to meet the ANSI required 55 ns setup time) before asserting REQ/ or ACK/. The CLK frequency does not affect the asynchronous transfer rate when receiving data. When the Enable Active Negation bit is set, Configuration 4 (Config 4) bit 2, the LSI53CF92A can transfer data asynchronously at up to 5 Mbytes/s.

#### 2.6.2 Synchronous Operation

The synchronous data transmission period is equal to the CLK input frequency multiplied by the encoded value in the Synchronous Transfer Period register. Sustained synchronous transfer rates of 10 Mbytes/s are attainable across the commercial voltage and temperature range.

The LSI53CF92A can transfer synchronous SCSI data in both initiator and target modes at transfer rates up to 10 Mbytes/s, using an input clock frequency of 40 MHz. The SCSI-1 and Fast SCSI-2 minimum timing requirements are in Table 2.2.

| Mode           | Setup | Hold   | Assert/Negate |

|----------------|-------|--------|---------------|

| SCSI-1         | 55 ns | 100 ns | 90 ns         |

| SE Fast SCSI-2 | 25 ns | 35 ns  | 30 ns         |

Table 2.2 Minimum Timing Requirements

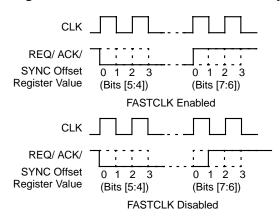

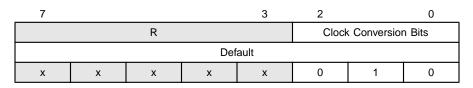

To support maximum Fast SCSI transfer rates and SCSI-1 transfer requirements, the FASTSCSI (bit 4) and FASTCLK (bit 3) bits have been added to the Configuration 3 (Config 3) register. They modify the SCSI state machine to provide fast and normal synchronous timings depending upon the clock frequency. A full description of the operations of these bits and the required clock frequencies are provided in the Configuration 3 (Config 3) register description in Chapter 4, "Registers."

During synchronous SCSI transfers, the assertion and deassertion of the REQ/ and ACK/ signals is programmable using the FASTCLK bit and other bits in the Synchronous Offset register. The input clock duty cycle affects the half clock assertion/deassertion delays. For more information, see the Synchronous Offset register description in Chapter 4, "Registers."

# 2.7 Chip Reset

The FSC has the following three levels of reset:

- Hard

- Soft

- Disconnect

## 2.7.1 Hard Reset

A hard reset is executed, when using the Reset Chip command, or when the RESET pin is asserted by external hardware. It stops all chip operations, resets all functions in the chip, and returns the chip to a disconnected state. The Reset Chip command remains at the top of the Command register FIFO, which locks the chip and all registers in a reset state until a NOP command is issued. At power up, the RESET pin must be asserted as V<sub>DD</sub> first becomes stable.

## 2.7.2 Soft Reset

A soft reset is applied when the SCSI Bus reset condition is received through the RST/ pin, or when the Reset SCSI Bus command is issued, which asserts the RST/ pin. This condition resets the following subset of the functions reset by the hard reset:

- Resets DMA interface

- Resets bus-initiated selection/reselection module

- Resets command sequence module

- Resets Sequence Step and clears Sequencer Mode bits (Enable Select/Reselect = 0, Target = 0, Initiator = 0)

- Initializes Command register FIFO to empty

- Releases all SCSI signals except RST/

- Resets disconnect, initiator, and target command modules

The Reset SCSI Bus command causes the RST/ signal to be asserted. See Chapter 5, "Command Set," for further description of this command.

A SCSI Bus reset may occur in any mode. The RST/ signal is asserted by another SCSI device on the bus, and returns the chip to a disconnected state. The chip generates a SCSI Reset interrupt to the microprocessor if the interrupt is not disabled by bit 6 of the Configuration 1 (Config 1) register. If the SCSI bus reset is still active when the microprocessor clears the interrupt, a new interrupt is generated. This new interrupt must be serviced.

The Reset SCSI Bus command asserts the SCSI RST/ pin for approximately 25  $\mu$ s and returns the chip to disconnected status. A SCSI reset interrupt is generated if the interrupt is not disabled by Bit 6 of the Configuration 1 (Config 1) register.

## 2.7.3 Disconnect Reset

The disconnect reset is caused by various circumstances that result in the chip becoming disconnected from the SCSI bus, as follows:

- The Target Mode Disconnect, Disconnect Sequence, or Terminate Sequence command is issued to the chip.

- The chip is in initiator mode and the SCSI bus changes to the bus free state.

- The Select or Reselect command terminates with a selection time-out.

A disconnect reset resets the following subset of the functions reset by the Soft Reset:

- Sequencer Mode bits are cleared (target = 0 and initiator = 0).

- Initializes Command register FIFO to empty.

- Releases all SCSI signals except RST/.

- Resets disconnect, initiator, and target command modules.

# 2.8 SCAM Capabilities

This section defines how SCAM functionality is accommodated within the LSI53CF92A SCSI protocol chip. The SCAM terminology and functionality presented within this section is consistent with definitions provided within the SCAM specification X3T9.2/93-109r5. The SCAM additions to the LSI53CF92A allow the chip to be a Level 1 or Level 2 SCAM Master or Slave device.

To provide SCAM functionality, SCSI interface chips must be able to control individual SCSI control and data lines and be able to disable active negation of signals. The LSI53CF92A uses hardware sequencers to control all SCSI interface activity. The general strategy for SCAM implementation in the LSI53CF92A is to provide a low-level SCSI programming mode along with hardware support for some of the SCAM operations.

## 2.8.1 SCSI Low-Level Programming

The LSI53CF92A design provides SCAM capability with a generic low-level SCSI programming mode. Low-level access to the SCSI bus is controlled by the Low Level bit, SCSI Control (SCONTROL) register, bit 0. When the Low Level bit is set, all SCSI bus sequences are performed using software control. Arbitration may be performed purely in software or by using the ARB bit, SCSI Control (SCONTROL) register, bit 1. See Section 2.8.2, "SCAM Operations,", for details. During low-level operation, no relational restrictions exist between SCSI signals; data bits may be driven without respect to the I/O control line, and there is no distinction between target/initiator signals.

## 2.8.2 SCAM Operations

The following categories describe the different SCAM operations:

- Section 2.8.2.1, "Arbitration With or Without an ID"

- Section 2.8.2.2, "SCAM Selection"

- Section 2.8.2.3, "Response to SCAM Selection"

- Section 2.8.2.4, "Response to Normal Selection"

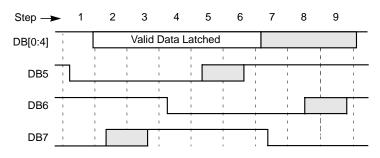

- Section 2.8.2.5, "SCAM Protocol and Transfer Cycles"

- Section 2.8.2.6, "Limitations"

#### 2.8.2.1 Arbitration With or Without an ID

Arbitration with or without an ID is possible through low-level control by utilizing the SCSI Output Data Latch and the ARB bit, SCSI Control (SCONTROL) register, bit 1. During arbitration, the contents of the SCSI Output Data Latch (SODL) are asserted onto the SCSI bus in a direct bit-mapped fashion. During arbitration, legal values for the SCSI Output Data Latch (SODL) are {0x01, 0x02, 0x04, 0x08, 0x10, 0x20, 0x40, 0x80}. Arbitration without an ID is accomplished by setting the SODL to {0x00} prior to the start of arbitration. The following steps should be performed by software to arbitrate for the SCSI bus in low-level mode:

- Step 1. Set the Low Level bit in the SCSI Control register.

- Step 2. Write bit-mapped ID (normal arbitration) or 00 (no ID) to the SCSI Output Data Latch (SODL) register.

- Step 3. Set the ARB bit.

- Step 4. Wait for the ARB1 status bit (normal arbitration) or the ARB4 status bit (SCAM, no ID).

Examine the bus (read SCSI Bus Data Lines (SBDL))

IF (any device with higher ID is present) then another device has won arbitration turn off ARB and Low Level goto Step 1 ELSE arbitration has been won assert BSY, SEL using SOCL register turn off ARB bit ENDIF

<u>Note:</u> If another device wins arbitration and asserts SEL/, the FSC deasserts BSY/ and rearbitrates the next time a bus free condition is detected. The FSC continues arbitrating until either it wins (ARB1, ARB4 set and no higher IDs on the bus) or until the ARB bit is reset.

#### 2.8.2.2 SCAM Selection

After arbitration is complete as described in Section 2.8.2.1, BSY/ and SEL/ are asserted on the bus. The following steps should be performed by software to generate a SCAM selection:

- Step 1. Assert MSG/ using the SCSI Output Control Latch (SOCL) register.

- Step 2. Delay at least two de-skew delays, then release BSY/ using the SCSI Output Control Latch (SOCL) register.

- Step 3. Maintain SEL/ and MSG/ asserted with BSY/ released for a minimum of a SCAM selection response time, then release MSG/.

- <u>Note:</u> The SCAM specification provides for two distinctly different SCAM selection response times; the long SCAM selection response time (250 ms), and the short SCAM selection response time (1 ms). Many Level 2 SCAM systems can accommodate the 1 ms SCAM selection response time.

- Step 4. Wait until MSG/ has been released by all other devices (examine the SCSI Bus Control Lines (SBCL) register), using wired-OR glitch filtering in software.

- Step 5. Assert BSY/ using the SCSI Output Data Latch (SODL) register.

- Step 6. Wait two de-skew delays.

- Step 7. Assert SEL/ and I/O while maintaining BSY/ asserted. At this time, if the device is a SCAM master, C/D should also be asserted.

- Step 8. Assert DB6 and DB7 by first writing them in the SCSI Output Data Latch (SODL) register, then enabling their drivers with bit 2 of the SCSI Control (SCONTROL) register.

- Step 9. Wait two de-skew delays.

- Step 10. Release SEL/ and wait until SEL/ has been deasserted, using wired-OR glitch filtering in software.

- Step 11. Release DB6 and examine the SCSI bus signals. If C/D is not asserted, then there are no SCAM master devices participating, and the slave devices release all signals. If C/D is asserted, wait for DB6 to be released by all devices, using wired-OR glitch filtering, then assert SEL/. This completes initiation of the SCAM selection protocol.

#### 2.8.2.3 Response to SCAM Selection

When response to SCAM selection is enabled (ENSS bit set in the SCSI Control (SCONTROL) register), the FSC monitors the SCSI bus for SCAM selection attempts (SEL/ and MSG/ asserted when BSY/ released). Upon detection of a SCAM selection, the FSC responds by asserting SEL/ and MSG/, and then interrupting the processor. A SCAM selection interrupt is indicated when both bits 1 and 0 of the Interrupt register are set (normally mutually exclusive events). Following a SCAM selection interrupt, software must enter the low-level programming mode and participate in the SCAM protocol. The following minimal steps must be taken by software in preparation for and response to the SCAM selection interrupt:

- Step 1. In the SCSI Control (SCONTROL) set the ENSS (bit 3) and Low Level (bit 0).

- Step 2. Wait for SCAM Selection Interrupt.

- Step 3. In the SCSI Output Control Latch (SOCL) set MSG (bit 2).

- Step 4. In the SCSI Control (SCONTROL) register reset ENSS (bit 3).

- Step 5. Release MSG/.

- Step 6. Wait until MSG/ has been released by all other devices (examine the SCSI Bus Control Lines (SBCL) register), using wired-OR glitch filtering in software.