# TECHNICAL MANUAL

# LSISAS1068 PCI-X to 8-Port Serial Attached SCSI/SATA Controller

October 2005 Version 2.1

DB14-000287-04

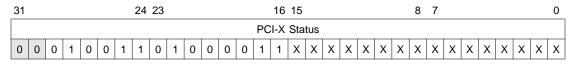

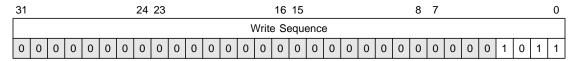

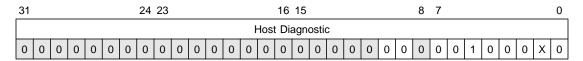

This document contains proprietary information of LSI Logic Corporation. The information contained herein is not to be used by or disclosed to third parties without the express written permission of an officer of LSI Logic Corporation.

LSI Logic products are not intended for use in life-support appliances, devices, or systems. Use of any LSI Logic product in such applications without written consent of the appropriate LSI Logic officer is prohibited.

Purchase of  $I^2C$  components of LSI Logic Corporation, or one of its sublicensed Associated Companies, conveys a license under the Philips  $I^2C$  Patent Rights to use these components in an  $I^2C$  system, provided that the system conforms to the  $I^2C$  standard Specification as defined by Philips.

Document DB14-000287-04, Version 2.1 (October 2005) This document describes LSI Logic Corporation's LSISAS1068 Serial Attached SCSI/SATA Controller and will remain the official reference source for all revisions/releases of this product until rescinded by an update.

LSI Logic Corporation reserves the right to make changes to any products herein at any time without notice. LSI Logic does not assume any responsibility or liability arising out of the application or use of any product described herein, except as expressly agreed to in writing by LSI Logic; nor does the purchase or use of a product from LSI Logic convey a license under any patent rights, copyrights, trademark rights, or any other of the intellectual property rights of LSI Logic or third parties.

Copyright © 2004, 2005 by LSI Logic Corporation. All rights reserved.

#### TRADEMARK ACKNOWLEDGMENT

LSI Logic, the LSI Logic logo design, Fusion-MPT, Gflx, GigaBlaze, Integrated Mirroring, Integrated RAID, and Integrated Striping are trademarks or registered trademarks of LSI Logic Corporation. ARM, ARM966E-S, and Multi-ICE are registered trademarks of ARM Ltd., used under license. CompactPCI is a registered trademark of the PCI Industrial Computer Manufacturers Group. PCI-X is a registered trademark of PCI SIG. All other brand and product names may be trademarks of their respective companies.

JM

To receive product literature, visit us at http://www.lsilogic.com.

For a current list of our distributors, sales offices, and design resource centers, view our web page located at

http://www.lsilogic.com/contacts/index.html

# Preface

This book is the primary reference and technical manual for the LSISAS1068 PCI-X to 8-Port Serial Attached SCSI/SATA Controller. It contains a complete functional description for the LSISAS1068, as well as the physical and electrical specifications for the LSISAS1068.

### Audience

This document assumes that you are familiar with microprocessors and related support devices. The people who benefit from this book are:

- Engineers and managers who are evaluating the LSISAS1068 for use in a system

- Engineers who are designing the LSISAS1068 into a system

#### Organization

This document has the following chapters and appendixes:

- Chapter 1, Introduction, provides an overview of the LSISAS1068 features and capabilities.

- Chapter 2, Functional Description, provides a detailed functional description of the LSISAS1068 operation. This chapter describes the LSISAS1068 implementations of the PCI, PCI-X, and SAS specifications.

- Chapter 3, Signal Description, provides a detailed signal description for the LSISAS1068.

- Chapter 4, PCI Host Register Description, provides a bit level description of the host interface registers.

- Chapter 5, **Specifications**, provides the electrical and physical specifications for the LSISAS1068.

- Appendix A, Register Summary, provides a register map for the LSISAS1068.

- Appendix B, Reference Specifications, lists several specifications that may benefit the reader.

#### **Related Publications**

#### **LSI Logic Documents**

Fusion-MPT<sup>™</sup> Device Management User's Guide, Version 2.0, DB15-000186-02

#### LSI Logic World Wide Web Home Page

www.lsilogic.com

### ANSI

11 West 42nd Street New York, NY 10036 (212) 642-4900

InterNational Committee on Information Technology Standards (INCITS) T10 Technical Committee http://www.t10.org

#### **Global Engineering Documents**

15 Inverness Way East Englewood, CO 80112 (800) 854-7179 or (303) 397-7956 (outside U.S.) FAX (303) 397-2740

#### **PCI Special Interest Group**

2575 N. E. Katherine Hillsboro, OR 97214 (800) 433-5177; (503) 693-6232 (International); FAX (503) 693-8344

#### Serial ATA Working Group

http://www.serialata.org Email: info@serialata.org

## Philips I<sup>2</sup>C Bus Specification

http://www.semiconductors.philips.com

#### SFF-8485 Serial GPIO Bus Specification

http://www.sffcommittee.org

## **Conventions Used in This Manual**

The word *assert* means to drive a signal true or active. The word *deassert* means to drive a signal false or inactive. Signals that are active LOW end with a "/."

Hexadecimal numbers are indicated by the prefix "0x" —for example, 0x32CF. Binary numbers are indicated by the prefix "0b" —for example, 0b0011.0010.1100.1111.

## **Revision History**

| Revision            | Date    | Remarks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|---------------------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Advance Version 0.2 | 7/2004  | Initial release of document.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Advance Version 0.3 | 7/2004  | Pin AC6 changed in Figure 5.4.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Version 1.0         | 1/2005  | Preliminary Release. Modified text regarding IM and IS drive sup-<br>port (page 1-4); identified throughout the Manual that the<br>LSISAS1068 PCI interface is not tolerant of 5V PCI; corrected<br>typo on page 3-2 regarding 636 Ball Grid Array; changed accu-<br>racy requirement for Reference Clock signal to +/- 50ppm (Table<br>3.9); corrected typo in Mode Select bus description (Table 3.13)<br>to "0b000000"; corrected two typos in value of Subsystem ID reg-<br>ister to 0x9000 (pages 4-13 and 4-14); added statement "The<br>LSISAS1068 sets this register to 0x0A" to Maximum Latency<br>register description (page 4-17); updated Write I/O Key descrip-<br>tion (page 4-34) to include an additional write of "0x00FF" at<br>beginning of sequence; updated Operating Conditions (Table 5-2);<br>provided GigaBlaze <sup>®</sup> characteristics (Tables 5.3 to 5.5); provided<br>External Memory Timing Diagrams (Section 5.3). Various addi-<br>tional editorial changes throughout document. |

| Version 2.0         | 2/2005  | Final Release. Added references to Philips I <sup>2</sup> C and SFF-8485<br>Serial GPIO bus specifications on page iv. Clarified support for<br>SAS and SATA features in Section 1.1. Changed description of<br>MAD[29] in Table 3.16 to "Reserved". Changed ESD specification<br>in Table 5.2 from TBD to 2000 V.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Version 2.1         | 10/2005 | Final Release. Updated the External Memory Timing Diagrams<br>and clarified NC vs. Reserved pins. Also removed references to<br>Serial EEPROM as this device does not support it.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                     |         | Updated the ACTIVE_LED[3:0]/ and FAULT_LED[3:0]/ pinouts.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

# Contents

| Chapter 1 | Introduction           |         |                                   |      |  |

|-----------|------------------------|---------|-----------------------------------|------|--|

|           | 1.1                    | Genera  | al Description                    | 1-1  |  |

|           | 1.2                    |         | s of SAS                          | 1-5  |  |

|           | 1.3                    | Benefit | s of the Fusion-MPT Architecture  | 1-5  |  |

|           | 1.4                    | Benefit | s of PCI-X                        | 1-6  |  |

|           | 1.5                    | Benefit | s of GigaBlaze Transceivers       | 1-7  |  |

|           | 1.6                    | Summa   | ary of LSISAS1068 Features        | 1-8  |  |

|           |                        | 1.6.1   | SAS Features                      | 1-8  |  |

|           |                        | 1.6.2   | SATA Features                     | 1-8  |  |

|           |                        | 1.6.3   | PCI Performance                   | 1-9  |  |

|           |                        | 1.6.4   | Integration                       | 1-10 |  |

|           |                        | 1.6.5   | Usability                         | 1-10 |  |

|           |                        | 1.6.6   | Flexibility                       | 1-10 |  |

|           |                        | 1.6.7   | Reliability                       | 1-11 |  |

|           |                        | 1.6.8   | Testability                       | 1-11 |  |

| Chapter 2 | Functional Description |         |                                   |      |  |

| -         | 2.1                    | Block I | Diagram Description               | 2-2  |  |

|           |                        | 2.1.1   | Host Interface Module Description | 2-4  |  |

|           |                        | 2.1.2   | Quad Port                         | 2-6  |  |

|           |                        | 2.1.3   | Context RAM                       | 2-8  |  |

|           | 2.2                    | Fusion  | -MPT Architecture Overview        | 2-8  |  |

|           | 2.3                    | PCI Fu  | inctional Description             | 2-9  |  |

|           |                        | 2.3.1   | PCI Addressing                    | 2-9  |  |

|           |                        | 2.3.2   | PCI Commands and Functions        | 2-11 |  |

|           |                        | 2.3.3   | PCI Arbitration                   | 2-16 |  |

|           |                        | 2.3.4   | PCI Cache Mode                    | 2-16 |  |

|           |                        | 2.3.5   | PCI Interrupts                    | 2-16 |  |

|           |                        | 2.3.6   | Power Management                  | 2-17 |  |

|           | 2.4                           | SAS Function             | al Description                          | 2-17 |  |

|-----------|-------------------------------|--------------------------|-----------------------------------------|------|--|

|           | 2.5                           | External Mem             | nory Interface                          | 2-20 |  |

|           |                               | 2.5.1 Men                | nory Requirements                       | 2-20 |  |

|           |                               | 2.5.2 Flas               | h ROM Controller                        | 2-21 |  |

|           |                               | 2.5.3 NVS                | SRAM Controller                         | 2-23 |  |

|           | 2.6                           | Zero Channel             | RAID                                    | 2-24 |  |

|           | 2.7                           | Universal Asy            | nchronous Receiver/Transmitter (UART)   | 2-25 |  |

|           | 2.8                           | Multi-ICE Tes            | t Interface                             | 2-26 |  |

| Chapter 3 | Signal Description            |                          |                                         |      |  |

|           | 3.1                           | Signal Organi            | zation                                  | 3-1  |  |

|           | 3.2                           | PCI Signals              |                                         | 3-4  |  |

|           |                               | 3.2.1 PCI                | System Signals                          | 3-4  |  |

|           |                               | 3.2.2 PCI                | Address and Data Signals                | 3-4  |  |

|           |                               | 3.2.3 PCI                | Interface Control Signals               | 3-5  |  |

|           |                               | 3.2.4 PCI                | Arbitration Signals                     | 3-5  |  |

|           |                               | 3.2.5 PCI                | Error Reporting Signals                 | 3-5  |  |

|           |                               | 3.2.6 PCI                | Interrupt Signals                       | 3-6  |  |

|           | 3.3                           | PCI-Related S            | Signals                                 | 3-6  |  |

|           | 3.4                           | CompactPCI               | Signals                                 | 3-7  |  |

|           | 3.5                           | SAS Signals              |                                         | 3-7  |  |

|           | 3.6                           | Memory Inter             | face Signals                            | 3-8  |  |

|           | 3.7                           | Communicatio             | on Signals                              | 3-9  |  |

|           | 3.8                           | SIO Signals              |                                         | 3-10 |  |

|           | 3.9                           | Configuration            | and General Purpose Signals             | 3-11 |  |

|           | 3.10                          | JTAG and Tes             | st Signals                              | 3-12 |  |

|           | 3.11                          | Power Signal             | 3                                       | 3-13 |  |

|           | 3.12                          | Power-On Se              | nse Pins Description                    | 3-15 |  |

|           | 3.13                          | Internal Pull-L          | Jps and Pull-Downs                      | 3-18 |  |

| Chapter 4 | PCI Host Register Description |                          |                                         |      |  |

|           | 4.1                           | PCI Configura            | ation Space Register Description        | 4-1  |  |

|           | 4.2                           | PCI I/O Spac             | e and Memory Space Register Description | 4-31 |  |

| Chapter 5 | Specifications                |                          |                                         |      |  |

|           | 5.1                           | 5.1 DC Characteristics 5 |                                         |      |  |

|           | 5.2                           | AC Character             | istics                                  | 5-9  |  |

|           |                               |                          |                                         |      |  |

|            | <ul><li>5.3 External Memory Timing Diagrams</li><li>5.4 Pinout</li><li>5.5 Package Drawings</li></ul> | 5-11<br>5-14<br>5-21 |  |  |

|------------|-------------------------------------------------------------------------------------------------------|----------------------|--|--|

| Appendix A | Register Summary                                                                                      |                      |  |  |

| Appendix B | Reference Specifications                                                                              |                      |  |  |

|            | Index                                                                                                 |                      |  |  |

|            | Customer Feedback                                                                                     |                      |  |  |

## Figures

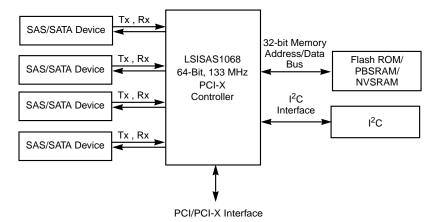

| 1.1 | LSISAS1068 Direct-Connect Example Application         | 1-3  |

|-----|-------------------------------------------------------|------|

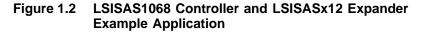

| 1.2 | LSISAS1068 Controller and LSISASx12 Expander          |      |

|     | Example Application                                   | 1-3  |

| 2.1 | LSISAS1068 Controller Block Diagram                   | 2-3  |

| 2.2 | Transceivers within a Phy                             | 2-18 |

| 2.3 | Narrow and Wide Links                                 | 2-19 |

| 2.4 | SSP, STP, and SMP Protocol Usage                      | 2-20 |

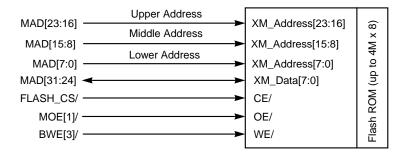

| 2.5 | Flash ROM Block Diagram                               | 2-22 |

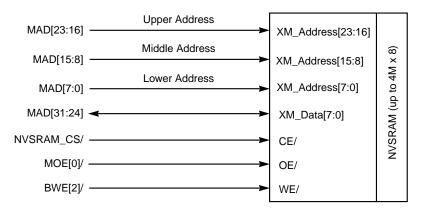

| 2.6 | NVSRAM Block Diagram                                  | 2-24 |

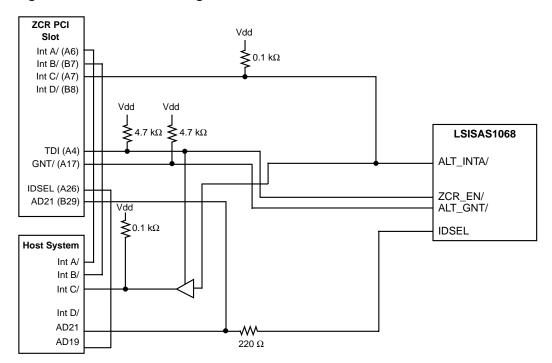

| 2.7 | ZCR Circuit Diagram for the LSISAS1068                | 2-25 |

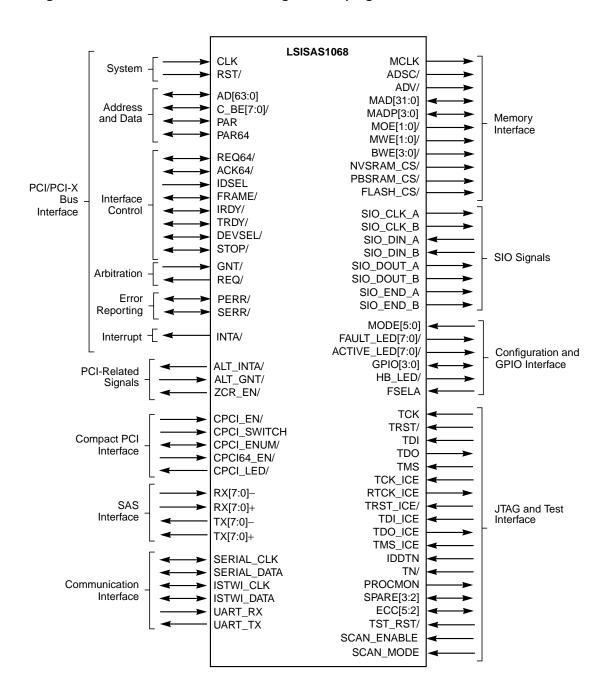

| 3.1 | LSISAS1068 Functional Signal Grouping                 | 3-3  |

| 5.1 | External Clock                                        | 5-9  |

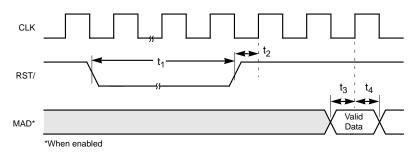

| 5.2 | Reset Input                                           | 5-10 |

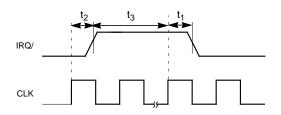

| 5.3 | Interrupt Output                                      | 5-10 |

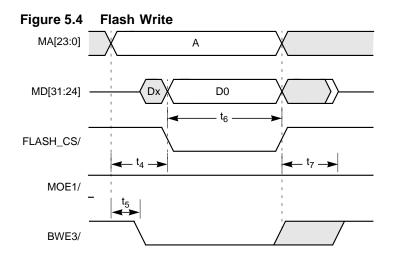

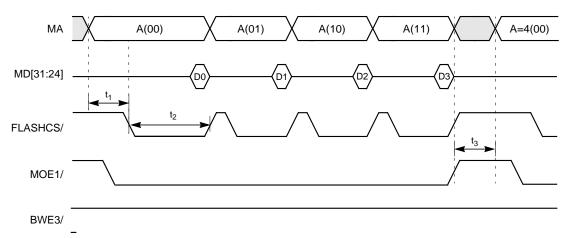

| 5.4 | Flash Write                                           | 5-11 |

| 5.5 | Flash Read                                            | 5-12 |

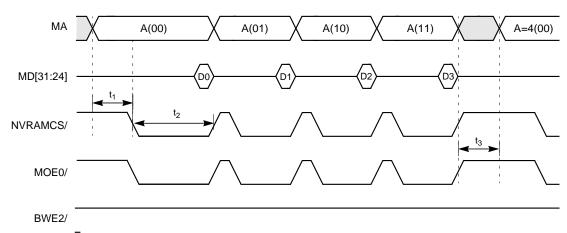

| 5.6 | NV Read                                               | 5-12 |

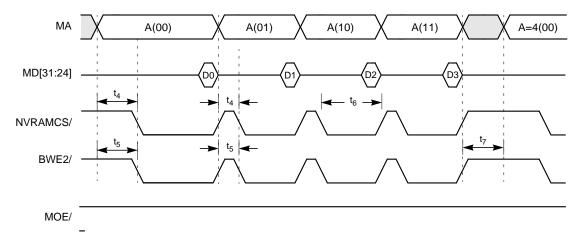

| 5.7 | NV Write                                              | 5-13 |

| 5.8 | LSISAS1068 636 EPBGA-T Diagram (Top View)             | 5-20 |

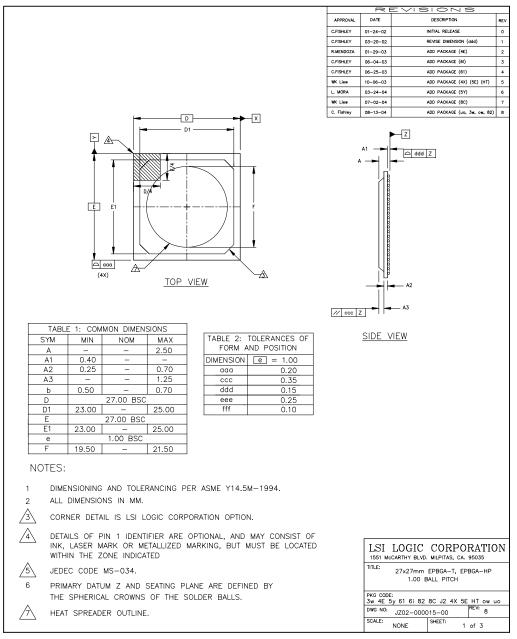

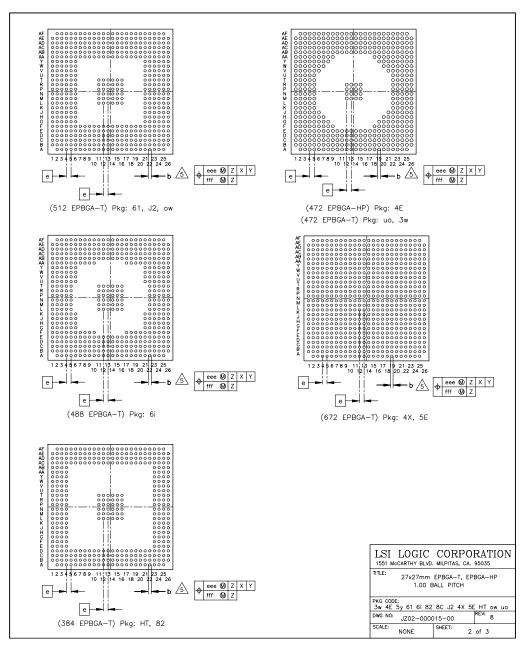

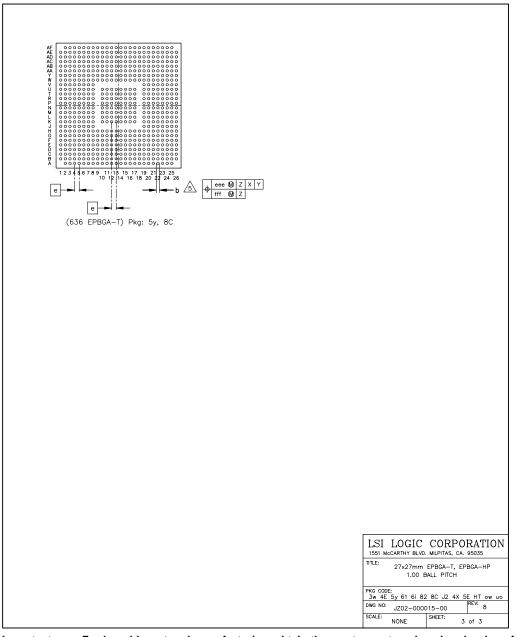

| 5.9 | JZ02-000015-00 (5Y) Mechanical Drawing (Sheet 1 of 3) | 5-22 |

## Tables

| 2.1  | PCI/PCI-X Bus Commands and Encodings                     | 2-11 |

|------|----------------------------------------------------------|------|

| 2.2  | Flash ROM Signature Value                                | 2-23 |

| 2.3  | ARM Multi-ICE Header Pinout                              | 2-26 |

| 3.1  | PCI System Signals                                       | 3-4  |

| 3.2  | PCI Address and Data Signals                             | 3-4  |

| 3.3  | PCI Interface Control Signals                            | 3-5  |

| 3.4  | PCI Arbitration Signals                                  | 3-5  |

| 3.5  | PCI Error Reporting Signals                              | 3-5  |

| 3.6  | PCI Interrupt Signals                                    | 3-6  |

| 3.7  | PCI-Related Signals                                      | 3-6  |

| 3.8  | CompactPCI Signals                                       | 3-7  |

| 3.9  | SAS Interface Signals                                    | 3-7  |

| 3.10 | Memory Interface Signals                                 | 3-8  |

| 3.11 | UART and I <sup>2</sup> C Signals                        | 3-9  |

| 3.12 | SIO Signals                                              | 3-10 |

| 3.13 | Configuration and General Purpose Signals                | 3-11 |

| 3.14 | Test and JTAG Signals                                    | 3-12 |

| 3.15 | Power and Ground Signals                                 | 3-13 |

| 3.16 | Power-On Sense Pin Definitions                           | 3-16 |

| 3.17 | Pull-Up and Pull-Down Conditions                         | 3-18 |

| 4.1  | LSISAS1068 PCI Configuration Space Address Map           | 4-2  |

| 4.2  | Multiple Message Enable Field Bit Encoding               | 4-21 |

| 4.3  | BIR Field Definitions                                    | 4-25 |

| 4.4  | Maximum Outstanding Split Transactions                   | 4-27 |

| 4.5  | Maximum Memory Read Count                                | 4-28 |

| 4.6  | PCI I/O Space Address Map                                | 4-31 |

| 4.7  | PCI Memory [0] Address Map                               | 4-32 |

| 4.8  | PCI Memory [1] Address Map                               | 4-32 |

| 4.9  | Interrupt Signal Routing                                 | 4-38 |

| 5.1  | Absolute Maximum Stress Ratings                          | 5-2  |

| 5.2  | Operating Conditions                                     | 5-2  |

| 5.3  | GigaBlaze Transmitter Voltage Characteristics—TX[7:0]    | 5-3  |

| 5.4  | GigaBlaze Receiver Voltage Characteristics—RX[7:0]       | 5-3  |

| 5.5  | GigaBlaze Transceiver Rise/Fall Characteristics—TX[7:0], |      |

|      | RX[7:0]                                                  | 5-3  |

| 5.6  | PCI-X Input Signals—CLK, RST/, GNT/, IDSEL,              |      |

|      | ALT GNT/, CPCI64 EN/                                     | 5-4  |

| 5.7  | PCI-X Output Signals—REQ/, INTA/, ALT_INTA/       | 5-4  |

|------|---------------------------------------------------|------|

| 5.8  | PCI-X Bidirectional Signals—AD[63:0], C_BE[7:0]/, |      |

|      | CPCI_ENUM/, PAR, PAR64, ACK64/, REQ64/, FRAME/,   |      |

|      | IRDY/, TRDY/, DEVSEL/, STOP/, PERR/, SERR/        | 5-4  |

| 5.9  | Inputs—ZCR_EN/, CPCI_EN/, TN/, UART_RX            | 5-4  |

| 5.10 | Inputs—CPCI_SWITCH, MODE[5:0], SCAN_ENABLE,       |      |

|      | SCAN_MODE, FSEL_A                                 | 5-5  |

| 5.11 | Schmitt Trigger Inputs—TST_RST/, TCK, TRST/, TDI, |      |

|      | TMS, TCK_ICE, TRST_ICE/, TDI_ICE, TMS_ICE         | 5-5  |

| 5.12 | Schmitt Trigger Inputs—REFCLK_B, SIO_DIN_A,       |      |

|      | SIO_DIN_B                                         | 5-5  |

| 5.13 | 10 mA, 3-State Outputs—CPCI_LED/, HB_LED/         | 5-5  |

| 5.14 | 5 mA, 3-State Outputs—TDO, TDO_ICE, RTCK_ICE,     |      |

|      | SIO_CLK_A, SIO_CLK_B, SIO_DOUT_A, SIO_DOUT_B,     |      |

|      | SIO_END_A, SIO_END_B                              | 5-6  |

| 5.15 | 8 mA Outputs—MCLK, ADSC/, ADV/, BWE[3:0]/,        |      |

|      | MWE[1:0]/, MOE[1:0]/, PBSRAM_CS/, FLASH_CS/,      |      |

|      | NVSRAM_CS/                                        | 5-6  |

| 5.16 | 5 mA Outputs—UART_TX                              | 5-6  |

| 5.17 | 4 mA Outputs—PROCMON                              | 5-6  |

| 5.18 | 8 mA Bidirectional Signals—MAD[31:0]              | 5-7  |

| 5.19 | 8 mA Bidirectional Signals—MADP[3:0]              | 5-7  |

| 5.20 | 5 mA Bidirectional Signals—SERIAL_CLK,            |      |

|      | SERIAL_DATA, ISTWI_CLK, ISTWI_DATA, GPIO[3:0],    |      |

|      | FAULT_LED[7:0]/, ACTIVE_LED[7:0]/                 | 5-7  |

| 5.21 | PECL Buffer Signals—REFCLK_P, REFCLK_N            | 5-8  |

| 5.22 | Capacitance                                       | 5-8  |

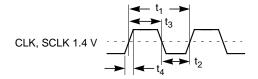

| 5.23 | External Clock                                    | 5-9  |

| 5.24 | Reset Input                                       | 5-10 |

| 5.25 | Interrupt Output                                  | 5-10 |

| 5.26 | Flash Write Timing Parameters                     | 5-11 |

| 5.27 | Flash Read Timing Parameters                      | 5-11 |

| 5.28 | NVRAM Read Timing Parameters                      | 5-12 |

| 5.29 | NVRAM Write Timing Parameters                     | 5-13 |

| 5.30 | Listing by Signal Name                            | 5-14 |

| 5.31 | Listing by Pin Number                             | 5-17 |

| A.1  | LSISAS1068 PCI Configuration Space Registers      | A-1  |

| A.2  | LSISAS1068 PCI I/O Space Registers                | A-3  |

| A.3  | LSISAS1068 PCI Memory [0] Space Registers         | A-4  |

| B.1  | Reference Specifications                          | B-1  |

# Chapter 1 Introduction

The LSISAS1068 is an eight-port, 3.0 Gbit/s SAS/SATA controller that is compliant with the Fusion-MPT<sup>TM</sup> architecture, provides a PCI-X interface, and supports the Integrated RAID<sup>TM</sup> solution. This chapter contains the following sections:

- Section 1.1, "General Description"

- Section 1.2, "Benefits of SAS"

- Section 1.3, "Benefits of the Fusion-MPT Architecture"

- Section 1.4, "Benefits of PCI-X"

- Section 1.5, "Benefits of GigaBlaze Transceivers"

- Section 1.6, "Summary of LSISAS1068 Features"

# 1.1 General Description

The LSISAS1068 controller brings 3.0 Gbit/s Serial Attached SCSI (SAS) performance to host adapter, workstation, and server designs, making it easy to add a SAS interface to any PCI or PCI-X<sup>1</sup> system. The LSISAS1068 integrates eight high-performance SAS/SATA phys and a 64-bit, 133 MHz PCI-X bus master DMA core. Each of the eight phys on the LSISAS1068 is capable of 3.0 Gbit/s and 1.5 Gbit/s SAS link rates, and 3.0 Gbit/s and 1.5 Gbit/s SATA link rates. The LSISAS1068 supports the SAS protocol as described in the Serial Attached SCSI Standard, version 1.0, as well as SAS 1.1 features, such as support for the BROADCAST (SES) primitive and support for SATA protocol defined by the

<sup>1.</sup> In some instances, this manual references PCI-X explicitly. References to the PCI bus may be inclusive of both the PCI specification and PCI-X addendum, or may only refer to the PCI bus depending on the operating mode of the device.

Serial ATA specification, version 1.0a. SATA II is an extension to SATA 1.0a. LSI Logic SAS/SATA controllers also support the following SATA II features:

- 3 Gbit/s SATA

- Staggered spin-up

- Hot Plug

- Native Command Queuing

- Activity and fault indicators per phy

- Port Selector (for dual-port drives)

Supporting both the SAS and SATA interfaces, the LSISAS1068 is a versatile controller that provides the backbone of both server and highend workstation environments. LSI Logic produces the LSISAS1068 using the Gflx<sup>™</sup> process technology.

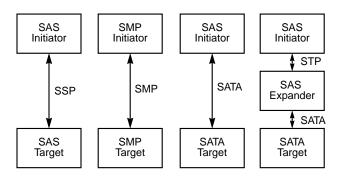

Each port on the LSISAS1068 supports SAS and SATA devices using the SAS Serial SCSI Protocol (SSP), Serial Management Protocol (SMP), Serial Tunneling Protocol (STP), and SATA. The SSP protocol enables communication with other SAS devices. SATA enables the LSISAS1068 to communicate with other SATA devices. The SMP protocol communicates topology management information directly with an attached SAS expander device, such as the LSISAS1068 to communicate with a SATA device through an attached expander.

The LSISAS1068 supports a 133 MHz, 64-bit PCI-X bus. With the exception that the PCI interface is not tolerant of 5 V PCI, the interface is backward compatible with previous revisions of the PCI/PCI-X bus. The LSISAS1068 supports PCI-X split completion cycles and 32-bit or 64-bit data bursts with variable burst length. The LSISAS1068 supports the PCI-X Addendum to the Peripheral Components Interface Specification, Revision 2.0, and the Peripheral Components Interface Specification, Revision 3.0.

Figure 1.1 shows a direct-connect configuration. Figure 1.2 provides an example of the LSISAS1068 configured with an LSISASx12 expander.

Figure 1.1 LSISAS1068 Direct-Connect Example Application

The LSISAS1068 employs an ARM966 processor to meet the data transfer flexibility requirements of the host interface PCI-X specifications.

The LSISAS1068 is based on the Fusion-MPT (Message Passing Technology) architecture, which features a performance based message passing protocol that off loads the host CPU by completely managing all I/Os and minimizes system bus overhead by coalescing interrupts. The Fusion-MPT architecture requires only a thin, easy to develop device drivers that is independent of the I/O bus. LSI Logic provides these device drivers.

The LSISAS1068 supports a 32-bit external memory bus. The external memory controller block provides an interface for flash ROM, NVSRAM, and PBSRAM devices. Most configurations use a flash ROM to store firmware, configuration information, and persistent data information.

The LSISAS1068 supports the Integrated RAID solution, which is a highly integrated, low cost RAID implementation. It is designed for systems requiring redundancy and high availability, but not needing a full-featured RAID implementation. The Integrated RAID solution includes Integrated Mirroring<sup>™</sup> (IM) technology and Integrated Striping<sup>™</sup> (IS) technology. IM provides physical mirroring of two physical drives. IM requires an NVSRAM to support write journaling. IS enables data striping across up to eight physical drives. The Integrated RAID solution is OS independent, easy to install and configure, supports up to eight drives at RAID Level 0, and does not require a special driver. The runtime operation of the Integrated RAID solution is transparent to the operating system. A single firmware build supports all Integrated RAID capabilities. The LSISAS1068 also provides Zero Channel RAID (ZCR) support.

The IR firmware requires a configuration mechanism, which enables configuration of the mirroring attributes during initial setup or reconfiguration after hardware failures or changes in the system environment. Use the LSI Logic BIOS Configuration Utility or the IM DOS Configuration Utility to configure the IR firmware attributes. Host based status software monitors the state of the mirrored drives and reports error conditions as they arise.

# 1.2 Benefits of SAS

SAS is a serial, point-to-point, enterprise-level device interface that leverages the proven SCSI protocol set. SAS is a convergence of the advantages of SATA, SCSI, and FC, and is the future mainstay of the enterprise and high-end workstation storage markets. SAS offers a higher bandwidth per pin than parallel SCSI, and improves signal and data integrity.

The SAS interface uses the proven SCSI command set to ensure reliable data transfers, while providing the connectivity and flexibility of point-topoint serial data transfers. The serial transmission of SCSI commands eliminates clock skew challenges. The SAS interface provides improved performance, simplified cabling, smaller connectors, lower pin count, and lower power requirements when compared to parallel SCSI.

SAS controllers leverage a common electrical and physical connection interface that is compatible with Serial ATA technology. The SAS and SATA protocols use a thin, 7-wire connector instead of the 68-wire SCSI cable or 26-wire ATA cable. The SAS/SATA connector and cable are easier to manipulate, allow connections to smaller devices, and do not inhibit airflow. The point-to-point SATA architecture eliminates inherent difficulties created by the legacy ATA master-slave architecture, while maintaining compatibility with existing ATA firmware.

The LSISAS1068 can function as an SSP initiator, an SSP target, an SMP initiator, an STP initiator, or a SATA initiator. The LSISAS1068 uses SSP to communicate with other SAS devices, and uses SMP to communicate topology management information with other SAS devices. STP communicates with SATA devices by tunneling through SAS expanders directly to the SATA device or by using the SATA protocol to communicate directly with the SATA device.

# **1.3 Benefits of the Fusion-MPT Architecture**

The Fusion-MPT architecture provides an open architecture that is ideal for SAS, SATA, SCSI, Fibre Channel, and other emerging interfaces. The I/O interface is interchangeable at the system and application level; embedded software uses the same device interface for different bus implementations, just as application software uses the same storage management interfaces for different bus implementations. LSI Logic provides Fusion-MPT device drivers that are binary compatible between SAS, SATA, Fibre Channel, and Ultra320 SCSI interfaces.

The Fusion-MPT architecture improves overall system performance by requiring only a thin device driver, which off loads the intensive work of managing I/Os from the system processor to the LSISAS1068. The use of thin, easy to develop, common OS device drivers accelerates time to market by reducing device driver development and certification times.

The Fusion-MPT architecture provides an interrupt coalescing feature. Interrupt coalescing allows an I/O controller to send multiple reply messages in a single interrupt to the host processor. Sending multiple reply messages per interrupt reduces context switching of the host processor and maximizes the host processor efficiency, which results in a significant improvement of system performance. To use the interrupt coalescing feature, the host processor must be able to accept and manage multiple replies per interrupt.

The Fusion-MPT architecture also provides built-in device driver stability since the device driver need not change for each revision of the LSISAS1068 silicon or firmware. This architecture is a reliable, constant interface between the host device driver and the LSISAS1068. Changes within the LSISAS1068 are transparent to the host device driver, operating system, and user. The Fusion-MPT architecture also saves the user significant development and maintenance effort since it is not necessary to alter or redevelop the device driver when a revision of the LSISAS1068 device or firmware occurs.

# 1.4 Benefits of PCI-X

PCI-X doubles the maximum clock frequency of the conventional PCI bus. The *PCI-X Addendum to the PCI Local Bus Specification, Revision 2.0*, defines enhancements to the proven *PCI Local Bus Specification, Revision 3.0.* PCI-X provides more efficient data transfers by enabling registered inputs and outputs, improves buffer management by including transaction information with each data transfer, and reduces bus overhead by restricting the use of wait states and disconnects. PCI-X

also reduces host processor overhead by providing a wide range of error recovery implementations.

The LSISAS1068 supports up to a 133 MHz, 64-bit PCI-X bus and is backwards compatible with previous versions of the PCI/PCI-X specification. Per the PCI-X addendum, the LSISAS1068 includes transaction information with all PCI-X transactions to enable more efficient buffer management schemes. Each PCI-X transaction contains a transaction sequence identifier (Tag), the identity of the initiator, and the number of bytes in the sequence. The LSISAS1068 clocks PCI-X data directly into and out of registers, which creates a more efficient data path. The LSISAS1068 increases bus efficiency since it does not insert wait states after the initial data phase when acting as a PCI-X target and never inserts wait states when acting as a PCI-X initiator.

# 1.5 Benefits of GigaBlaze Transceivers

The GigaBlaze transceivers provide the physical layer for the LSISAS1068 controller and are a proven component of LSI Logic semiconductor expertise. The Gflx GigaBlaze transceivers are the fifth generation of the LSI Logic GigaBlaze core. The GigaBlaze transceivers provide full-duplex, point-to-point communications channels that can operate at 3.0/1.5 Gbit/s SAS/SATA transfer rates.

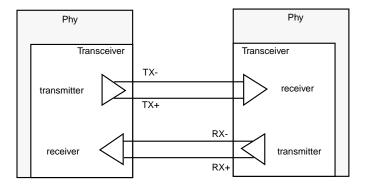

The integrated GigaBlaze transceivers perform the 8b/10b conversion that is necessary for SAS and SATA transfers, without burdening either the LSISAS1068 ARM<sup>®</sup> processor or the host interface. The transmitter accepts parallel data, serializes it, and transmits it on the differential TX+/TX- signals. The receiver recovers the clock and deserializes the data from the bitstream that it receives on the RX+/RX- signals. Because the transceiver and receiver operate independently, the GigaBlaze transceivers can send and receive data simultaneously, which maximizes system performance. The GigaBlaze transceivers also provide integrated internal termination.

# 1.6 Summary of LSISAS1068 Features

This section provides a summary of the LSISAS1068 features and benefits. It contains information on SAS Features, SATA Features, PCI Performance, Integration, Usability, Flexibility, Reliability, and Testability.

## 1.6.1 SAS Features

This section describes the SAS features.

- Provides 8 fully independent phys

- Each phy supports 3.0 Gbit/s and 1.5 Gbit/s SAS data transfers

- Supports SSP to enable communication with other SAS devices

- Supports SMP to communicate topology management information

- Provides a serial, point-to-point, enterprise-level storage interface

- Simplifies cabling between devices

- Provides a scalable interface that supports up to 128 devices through multiple expanders

- Supports wide ports consisting of 2, 3, or 4 phys within a single quad port

- Supports narrow ports consisting of a single phy

- Transfers data using SCSI information units

## 1.6.2 SATA Features

This section describes the SATA features.

- Supports SATA data transfers of 3.0 Gbits/s and 1.5 Gbits/s

- Supports STP data transfers of 3.0 Gbits/s and 1.5 Gbits/s

- Provides a serial, point-to-point storage interface

- Simplifies cabling between devices

- Eliminates the Master-Slave construction used in parallel ATA

- Allows addressing of multiple SATA targets through an expander

- Allows multiple initiators to address a single target (in a fail-over configuration) through an expander

## 1.6.3 PCI Performance

This section describes the PCI features:

- 133 MHz, 64-bit PCI/PCI-X interface that:

- Operates up to 133 MHz PCI-X

- Operates at 33 MHz or 66 MHz PCI

- Supports 32-bit or 64-bit data transfers

- Supports 32-bit or 64-bit addressing through Dual Address Cycles (DAC)

- Provides a theoretical 1066 Mbyte/s PCI bandwidth

- Supports 3.3 V PCI, and is not 5 V PCI tolerant

- Complies with the PCI Local Bus Specification, Revision 3.0

- Complies with the PCI-X Addendum to the PCI Local Bus Specification, Revision 2.0

- Complies with the PCI Power Management Interface Specification, Revision 1.2

- Complies with the PC2001 Specification

- Provides unequaled performance through the Fusion-MPT architecture

- Provides high throughput and low CPU utilization to off load the host processor

- Uses a dedicated ARM966 processor

- Presents a single electrical load to the PCI Bus

- Reduces Interrupt Service Routine (ISR) overhead with interrupt coalescing

- Supports Message Signaled Interrupts (MSI) and MSI-X

- Supports 32-bit or 64-bit data bursts with variable burst lengths

- Supports the PCI Cache Line Size register

- Supports the PCI Memory Write and Invalidate, Memory Read Line, and Memory Read Multiple commands

- Supports the PCI-X Memory Read Dword, Split Completion, Memory Read Block, Memory Write Block commands

• Supports a maximum of 16 outstanding Split Transactions

## 1.6.4 Integration

These features make the LSISAS1068 easy to integrate:

- Supports backwards compatibility with previous revisions of the PCI specification, with the exception that the LSISAS1068 does not support 5 V PCI

- Provides a full 32-bit or 64-bit PCI-X DMA bus master

- Reduces time to market with the Fusion-MPT architecture

- Single driver binary for SAS/SATA, SCSI, and Fibre Channel products

- One firmware build supports all Integrated RAID capabilities

- Thin, easy to develop drivers

- Reduced integration and certification effort

## 1.6.5 Usability

This section describes the usability features.

- Simplifies cabling with point-to-point, serial architecture

- Smaller, thinner cables do not restrict airflow

- Provides drive spin-up sequencing control

- Provides up to two LED signals for each phy to indicate link activity and faults

- Provides an Inter-IC (I<sup>2</sup>C) interface for enclosure management

## 1.6.6 Flexibility

These features increase the flexibility of the LSISAS1068.

- Supports a flash ROM interface, a nonvolatile RAM (NVSRAM) interface, and a pipelined synchronous burst SRAM (PBSRAM) interface

- Offers a flexible programming interface to tune I/O performance

- Allows mixed connections to SAS or SATA targets

- Leverages compatible connectors for SAS and SATA connections

- Allows grouping of up to 4 phys within a single quad port to form a wide port

- Allows programming of the World Wide Name

## 1.6.7 Reliability

These features enhance the reliability of the LSISAS1068.

- Uses proven GigaBlaze transceivers

- Provides ESD protection

- Provides latch-up protection

- Has a high proportion of power and ground pins

- Integrated RAID solution provides Integrated Mirroring technology and Integrated Striping technology

- Supports Zero Channel RAID

## 1.6.8 Testability

These features enhance the testability of the LSISAS1068.

- Offers JTAG boundary scan

- Provides a UART interface for debugging

- Offers ARM Multi-ICE<sup>®</sup> technology for debugging the ARM966 processor

# Chapter 2 Functional Description

This chapter provides a subsystem level overview of the LSISAS1068, a discussion of the Fusion-MPT architecture, and a functional description of the LSISAS1068 interfaces. This chapter contains the following sections:

- Section 2.1, "Block Diagram Description"

- Section 2.2, "Fusion-MPT Architecture Overview"

- Section 2.3, "PCI Functional Description"

- Section 2.4, "SAS Functional Description"

- Section 2.5, "External Memory Interface"

- Section 2.6, "Zero Channel RAID"

- Section 2.7, "Universal Asynchronous Receiver/Transmitter (UART)"

- Section 2.8, "Multi-ICE Test Interface"

The LSISAS1068 is an eight-port, 3.0 Gbit/s SAS controller that is compliant with the Fusion-MPT architecture, provides a PCI-X interface, and supports the Integrated RAID solution. The LSISAS1068 supports revision 3.0 of the *PCI Local Bus Specification*, revision 2.0 of the *PCI-X Addendum to the PCI Local Bus Specification*, revision 1.0 of the ANSI *Serial Attached SCSI* standard, and revision 1.0a of the *Serial ATA* standard.

The LSISAS1068 employs the LSI Logic Fusion-MPT architecture to ensure robust system performance, to provide binary compatibility of host software between the LSI Logic SAS/SATA, SCSI, and Fibre Channel products, and to significantly reduce software development time. Refer to the *Fusion-MPT Device Management User's Guide* for more information on the Fusion-MPT architecture.

# 2.1 Block Diagram Description

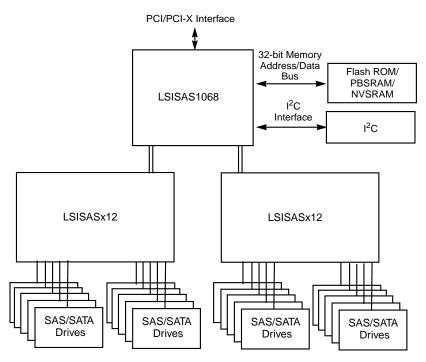

The LSISAS1068 consists of three major modules and a context RAM. The three major modules are the host interface module and the two Quad Port modules. The modules consist of the following components:

- Host Interface Module

- PCI/PCI-X Interface

- System Interface

- IOP (ARM966 processor)

- PCI Timer and Configuration

- Timer and Configuration

- DMA Arbiter

- External Memory Interface

- l<sup>2</sup>C

- SIO A and SIO B

- UART

- Quad Port Modules

- Queue Manager

- SATA Engine

- Four Transport Modules

- Port Layer Connection Management and Switch

- Four SAS Links and four SAS phys

- Context RAM

Figure 2.1 illustrates the relationship between these modules. The following sections describe each submodule.

Figure 2.1 LSISAS1068 Controller Block Diagram

## 2.1.1 Host Interface Module Description

The host interface module provides an interface between the host driver and the Quad Port modules. The host interface module controls system DMA transfers and the host side of the LSI Logic Fusion-MPT architecture. The host interface module contains the PCI/PCI-X interface, system interface, PCI timer and configuration, DMA arbiter, IOP, I<sup>2</sup>C, TimerConfig, UART, SIO, and external memory blocks. This section provides a detailed explanation of the host interface submodules.

## 2.1.1.1 PCI/PCI-X Interface

The LSISAS1068 provides a PCI-X interface that supports up to a 64-bit, 133 MHz PCI-X bus. The interface is backward compatible with previous implementations of the PCI specification, with the exception that the LSISAS1068 does not support 5 V PCI. For more information on the PCI interface, refer to Section 2.3, "PCI Functional Description".

## 2.1.1.2 System Interface

In combination with the IOP, the system interface supports the Fusion-MPT architecture. The system interface efficiently passes messages between the LSISAS1068 and the host using a high-performance, packetized mailbox architecture. The LSISAS1068 system interface coalesces PCI interrupts to minimize traffic on the PCI bus and maximize system performance. The system interface contains five hardware FIFOs for the message queuing lists: Request Free FIFO, Request Post FIFO, Reply Free FIFO, Reply Post FIFO, and High Priority Request FIFO. The LSISAS1068 contains control logic for the FIFOs, while the messages are stored in the context RAM or in external memory.

All host accesses to the IOP, external memory, and timer and configuration subsystems pass through the system interface and use the primary bus. The host system initiates data transactions on the primary bus with the system interface registers. PCI Memory Space [0] and the PCI I/O Base Address registers identify the location of the system interface register set. Chapter 4, "PCI Host Register Description", provides a bit level description of the system interface register set.

## 2.1.1.3 IOP

The LSISAS1068 I/O processor controls the system interface and manages the host side of the Fusion-MPT architecture without host processor intervention, which frees the host processor for other tasks. The LSISAS1068 I/O processor (IOP) is a 32-bit ARM966 RISC processor that provides instruction and data requests to streamline operations and increase performance.

## 2.1.1.4 PCI Timer and Configuration

This PCI Timer and Configuration module supports the PCI configuration register space, an industry-standard and a power-on reset (POR).

## 2.1.1.5 Timer and Configuration

This block supports the LSISAS1068 LED and GPIO interfaces. There are a total of 17 LED signals on the LSISAS1068. Each of the eight phys has an LED signal to indicate activity on the link and an LED signal to indicate an error on the link. The GPIO interface contains four independent GPIO signals. This block provides a firmware heartbeat LED. All LED signals (except the HB\_LED/ signal) can also be configured as GPIO signals. This block also supports internal timing adjustments and power-on sense configuration options.

## 2.1.1.6 DMA Arbiter

The LSISAS1068 provides the ability to transfer system memory blocks to and from local memory through the descriptor-based DMA arbiter and router.

## 2.1.1.7 External Memory

The external memory controller block provides an interface for flash ROM, NVSRAM, and PBSRAM devices. The external memory bus provides a 32-bit memory bus, parity checking, and chip select signals for PBSRAM, NVSRAM, and flash ROM.

Typical system configurations require a flash ROM to store firmware, configuration information, and persistent data information.

## 2.1.1.8 Inter-IC (I<sup>2</sup>C) Interface

The LSISAS1068 contains an Inter-IC (I<sup>2</sup>C) interface that communicates with peripherals. This interface is also referred to as an industry standard 2-wire interface (ISTWI). The I<sup>2</sup>C block operates as either a master or a slave on the bus and sustains data rates up to 400 Kbits/s. The I<sup>2</sup>C block accomplishes byte-wise bidirectional data transfers by using either an interrupt or a polling handshake at the completion of each byte. The style and operation of this interface closely follows the defacto standard for a two-wire serial interface chip. The I<sup>2</sup>C block controls all bus timing and performs bus-specific sequences.

## 2.1.1.9 SIO A and SIO B Interface

The SIO interface enables the user to control LED pattern generation, device information, and general purpose data. There is one SIO module for each Quad Port module. SIO A controls of the LEDs in Quad Port Module 0. SIO B controls the LEDs in Quad Port Module 1.

The SIO\_DOUT signals transmit output data and SIO\_IN signals receive data. The SIO module generates a pulse on the SIO\_END signal when transmitting the last valid data bit. The SIO interface is compliant to the SFF-8485 Serial GPIO (SGPIO) Bus specification.

## 2.1.1.10 UART

The UART provides test and debug access to the LSISAS1068.

## 2.1.2 Quad Port

The Quad Port modules in the LSISAS1068 implement the SSP, SMP, and STP/SATA protocols, and manage the eight SAS/SATA phys. Each Quad Port module supports four SAS/SATA phys. The following subsections describe the Quad Port modules. Refer to Section 2.4, "SAS Functional Description," for an operational description of the LSISAS1068 SAS ports.

## 2.1.2.1 Transport Module

The transport modules transmit frames to and from the port layer and implement the STP, SSP, and SMP protocols. Each Quad Port module

contains four instances of the transport module, one for each SAS/SATA phy on the LSISAS1068.

## 2.1.2.2 Queue Manager

The queue manager is responsible for managing various queue structures that support the SSP, SMP, and STP protocols. The queue structures are the primary means for the IOP to initiate I/Os to the hardware, and for the hardware to notify the IOP of I/O status.

## 2.1.2.3 SATA Engine

The SATA engine provides information to the transport modules to enable handling of SATA commands. The SATA engine tracks queued commands per device and provides these tags to the SATA transport layer blocks.

## 2.1.2.4 Port Layer Connection Manager and Switch

The port layer connection monitor and switch manages transmission requests from the transport modules and originates connection requests to the SAS links. It is also responsible for handling SAS wide port configurations.

## 2.1.2.5 SAS Link and Phy

The LSISAS1068 uses the Gflx GigaBlaze transceivers to implement the SAS link. The SAS link layer manages SAS connections between initiator and target ports, data clocking, and CRC checking on received data. The SAS link is also responsible for starting a link reset sequence.

The SAS phys interface to the physical layer, perform serial-to-parallel conversion of received data and parallel-to-serial conversion of transmit data, manage phy reset sequences, and perform 8b/10b encoding.

## 2.1.2.6 Quad Port DMA Arbiter

The quad port arbiter interfaces with the host interface DMA arbiter and determines bus priority between each of the four ports for DMA transfers.

## 2.1.3 Context RAM

The context RAM is a memory that is shared between the host interface module and the quad port modules. The context RAM contains the message frames, the FIFOs, and a portion of the firmware.

# 2.2 Fusion-MPT Architecture Overview

The Fusion-MPT architecture provides two I/O methods for the host system to communicate with the IOP: the system interface doorbell and the message queues.

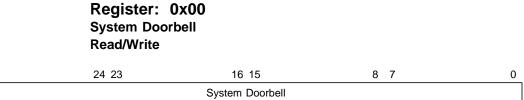

The system interface doorbell is a simple message passing mechanism that allows the PCI host system and IOP to exchange single 32-bit Dword messages. When the host system writes to the doorbell, the LSISAS1068 hardware generates a maskable interrupt to the IOP, which can then read the doorbell value and take the appropriate action. When the IOP writes a value to the doorbell, the LSISAS1068 hardware generates a maskable interrupt to the host system. The host system can then read the doorbell value and take the appropriate action.

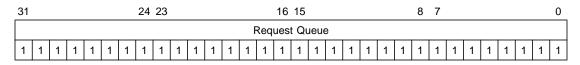

There are two, 32-bit message queues: the request message queue and the reply message queue. The host uses the request queue to request an action by the LSISAS1068, and the LSISAS1068 uses the reply queue to return status information to the host. The request message queue consists of the request post FIFO. The reply message queue consists of both the reply post FIFO and the reply free FIFO. The context RAM contains the message queues. The Fusion-MPT architecture also provides a High Priority Request FIFO to provide high priority request free messages to the host on reads and to accept high priority request post messages from the host on writes.

Communication using the message queues occurs through request messages and reply messages. Request message frame descriptors are pointers to the request message frames and are passed through the request post FIFO. The request message frame data structure is up to 128 bytes in length and includes a message header and a payload. The header uniquely identifies the message. The payload contains information that is specific to the request. Reply message frame descriptors have one of two formats and are passed through the reply post FIFO. When indicating the successful completion of a SCSI I/O, the IOP writes the reply message frame descriptor using the Context Reply format, which is a message context. If a SCSI I/O does not complete successfully, the IOP uses the Address Reply format. In this case, the IOP pops a reply message frame from the reply free FIFO, generates a reply message describing the error, writes the reply message to system memory, and writes the address of the reply message frame to the reply post FIFO. The host can then read the reply message and take the appropriate action.

The doorbell mechanism provides both a communication path that interrupts the host system device driver and an alternative communication path to the message queues. Since data transport through the system doorbell occurs a single Dword at a time, use the LSISAS1068 message queues for normal operation and data transport.

# 2.3 PCI Functional Description

The host PCI interface complies with the *PCI Local Bus Specification, Version 3.0* and the *PCI-X Addendum to the PCI Local Bus Specification, Revision 2.0.* The LSISAS1068 supports a 133 MHz, 64-bit PCI-X bus. The LSISAS1068 provides support for 64-bit addressing with Dual Address Cycle (DAC). The LSISAS1068 does not support 5 V PCI signaling.

## 2.3.1 PCI Addressing

The three physical address spaces the PCI specification defines are:

- PCI Configuration Space

- PCI I/O Space for operating registers

- PCI Memory Space for operating registers

The following sections describe the PCI address spaces.

## 2.3.1.1 PCI Configuration Space

The PCI Configuration Space is a contiguous 256 x 8-bit set of addresses. The system BIOS initializes the configuration registers using PCI configuration cycles. The LSISAS1068 decodes C\_BE[3:0]/ to

determine if a PCI cycle intends to access the configuration register space. The IDSEL signal behaves as a chip select signal that enables access to the configuration register space only. The LSISAS1068 ignores configuration read/write cycles when IDSEL is not asserted.

Bits AD[10:8] address the PCI Function Configuration Space (AD[10:8] = 0b000). The LSISAS1068 does not respond to any other encodings of AD[10:8]. Bits AD[7:2] select one of the 64 Dword registers in the device's PCI Configuration Space. Bits AD[1:0] determine if the configuration command is a Type 0 Configuration Command (AD[1:0] = 0b00) or a Type 1 Configuration Command (AD[1:0] = 0b01). Since the LSISAS1068 is not a PCI Bridge device, all PCI Configuration Commands designated for the LSISAS1068 must be Type 0. C\_BE[3:0]/ address the individual bytes within each Dword and determine the type of access to perform.

## 2.3.1.2 PCI I/O Space

The PCI specification defines I/O Space as a contiguous 32-bit I/O address that all system resources share, including the LSISAS1068. The I/O Base Address register determines the 256-byte PCI I/O area that the PCI device occupies.

#### 2.3.1.3 PCI Memory Space

The LSISAS1068 contains two PCI memory spaces: PCI Memory Space [0] and PCI Memory Space [1]. PCI Memory Space [0] supports normal memory accesses while PCI Memory Space [1] supports diagnostic memory accesses. The LSISAS1068 requires 64 Kbytes of memory space.

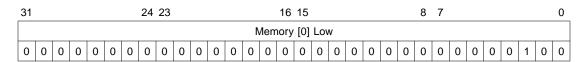

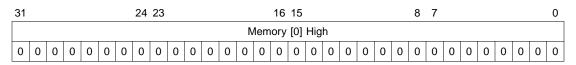

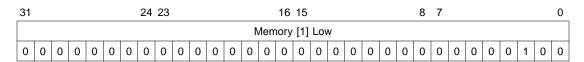

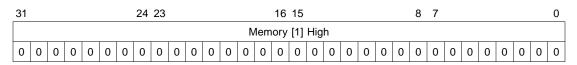

The PCI specification defines memory space as a contiguous 64-bit memory address that all system resources share. The Memory [0] Low and Memory [0] High registers determine which 64 Kbyte memory area PCI Memory Space [0] occupies. The Memory [1] Low and Memory [1] High registers determine which 64 Kbyte memory area PCI Memory Space [1] occupies.

### 2.3.2 PCI Commands and Functions

Bus commands indicate to the target the type of transaction the master is requesting. The master encodes the bus commands on the C\_BE[3:0]/ lines during the address phase. The PCI bus command encodings appear in Table 2.1.

| Table 2.1 | PCI/PCI-X Bus Commands and Encodings <sup>1</sup> |

|-----------|---------------------------------------------------|

|-----------|---------------------------------------------------|

| C_BE[3:0]/ | PCI Command                 | PCI-X Command                  | Supports<br>as Master | Supports<br>as Slave   |

|------------|-----------------------------|--------------------------------|-----------------------|------------------------|

| 0b0000     | Interrupt Acknowledge       | Interrupt Acknowledge          | No                    | No                     |

| 0b0001     | Special Cycle               | Special Cycle                  | No                    | No                     |

| 0b0010     | I/O Read                    | I/O Read                       | Yes                   | Yes                    |

| 0b0011     | I/O Write                   | I/O Write                      | Yes                   | Yes                    |

| 0b0100     | Reserved                    | Reserved                       | N/A                   | N/A                    |

| 0b0101     | Reserved                    | Reserved                       | N/A                   | N/A                    |

| 0b0110     | Memory Read                 | Memory Read Dword              | Yes                   | Yes                    |

| 0b0111     | Memory Write                | Memory Write                   | Yes                   | Yes                    |

| 0b1000     | Reserved                    | Alias to<br>Memory Read Block  | PCI: N/A<br>PCI-X: No | PCI: N/A<br>PCI-X: Yes |

| 0b1001     | Reserved                    | Alias to<br>Memory Write Block | PCI: N/A<br>PCI-X: No | PCI: N/A<br>PCI-X: Yes |

| 0b1010     | Configuration Read          | Configuration Read             | No                    | Yes                    |

| 0b1011     | Configuration Write         | Configuration Write            | No                    | Yes                    |

| 0b1100     | Memory Read Multiple        | Split Completion               | Yes                   | Yes <sup>2</sup>       |

| 0b1101     | Dual Address Cycle          | Dual Address Cycle             | Yes                   | Yes                    |

| 0b1110     | Memory Read Line            | Memory Read Block              | Yes                   | Yes <sup>2</sup>       |

| 0b1111     | Memory Write and Invalidate | Memory Write Block             | Yes                   | Yes <sup>3</sup>       |

1. The LSISAS1068 ignores reserved commands as a slave and never generates them as a master.

When acting as a slave in the PCI mode, the LSISAS1068 supports this command as the PCI Memory Read command.

3. When acting as a slave in the PCI mode, the LSISAS1068 supports this command as the PCI Memory Write command.

The following sections describe how the LSISAS1068 implements these commands.

#### 2.3.2.1 Interrupt Acknowledge Command

The LSISAS1068 ignores this command as a slave and never generates it as a master.

#### 2.3.2.2 Special Cycle Command

The LSISAS1068 ignores this command as a slave and never generates it as a master.

#### 2.3.2.3 I/O Read Command

The I/O Read command reads data from an agent mapped in the I/O address space. When decoding I/O commands, the LSISAS1068 decodes the lower 32 address bits and ignores the upper 32 address bits. The LSISAS1068 supports this command when operating in either the PCI or PCI-X bus mode.

#### 2.3.2.4 I/O Write Command

The I/O Write command writes data to an agent mapped in the I/O address space. When decoding I/O commands, the LSISAS1068 decodes the lower 32 address bits and ignores the upper 32 address bits. The LSISAS1068 supports this command when operating in either the PCI or PCI-X bus mode.

#### 2.3.2.5 Memory Read Command

The LSISAS1068 uses the Memory Read command to read data from an agent mapped in the memory address space. The target can perform an anticipatory read if such a read produces no side effects. The LSISAS1068 supports this command when operating in the PCI bus mode.

#### 2.3.2.6 Memory Read Dword Command

The Memory Read Dword command reads up to a single Dword of data from an agent mapped in the memory address space and can only be initiated as a 32-bit transaction. The target can perform an anticipatory read if such a read produces no side effects. The LSISAS1068 supports this command when operating in the PCI-X bus mode.

#### 2.3.2.7 Memory Write Command

The Memory Write command writes data to an agent mapped in the memory address space. The target assumes responsibility for data coherency when it returns "ready." The LSISAS1068 supports this command when operating in either the PCI or PCI-X bus mode.

#### 2.3.2.8 Alias to Memory Read Block Command

This command is reserved for future implementations of the PCI specification. The LSISAS1068 never generates this command as a master. When a slave, the LSISAS1068 supports this command using the Memory Read Block command.

#### 2.3.2.9 Alias to Memory Write Block Command

This command is reserved for future implementations of the PCI specification. The LSISAS1068 never generates this command as a master. When a slave, the LSISAS1068 supports this command using the Memory Write Block command.

#### 2.3.2.10 Configuration Read Command

The Configuration Read command reads the configuration space of a device. The LSISAS1068 never generates this command as a master, but does respond to it as a slave. A device on the PCI bus selects the LSISAS1068 by asserting its IDSEL signal when AD[1:0] equal 0b00. During the address phase of a configuration cycle, AD[7:2] address one of the 64 Dword registers in the configuration space of each device. C\_BE[3:0]/ address the individual bytes within each Dword register and determine the type of access to perform. Bits AD[10:8] address the PCI function Configuration Space (AD[10:8] = 0b000). The LSISAS1068 treats AD[63:11] as logical don't cares.

#### 2.3.2.11 Configuration Write Command

The Configuration Write command writes the configuration space of a device. The LSISAS1068 never generates this command as a master, but does respond to it as a slave. A device on the PCI bus selects the

LSISAS1068 by asserting its IDSEL signal when bits AD[1:0] equal 0b00. During the address phase of a configuration cycle, bits AD[7:2] address one of the 64 Dword registers in the configuration space of each device. C\_BE[3:0]/ address the individual bytes within each Dword register and determine the type of access to perform. Bits AD[10:8] decode the PCI function Configuration Space (AD[10:8] = 0b000). The LSISAS1068 treats AD[63:11] as logical don't cares.

#### 2.3.2.12 Memory Read Multiple Command

The Memory Read Multiple command is identical to the Memory Read command, except it additionally indicates that the master intends to fetch multiple cache lines before disconnecting. The LSISAS1068 supports PCI Memory Read Multiple functionality when operating in the PCI mode and determines when to issue a Memory Read Multiple command instead of a Memory Read command.

**Burst Size Selection** – The Read Multiple command reads multiple cache lines of data during a single bus ownership. The number of cache lines the LSISAS1068 reads is a multiple of the cache line size, which Revision 3.0 of the PCI specification provides. The LSISAS1068 selects the largest multiple of the cache line size based on the amount of data to transfer.

#### 2.3.2.13 Split Completion Command

Split transactions in PCI-X replace the delayed transactions in conventional PCI. The LSISAS1068 supports up to 16 outstanding split transactions when operating in the PCI-X mode. A split transaction consists of at least two separate bus transactions: a split request, which the requester initiates, and one or more split completion commands, which the completer initiates. Revision 2.0 of the PCI-X addendum permits split transaction completion for the Memory Read Block, Alias to Memory Read Block, Memory Read Dword, Interrupt Acknowledge, I/O Read, I/O Write, Configuration Read, and Configuration Write commands. When operating in the PCI-X mode, the LSISAS1068 supports the Split Completion command for all of these commands except the Interrupt Acknowledge command, which the LSISAS1068 neither responds to nor generates.

#### 2.3.2.14 Dual Address Cycles (DAC) Command

The LSISAS1068 performs Dual Address Cycles (DAC), per the *PCI Local Bus Specification, Version 3.0.* The LSISAS1068 supports this command when operating in either the PCI or PCI-X bus mode.

#### 2.3.2.15 Memory Read Line Command

This command is identical to the Memory Read command except it additionally indicates that the master intends to fetch a complete cache line. The LSISAS1068 supports this command when operating in the PCI mode.

#### 2.3.2.16 Memory Read Block Command

The LSISAS1068 uses this command to read from memory. The LSISAS1068 supports this command when operating in the PCI-X mode.

#### 2.3.2.17 Memory Write and Invalidate Command

The Memory Write and Invalidate command is identical to the Memory Write command, except it additionally guarantees a minimum transfer of one complete cache line. The master uses this command when it intends to write all bytes within the addressed cache line in a single PCI transaction unless interrupted by the target. This command requires implementation of the PCI Cache Line Size register. The LSISAS1068 determines when to issue a Write and Invalidate command instead of a Memory Write command and supports this command when operating in the PCI bus mode.

**Alignment** – The LSISAS1068 uses the calculated line size value to determine if the current address aligns to the cache line size. If the address does not align, the LSISAS1068 bursts data using a noncache command. If the starting address aligns, the LSISAS1068 issues a Memory Write and Invalidate command using the cache line size as the burst size.

**Multiple Cache Line Transfers** – The Memory Write and Invalidate command can write multiple cache lines of data in a single bus ownership. The LSISAS1068 issues a burst transfer as soon as it reaches a cache line boundary. The PCI Local Bus specification states that the transfer size must be a multiple of the cache line size. The

LSISAS1068 selects the largest multiple of the cache line size based on the transfer size. When the DMA buffer contains less data than the value Cache Line Size register specifies, the LSISAS1068 issues a Memory Write command on the next cache boundary to complete the data transfer.

#### 2.3.2.18 Memory Write Block Command

The LSISAS1068 uses this command to burst data to memory. The LSISAS1068 supports this command when operating in the PCI-X bus mode.

#### 2.3.3 PCI Arbitration

The LSISAS1068 contains an independent bus mastering function. The system interface bus mastering function manages DMA operations as well as the request and reply message frames.

### 2.3.4 PCI Cache Mode

The LSISAS1068 supports an 8-bit Cache Line Size register. The Cache Line Size register provides the ability to sense and react to nonaligned addresses corresponding to cache line boundaries. The LSISAS1068 determines when to issue a PCI cache command (Memory Read Line, Memory Read Multiple, and Memory Write and Invalidate), or PCI noncache command (Memory Read or Memory Write command).

#### 2.3.5 PCI Interrupts

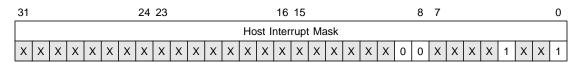

The LSISAS1068 signals an interrupt to the host processor either using PCI interrupt pins (INTA/ and ALT\_INTA/), or Message Signaled Interrupts (MSI and MSI-X). The Interrupt Request Routing Mode bits in the Host Interrupt Mask register configure the routing of each interrupt to either the INTA/ and/or the ALT\_INTA/ pin.

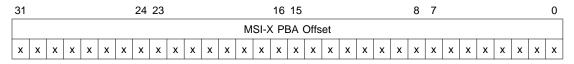

MSI is an optional feature that enables a device to signal an interrupt by writing to a specified address. MSI-X is an extension of the MSI that increases the number of available message vectors, allows software aliasing of message vectors, and allows each message vector to use an independent address and data value. If using MSI or MSI-X, the LSISAS1068 does not signal interrupts on INTA/ or ALT\_INTA/. Note that enabling MSI or MSI-X to mask PCI interrupts is a violation of the PCI

specification. The LSISAS1068 implements its own MSI and MSI-X register sets. The MSI functionality is managed through the MSI register set, and the MSI-X functionality is managed through the MSI-X register set. The PCI specification prohibits system software from simultaneously enabling MSI and MSI-X.

The Host Interrupt Mask register also prevents the assertion of a PCI interrupt to the host processor by selectively masking reply interrupts and system doorbell interrupts. This register masks both pin-based and MSI-based interrupts.

#### 2.3.6 Power Management

The LSISAS1068 complies with the *PCI Power Management Interface Specification, Revision 1.2,* and the *PC2001 System Design Guide.* The LSISAS1068 supports the D0, D1, D2, D3<sub>hot</sub>, and D3<sub>cold</sub> power states. D0 is the maximum power state, and D3 is the minimum power state. Power State D3 is further categorized as D3<sub>hot</sub> or D3<sub>cold</sub>. Powering the device off places it in the D3<sub>cold</sub> Power State.

# 2.4 SAS Functional Description

The LSISAS1068 provides eight SAS/SATA phys. Each phy can form one side of the physical link in a connection with a phy on a different SAS/SATA device. The physical link contains four wires that form two differential signal pairs. One differential pair transmits signals, while the other differential pair receives signals. Both differential pairs operate simultaneously, and allow concurrent data transmission in both the receive and the transmit directions. Figure 2.2 shows two phys that are attached with a physical link.

Figure 2.2 Transceivers within a Phy

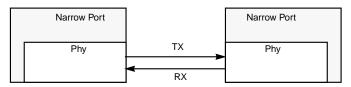

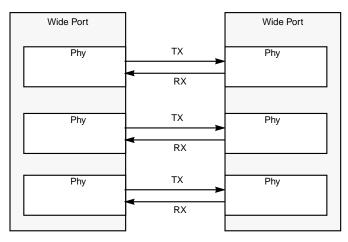

Phys are contained within ports. A port can contain a single phy or can contain multiple phys. A narrow port contains a single phy, while a wide port contains multiple phys. The LSISAS1068 supports wide ports that contain up to four phys. Phys within a single quad port can combine to form a wide port, which contains up to four phys. Since each phy within a wide port can transmit data at 3.0 Gbit/s SAS, increasing the number of phys in a port increases the data transfer rate. Combining four phys on the LSISAS1068 into a wide port enables bandwidths of up to 12.0 Gbits/s.

A link between two narrow ports is a narrow link. A link between two wide ports is a wide link. Figure 2.3 illustrates a narrow link and a wide link. The wide link contains three phys in each port.

#### Figure 2.3 Narrow and Wide Links

#### a. Narrow Link Containing One Phy in each Port

#### b. Wide Link Containing Three Phys in each Port

Each phy on the LSISAS1068 can function as an SSP Initiator, an SSP target, an SMP initiator, an STP initiator, or a SATA Initiator. A phy can function in only one role during a connection, but function in different roles during different connections. The LSISAS1068 uses SSP to communicate with other SAS devices, and uses SMP to communicate management information with other SAS devices. STP communicates with SATA devices in a SAS domain by tunneling through SAS expanders to the SATA device. The LSISAS1068 can also use SATA to communicate with other SATA devices. Figure 2.4 illustrates the uses of the SSP, STP, and SMP protocols.

Figure 2.4 SSP, STP, and SMP Protocol Usage

# 2.5 External Memory Interface

The external memory control block provides a direct slave interface between the internal primary AHB bus and an external 32-bit memory interface. This interface is for accessing external flash ROM and NVSRAM devices. Because the LSISAS1068 uses a 32-bit multiplexed address/data bus, designs using the LSISAS1068 do not require latches or CPLD devices to construct memory addresses.

#### 2.5.1 Memory Requirements

The memory requirements for the LSISAS1068 depend on the board design and application. Several board design possibilities and their respective memory requirements are presented as follows.

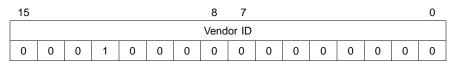

- System board implementation