#### PRELIMINARY

#### GENERAL DESCRIPTION

This data sheet covers two products: W83977F, and W83977AF whose pin assignment, and most of the functions are the same. W83977AF is an advanced version from W83977F featuring the FIR function.

W83977F/ AF is an evolving product from Winbond's most popular I/O chip W83877F --- which integrates the disk drive adapter, serial port (UART), IrDA 1.0 SIR, parallel port, configurable plugand-play registers in one chip --- plus additional powerful features: **ACPI**, 8042 keyboard controller with PS/2 mouse support, Real Time Clock, 14 general purpose I/O ports, full 16-bit address decoding, TV remote IR (Consumer IR, supporting NEC, RC-5, extended RC-5, and RECS-80 protocols). In addition, W83977AF provides the functions of **IrDA 1.1** (MIR for 1.152M bps or FIR for 4M bps).

The disk drive adapter functions of W83977F/ AF include a floppy disk drive controller compatible with the industry standard 82077/ 765, data separator, write pre-compensation circuit, decode logic, data rate selection, clock generator, drive interface control logic, and interrupt/ DMA logic. The wide range of functions integrated onto the W83977F/ AF greatly reduces the number of components required for interfacing with floppy disk drives. The W83977F/ AF supports up to four 360K, 720K, 1.2M, 1.44M, or 2.88M disk drives and data transfer rates of 250 Kb/s, 300 Kb/s, 500 Kb/s,1 Mb/s, and 2 Mb/s.

The W83977F/ AF provides two high-speed serial communication ports (UARTs), one of which supports serial Infrared communication. Each UART includes a 16-byte send/receive FIFO, a programmable baud rate generator, complete modem control capability, and a processor interrupt system. Both UARTs provide legacy speed with baud rate 115.2k and provide advanced speed with baud rate **230k**, **460k**, and **921k bps** which support higher speed modems. W83977AF alone provides independent **3rd UART** (32-byte FIFO) dedicated for IR function.

The W83977F/ AF supports one PC-compatible printer port (SPP), Bi-directional Printer port (BPP) and also Enhanced Parallel Port (EPP) and Extended Capabilities Port (ECP). Through the printer port interface pins, also available are: Extension FDD Mode and Extension 2FDD Mode allowing one or two external floppy disk drives to be connected.

The configuration registers support mode selection, function enable/disable, and power down function selection. Furthermore, the configurable PnP features are compatible with the plug-and-play feature demand of Windows 95<sup>TM</sup>, which makes system resource allocation more efficient than ever.

W83977F/ AF provides functions that complies with **ACPI** (*Advanced Configuration and Power Interface*), which includes support of legacy and ACPI power management through SMI or SCI function pins. W83977F/ AF also has auto power management to reduce power consumption.

The keyboard controller is based on 8042 compatible instruction set with a 2K Byte programmable ROM and a 256-Byte RAM bank. Keyboard BIOS firmware are available with optional AMIKEY<sup>TM</sup> -2, Phoenix MultiKey/42<sup>TM</sup>, or customer code.

The W83977F/ AF provides a set of flexible I/O control functions to the system designer through a set of General Purpose I/O ports. These GPIO ports may serve as simple I/O or may be individually configured to provide a pre-defined alternate function.

W83977F/ AF is made to fully comply with **Microsoft PC97 Hardware Design Guide**. IRQs, DMAs, and I/O space resource are flexible to adjust to meet ISA PnP requirement. Full 16-bit address decoding is also provided. Moreover W83977F/ AF is made to meet the specification of PC97 s requirement in the power management: **ACPI** and **DPM** (Device Power Management).

### FEATURES

PRELIMINARY

### General

- Plug & Play 1.0A Compliant

- Support 13 IRQs, 4 DMA channels, full 16-bit addresses decoding

- Capable of ISA Bus IRQ Sharing

- Compliant with Microsoft PC97 Hardware Design Guide

- Support DPM (Device Power Management), ACPI

- Programmable configuration settings

- 24 or 14.318 Mhz clock input

#### FDC

- Compatible with IBM PC AT disk drive systems

- · Variable write pre-compensation with track selectable capability

- Support vertical recording format

- DMA enable logic

- 16-byte data FIFOs

- Support floppy disk drives and tape drives

- Detects all overrun and underrun conditions

- Built-in address mark detection circuit to simplify the read electronics

- FDD anti-virus functions with software write protect and FDD write enable signal (write data signal was forced to be inactive)

- Support up to four 3.5-inch or 5.25-inch floppy disk drives

- Completely compatible with industry standard 82077

- 360K/720K/1.2M/1.44M/2.88M format; 250K, 300K, 500K, 1M, 2M bps data transfer rate

- Support 3-mode FDD, and its Win95 driver

#### UART

- Two high-speed 16550 compatible UARTs with 16-byte send/receive FIFOs

- 3rd UART with 32-byte send/receive FIFO is supported for IR function [W83977AF only]

- MIDI compatible

- Fully programmable serial-interface characteristics:

- --- 5, 6, 7 or 8-bit characters

- --- Even, odd or no parity bit generation/detection

- --- 1, 1.5 or 2 stop bits generation

- Internal diagnostic capabilities:

- --- Loop-back controls for communications link fault isolation

- --- Break, parity, overrun, framing error simulation

#### PRELIMINARY

- Programmable baud generator allows division of 1.8461 Mhz and 24 Mhz by 1 to (2<sup>16</sup>-1)

- Maximum baud rate up to **921k bps** for 14.769 Mhz and 1.5M bps for 24 Mhz

### Infrared

- Support IrDA version 1.0 SIR protocol with maximum baud rate up to 115.2K bps

- Support SHARP ASK-IR protocol with maximum baud rate up to 57,600 bps

- Support IrDA version 1.1 MIR (1.152M bps) and FIR (4M bps) protocol [W83977AF only]

- --- Single DMA channel for transmitter or receiver

- --- 3rd UART with 32-byte FIFO is supported in both TX/RX transmission [W83977AF only]

--- 8-byte status FIFO is supported to store received frame status (such as overrun CRC error, etc.)

• Support auto-config SIR and FIR [W83977AF only]

#### **Parallel Port**

- Compatible with IBM parallel port

- Support PS/2 compatible bi-directional parallel port

- Support Enhanced Parallel Port (EPP) Compatible with IEEE 1284 specification

- Support Extended Capabilities Port (ECP) Compatible with IEEE 1284 specification

- Extension FDD mode supports disk drive B; and Extension 2FDD mode supports disk drives A and B through parallel port

- Enhanced printer port back-drive current protection

### Advanced Power Management (APM) Controlling

- Power turned on when RTC reaches a preset date and time

- Power turned on when a ring pulse or pulse train is detected on the PHRI, or when a high to low transition on PWAKIN1, or PWAKIN2 input signals

- Power turned on when PANSW input signal indicates a switch on event

- Power turned off when PANSW input signal indicates a switch off event

- Power turned off when a fail-safe event occurs (power-save mode detected but system is hung up)

- · Power turned off when software issues a power off command

#### Keyboard Controller

- 8042 based with optional F/W from AMIKKEY<sup>TM</sup>-2, Phoenix MultiKey/42<sup>TM</sup> or customer code

- with 2K bytes of programmable ROM, and 256 bytes of RAM

- Asynchronous Access to Two Data Registers and One status Register

- · Software compatibility with the 8042 and PC87911 microcontrollers

- Support PS/2 mouse

- Support port 92

- Support both interrupt and polling modes

- Fast Gate A20 and Hardware Keyboard Reset

- 8 Bit Timer/ Counter; support binary and BCD arithmetic

- 6, 8, 12, or 16 Mhz operating frequency (16 Mhz available only if input clock rate = 14.318 Mhz)

### PRELIMINARY

#### **Real Time Clock**

- 27 bytes of clock, **On-Now**, and control/status register (14 bytes in Bank 0 and 13 bytes in Bank 2); 242 bytes of general purpose RAM

- BCD or Binary representation of time, calendar, and alarm registers

- Counts seconds, minutes, hours, days of week, days of month, month, year, and century

- 12-hour/ 24-hour clock with AM/PM in 12-hour mode

- Daylight saving time option; automatic leap-year adjustment

- Dedicated alarm (Alarm B) for On-Now function

- Programmable delay-time between panel switch off and power supply control

- Software control power-off; various and maskable events to activate system Power-On

- System Management Interrupt ( SMI ) for panel switch power-off event

#### **General Purpose I/O Ports**

- 14 programmable general purpose I/O ports; 6 dedicate, 8 optional

- General purpose I/O ports can serve as simple I/O ports, interrupt steering inputs, watching dog timer output, power LED output, infrared I/O pins, general purpose address decoder, KBC control I/O pins.

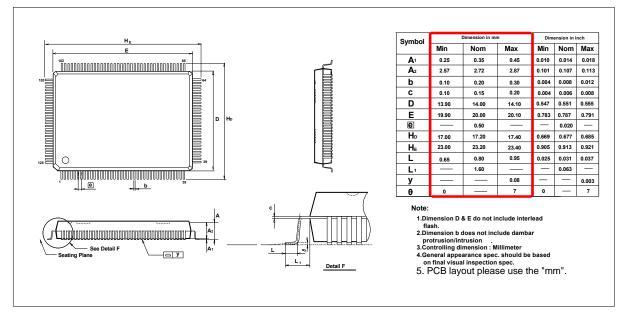

#### Package

• 128-pin PQFP

### PRELIMINARY

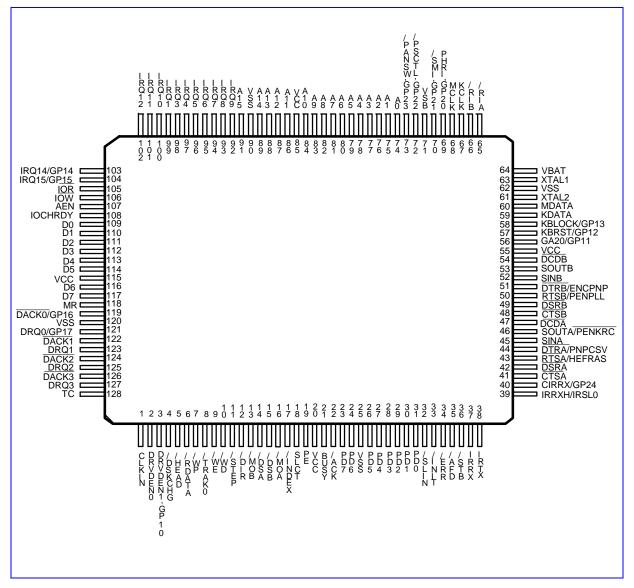

### **PIN CONFIGURATION**

PRELIMINARY

### **1. PIN DESCRIPTION**

Note: Please refer to Section 11.2 DC CHARACTERISTICS for details. I/O6t - TTL level bi-directional pin with 6 mA source-sink capability I/O8t - TTL level bi-directional pin with 8 mA source-sink capability I/O8 - CMOS level bi-directional pin with 8 mA source-sink capability I/O12t - TTL level bi-directional pin with 12 mA source-sink capability I/O12 - CMOS level bi-directional pin with 12 mA source-sink capability I/O16u - CMOS level bi-directional pin with 16 mA source-sink capability with internal pull-up resistor I/OD16u - CMOS level bi-directional pin open drain output with 16 mA sink capability with internal pull-up resistor I/O24t - TTL level bi-directional pin with 24 mA source-sink capability OUT8t - TTL level output pin with 8 mA source-sink capability OUT12t - TTL level output pin with 12 mA source-sink capability OD12 - Open-drain output pin with 12 mA sink capability OD24 - Open-drain output pin with 24 mA sink capability INt - TTL level input pin INc - CMOS level input pin INcu - CMOS level input pin with internal pull-up resitor INcs - CMOS level Schmitt-triggered input pin

INts - TTL level Schmitt-triggered input pin

INtsu - TTL level Schmitt-triggered input pin with internal pull-up resistor

| SYMBOL  | PIN     | I/O                | FUNCTION                                                                                  |

|---------|---------|--------------------|-------------------------------------------------------------------------------------------|

| A0–A10  | 74-84   | INt                | System address bus bits 0-10                                                              |

| A11-A14 | 86-89   | INt                | System address bus bits 11-14                                                             |

| A15     | 91      | INt                | System address bus bit 15                                                                 |

| D0-D5   | 109-114 | I/O <sub>12t</sub> | System data bus bits 0-5                                                                  |

| D6–D7   | 116-117 | I/O <sub>12t</sub> | System data bus bits 6-7                                                                  |

| IOR     | 105     | IN <sub>ts</sub>   | CPU I/O read signal                                                                       |

| ĪOW     | 106     | IN <sub>ts</sub>   | CPU I/O write signal                                                                      |

| AEN     | 107     | INt                | System address bus enable                                                                 |

| IOCHRDY | 108     | OD <sub>24</sub>   | In EPP Mode, this pin is the IO Channel Ready output to extend the host read/write cycle. |

| MR      | 118     | IN <sub>ts</sub>   | Master Reset. Active high. MR is low during normal operations.                            |

#### 1.1 Host Interface

# PRELIMINARY

### 1.1 Host Interface, continued

| SYMBOL          | PIN | I/O                                    | FUNCTION                                                                                             |

|-----------------|-----|----------------------------------------|------------------------------------------------------------------------------------------------------|

| DACK0<br>GP16   | 119 | IN <sub>ts</sub><br>I/O <sub>12t</sub> | CR2C bit5, 4= 00 (default): DMA Channel 0 Acknowledge signal.                                        |

| (WDTO)<br>P15   |     | I/O <sub>12t</sub>                     | CR2C bit5, 4= 01: General purpose I/O port 1 bit 6. It can be configured as a watchdog timer output. |

|                 |     | OUT <sub>12t</sub>                     | CR2C bit5, 4= 10: Keyboard P15 I/O port.                                                             |

| RTSC            |     | 121                                    | CR2C bit5, 4= 11: TTS output of UART C. [W83977AF only]                                              |

| DRQ0            | 121 | OUT <sub>12t</sub>                     | CR2C bit7, 6= 00 (default): DMA Channel 0 request signal.                                            |

| GP17<br>(PLEDO) |     | I/O <sub>12t</sub>                     | CR2C bit7, 6= 01: General purpose I/O port 1, bit 7. It can be configured as power LED output.       |

| P14             |     | I/O <sub>12t</sub>                     | CR2C bit7, 6= 10: Keyboard P14 I/O port.                                                             |

| DTRC            |     | OUT <sub>12t</sub>                     | CR2C bit7, 6= 11: DTR output of UART C. [W83977AF only]                                              |

| DACK1           | 122 | IN <sub>ts</sub>                       | DMA Channel 1 Acknowledge signal                                                                     |

| DRQ1            | 123 | OUT <sub>12t</sub>                     | DMA Channel 1 request signal                                                                         |

| DACK2           | 124 | IN <sub>ts</sub>                       | DMA Channel 2 Acknowledge signal                                                                     |

| DRQ2            | 125 | OUT <sub>12t</sub>                     | DMA Channel 2 request signal                                                                         |

| DACK3           | 126 | IN <sub>ts</sub>                       | DMA Channel 3 Acknowledge signal                                                                     |

| DRQ3            | 127 | OUT <sub>12t</sub>                     | DMA Channel 3 request signal                                                                         |

| тс              | 128 | IN <sub>ts</sub>                       | Terminal Count. When active, this pin indicates termination of a DMA transfer.                       |

| IRQ1            | 99  | OUT <sub>12t</sub>                     | Interrupt request 1                                                                                  |

| IRQ3            | 98  | OUT <sub>12t</sub>                     | Interrupt request 3                                                                                  |

| IRQ4            | 97  | OUT <sub>12t</sub>                     | Interrupt request 4                                                                                  |

| IRQ5            | 96  | OUT <sub>12t</sub>                     | Interrupt request 5                                                                                  |

| IRQ6            | 95  | OUT <sub>12t</sub>                     | Interrupt request 6                                                                                  |

| IRQ7            | 94  | OUT <sub>12t</sub>                     | Interrupt request 7                                                                                  |

| IRQ8/ nIRQ8     | 93  | OUT <sub>12t</sub>                     | Interrupt request 8; default is nIRQ8 for RTC                                                        |

| IRQ9            | 92  | OUT <sub>12t</sub>                     | Interrupt request 9                                                                                  |

| IRQ10           | 100 | OUT <sub>12t</sub>                     | Interrupt request 10                                                                                 |

| IRQ11           | 101 | OUT <sub>12t</sub>                     | Interrupt request 11                                                                                 |

| IRQ12           | 102 | OUT <sub>12t</sub>                     | Interrupt request 12                                                                                 |

## PRELIMINARY

## 1.1 Host Interface, continued

| SYMBOL  | PIN | I/O                | FUNCTION                                                       |

|---------|-----|--------------------|----------------------------------------------------------------|

| IRQ14   | 103 | OUT <sub>12t</sub> | CR2C bit1, 0= 00 (default): Interrupt request 14               |

| GP14    |     | I/O <sub>12t</sub> | CR2C bit1, 0= 01: General purpose I/O port 1, bit 4. It can be |

| (GPACS) |     |                    | configured as a general purpose address decode output.         |

| PLED    |     | OUT <sub>12t</sub> | CR2C bit1, 0= 10: Power LED output.                            |

| IRSL1   |     | OUT <sub>12t</sub> | CR2C bit1, 0= 11: IR module select signal 1. [W83977AF only]   |

| IRQ15   | 104 | OUT <sub>12t</sub> | CR2C bit3, 2= 00 (default): Interrupt request 15               |

| GP15    |     | I/O <sub>12t</sub> | CR2C bit3, 2= 01: General purpose I/O port 1, bit 5. It can be |

| (GPAWE) |     |                    | configured as a general purpose address write enable output.   |

| WDT     |     | OUT <sub>12t</sub> | CR2C bit3, 2= 10: Watch-Dog timer output.                      |

| IRSL2   |     | OUT <sub>12t</sub> | CR2C bit3, 2= 11: IR module select signal 2. [W83977AF only]   |

| CLKIN   | 1   | IN <sub>t</sub>    | 14.318/ 24 Mhz clock input, selectable through bit 5 of CR24.  |

### 1.2 Advanced Power Management

| SYMBOL          | PIN | I/O                | FUNCTION                                                                                                                                                      |

|-----------------|-----|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PHRI            | 69  | INt                | CR2B bit2, 1=00 (default): Advanced Power Management (APM) phone ring indicator. Detection of an active PHRI pulse or pulse train activates the PSCTL signal. |

| GP20<br>(KBRST) |     | I/O <sub>12t</sub> | CR2B bit2, 1=01: General purpose I/O port 2, bit 0. It can be configured as keyboard reset (Keyboard P20).                                                    |

| POFIRQ          | 70  | OUT <sub>12t</sub> | CR2B bit4, 3=00 (default): Advanced Power Management (APM) power off interrupt request.                                                                       |

| GP21 (P13)      |     | I/O <sub>12t</sub> | CR2B bit4, 3=01: General purpose I/O port 2, bit 1. It can be configured as Keyboard P13 I/O port.                                                            |

| P16             |     | I/O <sub>12t</sub> | CR2B bit4, 3=10: Keyboard P16 I/O port.                                                                                                                       |

| RIC             |     | INt                | CR2B bit4, 3=11: RI input of UART C. [W83977AF only]                                                                                                          |

| VSB             | 71  | -                  | Advanced Power Management (APM) standby current source                                                                                                        |

| PSCTL           | 72  | OUT <sub>12t</sub> | CR2B bit5=0 (default): On/Off control for Advanced Power Management (APM). This signal tells the main power supply whether power should be turned on.         |

| GP22 (P14)      |     | I/O <sub>12t</sub> | CR2B bit5=1: General purpose I/O port 2, bit 2. It can be configured as Keyboard P14 I/O port.                                                                |

## PRELIMINARY

#### 1.2 Advanced Power Management, continued

| SYMBOL     | PIN | I/O                | FUNCTION                                                                                                                                                                                                                                                                                                                                                      |

|------------|-----|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PANSW      | 73  | INt                | CR2B bit7, 6=00 (default): On/Off switch for Advanced Power<br>Management (APM). This signal indicates a request to switch<br>the power on or off. When the VDD of the chip is disrupted, a<br>high to low transition on this pin indicates a switch on request.<br>When VDD returns, a high to low transition on this pin indicates a<br>switch off request. |

| GP23 (P15) |     | I/O <sub>12t</sub> | CR2B bit7, 6=01: General purpose I/O port 2, bit 3. It can be configured as Keyboard P15 I/O port.                                                                                                                                                                                                                                                            |

| DCDC       |     | INt                | CR2B bit7, 6=11: DCD input of UART C. [W83977AF only]                                                                                                                                                                                                                                                                                                         |

#### **1.3 Serial Port Interface**

| SYMBOL  | PIN | I/O               | FUNCTION                                                                                                                                                                                                                                              |

|---------|-----|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CTSA    | 41  | INt               | Clear To Send is the modem control input.                                                                                                                                                                                                             |

| CTSB    | 48  |                   | The function of these pins can be tested by reading Bit 4 of the handshake status register.                                                                                                                                                           |

| DSRA    | 42  | INt               | Data Set Ready. An active low signal indicates the modem or                                                                                                                                                                                           |

| DSRB    | 49  |                   | data set is ready to establish a communication link and transfer data to the UART.                                                                                                                                                                    |

| RTSA    | 43  | I/O <sub>8t</sub> | UART A Request To Send. An active low signal informs the modem or data set that the controller is ready to send data.                                                                                                                                 |

| HEFRAS  |     |                   | During power-on reset, this pin is pulled down internally and is defined as HEFRAS, which provides the power-on value for CR26 bit 6 (HEFRAS). A 4.7 k $\Omega$ is recommended if intends to pull up. (select 370H as configuration I/O port address) |

| RTSB    | 50  | I/O <sub>8t</sub> | UART B Request To Send. An active low signal informs the modem or data set that the controller is ready to send data.                                                                                                                                 |

| nPENPLL |     |                   | During power-on reset, this pin is pulled down internally and is defined as nPENPLL, which provides the power-on value for CR24 bit 5 (ENPLL) and bit 6. A 4.7 k $\Omega$ is recommended if intends to pull up. (PLL is disabled)                     |

| DTRA    | 44  | I/O <sub>8t</sub> | UART A Data Terminal Ready. An active low signal informs the modem or data set that the controller is ready to communicate.                                                                                                                           |

| PNPCSV  |     |                   | During power-on reset, this pin is pulled down internally and is                                                                                                                                                                                      |

|         |     |                   | defined as PNPCSV, which provides the power-on value for                                                                                                                                                                                              |

|         |     |                   | CR24 bit 0 ( $\overrightarrow{\text{PNPCSV}}$ ). A 4.7 k $\Omega$ is recommended if intends to pull up. (clear the default value of FDC, UARTs, and PTR)                                                                                              |

## PRELIMINARY

### **1.3 Serial Port Interface, continued**

| SYMBOL       | PIN       | I/O               | FUNCTION                                                                                                                                                                                                                      |

|--------------|-----------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DTRB         | 51        | I/O <sub>8t</sub> | UART B Data Terminal Ready. An active low signal informs the modem or data set that controller is ready to communicate.                                                                                                       |

| ENCPNP       |           |                   | During power-on reset, this pin is pulled down internally and is defined as ENCPNP, which provides the power-on value for CR24 bit 1 (ENPNP). A 4.7 k $\Omega$ is recommended if intends to pull up. (enable comply PnP mode) |

| SINA<br>SINB | 45,<br>52 | IN <sub>t</sub>   | Serial Input. Used to receive serial data through the communication link.                                                                                                                                                     |

| SOUTA        | 46        | I/O <sub>8t</sub> | UART A Serial Output. Used to transmit serial data out to the communication link.                                                                                                                                             |

| PENKRC       |           |                   | During power-on reset, this pin is pulled down internally and is defined as PENKRC, which provides the power-on value for CR24 bit 2 (ENKBRTC). A 4.7 k $\Omega$ is recommended if intends to pull up. (enable KBC and RTC)   |

| SOUTB        | 53        | I/O <sub>8t</sub> | UART B Serial Output. Used to transmit serial data out to the communication link.                                                                                                                                             |

| DCDA         | 47        | INt               | Data Carrier Detect. An active low signal indicates the modem                                                                                                                                                                 |

| DCDB         | 54        |                   | or data set has detected a data carrier.                                                                                                                                                                                      |

| RIA          | 65        | INt               | Ring Indicator. An active low signal indicates that a ring signal is                                                                                                                                                          |

| RIB          | 66        |                   | being received from the modem or data set.                                                                                                                                                                                    |

### 1.4 Infrared Interface

| SYMBOL          | PIN | I/O                | FUNCTION                                                                                                                  |

|-----------------|-----|--------------------|---------------------------------------------------------------------------------------------------------------------------|

| IRRX (SINC)     | 37  | IN <sub>cs</sub>   | Infrared Receiver input. It functions as SIN input if UART C is configured as a simple serial port. [W83977AF only]       |

| IRTX<br>(SOUTC) | 38  | OUT <sub>12t</sub> | Infrared Transmitter Output. It functions as SOUT output if UART C is configured as a simple serial port. [W83977AF only] |

| IRRXH           | 39  | I/O <sub>12t</sub> | CR2A bit3, 2=00 (default): High speed IR receiving terminal.                                                              |

| IRSL0           |     | OUT <sub>12t</sub> | CR2A bit3, 2=01: IR module select 0.                                                                                      |

| GP25<br>(GA20)  |     | I/O <sub>12t</sub> | CR2A bit3, 2=10: General purpose I/O port 2, bit 5. It can be configured as GATE A20 (Keyboard P21).                      |

| CTSC            |     | INt                | CR2A bit3, 2=11: CTS input of UART C. [W83977AF only]                                                                     |

| CIRRX           | 40  | INt                | CR2A bit5, 4=00 (default): Consumer IR receiving terminal.                                                                |

| GP24 (P16)      |     | I/O <sub>12t</sub> | CR2A bit5, 4=01: General purpose I/O port 2, bit 4. It can be configured as Keyboard P16 I/O port.                        |

| P13             |     | I/O <sub>12t</sub> | CR2A bit5, 4=10: Keyboard P13 I/O                                                                                         |

# PRELIMINARY

#### 1.5 Multi-Mode Parallel Port

The following pins have alternate functions, which are controlled by CR28 and L3-CRF0.

| SYMBOL | PIN | I/O              | FUNCTION                                                                                                                                                                                                                     |

|--------|-----|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SLCT   | 18  | INt              | PRINTER MODE: SLCT                                                                                                                                                                                                           |

|        |     |                  | An active high input on this pin indicates that the printer is selected. This pin is pulled high internally. Refer to description of the parallel port for definition of this pin in ECP and EPP mode.                       |

|        |     | OD <sub>12</sub> | EXTENSION FDD MODE: WE2                                                                                                                                                                                                      |

|        |     |                  | This pin is for Extension FDD B; its function is the same as the $\overline{\text{WE}}$ pin of FDC.                                                                                                                          |

|        |     | OD <sub>12</sub> | EXTENSION 2FDD MODE: WE2                                                                                                                                                                                                     |

|        |     |                  | This pin is for Extension FDD A and B; it function is the same as the $\overline{\rm WE}$ pin of FDC.                                                                                                                        |

| PE     | 19  | INt              | PRINTER MODE: PE                                                                                                                                                                                                             |

|        |     |                  | An active high input on this pin indicates that the printer has detected the end of the paper. This pin is pulled high internally. Refer to description of the parallel port for definition of this pin in ECP and EPP mode. |

|        |     | OD <sub>12</sub> | EXTENSION FDD MODE: WD2                                                                                                                                                                                                      |

|        |     |                  | This pin is for Extension FDD B; its function is the same as the $\overline{\text{WD}}$ pin of FDC.                                                                                                                          |

|        |     | OD <sub>12</sub> | EXTENSION 2FDD MODE: WD2                                                                                                                                                                                                     |

|        |     |                  | This pin is for Extension FDD A and B; its function is the same as the $\overline{WD}$ pin of FDC.                                                                                                                           |

| BUSY   | 21  | INt              | PRINTER MODE: BUSY                                                                                                                                                                                                           |

|        |     |                  | An active high input indicates that the printer is not ready to receive data. This pin is pulled high internally. Refer to description of the parallel port for definition of this pin in ECP and EPP mode.                  |

|        |     | OD <sub>12</sub> | EXTENSION FDD MODE: MOB2                                                                                                                                                                                                     |

|        |     |                  | This pin is for Extension FDD B; the function of this pin is the same as the $\overline{\text{MOB}}$ pin of FDC.                                                                                                             |

|        |     | $OD_{12}$        | EXTENSION 2FDD MODE: MOB2                                                                                                                                                                                                    |

|        |     |                  | This pin is for Extension FDD A and B; the function of this pin is the same as the $\overline{\text{MOB}}$ pin of FDC.                                                                                                       |

## PRELIMINARY

| SYMBOL | PIN | I/O              | FUNCTION                                                                                                                                                                                                                                              |

|--------|-----|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ACK    | 22  | INt              | PRINTER MODE: ACK                                                                                                                                                                                                                                     |

|        |     |                  | An active low input on this pin indicates that the printer has<br>received data and is ready to accept more data. This pin is<br>pulled high internally. Refer to description of the parallel port for<br>definition of this pin in ECP and EPP mode. |

|        |     | OD <sub>12</sub> | EXTENSION FDD MODE: DSB2                                                                                                                                                                                                                              |

|        |     |                  | This pin is for the Extension FDD B; its functions is the same as the $\overline{\text{DSB}}$ pin of FDC.                                                                                                                                             |

|        |     | OD <sub>12</sub> | EXTENSION 2FDD MODE: DSB2                                                                                                                                                                                                                             |

|        |     |                  | This pin is for Extension FDD A and B; it functions is the same as the $\overline{\text{DSB}}$ pin of FDC.                                                                                                                                            |

| ERR    | 34  | INt              | PRINTER MODE: ERR                                                                                                                                                                                                                                     |

|        |     |                  | An active low input on this pin indicates that the printer has<br>encountered an error condition. This pin is pulled high internally.<br>Refer to description of the parallel port for definition of this pin in<br>ECP and EPP mode.                 |

|        |     | OD <sub>12</sub> | EXTENSION FDD MODE: HEAD2                                                                                                                                                                                                                             |

|        |     |                  | This pin is for Extension FDD B; its function is the same as the $\overline{\text{HEAD}}$ pin of FDC.                                                                                                                                                 |

|        |     | OD <sub>12</sub> | EXTENSION 2FDD MODE: HEAD2                                                                                                                                                                                                                            |

|        |     |                  | This pin is for Extension FDD A and B; its function is the same as the $\overline{\text{HEAD}}$ pin of FDC.                                                                                                                                           |

| SLIN   | 32  | OD <sub>12</sub> | PRINTER MODE: SLIN                                                                                                                                                                                                                                    |

|        |     |                  | Output line for detection of printer selection. This pin is pulled<br>high internally. Refer to description of the parallel port for<br>definition of this pin in ECP and EPP mode.                                                                   |

|        |     | OD <sub>12</sub> | EXTENSION FDD MODE: STEP2                                                                                                                                                                                                                             |

|        |     |                  | This pin is for Extension FDD B; its function is the same as the $\overline{\text{STEP}}$ pin of FDC.                                                                                                                                                 |

|        |     | OD <sub>12</sub> | EXTENSION 2FDD MODE: STEP2                                                                                                                                                                                                                            |

|        |     |                  | This pin is for Extension FDD A and B; its function is the same as the $\overline{\text{STEP}}$ pin of FDC.                                                                                                                                           |

## PRELIMINARY

| SYMBOL | PIN | I/O                | FUNCTION                                                                                                                                                                                                                                  |

|--------|-----|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| INIT   | 33  | OD <sub>12</sub>   | PRINTER MODE: INIT                                                                                                                                                                                                                        |

|        |     |                    | Output line for the printer initialization. This pin is pulled high internally. Refer to description of the parallel port for definition of this pin in ECP and EPP mode.                                                                 |

|        |     | OD <sub>12</sub>   | EXTENSION FDD MODE: DIR2                                                                                                                                                                                                                  |

|        |     |                    | This pin is for Extension FDD B; its function is the same as the $\overline{\text{DIR}}$ pin of FDC.                                                                                                                                      |

|        |     | OD <sub>12</sub>   | EXTENSION 2FDD MODE: DIR2                                                                                                                                                                                                                 |

|        |     |                    | This pin is for Extension FDD A and B; its function is the same as the $\overline{\text{DIR}}$ pin of FDC.                                                                                                                                |

| AFD    | 35  | OD <sub>12</sub>   | PRINTER MODE: AFD                                                                                                                                                                                                                         |

|        |     |                    | An active low output from this pin causes the printer to auto feed<br>a line after a line is printed. This pin is pulled high internally.<br>Refer to description of the parallel port for definition of this pin in<br>ECP and EPP mode. |

|        |     | OD <sub>12</sub>   | EXTENSION FDD MODE: DRVDEN0                                                                                                                                                                                                               |

|        |     | 12                 | This pin is for Extension FDD B; its function is the same as the DRVDEN0 pin of FDC.                                                                                                                                                      |

|        |     | OD <sub>12</sub>   | EXTENSION 2FDD MODE: DRVDEN0                                                                                                                                                                                                              |

|        |     | 0012               | This pin is for Extension FDD A and B; its function is the same as the DRVDEN0 pin of FDC.                                                                                                                                                |

| STB    | 36  | OD <sub>12</sub>   | PRINTER MODE: STB                                                                                                                                                                                                                         |

|        |     |                    | An active low output is used to latch the parallel data into the printer. This pin is pulled high internally. Refer to description of the parallel port for definition of this pin in ECP and EPP mode.                                   |

|        |     | -                  | EXTENSION FDD MODE: This pin is a tri-state output.                                                                                                                                                                                       |

|        |     | -                  | EXTENSION 2FDD MODE: This pin is a tri-state output.                                                                                                                                                                                      |

| PD0    | 31  | I/O <sub>24t</sub> | PRINTER MODE: PD0                                                                                                                                                                                                                         |

|        |     |                    | Parallel port data bus bit 0. Refer to description of the parallel port for definition of this pin in ECP and EPP mode.                                                                                                                   |

|        |     | INt                | EXTENSION FDD MODE: INDEX2                                                                                                                                                                                                                |

|        |     |                    | This pin is for Extension FDD B; the function of this pin is the same as the $\overline{\text{INDEX}}$ pin of FDC. It is pulled high internally.                                                                                          |

|        |     | INt                | EXTENSION 2FDD MODE: INDEX2                                                                                                                                                                                                               |

|        |     |                    | This pin is for Extension FDD A and B; the function of this pin is the same as the $\overline{\text{INDEX}}$ pin of FDC. It is pulled high internally.                                                                                    |

## PRELIMINARY

| SYMBOL | PIN | I/O                | FUNCTION                                                                                                                                                |

|--------|-----|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| PD1    | 30  | I/O <sub>24t</sub> | PRINTER MODE: PD1                                                                                                                                       |

|        |     |                    | Parallel port data bus bit 1. Refer to description of the parallel port for definition of this pin in ECP and EPP mode.                                 |

|        |     | INt                | EXTENSION FDD MODE: TRAK02                                                                                                                              |

|        |     |                    | This pin is for Extension FDD B; the function of this pin is the same as the TRAKO pin of FDC. It is pulled high internally                             |

|        |     | INt                | EXTENSION. 2FDD MODE: TRAK02                                                                                                                            |

|        |     |                    | This pin is for Extension FDD A and B; the function of this pin is the same as the $\overline{TRAK0}$ pin of FDC. It is pulled high internally.         |

| PD2    | 29  | I/O <sub>24t</sub> | PRINTER MODE: PD2                                                                                                                                       |

|        |     |                    | Parallel port data bus bit 2. Refer to description of the parallel port for definition of this pin in ECP and EPP mode                                  |

|        |     | INt                | EXTENSION FDD MODE: WP2                                                                                                                                 |

|        |     |                    | This pin is for Extension FDD B; the function of this pin is the same as the $\overline{WP}$ pin of FDC. It is pulled high internally.                  |

|        |     | INt                | EXTENSION. 2FDD MODE: WP2                                                                                                                               |

|        |     |                    | This pin is for Extension FDD A and B; the function of this pin is the same as the $\overline{WP}$ pin of FDC. It is pulled high internally.            |

| PD3    | 28  | I/O <sub>24t</sub> | PRINTER MODE: PD3                                                                                                                                       |

|        |     |                    | Parallel port data bus bit 3. Refer to description of the parallel port for definition of this pin in ECP and EPP mode.                                 |

|        |     | INt                | EXTENSION FDD MODE: RDATA2                                                                                                                              |

|        |     |                    | This pin is for Extension FDD B; the function of this pin is the same as the $\overline{\text{RDATA}}$ pin of FDC. It is pulled high internally.        |

|        |     | INt                | EXTENSION 2FDD MODE: RDATA2                                                                                                                             |

|        |     |                    | This pin is for Extension FDD A and B; this function of this pin is the same as the $\overline{\text{RDATA}}$ pin of FDC. It is pulled high internally. |

## PRELIMINARY

| SYMBOL | PIN | I/O                | FUNCTION                                                                                                                      |  |

|--------|-----|--------------------|-------------------------------------------------------------------------------------------------------------------------------|--|

| PD4    | 27  | I/O <sub>24t</sub> | PRINTER MODE: PD4                                                                                                             |  |

|        |     |                    | Parallel port data bus bit 4. Refer to description of the parallel port for definition of this pin in ECP and EPP mode.       |  |

|        |     | INt                | EXTENSION FDD MODE: DSKCHG2                                                                                                   |  |

|        |     |                    | This pin is for Extension FDD B; the function of this pin is the same as the DSKCHG pin of FDC. It is pulled high internally. |  |

|        |     | INt                | EXTENSION 2FDD MODE: DSKCHG2                                                                                                  |  |

|        |     |                    | This pin is for Extension FDD A and B; this function of this pin is the same as the DSKCHG pin of FDC. It is pulled high      |  |

|        |     |                    | internally.                                                                                                                   |  |

| PD5    | 26  | I/O <sub>24t</sub> | PRINTER MODE: PD5                                                                                                             |  |

|        |     |                    | Parallel port data bus bit 5. Refer to description of the parallel port for definition of this pin in ECP and EPP mode.       |  |

|        |     | -                  | EXTENSION FDD MODE: This pin is a tri-state output.                                                                           |  |

|        |     | -                  | EXTENSION 2FDD MODE: This pin is a tri-state output.                                                                          |  |

| PD6    | 24  | I/O <sub>24t</sub> | PRINTER MODE: PD6                                                                                                             |  |

|        |     |                    | Parallel port data bus bit 6. Refer to description of the parallel port for definition of this pin in ECP and EPP mode.       |  |

|        |     | -                  | EXTENSION FDD MODE: This pin is a tri-state output.                                                                           |  |

|        |     | OD <sub>24</sub>   | EXTENSION. 2FDD MODE: MOA2                                                                                                    |  |

|        |     |                    | This pin is for Extension FDD A; its function is the same as the $\overline{\text{MOA}}$ pin of FDC.                          |  |

| PD7    | 23  | I/O <sub>24t</sub> | PRINTER MODE: PD7                                                                                                             |  |

|        |     |                    | Parallel port data bus bit 7. Refer to description of the parallel port for definition of this pin in ECP and EPP mode.       |  |

|        |     | -                  | EXTENSION FDD MODE: This pin is a tri-state output.                                                                           |  |

|        |     | OD <sub>24</sub>   | EXTENSION 2FDD MODE: DSA2                                                                                                     |  |

|        |     |                    | This pin is for Extension FDD A; its function is the same as the $\overline{\text{DSA}}$ pin of FDC.                          |  |

# PRELIMINARY

## 1.6 FDC Interface

| SYMBOL          | PIN | I/O              | FUNCTION                                                                                                                                                                                                                                               |  |

|-----------------|-----|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| DRVDEN0         | 2   | OD <sub>24</sub> | Drive Density Select bit 0.                                                                                                                                                                                                                            |  |

| DRVDEN1         | 3   | OD <sub>24</sub> | Drive Density Select bit 1.                                                                                                                                                                                                                            |  |

| GP10            |     |                  | Alternate Function 1: General purpose I/O port 1, bit 0. It can be                                                                                                                                                                                     |  |

| (IRQIN1)<br>P12 |     |                  | configured as an interrupt channel.<br>Alternate Function 2: Keyboard P12 I/O port.                                                                                                                                                                    |  |

|                 |     |                  |                                                                                                                                                                                                                                                        |  |

| DSRC            | _   |                  | Alternate Function 3: DSR input of UART C [W83977AF only]                                                                                                                                                                                              |  |

| HEAD            | 5   | OD <sub>24</sub> | Head select. This open drain output determines which disk drive head is active.                                                                                                                                                                        |  |

|                 |     |                  | Logic 1 = side 0; Logic 0 = side 1                                                                                                                                                                                                                     |  |

| WE              | 9   | OD <sub>24</sub> | Write enable. An open drain output.                                                                                                                                                                                                                    |  |

| WD              | 10  | OD <sub>24</sub> | Write data. This logic low open drain writes precompensation serial data to the selected FDD. An open drain output.                                                                                                                                    |  |

| STEP            | 11  | OD <sub>24</sub> | Step output pulses. This active low open drain output produces a pulse to move the head to another track.                                                                                                                                              |  |

| DIR             | 12  | OD <sub>24</sub> | Direction of the head step motor. An open drain output.                                                                                                                                                                                                |  |

|                 |     |                  | Logic 1 = outward motion; Logic 0 = inward motion                                                                                                                                                                                                      |  |

| MOB             | 13  | OD <sub>24</sub> | Motor B On. When set to 0, this pin enables disk drive 1. This is an open drain output.                                                                                                                                                                |  |

| DSA             | 14  | OD <sub>24</sub> | Drive Select A. When set to 0, this pin enables disk drive A. This is an open drain output.                                                                                                                                                            |  |

| DSB             | 15  | OD <sub>24</sub> | Drive Select B. When set to 0, this pin enables disk drive B. This is an open drain output.                                                                                                                                                            |  |

| MOA             | 16  | OD <sub>24</sub> | Motor A On. When set to 0, this pin enables disk drive 0. This is an open drain output.                                                                                                                                                                |  |

| DSKCHG          | 4   | IN <sub>cs</sub> | Diskette change. This signal is active low at power on and when the diskette is removed. This input pin is pulled up internally by a 1 K $\Omega$ resistor, which can can be disabled by bit 7 of L0-CRF0 (FIPURDWN).                                  |  |

| RDATA           | 6   | IN <sub>cs</sub> | The read data input signal from the FDD. This input pin is pulled up internally by a 1 K $\Omega$ resistor, which can be disabled by bit 7 of L0-CRF0 (FIPURDWN).                                                                                      |  |

| WP              | 7   | IN <sub>cs</sub> | Write protected. This active low Schmitt input from the disk drive indicates that the diskette is write-protected. This input pin is pulled up internally by a 1 K $\Omega$ resistor, which can be disabled by bit 7 of L0-CRF0 (FIPURDWN).            |  |

| TRAK0           | 8   | IN <sub>cs</sub> | Track 0. This Schmitt-triggered input from the disk drive is active low when the head is positioned over the outermost track. This input pin is pulled up internally by a 1 K $\Omega$ resistor, which can be disabled by bit 7 of L0-CRF0 (FIPURDWN). |  |

## PRELIMINARY

### **1.6 FDC Interface, continued**

| SYMBOL | PIN | I/O              | FUNCTION                                                                                                                                                                                                                                                                   |

|--------|-----|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| INDEX  | 17  | IN <sub>cs</sub> | This Schmitt-triggered input from the disk drive is active low when the head is positioned over the beginning of a track marked by an index hole. This input pin is pulled up internally by a 1 K $\Omega$ resistor, which can be disabled by bit 7 of L0-CRF0 (FIPURDWN). |

### 1.7 KBC Interface

| SYMBOL                   | PIN | I/O                 | FUNCTION                                                                                                                                                                               |

|--------------------------|-----|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| KDATA                    | 59  | I/O <sub>16u</sub>  | Keyboard Data                                                                                                                                                                          |

| MDATA                    | 60  | I/O <sub>16u</sub>  | PS2 Mouse Data                                                                                                                                                                         |

| KCLK                     | 67  | I/O <sub>16u</sub>  | Keyboard Clock                                                                                                                                                                         |

| MCLK                     | 68  | I/O <sub>16u</sub>  | PS2 Mouse Clock                                                                                                                                                                        |

| GA20                     | 56  | OUT <sub>12t</sub>  | CR2A bit6= 0 (default): Keyboard GATE A20 (P21) Output.                                                                                                                                |

| GP11<br>(IRQIN2)         |     | I/O <sub>12t</sub>  | CR2A bit6= 1: General purpose I/O port 1, bit 1. It can be configured as an interrupt channel.                                                                                         |

| KBRST                    | 57  | OUT <sub>12t</sub>  | CR2A bit7= 0 (default): Keyboard Reset (P20) Output.                                                                                                                                   |

| GP12<br>(WDTO,<br>IRRX)  |     | I/O <sub>12t</sub>  | CR2A bit7= 1: General purpose I/O port 1, bit 2. It can be configured as watchdog timer output or IRRX (SINC if UART C is used as a simple serial port <i>[W83977AF only]</i> ) input. |

| KBLOCK                   | 58  | IN <sub>16tu</sub>  | CR2B bit0= 0 (default): Keyboard KINH (P17) Input.                                                                                                                                     |

| GP13<br>(PLEDO,<br>IRTX) |     | I/O <sub>16tu</sub> | CR2B bit0= 1: General purpose I/O port 1, bit 3. It can be configured as watchdog timer output or IRTX (SOUTC if UART C is used as a simple serial port [W83977AF only] ) output.      |

## 1.8 RTC Interface

| SYMBOL | PIN | I/O             | FUNCTION                   |

|--------|-----|-----------------|----------------------------|

| VBAT   | 64  |                 | RTC battery voltage input  |

| XTAL1  | 63  | INc             | RTC 32.768Khz Clock Input  |

| XTAL2  | 61  | O <sub>8t</sub> | RTC 32.768Khz Clock Output |

#### **1.9 POWER PINS**

| VCC | 20,55, | +5V power supply for the digital circuitry |  |

|-----|--------|--------------------------------------------|--|

|     | 85,115 |                                            |  |

| GND | 25,62, | Ground                                     |  |

|     | 90,120 |                                            |  |

## PRELIMINARY

### 2.0 ORDERING INSTRUCTION

| PART NO.   | KBC FIRMWARE                      | REMARKS               |

|------------|-----------------------------------|-----------------------|

| W83977F-P  | Phoenix MultiKey/42 <sup>TM</sup> | without FIR, 3rd UART |

| W83977F-A  | AMIKEY-2 <sup>TM</sup>            | without FIR, 3rd UART |

| W83977AF-P | Phoenix MultiKey/42 <sup>TM</sup> | with FIR, 3rd UART    |

| W83977AF-A | AMIKEY-2 <sup>TM</sup>            | with FIR, 3rd UART    |

### 3.0 PACKAGE DIMENSIONS

(128-pin QFP)

PRELIMINARY

#### Headquarters

No. 4, Creation Rd. III Science-Based Industrial Park Hsinchu, Taiwan TEL: 886-35-770066 FAX: 886-35-789467 www: http://www.winbond.com.tw/

Taipei Office

11F, No. 115, Sec. 3, Min-Sheng East Rd.

Taipei, Taiwan

TEL: 886-2-7190505

FAX: 886-2-7197502

TLX: 16485 WINTPE

Note: All data and specifications are subject to change without notice.

Winbond Electronics (H.K.) Ltd. Rm. 803, World Trade Square, Tower II 123 Hoi Bun Rd., Kwun Tong Kowloon, Hong Kong TEL: 852-27516023-7 FAX: 852-27552064 Winbond Electronics (North America) Corp. 2730 Orchard Parkway San Jose, CA 95134 U.S.A. TEL: 1-408-9436666 FAX: 1-408-9436668

Publication Release Date: January 1997 Revision 0.50