# **ST-NXP Wireless**

# **IMPORTANT NOTICE**

Dear customer,

As from August 2<sup>nd</sup> 2008, the wireless operations of NXP have moved to a new company, ST-NXP Wireless.

As a result, the following changes are applicable to the attached document.

- Company name Philips Semiconductors is replaced with ST-NXP Wireless.

- Copyright the copyright notice at the bottom of each page "© Koninklijke Philips Electronics N.V. 200x. All rights reserved", shall now read: "© ST-NXP Wireless 200x All rights reserved".

- Web site <a href="http://www.semiconductors.philips.com">http://www.semiconductors.philips.com</a> is replaced with <a href="http://www.stnwireless.com">http://www.stnwireless.com</a>

- Contact information the list of sales offices previously obtained by sending an email to <u>sales.addresses@www.semiconductors.philips.com</u>, is now found at <a href="http://www.stnwireless.com">http://www.stnwireless.com</a> under Contacts.

If you have any questions related to the document, please contact our nearest sales office. Thank you for your cooperation and understanding.

ST-NXP Wireless

**ST-NXP Wireless**

# 1. General description

The ISP1181A is a Universal Serial Bus (USB) peripheral controller that complies with *Universal Serial Bus Specification Rev. 2.0*, supporting data transfer at full-speed (12 Mbit/s). It provides full-speed USB communication capacity to microcontroller or microprocessor-based systems. The ISP1181A communicates with the system's microcontroller or microprocessor through a high-speed general-purpose parallel interface.

The ISP1181A supports fully autonomous, multi-configurable Direct Memory Access (DMA) operation.

The modular approach to implementing a USB peripheral controller allows the designer to select the optimum system microcontroller from the wide variety available. The ability to reuse existing architecture and firmware investments shortens development time, eliminates risks and reduces costs. The result is fast and efficient development of the most cost-effective USB peripheral solution.

The ISP1181A is ideally suited for application in many personal computer peripherals such as printers, communication devices, scanners, external mass storage (Zip® drive) devices and digital still cameras. It offers an immediate cost reduction for applications that currently use SCSI implementations.

#### 2. Features

- Complies with Universal Serial Bus Specification Rev. 2.0 and most Device Class specifications

- Supports data transfer at full-speed (12 Mbit/s)

- High performance USB peripheral controller with integrated Serial Interface Engine (SIE), FIFO memory, transceiver and 3.3 V voltage regulator

- High speed (11.1 Mbyte/s or 90 ns read/write cycle) parallel interface

- Fully autonomous and multi-configuration DMA operation

- Up to 14 programmable USB endpoints with 2 fixed control IN/OUT endpoints

- Integrated physical 2462 bytes of multi-configuration FIFO memory

- Endpoints with double buffering to increase throughput and ease real-time data transfer

- Seamless interface with most microcontrollers/microprocessors

- Bus-powered capability with low power consumption and low 'suspend' current

- 6 MHz crystal oscillator input with integrated PLL for low EMI

- Controllable LazyClock (100 kHz ± 50 %) output during 'suspend'

- Software controlled connection to the USB bus (SoftConnect™)

- Good USB connection indicator that blinks with traffic (GoodLink™)

#### Full-speed USB peripheral controller

- Clock output with programmable frequency (up to 48 MHz)

- Complies with the ACPI<sup>TM</sup>, OnNow<sup>TM</sup> and USB power management requirements

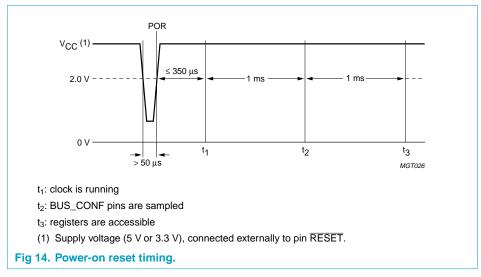

- Internal power-on and low-voltage reset circuit, with possibility of a software reset

- Operation over the extended USB bus voltage range (4.0 V to 5.5 V) with 5 V tolerant I/O pads

- Operating temperature range -40 °C to +85 °C

- Full-scan design with high fault coverage

- Available in TSSOP48 and HVQFN48 packages.

# 3. Applications

- Personal Digital Assistant (PDA)

- Digital camera

- Communication device, for example:

- Router

- Modem

- Mass storage device, for example:

- Zip drive

- Printer

- Scanner.

# 4. Ordering information

**Table 1: Ordering information**

| Type number | Package |                                                                                                            |          |

|-------------|---------|------------------------------------------------------------------------------------------------------------|----------|

|             | Name    | Description                                                                                                | Version  |

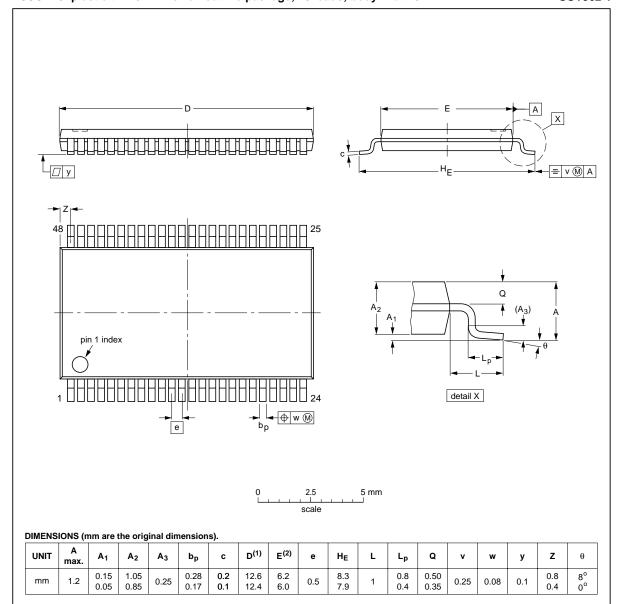

| ISP1181ADGG | TSSOP48 | Plastic thin shrink small outline package; 48 leads; body width 6.1 mm                                     | SOT362-1 |

| ISP1181ABS  | HVQFN48 | Plastic thermal enhanced very thin quad flat package; no leads; 48 terminals; body $7\times7\times0.85$ mm | SOT619-2 |

# Full-speed USB peripheral controller

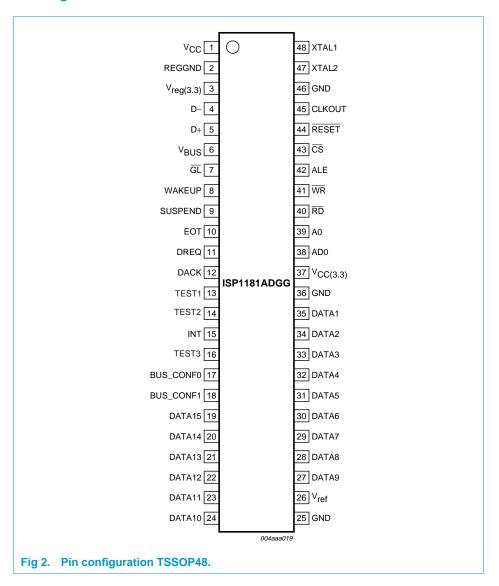

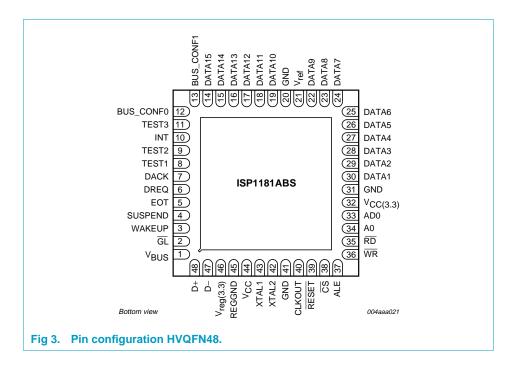

# 6. Pinning information

# 6.1 Pinning

Downloaded from Elcodis.com electronic components distributor

# Full-speed USB peripheral controller

# 6.2 Pin description

Table 2: Pin description

| Symbol <sup>[1]</sup> | Pin     |         | Туре | Description                                                                                                                                                                                                                       |

|-----------------------|---------|---------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                       | TSSOP48 | HVQFN48 |      |                                                                                                                                                                                                                                   |

| V <sub>CC</sub>       | 1       | 44      | -    | supply voltage (3.3 V or 5.0 V)                                                                                                                                                                                                   |

| REGGND                | 2       | 45      | -    | voltage regulator ground supply                                                                                                                                                                                                   |

| V <sub>reg(3.3)</sub> | 3       | 46      | -    | regulated supply voltage (3.3 V $\pm$ 10 %) from internal regulator; used to connect decoupling capacitor and pull-up resistor on D+ line;                                                                                        |

|                       |         |         |      | <b>Remark:</b> Cannot be used to supply external devices.                                                                                                                                                                         |

| D-                    | 4       | 47      | AI/O | USB D- connection (analog)                                                                                                                                                                                                        |

| D+                    | 5       | 48      | AI/O | USB D+ connection (analog)                                                                                                                                                                                                        |

| $V_{BUS}$             | 6       | 1       | I    | V <sub>BUS</sub> sensing input                                                                                                                                                                                                    |

| GL                    | 7       | 2       | 0    | GoodLink LED indicator output (open-drain, 8 mA); the LED is default ON, blinks OFF upon USB traffic; to connect an LED use a series resistor of 470 $\Omega$ (V <sub>CC</sub> = 5.0 V) or 330 $\Omega$ (V <sub>CC</sub> = 3.3 V) |

| WAKEUP                | 8       | 3       | I    | wake-up input (edge triggered,<br>LOW to HIGH); generates a remote<br>wake-up from 'suspend' state                                                                                                                                |

| SUSPEND               | 9       | 4       | 0    | 'suspend' state indicator output (4 mA);<br>used as power switch control output (active<br>LOW) for powered-off application                                                                                                       |

9397 750 13959

# Full-speed USB peripheral controller

Table 2:

Pin description...continued

| Table 2: Pin          | description | continued |      |                                                                                                                                                         |

|-----------------------|-------------|-----------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| Symbol <sup>[1]</sup> | Pin         |           | Туре | Description                                                                                                                                             |

|                       | TSSOP48     | HVQFN48   |      |                                                                                                                                                         |

| EOT                   | 10          | 5         | I    | End-Of-Transfer input (programmable polarity, see Table 21); used by the DMA controller to force the end of a DMA transfer to the ISP1181A              |

| DREQ                  | 11          | 6         | 0    | DMA request output (4 mA; programmable polarity, see Table 21); signals to the DMA controller that the ISP1181A wants to start a DMA transfer           |

| DACK                  | 12          | 7         | I    | DMA acknowledge input (programmable polarity, see Table 21); used by the DMA controller to signal the start of a DMA transfer requested by the ISP1181A |

| TEST1                 | 13          | 8         | I    | test input; this pin must be connected to $V_{CC}$ via an external 10 $k\Omega$ resistor                                                                |

| TEST2                 | 14          | 9         | I    | test input; this pin must be connected to $V_{CC}$ via an external 10 $k\Omega$ resistor                                                                |

| INT                   | 15          | 10        | 0    | interrupt output; programmable polarity (active HIGH or LOW) and signalling (level or pulse); see Table 21                                              |

| TEST3                 | 16          | 11        | 0    | test output; this pin is used for test purposes only                                                                                                    |

| BUS_CONF0             | 17          | 12        | I    | bus configuration selector; see Table 3                                                                                                                 |

| BUS_CONF1             | 18          | 13        | I    | bus configuration selector; see Table 3                                                                                                                 |

| DATA15                | 19          | 14        | I/O  | bit 15 of D[15:0]; bidirectional data line (slew-rate controlled output, 4 mA)                                                                          |

| DATA14                | 20          | 15        | I/O  | bit 14 of D[15:0]; bidirectional data line (slew-rate controlled output, 4 mA)                                                                          |

| DATA13                | 21          | 16        | I/O  | bit 13 of D[15:0]; bidirectional data line (slew-rate controlled output, 4 mA)                                                                          |

| DATA12                | 22          | 17        | I/O  | bit 12 of D[15:0]; bidirectional data line (slew-rate controlled output, 4 mA)                                                                          |

| DATA11                | 23          | 18        | I/O  | bit 11 of D[15:0]; bidirectional data line (slew-rate controlled output, 4 mA)                                                                          |

| DATA10                | 24          | 19        | I/O  | bit 10 of D[15:0]; bidirectional data line (slew-rate controlled output, 4 mA)                                                                          |

| GND                   | 25          | 20        | -    | ground supply                                                                                                                                           |

| V <sub>ref</sub>      | 26          | 21        | -    | I/O pin reference voltage (3.3 V); no connection if $V_{CC} = 5.0 \text{ V}$                                                                            |

| DATA9                 | 27          | 22        | I/O  | bit 9 of D[15:0]; bidirectional data line (slew-rate controlled output, 4 mA)                                                                           |

| DATA8                 | 28          | 23        | I/O  | bit 8 of D[15:0]; bidirectional data line (slew-rate controlled output, 4 mA)                                                                           |

| DATA7                 | 29          | 24        | I/O  | bit 7 of D[15:0]; bidirectional data line (slew-rate controlled output, 4 mA)                                                                           |

| DATA6                 | 30          | 25        | I/O  | bit 6 of D[15:0]; bidirectional data line (slew-rate controlled output, 4 mA)                                                                           |

9397 750 13959

# Full-speed USB peripheral controller

Table 2:

Pin description...continued

| Symbol <sup>[1]</sup> | Pin     |         | Туре | Description                                                                                                                                                                                                                               |

|-----------------------|---------|---------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                       | TSSOP48 | HVQFN48 |      |                                                                                                                                                                                                                                           |

| DATA5                 | 31      | 26      | I/O  | bit 5 of D[15:0]; bidirectional data line (slew-rate controlled output, 4 mA)                                                                                                                                                             |

| DATA4                 | 32      | 27      | I/O  | bit 4 of D[15:0]; bidirectional data line (slew-rate controlled output, 4 mA)                                                                                                                                                             |

| DATA3                 | 33      | 28      | I/O  | bit 3 of D[15:0]; bidirectional data line (slew-rate controlled output, 4 mA)                                                                                                                                                             |

| DATA2                 | 34      | 29      | I/O  | bit 2 of D[15:0]; bidirectional data line (slew-rate controlled output, 4 mA)                                                                                                                                                             |

| DATA1                 | 35      | 30      | I/O  | bit 1 of D[15:0]; bidirectional data line (slew-rate controlled output, 4 mA)                                                                                                                                                             |

| GND                   | 36      | 31      | -    | ground supply                                                                                                                                                                                                                             |

| V <sub>CC(3.3)</sub>  | 37      | 32      | -    | supply voltage (3.0 V to 3.6 V); leave this pin unconnected when using $V_{CC}$ = 5.0 V                                                                                                                                                   |

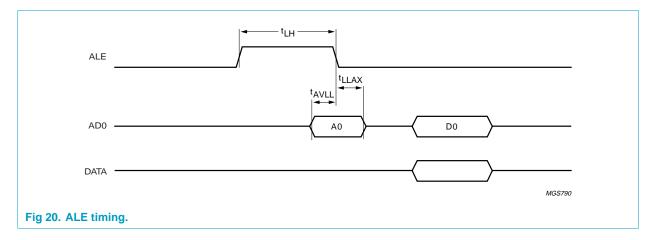

| AD0                   | 38      | 33      | I/O  | multiplexed bidirectional address and data line; represents address A0 or bit 0 of D[15:0] in conjunction with input ALE; level-sensitive input or slew-rate controlled output (4 mA)                                                     |

|                       |         |         |      | Address phase: a HIGH-to-LOW transition on input ALE latches the level on this pin as address A0 (1 = command, 0 = data)                                                                                                                  |

|                       |         |         |      | <b>Data phase</b> : during reading this pin outputs bit D[0]; during writing the level on this pin is latched as bit D[0]                                                                                                                 |

| A0                    | 39      | 34      | I    | address input; selects command (A0 = 1) or data (A0 = 0); in a multiplexed address/data bus configuration this pin is not used and must be tied LOW (connect to GND)                                                                      |

| RD                    | 40      | 35      | I    | read strobe input                                                                                                                                                                                                                         |

| WR                    | 41      | 36      | I    | write strobe input                                                                                                                                                                                                                        |

| ALE                   | 42      | 37      | I    | address latch enable input; a HIGH-to-LOW transition latches the level on pin AD0 as address information in a multiplexed address/data bus configuration; must be tied LOW (connect to GND) for a separate address/data bus configuration |

| CS                    | 43      | 38      | I    | chip select input                                                                                                                                                                                                                         |

| RESET                 | 44      | 39      | I    | reset input (Schmitt trigger); a LOW level produces an asynchronous reset; connect to $V_{CC}$ for power-on reset (internal POR circuit)                                                                                                  |

| CLKOUT                | 45      | 40      | 0    | programmable clock output (2 mA)                                                                                                                                                                                                          |

# Full-speed USB peripheral controller

Table 2:

Pin description...continued

| Symbol <sup>[1]</sup> | Pin     |         | Туре | Description                                                                                                                                              |

|-----------------------|---------|---------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

|                       | TSSOP48 | HVQFN48 |      |                                                                                                                                                          |

| GND                   | 46      | 41      | -    | ground supply                                                                                                                                            |

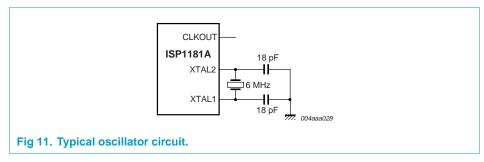

| XTAL2                 | 47      | 42      | 0    | crystal oscillator output (6 MHz); connect a fundamental parallel-resonant crystal; leave this pin open when using an external clock source on pin XTAL1 |

| XTAL1                 | 48      | 43      | I    | crystal oscillator input (6 MHz); connect a<br>fundamental parallel-resonant crystal or an<br>external clock source (leave pin XTAL2<br>unconnected)     |

<sup>[1]</sup> Symbol names with an overscore (for example,  $\overline{NAME}$ ) represent active LOW signals.

#### Full-speed USB peripheral controller

# 7. Functional description

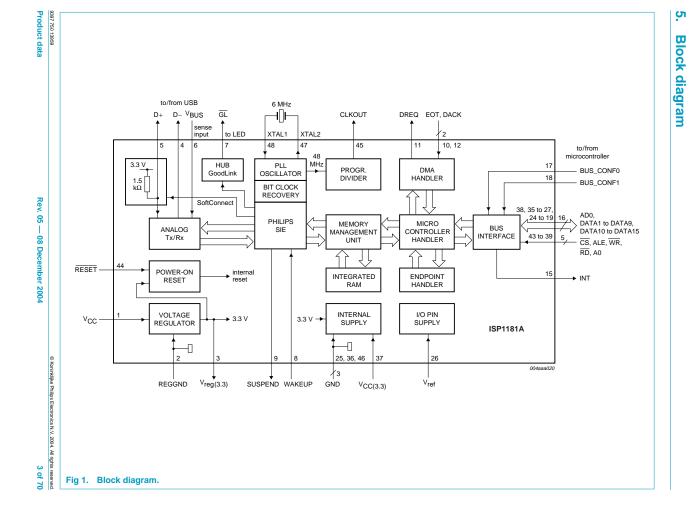

The ISP1181A is a full-speed USB peripheral controller with up to 14 configurable endpoints. It has a fast general-purpose parallel interface for communication with many types of microcontrollers or microprocessors. It supports different bus configurations (see Table 3) and local DMA transfers of up to 16 bytes per cycle. The block diagram is given in Figure 1.

The ISP1181A has 2462 bytes of internal FIFO memory, which is shared among the enabled USB endpoints. The type and FIFO size of each endpoint can be individually configured, depending on the required packet size. Isochronous and bulk endpoints are double-buffered for increased data throughput.

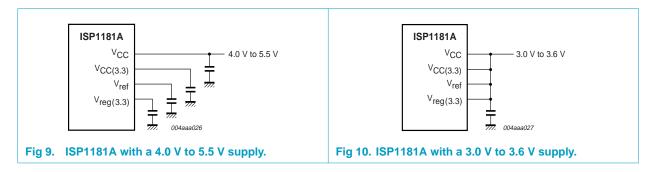

The ISP1181A requires a single supply voltage of 3.3 V or 5.0 V and has an internal 3.3 V voltage regulator for powering the analog USB transceiver. It supports bus-powered operation.

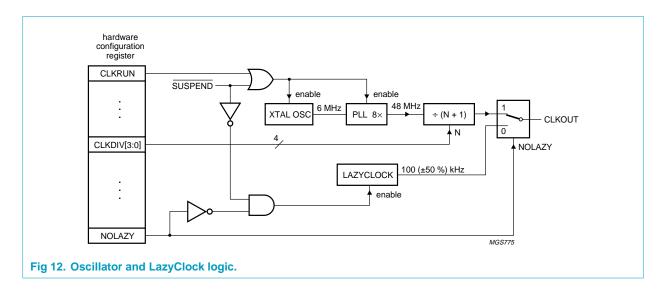

The ISP1181A operates on a 6 MHz oscillator frequency. A programmable clock output is available up to 48 MHz. During 'suspend' state the 100 kHz  $\pm\,50~\%$  LazyClock frequency can be output.

## 7.1 Analog transceiver

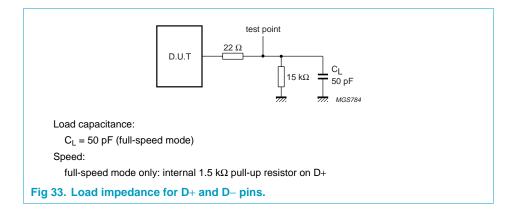

The transceiver is compliant with the *Universal Serial Bus Specification Rev. 2.0 (full speed)*. It interfaces directly with the USB cable through external termination resistors.

## 7.2 Philips Serial Interface Engine (SIE)

The Philips SIE implements the full USB protocol layer. It is completely hardwired for speed and needs no firmware intervention. The functions of this block include: synchronization pattern recognition, parallel/serial conversion, bit (de-)stuffing, CRC checking/generation, Packet IDentifier (PID) verification/generation, address recognition, handshake evaluation/generation.

#### 7.3 Memory Management Unit (MMU) and integrated RAM

The MMU and the integrated RAM provide the conversion between the USB speed (12 Mbit/s bursts) and the parallel interface to the microcontroller (max. 12 Mbyte/s). This allows the microcontroller to read and write USB packets at its own speed.

## 7.4 SoftConnect

The connection to the USB is accomplished by bringing D+ (for full-speed USB peripherals) HIGH through a 1.5 k $\Omega$  pull-up resistor. In the ISP1181A, the 1.5 k $\Omega$  pull-up resistor is integrated on-chip and is not connected to V<sub>CC</sub> by default. The connection is established by a command sent from the external/system microcontroller. This allows the system microcontroller to complete its initialization sequence before deciding to establish connection with the USB. Reinitialization of the USB connection can also be performed without disconnecting the cable.

The ISP1181A will check for USB  $V_{BUS}$  availability before the connection can be established.  $V_{BUS}$  sensing is provided through pin  $V_{BUS}$ .

9397 750 13959

#### Full-speed USB peripheral controller

$V_{BUS}$  sensing prevents the peripheral from wake-up when  $V_{BUS}$  is not present. Without  $V_{BUS}$  sensing, any activity or noise on (D+, D-) might wake up the peripheral. With  $V_{BUS}$  sensing, (D+, D-) is decoupled when no  $V_{BUS}$  is present. Therefore, even if there is noise on the (D+, D-) lines, it is not taken into account. This ensures that the peripheral remains in the suspend state.

**Remark:** Note that the tolerance of the internal resistors is 25 %. This is higher than the 5 % tolerance specified by the USB specification. However, the overall voltage specification for the connection can still be met with a good margin. The decision to make use of this feature lies with the USB equipment designer.

#### 7.5 GoodLink

Indication of a good USB connection is provided at pin  $\overline{GL}$  through GoodLink technology. During enumeration, the LED indicator will blink on momentarily. When the ISP1181A has been successfully enumerated (the peripheral address is set), the LED indicator will remain permanently on. Upon each successful packet transfer (with ACK) to and from the ISP1181A, the LED will blink off for 100 ms. During 'suspend' state, the LED will remain off.

This feature provides a user-friendly indication of the status of the USB peripheral, the connected hub, and the USB traffic. It is a useful field diagnostics tool for isolating faulty equipment. It can therefore help to reduce field support and hotline overhead.

# 7.6 Bit clock recovery

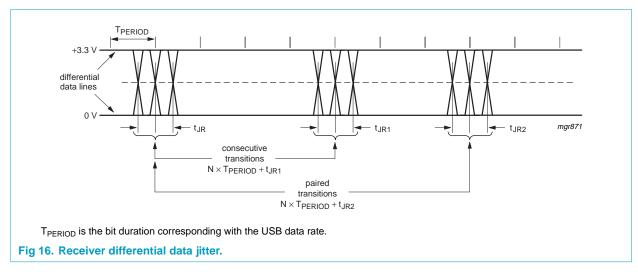

The bit clock recovery circuit recovers the clock from the incoming USB data stream using a 4 times over-sampling principle. It is able to track jitter and frequency drift as specified by the *USB Specification Rev. 2.0*.

#### 7.7 Voltage regulator

A 5 V-to-3.3 V voltage regulator is integrated on-chip to supply the analog transceiver and internal logic. This voltage is available at pin  $V_{\text{reg}(3.3)}$  to supply an external 1.5 k $\Omega$  pull-up resistor on the D+ line. Alternatively, the ISP1181A provides SoftConnect technology via an integrated 1.5 k $\Omega$  pull-up resistor (see Section 7.4).

#### 7.8 PLL clock multiplier

A 6 MHz to 48 MHz clock multiplier Phase-Locked Loop (PLL) is integrated on-chip. This allows for the use of a low-cost 6 MHz crystal, which also minimizes EMI. No external components are required for the operation of the PLL.

#### 7.9 Parallel I/O (PIO) and Direct Memory Access (DMA) interface

A generic PIO interface is defined for speed and ease-of-use. It also allows direct interfacing to most microcontrollers. To a microcontroller, the ISP1181A appears as a memory device with an 8/16-bit data bus and a 1-bit address line. The ISP1181A supports both multiplexed and non-multiplexed address and data buses.

The ISP1181A can also be configured as a DMA slave device to allow more efficient data transfer. One of the 14 endpoint FIFOs may directly transfer data to/from the local shared memory. The DMA interface can be configured independently from the PIO interface.

9397 750 13959 Product data

#### Full-speed USB peripheral controller

# 8. Modes of operation

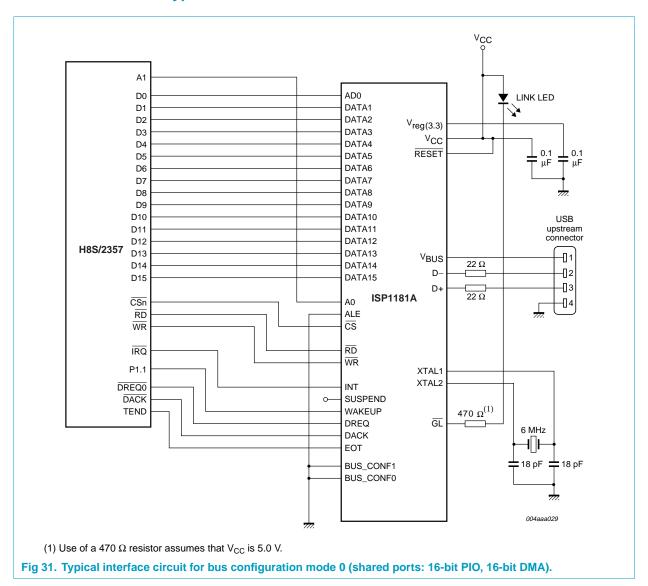

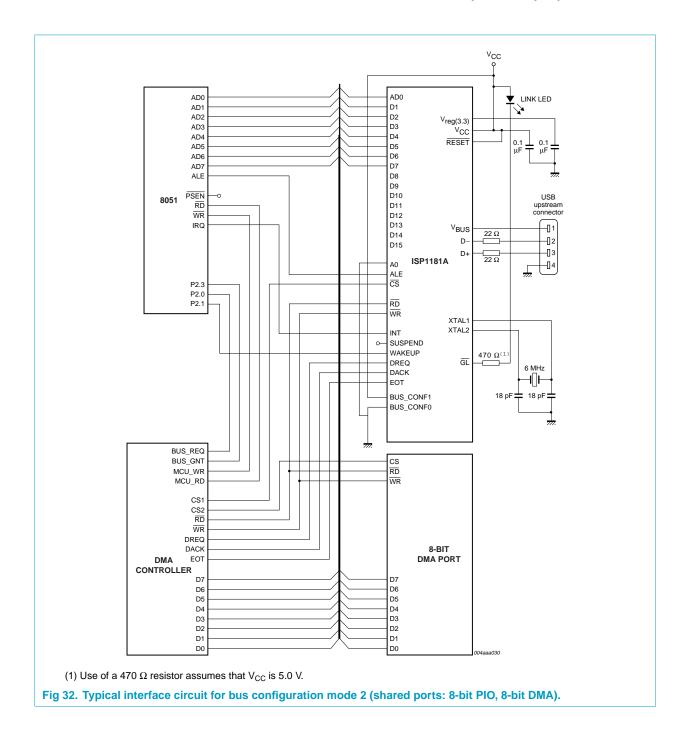

The ISP1181A has four bus configuration modes, selected via pins BUS\_CONF1 and BUS\_CONF0:

Mode 0 16-bit I/O port shared with 16-bit DMA port

Mode 1 reserved

Mode 2 8-bit I/O port shared with 8-bit DMA port

Mode 3 reserved.

The bus configurations for each of these modes are given in Table 3. Typical interface circuits for each mode are given in Section 21.1.

Table 3: Bus configuration modes

| Mode | BUS_CONI | F[1:0] | PIO width    | DMA         | width        | Description                                                                                     |

|------|----------|--------|--------------|-------------|--------------|-------------------------------------------------------------------------------------------------|

|      |          |        |              | DMAWD = 0   | DMAWD = 1    |                                                                                                 |

| 0    | 0        | 0      | D[15:1], AD0 | -           | D[15:1], AD0 | multiplexed address/data on pin AD0;<br>bus is shared by 16-bit I/O port and<br>16-bit DMA port |

| 1    | 0        | 1      | reserved     | reserved    | reserved     | reserved                                                                                        |

| 2    | 1        | 0      | D[7:1], AD0  | D[7:1], AD0 | -            | multiplexed address/data on pin AD0;<br>bus is shared by 8-bit I/O port and 8-bit<br>DMA port   |

| 3    | 1        | 1      | reserved     | reserved    | reserved     | reserved                                                                                        |

# 9. Endpoint descriptions

Each USB peripheral is logically composed of several independent endpoints. An endpoint acts as a terminus of a communication flow between the host and the peripheral. At design time each endpoint is assigned a unique number (endpoint identifier, see Table 4). The combination of the peripheral address (given by the host during enumeration), the endpoint number, and the transfer direction allows each endpoint to be uniquely referenced.

The ISP1181A has 16 endpoints: endpoint 0 (control IN and OUT) plus 14 configurable endpoints, which can be individually defined as interrupt/bulk/isochronous, IN or OUT. Each enabled endpoint has an associated FIFO, which can be accessed either via the parallel I/O interface or via DMA.

#### 9.1 Endpoint access

Table 4 lists the endpoint access modes and programmability. All endpoints support I/O mode access. Endpoints 1 to 14 also support DMA access. FIFO DMA access is selected and enabled via bits EPIDX[3:0] and DMAEN of the DMA Configuration Register. A detailed description of the DMA operation is given in Section 10.

9397 750 13959

#### Full-speed USB peripheral controller

Table 4: Endpoint access and programmability

| Endpoint identifier | FIFO size (bytes) <sup>[1]</sup> | Double<br>buffering | I/O mode access | DMA mode access | Endpoint type  |

|---------------------|----------------------------------|---------------------|-----------------|-----------------|----------------|

| 0                   | 64 (fixed)                       | no                  | yes             | no              | control OUT[2] |

| 0                   | 64 (fixed)                       | no                  | yes             | no              | control IN[2]  |

| 1                   | programmable                     | supported           | supported       | supported       | programmable   |

| 2                   | programmable                     | supported           | supported       | supported       | programmable   |

| 3                   | programmable                     | supported           | supported       | supported       | programmable   |

| 4                   | programmable                     | supported           | supported       | supported       | programmable   |

| 5                   | programmable                     | supported           | supported       | supported       | programmable   |

| 6                   | programmable                     | supported           | supported       | supported       | programmable   |

| 7                   | programmable                     | supported           | supported       | supported       | programmable   |

| 8                   | programmable                     | supported           | supported       | supported       | programmable   |

| 9                   | programmable                     | supported           | supported       | supported       | programmable   |

| 10                  | programmable                     | supported           | supported       | supported       | programmable   |

| 11                  | programmable                     | supported           | supported       | supported       | programmable   |

| 12                  | programmable                     | supported           | supported       | supported       | programmable   |

| 13                  | programmable                     | supported           | supported       | supported       | programmable   |

| 14                  | programmable                     | supported           | supported       | supported       | programmable   |

<sup>[1]</sup> The total amount of FIFO storage allocated to enabled endpoints must not exceed 2462 bytes.

## 9.2 Endpoint FIFO size

The size of the FIFO determines the maximum packet size that the hardware can support for a given endpoint. Only enabled endpoints are allocated space in the shared FIFO storage, disabled endpoints have zero bytes. Table 5 lists the programmable FIFO sizes.

The following bits in the Endpoint Configuration Register (ECR) affect FIFO allocation:

- Endpoint enable bit (FIFOEN)

- Size bits of an enabled endpoint (FFOSZ[3:0])

- Isochronous bit of an enabled endpoint (FFOISO).

**Remark:** Register changes that affect the allocation of the shared FIFO storage among endpoints must **not** be made while valid data is present in any FIFO of the enabled endpoints. Such changes will render **all** FIFO contents **undefined**.

<sup>[2]</sup> IN: input for the USB host (ISP1181A transmits); OUT: output from the USB host (ISP1181A receives). The data flow direction is determined by bit EPDIR in the Endpoint Configuration Register.

# Full-speed USB peripheral controller

Table 5: Programmable FIFO size

| FFOSZ[3:0] | Non-isochronous | Isochronous |

|------------|-----------------|-------------|

| 0000       | 8 bytes         | 16 bytes    |

| 0001       | 16 bytes        | 32 bytes    |

| 0010       | 32 bytes        | 48 bytes    |

| 0011       | 64 bytes        | 64 bytes    |

| 0100       | reserved        | 96 bytes    |

| 0101       | reserved        | 128 bytes   |

| 0110       | reserved        | 160 bytes   |

| 0111       | reserved        | 192 bytes   |

| 1000       | reserved        | 256 bytes   |

| 1001       | reserved        | 320 bytes   |

| 1010       | reserved        | 384 bytes   |

| 1011       | reserved        | 512 bytes   |

| 1100       | reserved        | 640 bytes   |

| 1101       | reserved        | 768 bytes   |

| 1110       | reserved        | 896 bytes   |

| 1111       | reserved        | 1023 bytes  |

Each programmable FIFO can be configured independently via its ECR, but the total physical size of all enabled endpoints (IN plus OUT) must not exceed 2462 bytes.

Table 6 shows an example of a configuration fitting in the maximum available space of 2462 bytes. The total number of logical bytes in the example is 1311. The physical storage capacity used for double buffering is managed by the peripheral hardware and is transparent to the user.

Table 6: Memory configuration example

| Physical size (bytes) | Logical size (bytes) | Endpoint description                           |

|-----------------------|----------------------|------------------------------------------------|

| 64                    | 64                   | control IN (64 byte fixed)                     |

| 64                    | 64                   | control OUT (64 byte fixed)                    |

| 2046                  | 1023                 | double-buffered 1023-byte isochronous endpoint |

| 16                    | 16                   | 16-byte interrupt OUT                          |

| 16                    | 16                   | 16-byte interrupt IN                           |

| 128                   | 64                   | double-buffered 64-byte bulk OUT               |

| 128                   | 64                   | double-buffered 64-byte bulk IN                |

**Product data**

#### Full-speed USB peripheral controller

## 9.3 Endpoint initialization

In response to the standard USB request, Set Interface, the firmware must program all 16 ECRs of the ISP1181A in sequence (see Table 4), whether the endpoints are enabled or not. The hardware will then automatically allocate FIFO storage space.

If all endpoints have been configured successfully, the firmware must return an empty packet to the control IN endpoint to acknowledge success to the host. If there are errors in the endpoint configuration, the firmware must stall the control IN endpoint.

When reset by hardware or via the USB bus, the ISP1181A disables all endpoints and clears all ECRs, except for the control endpoint which is fixed and always enabled.

Endpoint initialization can be done at any time; however, it is valid only after enumeration.

# 9.4 Endpoint I/O mode access

When an endpoint event occurs (a packet is transmitted or received), the associated endpoint interrupt bits (EPn) of the Interrupt Register (IR) will be set by the SIE. The firmware then responds to the interrupt and selects the endpoint for processing.

The endpoint interrupt bit will be cleared by reading the Endpoint Status Register (ESR). The ESR also contains information on the status of the endpoint buffer.

For an OUT (= receive) endpoint, the packet length and packet data can be read from ISP1181A using the Read Buffer command. When the whole packet has been read, the firmware sends a Clear Buffer command to enable the reception of new packets.

For an IN (= transmit) endpoint, the packet length and data to be sent can be written to ISP1181A using the Write Buffer command. When the whole packet has been written to the buffer, the firmware sends a Validate Buffer command to enable data transmission to the host.

#### 9.5 Special actions on control endpoints

Control endpoints require special firmware actions. The arrival of a SETUP packet flushes the IN buffer and disables the Validate Buffer and Clear Buffer commands for the control IN and OUT endpoints. The microcontroller needs to re-enable these commands by sending an Acknowledge Setup command to **both** control endpoints.

This ensures that the last SETUP packet stays in the buffer and that no packets can be sent back to the host until the microcontroller has explicitly acknowledged that it has seen the SETUP packet.

#### Full-speed USB peripheral controller

## 10. DMA transfer

Direct Memory Access (DMA) is a method to transfer data from one location to another in a computer system, without intervention of the central processor (CPU). Many different implementations of DMA exist. The ISP1181A supports two methods:

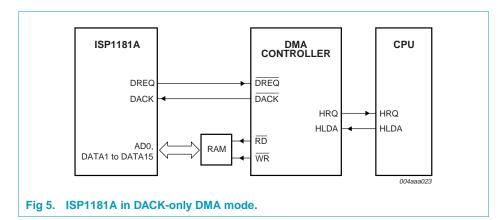

- 8237 compatible mode: based on the DMA subsystem of the IBM personal computers (PC, AT and all its successors and clones); this architecture uses the Intel 8237 DMA controller and has separate address spaces for memory and I/O

- **DACK-only mode**: based on the DMA implementation in some embedded RISC processors, which has a single address space for both memory and I/O.

The ISP1181A supports DMA transfer for all 14 configurable endpoints (see Table 4). Only one endpoint at a time can be selected for DMA transfer. The DMA operation of the ISP1181A can be interleaved with normal I/O mode access to other endpoints.

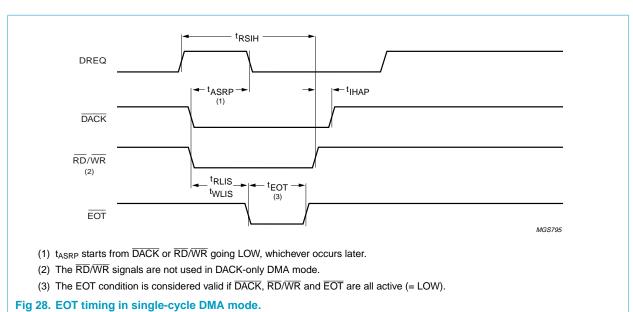

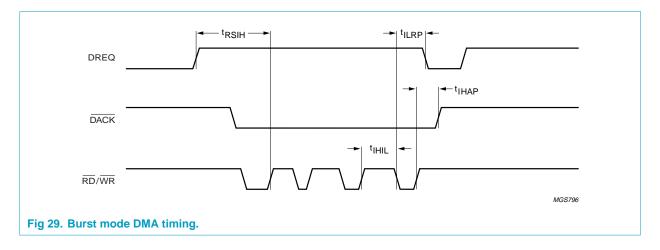

The following features are supported:

- Single-cycle or burst transfers (up to 16 bytes per cycle)

- Programmable transfer direction (read or write)

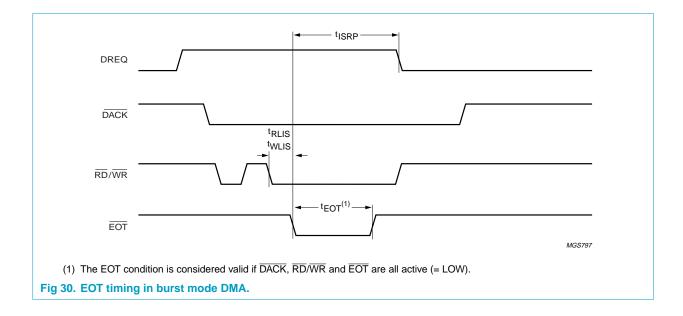

- Multiple End-Of-Transfer (EOT) sources: external pin, internal conditions, short/empty packet

- Programmable signal levels on pins DREQ, DACK and EOT.

# 10.1 Selecting an endpoint for DMA transfer

The target endpoint for DMA access is selected via bits EPDIX[3:0] in the DMA Configuration Register, as shown in Table 7. The transfer direction (read or write) is automatically set by bit EPDIR in the associated ECR, to match the selected endpoint type (OUT endpoint: read; IN endpoint: write).

Asserting input DACK automatically selects the endpoint specified in the DMA Configuration Register, regardless of the current endpoint used for I/O mode access.

Table 7: Endpoint selection for DMA transfer

| Endpoint   | EPIDX[3:0] | Transfer  | direction |

|------------|------------|-----------|-----------|

| identifier |            | EPDIR = 0 | EPDIR = 1 |

| 1          | 0010       | OUT: read | IN: write |

| 2          | 0011       | OUT: read | IN: write |

| 3          | 0100       | OUT: read | IN: write |

| 4          | 0101       | OUT: read | IN: write |

| 5          | 0110       | OUT: read | IN: write |

| 6          | 0111       | OUT: read | IN: write |

| 7          | 1000       | OUT: read | IN: write |

| 8          | 1001       | OUT: read | IN: write |

| 9          | 1010       | OUT: read | IN: write |

| 10         | 1011       | OUT: read | IN: write |

| 11         | 1100       | OUT: read | IN: write |

9397 750 13959

#### Full-speed USB peripheral controller

Table 7: Endpoint selection for DMA transfer...continued

| Endpoint   | EPIDX[3:0] | Transfer  | direction |

|------------|------------|-----------|-----------|

| identifier |            | EPDIR = 0 | EPDIR = 1 |

| 12         | 1101       | OUT: read | IN: write |

| 13         | 1110       | OUT: read | IN: write |

| 14         | 1111       | OUT: read | IN: write |

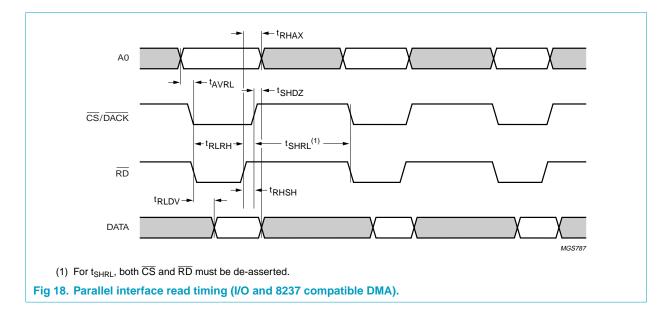

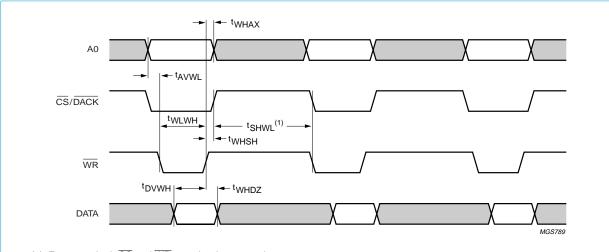

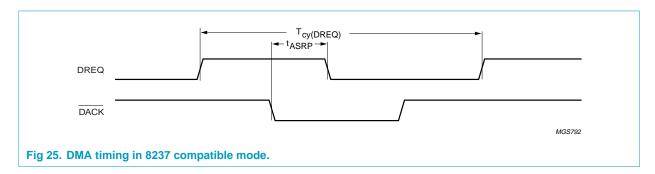

## 10.2 8237 compatible mode

The 8237 compatible DMA mode is selected by clearing bit DAKOLY in the Hardware Configuration Register (see Table 20). The pin functions for this mode are shown in Table 8.

Table 8: 8237 compatible mode: pin functions

| Symbol | Description     | I/O | Function                                    |

|--------|-----------------|-----|---------------------------------------------|

| DREQ   | DMA request     | 0   | ISP1181A requests a DMA transfer            |

| DACK   | DMA acknowledge | I   | DMA controller confirms the transfer        |

| EOT    | end of transfer | I   | DMA controller terminates the transfer      |

| RD     | read strobe     | I   | instructs ISP1181A to put data on the bus   |

| WR     | write strobe    | I   | instructs ISP1181A to get data from the bus |

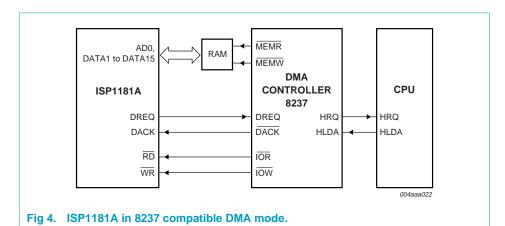

The DMA subsystem of an IBM compatible PC is based on the Intel 8237 DMA controller. It operates as a 'fly-by' DMA controller: the data is not stored in the DMA controller, but it is transferred between an I/O port and a memory address. A typical example of ISP1181A in 8237 compatible DMA mode is given in Figure 4.

The 8237 has two control signals for each DMA channel: DREQ (DMA Request) and DACK (DMA Acknowledge). General control signals are HRQ (Hold Request) and HLDA (Hold Acknowledge). The bus operation is controlled via MEMR (Memory Read), MEMW (Memory Write), IOR (I/O read) and IOW (I/O write).

9397 750 13959

#### Full-speed USB peripheral controller

The following example shows the steps which occur in a typical DMA transfer:

- 1. ISP1181A receives a data packet in one of its endpoint FIFOs; the packet must be transferred to memory address 1234H.

- 2. ISP1181A asserts the DREQ signal requesting the 8237 for a DMA transfer.

- 3. The 8237 asks the CPU to release the bus by asserting the HRQ signal.

- 4. After completing the current instruction cycle, the CPU places the bus control signals (MEMR, MEMW, IOR and IOW) and the address lines in three-state and asserts HLDA to inform the 8237 that it has control of the bus.

- 5. The 8237 now sets its address lines to 1234H and activates the MEMW and IOR control signals.

- 6. The 8237 asserts DACK to inform the ISP1181A that it will start a DMA transfer.

- 7. The ISP1181A now places the byte or word to be transferred on the data bus lines, because its  $\overline{\text{RD}}$  signal was asserted by the 8237.

- 8. The 8237 waits one DMA clock period and then de-asserts MEMW and IOR. This latches and stores the byte or word at the desired memory location. It also informs the ISP1181A that the data on the bus lines has been transferred.

- The ISP1181A de-asserts the DREQ signal to indicate to the 8237 that DMA is no longer needed. In **Single cycle mode** this is done after each byte or word, in **Burst mode** following the last transferred byte or word of the DMA cycle.

- 10. The 8237 de-asserts the DACK output indicating that the ISP1181A must stop placing data on the bus.

- 11. The 8237 places the bus control signals (MEMR, MEMW, IOR and IOW) and the address lines in three-state and de-asserts the HRQ signal, informing the CPU that it has released the bus.

- 12. The CPU acknowledges control of the bus by de-asserting HLDA. After activating the bus control lines (MEMR, MEMW, IOR and IOW) and the address lines, the CPU resumes the execution of instructions.

For a typical bulk transfer the above process is repeated 64 times, once for each byte. After each byte the address register in the DMA controller is incremented and the byte counter is decremented. When using 16-bit DMA, the number of transfers is 32, and address incrementing and byte counter decrementing is done by 2 for each word.

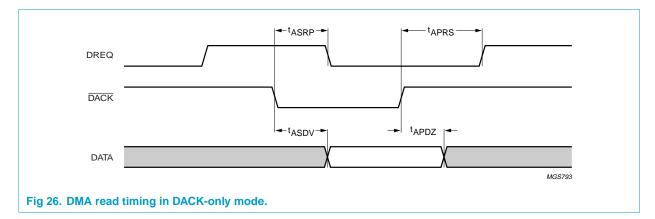

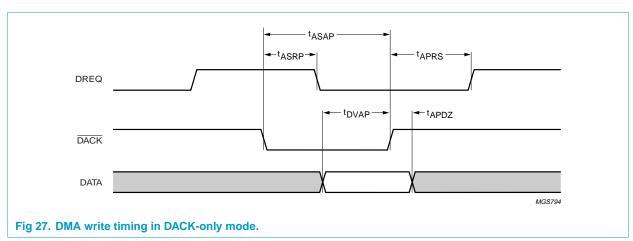

## 10.3 DACK-only mode

The DACK-only DMA mode is selected by setting bit DAKOLY in the Hardware Configuration Register (see Table 20). The pin functions for this mode are shown in Table 9. A typical example of ISP1181A in DACK-only DMA mode is given in Figure 5.

Table 9: DACK-only mode: pin functions

| Symbol | Description     | I/O | Function                                                            |

|--------|-----------------|-----|---------------------------------------------------------------------|

| DREQ   | DMA request     | 0   | ISP1181A requests a DMA transfer                                    |

| DACK   | DMA acknowledge | I   | DMA controller confirms the transfer; also functions as data strobe |

| EOT    | End-Of-Transfer | I   | DMA controller terminates the transfer                              |

| RD     | read strobe     | I   | not used                                                            |

| WR     | write strobe    | I   | not used                                                            |

9397 750 13959 Product data

#### Full-speed USB peripheral controller

In DACK-only mode the ISP1181A uses the DACK signal as data strobe. Input signals  $\overline{\text{RD}}$  and  $\overline{\text{WR}}$  are ignored. This mode is used in CPU systems that have a single address space for memory and I/O access. Such systems have no separate  $\overline{\text{MEMW}}$  and  $\overline{\text{MEMR}}$  signals: the  $\overline{\text{RD}}$  and  $\overline{\text{WR}}$  signals are also used as memory data strobes.

#### 10.4 End-Of-Transfer conditions

#### 10.4.1 Bulk endpoints

A DMA transfer to/from a bulk endpoint can be terminated by any of the following conditions (bit names refer to the DMA Configuration Register, see Table 24):

- An external End-Of-Transfer signal occurs on input EOT

- The DMA transfer completes as programmed in the DMA Counter register (CNTREN = 1)

- A short packet is received on an enabled OUT endpoint (SHORTP = 1)

- DMA operation is disabled by clearing bit DMAEN.

**External EOT:** When reading from an OUT endpoint, an external EOT will stop the DMA operation and **clear any remaining data** in the current FIFO. For a double-buffered endpoint the other (inactive) buffer is not affected.

When writing to an IN endpoint, an EOT will stop the DMA operation and the data packet in the FIFO (even if it is smaller than the maximum packet size) will be sent to the USB host at the next IN token.

**DMA Counter Register:** An EOT from the DMA Counter Register is enabled by setting bit CNTREN in the DMA Configuration Register. The ISP1181A has a 16-bit DMA Counter Register, which specifies the number of bytes to be transferred. When DMA is enabled (DMAEN = 1), the internal DMA counter is loaded with the value from the DMA Counter Register. When the internal counter completes the transfer as programmed in the DMA counter, an EOT condition is generated and the DMA operation stops.

9397 750 13959

#### Full-speed USB peripheral controller

**Short packet:** Normally, the transfer byte count must be set via a control endpoint before any DMA transfer takes place. When a short packet has been enabled as EOT indicator (SHORTP = 1), the transfer size is determined by the presence of a short packet in the data. This mechanism permits the use of a fully autonomous data transfer protocol.

When reading from an OUT endpoint, reception of a short packet at an OUT token will stop the DMA operation after transferring the data bytes of this packet.

Table 10: Summary of EOT conditions for a bulk endpoint

| EOT condition                              | OUT endpoint                                                       | IN endpoint                                                        |

|--------------------------------------------|--------------------------------------------------------------------|--------------------------------------------------------------------|

| EOT input                                  | EOT is active                                                      | EOT is active                                                      |

| DMA Counter Register                       | transfer completes as<br>programmed in the DMA<br>Counter register | transfer completes as<br>programmed in the DMA<br>Counter register |

| Short packet                               | short packet is received and transferred                           | counter reaches zero in the middle of the buffer                   |

| DMAEN bit in DMA<br>Configuration Register | DMAEN = 0 <sup>[1]</sup>                                           | DMAEN = 0 <sup>[1]</sup>                                           |

<sup>[1]</sup> The DMA transfer stops. However, no interrupt is generated.

#### 10.4.2 Isochronous endpoints

A DMA transfer to/from an isochronous endpoint can be terminated by any of the following conditions (bit names refer to the DMA Configuration Register, see Table 24):

- An external End-Of-Transfer signal occurs on input EOT

- The DMA transfer completes as programmed in the DMA Counter register (CNTREN = 1)

- An End-Of-Packet (EOP) signal is detected

- DMA operation is disabled by clearing bit DMAEN.

Table 11: Recommended EOT usage for isochronous endpoints

| EOT condition             | OUT endpoint | IN endpoint |

|---------------------------|--------------|-------------|

| EOT input active          | do not use   | preferred   |

| DMA Counter Register zero | do not use   | preferred   |

| End-Of-Packet             | preferred    | do not use  |

#### Full-speed USB peripheral controller

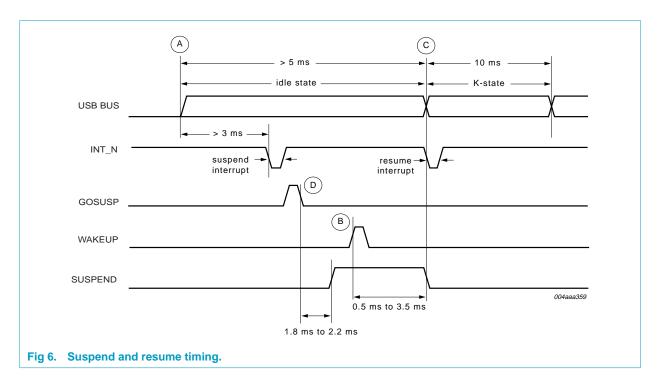

# 11. Suspend and resume

# 11.1 Suspend conditions

The ISP1181A detects a USB suspend status when a constant idle state is present on the USB bus for more than 3 ms.

The bus-powered devices that are suspended must not consume more than 500  $\mu A$  of current. This is achieved by shutting down power to system components or supplying them with a reduced voltage.

The steps leading up to suspend status are as follows:

- 1. On detecting a wakeup-to-suspend transition, the ISP1181A sets bit SUSPND in the Interrupt register. This will generate an interrupt if bit IESUSP in the Interrupt Enable register is set.

- 2. When the firmware detects a suspend condition, it must prepare all system components for the suspend state:

- a. All signals connected to the ISP1181A must enter appropriate states to meet the power consumption requirements of the suspend state.

- b. All input pins of the ISP1181A must have a CMOS LOW or HIGH level.

- 3. In the interrupt service routine, the firmware must check the current status of the USB bus. When bit BUSTATUS in the Interrupt register is logic 0, the USB bus has left the suspend mode and the process must be aborted. Otherwise, the next step can be executed.

- 4. To meet the suspend current requirements for a bus-powered device, the internal clocks must be switched off by clearing bit CLKRUN in the Hardware Configuration register.

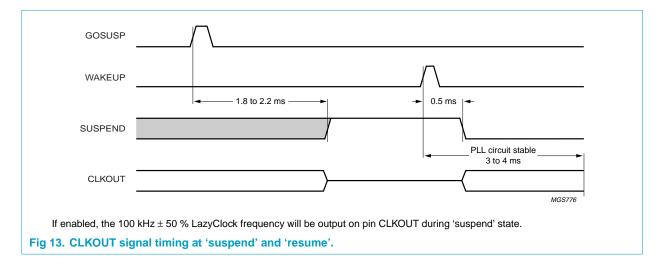

- 5. When the firmware has set and cleared bit GOSUSP in the Mode register, the ISP1181A enters the suspend state. In powered-off application, the ISP1181A asserts output SUSPEND and switches off the internal clocks after 2 ms.

Figure 6 shows a typical timing diagram.

#### Full-speed USB peripheral controller

#### In Figure 6:

- A: indicates the point at which the USB bus enters the idle state.

- **B**: indicates resume condition, which can be a 20 ms K-state on the USB bus, a HIGH level on pin WAKEUP, or a LOW level on pin  $\overline{\text{CS}}$ .

- C: indicates remote wake-up. The ISP1181A will drive a K-state on the USB bus for 10 ms after pin WAKEUP goes HIGH or pin CS goes LOW.

- **D**: after detecting the suspend interrupt, set and clear bit GOSUSP in the Mode register.

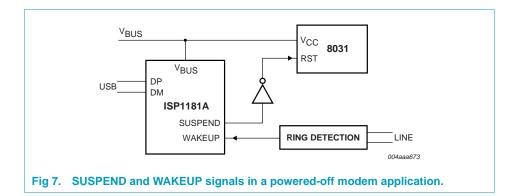

# 11.1.1 Powered-off application

Figure 7 shows a typical bus-powered modem application using the ISP1181A. The SUSPEND output switches off power to the microcontroller and other external circuits during the suspend state. The ISP1181A is woken up through the USB bus (global resume) or by the ring detection circuit on the telephone line.

#### Full-speed USB peripheral controller

#### 11.2 Resume conditions

A wake-up from the suspend state is initiated either by the USB host or by the application:

- USB host: drives a K-state on the USB bus (global resume)

- Application: remote wake-up through a HIGH level on input WAKEUP or a LOW level on input <del>CS</del> (if enabled using bit WKUPCS in the Hardware Configuration register). Wake-up on <del>CS</del> will work only if V<sub>BUS</sub> is present.

The steps of a wake-up sequence are as follows:

- 1. The internal oscillator and the PLL multiplier are re-enabled. When stabilized, the clock signals are routed to all internal circuits of the ISP1181A.

- The SUSPEND output is deasserted, and bit RESUME in the Interrupt register is set. This will generate an interrupt if bit IERESUME in the Interrupt Enable register is set.

- 3. Maximum 15 ms after starting the wake-up sequence, the ISP1181A resumes its normal functionality.

- In case of a remote wake-up, the ISP1181A drives a K-state on the USB bus for 10 ms.

- 5. Following the deassertion of output SUSPEND, the application restores itself and other system components to the normal operating mode.

- After wake-up, the internal registers of the ISP1181A are write-protected to prevent corruption by inadvertent writing during power-up of external components. The firmware must send an Unlock Device command to the ISP1181A to restore its full functionality.

#### 11.3 Control bits in suspend and resume

Table 12: Summary of control bits

| Register  | Bit      | Function                                                                     |

|-----------|----------|------------------------------------------------------------------------------|

| Interrupt | SUSPND   | a transition from awake to the suspend state was detected                    |

|           | BUSTATUS | monitors USB bus status (logic 1 = suspend); used when interrupt is serviced |

|           | RESUME   | a transition from suspend to the resume state was detected                   |

9397 750 13959

#### Full-speed USB peripheral controller

Table 12: Summary of control bits...continued

| Register         | Bit      | Function                                                                     |

|------------------|----------|------------------------------------------------------------------------------|

| Interrupt Enable | IESUSP   | enables output INT to signal the suspend state                               |

|                  | IERESUME | enables output INT to signal the resume state                                |

| Mode             | SOFTCT   | enables SoftConnect pull-up resistor to USB bus                              |

|                  | GOSUSP   | a HIGH-to-LOW transition enables the suspend state                           |

| Hardware         | EXTPUL   | selects internal (SoftConnect) or external pull-up resistor                  |

| Configuration    | WKUPCS   | enables wake-up on LOW level of input $\overline{\text{CS}}$                 |

|                  | PWROFF   | selects powered-off mode during the suspend state                            |

| Unlock           | all      | sending data AA37H unlocks the internal registers for writing after a resume |

# 12. Commands and registers

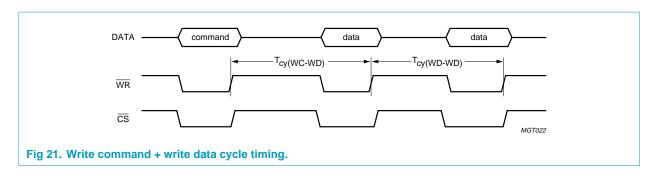

The functions and registers of ISP1181A are accessed via commands, which consist of a command code followed by optional data bytes (read or write action). An overview of the available commands and registers is given in Table 13.

A complete access consists of two phases:

- 1. **Command phase**: when address bit A0 = 1, the ISP1181A interprets the data on the lower byte of the bus bits D[7:0] as a command code. Commands without a data phase are executed immediately.

- Data phase (optional): when address bit A0 = 0, the ISP1181A transfers the

data on the bus to or from a register or endpoint FIFO. Multi-byte registers are

accessed least significant byte/word first.

The following applies for register or FIFO access in 16-bit bus mode:

- The upper byte (bits D15 to D8) in command phase or the undefined byte in data phase are ignored.

- The access of registers is word-aligned: byte access is not allowed.

- If the packet length is odd, the upper byte of the last word in an IN endpoint buffer is **not** transmitted to the host. When reading from an OUT endpoint buffer, the upper byte of the last word must be ignored by the firmware. The packet length is stored in the first 2 bytes of the endpoint buffer.

Table 13: Command and register summary

| Name                                         | Destination                                      | Code (Hex) | Transaction <sup>[1]</sup>     |

|----------------------------------------------|--------------------------------------------------|------------|--------------------------------|

| Initialization commands                      |                                                  |            |                                |

| Write Control OUT Configuration              | Endpoint Configuration Register endpoint 0 OUT   | 20         | write 1 byte <sup>[2]</sup>    |

| Write Control IN Configuration               | Endpoint Configuration Register endpoint 0 IN    | 21         | write 1 byte <sup>[2]</sup>    |

| Write Endpoint n Configuration (n = 1 to 14) | Endpoint Configuration Register endpoint 1 to 14 | 22 to 2F   | write 1 byte <sup>[2][3]</sup> |

| Read Control OUT Configuration               | Endpoint Configuration Register endpoint 0 OUT   | 30         | read 1 byte <sup>[2]</sup>     |

9397 750 13959

# Full-speed USB peripheral controller

Table 13: Command and register summary...continued

| Name                                        | Destination                                                  | Code (Hex) | Transaction <sup>[1]</sup>       |

|---------------------------------------------|--------------------------------------------------------------|------------|----------------------------------|

| Read Control IN Configuration               | Endpoint Configuration Register endpoint 0 IN                | 31         | read 1 byte <sup>[2]</sup>       |

| Read Endpoint n Configuration (n = 1 to 14) | Endpoint Configuration Register endpoint 1 to 14             | 32 to 3F   | read 1 byte <sup>[2]</sup>       |

| Write/Read Device Address                   | Address Register                                             | B6/B7      | write/read 1 byte <sup>[2]</sup> |

| Write/Read Mode Register                    | Mode Register                                                | B8/B9      | write/read 1 byte <sup>[2]</sup> |

| Write/Read Hardware Configuration           | Hardware Configuration Register                              | BA/BB      | write/read 2 bytes               |

| Write/Read Interrupt Enable<br>Register     | Interrupt Enable Register                                    | C2/C3      | write/read 4 bytes               |

| Write/Read DMA Configuration                | DMA Configuration Register                                   | F0/F1      | write/read 2 bytes               |

| Write/Read DMA Counter                      | DMA Counter Register                                         | F2/F3      | write/read 2 bytes               |

| Reset Device                                | resets all registers                                         | F6         | -                                |

| Data flow commands                          |                                                              |            |                                  |

| Write Control OUT Buffer                    | illegal: endpoint is read-only                               | (00)       | -                                |

| Write Control IN Buffer                     | FIFO endpoint 0 IN                                           | 01         | N ≤ 64 bytes                     |

| Write Endpoint n Buffer                     | FIFO endpoint 1 to 14                                        | 02 to 0F   | isochronous: $N \le 1023$ bytes  |

| (n = 1 to 14)                               | (IN endpoints only)                                          |            | interrupt/bulk: $N \le 64$ bytes |

| Read Control OUT Buffer                     | FIFO endpoint 0 OUT                                          | 10         | N ≤ 64 bytes                     |

| Read Control IN Buffer                      | illegal: endpoint is write-only                              | (11)       | -                                |

| Read Endpoint n Buffer                      | FIFO endpoint 1 to 14                                        | 12 to 1F   | isochronous:                     |

| (n = 1 to 14)                               | (OUT endpoints only)                                         |            | N ≤ 1023 bytes <sup>[4]</sup>    |

| 0. 10                                       | 5 1 1 1 0 OUT                                                |            | interrupt/bulk: N ≤ 64 bytes     |

| Stall Control OUT Endpoint                  | Endpoint 0 OUT                                               | 40         | -                                |

| Stall Control IN Endpoint                   | Endpoint 0 IN                                                | 41         | -                                |

| Stall Endpoint n<br>(n = 1 to 14)           | Endpoint 1 to 14                                             | 42 to 4F   | -                                |

| Read Control OUT Status                     | Endpoint Status Register endpoint 0 OUT                      | 50         | read 1 byte <sup>[2]</sup>       |

| Read Control IN Status                      | Endpoint Status Register endpoint 0 IN                       | 51         | read 1 byte <sup>[2]</sup>       |

| Read Endpoint n Status<br>(n = 1 to 14)     | Endpoint Status Register n endpoint 1 to 14                  | 52 to 5F   | read 1 byte <sup>[2]</sup>       |

| Validate Control OUT Buffer                 | illegal: IN endpoints only[5]                                | (60)       | -                                |

| Validate Control IN Buffer                  | FIFO endpoint 0 IN <sup>[5]</sup>                            | 61         | _[3]                             |

| Validate Endpoint n Buffer (n = 1 to 14)    | FIFO endpoint 1 to 14<br>(IN endpoints only) <sup>[5]</sup>  | 62 to 6F   | _[3]                             |

| Clear Control OUT Buffer                    | FIFO endpoint 0 OUT                                          | 70         | _[3]                             |

| Clear Control IN Buffer                     | illegal <sup>[6]</sup>                                       | (71)       | -                                |

| Clear Endpoint n Buffer (n = 1 to 14)       | FIFO endpoint 1 to 14<br>(OUT endpoints only) <sup>[6]</sup> | 72 to 7F   | [3]                              |

| Unstall Control OUT Endpoint                | Endpoint 0 OUT                                               | 80         | -                                |

| Unstall Control IN Endpoint                 | Endpoint 0 IN                                                | 81         | -                                |

9397 750 13959

#### Full-speed USB peripheral controller

Table 13: Command and register summary...continued

| Name                                     | Destination                                       | Code (Hex) | Transaction <sup>[1]</sup> |

|------------------------------------------|---------------------------------------------------|------------|----------------------------|

| Unstall Endpoint n<br>(n = 1 to 14)      | Endpoint 1 to 14                                  | 82 to 8F   | -                          |

| Check Control OUT Status <sup>[7]</sup>  | Endpoint Status Image Register endpoint 0 OUT     | D0         | read 1 byte <sup>[2]</sup> |

| Check Control IN Status <sup>[7]</sup>   | Endpoint Status Image Register endpoint 0 IN      | D1         | read 1 byte <sup>[2]</sup> |

| Check Endpoint n Status (n = 1 to 14)[7] | Endpoint Status Image Register n endpoint 1 to 14 | D2 to DF   | read 1 byte <sup>[2]</sup> |

| Acknowledge Setup                        | Endpoint 0 IN and OUT                             | F4         | _[3]                       |

| General commands                         |                                                   |            |                            |

| Read Control OUT Error Code              | Error Code Register endpoint 0 OUT                | A0         | read 1 byte <sup>[2]</sup> |

| Read Control IN Error Code               | Error Code Register endpoint 0 IN                 | A1         | read 1 byte <sup>[2]</sup> |

| Read Endpoint n Error Code (n = 1 to 14) | Error Code Register endpoint 1 to 14              | A2 to AF   | read 1 byte <sup>[2]</sup> |

| Unlock Device                            | all registers with write access                   | В0         | write 2 bytes              |

| Write/Read Scratch Register              | Scratch Register                                  | B2/B3      | write/read 2 bytes         |

| Read Frame Number                        | Frame Number Register                             | B4         | read 1 or 2 bytes          |

| Read Chip ID                             | Chip ID Register                                  | B5         | read 2 bytes               |

| Read Interrupt Register                  | Interrupt Register                                | C0         | read 4 bytes               |

- [1] With N representing the number of bytes, the number of words for 16-bit bus width is: (N + 1) DIV 2.

- [2] When accessing an 8-bit register in 16-bit mode, the upper byte is invalid.

- [3] In 8-bit bus mode this command requires more time to complete than other commands. See Table 58.

- $[4] \quad \text{During isochronous transfer in 16-bit mode, because N} \leq 1023, \text{ the firmware must take care of the upper byte.}$

- [5] Validating an OUT endpoint buffer causes unpredictable behavior of ISP1181A.

- [6] Clearing an IN endpoint buffer causes unpredictable behavior of ISP1181A.

- [7] Reads a copy of the Status Register: executing this command does not clear any status bits or interrupt bits.

#### 12.1 Initialization commands

Initialization commands are used during the enumeration process of the USB network. These commands are used to configure and enable the embedded endpoints. They also serve to set the USB assigned address of ISP1181A and to perform a device reset.

#### 12.1.1 Write/Read Endpoint Configuration

This command is used to access the Endpoint Configuration Register (ECR) of the target endpoint. It defines the endpoint type (isochronous or bulk/interrupt), direction (OUT/IN), FIFO size and buffering scheme. It also enables the endpoint FIFO. The register bit allocation is shown in Table 14. A bus reset will disable all endpoints.

The allocation of FIFO memory only takes place after **all** 16 endpoints have been configured in sequence (from endpoint 0 OUT to endpoint 14). Although the control endpoints have fixed configurations, they must be included in the initialization sequence and be configured with their default values (see Table 4). Automatic FIFO allocation starts when endpoint 14 has been configured.

9397 750 13959

#### Full-speed USB peripheral controller

**Remark:** If any change is made to an endpoint configuration which affects the allocated memory (size, enable/disable), the FIFO memory contents of **all** endpoints becomes invalid. Therefore, all valid data must be removed from enabled endpoints before changing the configuration.

Code (Hex): 20 to 2F — write (control OUT, control IN, endpoint 1 to 14)

Code (Hex): 30 to 3F — read (control OUT, control IN, endpoint 1 to 14)

Transaction — write/read 1 byte

Table 14: Endpoint Configuration Register: bit allocation

| Bit    | 7      | 6     | 5      | 4      | 3   | 2    | 1      | 0   |

|--------|--------|-------|--------|--------|-----|------|--------|-----|

| Symbol | FIFOEN | EPDIR | DBLBUF | FFOISO |     | FFOS | Z[3:0] |     |

| Reset  | 0      | 0     | 0      | 0      | 0   | 0    | 0      | 0   |

| Access | R/W    | R/W   | R/W    | R/W    | R/W | R/W  | R/W    | R/W |

Table 15: Endpoint Configuration Register: bit description

| Bit    | Symbol     | Description                                                                                                                     |

|--------|------------|---------------------------------------------------------------------------------------------------------------------------------|

| 7      | FIFOEN     | A logic 1 indicates an enabled FIFO with allocated memory. A logic 0 indicates a disabled FIFO (no bytes allocated).            |

| 6      | EPDIR      | This bit defines the endpoint direction (0 = OUT, 1 = IN). It also determines the DMA transfer direction (0 = read, 1 = write). |

| 5      | DBLBUF     | A logic 1 indicates that this endpoint has double buffering.                                                                    |

| 4      | FFOISO     | A logic 1 indicates an isochronous endpoint. A logic 0 indicates a bulk or interrupt endpoint.                                  |

| 3 to 0 | FFOSZ[3:0] | Selects the FIFO size according to Table 5                                                                                      |

#### 12.1.2 Write/Read Device Address

This command is used to set the USB assigned address in the Address Register and enable the USB device. The Address Register bit allocation is shown in Table 16.

A USB bus reset sets the device address to 00H (internally) and enables the device. The value of the Address Register (accessible by the micro) is not altered by the bus reset. In response to the standard USB request Set Address the firmware must issue a Write Device Address command, followed by sending an empty packet to the host. The **new** device address is activated when the host acknowledges the empty packet.

Code (Hex): B6/B7 — write/read Address Register

Transaction — write/read 1 byte

Table 16: Address Register: bit allocation

| Bit    | 7     | 6   | 5   | 4   | 3           | 2   | 1   | 0   |

|--------|-------|-----|-----|-----|-------------|-----|-----|-----|

| Symbol | DEVEN |     |     |     | DEVADR[6:0] |     |     |     |

| Reset  | 0     | 0   | 0   | 0   | 0           | 0   | 0   | 0   |

| Access | R/W   | R/W | R/W | R/W | R/W         | R/W | R/W | R/W |

9397 750 13959 Product data

#### Full-speed USB peripheral controller

Table 17: Address Register: bit description

| Bit    | Symbol      | Description                                  |

|--------|-------------|----------------------------------------------|

| 7      | DEVEN       | A logic 1 enables the device.                |

| 6 to 0 | DEVADR[6:0] | This field specifies the USB device address. |

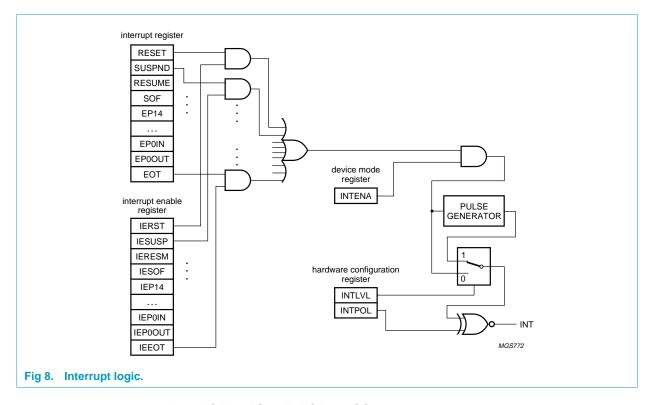

## 12.1.3 Write/Read Mode Register

This command is used to access the ISP1181A Mode Register, which consists of 1 byte (bit allocation: see Table 18). In 16-bit bus mode the upper byte is ignored.

The Mode Register controls the DMA bus width, resume and suspend modes, interrupt activity and SoftConnect operation. It can be used to enable debug mode, where all errors and Not Acknowledge (NAK) conditions will generate an interrupt.

Code (Hex): B8/B9 — write/read Mode Register

Transaction — write/read 1 byte

Table 18: Mode Register: bit allocation

| Bit    | 7     | 6        | 5      | 4        | 3      | 2      | 1        | 0      |

|--------|-------|----------|--------|----------|--------|--------|----------|--------|

| Symbol | DMAWD | reserved | GOSUSP | reserved | INTENA | DBGMOD | reserved | SOFTCT |

| Reset  | 0[1]  | 0        | 0      | 0        | 0[1]   | 0[1]   | 0[1]     | 0[1]   |

| Access | R/W   | R/W      | R/W    | R/W      | R/W    | R/W    | R/W      | R/W    |

[1] Unchanged by a bus reset.

Table 19: Mode Register: bit description

| Bit | Symbol | Description                                                                                                                                                                                                                                                            |

|-----|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | DMAWD  | A logic 1 selects 16-bit DMA bus width (bus configuration modes 0 and 2). A logic 0 selects 8-bit DMA bus width. Bus reset value: unchanged.                                                                                                                           |

| 6   | -      | reserved                                                                                                                                                                                                                                                               |

| 5   | GOSUSP | Writing a logic 1 followed by a logic 0 will activate 'suspend' mode.                                                                                                                                                                                                  |

| 4   | -      | reserved                                                                                                                                                                                                                                                               |

| 3   | INTENA | A logic 1 enables all interrupts. Bus reset value: unchanged.                                                                                                                                                                                                          |

| 2   | DBGMOD | A logic 1 enables debug mode. where all NAKs and errors will generate an interrupt. A logic 0 selects normal operation, where interrupts are generated on every ACK (bulk endpoints) or after every data transfer (isochronous endpoints). Bus reset value: unchanged. |

| 1   | -      | reserved                                                                                                                                                                                                                                                               |

| 0   | SOFTCT | A logic 1 enables SoftConnect (see Section 7.4). This bit is ignored if EXTPUL = 1 in the Hardware Configuration Register (see Table 20). Bus reset value: unchanged.                                                                                                  |

9397 750 13959

# Full-speed USB peripheral controller

## 12.1.4 Write/Read Hardware Configuration

This command is used to access the Hardware Configuration Register, which consists of 2 bytes. The first (lower) byte contains the device configuration and control values, the second (upper) byte holds the clock control bits and the clock division factor. The bit allocation is given in Table 20. A bus reset will not change any of the programmed bit values.