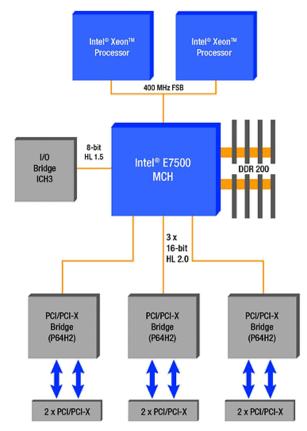

channels. To balance the performance offered by the processor and memory interfaces, the MCH allows several high-bandwidth I/O configuration options for a total of 3.2 GB/s of I/O bandwidth. Together, these features deliver balanced, high-throughput system performance.

The 82870P2 64-bit PCI/PCI-X Controller Hub 2 (P64H2) connects to the MCH

$http://www.intel.com/design/chipsets/embedded/273686.htm\ (1\ of\ 4)12/10/2006\ 8:14:31\ PM$

through a point-to-point Hub Interface 2.0 connection. Up to three P64H2 devices can be attached to the MCH, each providing an I/O bandwidth greater than 1 GB/s for a total of 3.2 GB/s of I/O bandwidth. Each P64H2 contains two independent 64-bit PCI-X interfaces and twoPCI hot plug controllers, one per PCI-X interface. Each 64-bit PCI-X segment supports multiple PCI-X slots for high-bandwidth connectivity of next-generation components such as Intel® Gigabit Ethernet adapters and Intel® I/O processors.

The 82801CA I/O Controller Hub 3-S (ICH3-S) connects to the MCH through a point-topoint Hub Interface 1.5 connection. The ICH3-S provides legacy I/O interfaces through integrated features including a two-channel Ultra ATA/100 bus master IDE controller and three USB controllers for up to six USB ports. The ICH3-S also offers an integrated System Manageability Bus 2.0 (SMBus 2.0) controller, an integrated LAN controller, as well as AC97 2.2-compliant and PCI 2.2-compliant interfaces.

Features that maximize performance and balance the platform: Dual Intel Xeon processors with 512 KB L2 cache or Low Voltage Intel Xeon processors and a 400 MHz system bus provide up to 3.2 GB/s of available bandwidth. Dual DDR-200 memory channels operate in lock-step to provide up to 3.2 GB/s of memory bandwidth. Three Hub Interface 2.0 connections provide multiple high-bandwidth I/O configuration options, yielding up to 3.2 GB/ s of I/O bandwidth.

Download Product Brief

#### **Block Diagram**

http://www.intel.com/design/chipsets/embedded/273686.htm (2 of 4)12/10/2006 8:14:31 PM

## **Product Highlights**

- Supports one or two Intel® Xeon® processors with 512 KB L2 cache or Low Voltage Intel Xeon processors for embedded computing platforms

- 400 MHz system bus capability

- The P64H2 provide an Intel® Hub Architecture 2.0 connection to the MCH

64-bit PCI/PCI-X Controller Hub-2

- Dual-channel DDR-200 memory interface

- Advanced Platform RASUM

# Intel® E7500 Chipset

$http://www.intel.com/design/chipsets/embedded/273686.htm\ (3\ of\ 4)12/10/2006\ 8:14:31\ PM$

## Intel® E7500 Chipset for Embedded Computing - Overview

| Product                                        | <b>Product Code</b> | Package                                 |

|------------------------------------------------|---------------------|-----------------------------------------|

| E7500 Memory Controller Hub<br>(MCH)           | RGE7500PL           | 1005 Flip Chip-Ball Grid Array (FC-BGA) |

| 82801CA Integrated Controller<br>Hub (ICH3-S)  | FW82801CA           | 421 Ball Grid Array (BGA)               |

| 82870P2 64-bit PCI/PCI-X<br>Controller (P64H2) | RG82870P2           | 567 Flip Chip-Ball Grid Array (FC-BGA)  |

Back to Top^

• Site Map | RSS Feeds | Jobs at Intel | Investor Relations

• \*Legal Information | Privacy Policy | ©2006 Intel Corporation

# ©2005 Intel Corporation

http://www.intel.com/design/chipsets/embedded/273686.htm (4 of 4)12/10/2006 8:14:31 PM