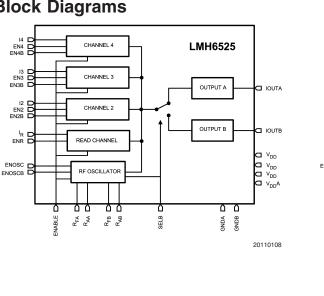

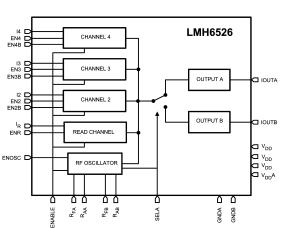

# LMH6525/LMH6526 Four–Channel Laser Diode Driver with Dual Output **General Description** Features

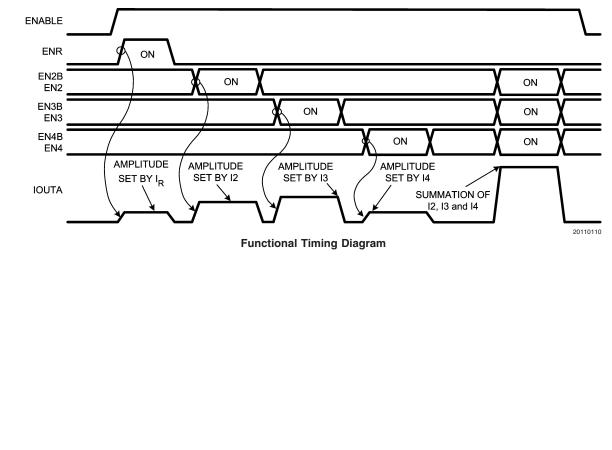

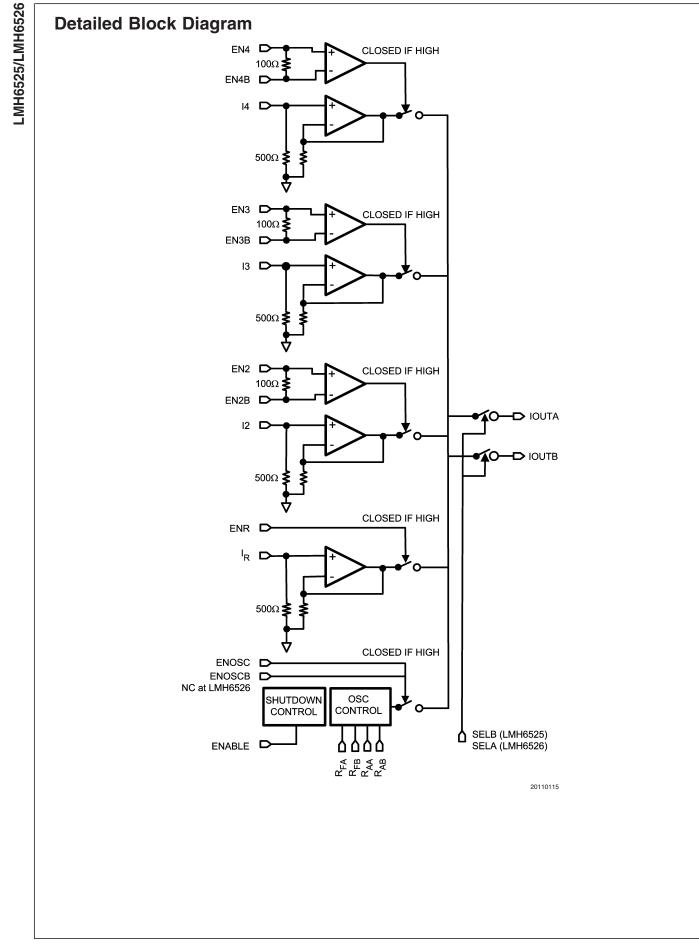

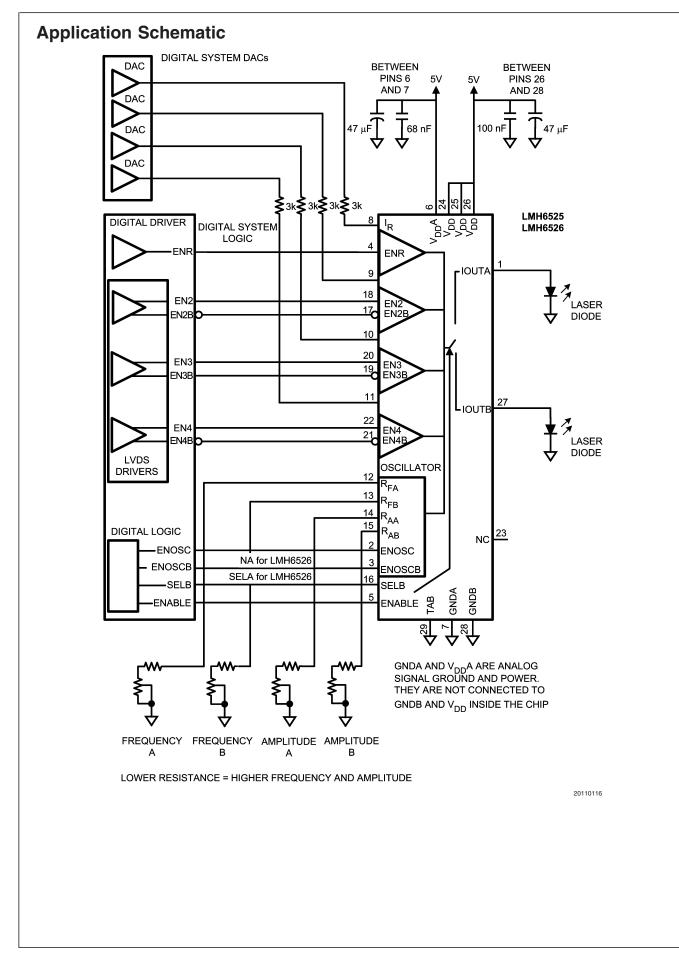

The LMH™6525/6526 is a laser diode driver for use in combination DVD/CD recordable and rewritable systems. The part contains two high-current outputs for reading and writing the DVD (650 nm) and CD (780 nm) lasers. Functionality includes read, write and erase through four separate switched current channels. The channel currents are summed together at the selected output to generate multilevel waveforms for reading, writing and erasing of optical discs. The LVDS interface delivers DVD write speeds of 16x and higher while minimizing noise and crosstalk. The LMH6525/6526 is optimized for both speed and power consumption to meet the demands of next generation systems. The part features a 150 mA read channel plus one 300 mA and two 150 mA write channels, which can be summed to allow a total output current of 600 mA or greater. The channel currents are set through four independent current inputs.

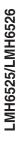

An on-board High-Frequency Modulator (HFM) oscillator helps reduce low-frequency noise of the laser and is enabled by applying LVDS levels on the ENOSC pins for the LMH6525, while the LMH6526 is enabled by applying an asymmetrical signal on the ENOSC pin. The fully differential oscillator circuit minimizes supply line noise, easing FCC approval of the overall system. The SELA/B pin (active HIGH) selects the output channel and oscillator settings. External resistors determine oscillator frequency and amplitude for each setting. The write and erase channels can be switched on and off through dedicated LVDS interface pins.

- Fast switching: Rise and fall times: 0.6/1.0 ns.

- Low Voltage Differential Signaling (LVDS) channels enable interface for the fast switching lines

- Low output current noise: 0.24 nA/ √Hz

- **Dual Output:** Selectable by SELA/B pin (active HIGH) SELA = LMH6526SELB = LMH6525

- Four independent current channels Gain of 300, 300 mA write channel Gain of 150, 150 mA low-noise read channel Two gain of 150, 150 mA write channels 600 mA minimum combined output current

- Integrated AC Coupled HFM Oscillator Selectable frequency and amplitude setting by external resistors 200 MHz to 600 MHz frequency range Amplitude to 100 mA peak-to-peak modulation

- Complete shutdown by ENABLE pin

- 5V single-supply operation

- Logic inputs TTL and CMOS compatible

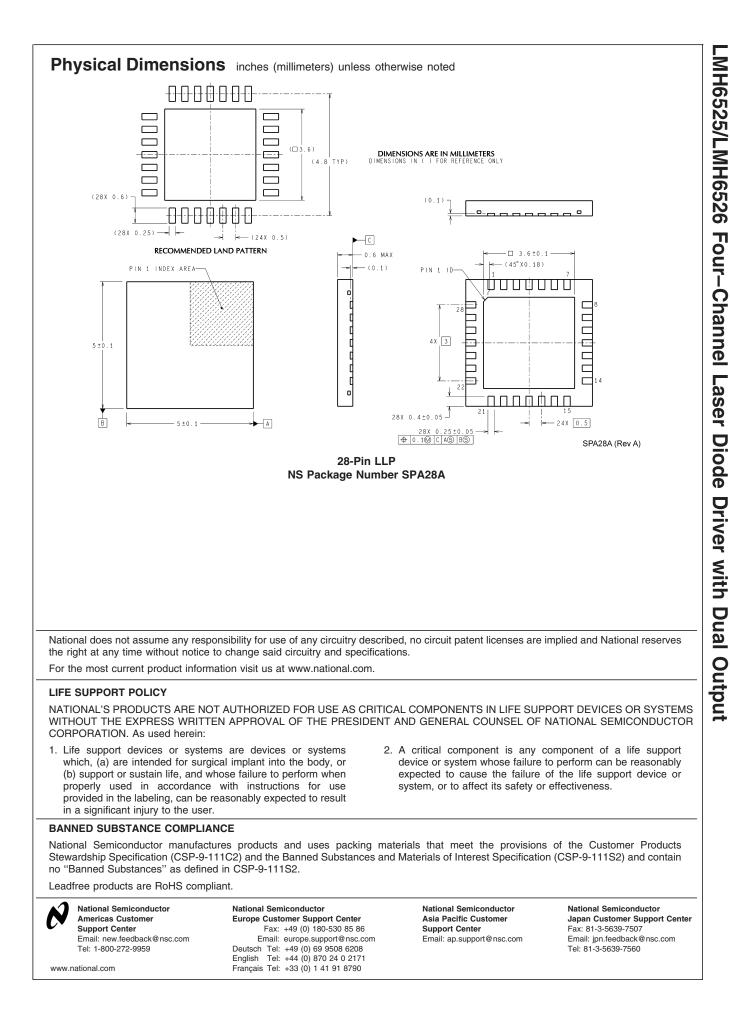

- Space saving Leadless Leadframe Package (LLP®-28)

- LMH6525 has differential enable oscillator inputs

- LMH6526 has single ended enable oscillator inputs

## Applications

- Combination DVD/CD recordable and rewritable drives

- DVD camcorders

- DVD recorders

# **Block Diagrams**

EN4

EN3 EN3B

LLP® is a registered trademark of National Semiconductor. LMH<sup>™</sup> is a trademark of National Semiconductor Corporation

DS201101 © 2005 National Semiconductor Corporation

www.national.com

20110109

# Absolute Maximum Ratings (Note 1)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

| ESD Tolerance                                   |                 |

|-------------------------------------------------|-----------------|

| Human Body Model (Note 2)                       | 2 KV            |

| Machine Model (Note 3)                          | 200V            |

| Supply Voltages V <sup>+</sup> – V <sup>-</sup> | 5.5V            |

| Differential Input Voltage                      | ±5.5V           |

| Output Short Circuit to Ground                  |                 |

| (Note 4)                                        | Continuous      |

| Input Common Mode Voltage                       | $V^-$ to $V^+$  |

| Storage Temperature Range                       | –65°C to +150°C |

| Junction Temperature (Note 5)                   | +150°C          |

|                                                 |                 |

# Operating Ratings (Note 1)

| Supply Voltage (V <sup>+</sup> - V <sup>-</sup> ) | $4.5V \leq V_S \leq 5.5V$                |

|---------------------------------------------------|------------------------------------------|

| Operating Temperature Range (T <sub>A</sub> )     |                                          |

| (Note 8)                                          | $-40^{\circ}C \leq T_A \leq 85^{\circ}C$ |

| Package Thermal Resistance                        |                                          |

| (Note 5), (Note 8)                                | LLP Package                              |

| $(\theta_{JC})$                                   | 3°C/W                                    |

| $(\theta_{JA})$ (no heatsink)                     | 42°C/W                                   |

| $(\theta_{JA})$ (no heatsink see (Note 10))       | 30.8°C/W                                 |

| I <sub>INR/3/4</sub>                              | 1.5 mA (Max)                             |

| I <sub>IN2</sub>                                  | 1.0 mA (Max)                             |

| R <sub>FREQ</sub>                                 | 1000 Ω (Min)                             |

| R <sub>AMP</sub>                                  | 1000 Ω (Min)                             |

| F <sub>osc</sub>                                  | 100-600 MHz                              |

| A <sub>OSC</sub>                                  | 10-100 mA <sub>PP</sub>                  |

# +5V DC Electrical Characteristics (Note 8)

Unless otherwise specified, all limits guaranteed for  $T_J = 25$  °C,  $R_L = 10\Omega$ . Boldface limits apply at the temperature extremes.

| Symbol                   | Parameter                     | Conditions                                                            |      | Typ<br>(Note 6) | Max<br>(Note 7) | Units |

|--------------------------|-------------------------------|-----------------------------------------------------------------------|------|-----------------|-----------------|-------|

| LVDS                     | I                             |                                                                       | ,    | , ,             | , ,             |       |

| VI                       | Input Voltage Range           | V <sub>GPD</sub>   < 50 mV<br>(Note 9),                               | 0    | 1.7             | 2.4             | V     |

| V <sub>IDTH</sub>        | Input Diff. Threshold         | $ V_{GPD}  < 50 \text{ mV}$<br>(Note 9),                              | -100 | 0               | 100             | mV    |

| V <sub>HYST</sub>        | Input Diff. Hysteresis        | V <sub>IDTHH</sub> – V <sub>IDTHL</sub>                               | 25   | 0               |                 | mV    |

| R <sub>IN</sub>          | Input Diff. Impedance         |                                                                       | 95   | 115             | 135             | Ω     |

| I <sub>IN</sub>          | Input Current                 | Excluding R <sub>IN</sub> Current<br>V <sub>CM</sub> = 1.25V          |      | 8               | 20              | μA    |

| Current Cl               | nannels                       |                                                                       |      |                 |                 |       |

| R <sub>IN</sub>          | Input Resistance all Channels | R <sub>IN</sub> to Ground                                             | 475  | 580             | 675             | Ω     |

| I <sub>OS2</sub>         | Current Offset Channel 2      | Channel R,3,4 Off<br>I <sub>IN</sub> = 0, EN = High                   |      | 2.1             | 16              | mA    |

| I <sub>OS,R,3,4</sub>    | Current Offset Channel R,3,4  | All Channels Off $I_{IN} = 0$ , EN = High                             |      | 1.2             | 9               | mA    |

| A <sub>IW</sub>          | Current Gain                  | Channel 2                                                             | 345  | 386             | 430             | A/A   |

| A <sub>IR</sub>          | Current Gain                  | Channel Read                                                          | 135  | 159             | 180             | A/A   |

| A <sub>I,3,4</sub>       | Current Gain                  | Channel 3 and 4                                                       | 160  | 182             | 200             | A/A   |

| I <sub>LIN-R,2,3,4</sub> | Output Current Linearity      | 200 μA < $I_{IN}$ < 1000 μA; $R_{LOAD}$ = 5Ω Channels Read, 2,3 and 4 |      | 1.7             | 3               | %     |

| IOUTw                    | Output Current                | Channel 2 @ 1 mA input current                                        | 285  | 300             |                 | mA    |

| IOUT <sub>R</sub>        | Output Current                | Channel Read<br>@ 1 mA input current                                  |      | 162             |                 | mA    |

| IOUT <sub>3,4</sub>      | Output Current                | Channel 3 and 4 160<br>@ 1 mA input current                           |      | 183             |                 | mA    |

| IOUT <sub>TOTAL</sub>    | Total Output Current          | All Channels (Note 12)                                                | 600  |                 |                 | mA    |

| V <sub>TLO</sub>         | TTL Low Voltage               | Input (H to L)<br>ENR<br>ENOSC (LMH6526)                              |      | 1.29            | 0.8             | V     |

| V <sub>TLO</sub>         | TTL Low Voltage               | Input (H to L)<br>B-Select (LMH6525)<br>A-Select (LMH6526)            |      | 1.40            | 0.8             | V     |

| V <sub>ELO</sub>         | Enable Low Voltage            | Enable Input (H to L)                                                 |      | 1.98            | 0.8             | V     |

| Symbol           | Parameter                                         | nteed for $T_J = 25$ °C, $R_L = 10\Omega$ . Boldfac                                                           | Min      |                 | Max      | Units |

|------------------|---------------------------------------------------|---------------------------------------------------------------------------------------------------------------|----------|-----------------|----------|-------|

| Symbol           | Parameter                                         | Conditions                                                                                                    | (Note 7) | Typ<br>(Note 6) | (Note 7) | Units |

| V <sub>THI</sub> | TTL High Voltage                                  | Input (L to H)<br>ENR<br>ENOSC (LMH6526)                                                                      | 2        | 1.27            |          | V     |

| V <sub>THI</sub> | TTL High Voltage                                  | Input (L to H)<br>B-Select (LMH6525)<br>A-Select (LMH6526)                                                    | 2        | 1.51            |          | V     |

| V <sub>EHI</sub> | Enable High Voltage                               | Enable Input (L to H)                                                                                         | 2.8      | 2.13            |          | V     |

| I <sub>Spd</sub> | Supply Current, Power Down                        | Enable = Low                                                                                                  |          | 0.003           | 0.1      | mA    |

| I <sub>Sr1</sub> | Supply Current, Read Mode,<br>Oscillator Disabled | ENOSC = Low; ENOSCB = High<br>I2 = I3 = I4 = I <sub>B</sub> = 125 $\mu$ A                                     |          | 81.5            | 100      | mA    |

| I <sub>Sr2</sub> | Supply Current, Read Mode,<br>Oscillator Enabled  | ENOSC = High; ENOSCB = Low<br>$I2 = I3 = I4 = I_R = 125 \ \mu A$<br>$R_{FA} = 3.5 \ k\Omega$                  |          | 81.5            | 100      | mA    |

| I <sub>Swr</sub> | Supply Current, Write Mode                        | EN2 = EN3 = EN4 = High;<br>I2 = I3 = I4 = I <sub>B</sub> = 125 μA                                             |          | 180             | 210      | mA    |

| I <sub>S</sub>   | Supply Current                                    | All Channels disable, no input<br>current. SELA/B = Low<br>$R_{AA}$ , $R_{AB}$ , $R_{FA}$ , $R_{FB} = \infty$ |          | 33              | 40       | mA    |

# +5V AC ELECTRICAL CHARACTERISTICS

Unless otherwise specified, all limits guaranteed for  $T_J = 25^{\circ}C$ ,  $I_{OUT} = 40$  mA DC and 40 mA pulse,  $R_L = 50\Omega$ . **Boldface** limits apply at the temperature extremes.

| Symbol                         | Parameter                        | Conditions                                       | Min      | Тур      | Мах      | Units   |  |

|--------------------------------|----------------------------------|--------------------------------------------------|----------|----------|----------|---------|--|

|                                |                                  |                                                  | (Note 7) | (Note 6) | (Note 7) |         |  |

| t <sub>r</sub> Write Rise Time |                                  | I <sub>OUT</sub> = 40 mA (Read) + 40 mA          |          | 0.6      |          | ns      |  |

|                                |                                  | (10% to 90%) $R_{LOAD} = 5\Omega$                |          |          |          |         |  |

| t <sub>f</sub>                 | Write Fall Time                  | I <sub>OUT</sub> = 40 mA (Read) + 40 mA          |          | 1.6      |          | ns      |  |

|                                |                                  | (90% to 10%) $R_{LOAD} = 5\Omega$                |          |          |          |         |  |

| t <sub>r</sub>                 | Write Rise Time                  | I <sub>OUT</sub> = 100 mA (Read) + 100 mA        |          | 0.6      |          | ns      |  |

|                                |                                  | (10% to 90%) $R_{LOAD} = 5\Omega$                |          |          |          |         |  |

| t <sub>f</sub>                 | Write Fall Time                  | I <sub>OUT</sub> = 100 mA (Read) + 100 mA        |          | 1.0      |          | ns      |  |

|                                |                                  | (90% to 10%) $R_{LOAD} = 5\Omega$                |          |          |          |         |  |

| t <sub>r</sub>                 | Write Rise Time                  | I <sub>OUT</sub> = 150 mA (Read) + 150 mA        |          | 0.6      |          | ns      |  |

|                                |                                  | (10% to 90%) $R_{LOAD} = 5\Omega$                |          |          |          |         |  |

| t <sub>f</sub>                 | Write Fall Time                  | I <sub>OUT</sub> = 150 mA (Read) + 150 mA        |          | 1.0      |          | ns      |  |

|                                |                                  | (90% to 10%) $R_{LOAD} = 5\Omega$                |          |          |          |         |  |

| OS                             | Output Current Overshoot         | I <sub>OUT</sub> = 40 mA (Read) + 40 mA          |          | 18       |          | %       |  |

|                                |                                  | (Note 11)                                        |          |          |          |         |  |

| INo                            | Output Current Noise             | $I_{OUT} = 40 \text{ mA};  R_{LOAD} = 50\Omega;$ |          | 0.24     |          | nA/ √Hz |  |

|                                |                                  | f = 50 MHz; ENOSC = Low                          |          |          |          |         |  |

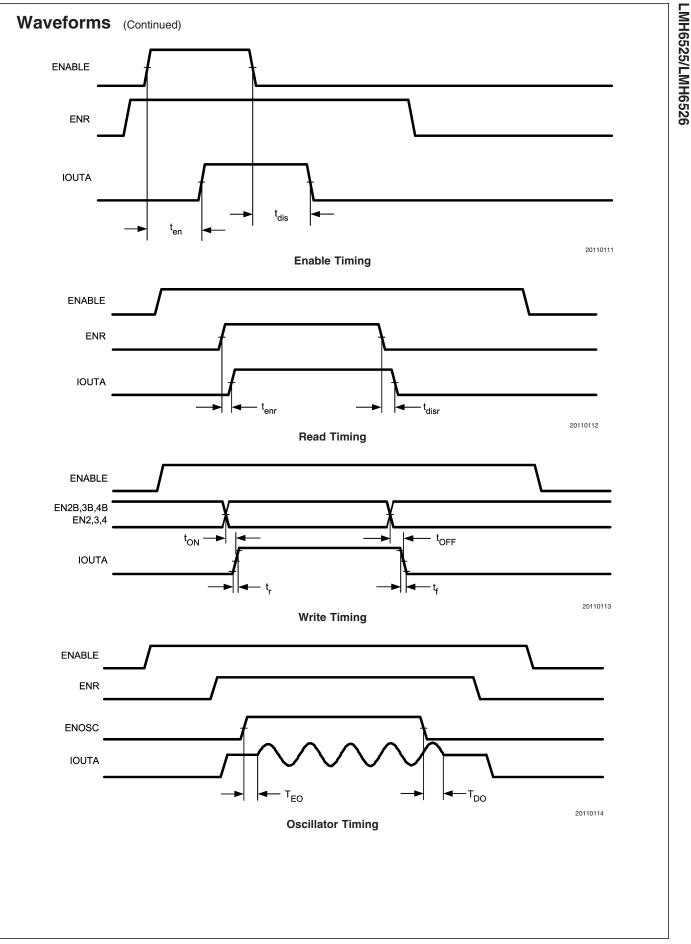

| t <sub>on</sub>                | I <sub>OUT</sub> ON Prod. Delay  | Switched on EN2 and EN2B                         |          | 3.1      |          | ns      |  |

| t <sub>OFF</sub>               | I <sub>OUT</sub> OFF Prop. Delay | Switched on EN2 and EN2B                         |          | 3.3      |          | ns      |  |

| t <sub>disr</sub>              | Disable Time, Read Channel       | Switched on ENR                                  |          | 3.5      |          | as      |  |

| T <sub>enr</sub>               | Enable Time, Read Channel        | Switched on ENR                                  |          | 2.8      |          | ns      |  |

| t <sub>dis</sub>               | Disable Time (Shutdown)          | Enable = High to Low 37                          |          |          | ns       |         |  |

| t <sub>en</sub>                | Enable Time (Shutdown)           | Enable = Low to High 4.5                         |          |          | μs       |         |  |

| BW <sub>c</sub>                | Channel Bandwidth, -3 dB         | I <sub>OUT</sub> = 50 mA, All Channels           |          | 250      |          | KHz     |  |

| Fosc                           | Oscillator Frequency             | R <sub>F</sub> = 3.48 kΩ                         | 290      | 360      | 430      | MHz     |  |

|                                |                                  | Range 200 MHz to 600 MHz                         |          |          |          |         |  |

Downloaded from Elcodis.com electronic components distributor

# LMH6525/LMH6526

# +5V AC ELECTRICAL CHARACTERISTICS (Continued)

Unless otherwise specified, all limits guaranteed for  $T_J = 25^{\circ}$ C,  $I_{OUT} = 40$  mA DC and 40 mA pulse,  $R_L = 50\Omega$ . **Boldface** limits apply at the temperature extremes.

| Symbol          | Parameter               | Conditions | Min      | Тур      | Мах      | Units |

|-----------------|-------------------------|------------|----------|----------|----------|-------|

|                 |                         |            | (Note 7) | (Note 6) | (Note 7) |       |

| T <sub>DO</sub> | Disable Time Oscillator | LMH6525    |          | 5        |          | ns    |

| T <sub>EO</sub> | Enable Time Oscillator  | LMH6525    |          | 4        |          | ns    |

| T <sub>DO</sub> | Disable Time Oscillator | LMH6526    |          | 7        |          | ns    |

| Τ <sub>ΕΟ</sub> | Enable Time Oscillator  | LMH6526    |          | 4        |          | ns    |

Note 1: Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is intended to be functional, but specific performance is not guaranteed. For guaranteed specifications, see the Electrical Characteristics tables.

Note 2: For testing purposes, ESD was applied using "Human Body Model"; 1.5 k $\Omega$  in series with 100 pF.

Note 3: Machine Model, 0Ω in series with 200 pF.

Note 4: Applies to both single-supply and split-supply operation. Continuous short circuit operation at elevated ambient temperature can result in exceeding the maximum allowed junction temperature of 150°C.

Note 5: The maximum power dissipation is a function of  $T_{J(MAX)}$ ,  $\theta_{JA}$  and  $T_A$ . The maximum allowable power dissipation at any ambient temperature is  $P_D = (T_{J(MAX)} - T_A)/\theta_{JA}$ . All numbers apply for packages soldered directly onto a PC board.

Note 6: Typical values represent the most likely parametric norm.

Note 7: All limits are guaranteed by testing or statistical analysis.

**Note 8:** Electrical Table values apply only for factory testing conditions at the temperature indicated. Factory testing conditions result in very limited self-heating of the device such that  $T_J = T_A$ . There is no guarantee of parametric performance as indicated in the electrical tables under conditions of internal self-heating where  $T_J > T_A$ . See Applications section for information on temperature de-rating of this device.

Note 9:  $V_{GPD}$  = ground potential difference voltage between driver and receiver

Note 10: This figure is taken from a thermal modeling result. The test board is a 4 layer FR-4 board measuring 101 mm x 101 mm x 1.6 mm with a 3 x 3 array of thermal vias. The ground plane on the board is 50 mm x 50 mm. Ambient temperature in simulation is 22°C, still air. Power dissipation is 1W.

Note 11: This is the average between the positive and negative overshoot.

Note 12: Total input current is 4 mA (all 4 channels equal) and output currents are summed together (see typical performance characteristics).

# **Ordering Information**

| Package     | Part Number     | Package Marking | Transport Media          | NSC Drawing |

|-------------|-----------------|-----------------|--------------------------|-------------|

|             | LMH6525SP NOPB  | L6525SP         | 1k Units Tape and Reel   |             |

| 28-Pin LLP  | LMH6525SPX NOPB | LOSZOGF         | 4.5k Units Tape and Reel | SPA28A      |

| 20-FIII LLF | LMH6526SP NOPB  | L6526SP         | 1k Units Tape and Reel   | JFA20A      |

|             | LMH6526SPX NOPB | LOSZOSF         | 4.5k Units Tape and Reel |             |

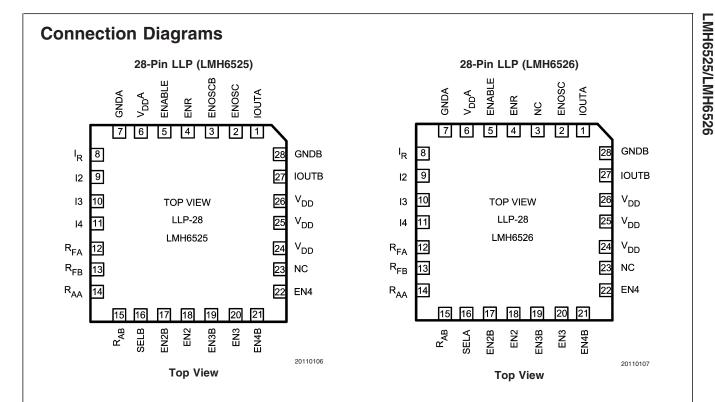

# **Pin Description**

| Pin # | Description                                 | Remarks                                                |

|-------|---------------------------------------------|--------------------------------------------------------|

| 1.    | Laser driver output channel A               |                                                        |

| 2.    | LVDS Oscillator Enable pin                  | Internal Oscillator activated if logical input is high |

| 3.    | LVDS Oscillator Enable pin B (only LMH6525) | Internal Oscillator activated if logical input is low  |

| 4.    | Read Channel Enable pin                     | Read Channel active if pin is high                     |

| 5.    | Chip Enable pin                             | Chip Enabled if pin is high                            |

| 6.    | Supply Voltage A                            |                                                        |

| 7.    | Ground Connection A                         |                                                        |

| 8.    | Read Channel current setting                | 1 mA input current result in 150 mA output current     |

| 9.    | Channel 2 current setting                   | 1 mA input current result in 300 mA output current     |

| 10.   | Channel 3 current setting                   | 1 mA input current result in 150 mA output current     |

| 11.   | Channel 4 current setting                   | 1 mA input current result in 150 mA output current     |

| 12.   | Oscillator Frequency setting Channel A      | Set by external resistor to ground                     |

| 13.   | Oscillator Frequency setting Channel B      | Set by external resistor to ground                     |

| 14.   | Oscillator Amplitude setting Channel A      | Set by external resistor to ground                     |

| 15.   | Oscillator Amplitude setting Channel B      | Set by external resistor to ground                     |

| 16.   | Channel select B (LMH6525)                  | Channel selected if pin is high                        |

|       | Channel select A (LMH6526)                  |                                                        |

| 17.   | LVDS input Channel 2B                       | Channel 2 active if logical input is low               |

| 18.   | LVDS input Channel 2                        | Channel 2 active if logical input is high              |

| 19.   | LVDS input Channel 3B                       | Channel 3 active if logical input is low               |

| 20.   | LVDS input Channel 3                        | Channel 3 active if logical input is high              |

| 21.   | LVDS input Channel 4B                       | Channel 4 active if logical input is low               |

| 22.   | LVDS input Channel 4                        | Channel 4 active if logical input is high              |

| 23.   | NC                                          |                                                        |

| 24.   | Supply Voltage                              |                                                        |

| 25.   | Supply Voltage                              |                                                        |

| 26.   | Supply Voltage                              |                                                        |

# Downloaded from Elcodis.com electronic components distributor

5

| Pin De | Pin Description (Continued)   |         |  |  |  |  |

|--------|-------------------------------|---------|--|--|--|--|

| Pin #  | Description                   | Remarks |  |  |  |  |

| 27.    | Laser driver output channel B |         |  |  |  |  |

| 28.    | Ground Connection B           |         |  |  |  |  |

# **Truth Tables**

# **IOUT Control**

| ENABLE | ENR | EN2 | EN3 | EN4 | IOUT                              |

|--------|-----|-----|-----|-----|-----------------------------------|

| 0      | Х   | Х   | Х   | Х   | OFF                               |

| 1      | 0   | 0   | 0   | 0   | OFF                               |

| 1      | 1   | 0   | 0   | 0   | A <sub>R</sub> * I <sub>INR</sub> |

| 1      | 1   | 1   | 0   | 0   | $A_R * I_{INR} + A_2 * I_{IN2}$   |

| 1      | 1   | 0   | 1   | 0   | $A_R * I_{INR} + A_3 * I_{IN3}$   |

| 1      | 1   | 0   | 0   | 1   | $A_R * I_{INR} + A_4 * I_{IN4}$   |

# **Oscillator Control**

| ENABLE | ENOSC | ENR | EN2 | EN3 | EN 4 | OSCILLATOR |

|--------|-------|-----|-----|-----|------|------------|

| 0      | Х     | Х   | Х   | Х   | Х    | OFF        |

| 1      | 0     | Х   | Х   | Х   | Х    | OFF        |

| 1      | 1     | Х   | Х   | Х   | Х    | ON         |

Note: Note: EN2, EN3, EN4 AND ENOSC are LVDS SIGNALS USING THE LMH6525. EN2, EN3 and EN4 are LVDS signals using the LMH6526.

# Waveforms

# LMH6525/LMH6526

www.national.com

# LMH6525/LMH6526

# **Application Section**

### CIRCUIT DESCRIPTION

### General & Spec

The LMH6525/6526 is a 4-channel-input, dual-output laser driver. The dual outputs are meant to drive two different laser diodes, one for CD reading and writing and one for DVD reading and writing. The part has an oscillator that can be set for both amplitude and frequency. The oscillator has four input pins for setting both the amplitude and frequency by connecting external resistors to ground. The part operates at 5V and is capable to deliver a minimum total output current of 500 mA.

### INPUTS

### **Current-Setting Inputs**

The 4 input channels are transconductance-type inputs. This means the output current of the channel is proportional to the current (not voltage) sourced into the input pin. That is why these pins are designated by the letter "I" to indicate the current input nature of the pin. The read channel currentsetting pin is "I<sub>B</sub>", the Channel 2 current-setting pin is "I2" and so on. Using a transconductance-type input eliminates the high-impedance inputs associated with a voltage input amplifier. The lower input impedances of the input nodes lowers the susceptibility of the part to EMI/RFI. The Read Channel (I<sub>B</sub>) and Channel 3 (I3) and 4 (I4) current-setting inputs have a gain of 150. The Channel 2 input (I2) has a current gain of 300. Sourcing one milliampere into the pins I<sub>B</sub>, I3 or I4, will result in 150 mA at the output for each Channel, while 1 mA into I2 will result in 300 mA at the output for Channel 2. These currents of 150 mA and 300 mA are the maximum allowable currents per channel. The total allowable output current from all the channels operating together exceeds 500 mA.

### **Channel Enable Inputs**

Each of the four channels has one (read) or two enable inputs that allow the channel to be turned on or off. The read channel enable (ENR) is a single-ended TTL/CMOS compatible input. A single-ended signal is adequate for this channel because the read channel is generally enabled the entire time the drive is reading or writing. The three write/erase channels need to be operated much faster so these channel enables are LVDS (Low Voltage Differential Signal) inputs. Each channel has two inputs, such as EN2 and EN2B. Following the standard an LVDS output consists of a current source of 3.5 mA, and this current produces across the internal termination resistor of  $100\Omega$  in the LMH6525 or LMH6526 a voltage of 350 mV. The polarity of the current through the resistor can change very quickly thus switching the channel current on or off. The bias level of the LVDS signal is about 1.2V, so the operating levels are 175 mV above and below this bias level. The ENxB inputs act as the not input so if the other input is at logical '1' state and the not input at '0' state the channel is activated. The internal  $100\Omega$ resister provides a proper termination for the LVDS signals, saving space and simplifying layout and assembly.

### **Control Inputs**

There are two other control inputs (next to the oscillator enable which is covered in the next section). There are the global chip Enable and output select pin SELA or SELB. Setting the Enable pin to a level above 2V will enable the part. This means the supply current raises from sleep mode value to the normal operating values. The SELA or SELB input (TTL/ CMOS levels) controls which output is active. When at logical '1' state the output indicated by it's name is active. The mode of this pin also controls the oscillator circuitry which means that the appropriate setting resistors become active as described in the next section.

### **Oscillator Inputs**

The oscillator section can be switched on or off by a LVDS signal for the LMH6525 and by a TTL/ CMOS signal for the LMH6526. When switched on the oscillator will modulate the output current. The settings of the frequency and amplitude are done by 4 resistors, two for every channel.  $R_{FA}$  and  $R_{FB}$ pins set the oscillator frequency for the A and B outputs respectively. The  $R_{AA}$  and  $R_{AB}$  pins set the oscillator amplitude for the A and B channels respectively. These 4 inputs work by having current drawn out of the pin by a setting resistor or potentiometer. The frequency and amplitude increase by decreasing setting resistor value. There are two charts in the Typical Performance Characteristics section that relates the setting resistor value to the resulting frequency or amplitude. Normally the settings for the frequency and amplitude are done by connecting the pin via a resistor to ground. If needed to program this settings it is possible to connect these R<sub>Fx</sub> and R<sub>Ax</sub> pins via a current limiting resistor to the output of an op amp or DAC. When using such a circuitry the output can be held at a negative voltage, which means even if the channel pins  $\mathsf{R}_{\mathsf{Fx}}$  and  $\mathsf{R}_{\mathsf{Ax}}$  are not selected, current is drawn from the pin. This is only true when the negative voltage has such a value that the internal transistors connected to the pin will conduct. This will influence the settings of the active pins R<sub>Fx</sub> and R<sub>Ax</sub>. Due to this effect it is recommended, when using a negative voltage lower as -0.5V, to disable this voltage simultaneously with the channel.

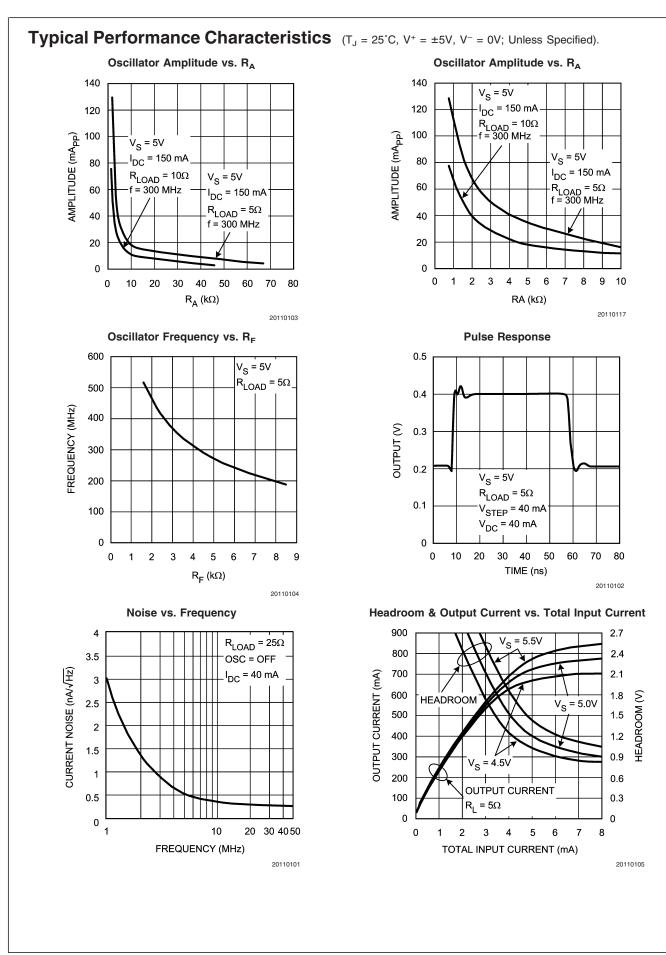

### OUTPUT

The outputs can source currents in excess of 600 mA. The output pins have been designed to have minimal series inductance in order to minimize current overshoot on fast pulses. The outputs have a saturation voltage of about 1V. The table below shows the typical output saturation Voltages into a 5 $\Omega$  load at various supply voltages.

# **TABLE 1. Output Saturation**

| Supply Voltage<br>(V) | Maximum<br>Output (mA) 5Ω | Saturation<br>Voltage (V) |

|-----------------------|---------------------------|---------------------------|

| 4.5V                  | 700                       | 0.8                       |

| 5.0V                  | 777                       | 0.89                      |

| 5.5V                  | 846                       | 1.02                      |

As can be seen, even with a 4.5V supply voltage the part can deliver 700 mA while the saturation voltage is at 0.8V. This means the output voltage of the part can be at maximum 700e- $3^*5 = 3.5V$ . With a saturated output voltage (see *Figure 1*) of 0.8V the voltage on the supply pin of the part is 4.3V. The used supply voltage is 4.5V so there is a supply voltage loss of 0.2V over the supply line resistance, but nevertheless the part can drive laser diodes with a forward voltage up to 3.5V with currents over 500 mA. When operating at 5.5V the part can deliver currents over 800 mA. In this case the output at the anode of the laser diode is 846e- $3^*5 = 4.23V$ , combined with the saturated output voltage of 1.02V the supply

# Application Section (Continued)

voltage of the part at the power pin is 5.25V and this means the supply line loss is 0.25V. So at 5.5V supply voltage the part can drive laser diodes with a forward voltage in access of 4V.

FIGURE 1. Output Configuration

# **Application Hints**

### SUPPLY SEQUENCING

As the LMH6525/6526 is fabricated in the CMOS7 process, latch-up concerns are minimal. Be aware that applying a low impedance input to the part when it has no supply voltage will forward bias the ESD diode on the input pin and then source power into the part's  $V_{DD}$  pin. If the potential exists for sustained operation with active inputs and no supply voltage, all the active inputs should have series resistors to limit the current into the input pins to levels below a few milliamperes.

### DECOUPLING

The LMH6525/6526 has very high output currents changing within a nanosecond. This makes decoupling especially important. High performance, low impedance ceramic capacitors should be located as close as possible to the supply pins. The LMH6525/6526 needs two decoupling capacitors, one for the analog power and ground  $V_{DD}A$ , GNDA) and one for the power side supply and ground (3xV<sub>DD</sub> and GNDB). The high level of output current dictates the power side decoupling capacitor should be 0.1 microfarads minimum. Larger values may improve rise times depending on the layout and trace impedances of the connections. The capacitors should have direct connection across the supply pins on the top layer, preferably with small copper-pour planes. These planes can connect to the bottom side ground and/or power planes with vias but there should be a topside low impedance path with no vias if possible. (see also Figure 4 Decoupling Capacitors).

### OVERSHOOT

As the LMH6525/6526 has fast rise times of less then a nanosecond, any inductance in the output path will cause overshoot. This includes the inductance in the laser diode itself as well as any trace inductance. A series connection of a resistor and a capacitor across the laser diode could be helpful to reduce unwanted overshoot or to reduce the very

high peaks caused by the relaxation oscillations of a laser diode when driven from below the knee voltage. But keep always in mind that this causes a slower rise and/ or fall time. Typical values are 10 $\Omega$  and 100 pF. The actual values required depend on the laser diode used and the circuit layout and should be determined empirically.

### THERMAL

### General

The LMH6525/6526 is a very high current output device. This means that the device must have adequate heatsinking to prevent the die from reaching its absolute maximum rating of 150°C. The primary way heat is removed from the LMH6525/6526 is through the Die Attach Pad, the large center pad on the bottomside of the device. Heat is also carried out of the die through the bond wires to the traces. The outputs and the  $V_{\mbox{\scriptsize DD}}$  pads of the device have double bond wires on this device so they will conduct about twice as much heat to the pad. In any event, the heat able to be transferred out the bond wires is far less than that which can be conducted out of the die attach pad. Heat can also be removed from the top of the part but the plastic encapsulation has worse thermal conductivity then copper. This means a heat sink on top of the part is less effective than the same copper area on the circuit board that is thermally attached to the Die Attach Pad.

### **PBC Heatsinks**

In order to remove the heat from the die attach pad there must be a good thermal path to large copper pours on the circuit board. If the part is mounted on a dual-layer board the simplest method is to use 6 or 8 vias under the die attach pad to connect the pad thermally (as well as electrically, of course) to the bottomside of the circuit board. The vias can then conduct heat to a copper pour area with a size as large as possible. Please see application note AN-1187 for guidelines about these vias and LLP packaging in general. Follow the link below to view the mentioned application note. http:// www.national.com/an/AN/AN-1187.pdf

### Derating

It is essential to keep the LMH6525/6526 die under 150°C. This means that if there is inadequate heat sinking the part may overheat at maximum load while at maximum operating ambient of 85°C. How much power (current) the part can deliver to the load at elevated ambient temperatures is purely dependent on the amount of heat sinking the part is provided with.

### LAYOUT

### Inputs

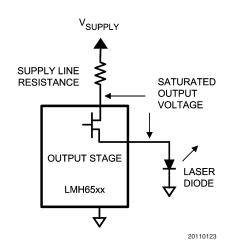

Critical inputs are the LVDS lines. These are two coupled lines of a certain impedance, mostly  $100\Omega$ . For some reason those lines could have another value but in that case the termination resistance must have the same value. The differential input resistance of the LMH6525 and LMH6526 is  $100\Omega$  and normally the impedance of the incoming transmission line matches that value. When using a flexible flat cable it is important to know the impedance of two parallel wires in that cable. Flex cables can have different pitch distances, but a commonly used cable has a pitch of 0.5 mm. When verified by TDR equipment, the measurements show an impedance of such a cable when some parameters are known. Needed parameters are the pitch (a) of the wires, the

# Application Hints (Continued)

thickness (d) en r (see *Figure 2*). When Checked under a microscope: the thickness of the wires is 0.3 mm. The pitch is 0.5 mm, while the ;r must be 1 for air. The impedance of two parallel wires is given by this formula,

$Z = (276/r) * \log\{(2*a)/d\}$

With the data above filled in this formula the result is:

### FIGURE 2. Parallel Wires

Both the measured and the calculated numbers matches very closely. The impedance of the flex cable is a physical parameter so when designing a transmission path using this flex cable, the impedance of the total path must be based on 140 $\Omega$ . There is another parameter which is the termination resistance inside the LMH6525 or LMH6526 which is  $100\Omega$ . When terminating the  $140\Omega$  transmission path with an impedance of  $100\Omega$  a mismatch will occur causing reflections on the transmission line. To solve this problem it is possible to connect directly at the input terminals of the part two resistors of  $20\Omega$  one on every pin to keep it symmetrical. Normally this causes signal loss over the total extra series resistance of  $40\Omega$  when using a voltage source for driving the transmission line. An advantage of a LVDS source is it's current nature. The current of a LVDS output is 3.5 mA and this current produces across a resistor of  $140\Omega$  a voltage of 490 mV, while this voltage across the  $100\Omega$  internal termination resistor of the part remains at 350 mV, which is conform the LVDS standard. With the usage of a series resistance of  $40\Omega$  and the termination resistor of  $100\Omega$  the total termination resistance now matches the line impedance and reflections will be as low as possible. A helpful tool for calculating impedances of transmission lines is the: 'Transmission Line Rapidesigner' available from the National Semiconductor Interface Products Group. Application Note AN-905 details the use of this handy software tool.

The Read Enable and Enable inputs are slower and much less critical. The Oscillator Enable input is toggled in combination with the write pulse so special attention should be given to this signal to insure it is routed cleanly. It may be desirable to put a termination resistor close to the LMH6526 for the Enable Oscillator line, to achieve the best turn-on and turn-off performance of the oscillator.

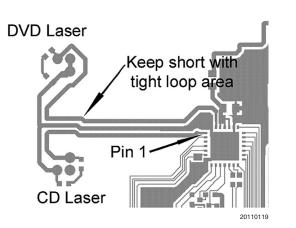

### OUTPUTS

In order to achieve the fastest output rise times the layout of the output lines should be short and tight (see *Figure 3*). It is intended that the Output B trace be routed under the decoupling capacitor and that the ground return for the laser be closely coupled to the output and terminated at the ground side of the decoupling capacitor.

LMH6525/LMH6526

### FIGURE 3. Laser Connection

The capacitance on the output lines should also be reduced as much as possible. As always the loop area of the laser current should be minimized and keep in mind that it is important not to have vias in the current path of the output lines. Via's will introduce some inductance which lead to extra overshoot on the pulse shape.

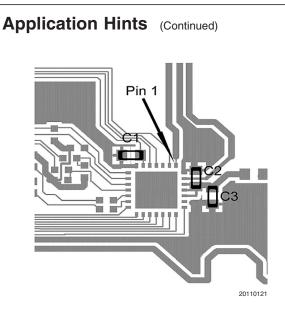

### **DECOUPLING CAPACITORS**

As mentioned before, the decoupling capacitors are critical to the performance of the part. The output section above mentioned that the power-side decoupling capacitor should be as close as possible to the  $V_{\mbox{\scriptsize DD}}$  and GND pins and that the B output should pass under the decoupling capacitor. Similarly the analog-side decoupling capacitor should be as close as possible to the  $V_{DD}A$  and GNDA pins. Figure 4 shows a layout where the analog (V<sub>DD</sub>A and GNDA) decoupling cap C1 is placed next to pins 6 and 7. (Note the layout is rotated 90 degrees from the last figure.) The ground extends into a plane that should connect to the oscillator amplitude and current setting resistors. C2 is the power-side decoupling capacitor and it can be seen placed as close to the  $V_{DD}$  and GNDB pins as possible while straddling the B output trace. This layout has also provided for a second power decoupling capacitor C3 that connects from  $V_{DD}$  to a different GND copper pour. It must be noted that the two ground planes extending from C2 and C3 must be tied together. This will be shown in the thermal section below. Bear in mind that the closeness of the parts to the LMH6525/ 6526 may be dictated by manufacturing rework considerations such that the LMH6525/6526 can be de-soldered with a hot-air rework station without the need to remove the capacitors. The relevant manufacturing organization can provide guidelines for this minimum spacing.

**FIGURE 4. Decoupling Capacitors**

### **OSCILLATOR RESISTORS**

The resistors and/or potentiometers used to set oscillator frequency or amplitude should be as close to the part as possible. If the grounds are split when using a single-sided flex circuit, it is essential that these resistors and potentiometers share the same ground as the GNDA pin and decoupling capacitor.

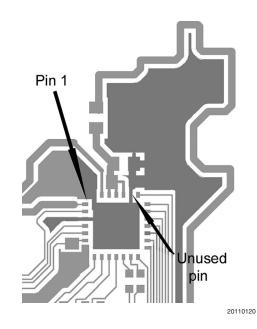

### THERMAL

As mentioned previously, the primary way to get heat out of the LLP package is by the large Die Attach Pad at the center of the part's underside. On two-layer circuits this can be done with vias. On single-sided circuits the pad should connect with a copper pour to either the GND pin or, if a better thermal path can be achieved, with the V<sub>DD</sub> pins. Be aware

that the unused pins on the part can also be used to connect a copper pour area to the Die Attach Pad. *Figure 5* Heat Sinking (with the same orientation as the first layout example) shows using the unused pin to provide a thermal path to copper pour heat sinks. In this layout the analog ground has been separated from the power ground so pin 7 is not connected to the Die Attach Paddle even though it would help remove heat from the part. The above layout is based on a single-sided circuit board. If a dual-sided circuit board was used there would also be vias on the Die Attach Pad that would conduct heat to a copper plane on the bottom side of the board.

FIGURE 5. Heat Sinking