### **LX1688**

# Multiple Lamp CCFL Controller

### **PRODUCTION DATA SHEET**

### DESCRIPTION

The LX1688 is a fixed frequency, dual that provides the control function for Cold Cathode Fluorescent Lighting (CCFL). as well as lamp current. single lamp, but is specifically designed synchronize up to 12 controllers.

The LX1688 includes highly integrated universal 'PWM or DC' dim input that allows either a PWM or DC input to adjust brightness without requiring external conditioning, since a single external capacitor CPWM can be used to integrate a PWM input. Burst mode dimming is possible if the user supplies a low patented resonant lamp strike generation components. technique.

Safety and reliability features include a current/voltage mode, switching regulator dual feedback control loop that permits regulation of maximum lamp strike voltage Regulating This controller can be used to drive a maximum lamp voltage permits the designer to provide for ample worst-case lamp strike for multiple lamp LCD panels. The IC can voltage while conservatively limiting be configured as a master or slave and maximum open circuit voltage. In addition controller features include auto the shutdown for an open or broken lamp, and a lamp fault detection with a status reporting output.

To improve design flexibility the IC includes the ability to select the polarity of both the chip enable and dim (BRITE) inputs. Also included is a switched VDD output of up to 10mA that will allow the frequency PWM signal on the BRITE user to power other circuitry that can be input and no CPWM capacitor is used. The switched on and off with the inverters controller utilizes Microsemi's patented enable input. This preserves the micro direct drive fixed frequency topology and power sleep mode with no additional

IMPORTANT: For the most current data, consult MICROSEMI's website: http://www.microsemi.com Protected by U.S. Patents 5,615,093; 5,923,129; 5,930,121; 6,198,234; Patents Pending

### **KEY FEATURES**

- Provision to Synchronize Lamp Current & Frequency With Other Controllers

- Dimming With Analog or Digital (PWM) Methods (>20:1)

- Programmable Fixed Frequency

- Adjustable Power-up Reset

- ENABLE/BRITE Polarity Selection Voltage Limiting on Step-up

- Transformer Secondary Winding

- Open Lamp Timeout Circuitry Switched VDD Output (10mÅ)

- Micro-Amp Sleep Mode

- Operates With 3.3V to 5V Supply

- 100mA Output Drive Capability

### **APPLICATIONS / BENEFITS**

- Desktop LCD Monitors

- Multiple Lamp Panels

- Low Ambient Light Displays

- High Efficiency

- Lower Cost than Conventional

- Buck/Rover Inverter Topologies

- Improved Lamp Strike Capability

- Improved Over-Voltage Control

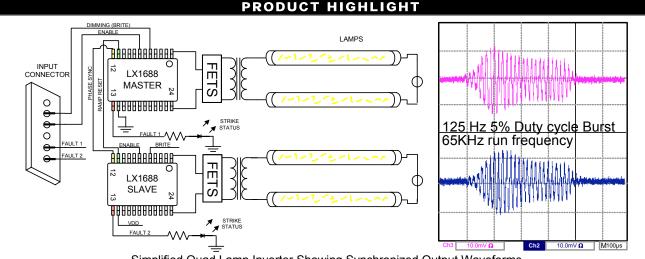

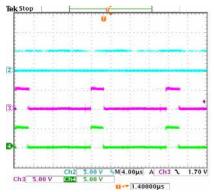

Simplified Quad Lamp Inverter Showing Synchronized Output Waveforms

| PACKAGE ORDER INFO                      |      |                     |                                                                            |  |  |  |  |  |

|-----------------------------------------|------|---------------------|----------------------------------------------------------------------------|--|--|--|--|--|

| T <sub>J</sub> (°C) MIN V <sub>DD</sub> |      | MAX V <sub>DD</sub> | PW Plastic TSSOP<br>24-Pin<br>RoHS compliant / Pb-free Transition DC: 0442 |  |  |  |  |  |

| 0 to 70                                 | 3.0V | 5.5V                | LX1688CPW                                                                  |  |  |  |  |  |

| -40 to 85                               | 3.0V | 5.5V                | LX1688IPW                                                                  |  |  |  |  |  |

Note: Available in Tape & Reel. Append the letters "TR" to the part number. (i.e. LX1688CPW-TR)

Copyright © 2001 Rev. 1.2, 2006-03-09

### Microsemi Integrated Products Division 11861 Western Avenue, Garden Grove, CA. 92841, 714-898-8121, Fax: 714-893-2570

# LX1688

### Multiple Lamp CCFL Controller

**PRODUCTION DATA SHEET**

| ABSOLUTE MAXIMUM RAT                                       | INGS              |

|------------------------------------------------------------|-------------------|

| Supply Voltage (VDD_P, VDD)                                | 6 5V              |

| Digital Inputs                                             |                   |

| Analog Inputs                                              |                   |

| Digital Outputs                                            |                   |

| Analog Outputs                                             | 0.1V to VDD +0.5V |

| Maximum Operating Junction Temperature                     |                   |

| Storage Temperature                                        |                   |

| Peak Package Solder Reflow Temp. (40 seconds max. exposure | e)260°C(+05)      |

Note 1: Exceeding these ratings could cause damage to the device. All voltages are with respect to Ground. Currents are positive into, negative out of the specified terminal.

### THERMAL DATA

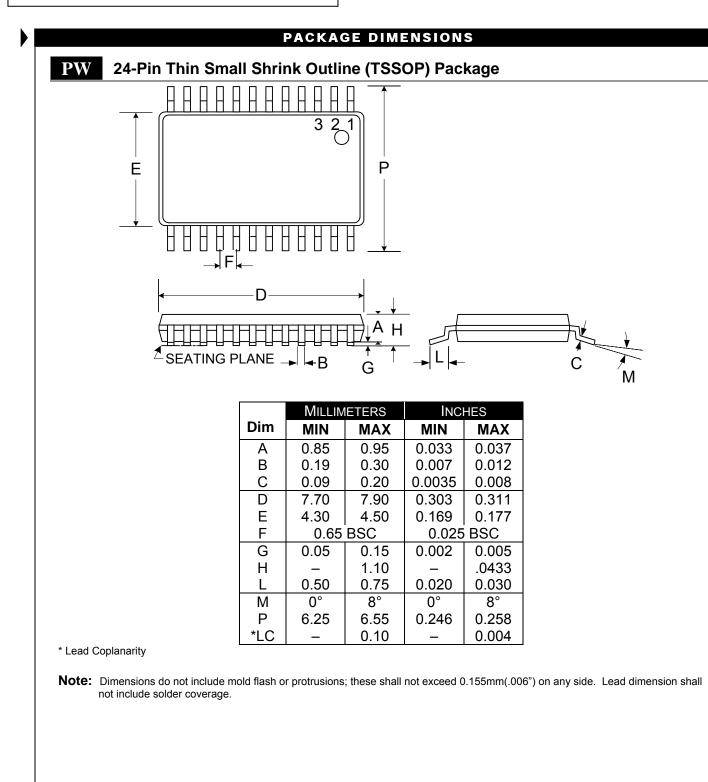

### **PW** Plastic TSSOP 24-Pin

THERMAL RESISTANCE-JUNCTION TO AMBIENT,  $\theta_{JA}$

100°C/W

Junction Temperature Calculation:  $T_J = T_A + (P_D \ge \theta_{JA})$ .

The  $\theta_{IA}$  numbers are guidelines for the thermal performance of the device/pc-board system. All of the above assume no ambient airflow.

| Pin Name | Description                                                                                                                                    | Pin Name | Description                                                                                                            |  |

|----------|------------------------------------------------------------------------------------------------------------------------------------------------|----------|------------------------------------------------------------------------------------------------------------------------|--|

| Aout     | Output Driver A                                                                                                                                | Bout     | Output Driver B                                                                                                        |  |

| VSS_P    | Connects to dedicated GND for Aout and Bout<br>Drivers                                                                                         | VDD_P    | Connects to dedicated VDD for Aout and Bout<br>Drivers                                                                 |  |

| VSS      | Connects to analog GND                                                                                                                         | VDD      | Connects to analog VDD                                                                                                 |  |

| BEPOL    | Tri-mode input pin to control the polarity of the<br>ENABLE and BRITE signal                                                                   | VDDSW    | Switchable VDD output controlled by ENABLE                                                                             |  |

| BRITE    | Analog/PWM input for brightness control                                                                                                        | TRI_C    | Connects to external capacitor C <sub>TRI</sub>                                                                        |  |

| CPOR     | Connects an external capacitor C <sub>POR</sub> to VDD and is used for setting power-up reset pulse width.                                     | OLSNS    | Analog input to detect open-lamp condition                                                                             |  |

| ENABLE   | Used to enable or disable the chip                                                                                                             | ISNS     | Analog input from lamp current, has built-in 300m offset                                                               |  |

| I_R      | Connects to external resistor R <sub>i</sub> ; for bias current setting for internal oscillator                                                | ICOMP    | Current error Amp's output; connects to external capacitor C <sub>ICOMP</sub>                                          |  |

| CPWM1    | Connects to external capacitor $C_{\text{PWM}}$ , used for integrating an external digital PWM signal for analog dimming                       | VCOMP    | Voltage error Amp's output; connects to external capacitor $C_{\text{VCOMP}},$ can be used for soft-start              |  |

| CPWM2    | Connects to external capacitor $C_{PWM}$ , used for integrating an external digital PWM signal for analog dimming.                             | VSNS     | Analog input from transformer output voltage                                                                           |  |

| RMP_RST  | If SLAVE = "0", RMP_RST is a CMOS output; if SLAVE = "1", it is a CMOS input that locks the ramp oscillation frequency to the master clock     | SLAVE    | Input control pin for setting the IC either in Master<br>or Slave mode; "1" for slave mode and "0" for<br>master mode. |  |

| PHA_SYNC | If SLAVE= "0", PHA_SYNC is a CMOS output; if SLAVE = "1", it is a CMOS input that make the $A_{OUT}/B_{OUT}$ phase synchronous with the master | FAULT    | Digital output to indicate maximum number of lam<br>striking attempts has occurred without lamp<br>ignition.           |  |

### PACKAGE PIN OUT

PW PACKAGE (Top View)

RoHS / Pb-free 100% matte Tin Lead Finish

Copyright © 2001

Rev. 1.2, 2006-03-09

PACKAGE DATA

# LX1688

# Multiple Lamp CCFL Controller

**PRODUCTION DATA SHEET**

### RECOMMENDED OPERATING CONDITIONS

| Parameter                                                 | LX1688 |     |                 |       |

|-----------------------------------------------------------|--------|-----|-----------------|-------|

|                                                           | Min    | Тур | Max             | Units |

| Supply Voltage (V <sub>DD</sub> ,V <sub>DDP</sub> )       | 3      |     | 5.5             | V     |

| BRITE Linear DC Voltage Range                             | 1      |     | 2.5             | V     |

| BRITE PWM Logic Signal Voltage Range                      | 0      |     | V <sub>DD</sub> | V     |

| Digital Inputs (SLAVE, PHA_SYNC, RMP_RST, BEPOL, ENABLE ) | 0      |     | V <sub>DD</sub> | V     |

### ELECTRICAL CHARACTERISTICS

Unless otherwise specified, specifications apply over the range:  $T_A$ =-40 to 85<sup>o</sup>C,  $V_{DD}$  (For LX1688IWP) &  $T_A$ = 0 to 70<sup>o</sup>C,  $V_{DD}$  (For LX1688CWP),  $V_{DD_P}$  = 3.0 to 5.5V.  $R_i$  = 80Kohms,  $C_{TRI}$  = 0.083 $\mu$ F

| Parameter                                                | Symbol Test Conditions         |                                                                          | LX1688                |      |      | Units |

|----------------------------------------------------------|--------------------------------|--------------------------------------------------------------------------|-----------------------|------|------|-------|

| i arameter                                               | Symbol                         | Test conditions                                                          | Min                   | Тур. | Max  | Ont   |

| DIMMER                                                   |                                |                                                                          |                       |      | _    |       |

| Conventional <sup>1</sup> Dimming                        | $V_{\text{BRITE}\_\text{MAX}}$ | $V_{BEPOL} = V_{DD}$                                                     | 2.6                   | 2.5  |      | v     |

| BRITE Input Voltage                                      | V <sub>BRITE_MIN</sub>         | V <sub>BEPOL</sub> = V <sub>DD</sub>                                     | 0.4                   | 0.5  |      |       |

| Reverse Dimming                                          | V <sub>BRITE_MAX</sub>         | $V_{BEPOL} = V_{SS}$ or float                                            | 0.4                   | 0.5  |      | v     |

| BRITE Input Voltage                                      | V <sub>BRITE_MIN</sub>         | V <sub>BEPOL</sub> = V <sub>SS</sub> or float                            | 2.6                   | 2.5  |      | v     |

| Max Brightness V <sub>BRT</sub> Voltage                  | V <sub>BRT_FULL</sub>          | $V_{BEPOL} = V_{SS}, V_{BRITE} = 0.4V$                                   | 1.90                  | 2.0  | 2.05 | V     |

| Full-darkness V <sub>BRT</sub> voltage                   | V <sub>BRT_DARK</sub>          | V <sub>BEPOL</sub> = V <sub>SS</sub> , V <sub>BRITE</sub> = 2.6V         |                       | 0    | 0.05 | V     |

| ISNS input threshold voltage                             | V <sub>TH_IAMP</sub>           | $T_A = 0$ to $70^{\circ}C$                                               | 150                   | 300  | 450  | mV    |

| ISNS input threshold voltage                             | V <sub>TH_IAMP</sub>           | T <sub>A</sub> = -40 to 85 <sup>o</sup> C                                | 150                   | 300  | 550  | m۷    |

| BRITE-to-ICOMP propagation delay                         |                                |                                                                          |                       | 2    |      | μS    |

| STRIKE AND RAMP GENERATOR                                |                                |                                                                          |                       |      |      |       |

| Max. number of strike before fault                       | N <sub>FAULT</sub>             |                                                                          | 63                    |      |      |       |

| Triangular Wave Generator Analog Output<br>Peak Voltage  | V <sub>P_TRI</sub>             |                                                                          | 2.3                   | 2.5  | 2.6  | V     |

| Triangular Wave Generator Analog Output Valley Voltage   | V <sub>V_TRI</sub>             |                                                                          | 0.15                  | 0.3  | 0.40 |       |

| Triangular Wave Generator Oscillation<br>Frequency       | F_tri                          |                                                                          | 7                     | 10   | 13   | Hz    |

| Max. Lamp Strike Frequency                               | F <sub>MAX_STK</sub>           | F <sub>MAX_STK</sub> = F <sub>LAMP</sub> X ~2.5                          | 150                   | 195  |      | KH:   |

| Lamp Run Frequency                                       | FLAMP                          | $V_{OLSNS} > 0.65V; VDD=5V$<br>$T_{A}= 0 \text{ to } 70^{\circ}\text{C}$ | 60                    | 65   | 70   | KH    |

| Lamp Run Frequency                                       | FLAMP                          | $V_{OLSNS} > 0.65V; VDD=5V$<br>$T_{A}$ =-40 to 85 <sup>o</sup> C         | 57                    | 65   | 70   | KH    |

| Lamp Run Frequency regulation over $V_{\mbox{\tiny DD}}$ | F <sub>LAMP_REG</sub>          | V <sub>OLSNS</sub> > 0.65V                                               |                       | 4    | 6    | % /   |

| OLSNS threshold voltage                                  | V <sub>TH_OLSNS</sub>          |                                                                          | 740                   | 790  | 840  | m\    |

| OLSNS hysteresis                                         | V <sub>H_OLSNS</sub>           |                                                                          | 540                   | 590  | 640  | mV    |

| OLSNS-to-ICOMP propagation delay                         | T <sub>D_OLSNS</sub>           | GBNT <sup>2</sup>                                                        |                       |      | 1    | us    |

| Fault, PHA_SYNC, RMP_RST, logic high threshold           | V <sub>H</sub>                 |                                                                          | V <sub>DD</sub> – 0.5 |      | 1    | V     |

| Fault, PHA_SYNC, RMP_RST, logic low threshold            | VL                             |                                                                          |                       | 0.7  | 1    | V     |

| Minimum Fault-pin output current                         | I_FAULT                        |                                                                          | 10                    | 15   |      | mA    |

<sup>1</sup>Conventional polarity means that the lamp brightness increases with increasing voltage on the BRITE pin. Reverse polarity means that brightness decreases with increasing voltage

<sup>2</sup> Guaranteed but not production tested

ELECTRICALS

# LX1688

# Multiple Lamp CCFL Controller

**PRODUCTION DATA SHEET**

### **ELECTRICAL CHARACTERISTICS (CONTINUED)**

| Parameter                                  | Symbol Test Conditions     |                                                                                        |      | LX1688 |      | Unit |

|--------------------------------------------|----------------------------|----------------------------------------------------------------------------------------|------|--------|------|------|

| Faranieter                                 | Symbol                     | Test conditions                                                                        | Min  | Тур.   | Max  | Unit |

| STRIKE AND RAMP GENERATOR (CONTIN          | IUED)                      |                                                                                        |      | 1      | -    |      |

| Minimum PHA_SYNC-pin output current        | I_PHA_SYNC                 | V <sub>SLAVE</sub> = 0V                                                                | 10   |        |      | mA   |

| Minimum RMP_RST-pin output current         | I_RMP_RST                  | V <sub>SLAVE</sub> = 0V                                                                | 10   |        |      | mA   |

| Minimum A_SYNC output pulse duty-cycle     | D <sub>O_ASYNC</sub>       | V <sub>SLAVE</sub> = 0V                                                                | 49   | 50     |      | %    |

| Minimum A_SYNC input pulse duty-cycle      | D <sub>I_ASYNC</sub>       | V <sub>SLAVE</sub> = V <sub>DD</sub>                                                   | 48   | 50     |      | %    |

| Minimum RMP_RST output pulse duty-cycle    | D <sub>O_RST</sub>         | V <sub>SLAVE</sub> = 0V                                                                | 10   | 17     |      | %    |

| Minimum RMP_RST input pulse duty-cycle     | D <sub>I_RST</sub>         | $V_{SLAVE} = V_{DD}$                                                                   | 5    |        |      | %    |

| OUTPUT BUFFER                              |                            |                                                                                        |      |        |      |      |

| Output Sink Current                        | I <sub>SK_OUTBUF</sub>     | $V_{AOUT, BOUT} = 1V$<br>$V_{DD} = 5.5V$                                               |      | 100    |      | mA   |

| Output Source Current                      | Is_outbuf                  | $V_{AOUT}$ , $_{BOUT}$ = 4.5V<br>$V_{DD}$ = 5.5V                                       |      | 100    |      | mA   |

| Output Sink Current                        | I <sub>SK_OUTBUF</sub>     | V <sub>AOUT</sub> , <sub>BOUT</sub> = 1V, V <sub>DD</sub> = 3V                         |      | 50     |      | mA   |

| Output Source Current                      | Is_outbuf                  | $V_{AOUT, BOUT} = 2V, V_{DD} = 3V$                                                     |      | 50     |      | mA   |

| Output Sink Current                        | I <sub>SK_OUTBUF</sub>     | $V_{AOUT}$ , $_{BOUT}$ = 1V, $V_{DD}$ = 5.5V                                           |      | 100    |      | mA   |

| PWM                                        |                            |                                                                                        |      |        | _    |      |

| VSNS threshold voltage                     | V <sub>TH_VSNS</sub>       |                                                                                        | 1.2  | 1.25   | 1.3  | V    |

| VCOMP Discharge Current                    | I <sub>D_VCOMP</sub>       |                                                                                        |      | 4      |      | m/   |

| IAMP transconductance                      | G <sub>M_IAMP</sub>        | $\Delta I_{SNS} = 0.2V$                                                                | 100  | 200    | 500  | μmł  |

| VAMP, IAMP output source current           | I <sub>S_IAMP</sub>        | $V_{\text{COMP}}, I_{\text{COMP}} = 0$                                                 |      | 75     |      | μA   |

| VAMP, IAMP output sink current             | I <sub>SK_IAMP</sub>       | $V_{COMP}$ , $I_{COMP} = V_{DD}$                                                       |      | 75     |      | μA   |

| ICOMP discharge current                    | I <sub>D_ICOMP</sub>       |                                                                                        |      | 10     |      | m    |

| VAMP transconductance                      | $G_{M\_ICMP}$              | $\Delta V_{SNS} = 0.1V$                                                                | 200  | 500    | 800  | μmł  |

| ICOMP-to-output propagation delay          | T <sub>D_ICOMP</sub>       |                                                                                        |      | 1100   |      | nS   |

| BIAS                                       |                            |                                                                                        |      |        |      |      |

| Voltage at Pin I_R                         | V_IR                       |                                                                                        | 0.95 |        | 1.05 | V    |

| Pin I_R max. source current                | I <sub>MAX_IR</sub>        |                                                                                        |      | 50     |      | μA   |

| Power-on Reset Pulse Width                 | T <sub>POR</sub>           | C <sub>POR</sub> =.1uF                                                                 |      | 31     |      | ms   |

| Minimum V <sub>DDSW</sub> sourcing Current | I <sub>MIN_VDDSW</sub>     | $(V_{DD} - V_{DDSW}) < 0.2V$                                                           | 10   | 25     |      | m/   |

| V <sub>DDSW</sub> Off Current              | I <sub>OFF_VDDSW</sub>     | $V_{\text{ENABLE}} = 0.8V, V_{\text{BEPOL}} = V_{\text{DD}}$<br>$V_{\text{DDSW}} = 0V$ |      | 1      | 15   | μA   |

| GENERAL                                    | •                          |                                                                                        |      |        |      |      |

| Operating Current                          | I <sub>DD</sub>            | $V_{DD} = V_{DD_P} = 5V$                                                               |      | 5.5    | 8    | m/   |

| Output buffer operating current            | I <sub>DD_P</sub>          | $V_{OLSNS} = V_{DD} = V_{DD_P} = 5V,$<br>$C_A = C_B = 1000 pF$                         |      | 2      | 4    | m/   |

| ENABLE logic threshold                     | $V_{\text{TH}\_\text{EN}}$ |                                                                                        | 0.8  | 1.7    | 2.4  | V    |

| ENABLE threshold hysteresis                | V <sub>TH_EN</sub>         |                                                                                        |      | 0.2    |      | V    |

| Sleep-mode current (see table-1 for Pin    | I <sub>DD_SLEEP</sub>      | $V_{\text{ENABLE}} = 0.8V$<br>( $V_{\text{BEPOL}} = V_{\text{DD}}$ or float)           |      | 20     | 50   |      |

| ENABLE polarity)                           | I <sub>DD_SLEEP</sub>      | $V_{\text{ENABLE}} = 2.5V$<br>( $V_{\text{BEPOL}} = V_{\text{DD}}$ or float)           |      | 20     | 50   | μA   |

| VDD P Leakage in Sleep Mode                | I <sub>DD_SLEEP</sub>      | $V_{\text{ENABLE}} = 0.8V$<br>( $V_{\text{BEPOL}} = V_{\text{SS}}$ )                   |      | 20     | 300  | μ,   |

|                                            | I <sub>DD_SLEEP</sub>      | $V_{\text{ENABLE}} = 2.5V$<br>( $V_{\text{BEPOL}} = V_{\text{SS}}$ )                   |      | 20     | 300  |      |

| UVLO threshold                             | V <sub>TH_UVLO</sub>       | Rising turn-on threshold                                                               | 2.6  | 2.8    | 2.9  | V    |

| UVLO hysteresis                            | V <sub>H_UVLO</sub>        | Falling turn-off hysteresis                                                            |      | 190    |      | m∖   |

ELECTRICALS

# LX1688

# Multiple Lamp CCFL Controller

**PRODUCTION DATA SHEET**

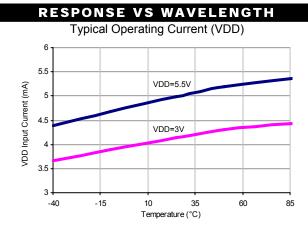

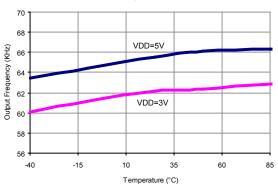

Output Frequency Vs Temperature

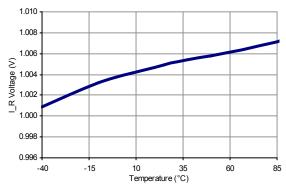

I\_R Voltage Vs Temperature VDD=V

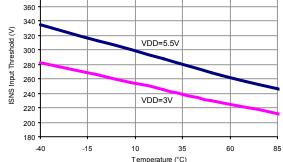

ISNK STEP RESPONSE ISNS Input Threshold Voltage Vs Temperature

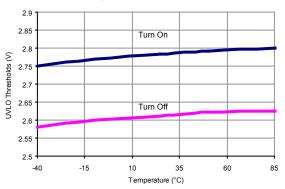

Under Voltage Lockout Vs Temperature

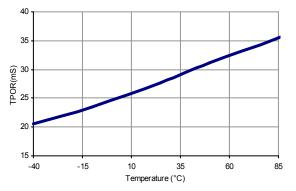

Power-on-Reset Pulse Width Vs Temperature VDD=5V

# LX1688

# Multiple Lamp CCFL Controller

**PRODUCTION DATA SHEET**

| TABLE 1                          |                                                                                        |  |  |  |  |  |  |  |

|----------------------------------|----------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| ENABLE POLARITY                  | DIMMING POLARITY*                                                                      |  |  |  |  |  |  |  |

| + (HI = CHIP_ON, LOW = CHIP_OFF  | CONVENTIONAL                                                                           |  |  |  |  |  |  |  |

| + (HI = CHIP_ON, LOW = CHIP_OFF) | REVERSE                                                                                |  |  |  |  |  |  |  |

| - (LOW = CHIP_ON, HI = CHIP_OFF) | REVERSE                                                                                |  |  |  |  |  |  |  |

|                                  | ENABLE POLARITY<br>+ (HI = CHIP_ON, LOW = CHIP_OFF<br>+ (HI = CHIP_ON, LOW = CHIP_OFF) |  |  |  |  |  |  |  |

\* Conventional polarity means that the lamp brightness increases with increasing voltage on the BRITE pin. Reverse polarity means that brightness decreases with increasing voltage

### OPERATIONAL MODES

| Controller<br>Mode | Controller<br>Operation | Input Pin:<br>OLSNS | Input Pin:<br>SLAVE | Output Pin:<br>FAULT | Pin: RMP_RST             | Pin: A_SYNC                  | Lamp<br>Frequency    |

|--------------------|-------------------------|---------------------|---------------------|----------------------|--------------------------|------------------------------|----------------------|

|                    | Run                     | > 0.6V              | VSS                 | L                    | Output: F <sub>INT</sub> | Output: F <sub>INT</sub> / 2 | F <sub>INT</sub> / 2 |

| Master             | Striking                | < 0.2V              | VSS                 | L                    | Output: F <sub>INT</sub> | Output: F <sub>INT</sub> / 2 | Ramping up /<br>down |

|                    | Fault                   | х                   | VSS                 | Н                    | Output: FINT             | Output: F <sub>INT</sub> / 2 | Off                  |

|                    | Run                     | > 0.6V              | VDD                 | L                    | Input: F <sub>EXT</sub>  | Input: F <sub>EXT</sub> / 2  | F <sub>EXT</sub> / 2 |

| Slave              | Striking                | < 0.2V              | VDD                 | L                    | Input: F <sub>EXT</sub>  | Input: F <sub>EXT</sub> / 2  | Ramping up /<br>down |

| -                  | Fault                   | х                   | VDD                 | Н                    | Input: F <sub>EXT</sub>  | Input: F <sub>EXT</sub> / 2  | Off                  |

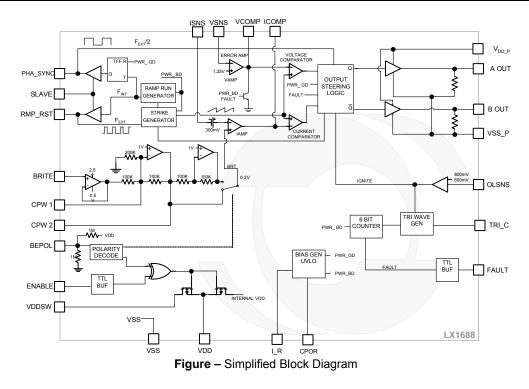

### SIMPLIFIED BLOCK DIAGRAM

Copyright © 2001 Rev. 1.2, 2006-03-09

Microsemi Integrated Products Division 11861 Western Avenue, Garden Grove, CA. 92841, 714-898-8121, Fax: 714-893-2570

LX1688

# Multiple Lamp CCFL Controller

### **PRODUCTION DATA SHEET**

The LX1688 is a backlight controller specifically designed with a special feature set needed in multiple lamp desktop monitors, and other multiple lamp displays. While utilizing the same architecture as Microsemi's LX1686 controller it eliminates the synchronized digital dimming and adds, lamp 'strike' count out timer, lamp fault status output, and external clock input/output that permits multiple controllers to synchronize their output current both in frequency and phase.

### **OPERATION FROM 3.3V AND/OR 5.0V INPUT SUPPLY**

The LX1688 is designed to operate and meet all specifications at  $3.3V \pm 10\%$  to  $5.0V \pm 10\%$ . The under voltage lockout is set at nominally 2.8V with a 190mV hysteresis.

### MASTER/SLAVE CLOCK SYNCHRONIZATION

One or more controllers (up to 11) may be designated as slave controllers and receive ramp reset and phase synchronization from the designated master controller. This will allow up to 12 lamps (24 with two lamps in series/controller design) to all operate in phase and frequency synchronization. This is important to prevent random interference between lamps through unpredictably changing electric and magnetic fields that will inevitably link them.

The LX1688 has two independent oscillators, one for lamp strike and one for the lamp run frequency. The strike oscillator ramps the operating frequency slowly up and down when the open lamp sense input (OLSNS) indicates the lamp is not ignited. During this lamp strike condition the operating frequency of each IC will vary up and down as needed to strike its lamp. The controller is so designed that the master controller clock remains at the pre-selected frequency for fully ignited lamps even while striking. Likewise the designated slave controller will not alter the frequency or phase of the master clock during its strike phase. Thus each controller will vary its frequency as needed to strike its lamp then it will synchronize to the master clock frequency and phase.

The TRI\_C wave generator (see Block Diagram) sets the rate of operating frequency variation during lamp strike. The TRI\_C generator is connected to a 6-bit counter that times out after 63 cycles and then latches the FAULT output high if the OLSNS input indicates no lamp current is flowing. Even in the case of timeout fault the master controller clock will continue to provide synchronization to the slave controllers.

When synchronizing more than one controller the Ramp Reset (RMP\_RST), Phase Sync (PHA\_SYNC),

and Slave Input/Output are used. RMP\_RST and PHA\_SYNC should be connected between all the controllers. The master controller should have its SLAVE pin connected to VSS (GND) and the slave controllers SLAVE input to VDD (High).

### **BEPOL INPUT**

The BEPOL pin is a tri-mode input that controls the polarity of the ENABLE and BRITE input signals. Depending on the state of this pin (VDD, floating, or VSS) the controller can be set to allow active high enable with active high full brightness or active high or low enable with active low full brightness (see Table 1).

### **BRITE INPUT (DIMMING INPUT)**

The BRITE input is capable of accepting either a DC voltage ( $\geq .5V$  to  $\leq 2.5V$ ) or a PWM digital signal that is clamped on chip ( $\leq .5V$  or  $\geq 2.5V$ ). A digital signal can either be passed unfiltered to effect pulse 'digital' dimming or filtered with a capacitor to effect analog dimming with a digital PWM signal.

Analog Dimming Methods:

- Mechanical or digital potentiometer set to provide 1V to 2.5V on the wiper output. A filter cap from BRITE to signal ground is recommended.

- D/A converter output directly connected to BRITE input. A R/C filter using a capacitor from the CPW1 input to ground for applications where the ADC output may contain noise sufficient to modulate the BRITE input.

- A high frequency PWM digital logic pulse connected directly to the BRITE input. The Brightness (BRT, internal node) output will be sensitive only to the PWM duty cycle, and not to the PWM signal amplitude, so long as the amplitude exceeds 2.6V for a logic high (1) and is less than .4V for a logic (0). This pulse frequency will typically be between 1KHz and 100KHz and will not be synchronized with the LCD video frame rate. A capacitor (CPWM) between CPW1 and CPW2 will integrate the PWM signal for use by the controller.

Digital Dimming Methods:

• Low frequency PWM digital logic pulses connected directly to the BRITE input. As above the Brightness (BRT internal) will be sensitive only to the PWM duty cycle, and not to the PWM signal amplitude, so long as the amplitude exceeds 2.6V for a logic high (1) and is less than .4V for a logic (0). This pulse frequency will typically be in the range of 90-320Hz.

LX1688

# Multiple Lamp CCFL Controller

**PRODUCTION DATA SHEET**

and may or may not be externally synchronized to the LCD video frame rate. It will directly gate the signal BRT. CPWM should not be used in this case.

### FAULT PIN

The fault pin is a digital output that indicates that the maximum numbers of strike attempts has occurred without lamp ignition. In this condition the FAULT pin will go active high with typically 20mA drive capability. Holding the OLSNS pin low (<200mV) will also force timeout and activate the FAULT pin. When used as a master, fault condition true does not inhibit master clock outputs PHA\_SYNC and RMP\_RST.

### I\_R PIN

The run mode frequency of the output is one half the internal ramp frequency, which is proportional to a bias current set by resistor RI of 80.6K. The output frequency

can thus be adjusted by varying the value of RI-R, the typical range from about 50K to 100K. Since there is some variation in the frequency due to change in the input supply (VDD) it is recommended that the value of RI-R be selected at the nominal input voltage.

# SLEEP MODE (ENABLE SIGNAL) AND SWITCHED VDD (VDDSW)

Since the LX1688 can be used in portable battery operated systems, a very low power sleep mode is included. The IC will consume less than  $10\mu$ A quiescent current from both the VDD and VDD\_P pins combined, when the ENABLE pin is deactivated. The polarity of the ENABLE pin is programmable by the BEPOL input (see table 1). In addition the controller provides a switched supply pin VDDSW this output supplies at least 10mA at VDD – .2V for external circuitry. This output can be used to power additional circuitry that can be enabled with the controller.

$F_{TRI} = \frac{1}{(25 \times R_I \times C_{TRI})} [Hz]$

$B_{\text{WIEA}_{\text{MIN}}} = \frac{0.000048}{C_{\text{ICOMP}}} \text{ [Hz]}$

$T_{ss} = 4.500.000 \times C_{VCOMP}$  [sec]

Minimum Current Error Amp Bandwidth, BWIEA MIN

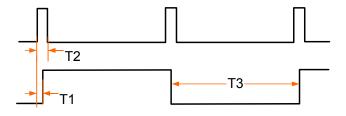

### **RMP\_RST** AND **PHA\_SYNC** PIN TIMING REQUIREMENT WITH SLAVE MODE OPERATION

When the LX1688 is configured for slave mode operation, and RMP\_RST and PHA\_SYNC is supplied from an external source, the signal timing should be met as outlined below.

RMP\_RST should be 2 times frequency of lamp frequency and duty should be 10 to 13%, and PHA\_SYNC should be generated by divide by 2 of RMP\_RST signal. Phase of these signals should be met the as shown, note the delay between the RMP\_RST and PHA\_SYNC signals:

|        | Min | Тур | Max | Unit |

|--------|-----|-----|-----|------|

| T1     | 150 | 250 |     | nsec |

| T2     | 10  |     | 13  | %    |

| Т3     | 49  | 50  | 51  | %    |

| Tr, Tf |     |     | 100 | nsec |

T3 duty is 50% of operating frequency.

www.Microsemi.com

APPLICATIONS

### **BIAS & TIMING EQUATIONS**

Formula 2:

Lamp Frequency ( $A_{OUT}$ 's switching frequency),  $F_{LAMP}$

# $F_{LAMP} = \frac{1}{200e \cdot 12 \times R_I} [Hz]$ Formula 4:

Minimum Voltage Error Amp Bandwidth, B<sub>WVEA MIN</sub>

$$B_{WVEA\_MIN} = \frac{0.000048}{C_{VCOMP}} [Hz]$$

Formula 6:

Minimum Power-on Reset Pulse Width,

$$T_{MIN_POF}$$

$T_{MIN_POR} = 2.3e6 \times C_{POR} [sec]$

Copyright © 2001 Rev. 1.2, 2006-03-09

Formula 1:

Formula 3:

Formula 5:

Softstart time, T<sub>SS</sub>

Triangular Wave Generator Frequency, F<sub>TRI</sub>

Page 8

# LX1688

### Multiple Lamp CCFL Controller

**PRODUCTION DATA SHEET**

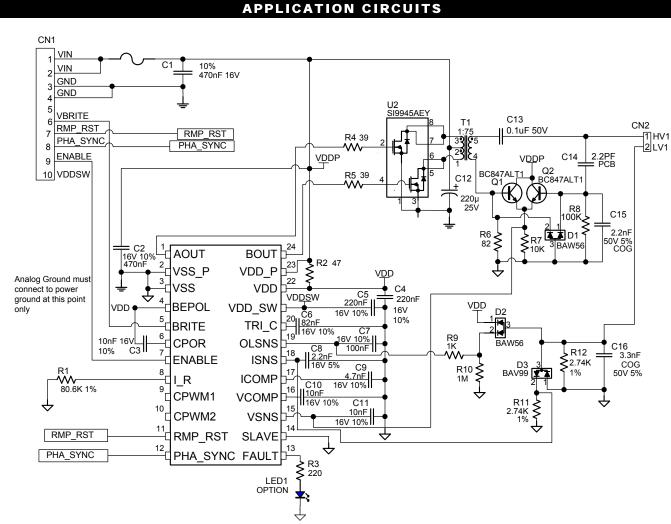

Figure 1 – Schematic for LX1688 Inverter Module Configured as Master

LX1688

# Multiple Lamp CCFL Controller

**PRODUCTION DATA SHEET**

### APPLICATION INFORMATION

### **APPLICATION EXAMPLE WITH LX1688**

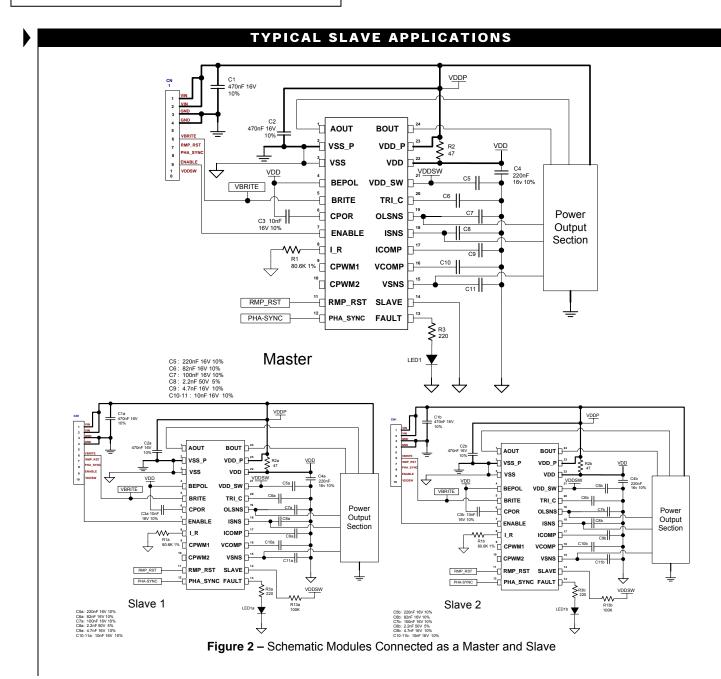

This section will highlight the features of LX1688 controller by showing a practical example. Three identical inverter modules are connected to each other and each module drives a single lamp. One module configured as a master and two others configured as slaves.

A complete schematic hooked up a a master is given in Figure 1, the schematic provides all necessary functions such as high voltage feedback for regulation the peak lamp voltage, short-circuit protection, open lamp sensing and lamp current regulation needed for a typical application. The section follows with measurement waveforms and list of material of the actual modules. For more detail design procedure and circuit description please refer to application note (AN-13), which is available in Microsemi's web site. **INPUT VOLTAGE**

# The LX1688 controller can operate at 3.3 to $5.0V \pm 10\%$ , in this application all modules were driven by the same power voltage (a constant 5.0V), which provides VDD for controllers, and input voltage for the power section. Notice that VDD feeds all analog signals and VDD\_P feeds only the output driver stage, these two signals should be filtered separately (Figure 1).

### SETTING LAMP FREQUENCY

The value of R1 determines magnitude of internal current sources that set timing parameters. Equation (2) gives the relationship between Lamp frequency (FLAMP) and (RI\_R), R1 in schematic. For this application we choose R6=80.6 K $\Omega$ , which results to a lamp frequency at 62.0 KHz.

### DIMMING

The LX1688 includes highly integrated universal 'PWM or DC' dim input that allows either a PWM or DC input without requiring external conditioning.

In this application we choose Digital Dimming by applying a PWM signal to BRITE pin.

All modules were driven by the same PWM signals, but notice that it is possible to dim each module quite separately.

BEPOL pin has three different modes (see table 1), in this application it is connected to VDD which means active high enable with active high full brightness.

The PWM signal can be varied in frequency between 48-320 HZ. No capacitor between CPWM1 and CPWM2 is necessary.

### SETTING MASTER/SLAVE CONFIGURATION

Simply connecting pin 14 to the ground for a master and to the VDD for a slave will do master and slave configuration. As shown in figure 2, module (A) configured as master and modules (B) and (C) configured as slaves.

### SYNCHRONIZATION OF FREQUENCY AND PHASE

To synchronize the Lamp frequency and phase of all modules, it is required to connect the RMP\_RST pin of all the modules together and connect PHA\_SYNC pin of all the modules together.

### LAYOUT CONSIDERATION

By designing the layout in a proper way we can reduce the overall noise and EMI for the module.

The gate drivers for MOSFETs should have an independent loop that doesn't interface with the more sensitive analog control function, therefore LX1688 provides two power inputs with separate ground pins (analog/signal), VDD feeds all analog signals and VDD\_P feeds only the output drivers, as shown in figure1 these two pins (pin 23, 24) are separated and filtered by R14, C2 and C7. The connection of two ground pins should be at only one point as shown in figure1.

The power traces should be short and wide as possible and all periphery components such capacitors should be located as closed as possible to the controller.

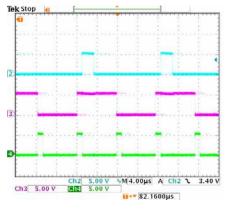

### **OSCILLOSCOPE WAVEFORMS PICTURES**

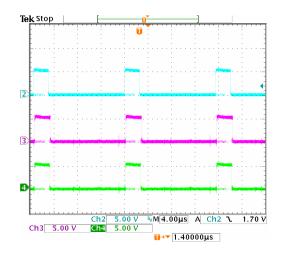

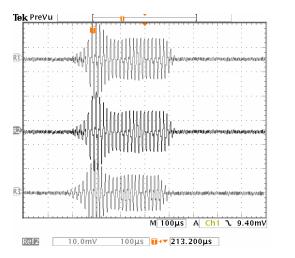

The following oscilloscope waveform pictures are taken from the actual circuits and will show the operation of the modules in different modes when three identical modules are synchronized, one as a master, and two others as slaves.

# LX1688

### Multiple Lamp CCFL Controller

**PRODUCTION DATA SHEET**

www.Microsemi.com

Copyright © 2001 Rev. 1.2, 2006-03-09

LX1688

# Multiple Lamp CCFL Controller

**PRODUCTION DATA SHEET**

### THEORY OF OPERATION

### Multiple Lamp Sync

The figure 3 shows the sync signals (PHA\_SYNC and RMP\_RST) timing relationship to Gate signal AOUT, for the master module. AOUT and PHA\_SYNC running at the same frequency and RMP RST signal has the twice frequency.

Figure 3- Sync signals-Timing relationship to A<sub>OUT</sub> CH2= A<sub>OUT</sub>(Master), CH3=PHA\_SYNC, CH4=RMP\_RST

### <u>Strike Mode</u>

Every IC includes a separate strike controller that operates from the primary oscillator; therefore the strike controller is independent of the sync signals. The following oscilloscope waveform picture is taken when the master module is on striking mode and the salves are on running mode.

Figure 5- Master is in striking mode while slaves are in running mode CH2= A<sub>OUT</sub>(Master), CH3=A<sub>OUT</sub>(Slave1), CH4=A<sub>OUT</sub>(Slave2)

### **Output Drivers**

The figure 4 shows the gate signals of the modules, which are operating, in running mode during digital dimming with 95% duty cycle. As shown all signals are synchronized. The difference between each signal's duty cycles is because each lamp has an independent control loop.

Figure 4- Output drivers of both Master and Slaves.  $CH2=A_{OUT}(Master),$  $CH3=A_{OUT}(Slave1),$  $CH4=A_{OUT}(Slave2)$  www.Microsemi.com

# LX1688

# Multiple Lamp CCFL Controller

**PRODUCTION DATA SHEET**

### THEORY OF OPERATION

### **Digital Dimming**

### **Output currents**

Figure 8 shows the output current of master and slaves during digital dimming with 5% duty cycle. The lamp currents are operating in phase and frequency synchronization. This prevents random interface between controllers and reduces EMI.

Figure 8- Output current during digital dimming with 5% duty cycle R1= out(Master) R2=Iout(Slave1) R3=Iout(Slave2) Lamp Current at 10mA/Div

# LX1688

# Multiple Lamp CCFL Controller

**PRODUCTION DATA SHEET**

### LX1688 MODULE BOARD LIST OF MATERIAL

| Reference  | Part Description                                    | Manufacture           | Part Number    |

|------------|-----------------------------------------------------|-----------------------|----------------|

| Designator |                                                     | Wanulacture           | 1              |

| U1         | Backlight Controller                                | Microsemi             | LX1688         |

| U2         | Dual N-Channel MOSFET                               | Siliconix<br>Motorola | Si9945AEY      |

| Q1, Q2     |                                                     |                       | BC847ALT1      |

| D1, D2     | Dual Diode                                          | Motorola              | BAW56          |

| D3         | Dual Diode                                          | Philips               | BAV99          |

| LED1       | LED                                                 |                       |                |

| R1<br>R2   | 80.6K 1% 1/16 W<br>47 ohm 5% 1/8 W                  |                       |                |

| R2<br>R3   | 220 ohm 5% 1/8 W                                    |                       |                |

|            |                                                     |                       |                |

| R4, R5     | 39 ohm 5% 1/16 W                                    |                       |                |

| R6         | 82 ohm 5% 1/16 W                                    |                       |                |

| R7         | 10K 5% 1/16 W                                       |                       |                |

| R8         | 100K 5% 1/16 W                                      |                       |                |

| R9         | 1K 5% 1/16 W                                        |                       |                |

| R10        | 1 M 5% 1/16 W                                       |                       |                |

| R11, R12   | 2.74K 1% 1/16 W                                     |                       |                |

| C1, C2     | 470nF 16V 10% X7R 1206                              |                       |                |

| C3         | 10nF 16V 10% 0805                                   | NOVACAP               |                |

| C4         | 220nF 16V 10% X7R 1206                              |                       |                |

| C5         | 220nF 16V 20% 0805                                  | AVX                   | 0805YC224MAT2A |

| C6         | 82nF 16V 10% X7R 0603                               | AVX                   | 0603YC823KAT2A |

| C7         | 100nF 16V 20% X7R                                   | AVX                   | 0603YC104MAT2A |

| C8         | 2.2nF 50V 10%                                       | NOVACAP               | 0603B22K500NT  |

| C9         | 4.7nF 16V 10% X7R                                   | AVX                   | 0603YC472KAT2A |

| C10, C11   | 10nF 16V 10% X7R                                    | AVX                   | 0603YC103KAT2A |

| C12        | 220µF Tantalum 7343                                 | AVX                   |                |

| C13        | 220pF 2KV 5% COG                                    | NOVACAP               | 1206N221J202NT |

| C14        | 2.2pF PCB                                           |                       |                |

| C15        | 2.2nF 50V 5% COG                                    | AVX                   | 08055A222JAT2A |

| C16        | 3.3nF 50V 5% COG                                    | NOVACAP               | 0805N332J500NT |

| T1         | Low profile, High voltage xfmr,<br>turns ratio 1:75 | Microsemi             | SGE2645-1      |

| CN1        | Connector, 10 pin                                   | Molex                 | 53261-1090     |

| CN2        | Connector, 2 pin                                    | Molex                 |                |

Table 2- List of material for LX1688 inverter module

LX1688

# Multiple Lamp CCFL Controller

**PRODUCTION DATA SHEET**

### LX1688

# Multiple Lamp CCFL Controller

**PRODUCTION DATA SHEET**

### NOTES

NOTES

www.Microsemi.com

PRODUCTION DATA – Information contained in this document is proprietary to Microsemi and is current as of publication date. This document may not be modified in any way without the express written consent of Microsemi. Product processing does not necessarily include testing of all parameters. Microsemi reserves the right to change the configuration and performance of the product and to discontinue product at any time.

Downloaded from Elcodis.com electronic components distributor