Datasheet

# Numonyx<sup>®</sup> Omneo<sup>™</sup> P8P PCM

128-Mbit Parallel Phase Change Memory

## **Product Features**

- High Performance Read

- 115 ns initial read access

- 135 ns initial read access

- 25 ns 8-word asynchronous-page read

- Architecture

- Asymmetrically-blocked architecture

- Four 32-KByte parameter blocks: top or bottom configuration

- 128-KByte main blocks

- Serial Peripheral Interface (SPI) to enable lower pin count on-board programming

- Phase Change Memory (PCM)

- Chalcogenide phase change storage element

- Bit alterable write operation

- Voltage and Power

- V<sub>CC</sub> (core) voltage: 2.7 V 3.6 V

- V<sub>CCO</sub> (I/O) voltage: 1.7 V 3.6 V

- Standby current: 80 µA (Typ)

- Quality and Reliability

- More than 1,000,000 write cycles

- 90 nm PCM technology

- Temperature

- Operating temperature -30 °C to +85 °C (135ns initial read access)

- Operating temperature 0 °C to +70 °C (115ns initial read access)

- Security

- One-Time Programmable Registers:

- 64 unique factory device identifier bits

- 2112 user-programmable OTP bits

- Selectable OTP Space in Main Array:

- Four pre-defined 32-KByte blocks (top or bottom configuration)

- Three adjacent Main Blocks available for boot code or other secure information

- Absolute write protection:  $V_{PP} = V_{SS}$

- Power-transition erase/program lockout

- Individual zero-latency block locking

- Individual block lock-down

- Simplified Software Management

- No block erase or cleanup required

- Bit "twiddle" in either direction (1:0, 0:1)

- 35 µs (Typ) program suspend

- 35 µs (Typ) erase suspend

- Numonyx® Flash Data Integrator optimized

- Scalable Command Set and Extended Command Set compatible

- Common Flash Interface capable

- Density and Packaging

- 128 Mbit density

- 56-Lead TSOP package

- 64-Ball Numonyx® Easy BGA package

INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH NUMONYX<sup>™</sup> PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN NUMONYX'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, NUMONYX ASSUMES NO LIABILITY WHATSOEVER, AND NUMONYX DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO SALE AND/OR USE OF NUMONYX PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT. Numonyx products are not intended for use in medical, life saving, life sustaining, critical control or safety systems, or in nuclear facility applications.

Numonyx B.V. may make changes to specifications and product descriptions at any time, without notice

Numonyx B.V. may have patents or pending patent applications, trademarks, copyrights, or other intellectual property rights that relate to the presented subject matter. The furnishing of documents and other materials and information does not provide any license, express or implied, by estoppel or otherwise, to any such patents, trademarks, copyrights, or other intellectual property rights.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Numonyx reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

Contact your local Numonyx sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an order number and are referenced in this document, or other Numonyx literature may be obtained by visiting the Numonyx webbiest at http://www.numonyx.com.

Numonyx, the Numonyx logo, StrataFlash, Axcell, Forté, and Omneo are trademarks or registered trademarks of Numonyx B.V. or its subsidiaries in other countries.

\*Other names and brands may be claimed as the property of others.

Copyright © 2010, Numonyx, B.V., All Rights Reserved.

| 1.0  |                | escription                                       |    |

|------|----------------|--------------------------------------------------|----|

|      |                | duction                                          |    |

|      |                | uct Overview                                     |    |

|      |                | огу Мар                                          |    |

| 2.0  | Package II     | nformation                                       | 11 |

|      |                | ead TSOP                                         |    |

|      | 2.2 64-B       | all Easy BGA Package                             | 12 |

| 3.0  | Pinouts an     | nd Ballouts                                      | 14 |

| 4.0  | Signals        |                                                  | 16 |

| 5.0  | -<br>Bus Opera | tions                                            | 17 |

| 0.0  | •              | ls                                               |    |

|      |                | 25                                               |    |

|      |                | ut Disable                                       |    |

|      |                | dby                                              |    |

|      | 5.5 Rese       | t                                                | 18 |

| 6.0  | Command        | Set                                              | 19 |

|      | 6.1 Devic      | ce Command Codes                                 | 19 |

|      | 6.2 Devic      | ce Command Bus Cycles                            | 20 |

| 7.0  | Read Oper      | ation                                            | 22 |

|      | 7.1 Read       | I Array Command                                  | 22 |

|      |                | I Identifier Command                             |    |

|      |                | I Query Command                                  |    |

|      |                | r ID Mode Data                                   |    |

|      |                | y (CFI) Data                                     |    |

| 8.0  |                | Operations                                       |    |

|      |                | d Program                                        |    |

|      |                | Iterable Word Write Command                      |    |

|      |                | ered Program Command<br>Iterable Buffer Write    |    |

|      |                | Iterable Buffer Program                          |    |

|      |                | ram Suspend                                      |    |

|      |                | ram Resume                                       |    |

|      |                | ram Protection                                   |    |

| 9.0  | Erase          |                                                  | 28 |

|      |                | < Erase                                          |    |

|      |                | e Suspend Command                                |    |

|      | 9.3 Erase      | e Resume                                         | 29 |

| 10.0 | Security M     | lode                                             | 30 |

|      | -              | < Locking                                        |    |

|      | 10.2 Perm      | nanent One Time Programmable (OTP) Block Locking | 33 |

| 11.0 | Registers.     |                                                  | 36 |

|      | •              | I Status Register                                |    |

|      | 11.2 Syste     | em Protection Registers                          | 37 |

| 12.0 | Serial Peri    | pheral Interface (SPI)                           | 40 |

|      |                | Dverview                                         |    |

|      |                | Signal Names                                     |    |

|      | 12.3 SPI N     | Memory Orginization                              | 41 |

|      |                |                                                  |    |

|      | 12.4                             | SPI Instruction                                                                                                                   | 43                   |

|------|----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|----------------------|

| 13.0 | 13.1<br>13.2                     | er and Reset Specification<br>Power-Up and Power-Down<br>Reset Specifications<br>Power Supply Decoupling                          | 56<br>56             |

| 14.0 | 14.1<br>14.2                     | Ratings and Operating Conditions<br>Absolute Maximum Ratings<br>Operating Conditions<br>Endurance                                 | 58<br>58             |

| 15.0 | <b>Elect</b><br>15.1<br>15.2     | rical Specifications<br>DC Current Characteristics<br>DC Voltage Characteristics                                                  | 60                   |

| 16.0 | 16.1<br>16.2                     | haracteristics<br>AC Test Conditions<br>Capacitance<br>AC Read Specifications<br>AC Write Specifications<br>SPI AC Specifications | 62<br>62<br>63<br>65 |

| 17.0 | Prog                             | ram and Erase Characteristics                                                                                                     | 71                   |

| 18.0 | Orde                             | ring Information                                                                                                                  | 72                   |

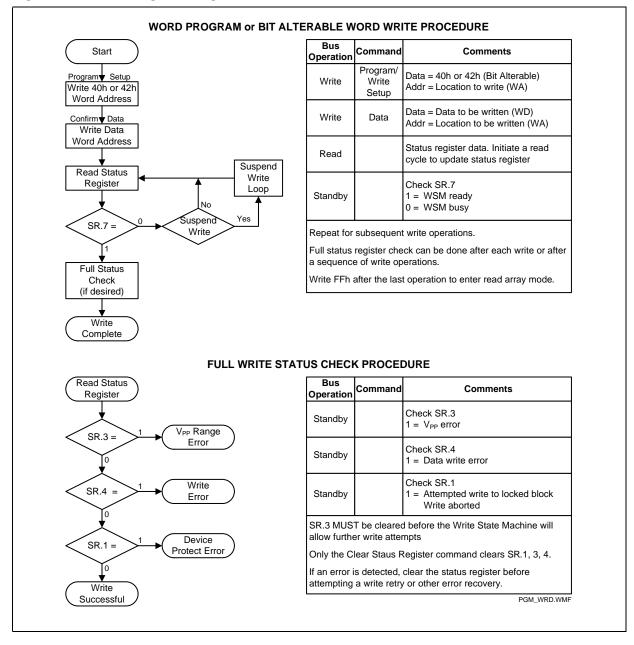

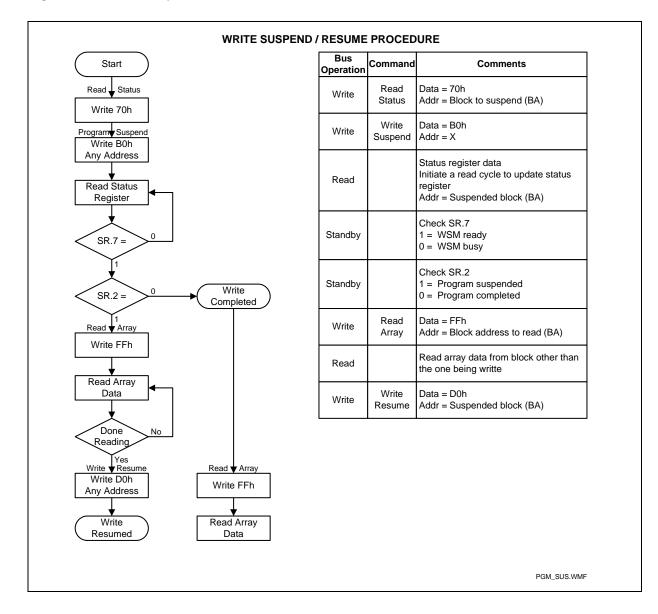

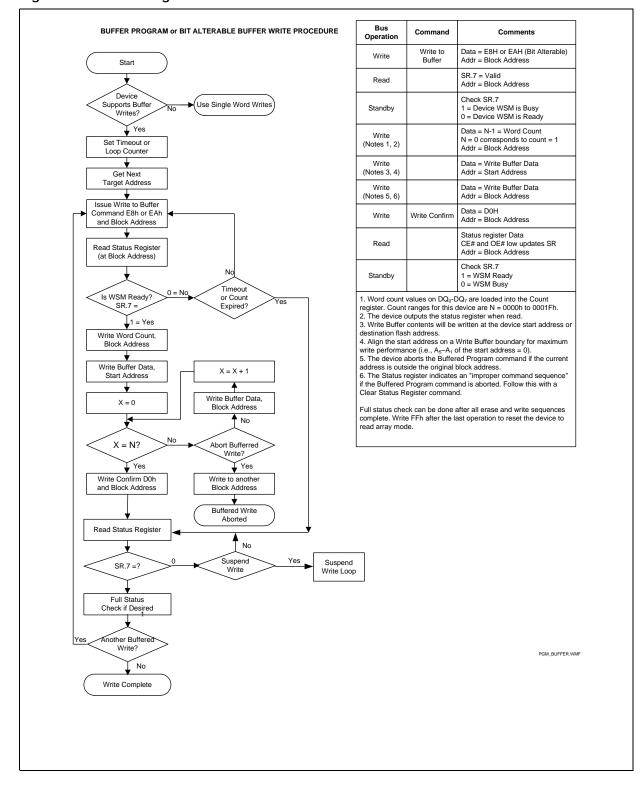

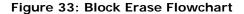

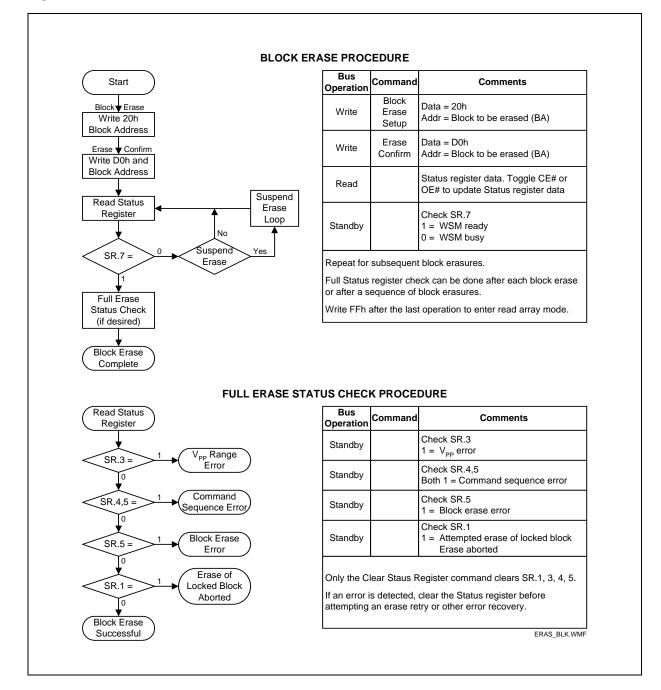

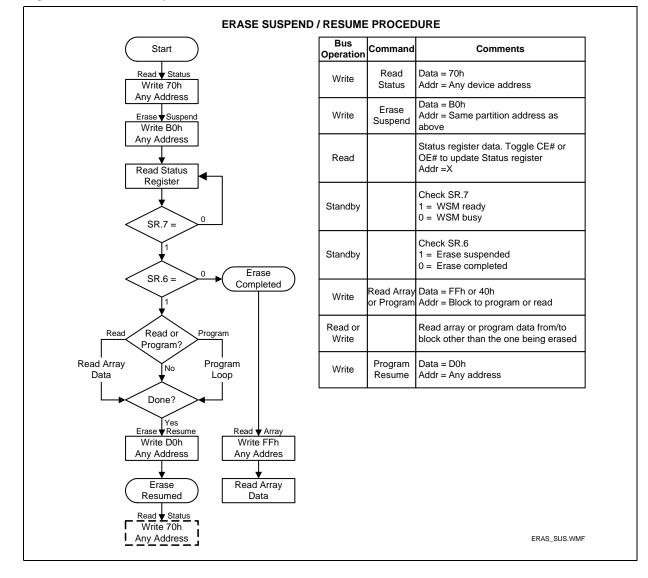

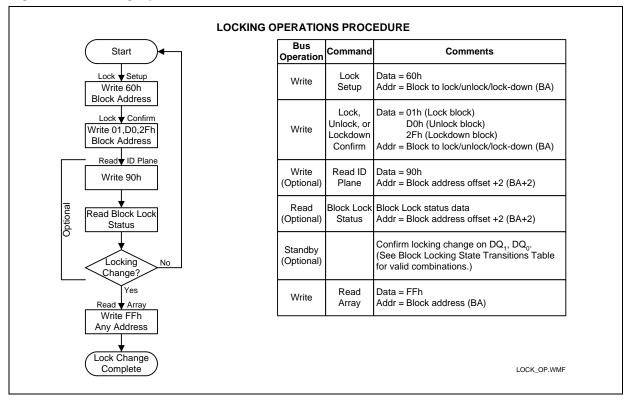

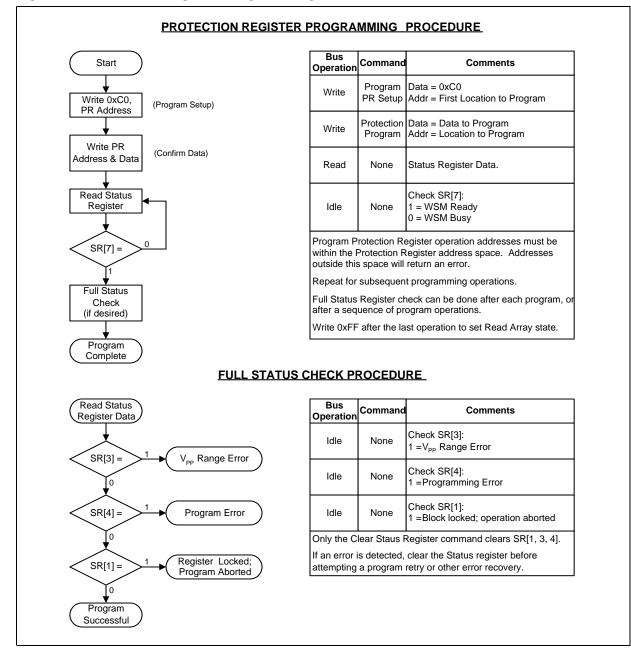

| Α    | <b>Supp</b><br>A.1<br>A.2<br>A.3 | Plemental Reference Information<br>Flow Charts<br>Write State Machine<br>Common Flash Interface                                   | 73<br>80             |

# **Revision History**

| Date                | Revision | Description                                                                                                                                                                                                                                                                                                                                                                            |

|---------------------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| December 14th, 2006 | 0        | Initial Advance Information Datasheet                                                                                                                                                                                                                                                                                                                                                  |

| March, 2007         | 1        | Advance Information Datasheet                                                                                                                                                                                                                                                                                                                                                          |

| July, 2007          | 2        | Fixed the spelling error and deleted a repeated sentence on page 10<br>Added Section 2.3 "64-Ball EBGA Package" on page 12<br>Added Figure 1 "EBGA Mechanical Specifications" on page 12<br>Added Table 1 "EBGA Package Dimensions" on page 12<br>Added note 6 on page 67<br>Updated note 5 on page 68<br>Fixed an error on the A33 Device Code on "from 881E8 Hex, to 881E Hex"       |

| April 2008          | 03       | Applied Numonyx branding.                                                                                                                                                                                                                                                                                                                                                              |

| February 2009       | 04       | Changed the Operating Temperature on the Title page as well as Table 19<br>Changed the Writing Endurance to 100,000<br>No Read while at Streaming Mode in Section 4.4<br>Changed the stand by current to 160usec in Section 7.2<br>Added note 5 in Table 19 footnotes<br>Changed the read latency to 115nsec. Also, changed the values of R1 and R2 to 115nsec in<br>Section 7.4       |

| July 2009           | 05       | Removed Numonyx Confidential<br>Removed Streaming Mode references<br>Changed all A33 references to P8P<br>Revised Easy BGA Package Dimensions (Table 4)<br>Revised SPI Section (Ch-12)<br>Changes Erase & Program Suspend Specification<br>Changed P2 Specification<br>Changed W250 non-streaming mode legacy programming<br>Applied Numonyx DS formatting                             |

| April 2010          | 06       | Added Numonyx® Omneo <sup>™</sup> Branding<br>Added Program on all 1's command (D1h) to Table-20<br>Added Edurance table to operating conditions section<br>Updated AC/DC Specifications: P3 (max), ICCS (typ), ICCS/ICCD/ICCES/ICCWS (typ), ICCR<br>(typ/max), Capacitance (max), tCLQV (max), tHHQX (max), Buffer Program (typ/max), Block<br>Erase (typ/max), Suspend Latency (max) |

| August 2010         | 07       | Added -30 to +85C (Cover Page, Section 14)<br>Removed Storage Temp Range (Section 14)<br>Revised AC Read Spec for -30 to +85C (Section 16.3)<br>Revised SPI AC Spec for -30 to +85C (Section 16.5)<br>Revised Ordering Information (Section 18)                                                                                                                                        |

## 1.0 **Product Description**

## 1.1 Introduction

Numonyx® Omneo<sup>™</sup> Phase Change Memory for embedded applications offers all of the best attributes from other memory types in a new, highly scalable and flexible technology.

Phase Change Memory (PCM) is a new type of nonvolatile semiconductor memory that stores information through a reversible structural phase change in a chalcogenide material. The material exhibits a change in material properties, both electrical and optical, when changed from the amorphous (disordered) to the polycrystalline (regularly ordered) state. In the case of Phase Change Memory, information is stored via the change in resistance the chalcogenide material experiences upon undergoing a phase change. The material also changes optical properties after experiencing a phase change, a characteristic that has been successfully mastered for use in current rewritable optical storage devices such as rewritable CDs and DVDs.

The PCM storage element consists of a thin film of chalcogenide contacted by a resistive heating element. In PCM, the phase change is induced in the memory cell by highly localized Joule heating caused by an induced current at the material junction. During a write operation, a small volume of the chalcogenide material is made to change phase. The phase change is a reversible process, and is modulated by the magnitude of injected current, the applied voltage, and the duration of the heating pulse.

PCM combines the benefits of traditional floating gate flash, both NOR-type and NANDtype, with some of the key attributes of RAM and EEpROM. Like NOR flash and RAM technology, PCM offers fast random access times. Like NAND flash, PCM has the ability to write moderately fast. And like RAM and EEpROM, PCM supports bit alterable writes (overwrite). Unlike flash, no separate erase step is required to change information from 0 to 1 and 1 to 0. Unlike RAM, however, the technology is nonvolatile with data retention comparable NOR flash. However, at the current time, PCM technology appears to have a write cycling endurance better than that of NAND or NOR flash, but less than that of RAM.

Unlike other proposed alternative memories, PCM technology uses a conventional CMOS process with the addition of a few additional layers to form the memory storage element. Overall, the basic memory manufacturing process used to make PCM is less complex than that of NAND, NOR or DRAM.

Historically, systems have adopted many different types of memory to meet different needs within a design. Some systems might include boot memory, configuration memory, data storage memory, high speed execution memory, and dynamic working memory. The demands of many of today's designs require better performance from the memory subsystem and a reduction in the overall component count. PCM provides many of the attributes of different kinds of memory found in a typical design, enabling the opportunity to consolidate or eliminate of different types of memory.

The combination of fast random access with high speed, bit alterable writes in a nonvolatile memory is a capability only offered in complex, low density technologies such as parallel EEpROM or battery-backed RAM. The PCM feature set is intended to facilitate easy evaluation and adoption in systems and to enable the consolidation of memory functions into a single device. In some cases, PCM may enable new usages or new solutions to existing problems, in a manner that is more efficient, higher performance and/or more cost effective.

Datasheet

## 1.2 Product Overview

The Numonyx® Omneo<sup>™</sup> P8P PCM provides the convenience and ease of NOR flash emulation while providing a set of Super Set features that exploit the inherent capabilities of the PCM technology. The device emulates most of the features of the Numonyx® Axcell<sup>™</sup> Embedded Memory (P33). This is intended to ease the evaluation and design of Numonyx® Omneo<sup>™</sup> P8P PCM into existing hardware and software development platforms. This basic features set is supplemented by the Super Set Features. The Super Set Features are intended to allow the designer to exploit the inherent capabilities of the phase change memory technology, and to enable the eventual simplification of hardware and software in the design. This section describes an overview of the features and capabilities of Numonyx® Omneo<sup>™</sup> P8P PCM.

- **Density:** Numonyx® Omneo<sup>™</sup> P8P PCM product family begins with a 128-Mbit density.

- **Packages:** Numonyx<sup>®</sup> Omneo<sup>™</sup> P8P PCM devices are available in 64 Ball Easy BGA and 56 Lead TSOP packages. These are the same pinouts and packages as the existing P33 NOR flash devices.

- Low Power: Designed for low voltage systems, Numonyx® Omneo<sup>™</sup> P8P PCM supports read, write and erase operations at a core supply of 2.7V V<sub>CC</sub>. P8P offers additional power savings through standby mode. Standby mode is initiated when the system deselects the device by driving CE inactive, which significantly reduces power consumption.

- NOR-Compatible Program and Emulated Erase Operation: Numonyx® Omneo<sup>™</sup> P8P PCM provides a complete set of commands that are compatible with industry-standard command sequences used by NOR-type flash. An internal Write State Machine (WSM) automatically executes the algorithms and timings necessary for block erase and write. Each emulated block erase operation results in the contents of the addressed block being written to all "1s" (ones). Data can be programmed in word or buffer increments. Erase-suspend allows system software to pause an erase command so it can read or program data in another block. Program suspend allows system software to pause programming so it can read from other locations within the device. The Status Register indicates when the WSM's block erase, or program operation is finished.

- Write Buffer: A 64 byte/32 word Write Buffer is also included to allow optimum write performance. By using the write buffer, data is overwritten or programmed in buffer increments. This feature improves system program performance more than 20 times over independent byte writes.

- **Command User Interface**: As with floating gate flash, a Command User Interface (CUI) serves as the interface between the system processor and internal operation of the device. A valid command sequence written to the CUI initiates device automation.

- Data Protection: Numonyx® Omneo<sup>™</sup> P8P PCM block locking enables zerolatency block locking/unlocking and permanent locking. Permanent block locking provides enhanced security for boot code. The combination of these two locking features provides complete locking solution for code and data.

- **CFI Compliant**: A flash-compatible Common Flash Interface (CFI) permits software algorithms to be used for entire families of devices. This allows device-independent, JEDEC ID-independent, and forward- and backward-compatible software support for the specified flash device families.

- **Bit Alterability or Overwrite:** PCM technology supports the ability to change each memory bit independently from 0 to 1 or 1 to 0 without an intervening block erase operation. Bit Alterability enables software to write to the non-volatile memory in a similar manner as writing to RAM or EEpROM without the overhead of erasing blocks prior to write. Bit Alterable writes use similar command sequences as word programming and Buffer Programming.

- Serial Peripheral Interface (SPI): SPI allows for in-system programming through a minimal pin count interface. This interface is provided in addition to a traditional parallel system interface. This feature has been added to facilitate the on-board, in-system programming of code into the Numonyx® Omneo<sup>™</sup> P8P PCM device, after it has been soldered to a circuit board. Pre-programming of code prior to high temperature board attach is not recommended with the P8P device. Although the device reliability across the operating temperature range is typically superior to that of floating gate flash, the P8P device may be subject to thermallyactivated disturbs at higher temperatures. However, no permanent device damage occurs during either leaded and lead-free board attach.

Datasheet 8

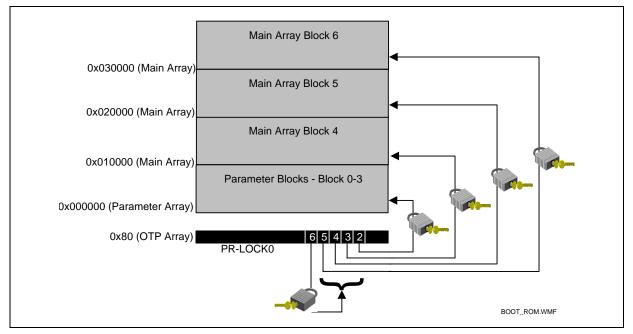

## 1.3 Memory Map

This section covers the memory map for the Top and Bottom boot devices

Table 1:

Top Parameter Memory Map

| Programming Region<br>Number | Size<br>(KW) | Blk | 128-Mbit      |

|------------------------------|--------------|-----|---------------|

|                              | 16           | 130 | 7FC000-7FFFFF |

|                              | 16           | 129 | 7F8000-7FBFFF |

|                              | 16           | 128 | 7F4000-7F7FFF |

| 7                            | 16           | 127 | 7F0000-7F3FFF |

|                              | 64           | 126 | 7E0000-7EFFFF |

|                              | :            | ÷   | ÷             |

|                              | 64           | 112 | 700000-70FFFF |

|                              | 64           | 111 | 6F0000-6FFFFF |

| 6                            | :            | :   | E             |

|                              | 64           | 96  | 600000-60FFFF |

|                              | 64           | 95  | 5F0000-5FFFFF |

| 5                            | :            | :   | :             |

|                              | 64           | 80  | 500000-50FFFF |

|                              | 64           | 79  | 4F0000-4FFFFF |

| 4                            | :            | :   | :             |

|                              | 64           | 64  | 400000-40FFFF |

|                              | 64           | 63  | 3F0000-3FFFFF |

| 3                            | :            | :   | :             |

|                              | 64           | 48  | 300000-30FFFF |

|                              | 64           | 47  | 2F0000-2FFFFF |

| 2                            | :            | :   | :             |

|                              | 64           | 32  | 200000-20FFFF |

|                              | 64           | 31  | 1F0000-1FFFFF |

| 1                            | :            | :   | :             |

|                              | 64           | 16  | 100000-10FFFF |

|                              | 64           | 15  | OF0000-OFFFFF |

| 0                            | :            | :   | ÷             |

|                              | 64           | 0   | 000000-00FFFF |

| Programming Region<br>Number | Size<br>(KW) | Bik | 128-Mbit      |

|------------------------------|--------------|-----|---------------|

|                              | 64           | 130 | 7F0000-7FFFFF |

| 7                            | :            | :   | ÷             |

|                              | 64           | 115 | 700000-70FFFF |

|                              | 64           | 114 | 6F0000-6FFFFF |

| 6                            | :            | ÷   | :             |

|                              | 64           | 99  | 600000-60FFFF |

|                              | 64           | 98  | 5F0000-5FFFFF |

| 5                            | :            | ÷   | ÷             |

|                              | 64           | 83  | 500000-50FFFF |

|                              | 64           | 82  | 4F0000-4FFFFF |

| 4                            | :            | :   | ÷             |

|                              | 64           | 67  | 400000-40FFFF |

|                              | 64           | 66  | 3F0000-3FFFFF |

| 3                            | :            | ÷   | ÷             |

|                              | 64           | 51  | 300000-30FFFF |

|                              | 64           | 50  | 2F0000-2FFFFF |

| 2                            | :            | :   | ÷             |

|                              | 64           | 35  | 200000-20FFFF |

|                              | 64           | 34  | 1F0000-1FFFFF |

| 1                            | :            | :   | ÷             |

|                              | 64           | 19  | 100000-10FFFF |

|                              | 64           | 18  | OF0000-OFFFFF |

|                              | :            | ÷   | ÷             |

|                              | 64           | 4   | 010000-01FFFF |

| 0                            | 16           | 3   | 00C000-00FFFF |

|                              | 16           | 2   | 008000-00BFFF |

|                              | 16           | 1   | 004000-007FFF |

|                              | 16           | 0   | 000000-003FFF |

## Table 2:Bottom Parameter Memory Map

#### Package Information 2.0

This section covers the mechanical specifications for the available packages.

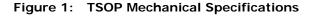

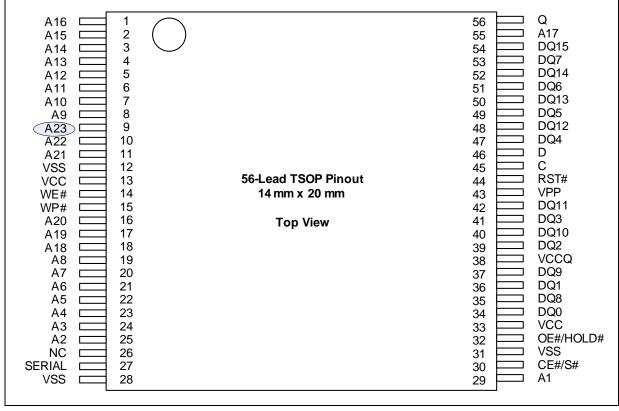

#### 2.1 56-Lead TSOP

Notes:

One dimple on package denotes Pin 1. If two dimples, then the larger dimple denotes Pin 1. Pin 1 will always be in the upper left corner of the package, in reference to the product mark. 1. 2. 3.

TSOP Package Dimensions (Sheet 1 of 2) Table 3:

| Product Information    | Symbol         | Millimeters |       |       |       | Notes |       |       |

|------------------------|----------------|-------------|-------|-------|-------|-------|-------|-------|

| Product miormation     | Symbol         | Min         | Nom   | Мах   | Min   | Nom   | Мах   | Notes |

| Package Height         | А              | -           | -     | 1.200 | -     | -     | 0.047 |       |

| Standoff               | A <sub>1</sub> | 0.050       | -     | -     | 0.002 | -     | -     |       |

| Package Body Thickness | A <sub>2</sub> | 0.965       | 0.995 | 1.025 | 0.038 | 0.039 | 0.040 |       |

| Lead Width             | b              | 0.100       | 0.150 | 0.200 | 0.004 | 0.006 | 0.008 |       |

| Product Information       | Symphol        | Millimeters |        |        | Inches |        |       | Netza |

|---------------------------|----------------|-------------|--------|--------|--------|--------|-------|-------|

| Product Information       | Symbol         | Min         | Nom    | Max    | Min    | Nom    | Max   | Notes |

| Lead Thickness            | С              | 0.100       | 0.150  | 0.200  | 0.004  | 0.006  | 0.008 |       |

| Package Body Length       | D <sub>1</sub> | 18.200      | 18.400 | 18.600 | 0.717  | 0.724  | 0.732 |       |

| Package Body Width        | E              | 13.800      | 14.000 | 14.200 | 0.543  | 0.551  | 0.559 |       |

| Lead Pitch                | е              | -           | 0.500  | -      | -      | 0.0197 | -     |       |

| Terminal Dimension        | D              | 19.800      | 20.00  | 20.200 | 0.780  | 0.787  | 0.795 |       |

| Lead Tip Length           | L              | 0.500       | 0.600  | 0.700  | 0.020  | 0.024  | 0.028 |       |

| Lead Count                | Ν              | -           | 56     | -      | -      | 56     | -     |       |

| Lead Tip Angle            | θ              | 0°          | 3°     | 5°     | 0°     | 3°     | 5°    |       |

| Seating Plane Coplanarity | Y              | -           | -      | 0.100  | -      | -      | 0.004 |       |

| Lead to Package Offset    | Z              | 0.150       | 0.250  | 0.350  | 0.006  | 0.010  | 0.014 |       |

Table 3:

TSOP Package Dimensions (Sheet 2 of 2)

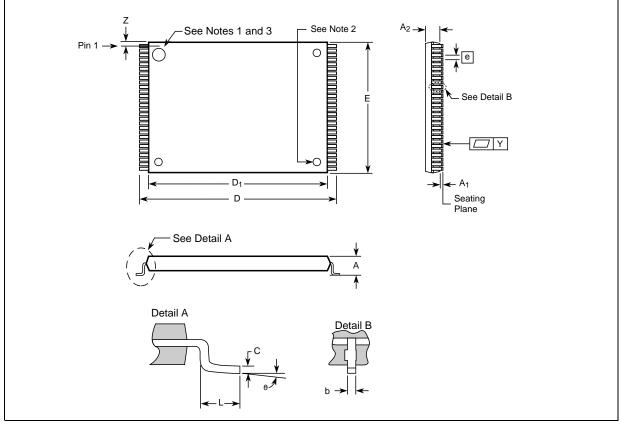

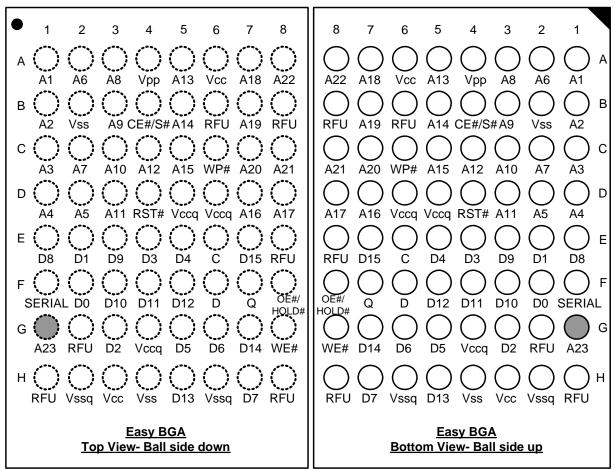

## 2.2 64-Ball Easy BGA Package

| Product Information                | Symbol |      | Netes |       |       |

|------------------------------------|--------|------|-------|-------|-------|

|                                    | Symbol | Min  | Nom   | Max   | Notes |

| Package Height (128-Mbit)          | А      | -    | -     | 1.20  |       |

| Ball Height                        | A1     | 0.25 | -     | -     |       |

| Package Body Thickness (128-Mbit)  | A2     | -    | 0.78  | -     |       |

| Ball (Lead) Width                  | b      | 0.33 | 0.43  | 0.53  |       |

| Package Body Width                 | D      | 9.90 | 10.00 | 10.10 |       |

| Package Body Length                | E      | 7.90 | 8.00  | 8.10  |       |

| Pitch                              | e      | -    | 1.00  | -     |       |

| Ball (Lead) Count                  | Ν      | -    | 64    | -     |       |

| Seating Plane Coplanarity          | Y      | -    | -     | 0.10  |       |

| Corner to Ball A1 Distance Along D | S1     | 1.40 | 1.50  | 1.60  |       |

| Corner to Ball A1 Distance Along E | S2     | 0.49 | 0.50  | 0.51  |       |

Table 4: Easy BGA Package Dimensions

## 3.0 Pinouts and Ballouts

Figure 3: 56-Lead TSOP Pinout (128-Mbit)

Notes:

1. A1 is the least significant address bit to be compatible with x8 addressing systems. Even though Numonyx® Omneo<sup>™</sup> P8P PCM is a 16 bit data bus.

Figure 4: 64-Ball Easy BGA Ballout (128-Mbit)

Notes:

1. A1 is the least significant address bit to be compatible with x8 addressing systems, even though Numonyx® Omneo<sup>™</sup> P8P PCM is a 16 bit data bus.

# 4.0 Signals

| Symbol           | Туре             | Name and Function                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |

|------------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| A[MAX:1]         | Input            | ADDRESS INPUTS: Device address inputs. 128-Mbit: A[23:1]         Put         Note: The address bus for TSOP and Easy BGA starts at A1. Numonyx® Omneo™ P8P PCM uses x16 addressing. The Numonyx® Omneo™ P8P PCM package is x8 addressing and is compatible with J3 or products.                                                                                                                                                                             |  |  |  |  |  |  |

| DQ[15:0]         | Input/<br>Output | <b>DATA INPUT/OUTPUTS:</b> Inputs data and commands during writes (internally latched). Outputs dat during read operations. Data signals float when CE# or OE# are $V_{IH}$ . or RST# is $V_{IL}$ .                                                                                                                                                                                                                                                         |  |  |  |  |  |  |

| 05# or 6#        | Input            | <b>CHIP ENABLE:</b> CE#-low activates internal control logic, I/O buffers, decoders, and sense amps. CE#-<br>high deselects the device, places it in standby state, and places data outputs at high-Z.                                                                                                                                                                                                                                                      |  |  |  |  |  |  |

| CE# or S#        | SPI              | <b>SPI Select:</b> S# low activates command writes to the SPI interface. Raising S# to VIH completes (or terminates) the SPI command cycle; it also sets Q to high-Z.                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |

| OE# or           | Input            | <b>OUTPUT ENABLE:</b> Active low OE# enables the device's output data buffers during a read cycle. With OE# at V <sub>IH</sub> , device data outputs are placed in high-Z state.                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |

| HOLD#            | SPI              | SPI HOLD#: When asserted, suspends the current cycle and sets Q to high-Z until de-asserted.                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |

| RST#             | Input            | <b>RESET CHIP:</b> When low, RST# resets internal automation and inhibits write operations. This provides data protection during power transitions. RST#-high enables normal operation. The device is in 8-Word page mode array read after reset exits.                                                                                                                                                                                                     |  |  |  |  |  |  |

| WE#              | Input            | WRITE ENABLE: controls Command User Interface (CUI) and array writes. Its rising edge latches addresses and data.                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |

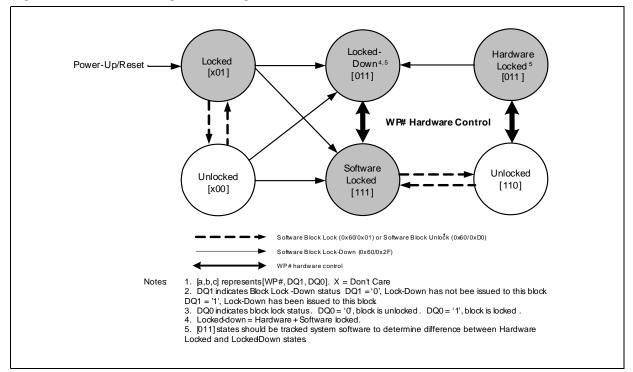

|                  | Input            | WRITE PROTECT: Disables/enables the lock-down function.<br>When WP# is V <sub>IL</sub> , the lock-down mechanism is enabled and software cannot unlock blocks marked lock-down.                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |

| WP#              |                  | When WP# is V <sub>IH</sub> , the lock-down mechanism is disabled and blocks previously locked-down are<br>now locked; software can unlock and lock them. After WP# goes low, blocks previously marked lock-<br>down revert to that state.                                                                                                                                                                                                                  |  |  |  |  |  |  |

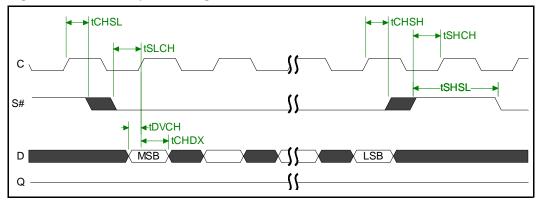

| С                | SPI              | SPI Clock: Synchronization clock for input and output data                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |

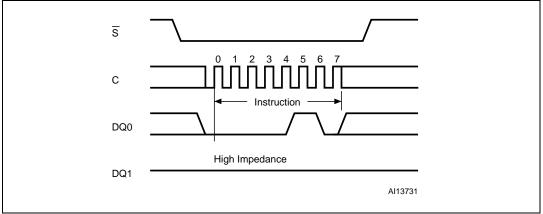

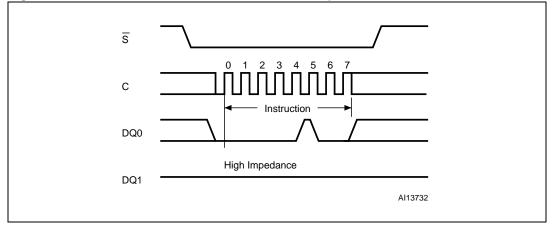

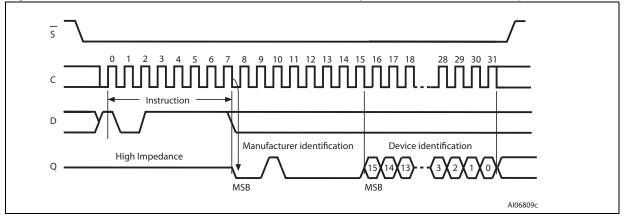

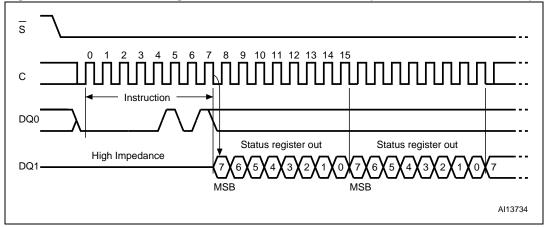

| D                | SPI              | <b>SPI Data Input:</b> Serial data input for Op Codes, address and program data bytes. Input data is clocked in on the rising edge of C, starting with the MSB.                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |

| Q                | SPI              | <b>SPI Data Output:</b> Serial data output for read data. Output data is clocked out, triggered by the falling edge of C, starting with the MSB.                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |

| SERIAL           | SPI              | SPI Enable: SERIAL is a port select switching between the normal parallel or serial interface. When Vss, the normal (non-SPI) Numonyx® Omneo <sup>™</sup> P8P PCM interface is enabled; all other SPI inputs are Don't Care, and Q is at High-Z. When Vcc, SPI mode is enabled, all non-SPI inputs are Don't Care, and all outputs are at High-Z. This pin has an internal weak pull down resistor to select the normal parallel interface when users leave |  |  |  |  |  |  |

|                  |                  | the pin floating. A CAM can be used to permanently disable this feature.<br><b>ERASE AND WRITE POWER:</b> A valid V <sub>PP</sub> voltage allows erase or programming. Memory contents can't                                                                                                                                                                                                                                                                |  |  |  |  |  |  |

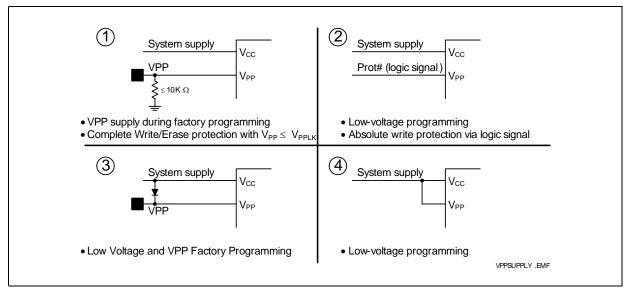

| V <sub>PP</sub>  | Pwr              | be altered when $V_{PP} \le V_{PPLK}$ .<br>Set $V_{PP} = V_{CC}$ for in-system program and erase operations. To accommodate resistor or diode drops from the system supply, $V_{PP}$ 's $V_{IH}$ level can be as low as $V_{PPLMIN}$ .<br>Program/erase voltage is normally 1.7 V–3.6 V.                                                                                                                                                                    |  |  |  |  |  |  |

| V <sub>CC</sub>  | Pwr              | <b>DEVICE POWER SUPPLY:</b> Writes are inhibited at $V_{CC} \le V_{LKO}$ . Device operations at invalid $V_{CC}$ voltages should not be attempted.                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |

| V <sub>CCQ</sub> | Pwr              | <b>OUTPUT POWER SUPPLY:</b> Enables all outputs to be driven at $V_{CCQ}$ . This input may be tied directly to $V_{CC}$ if $V_{CCQ}$ is to function within the $V_{CC}$ range.                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |

| V <sub>SS</sub>  | Pwr              | GROUND: connects device circuitry to system ground.                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |

| V <sub>SSQ</sub> | Pwr              | I/O GROUND: Tie to GND                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |

| NC               | İ                | NO CONNECT: No internal connection; can be driven or floated.                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |

| DU               |                  | DON'T USE: Don't connect to power supply or other signals.                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |

| RFU              | İ                | RESERVED FOR FUTURE USE: Don't connect to other signals.                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

## Table 5: Ball/Pin Descriptions

Datasheet 16

#### 5.0 **Bus Operations**

CE# at V<sub>IL</sub> and RST# at V<sub>IH</sub> enables device read operations. Addresses are always assumed to be valid. OE#-low activates the outputs and gates selected data onto the I/ O bus. WE#-low enables device write operations. When the VPP voltage ≤ VPPLK (lockout voltage), only read operations are enabled.

#### Table 6: **Bus Operations**

| State                            | RST#            | CE#             | OE#             | WE#             | DQ[15:0]         | Note |

|----------------------------------|-----------------|-----------------|-----------------|-----------------|------------------|------|

| Read (Main Array)                | V <sub>IH</sub> | V <sub>IL</sub> | V <sub>IL</sub> | V <sub>IH</sub> | D <sub>OUT</sub> |      |

| Read (Status, Query, Identifier) | V <sub>IH</sub> | V <sub>IL</sub> | V <sub>IL</sub> | V <sub>IH</sub> | D <sub>OUT</sub> |      |

| Output Disable                   | V <sub>IH</sub> | V <sub>IL</sub> | V <sub>IH</sub> | V <sub>IH</sub> | High-Z           |      |

| Standby                          | V <sub>IH</sub> | V <sub>IH</sub> | Х               | Х               | High-Z           | 2    |

| Reset                            | V <sub>IL</sub> | Х               | Х               | Х               | High-Z           | 2    |

| Write                            | V <sub>IH</sub> | V <sub>IL</sub> | V <sub>IH</sub> | V <sub>IL</sub> | D <sub>IN</sub>  | 1    |

Notes:

see Table 8, "Command Sequences in x16 Bus Mode" on page 20 for valid D<sub>IN</sub> during a write operation. 1

X = Don't care (L or H)2.3.

OE# and WE# should never be asserted simultaneously. If done so, OE# overrides WE#.

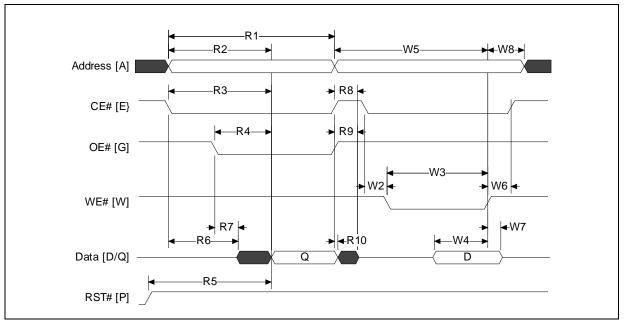

#### 5.1 Reads

To perform a read operation, RST# and WE# must be deasserted while CE# and OE# are asserted. CE# is the device-select control. When asserted, it enables the flash memory device. OE# is the data-output control. When asserted, the addressed flash memory data is driven onto the I/O bus.

#### 5.2 Writes

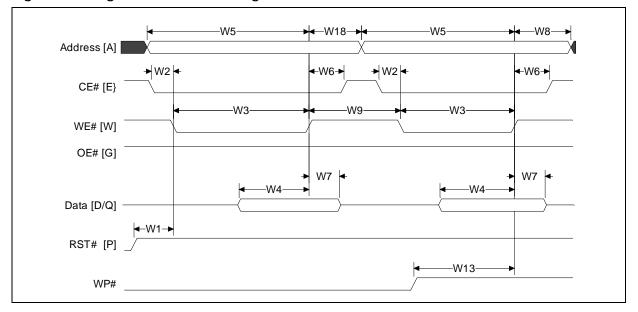

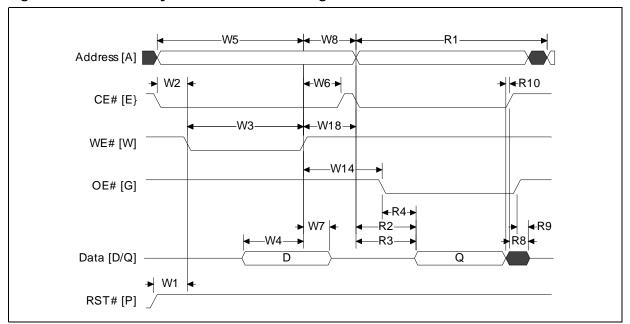

To perform a write operation, both CE# and WE# are asserted while RST# and OE# are deasserted. During a write operation, address and data are latched on the rising edge of WE# or CE#, whichever occurs first. Table 7, "Command Codes and Descriptions" on page 19 shows the bus cycle sequence for each of the supported device commands, while Table 8, "Command Sequences in x16 Bus Mode" on page 20 describes each command. See Section 16.0, "AC Characteristics" on page 62 for signal-timing details.

Note: Write operations with invalid  $V_{CC}$  and/or  $V_{PP}$  voltages can produce spurious results and should not be attempted.

#### 5.3 **Output Disable**

When OE# is deasserted, device outputs DQ[15:0] are disabled and placed in a highimpedance (High-Z) state, WAIT is also placed in High-Z.

#### 5.4 Standby

When CE# is deasserted the device is deselected and placed in standby, substantially reducing power consumption. In standby, the data outputs are placed in High-Z, independent of the level placed on OE#. Standby current, I<sub>CCS</sub>, is the average current measured over any 5 ms time interval, 5 µs after CE# is deasserted. During standby, average current is measured over the same time interval 5 µs after CE# is deasserted. When the device is deselected (while CE# is deasserted) during a program or erase operation, it continues to consume active power until the program or erase operation is completed.

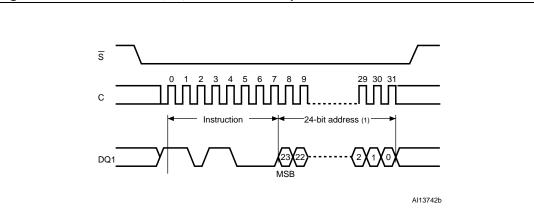

### 5.5 Reset

As with any automated device, it is important to assert RST# when the system is reset. When the system comes out of reset, the system processor attempts to read from the flash memory if it is the system boot device. If a CPU reset occurs with no flash memory reset, improper CPU initialization may occur because the flash memory may be providing status information rather than array data. Flash memory devices from Numonyx allow proper CPU initialization following a system reset through the use of the RST# input. RST# should be controlled by the same low-true reset signal that resets the system CPU.

After initial power-up or reset, the device defaults to asynchronous Read Array mode, and the Status Register is set to 0x80. Asserting RST# de-energizes all internal circuits, and places the output drivers in High-Z. When RST# is asserted, the device shuts down the operation in progress, a process which takes a minimum amount of time to complete. When RST# has been deasserted, the device is reset to asynchronous Read Array state.

*Note:* If RST# is asserted during a program or erase operation, the operation is terminated and the memory contents at the aborted location (for a program) or block (for an erase) are no longer valid, because the data may have been only partially written or erased.

When returning from a reset (RST# deasserted), a minimum wait is required before the initial read access outputs valid data. Also, a minimum delay is required after a reset before a write cycle can be initiated. After this wake-up interval passes, normal operation is restored. See Section 16.0, "AC Characteristics" on page 62 for details about signal-timing.

## 6.0 Command Set

## 6.1 Device Command Codes

The system CPU provides control of all in-system read, write, and erase operations of the device via the system bus. The on-chip Write State Machine (WSM) manages all block-erase and word-program algorithms.

Device commands are written to the Command User Interface (CUI) to control all flash memory device operations. The CUI does not occupy an addressable memory location; it is the mechanism through which the flash device is controlled.

Table 7: Command Codes and Descriptions

| Mode    | Code | Device Mode                     | Description                                                                                                                                                                                                                                                                                                                                                                                                       |

|---------|------|---------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | FFh  | Read Array                      | Places device in read array mode so that data signals output array data on DQ[15:0].                                                                                                                                                                                                                                                                                                                              |

|         | 70h  | Read Status<br>Register         | Places the device in Status Register read mode. Status data is output on DQ[7:0]. The device automatically enters this mode after a program or erase command is issued to it.                                                                                                                                                                                                                                     |

| Read    | 90h  | Read ID Code                    | Puts the device in read identifier mode. Device reads from the addresses output manufacturer/ device codes, block lock status, or protection register data on DQ[15:0].                                                                                                                                                                                                                                           |

| R       | 98h  | Read Query                      | Puts the device in read query mode. Device reads from the address given outputting the Common Flash Interface information on DQ[7:0]                                                                                                                                                                                                                                                                              |

|         | 50h  | Clear Status<br>Register        | The WSM can set the Status Register's block lock (SR.1), $V_{PP}$ (SR.3), program (SR.4), and erase (SR.5) status bits to "1" but cannot clear them. Device reset or the Clear Status Register command at any device address clears those bits to "0."                                                                                                                                                            |

|         | 40h  | Program<br>Set-Up               | This preferred program command's first cycle prepares the CUI for a program operation. The second cycle latches address and data and executes the WSM Program algorithm at this location. Status Register updates occur when CE# or OE# is toggled. A Read Array command is required to read array data after programming.                                                                                        |

|         | 10h  | Alt Set-up                      | Equivalent to a Program Set-Up command (40h).                                                                                                                                                                                                                                                                                                                                                                     |

| am      | 42h  | Bit Alterable<br>Write          | The command sequence is the same as Word Program (40h). The difference is the state of the PCM memory cell can change from a 0 to 1 or 1 to 0, unlike a flash memory cell, which can only change from 1 to 0 during programming.                                                                                                                                                                                  |

| Program | E8h  | Buffered<br>Program             | This command loads a variable number of bytes up to the buffer size 32 words onto the program buffer.                                                                                                                                                                                                                                                                                                             |

|         | EAh  | Bit Alterable<br>Buffered Write | This command sequence is the similar to Buffered Program, but the buffer write command is bit alterable or overwrite operation. The command sequence is the same as E8h.                                                                                                                                                                                                                                          |

|         | DEh  | Buffer Program<br>on all 1s     | This command is the same as Buffered Program, but user indicates that the pagee is already set to all 1s. The command sequence is the same as E8h                                                                                                                                                                                                                                                                 |

|         | D0h  | Buffered Write<br>Confirm       | The confirm command is issued after the data streaming for writing into the buffer is done. This initiates the WSM to carry out the buffered programing algorithm.                                                                                                                                                                                                                                                |

| Erase   | 20h  | Block Erase<br>Set-Up           | Prepares the CUI for Block Erase. The device emulates erasure of the block addressed by the Erase Confirm command by writing all ones. If the next command is not Erase Confirm, the CUI (a) sets Status Register bits SR.4 and SR.5 to "1," (b) places the device in the read Status Register mode, and (c) waits for another command.                                                                           |

|         | D0h  | Erase Confirm                   | If the first command was Erase Set-Up (20h), the CUI latches address and data then emulates erasure of the block indicated by the Erase confirm cycle address.                                                                                                                                                                                                                                                    |

| Suspend | B0h  | Write or<br>Erase Suspend       | This command issued at any device address initiates suspension of the currently executing program/erase operation. The Status Register, invoked by a Read Status Register command, indicates successful suspend operation by setting (1) status bits SR.2 (write suspend) or SR.6 (erase suspend) and SR.7. The WSM remains in the Suspend mode regardless of the control signal states, except RST# = $V_{IL}$ . |

| S       | D0h  | Suspend<br>Resume               | This command issued at any device address resumes suspended program or erase operation.                                                                                                                                                                                                                                                                                                                           |

| Mode       | Code | Device Mode                     | Description                                                                                                                                                                                                                                                                                          |

|------------|------|---------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| g          | 60h  | Lock Set-Up                     | Prepares the CUI for lock configuration. If the next command is not Block-Lock, Unlock, or Lock-<br>Down the CUI sets SR.4 and SR.5 to indicate command sequence error.                                                                                                                              |

| Locking    | 01h  | Lock Block                      | If the previous command was Lock Set-Up (60h), the CUI locks the addressed block.                                                                                                                                                                                                                    |

| Block Lo   | D0h  | Unlock Block                    | After a Lock Set-Up (60h) command the CUI latches the address and unlocks the addressed block.                                                                                                                                                                                                       |

| BI         | 2Fh  | Lock-Down                       | After a Lock Set-Up (60h) command, the CUI latches the address and locks-down the addressed block.                                                                                                                                                                                                   |

| Protection | C0h  | Protection<br>Program<br>Set-Up | Prepares the CUI for a protection register program operation. The second cycle latches address, data, and starts the WSM's protection register program or lock algorithm. Toggling CE# or OE# updates the PCM Status Register data. To read array data after programming issue a Read Array command. |

Table 7: Command Codes and Descriptions

*Note:* Don't use unassigned (reserved) commands

## 6.2 Device Command Bus Cycles

Device operations are initiated by writing specific device commands to the Command User Interface (CUI). Several commands are used to modify array data including Word Program and Block Erase commands. Writing either command to the CUI initiates a sequence of internally-timed functions that culminate in the completion of the requested task. However, the operation can be aborted by either asserting RST# or by issuing an appropriate suspend command

| Mode    | Command                                          | Bus    | First Bus Cycle |                     |                     | Second Bus Cycle |                     |                     |

|---------|--------------------------------------------------|--------|-----------------|---------------------|---------------------|------------------|---------------------|---------------------|

| wode    | command                                          | Cycles | Oper            | Addr <sup>(1)</sup> | Data <sup>(2)</sup> | Oper             | Addr <sup>(1)</sup> | Data <sup>(2)</sup> |

|         | Read Array/Reset                                 | 1      | Write           | DnA                 | FFh                 | -                | -                   | -                   |

|         | Read Device Identifiers                          | ≥ 2    | Write           | DnA                 | 90h                 | Read             | DBA+IA              | ID                  |

| Read    | Read Query                                       | ≥ 2    | Write           | DnA                 | 98h                 | Read             | DBA+QA              | QD                  |

|         | Read Status Register                             | 2      | Write           | BA                  | 70h                 | Read             | BA                  | SRD                 |

|         | Clear Status Register                            | 1      | Write           | Х                   | 50h                 | -                | -                   | -                   |

|         | Program                                          | 2      | Write           | WA                  | 40h or 10h          | Write            | WA                  | WD                  |

|         | Bit Alterable Program                            | 2      | Write           | WA                  | 42h                 | Write            | PA                  | PD                  |

| Program | Buffered Program <sup>(3)</sup>                  | > 2    | Write           | WA                  | E8h                 | Write            | WA                  | N-1                 |

| 5       | Bit Alterable Buffered<br>Program <sup>(3)</sup> | >2     | Write           | WA                  | EAh                 | Write            | WA                  | N-1                 |

|         | Buffered Program on all 1s                       | >2     | Write           | WA                  | DEh                 | Write            | WA                  | N-1                 |

| Erase   | Block Erase                                      | 2      | Write           | BA                  | 20h                 | Write            | BA                  | D0h                 |

| Suspend | Program/Erase Suspend                            | 1      | Write           | Х                   | B0h                 | -                | -                   | -                   |

| Suspend | Program/Erase Resume                             | 1      | Write           | Х                   | D0h                 | -                | -                   | -                   |

Table 8: Command Sequences in x16 Bus Mode

| Mode                                                                          | Command                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Bus                                                                                                                            | First Bus Cycle                                           |                                                         |                                  | Second Bus Cycle |                     |                     |

|-------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|---------------------------------------------------------|----------------------------------|------------------|---------------------|---------------------|

| wode                                                                          | de Command Bus<br>Cycles                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                | Oper                                                      | Addr <sup>(1)</sup>                                     | Data <sup>(2)</sup>              | Oper             | Addr <sup>(1)</sup> | Data <sup>(2)</sup> |

|                                                                               | Lock Block                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 2                                                                                                                              | Write                                                     | BA                                                      | 60h                              | Write            | BA                  | 01h                 |

| Block<br>Lock                                                                 | k Uplock Block                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                | Write                                                     | BA                                                      | 60h                              | Write            | BA                  | D0h                 |

|                                                                               | Lock-down Block                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 2                                                                                                                              | Write                                                     | BA                                                      | 60h                              | Write            | BA                  | 2Fh                 |

| Ductostion                                                                    | Protection Program                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 2                                                                                                                              | Write                                                     | PA                                                      | C0h                              | Write            | PA                  | PD                  |

| Protection                                                                    | Lock Protection Program                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 2                                                                                                                              | Write                                                     | LPA                                                     | C0h                              | Write            | LPA                 | FFFDh               |

| LPA = PA = DnA = DBA = DA = D | Address within the block.<br>Lock Protection Address (from th<br>4-word protection address in the<br>Address within the device.<br>Device Base Address. (A[MAX: 1<br>Program Region<br>Query code address.<br>Word address of memory location<br>Data read from the status regis<br>Data to be written at location W.<br>Identifier code data.<br>User programmable protection da<br>Query code data on DQ[7:0].<br>Data count to be loaded into the d<br>hal registers count from 0, the use<br>econd cycle of the Buffered Program<br>ming up to 32 words and then a c<br>ppendix A, "Buffered Program Flo | user progra<br>1]=0h)<br>n to be writ<br>ter.<br>A.<br>ta.<br>ta.<br>levice to inc<br>er writes N-<br>am commai<br>confirm com | itten.<br>iten.<br>licate how<br>1 to load l<br>nd, which | area of devic<br>many words<br>N words.<br>is the count | s would be wri<br>being loaded i | itten into t     | ffer is follow      | ed by data          |

## Table 8: Command Sequences in x16 Bus Mode

## 7.0 Read Operation

Numonyx<sup>®</sup> Omneo<sup>™</sup> P8P PCM has several read modes:

- Read array mode: read returns PCM array data from the addressed locations.

- **Read identifier mode:** reads returns manufacturer device identifier data, block lock status, and protection register data.

- Read query mode: read returns device CFI (or query) data.

- Read Status Register mode: read returns the device Status Register data. A system processor can check the Status Register to determine the device's state or monitor program or erase progress.

### 7.1 Read Array Command

The Read Array command places (or resets) the device to read array mode. Upon initial device power-up or after reset (RST# transitions from  $V_{IL}$  to  $V_{IH}$ ), the device defaults to read array mode. If an Erase- or Program-Suspend command suspends the WSM, a subsequent Read Array command will place the device in read array mode. The Read Array command functions independently of  $V_{PP}$  voltage.

## 7.2 Read Identifier Command

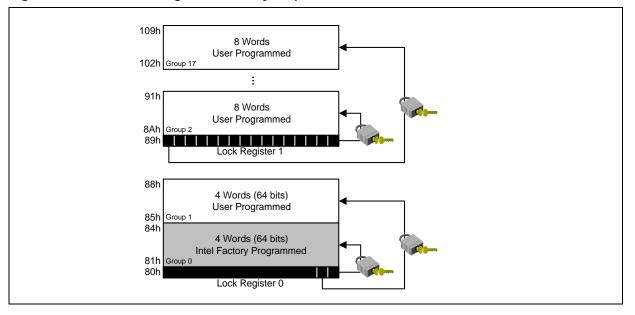

The read identifier mode is used to access the manufacturer/device identifier, block lock status, and protection register codes. The identifier space occupies the address range supplied by the Read Identifier command (90h) address.

| Item Address <sup>(1,2)</sup>                     |                 | s <sup>(1,2)</sup> | Data                     |

|---------------------------------------------------|-----------------|--------------------|--------------------------|

| Manufacturer Code                                 | DBA + 000000h   |                    |                          |

|                                                   |                 |                    | 0089h                    |

| Device Code                                       | DBA + 000001h   |                    | ID (see Table 10)        |

| Block Lock Configuration                          |                 |                    | Lock                     |

| Block Is Unlocked                                 |                 |                    | $DQ_0 = 0$               |

| Block Is Locked                                   | BBA + 000002h   |                    | DQ <sub>0</sub> = 1      |

| Block Is not Locked-Down                          | BBA + 0000021   |                    | $DQ_1 = 0$               |

| Block Is Locked-Down                              |                 |                    | DQ <sub>1</sub> = 1      |

| • Reserved for Future Use <sup>(3)</sup>          |                 |                    | DQ[7:2]                  |

| Lock Protection Register 0                        | DBA + 000080h   |                    | PR-LK0                   |

| 64-bit Factory-Programmable Protection Register   | DBA + 000081h-0 | 00084h             | Protection Register Data |

| 64-bit User-Programmable Protection Register      | DBA + 000085h-0 | 00088h             | Protection Register Data |

| Lock Protection Register 1                        | DBA + 000089h   |                    | PR-LK1                   |

| 16x128 bit User-Programmable Protection Registers | DBA + 00008Ah-0 | 000109h            | Protection Register Data |

#### Table 9: Read Identifier Table

Notes:

1. DBA = Device Base Address. (A[MAX:18] = DBA). Numonyx reserves other configuration address locations.

2. BBA = Block Base Address.

#### Table 10: Device ID Table

|        | De   | evice Code (Byt |          |             |

|--------|------|-----------------|----------|-------------|

| Device | Hex  | Binary          |          | Mode        |

|        | пех  | High Byte       | Low Byte |             |

| 128 Mb | 881E | 10001000        | 00011110 | Top Boot    |

| 128 Mb | 8821 | 10001000        | 00100001 | Bottom Boot |

## 7.3 Read Query Command

The Query space comes to the foreground and occupies the device address range supplied by the Read Query command address. The mode outputs Common Flash Interface (CFI) data when the device addresses are read. Appendix A, "Common Flash Interface" on page 84 shows the query mode information and addresses. Write the Read Array command to return to read array mode.

The read performance of this CFI data follows the same timings as the main array.

## 7.4 Other ID Mode Data

Other ID mode data besides the Protection registers (such as block locking information and the device JEDEC ID) may be accessed as long as there are no ongoing write or erase operations.

## 7.5 Query (CFI) Data

Query data is read by sending the Read Query command to the device. Reading the Query data is subject to the same restrictions as reading the Protection Registers.

## 8.0 Program Operations

There are five kinds of write operations available in Numonyx® Omneo<sup>™</sup> P8P PCM.

- Word Program (40h, or 10h)

- Bit Alterable Word Write (42h)

- Buffered Program (E8h)

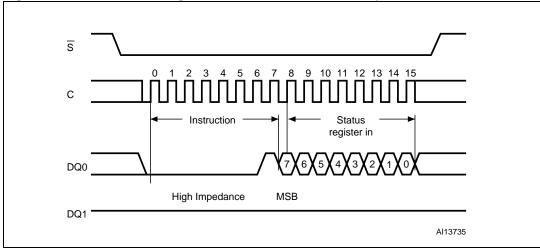

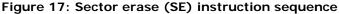

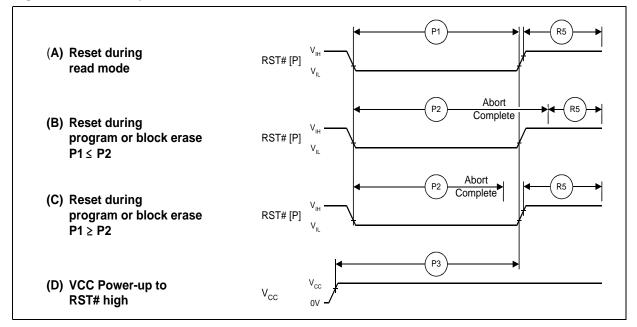

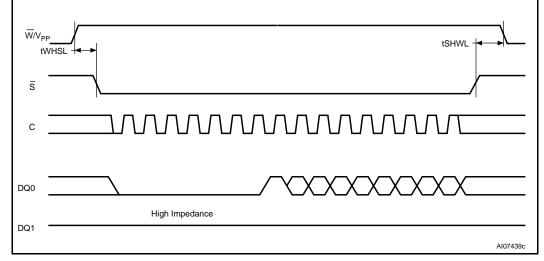

- Bit Alterable Buffered Write (EAh)