# Numonyx™ Wireless Flash Memory (W18 SCSP)

128-Mbit W18 Family with Synchronous PSRAM

### **Datasheet**

# **Product Features**

- Device Architecture

- Flash Die Density: 32, 64 or 128-Mbit

- PSRAM Die Density: 16 or 32-Mbit

- x16 Non-Mux or ADMux I/O Interface Option

- Bottom or Top Flash Parameter Configuration

- Device Voltage

- Core:  $V_{CC} = 1.8 V$

- $I/O: V_{CCQ} = 1.8 V$

- Device Packaging

- Ballout: QUAD+ (88 Balls)

- Area: 8x10 mmHeight: 1.2 mm

- PSRAM Performance

- 70 ns Initial Read Access;

20 ns Asynchronous Page-Mode Read

- Up to 66 MHz with 9 ns Clock-to-Data Synchronous Burst-Mode Reads and Writes

- Configurable 4-, 8-, 16- and Continuous-Word Burst-Length Reads and Writes

- Partial-Array Self and Temperature-Compensated Refresh

- Programmable Output Impedance

- Flash Performance

- 60 ns Initial Read Access;

20 ns Asynchronous Page-Mode Read

- Up to 66 MHz with 11 ns Clock-to-Data Output Synchronous Burst-Mode Read

- Enhanced Factory Programming Modes:3.1 μs/Word (Typ)

- Flash Architecture

- Read-While-Write/Erase

- Asymmetrical blocking structure

- 4-KWord parameter blocks (Top or Bottom)

- 32-KWord main blocks

- 4-Mbit partition size

- 128-bit One-Time Programmable (OTP)

Protection Register

- Zero-latency block locking

- Absolute write protection with block lock using F-VPP and F-WP#

- Flash Software

- Numonyx<sup>™</sup> FDI, Numonyx<sup>™</sup> PSM, and Numonyx<sup>™</sup> VFM

- Common Flash Interface

- Basic and Extended Flash Command Set

- Quality and Reliability

- Extended Temperature –25 °C to +85 °C

- Minimum 100K Flash Block Erase cycles

- 90 nm ETOX ™ IX Flash Technology

- 130 nm ETOX™ VIII Flash Technology

Order Number: 311760-10 November 2007

INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH NUMONYX™ PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN NUMONYX'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, NUMONYX ASSUMES NO LIABILITY WHATSOEVER, AND NUMONYX DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO SALE AND/OR USE OF NUMONYX PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT. Numonyx products are not intended for use in medical, life saving, life sustaining, critical control or safety systems, or in nuclear facility applications.

Numonyx B.V. may make changes to specifications and product descriptions at any time, without notice.

Numonyx B.V. may have patents or pending patent applications, trademarks, copyrights, or other intellectual property rights that relate to the presented subject matter. The furnishing of documents and other materials and information does not provide any license, express or implied, by estoppel or otherwise, to any such patents, trademarks, copyrights, or other intellectual property rights.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Numonyx reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

Contact your local Numonyx sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an order number and are referenced in this document, or other Numonyx literature may be obtained by visiting Numonyx's website at <a href="http://www.numonyx.com">http://www.numonyx.com</a>.

Numonyx, the Numonyx logo, and StrataFlash are trademarks or registered trademarks of Numonyx B.V. or its subsidiaries in other countries.

$\ensuremath{^{*}\text{O}}$  ther names and brands may be claimed as the property of others.

Copyright © 2007, Numonyx B.V., All Rights Reserved.

Datasheet November 2007

2 Order Number: 311760-10

# **Contents**

| 1.0 | Intro      | duction                                             | 6  |

|-----|------------|-----------------------------------------------------|----|

|     | 1.1        | Nomenclature                                        | 6  |

|     | 1.2        | Acronyms                                            | 7  |

|     | 1.3        | Conventions                                         | 7  |

| 2.0 | Func       | ional Overview                                      | g  |

| 2.0 | 2.1        | Product Description                                 |    |

|     | 2.2        | Device Combinations                                 |    |

|     | 2.3        | Device Operation Overview                           |    |

|     | 2.5        | 2.3.1 Flash and Synchronous PSRAM Bus Operations    |    |

|     |            | 2.3.2 Flash Configuration Operation                 |    |

|     |            | 2.3.3 Flash Memory Map and Partitioning             |    |

| 3.0 | Davis      | e Package Information                               |    |

|     |            | _                                                   |    |

| 4.0 |            | ut and Signal Descriptions                          |    |

|     | 4.1        | Device Signal Ballout                               |    |

|     | 4.2        | Signal Descriptions                                 | 14 |

| 5.0 | Maxi       | num Ratings and Operating Conditions                | 16 |

|     | 5.1        | Device Absolute Maximum Ratings                     |    |

|     | 5.2        | Device Operating Conditions                         |    |

| 6.0 | Dovid      | e Electrical Specifications                         | 17 |

| 0.0 | 6.1        | Flash DC Characteristics                            |    |

|     | 6.2        | Synchronous PSRAM DC Characteristics                |    |

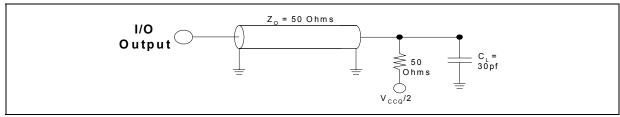

|     | 6.3        | Device AC Test Conditions                           |    |

|     | 0.5        | 6.3.1 Flash Die Capacitance                         |    |

|     |            | 6.3.2 Synchronous PSRAM Die Capacitance             |    |

| 7.0 | Davis      | e AC Characteristics                                |    |

| 7.0 |            |                                                     |    |

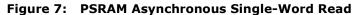

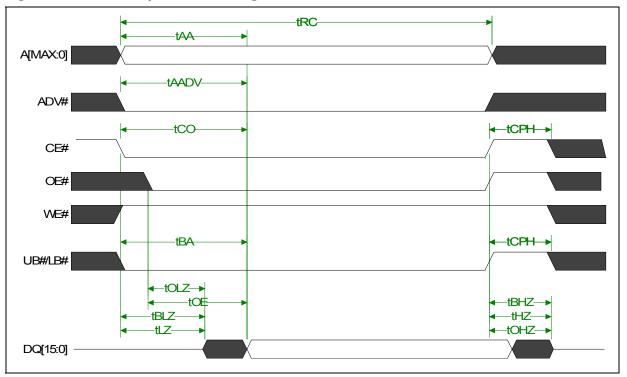

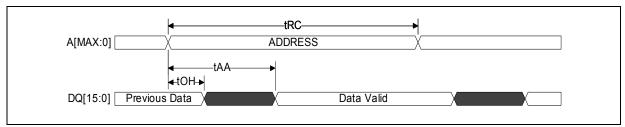

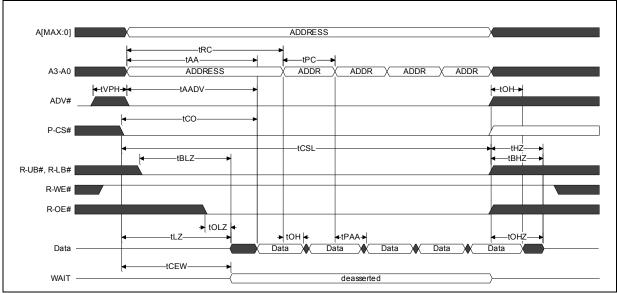

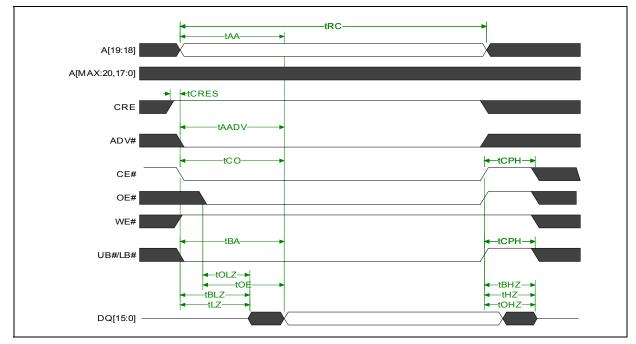

|     | 7.1<br>7.2 | Flash AC Characteristics PSRAM Asynchronous Read.   |    |

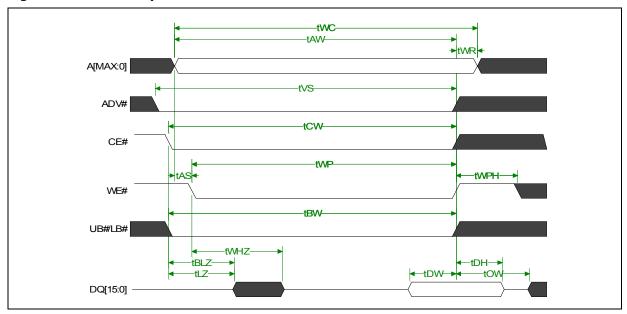

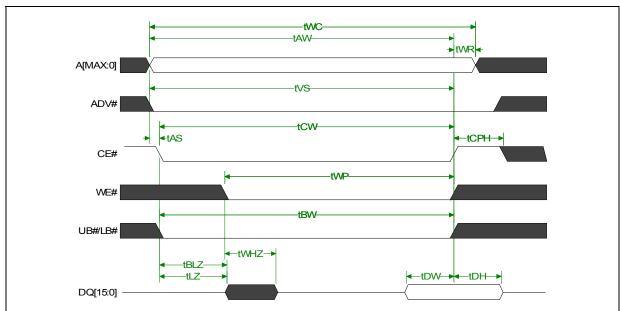

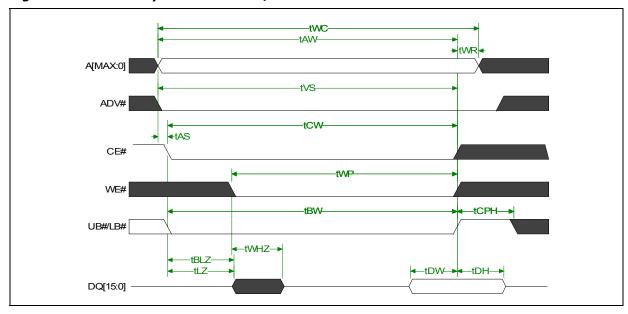

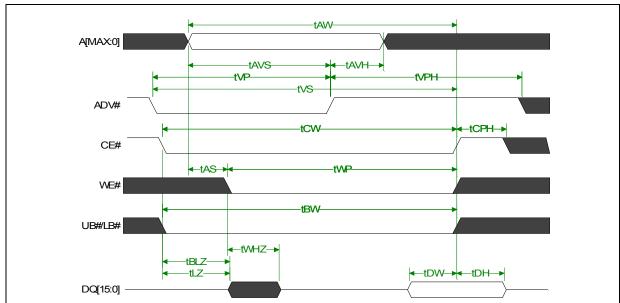

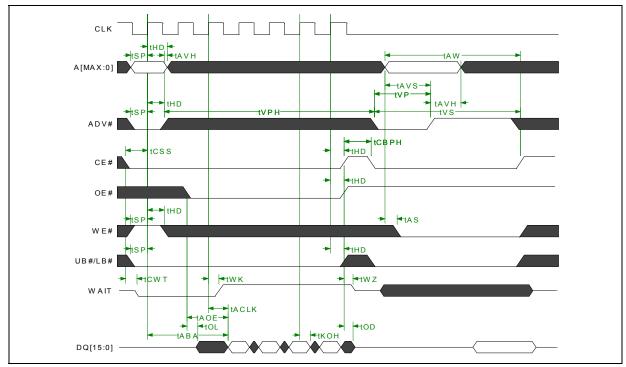

|     | 7.2<br>7.3 | PSRAM Asynchronous Write                            |    |

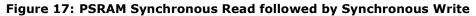

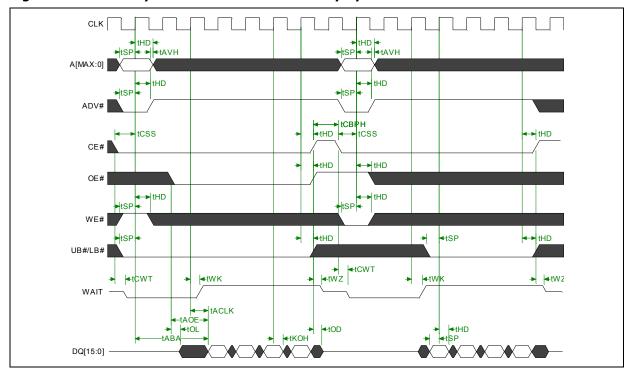

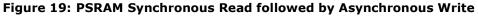

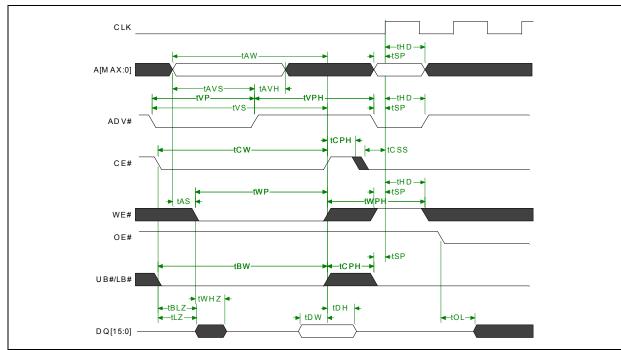

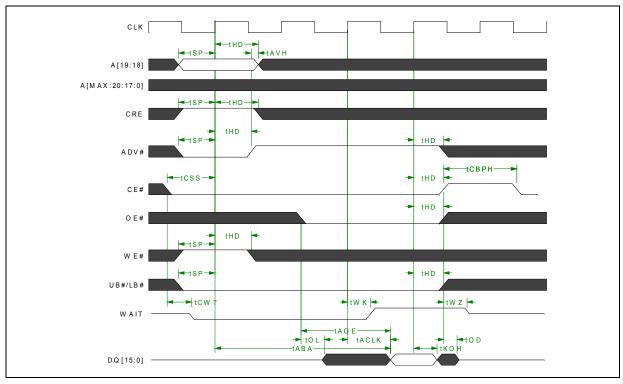

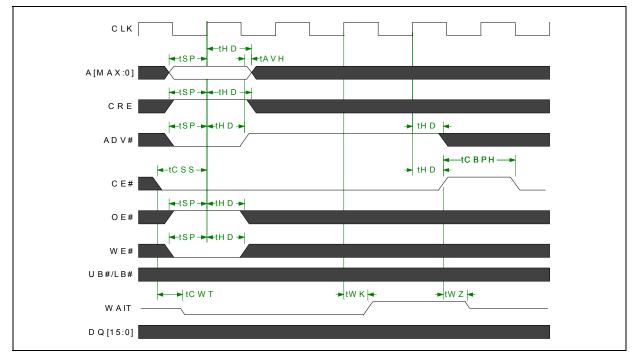

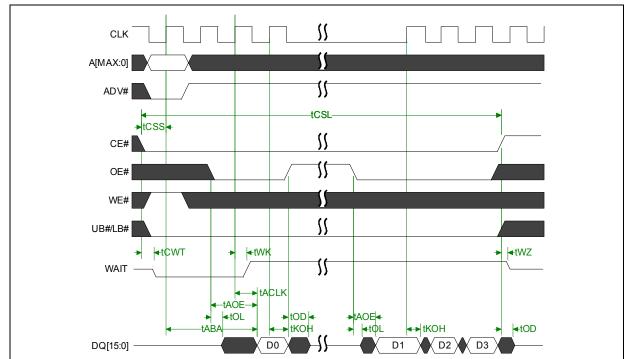

|     | 7.3<br>7.4 | PSRAM Synchronous Read and Write                    |    |

|     |            | ,                                                   |    |

| 8.0 |            | e Bus Interface                                     |    |

|     | 8.1        | PSRAM Reads                                         |    |

|     |            | 8.1.1 PSRAM Asynchronous Read                       |    |

|     |            | 8.1.2 PSRAM Asynchronous Page-Mode Read             |    |

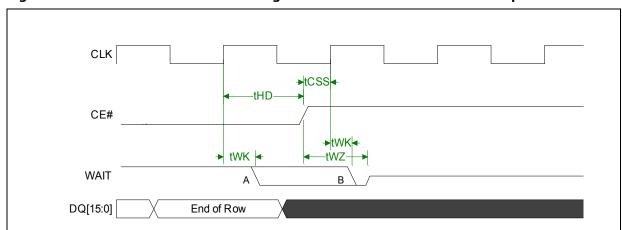

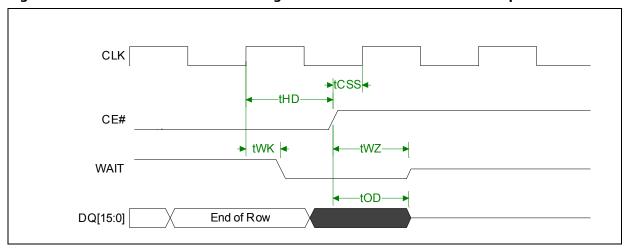

|     |            | 8.1.3 PSRAM Synchronous Burst-Mode Reads            |    |

|     | 8.2        | PSRAM Writes                                        |    |

|     | 0.2        | 8.2.1 PSRAM Asynchronous Write                      |    |

|     |            | 8.2.2 PSRAM Synchronous Write                       |    |

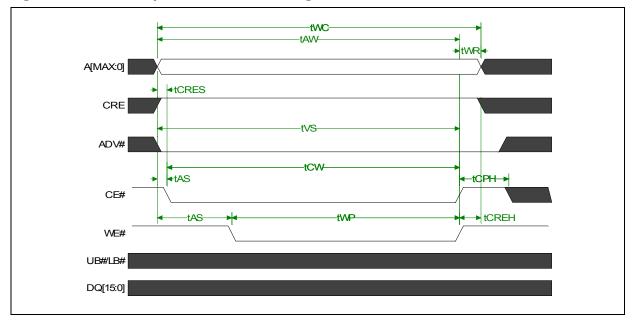

|     |            | 8.2.3 PSRAM Asynchronous Set Control Register Write |    |

|     |            | 8.2.4 PSRAM Synchronous Set Control Register Write  |    |

|     | 8.3        | PSRAM No Operation Command                          |    |

|     | 8.4        | PSRAM Deselect                                      |    |

|     | 8.5        | PSRAM Deep Power Down                               |    |

|     | 8.6        | PSRAM WAIT Signal                                   |    |

| 9.0 | Devis      | e Operations                                        | 37 |

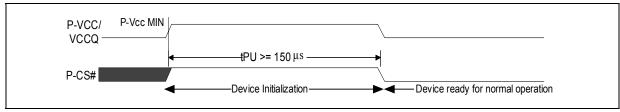

| ٥.٠ | 9.1        | Device Power-Up/Down                                |    |

|     | J. 1       | 9.1.1 Flash Power and Reset Specifications          | 37 |

|     |            |                                                     |    |

November 2007 Order Number: 311760-10

# 128-Mbit W18 Family with Synchronous PSRAM

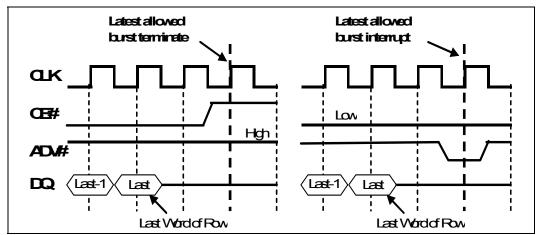

| 9.7 |       | Row Boundary Crossing                          |     |

|-----|-------|------------------------------------------------|-----|

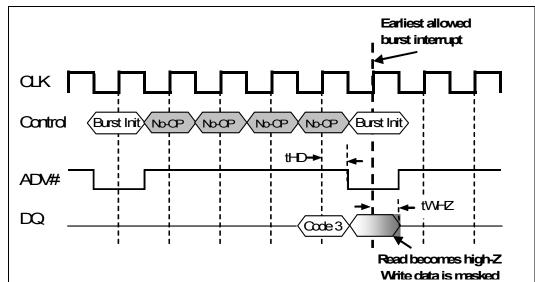

|     |       | PSRAM Burst Termination                        |     |

|     |       | PSRAM Burst Interrupt                          |     |

| 2.3 |       | PSRAM Burst Suspend                            |     |

| 9.6 |       | Burst Suspend, Interrupt, or Termination       |     |

|     |       | PSRAM Self-Refresh Operations at Low Frequency |     |

| 9.5 |       | Self-Refresh Operation                         |     |

|     |       | Cautionary Note About Software Register Access |     |

|     |       | PSRAM Software Register Access                 |     |

|     |       | PSRAM Hardware Control Register Access         |     |

| 9.4 |       | Access to Control Register                     |     |

|     |       | PSRAM Refresh Control Register                 |     |

|     |       | PSRAM Bus Control Register                     |     |

| 9.3 |       | Control Registers                              |     |

| 9.2 |       | Operating Modes                                |     |

|     | 9.1.2 | PSRAM Power-Up Sequence and Initialization     | .37 |

Downloaded from **Elcodis.com** electronic components distributor

November 2007 Order Number: 311760-10

# **Revision History**

| Date          | Revision | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|---------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| February 2006 | 001      | Initial release                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| March 2006    | 002      | <ul> <li>Corrected flash and PSRAM specification of CLK from 66 MHz to 54 MHz, and flash burst-mode read timing from 11 ns to 14 ns.</li> <li>Remove Page-Mode Read details for flash and PSRAM, feature not supported.</li> <li>Changed tCLK3 Min value in Section 11, "PSRAM AC Characteristics—Asynchronous Read" on page 21 from 15 ns to 18 ns to correlate CLK value change.</li> <li>Updated Ordering Information Table.</li> </ul>                                                      |

| May 2006      | 003      | <ul> <li>Added ADMux I/O interface flash references, making document inclusive of Non-Mux and ADMux I/O flash interface WQ product family, superseding 64-Mbit WQ Family with Synchronous PSRAM datasheet #311641.</li> <li>Updated PSRAM burst-mode improved read timing from 14 ns to 9 ns. Added 16 Mbit PSRAM AC/DC specifications that was TBD in revision -002.</li> <li>Update various descriptions of the W18 and PSRAM features, specifications and operations for clarity.</li> </ul> |

| July 2006     | 004      | Made miscellaneous edits and formatting changes.                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| August 2006   | 005      | Added 90 nm device option.                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| November 2006 | 006      | <ul> <li>Revised datasheet to show improved CLK from 54 MHz to 66 MHz for Non Mux and AD Mux products.</li> <li>Revised datasheet to show improved flash burst mode read timing from 14 ns to 11 ns.</li> </ul>                                                                                                                                                                                                                                                                                 |

| January 2007  | 007      | Revised ordering information to add non-muxed line items                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| July 2007     | 008      | <ul> <li>Added section for configuring device in asynchronous mode. Revised typos in Ordering<br/>infomation: Changed AD-Mux to Non-Mux. Added LIs PF38F2030W0YTQE and<br/>PF38F2040W0YCQE.</li> </ul>                                                                                                                                                                                                                                                                                          |

| August 2007   | 009      | Updated ordering information                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| November 2007 | 10       | Applied Numonyx branding.                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

# 1.0 Introduction

The 128-Mbit Numonyx™ Wireless Flash memory with synchronous PSRAM stacked device family offers multiple high-performance solutions. The W18 (Non-Mux or AD Mux I/O interface option) highlighted features like asymmetrical block array, configurable burst lengths, security using OTP and zero-latency block lock. The W18 delivers up to 66 MHz synchronous burst and page-mode read rates with multipartitioning Read-While-Write and Read-While-Erase operations. The synchronous PSRAM (Non-Mux and AD-Mux I/O interface) is a high-performance volatile memory operating at speeds up to 66 MHz with configurable burst lengths. The PSRAM lower sixteen addresses can be routed to the data pins on the PCB board to enable a flexible flash and PSRAM A/D-Mux I/O interface device design. The W18 stacked device features 1.8 volt low-voltage operation in an Numonyx™ QUAD+ standard footprint and signal ballouts.

This document contains information pertaining to the 128-Mbit Title stacked device family. The W18 is available as a Non-Multiplex or Address-Data MuxItiplex (ADMux) I/O interface option, while the synchronous PSRAM is available only as a Non-Multiplex I/O interface. The intent of this document is to provide information where this product differs from the  $Intel^{\circledR}$  Wireless Flash Memory (W18) device.

Refer to the latest revision of the  $Intel^{\circledR}$  Wireless Flash Memory (W18) Discrete Datasheet (order number: Non-Mux I/O doc #290701 and ADMux I/O doc #313272) for specific flash product details not included in this document.

### 1.1 Nomenclature

| 1.8 Volt Core      | VCC (memory subsystem die core) voltage range of 1.7 V – 1.95 V.                                                                                   |

|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.8 Volt I/O       | VCCQ (memory subsystem I/O) voltage range of 1.7 V – 1.95 V.                                                                                       |

| ADMux I/O          | Address-Data Multiplex I/O interface, where the lower sixteen (16) addresses are multiplexed on the data pins (DQ[15:0]) during any address cycle. |

| Asserted           | Signal with logical voltage level $V_{\mathrm{IL}}$ , or enabled.                                                                                  |

| Block              | Group of cells, bits, bytes, or words within the flash memory array that get erased with one erase instruction.                                    |

| Deasserted         | Signal with logical voltage level VIH or disabled.                                                                                                 |

| Device             | A specific memory type or stacked flash and xRAM memory density configuration combination within a memory subsystem product family.                |

| Die                | Individual flash or xRAM die used in a stacked package memory device.                                                                              |

| High-Z             | High Impedance.                                                                                                                                    |

| Low-Z              | Signal is Driven on the bus.                                                                                                                       |

| Non-Array<br>Reads | Flash reads which return flash Device Identifier, CFI Query, Protection Register, and Status Register information.                                 |

| Non-Mux I/O        | Traditional parallel flash interface where address are not multiplex onto the data pins. All address and data pins are unique.                     |

| Partition          | A group of flash blocks that shares common status register read state.                                                                             |

| Program            | An operation to Write data to the flash array or xRAM.                                                                                             |

| Write              | Bus cycle operation at the inputs of the flash or xRAM die, in which a command or data are sent to the flash array or xRAM.                        |

Datasheet November 2007 6 Order Number: 311760-10

# 1.2 Acronyms

| ADC          | A tomatic Book Go tom                 |

|--------------|---------------------------------------|

| APS          | Automatic Power Savings               |

| EFA          | Extended Flash Array                  |

| BCR          | (PSRAM) Bus Control Register          |

| Buffered EFP | Buffered Enhanced Factory Programming |

| CR           | (Flash) Configuration Register        |

| CSP          | Chip Scale Package                    |

| MLC          | Multi-Level Cell                      |

| OTP          | One-Time Programmable                 |

| PLR          | Protection Lock Register              |

| PR           | Protection Register                   |

| RCR          | (PSRAM) Refresh Control Register      |

| RFU          | Reserved for Future Use               |

| RWW / RWE    | Read-While-Write / Read-While-Erase   |

| SR           | Status Register                       |

| WSM          | Write State Machine                   |

#### **Conventions** 1.3

| A5              | Denotes one element of a signal group, in this case address bit 5.                                                                                                                                                 |

|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Clear           | Logical zero (0).                                                                                                                                                                                                  |

| DQ[15:0]        | Denotes a group of similarly named signals, such as data bus.                                                                                                                                                      |

| F-CE#           | Denotes Chip Enable of the flash die, where "F" to denote the specific signal suffix and "CE#" is the root signal name of the NOR flash die.                                                                       |

| P-CE# or P-CS#  | Denotes Chip Enable of the PSRAM die, where "P" to denote the specific signal suffix and "CE# or CS#" are the root signal name of the PSRAM die. PSRAM CE# and CS# is used interchangably throughout the document. |

| S-CS1#          | Denotes Chip Enable of the SRAM die, where "S" to denote the specific signal suffix and "CS1#" is the root signal name of the SRAM die.                                                                            |

| Set             | Logical one (1).                                                                                                                                                                                                   |

| SR4             | A flash status register bit, in this case status register bit 4 of SR[15:0].                                                                                                                                       |

| VCC             | Signal or voltage connection.                                                                                                                                                                                      |

| V <sub>CC</sub> | Signal or voltage level.                                                                                                                                                                                           |

| VSS             | Denotes a global power signal of the stacked device. VSS is common to all memory dies within a stacked memory device.                                                                                              |

November 2007 Order Number: 311760-10 Datasheet 7

#### **Functional Overview** 2.0

#### 2.1 **Product Description**

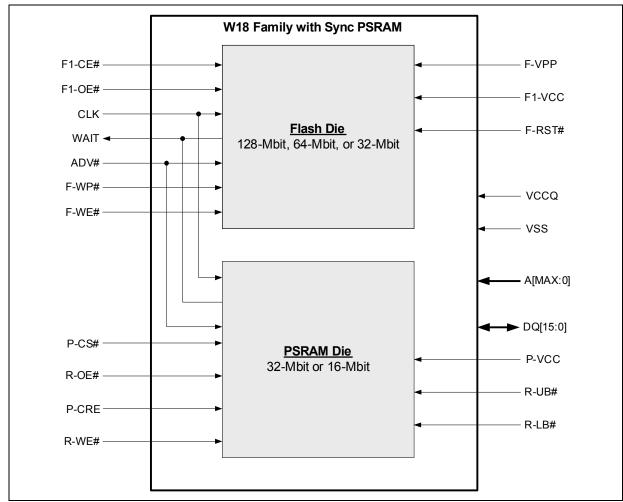

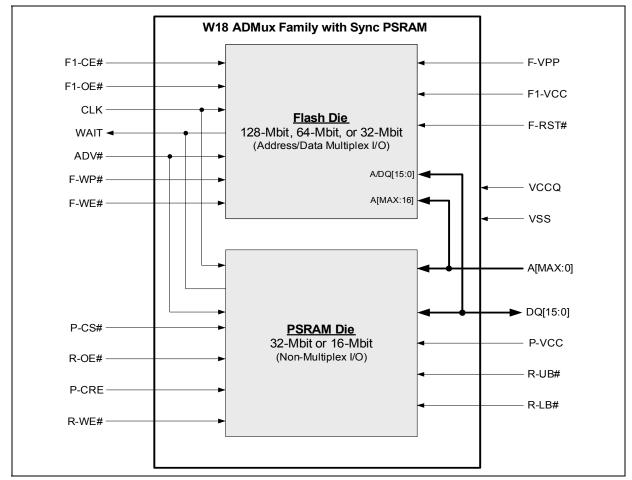

The W18 family with synchronous PSRAM stacked product family encompasses multiple W18 flash memory plus synchronous PSRAM die combinations. Figure 1 shows the maximum configuration options for W18 non-multiplex I/O (standard) product and Figure 2 shows the maximum configuration options for W18 AD-Multiplex I/O product family with synchronous PSRAM internal package connections.

Note: See detailed signal information in Section 4.2, "Signal Descriptions" on page 14.

Figure 1: W18 Product Family with Sync PSRAM Block Diagram

### Notes:

F2-OE# must be treated as RFU. However, for future product compatibility, F2-OE# can be tied to F1-OE# or left floated. F2-VCC must be treated as RFU. However, for future product compatibility, F2-VCC can be tied to F1-VCC or left floated.

Note: See detailed signal information in Section 4.2, "Signal Descriptions" on page 14.

Datasheet

November 2007

Figure 2: W18 ADMux I/O Interface Product Family with Sync PSRAM Block Diagram

### Notes:

- F2-OE# must be treated as RFU. However, for future product compatibility, F2-OE# can be tied to F1-OE# or left floated. F2-VCC must be treated as RFU. However, for future product compatibility, F2-VCC can be tied to F1-VCC or left floated.

#### 2.2 **Device Combinations**

Note: For combination not listed, contact your local Numonyx Sales Representative for details.

Table 1: **Device Combinations**

| I/O<br>Voltage | Flash Type (Mbit)  | xRAM Type (Mbit) | Package Size<br>(mm) | Package Ballout |

|----------------|--------------------|------------------|----------------------|-----------------|

|                | 64 W18             | 32 Sync PSRAM    | 8x10x1.2             | QUAD+           |

| 1.8 V          | 32 W18 (ADMux I/O) | 16 Sync PSRAM    | 8x10x1.2             | QUAD+           |

| 1.0 V          | 64 W18 (ADMux I/O) | 16 Sync PSRAM    | 8x10x1.2             | QUAD+           |

|                | 64 W18 (ADMux I/O) | 32 Sync PSRAM    | 8x10x1.2             | QUAD+           |

November 2007 Order Number: 311760-10

Datasheet

#### 2.3 **Device Operation Overview**

The following sections describes the bus operations and device state between the flash and synchronous PSRAM.

#### 2.3.1 Flash and Synchronous PSRAM Bus Operations

Bus operations for the W18 stacked device involve the control of flash and PRAM inputs. The bus operations are shown in Table 2.

Note:

See the Intel® Wireless Flash Memory (W18) Discrete Datasheet (order number: Non-Mux I/O doc #290701 and ADMux I/O doc #313272) for complete descriptions of the flash modes and commands, command bus-cycle definitions, and flowcharts that illustrate operational routines not documented in this Datasheet.

Table 2: Flash and PSRAM Device Bus Operations

| Device    | Mode                                        | F-RST# | F-CE#               | F-0E# | F-WE# | ADV#8   | F-VPP                                   | P-CRE#                                               | h-CS# | R-0E# | R-WE# | R-UB#,<br>R-LB# | DQ[15:0]                  | WAIT <sup>7</sup> | Notes           |                 |     |

|-----------|---------------------------------------------|--------|---------------------|-------|-------|---------|-----------------------------------------|------------------------------------------------------|-------|-------|-------|-----------------|---------------------------|-------------------|-----------------|-----------------|-----|

| •         | Synchronous<br>Array and Non-<br>Array Read | Н      | L                   | L     | Н     | L       | Х                                       | Х                                                    | Н     | Х     | Х     | Х               | Flash D <sub>OUT</sub>    | Active            | 1,2,4           |                 |     |

| or #4)    | Asynchronous<br>Read                        | Н      | L                   | L     | Н     | Х       | Х                                       | Х                                                    | Н     | Х     | Х     | Х               | Flash D <sub>OUT</sub>    | Deasserted        | 1,2,4           |                 |     |

| 2, #3,    | Write                                       | Н      | L                   | Н     | L     | L       | V <sub>PPL</sub> or<br>V <sub>PPH</sub> | Х                                                    | Н     | Х     | Х     | Х               | Flash D <sub>IN</sub>     | Deasserted        | 1,2,3           |                 |     |

| (#1, #    | Output Disable                              |        | L                   | Н     | Н     | Х       | Х                                       |                                                      |       |       |       |                 | Flash<br>High-Z           | Flash<br>High-Z   | 1,2             |                 |     |

| Flash (   | Standby                                     | Н      | Н                   | Х     | Х     | Х       | Х                                       | Any PSRAM mode allowed Flash Flash High-Z High-Z 1,2 |       |       |       |                 |                           | 1,2               |                 |                 |     |

|           | Reset                                       | L      | Х                   | Х     | Х     | Х       | Х                                       |                                                      |       |       |       | Flash<br>High-Z | Flash<br>High-Z           | 1,2               |                 |                 |     |

|           | Read                                        | Х      | Н                   | Х     | Х     | Х       | Х                                       | L                                                    | L     | L     | Н     | L               | PSRAM<br>D <sub>OUT</sub> | Active            | 1,2,5,7         |                 |     |

| #2)       | Write                                       | Х      | Н                   | Х     | Х     | Х       | Х                                       | L                                                    | L     | Н     | L     | L               | PSRAM D <sub>IN</sub>     | Active            | 1,2,5,7         |                 |     |

| (#1 or    | Output Disable                              |        |                     |       |       |         |                                         |                                                      |       | L     | L     | Н               | Н                         | Х                 | PSRAM<br>High-Z | PSRAM<br>High-Z | 1,2 |

| PSRAM (#1 | Standby                                     |        | Any Flash mode allo |       |       | le allo | wed                                     | L                                                    | Н     | Х     | Х     | Х               | PSRAM<br>High-Z           | PSRAM<br>High-Z   | 1,2             |                 |     |

| ă         | Low Power<br>Mode                           |        |                     |       |       |         |                                         | Х                                                    | Х     | Х     | х     | Х               | PSRAM<br>High-Z           | PSRAM<br>High-Z   | 1,2             |                 |     |

### Notes:

- For flash, do not simultaneously assert F-OE# and F-WE#. For PSRAM, do not simultaneously assert 1. R-OE# and R-WE#.

- 2.

- Refer to the latest revision of the  $Intel^{\textcircled{B}}$  Wireless Flash Wireless Wirel3.

- 4.

- Non-Mux I/O doc #290701 and ADMux I/O doc #313272) for valid D<sub>IN</sub> during Flash writes.

Flash CFI query and Status Register accesses, use DQ[7:0] only. All other reads use DQ[15:0].

P-CRE# is low if PSRAM is in standby. P-CRE# is X if PSRAM is in Low-Power mode. See Section 9.0, "Device Operations" on page 37 for more details about Standby and Low Power mode.

WALT indicates data published whose is Superpressed about Standby and Low Power mode. 5.

- WAIT indicates data validity only when in Synchronous mode. Ignore this setting in Asynchronous and Page-mode. The Flash and Synchronous PSRAM dies share the WAIT signal. 6.

- During AD-Mux I/O operation, ADV# must remain deasserted during the data phase.

Datasheet November 2007 Order Number: 311760-10 10

Table 3: **PSRAM Bus Operation**

| State                        | Operation<br>Modes                       | Power<br>Mode         | CLK  | P-<br>CS# | ADV# | R-<br>WE# | R-<br>OE# | R-UB#<br>R-LB# | P-<br>CRE | A19/<br>A18    | Addr.      | DQ                 | Notes |

|------------------------------|------------------------------------------|-----------------------|------|-----------|------|-----------|-----------|----------------|-----------|----------------|------------|--------------------|-------|

| Read                         | Asynchronous                             | Active                | L    | L         | L    | Н         | L         | L              | L         | V              | V          | DOUT               |       |

| Write                        | Asynchronous<br>NOR-Flash                | Active                | L    | L         | L    | L         | х         | L              | L         | ٧              | ٧          | DIN                | 1,2   |

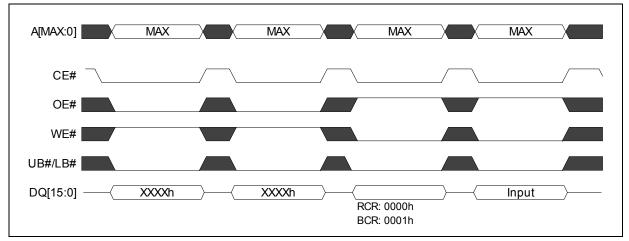

| Set Control<br>Register      | Asynchronous<br>NOR-Flash                | Active                | L    | L         | L    | L         | Н         | Х              | Н         | LL<br>HL       | RCR<br>BCR | Х                  |       |

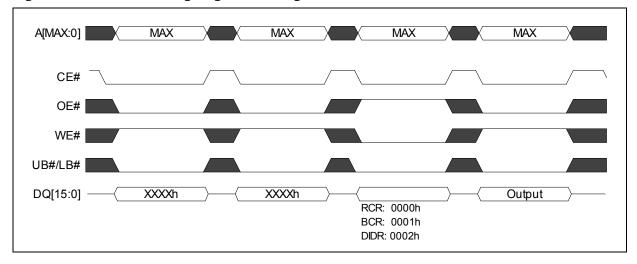

| Fetch<br>Control<br>Register | Asynchronous                             | Active                | L    | L         | L    | Н         | L         | L              | Н         | LL<br>HL<br>LH | х          | RCR<br>BCR<br>DIDR |       |

| No<br>Operation              | Asynchronous<br>Synchronous<br>NOR-Flash | Standby<br>/Active    | L    | L         | Н    | Н         | Н         | х              | L         | х              | х          | High-Z             | 3     |

| Deselect                     | Asynchronous<br>Synchronous<br>NOR-Flash | Standby               | L    | Н         | Х    | Х         | х         | х              | Х         | х              | х          | High-Z             |       |

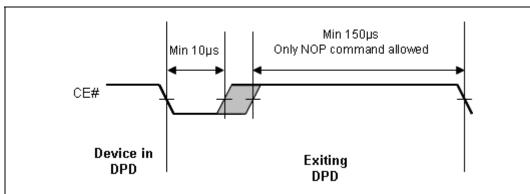

| Deep<br>Power<br>Down        | Asynchronous<br>Synchronous<br>NOR-Flash | Deep<br>Power<br>Down | L    | Н         | Х    | х         | Х         | х              | Х         | х              | х          | High-Z             |       |

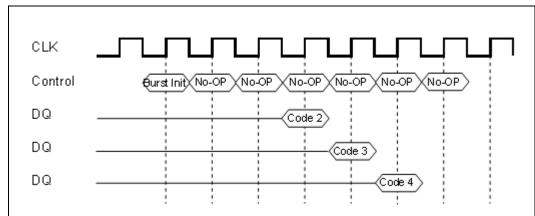

| Burst Init<br>Read           | Synchronous<br>NOR-Flash                 | Active                | L->H | L         | L    | Н         | Х         | L              | L         | ٧              | ٧          | Х                  | 4     |

| Burst Read                   | Synchronous<br>NOR-Flash                 | Active                | L->H | L         | Н    | Х         | L         | L              | Х         | х              | х          | DOUT               | 4,5   |

| Burst Init<br>Write          | Synchronous                              | Active                | L->H | L         | L    | L         | Н         | х              | L         | ٧              | ٧          | Х                  | 4     |

| Burst Write                  | Synchronous                              | Active                | L->H | L         | Н    | Х         | Х         | L              | Х         | Х              | Х          | DIN                | 4     |

| Set Control<br>Register      | Synchronous                              | Active                | L->H | L         | L    | L         | Н         | х              | Н         | LL<br>HL       | RCR<br>BCR | х                  | 4     |

| Fetch<br>Control<br>Register | Synchronous                              | Active                | L->H | L         | L    | Н         | L         | L              | н         | LL<br>HL<br>LH | ×          | RCR<br>BCR<br>DIDR | 4,6   |

### Notes:

- The table reflects behavior if R-UB# and R-LB# are asserted low. If only either of the signals, R-UB# or R-LB# is asserted low only the corresponding data byte will be written (UB# enables DQ15-DQ8, LB# enables DQ7-DQ0). 1.

- 2. 3. 4. During a write access invoked by R-WE# set to low the R-OE# signal is ignored.

- Power mode of Standby or Active will depend on the internal operation of device at the time.

- Clock configuration is rising edge.

- Output drivers are controlled by the asynchronous R-OE# control signal.

- During the initial command cycle R-OE# is don't care (X) and subsequent cycles it must be low (L)

#### 2.3.2 **Flash Configuration Operation**

Refer to the Intel® Wireless Flash Memory (W18) Datasheet (order number: Non-Mux I/O doc #290701 and ADMux I/O doc #313272) for configuration operation detailed information.

#### 2.3.3 Flash Memory Map and Partitioning

Refer to the <code>Intel</code>  $^{\circledR}$  <code>Wireless Flash Memory (W18) Datasheet</code> (order number: Non-Mux I/O doc #290701 and ADMux I/O doc #313272) for the memory map and partitioning information.

# 3.0 Device Package Information

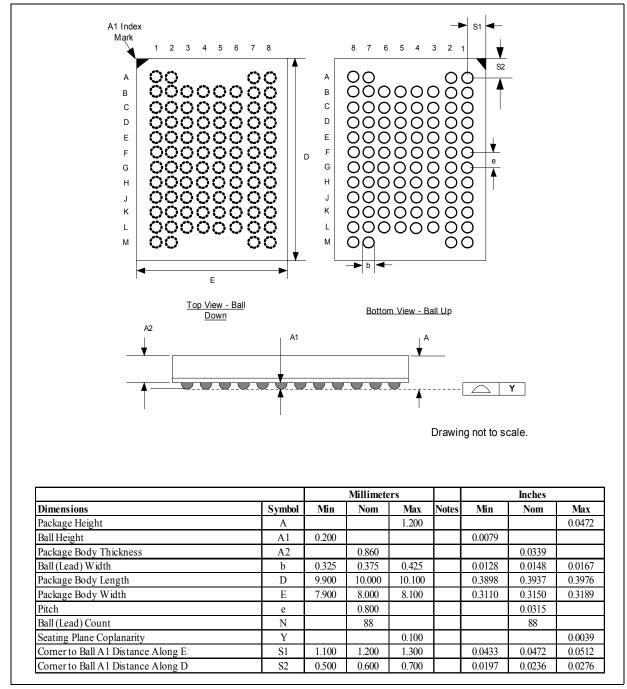

Figure 3: Mechanical Specifications for QUAD+ Ballout Package (8x10x1.2 mm)

**Note:** For mechanical drawings not shown in this document, contact your local Numonyx Sales representative for additional details.

Datasheet November 2007 12 Order Number: 311760-10

# 4.0 Ballout and Signal Descriptions

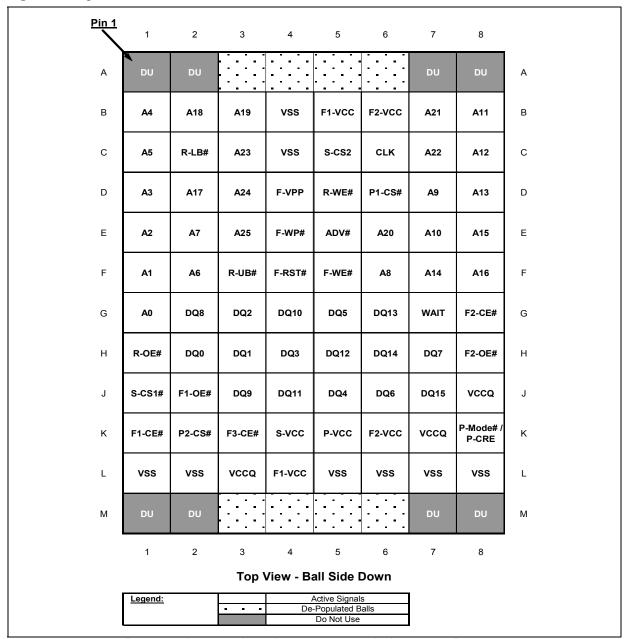

# 4.1 Device Signal Ballout

Figure 4: QUAD+ Ballout

**Note:** See Figure 1, "W18 Product Family with Sync PSRAM Block Diagram" on page 8 for electrical connections details.

# 4.2 Signal Descriptions

Table 4: Signal Descriptions (Sheet 1 of 3)

| Table 4.       |                   | an Descriptions (Sheet 1 of 3)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Neta      |

|----------------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

| Symbol         | Туре              | Signal Descriptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Note<br>s |

| Address ar     | nd Data S         | Signals, Non-Mux                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |           |

| A[MAX:0]       | Input             | ADDRESS: Global device signals.  Shared address inputs for all memory die during Read and Write operations.  • 128-Mbit: AMAX = A22  • 64-Mbit: AMAX = A21  • 32-Mbit: AMAX = A20  • 16-Mbit: AMAX = A19  • A0 is the lowest-order word address.  • Unused address inputs should be treated as RFU.  Note: During AD-Mux I/O operation, W18 A[MAX:16] can be treated as a NC pins, but C <sub>L</sub> will exist on the pins.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 1         |

| DQ[15:0]       | Input /<br>Output | <b>DATA INPUT/OUTPUTS:</b> Global device signals. Inputs data and commands during Write cycles, outputs data during Read cycles. Data signals are High-Z when the device is deselected or its output is disabled.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |           |

| Address ar     | d Data S          | Signals, AD-Mux                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |           |

| DQ[15:0]       | Input /<br>Output | ADDRESS-DATA MULTIPLEXED INPUTS/ OUTPUTS: AD-Mux I/O flash signals.  During AD-Mux Read cycles, DQ[15:0] are used to input the lower address followed by read-data output. During AD-Mux Write cycles, DQ[15:0] are used to input the lower address followed by commands or data.  • DQ[15:0] are High-Z when the device is deselected or its output is disabled.  • DQ[15:0] is only used with AD-Mux I/O flash device.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 1         |

| Control Sig    | ınals             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |           |

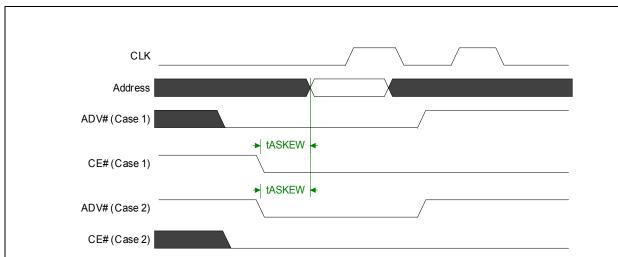

| ADV#           | Input             | <ul> <li>ADDRESS VALID: Flash- and Synchronous PSRAM-specific signal; low-true input.</li> <li>During a synchronous read operation, the address is latched on the rising edge of ADV# or on the next valid CLK edge with ADV# low, whichever occurs first.</li> <li>In an asynchronous flash read operation, the address is latched on the rising edge of ADV#, or continuously flows through while ADV# is low.</li> <li>During a synchronous flash Read operation, the address is latched on the rising edge of ADV# or the first active CLK edge whichever occurs first.</li> <li>During synchronous PSRAM read and synchronous write modes, the address is either latched on the first rising clock edge after ADV# assertion or on the rising edge of ADV# whichever edge occurs first. In asynchronous read and asynchronous write modes, ADV# can be used to latch the address, but can be held low for the entire operation as well.</li> <li>Note: During AD-Mux I/O operation, ADV# must remain deasserted during the data phase.</li> </ul> |           |

| F[3:1]-<br>CE# | Input             | <ul> <li>FLASH CHIP ENABLE: Flash-specific signal; low-true input.</li> <li>When low, F-CE# selects the associated flash memory die. When high, F-CE# deselects the associated flash die. Flash die power is reduced to standby levels, and its data and F-WAIT outputs are placed in a High-Z state.</li> <li>F1-CE# is dedicated to flash die #1.</li> <li>F[3:2]-CE# are dedicated to flash die #3 through #2, respectively, if present. Otherwise, any unused flash chip enable should be treated as RFU.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |           |

| CLK            | Input             | <b>CLOCK:</b> Flash- and Synchronous PSRAM-specific input signal.  CLK synchronizes the flash and/or synchronous PSRAM with the system clock during synchronous operations.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |           |

| F[2:1]-<br>OE# | Input             | FLASH OUTPUT ENABLE: Flash-specific signal; low-true input.  When low, F-OE# enables the output drivers of the selected flash die. When high, F-OE# disables the output drivers of the selected flash die and places the output drivers in High-Z.  • F2-OE# common to all other flash dies, if present. Otherwise it is an RFU, however, it is highly recommended to always common F1-OE# and F2-OE# on the PCB.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |           |

Datasheet November 2007 14 Order Number: 311760-10

Table 4: Signal Descriptions (Sheet 2 of 3)

| Symbol          | Туре   | Signal Descriptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Note<br>s |

|-----------------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

| R-OE#           | Input  | RAM OUTPUT ENABLE: PSRAM- and SRAM-specific signal; low-true input.  When low, R-OE# enables the output drivers of the selected memory die. When high, R-OE# disables the output drivers of the selected memory die and places the output drivers in High-Z if present. Otherwise it is an RFU.                                                                                                                                                                                                                                             | 3         |

| F-RST#          | Input  | <b>FLASH RESET:</b> Flash-specific signal; low-true input. When low, F-RST# resets internal operations and inhibits writes. When high, F-RST# enables normal operation.                                                                                                                                                                                                                                                                                                                                                                     |           |

| WAIT            | Output | <ul> <li>WAIT: Flash- and Synchronous PSRAM-specific signal; configurable true-level output.</li> <li>When asserted, WAIT indicates invalid output data. When deasserted, WAIT indicates valid output data.</li> <li>WAIT is driven whenever the flash or the synchronous PSRAM is selected and its output enable is low.</li> <li>WAIT is High-Z whenever flash or the synchronous PSRAM is deselected, or its output enable is high.</li> <li>Flash and PSRAM must configure the WAIT RCR bit to be the same true-level state.</li> </ul> |           |

| F-WE#           | Input  | <b>FLASH WRITE ENABLE:</b> Flash-specific signal; low-true input. When low, F-WE# enables Write operations for the enabled flash die. Address and data are latched on the rising edge of F-WE#.                                                                                                                                                                                                                                                                                                                                             |           |

| R-WE#           | Input  | RAM WRITE ENABLE: PSRAM- and SRAM-specific signal; low-true input. When low, R-WE# enables Write operations for the selected memory die. Data is latched on the rising edge of R-WE# if present. Otherwise it is an RFU.                                                                                                                                                                                                                                                                                                                    | 3         |

| F-WP#           | Input  | <b>FLASH WRITE PROTECT:</b> Flash-specific signals; low-true inputs.  When low, F-WP# enables the Lock-Down mechanism. When high, F-WP# overrides the Lock-Down function, enabling locked-down blocks to be unlocked with the Unlock command.                                                                                                                                                                                                                                                                                               |           |

| P-CRE           | Input  | PSRAM CONTROL REGISTER ENABLE: Synchronous PSRAM-specific signal; high-true input. When high, P-CRE enables access to the PSRAM Refresh Control Register (P-RCR) or Bus Control Register (P-BCR). When low, P-CRE enables normal Read or Write operations if present. Otherwise it is an RFU.                                                                                                                                                                                                                                               | 2         |

| P-MODE#         | Input  | PSRAM MODE#: Asynchronous only PSRAM-specific signal; low-true input.  When low, P-MODE# enables access to the PSRAM configuration register, and to enter or exit Low-Power mode. When high, P-MODE# enables normal Read or Write operations if present. Otherwise it is an RFU.                                                                                                                                                                                                                                                            | 2         |

| P[2:1]-<br>CS#  | Input  | PSRAM CHIP SELECT: PSRAM-specific signal; low-true input.  When low, P-CS# selects the associated PSRAM memory die. When high, P-CS# deselects the associated PSRAM die. PSRAM die power is reduced to standby levels, and its data and WAIT outputs are placed in a High-Z state.  • P1-CS# is dedicated to PSRAM die #1 if present. Otherwise it is an RFU.  • P2-CS# is dedicated to PSRAM die #2 if present. Otherwise it is an RFU.                                                                                                    | 3         |

| S-CS1#<br>S-CS2 | Input  | SRAM CHIP SELECTS: SRAM-specific signals; S-CS1# low-true input, S-CS2 high-true input.  When both S-CS1# and S-CS2 are asserted, the SRAM die is selected. When either S-CS1# or S-CS2 is deasserted, the SRAM die is deselected.  • S-CS1# and S-CS2 are dedicated to SRAM if present. Otherwise it is an RFU.                                                                                                                                                                                                                            | 3         |

| R-UB#<br>R-LB#  | Input  | RAM UPPER/LOWER BYTE ENABLES: PSRAM- and SRAM-specific signals; low-true inputs. When low, R-UB# enables DQ[15:8] and R-LB# enables DQ[7:0] during PSRAM or SRAM Read and Write cycles. When high, R-UB# masks DQ[15:8] and R-LB# masks DQ[7:0] if present. Otherwise it is an RFU.                                                                                                                                                                                                                                                         | 3         |

| Power Sign      | nals   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |           |

| F-VPP           | Power  | FLASH PROGRAM/ERASE VOLTAGE: Flash specific. F-VPP supplies program or erase power to the flash die.                                                                                                                                                                                                                                                                                                                                                                                                                                        |           |

| F[2:1]-<br>VCC  | Power  | FLASH CORE POWER SUPPLY: Flash specific.  • F[2:1]-VCC supplies the core power to the flash dies.  • F2-VCC is recommended to be tied to F1-VCC, else it is an RFU.                                                                                                                                                                                                                                                                                                                                                                         |           |

Signal Descriptions (Sheet 3 of 3)

| Symbol | Туре       | Signal Descriptions                                                                                                                                         | Note<br>s |

|--------|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

| VCCQ   | Power      | I/O POWER SUPPLY: Global device I/O power. VCCQ supplies the device input/output driver voltage.                                                            |           |

| P-VCC  | Power      | PSRAM CORE POWER SUPPLY: PSRAM specific. P-VCC supplies the core power to the PSRAM die if present. Otherwise it is an RFU.                                 | 3         |

| S-VCC  | Power      | SRAM POWER SUPPLY: SRAM specific. S-VCC supplies the core power to the SRAM die if present. Otherwise it is an RFU.                                         | 3         |

| VSS    | Groun<br>d | <b>DEVICE GROUND:</b> Global ground reference for all signals and power supplies. Connect all VSS balls to system ground. Do not float any VSS connections. |           |

| DU     | _          | <b>DO NOT USE:</b> This ball should not be connected to any power supplies, signals, or other balls. This ball can be left floating.                        |           |

| RFU    | _          | RESERVED for FUTURE USE: Reserved by Numonyx for future device functionality and enhancement. This ball must be left floating.                              |           |

#### Notes:

- Only used when AD-Mux I/O flash is present

- 2. P-CRE and P-Mode share the same package ball location. Only one signal function is available, depending on the stacked device combination.

- 3. Only available on stacked device combinations with PSRAM, and/or SRAM die. Otherwise, it should be treated as RFU.

#### **Maximum Ratings and Operating Conditions** 5.0

#### 5.1 **Device Absolute Maximum Ratings**

Warning: Stressing the device beyond the Absolute Maximum Ratings may cause permanent damage. These are stress ratings only.

Table 5: **Device Absolute Maximum Ratings**

| Parameter                                                                                                                                | Min  | Max   | Unit | Notes |

|------------------------------------------------------------------------------------------------------------------------------------------|------|-------|------|-------|

| Device Case Temperature Under Bias                                                                                                       | -25  | +85   | °C   |       |

| Storage Temperature                                                                                                                      | -55  | +125  | °C   |       |

| Voltage On Any Signal (Except for F-V <sub>CC</sub> , F-V <sub>PP</sub> , P-V <sub>CC</sub> , V <sub>CCQ</sub> , and S-V <sub>CC</sub> ) | -0.2 | +2.1  | V    | 1,3   |

| F-V <sub>CC</sub> Voltage                                                                                                                | -0.2 | +2.45 | V    | 1,2   |

| V <sub>CCQ</sub> , P-V <sub>CC</sub> , and Optional S-V <sub>CC</sub> Voltage                                                            | -0.2 | +2.45 | V    | 1,3   |

| F-V <sub>PP</sub> Voltage                                                                                                                | -0.2 | +13.1 | V    | 1,4   |

| I <sub>SH</sub> (Output Short Circuit Current)                                                                                           | _    | +50   | mA   | 5     |

### Notes:

- Voltage is referenced to  $V_{SS}$ . During power transitions, minimum DC voltage may undershoot to -2.0~V for periods <~20~ns; maximum DC voltage 2.

- 3.

- During power transitions, minimum DC voltage may undershoot to -2.0 V for periods < 20 ns; maximum DC voltage may overshoot to  $V_{CC}$  (operating max) + 2.0 V for periods < 20 ns; During power transitions, minimum DC voltage may undershoot to -1.0 V for periods < 20 ns; maximum DC voltage may overshoot to  $V_{CCQ}$  (operating max) + 1.0 V for periods < 20 ns. During power transitions, minimum DC voltage may undershoot to -2.0 V for periods < 20 ns; maximum DC voltage may overshoot to  $V_{PPH}$  (operating max) + 2.0 V for periods < 20 ns. Output shorted for no more than one second. No more than one output shorted at a time. 4.

- 5. Output shorted for no more than one second. No more than one output shorted at a time.

# **5.2** Device Operating Conditions

**Warning:** Operation beyond the Operating Conditions is not recommended and extended

exposure may affect device reliability.

Table 6: Device Operating Conditions

| Symbol                                                   | Parameter                                                            | Test               | Flash + | Unit  |        |

|----------------------------------------------------------|----------------------------------------------------------------------|--------------------|---------|-------|--------|

| Symbol                                                   | Parameter                                                            | Condition          | Min     | Max   | Oilit  |

| τ <sub>c</sub>                                           | Device Case Operating Temperature                                    | _                  | -25     | +85   | °C     |

| F-V <sub>CC</sub>                                        | V <sub>CC</sub> Flash Supply Voltage —                               |                    | +1.7    | +1.95 | V      |

| V <sub>CCQ</sub> , P-V <sub>CC</sub> , S-V <sub>CC</sub> | Flash and PSRAM I/O Voltage<br>PSRAM and SRAM Supply Voltage         | _                  | +1.7    | +1.95 | V      |

| V <sub>PPL</sub>                                         | F-V <sub>PP</sub> (Flash Programming Voltage Supply,<br>Logic Level) | _                  | -0.9    | +1.95 | V      |

| V <sub>PPH</sub>                                         | F-V <sub>PP</sub> (Flash Factory Word Programming<br>Voltage Supply) | _                  | +11.4   | +12.6 | V      |

| Block Erase Cycles                                       | Flash Main Array and FFA Blocks                                      | $V_{PP} = V_{CC}$  | 100,000 | Ī     | Cycles |

| Diock Liuse Cycles                                       | Flash Main Array and EFA Blocks                                      | $V_{PP} = V_{PPH}$ | _       | 1000  | Cycles |

**Note:** In typical operation, the F-VPP program voltage is  $V_{PPL}$ . F-VPP can be connected to 11.4 V - 12.6 V for a maximum of 80 cumulative hours or 1000 cycles on the main array blocks.

# **6.0** Device Electrical Specifications

The DC current and voltage characteristics referenced in this document are for individual memory die types within the SCSP device. The total current for each parameter is determined by sum of the current for each memory die type specification within the SCSP device.

NOTICE: Individual DC Characteristics of all dies in a SCSP device must be considered accordingly, depending on the SCSP device stacked combinations and operations.

# 6.1 Flash DC Characteristics

Refer to the  $Intel^{\circledR}$  Wireless Flash Memory (W18) Datasheet (order number: Non-Mux I/O doc #290701 and ADMux I/O doc #313272) for flash DC characteristics.

# **6.2** Synchronous PSRAM DC Characteristics

Synchronous PSRAM DC characteristics are shown in Table 7 and Table 8.

Table 7: PSRAM DC Characteristics (Sheet 1 of 2)

| Parameter        | Description              | Test<br>Conditions | Density | Min                    | Тур | Max             | Unit | Notes |

|------------------|--------------------------|--------------------|---------|------------------------|-----|-----------------|------|-------|

| V <sub>CC</sub>  | Supply Voltage range     | _                  | •       | 1.7                    | 1.8 | 1.95            | V    |       |

| V <sub>CCQ</sub> | I/O Supply Voltage range | _                  |         | 1.7                    | 1.8 | 1.95            | V    | 1     |

| V <sub>IH</sub>  | Input High Voltage       | _                  |         | V <sub>CCQ</sub> - 0.4 | _   | $V_{CCQ} + 0.2$ | V    |       |

Table 7: PSRAM DC Characteristics (Sheet 2 of 2)

| V <sub>IL</sub>   | Input Low Voltage                             | _                                       |                                      | -0.2                                 | _                                    | 0.4                                  | V                                    |                                                                                               |   |   |    |      |  |

|-------------------|-----------------------------------------------|-----------------------------------------|--------------------------------------|--------------------------------------|--------------------------------------|--------------------------------------|--------------------------------------|-----------------------------------------------------------------------------------------------|---|---|----|------|--|

| V <sub>OH</sub>   | Output High Voltage                           | I <sub>OH</sub> = -0.2 mA               |                                      | 0.8 x V <sub>CCQ</sub>               | _                                    | _                                    | V                                    |                                                                                               |   |   |    |      |  |

| V <sub>OL</sub>   | Output Low Voltage                            | I <sub>OL</sub> = 0.2                   | mA                                   | _                                    | _                                    | 0.2 x V <sub>CCQ</sub>               | V                                    |                                                                                               |   |   |    |      |  |

| I <sub>IL</sub>   | Input Leakage Current                         | _                                       |                                      | _                                    | _                                    | 1                                    | μΑ                                   |                                                                                               |   |   |    |      |  |

| I <sub>OL</sub>   | Output Leakage Current                        | _                                       |                                      | _                                    | _                                    | 1                                    | μΑ                                   |                                                                                               |   |   |    |      |  |

| I                 | Async Random Read/Write @ T <sub>RC</sub> Min | $V_{IN} = V_{CC}$ or                    | 16Mb                                 | _                                    | _                                    | 20                                   | mA                                   |                                                                                               |   |   |    |      |  |

| I <sub>CC1</sub>  | Asylic Ralidolli Read/Wille @ TRCMIII         | $V_{SS}$ ; $I_{OUT} = 0$                | 32Mb                                 | _                                    | _                                    | 20                                   | IIIA                                 |                                                                                               |   |   |    |      |  |

| T                 | Async Page Read                               | $V_{IN} = V_{CC}$ or                    | 16Mb                                 | _                                    | _                                    | 15                                   | mA                                   |                                                                                               |   |   |    |      |  |

| I <sub>CC1P</sub> | Asylic Page Read                              | $V_{SS}$ ; $I_{OUT} = 0$                | $V_{SS}$ ; $I_{OUT} = 0$ 32Mb        | _                                    | _                                    | 15                                   | IIIA                                 |                                                                                               |   |   |    |      |  |

| т                 | Synchronous Burst Read (continuous)           | $V_{IN} = V_{CC}$ or                    | 16Mb                                 | _                                    | _                                    | 25                                   | mA                                   |                                                                                               |   |   |    |      |  |

| I <sub>CC4R</sub> | Sylicinollous Burst Read (continuous)         | $V_{SS}$ ; $I_{OUT} = 0$                | 32Mb                                 | _                                    | _                                    | 25                                   | IIIA                                 |                                                                                               |   |   |    |      |  |

| т                 | Synchronous Burst Write (continuous)          | $V_{IN} = V_{CC}$ or                    | 16Mb                                 | _                                    | _                                    | 25                                   | mA                                   |                                                                                               |   |   |    |      |  |

| I <sub>CC4W</sub> | Synchronous Burst Write (continuous)          | Syliciliolous Burst Write (continuous)  | Synchronous Burst Write (continuous) | Synchronous Burst write (continuous) | Synchronous Burst Write (continuous) | Synchronous Burst Write (continuous) | Synchronous Burst Write (continuous) | Synchronous Burst Write (continuous) $V_{SS}^{IN - V_{CC} OI}$ $V_{SS}^{IOUT} = 0$ $32Mb$ $-$ | _ | _ | 35 | IIIA |  |

| т                 | Burst Initial Access                          | $V_{IN} = V_{CC}$ or                    | 16Mb                                 | _                                    | _                                    | 30                                   | mA                                   |                                                                                               |   |   |    |      |  |

| I <sub>CC5</sub>  | V <sub>SS</sub> ; I <sub>0</sub>              | $V_{SS}$ ; $I_{OUT} = 0$                | 32Mb                                 | _                                    | _                                    | 35                                   | IIIA                                 |                                                                                               |   |   |    |      |  |

| т                 | Standby Current                               | $V_{IN} = V_{CC}$ or                    | 16Mb                                 | _                                    | _                                    | 80                                   | ^                                    |                                                                                               |   |   |    |      |  |

| I <sub>CC2</sub>  | (Full Array Refresh)                          | V <sub>SS</sub> ; P-CS# =<br>Deselected | 32Mb                                 | _                                    | _                                    | 110                                  | μΑ                                   |                                                                                               |   |   |    |      |  |

|                   | V <sub>IN</sub> =                             | $V_{IN} = V_{CC}$ or                    | 16Mb                                 | _                                    | _                                    | 70                                   | ^                                    |                                                                                               |   |   |    |      |  |

| I <sub>CC3</sub>  | Deep Power-Down                               | V <sub>SS</sub> ; P-CS# =<br>Deselected | 32Mb                                 | _                                    | _                                    | 70                                   | μА                                   |                                                                                               |   |   |    |      |  |

Note: To avoid unnecessary current flow, VCCQ is not allowed to be outside of P-V<sub>CC</sub> ± 0.2 V except during power-up situation.

Table 8: PSRAM Partial-Array Self-Refresh (Typical) Current

| Donaitus | _            |       | Typical Standby Current (μA) |       |       |  |  |  |