# Features

- 64-Mbit Flash and 16-Mbit PSRAM

- Single 66-ball (8 mm x 10 mm x 1.2 mm) CBGA Package

- 2.7V to 3.1V Operating Voltage

# Flash

- Single Voltage Read/Write Operation: 2.65V to 3.6V

- Access Time 70 ns

- Sector Erase Architecture

- One Hundred Twenty-seven 32K Word Sectors with Individual Write Lockout

- Eight 4K Word Sectors with Individual Write Lockout

- Fast Word Program Time 10 μs

- Typical Sector Erase Time: 32K Word Sectors 700 ms; 4K Word Sectors 100 ms

- Suspend/Resume Feature for Erase and Program

- Supports Reading and Programming Data from Any Sector by Suspending Erase of a Different Sector

- Supports Reading Any Word by Suspending Programming of Any Other Word

- Low-power Operation

- 10 mA Active

- 15 µA Standby

- VPP Pin for Write Protection and Accelerated Program Operation

- WP Pin for Sector Protection

- RESET Input for Device Initialization

- Flexibel Sector Protection

- Top or Bottom Boot Block Configuration Available

- 128-bit Protection Register

- Minimum 100,000 Erase Cycles

- Common Flash Interface (CFI)

## **PSRAM**

- 16-megabit (1M x 16)

- 2.7V to 3.1V V<sub>cc</sub>

- 70 ns Access Time

| Device Number | Flash Boot<br>Location | Flash Plane<br>Configuration | PSRAM<br>Configuration |  |  |

|---------------|------------------------|------------------------------|------------------------|--|--|

| AT52BC6402D   | Bottom                 | 64M (4M x 16)                | 16M (1M x 16)          |  |  |

| AT52BC6402DT  | Тор                    | 64M (4M x 16)                | 16M (1M x 16)          |  |  |

# Flash & PSRAM Datasheets

| Datasheets                      | PDF File         |

|---------------------------------|------------------|

| 64M Flash Memory: AT49BV640D(T) | Acrobal Document |

| 16M PSRAM: 2FHY64UD16161B       | Acobal Document  |

64-megabit Flash + 16-megabit PSRAM Stack Memory

# AT52BC6402D AT52BC6402DT

# Preliminary

# 1. Pin Configuration

| Pin Name      | Function                                                      |

|---------------|---------------------------------------------------------------|

| A0 - A19, A21 | Common Address Input for 16M PSRAM/Flash, Flash Address Input |

| CE            | Flash Chip Enable                                             |

| ŌĒ            | Flash Output Enable                                           |

| WE            | Flash Write Enable                                            |

| RESET         | Flash Reset                                                   |

| PW            | Flash Write Protect                                           |

| VPP           | Flash Power Supply for Accelerated Program Operation          |

| VCC           | Flash Power                                                   |

| GND           | Flash Ground                                                  |

| I/O0 - I/O15  | Data Inputs/Outputs                                           |

| NC            | No Connect                                                    |

| LB            | PSRAM Lower Byte                                              |

| UB            | PSRAM Upper Byte                                              |

| PVCC          | PSRAM Power                                                   |

| PGND          | PSRAM Ground                                                  |

| PCS1          | PSRAM Chip Select 1                                           |

| PCS2          | Low Power Modes                                               |

| PWE           | PSRAM Write Enable                                            |

| POE           | PSRAM Output Enable                                           |

# 2. AT52BC6402D(T) (Top View)

|   | 1          | 2          | 3             | 4          | 5          | 6          | 7          | 8          | 9          | 10               | 11         | 12         |  |

|---|------------|------------|---------------|------------|------------|------------|------------|------------|------------|------------------|------------|------------|--|

|   | •          |            |               |            |            |            |            |            |            |                  |            |            |  |

| Α | $\bigcirc$ | $\bigcirc$ | $\bigcirc$    | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ | $\bigcirc$       | $\bigcirc$ | $\bigcirc$ |  |

| в | NC         | NC         | A20           | A11        | A15<br>()  | A14        | A13        | A12        | GND        | NC<br>()         | NC         | NC         |  |

| с |            |            | A16           | A8         | A10        | A9         | I∕O15<br>⊖ | PWE        | I∕014<br>⊖ | <b>1∕07</b><br>◯ |            |            |  |

| D |            |            | WE<br>()      | $\bigcirc$ | A21        |            | I∕O13<br>⊖ | I/O6<br>◯  | I∕O4<br>⊖  | I∕O5<br>⊖        |            |            |  |

| Е |            |            | PGND          | RESET      | $\odot$    | $\bigcirc$ | I/O12      | PCS2       |            | <b>vcc</b>       |            |            |  |

| F |            |            | WP<br>()      | VPP        | A19        | I/O11      | $\bigcirc$ | I∕O10<br>⊖ | I∕O2<br>⊖  | ₩03<br>()        |            |            |  |

| Ġ |            |            | Ŭ<br>ÎB<br>() | ŬB<br>()   | POE        | $\odot$    | I∕O9<br>⊖  | I∕O8<br>⊖  | I∕O0<br>⊖  | l∕01<br>⊖        |            |            |  |

|   | 0          | ~          | A18           | A17        | A7         | A6         | A3         | A2         | A1         | PCS1             | ~          | ~          |  |

| Н | ⊖<br>NC    | ()<br>NC   | ()<br>NC      | ()<br>A5   | ()<br>A4   | ()<br>A0   | )<br>CE    | )<br>GND   | ()<br>De   | ()<br>NC         | ⊖<br>NC    | ()<br>NC   |  |

# <sup>2</sup> AT52BC6402D(T) Preliminary

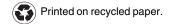

## 3. Block Diagram

## 4. Description

The AT52BC6402D(T) combines a 64-megabit Flash (4M x 16) and an 16-megabit PSRAM (organized as  $1M \times 16$ ) in a stacked 66-ball CBGA package. The stacked modules operate at 2.7V to 3.1V in the extended temperature range.

## 5. Absolute Maximum Ratings

| Temperature under Bias55° C to +85° C                                                               |

|-----------------------------------------------------------------------------------------------------|

| Storage Temperature                                                                                 |

| All Input Voltages except $V_{PP}$ (including NC Pins) with Respect to Ground0.2V to $V_{CC}$ +0.3V |

| Voltage on V <sub>PP</sub><br>with Respect to Ground0.2V to + 10.0V                                 |

| All Output Voltages with Respect to Ground0.2V to $V_{CC}$ +0.3V                                    |

\*NOTICE: Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

# 6. DC and AC Operating Range

|                              | AT52BC6402D(T)-70CU |

|------------------------------|---------------------|

| Operating Temperature (Case) | -30° C - 85° C      |

| V <sub>CC</sub> Power Supply | 2.7V to 3.1V        |

# 7. Flash Operating Modes

| Mode                               | CE              | ŌĒ               | WE              | RESET           | <b>V</b> <sub>PP</sub> <sup>(2)</sup> | Ai                                                | I/O                  | PSRAM<br>Operation      |  |

|------------------------------------|-----------------|------------------|-----------------|-----------------|---------------------------------------|---------------------------------------------------|----------------------|-------------------------|--|

| Read                               | V <sub>IL</sub> | V <sub>IL</sub>  | $V_{\rm IH}$    | V <sub>IH</sub> | х                                     | Ai                                                | D <sub>OUT</sub>     |                         |  |

| Program/Erase                      | V <sub>IL</sub> | $V_{\text{IH}}$  | V <sub>IL</sub> | V <sub>IH</sub> | V <sub>IHPP</sub> <sup>(3)</sup>      | Ai                                                | D <sub>IN</sub>      |                         |  |

| Drogrom Inhihit                    | V <sub>IL</sub> | Х                | V <sub>IH</sub> | V <sub>IH</sub> | х                                     |                                                   |                      | PSRAM                   |  |

| Program Inhibit                    | V <sub>IL</sub> | Х                | Х               | х               | V <sub>ILPP</sub> <sup>(4)</sup>      |                                                   |                      | Must Be<br>High-Z       |  |

| Software Product<br>Identification | V <sub>IL</sub> | V <sub>IL</sub>  | V <sub>IH</sub> | VIH             | х                                     | $A0 = V_{IL}, A1 - A19 = V_{IL}$                  | Manufacturer<br>Code | Figh-2                  |  |

| Identification                     |                 |                  |                 |                 |                                       | A0 = V <sub>IH</sub> , A1 - A19 = V <sub>IL</sub> | Device Code          |                         |  |

| Standby/Program<br>Inhibit         | V <sub>IH</sub> | X <sup>(1)</sup> | х               | V <sub>IH</sub> | х                                     | x                                                 | High Z               | Any PSRAM               |  |

| Output Disable                     | Х               | V <sub>IH</sub>  | Х               | V <sub>IH</sub> | Х                                     |                                                   | High Z               | Operation is<br>Allowed |  |

| Reset                              | Х               | Х                | Х               | V <sub>IL</sub> | Х                                     | Х                                                 | High Z               |                         |  |

Notes: 1. X can be  $V_{IL}$  or  $V_{IH}$

- 2. The VPP pin can be tied to  $V_{CC}.$  For faster program operations,  $V_{PP}$  can be set to 9.5V  $\pm$  0.5V.

- 3. V<sub>IHPP</sub> (min) = 1.65V

4.  $V_{ILPP}$  (max) = 0.4V

# 8. Functional Description

| PCS1             | PCS2 | POE              | PWE              | LB               | UB               | I/O0 - 7         | I/O8 - 15        | Mode                | Power              | Flash<br>Operation      |  |

|------------------|------|------------------|------------------|------------------|------------------|------------------|------------------|---------------------|--------------------|-------------------------|--|

| Н                | Н    | X <sup>(1)</sup> | X <sup>(1)</sup> | X <sup>(1)</sup> | X <sup>(1)</sup> | High-Z           | High-Z           | Deselected          | Standby            | Any Flash               |  |

| X <sup>(1)</sup> | L    | X <sup>(1)</sup> | X <sup>(1)</sup> | X <sup>(1)</sup> | X <sup>(1)</sup> | High-Z           | High-Z           | Deselected          | Low-power<br>Modes | Operation<br>Allowed    |  |

| L <sup>(1)</sup> | Н    | X <sup>(1)</sup> | X <sup>(1)</sup> | Н                | Н                | High-Z           | High-Z           | Output Disabled     | Active             |                         |  |

|                  | Н    | Н                | Н                | L                | X <sup>(1)</sup> | High-Z           | High-Z           | Output Disabled     | Active             |                         |  |

| L                | Н    | Н                | Н                | X <sup>(1)</sup> | L                | High-Z           | High-Z           | Output Disabled     | Active             |                         |  |

|                  |      |                  |                  | L                | Н                | D <sub>OUT</sub> | High-Z           | Lower Byte<br>Read  | Active             |                         |  |

|                  |      | L                | Н                | Н                | L                | High-Z           | D <sub>OUT</sub> | Upper Byte<br>Read  | Active             | Flash Must<br>Be High Z |  |

|                  |      |                  |                  | L                | L                | D <sub>OUT</sub> | D <sub>OUT</sub> | Word Read           | Active             | Dorngriz                |  |

| L                | Н    |                  |                  | L                | Н                | D <sub>IN</sub>  | High-Z           | Lower Byte<br>Write | Active             |                         |  |

|                  |      | X <sup>(1)</sup> | L                | Н                | L                | High-Z           | D <sub>IN</sub>  | Upper Byte<br>Write | Active             |                         |  |

|                  |      |                  |                  | L                | L                | D <sub>IN</sub>  | D <sub>IN</sub>  | Word Write          | Active             |                         |  |

Note: 1. X means don't care (must be low or high state).

# 4 AT52BC6402D(T) Preliminary

# AT52BC6402D(T) Preliminary

# 9. Ordering Information

## 9.1 Green Package (Pb/Halide-free)

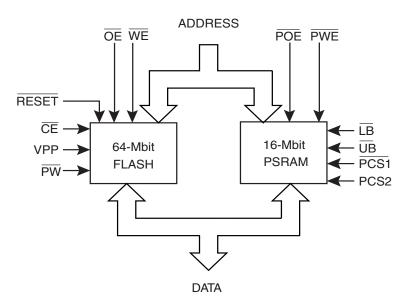

| t <sub>ACC</sub> (ns) | Ordering Code     | Flash Boot<br>Block | Flash Plane Architecture | PSRAM   | Package | Operation Range |

|-----------------------|-------------------|---------------------|--------------------------|---------|---------|-----------------|

| 70                    | AT52BC6402D-70CU  | Bottom              | 64M – Single Bank        | 1M x 16 | 66C7    | Extended        |

| 70                    | AT52BC6402DT-70CU | Тор                 | 64M – Single Bank        |         | 0007    | (-30° to 85°C)  |

|      | Package Type                                              |

|------|-----------------------------------------------------------|

| 66C7 | 66-ball, Plastic Chip-size Ball Grid Array Package (CBGA) |

## 10. Packaging Information

### 10.1 66C7 - CBGA

# 6 AT52BC6402D(T) Preliminary

# 11. Revision History

| Revision No.           | History         |

|------------------------|-----------------|

| Revision A – July 2006 | Initial Release |

### **Atmel Corporation**

2325 Orchard Parkway San Jose, CA 95131, USA Tel: 1(408) 441-0311 Fax: 1(408) 487-2600

### **Regional Headquarters**

#### Europe

Atmel Sarl Route des Arsenaux 41 Case Postale 80 CH-1705 Fribourg Switzerland Tel: (41) 26-426-5555 Fax: (41) 26-426-5500

### Asia

Room 1219 Chinachem Golden Plaza 77 Mody Road Tsimshatsui East Kowloon Hong Kong Tel: (852) 2721-9778 Fax: (852) 2722-1369

#### Japan

9F, Tonetsu Shinkawa Bldg. 1-24-8 Shinkawa Chuo-ku, Tokyo 104-0033 Japan Tel: (81) 3-3523-3551 Fax: (81) 3-3523-7581

### **Atmel Operations**

Memory 2325 Orchard Parkway San Jose, CA 95131, USA Tel: 1(408) 441-0311 Fax: 1(408) 436-4314

#### Microcontrollers

2325 Orchard Parkway San Jose, CA 95131, USA Tel: 1(408) 441-0311 Fax: 1(408) 436-4314

La Chantrerie BP 70602 44306 Nantes Cedex 3, France Tel: (33) 2-40-18-18-18 Fax: (33) 2-40-18-19-60

#### ASIC/ASSP/Smart Cards

Zone Industrielle 13106 Rousset Cedex, France Tel: (33) 4-42-53-60-00 Fax: (33) 4-42-53-60-01

1150 East Cheyenne Mtn. Blvd. Colorado Springs, CO 80906, USA Tel: 1(719) 576-3300 Fax: 1(719) 540-1759

Scottish Enterprise Technology Park Maxwell Building East Kilbride G75 0QR, Scotland Tel: (44) 1355-803-000 Fax: (44) 1355-242-743

#### **RF**/Automotive

Theresienstrasse 2 Postfach 3535 74025 Heilbronn, Germany Tel: (49) 71-31-67-0 Fax: (49) 71-31-67-2340

1150 East Cheyenne Mtn. Blvd. Colorado Springs, CO 80906, USA Tel: 1(719) 576-3300 Fax: 1(719) 540-1759

### Biometrics/Imaging/Hi-Rel MPU/

High Speed Converters/RF Datacom Avenue de Rochepleine BP 123 38521 Saint-Egreve Cedex, France Tel: (33) 4-76-58-30-00 Fax: (33) 4-76-58-34-80

*Literature Requests* www.atmel.com/literature

Disclaimer: The information in this document is provided in connection with Atmel products. No license, express or implied, by estoppel or otherwise, to any intellectual property right is granted by this document or in connection with the sale of Atmel products. EXCEPT AS SET FORTH IN ATMEL'S TERMS AND CONDI-TIONS OF SALE LOCATED ON ATMEL'S WEB SITE, ATMEL ASSUMES NO LIABILITY WHATSOEVER AND DISCLAIMS ANY EXPRESS, IMPLIED OR STATUTORY WARRANTY RELATING TO ITS PRODUCTS INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTY OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT. IN NO EVENT SHALL ATMEL BE LIABLE FOR ANY DIRECT, INDIRECT, CONSEQUENTIAL, PUNITVE, SPECIAL OR INCIDEN-TAL DAMAGES (INCLUDING, WITHOUT LIMITATION, DAMAGES FOR LOSS OF PROFITS, BUSINESS INTERRUPTION, OR LOSS OF INFORMATION) ARISING OUT OF THE USE OR INABILITY TO USE THIS DOCUMENT, EVEN IF ATMEL HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES. Atmel makes no representations or warranties with respect to the accuracy or completeness of the contents of this document and reserves the right to make changes to specifications and product descriptions at any time without notice. Atmel does not make any commitment to update the information contained herein. Unless specifically provided otherwise, Atmel products are not suitable for, and shall not be used in, automotive applications. Atmel's products are not intended, or warranted for use as components in applications intended to support or sustain life.

© 2006 Atmel Corporation. All rights reserved. Atmel<sup>®</sup>, logo and combinations thereof, Everywhere You Are<sup>®</sup> and others are registered trademarks or trademarks of Atmel Corporation or its subsidiaries. Other terms and product names may be trademarks of others.