### **PRODUCT INFORMATION**

# SHARP

## LRS13012 Stacked Chip

#### **FEATURES**

- 4M Flash and 1M SRAM

- Flash memory access time 150 ns MAX.

- SRAM access time 70 ns MAX.

- Operating current

- Flash memory read 12 mA MAX. ( $t_{CYCLE} = 200 \text{ ns}$ )

- Flash byte write 40 mA MAX.

- Flash block erase 37 mA MAX.

- SRAM operating 25 mA MAX. ( $t_{CYCLE} = 200 \text{ ns}$ )

- Standby current

- $\begin{array}{ll} & \mbox{Flash memory 20 } \mu\mbox{A MAX}. \\ & (\mbox{F-}\overline{\mbox{CE}} \geq \mbox{V}_{\mbox{CC}} 0.2 \mbox{ V}, \mbox{\overline{\mbox{RP}}} \leq 0.2 \mbox{ V}) \end{array}$

- $\begin{array}{l} & \mbox{SRAM 30 } \mbox{$\mu$A MAX. (S-\overline{\mbox{CE}} \geq V_{cc} 0.2 $V$)} \\ & \mbox{$0.3 $ $\mu$A TYP. (T_A = 25 °C, $V_{CC} = 3 $V$, $S-\overline{\mbox{CE}} \geq V_{CC} 0.2 $V$)} \end{array}$

- Total standby current is the summation of flash memory's standby current and SRAM's standby current

- Power supply 2.7 V to 3.6 V. (Block erase, byte write and lock-bit configuration operations with  $V_{CC} < 3.0$  V are not supported)

- SRAM data retention current 1  $\mu$ A MAX. (V<sub>CCDR</sub> = 3 V, T<sub>A</sub>, = 25°C)

- Operating temperature -40°C to +85°C

- Fully static operation

- Three-state output

- Not designed or rated as radiation hardened

- 40-pin TSOP (TSOP40-P-0813) plastic package

- Flash Memory has P-type bulk silicon, and SRAM has N-type bulk silicon

#### DESCRIPTION

The LRS13012 is a combination memory organization as  $524,288 \times 8$  bit flash memory and  $131,072 \times 8$  bit static RAM in one package. It is fabricated using silicon-gate CMOS process technology.

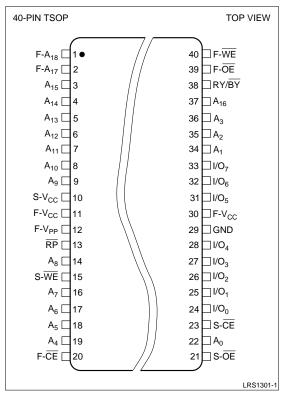

#### **40-PIN TSOP PINOUT**

**APPLICATIONS:**

Pager PDA Set Top Box

**Cellular Phone**

#### **PIN DESCRIPTION**

| PIN                                    | DESCRIPTION                                      |

|----------------------------------------|--------------------------------------------------|

| A <sub>0</sub> to A <sub>16</sub>      | Common Address Input Pins                        |

| F-A <sub>17</sub> to F-A <sub>18</sub> | Address Input Pins for Flash Memory              |

| F-TE                                   | Chip Enable Input Pin for Flash Memory           |

| S-TE                                   | Chip Enable Input Pin for SRAM                   |

| F-WE                                   | Write Enable Input Pin for Flash Memory          |

| S-WE                                   | Write Enable Input Pin for SRAM                  |

| F-OE                                   | Output Enable Input Pin for Flash Memory         |

| S-OE                                   | Output Enable Input Pin for SRAM                 |

| I/0 <sub>0</sub> to I/0 <sub>7</sub>   | Common Data Input/Output Pins                    |

| RP                                     | Reset/Deep Power Down Input Pin for Flash Memory |

| RY/BY                                  | Ready/Busy Output Pin for Flash Memory           |

| F-V <sub>CC</sub>                      | Power Supply Pin for Flash Memory                |

| F-V <sub>PP</sub>                      | Power Supply for Flash Memory Write/Erase        |

| S-V <sub>CC</sub>                      | Power Supply Pin for SRAM                        |

| GND                                    | Common GND                                       |

The information for this document is from Specification No. EL103011, issued on March 3, 1998.

Copyright ©1998, Sharp Electronics Corp. All rights reserved. All tradenames are the registered property of their respective owners. Specifications are subject to change without notice.