### LM1237

# 150 MHz I<sup>2</sup>C Compatible RGB Preamplifier with Internal 254 Character OSD and 4 DACs

### **General Description**

The LM1237 pre-amp is an integrated CMOS CRT preamp. It has an I<sup>2</sup>C compatible interface which allows control of all the parameters necessary to directly setup and adjust the gain and contrast in the CRT display. Brightness and bias can be controlled through the DAC outputs which are well matched to the LM2479 and LM2480 integrated bias clamp ICs. The LM1237 preamp is also designed to be compatible with the LM246x high gain driver family.

Black level clamping of the video signal is carried out directly on the AC coupled input signal into the high impedance preamplifier input, thus eliminating the need for additional clamp capacitors. Horizontal and vertical blanking of the outputs is provided. Vertical blanking is optional and its duration is register programmable.

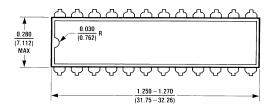

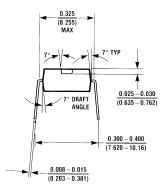

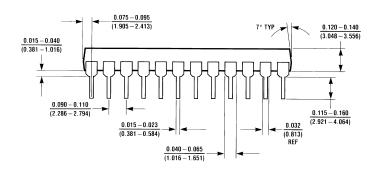

The IC is packaged in an industry standard 24 lead DIP molded plastic package.

### **Features**

■ I<sup>2</sup>C compatible microcontroller interface

- Internal 254 character OSD usable as either (a) 190

2-color plus 64 4-color characters, (b) 318 2-color characters, or (c) some combination in between.

- OSD override allows OSD messages to override video and the use of burn-in screens with no video input

- 4 DAC outputs (8-bit resolution) for bus controlled CRT bias and brightness

- Spot killer which blanks the video outputs when V<sub>CC</sub> falls below the specified threshold

- Suitable for use with discrete or integrated clamp, with software configurable brightness mixer

- H and V blanking (V blanking is optional and has register programmable width)

- Power Saving Mode with 80% power reduction

- Matched to LM246x driver and LM2479/80 drivers

### **Applications**

- Low end 15" and 17" bus controlled monitors with OSD

- 1024x768 displays up to 85 Hz requiring OSD capability

- Very low cost systems with LM246x driver

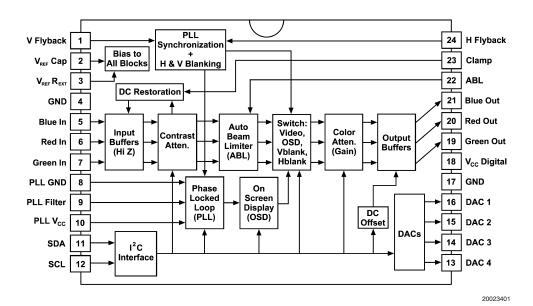

### **Block and Connection Diagram**

FIGURE 1. Order Number LM1237BAAF/NA See NS Package Number N24D

### **Absolute Maximum Ratings** (Notes 1, 3)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

Junction Temperature (T<sub>J</sub>) Supply Voltage, Pins 15 and 19 6.0V 150°C Peak Video DC Output Source Current ESD Susceptibility (Note 4) 3.5 kV (Any One Amp) Pins 18, 19 or 20 1.5 mA ESD Machine Model (Note 13) 350V Voltage at Any  $V_{CC} + 0.5 > V_{IN} > -0.5V$ Storage Temperature -65°C to +150°C Input Pin (V<sub>IN</sub>) Lead Temperature (Soldering, 10 sec.) 265°C

Video Inputs (pk-pk)  $0.0 < V_{\rm IN} < 1.2V$

Thermal Resistance to Ambient ( $\theta_{JA}$ ) 51°C/W

Power Dissipation (P<sub>D</sub>)

(Above 25°C Derate Based

on  $\theta_{JA}$  and  $T_{J}$ )

Thermal Resistance to case  $(\theta_{JC})$

**Operating Ratings** (Note 2)

Temperature Range  $0^{\circ}\text{C to } +70^{\circ}\text{C}$  Supply Voltage  $V_{\text{CC}}$   $4.75\text{V} < V_{\text{CC}} < 5.25\text{V}$  Video Inputs (pk-pk)  $0.0\text{V} < V_{\text{IN}} < 1.0\text{V}$

### **Video Signal Electrical Characteristics**

Unless otherwise noted:  $T_A = 25^{\circ}C$ ,  $V_{CC} = +5.0V$ ,  $V_{IN} = 0.70~V_{P-P}$ ,  $V_{ABL} = V_{CC}$ ,  $C_L = 8~pF$ , Video Outputs = 2.0  $V_{P-P}$ . Setting numbers refer to the definitions in Table 1. See Note 7 for Min and Max parameters and Note 6 for Typicals.

2.4W

32°C/W

| Symbol                                | Parameter                                                                                     | Conditions                                                                       | Min | Тур  | Max | Units |

|---------------------------------------|-----------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|-----|------|-----|-------|

| I <sub>S</sub>                        | Supply Current                                                                                | Test Setting 1, both supplies, no output loading. See Note 8.                    |     | 170  | 245 | mA    |

| I <sub>S-PS</sub>                     | Supply Current, Power Save Mode Test Setting 1, both supplies, no output loading. See Note 8. |                                                                                  |     | 60   | 82  | mA    |

| V <sub>O BLK</sub>                    | Active Video Black Level Output<br>Voltage                                                    | Test Setting 4, no AC input signal, DC offset (register 0x8438 set to 0xd5).     |     | 1.2  |     | VDC   |

| V <sub>O BLK STEP</sub>               | Active Video Black Level Step Size                                                            | Test Setting 4, no AC input signal.                                              |     | 100  |     | mVDC  |

| V <sub>O</sub> Max                    | Maximum Video Output Voltage                                                                  | Test Setting 3, Video in = 0.70 V <sub>P-P</sub>                                 | 4.0 | 4.4  |     | V     |

| LE                                    | Linearity Error                                                                               | Test Setting 4, staircase input signal (see Note 9).                             |     | 5    |     | %     |

| t <sub>r</sub>                        | Video Rise Time                                                                               | Note 5, 10% to 90%, Test Setting 4, AC input signal.                             |     | 3.1  |     | ns    |

| OS <sub>R</sub>                       | Rising Edge Overshoot                                                                         | Note 5, Test Setting 4, AC input signal.                                         | 2   |      |     | %     |

| t <sub>f</sub>                        | Video Fall Time                                                                               | Note 5, 90% to 10%, Test Setting 4, AC input signal.                             |     | 2.9  |     | ns    |

| OS <sub>F</sub>                       | Falling Edge Overshoot                                                                        | Note 5, Test Setting 4, AC input signal.                                         | 2   |      |     | %     |

| BW                                    | Channel bandwidth (-3 dB)                                                                     | Note 5, Test Setting 4, AC input signal.                                         |     | 150  |     | MHz   |

| V <sub>SEP</sub> 10 kHz               | Video Amplifier 10 kHz Isolation                                                              | Note 14, Test Setting 8.                                                         |     | -60  |     | dB    |

| V <sub>SEP</sub> 10 MHz               | Video Amplifier 10 MHz Isolation                                                              | Note 14, Test Setting 8.                                                         |     | -50  |     | dB    |

| A <sub>V</sub> Max                    | Maximum Voltage Gain                                                                          | Test Setting 8, AC input signal.                                                 | 3.8 | 4.2  |     | V/V   |

| A <sub>V</sub> C-50%                  | Contrast Attenuation @ 50%                                                                    | Test Setting 5, AC input signal.                                                 |     | -5.2 |     | dB    |

| A <sub>V</sub> Min/A <sub>V</sub> Max | Maximum Contrast Attenuation in dB                                                            | Test Setting 2, AC input signal.                                                 |     | -20  |     | dB    |

| A <sub>V</sub> G-50%                  | Gain Attenuation @ 50%                                                                        | Test Setting 6, AC input signal.                                                 |     | -3.6 |     | dB    |

| A <sub>V</sub> G-Min                  | Maximum Gain Attenuation                                                                      | Test Setting 7, AC input signal.                                                 |     | -10  |     | dB    |

| A <sub>V</sub> Match                  | Maximum Gain Match between channels                                                           | Test Setting 3, AC input signal.                                                 |     | ±0.5 |     | dB    |

| A <sub>V</sub> Track                  | Gain Change between channels                                                                  | Tracking when changing from Test<br>Setting 8 to Test Setting 5. See<br>Note 11. |     | ±0.5 |     | dB    |

2

$\label{eq:Video Signal Electrical Characteristics} \mbox{(Continued)} \\ \mbox{Unless otherwise noted: $T_A = 25^{\circ}$C, $V_{CC} = +5.0$V, $V_{IN} = 0.70$ $V_{P-P}$, $V_{ABL} = V_{CC}$, $C_L = 8$ pF$, $V$ideo Outputs = 2.0 $V_{P-P}$. Setting numbers refer to the definitions in Table 1. See Note 7 for Min and Max parameters and Note 6 for Typicals.}$

| Symbol                                 | Parameter                           | Conditions                                   | Min | Тур | Max               | Units |

|----------------------------------------|-------------------------------------|----------------------------------------------|-----|-----|-------------------|-------|

| V <sub>ABL</sub> TH                    | ABL Control Range upper limit       | Note 12, Test Setting 4, AC input            |     | 4.8 |                   | V     |

|                                        |                                     | signal.                                      |     |     |                   |       |

| V <sub>ABL</sub> Range                 | ABL Gain Reduction Range            | Note 12, Test Setting 4, AC input            |     | 2.8 |                   | V     |

|                                        |                                     | signal.                                      |     |     |                   |       |

| A <sub>V 3.5</sub> /A <sub>V Max</sub> | ABL Gain Reduction at 3.5V          | Note 12, Test Setting 4, AC input            |     | -3  |                   | dB    |

|                                        |                                     | signal. V <sub>ABL</sub> = 3.5V              |     | _3  |                   | l ap  |

| A <sub>V 2.0</sub> /A <sub>V Max</sub> | ABL Gain Reduction at 2.0V          | Note 12, Test Setting 4, AC input            |     | -11 |                   | dB    |

|                                        |                                     | signal. V <sub>ABL</sub> = 2.0V              |     | -11 |                   | UD UD |

| I <sub>ABL</sub> Active                | ABL Input bias current during ABL   | Note 12, Test Setting 4, AC input            |     |     | 10                | μA    |

|                                        |                                     | signal. $V_{ABL} = V_{ABL}$ MIN GAIN         |     |     | 10                | μΑ    |

| I <sub>ABL</sub> Max                   | ABL input current sink capability   | Note 12, Test Setting 4, AC input            |     |     | 1.0               | mA    |

|                                        |                                     | signal.                                      |     |     |                   |       |

| V <sub>ABL</sub> Max                   | Maximum ABL Input voltage during    | Note 12, Test Setting 4, AC input            |     |     | V <sub>CC</sub> + | V     |

|                                        | clamping                            | signal. $I_{ABL} = I_{ABL} MAX$              |     |     | 0.1               | _ v   |

| A <sub>V</sub> ABL Track               | ABL Gain Tracking Error             | Note 9, Test Setting 4, 0.7 V <sub>P-P</sub> |     |     |                   |       |

|                                        |                                     | input signal, ABL voltage set to             |     |     | 4.5               | %     |

|                                        |                                     | 4.5V and 2.5V.                               |     |     |                   |       |

| R <sub>IP</sub>                        | Minimum Input resistance pins 5, 6, | Test Setting 4.                              |     | 20  |                   | ΜΩ    |

|                                        | 7.                                  |                                              |     | 20  |                   | IVISZ |

### **OSD Electrical Characteristics**

Unless otherwise noted:  $T_A = 25$ °C,  $V_{CC} = +5.0$ V. See Note 7 for Min and Max parameters and Note 6 for Typicals.

| Symbol                       | Symbol Parameter Conditions       |                                    | Min | Тур | Max | Units |

|------------------------------|-----------------------------------|------------------------------------|-----|-----|-----|-------|

| V <sub>OSDHIGH</sub> max     | Maximum OSD Level with OSD        | Palette Set at 111, OSD Contrast = |     | 3.8 |     | V     |

|                              | Contrast 11                       | 11, Test Setting 3                 |     | 3.6 |     | v     |

| V <sub>OSDHIGH</sub> 10      | Maximum OSD Level with OSD        | Palette Set at 111, OSD Contrast = |     | 3.1 |     | V     |

|                              | Contrast 10                       | 10, Test Setting 3                 |     | 3.1 |     | , v   |

| V <sub>OSDHIGH</sub> 01      | Maximum OSD Level with OSD        | Palette Set at 111, OSD Contrast = |     | 0.4 |     | V     |

|                              | Contrast 01                       | 01, Test Setting 3                 |     | 2.4 |     | \ \   |

| V <sub>OSDHIGH</sub> 00      | Maximum OSD Level with OSD        | Palette Set at 111, OSD Contrast = |     | 1.7 |     | V     |

|                              | Contrast 00                       | 00, Test Setting 3                 |     | 1.7 |     | , v   |

| ΔV <sub>OSD</sub> (Black)    | Difference between OSD Black      | Register 08=0x18, Input Video =    |     |     |     |       |

|                              | Level and Video Black Level (same | Black, Same Channel, Test Setting  |     | 20  |     | mV    |

|                              | channel)                          | 8                                  |     |     |     |       |

| ΔV <sub>OSD</sub> (White)    | Output Match between Channels     | Palette Set at 111, OSD Contrast = |     |     |     |       |

|                              |                                   | 11, Maximum difference between R,  |     | 3   |     | %     |

|                              |                                   | G and B                            |     |     |     |       |

| V <sub>OSD-out</sub> (Track) | Output Variation between Channels | OSD contrast varied from max to    | ·   | 3   |     | %     |

|                              |                                   | min                                |     | 3   |     | /0    |

### **DAC Output Electrical Characteristics**

Unless otherwise noted:  $T_A = 25^{\circ}C$ ,  $V_{CC} = +5.0V$ ,  $V_{IN} = 0.7V$ ,  $V_{ABL} = V_{CC}$ ,  $C_L = 8$  pF, Video Outputs = 2.0  $V_{P-P}$ . See Note 7 for Min and Max parameters and Note 6 for Typicals. DAC parameters apply to all 4 DACs.

|                              | abol Parameter Conditions                |                                          | Min  | Тур  | Max | Units |

|------------------------------|------------------------------------------|------------------------------------------|------|------|-----|-------|

| V <sub>Min DAC</sub>         | Min output voltage of DAC                | Register Value = 0x00                    |      | 0.5  | 0.7 | V     |

| V <sub>Max DAC</sub> Mode 00 | Max output voltage of DAC                | Register Value = 0xFF,<br>DCF[1:0] = 00b | 3.6  | 4.2  |     | V     |

| William Dirico               | Max output voltage of DAC in DCF mode 01 | Register Value = 0xFF,<br>DCF[1:0] = 01b | 1.85 | 2.35 |     | V     |

**DAC Output Electrical Characteristics** (Continued) Unless otherwise noted:  $T_A = 25^{\circ}C$ ,  $V_{CC} = +5.0V$ ,  $V_{IN} = 0.7V$ ,  $V_{ABL} = V_{CC}$ ,  $C_L = 8$  pF, Video Outputs = 2.0  $V_{P-P}$ . See Note 7 for Min and Max parameters and Note 6 for Typicals. DAC parameters apply to all 4 DACs.

| Symbol                                      | Parameter                                        | Conditions                     | Min  | Тур  | Max | Units |

|---------------------------------------------|--------------------------------------------------|--------------------------------|------|------|-----|-------|

| V <sub>Min DAC</sub>                        | Min output voltage of DAC                        | Register Value = 0x00          |      | 0.5  | 0.7 | V     |

| ΔV <sub>Max DAC</sub> (Temp)                | Variation in voltage of DAC with temperature     | 0 < T < 70°C ambient           |      | ±0.5 |     | mV/°C |

| $\Delta V_{\text{Max DAC}} (V_{\text{CC}})$ | Variation in voltage of DAC with V <sub>CC</sub> | 4.75 < V <sub>CC</sub> < 5.25V |      | ±50  |     | mV/V  |

| Linearity                                   | Linearity of DAC over its range                  |                                |      | 5    |     | %     |

| Monotonicity                                | Monotonicity of the DAC                          | Excluding dead zones           |      | ±0.5 |     | LSB   |

| I <sub>MAX</sub>                            | Max Load Current                                 |                                | -1.0 |      | 1.0 | mA    |

### **System Interface Signal Characteristics**

Unless otherwise noted: T<sub>A</sub> = 25°C, V<sub>CC</sub> = +5.0V, V<sub>IN</sub> = 0.7V, V<sub>ABL</sub> = V<sub>CC</sub>, C<sub>L</sub> = 8 pF, Video Outputs = 2.0 V<sub>P-P</sub>. See Note 7 for Min and Max parameters and Note 6 for Typicals. DAC parameters apply to all 4 DACs.

Symbol

Parameter

Conditions

Min Typ Max Unit

| Symbol                     | ymbol Parameter Conditions                     |                                                                                               | Min  | Тур  | Max                   | Units |

|----------------------------|------------------------------------------------|-----------------------------------------------------------------------------------------------|------|------|-----------------------|-------|

| $V_{VTH+}$                 | VFLYBACK positive switching guarantee.         | Vertical Blanking triggered                                                                   | 2.0  |      |                       | V     |

| V <sub>SPOT</sub>          | Spot Killer Voltage                            | Note 17, V <sub>CC</sub> Adjusted to Activate                                                 | 3.4  | 3.9  | 4.25                  | V     |

| V <sub>Ref</sub>           | V <sub>Ref</sub> Output Voltage                |                                                                                               | 1.25 | 1.45 | 1.65                  | V     |

| V <sub>IL</sub> (SCL, SDA) | Logic Low Input Voltage                        |                                                                                               | -0.5 |      | 1.5                   | V     |

| V <sub>IH</sub> (SCL, SDA) | Logic High Input Voltage                       |                                                                                               | 3.0  |      | V <sub>CC</sub> + 0.5 | V     |

| I <sub>L</sub> (SCL, SDA)  | Logic Low Input Current                        | SDA or SCL, Input Voltage = 0.4V                                                              |      | ±10  |                       | μΑ    |

| I <sub>H</sub> (SCL, SDA)  | Logic High Input Voltage                       | SDA or SCL, Input Voltage = 4.5V                                                              |      | ±10  |                       | μΑ    |

| V <sub>OL</sub> (SCL, SDA) | Logic Low Output Voltage                       | I <sub>O</sub> = 3 mA                                                                         |      | 0.5  |                       | V     |

| f <sub>H</sub> Min         |                                                |                                                                                               |      | 25   |                       | kHz   |

| f <sub>H</sub> Max         | Maximum Horizontal Frequency                   | PLL & OSD Operational; PLL<br>Range = 3                                                       |      | 110  |                       | kHz   |

| I <sub>HFB IN</sub> Max    | Horizontal Flyback Input Current               | Absolute Maximum During Flyback                                                               |      |      | 5                     | mA    |

| I <sub>IN</sub>            | Peak Current during flyback                    | Design Value                                                                                  |      | 4    |                       | mA    |

| I <sub>HFB OUT</sub> Max   | Horizontal Flyback Input Current               | Absolute Maximum During Scan                                                                  | -700 |      |                       | μΑ    |

| I <sub>OUT</sub>           | Peak Current during Scan                       | Design Value                                                                                  |      | -550 |                       | μΑ    |

| I <sub>IN THRESHOLD</sub>  | I <sub>IN</sub> H-Blank Detection Threshold    |                                                                                               |      | 0    |                       | μΑ    |

| t <sub>H-BLANK</sub> ON    | H-Blank Time Delay - On                        | + Zero crossing of I <sub>HFB</sub> to 50% of output blanking start. I <sub>24</sub> = +1.5mA |      | 45   |                       | ns    |

| t <sub>H-BLANK</sub> OFF   | H-Blank Time Delay - Off                       | - Zero crossing of $I_{HFB}$ to 50% of output blanking end. $I_{24} = -100\mu A$              |      | 85   |                       | ns    |

| V <sub>BLANK</sub> Max     | Maximum Video Blanking Level                   | Test Setting 4, AC input signal.                                                              | 0    |      | 0.25                  | V     |

| f <sub>FREERUN</sub>       | Free Run H Frequency, including H Blank        |                                                                                               |      | 42   |                       | kHz   |

| t <sub>PW CLAMP</sub>      | Minimum Clamp Pulse Width                      | See Note 15                                                                                   | 200  |      |                       | ns    |

| V <sub>CLAMP MAX</sub>     | Maximum Low Level Clamp Pulse Voltage          | Video Clamp Functioning                                                                       |      |      | 2.0                   | V     |

| V <sub>CLAMP MIN</sub>     | Minimum High Level Clamp Pulse<br>Voltage      | Video Clamp Functioning                                                                       | 3.0  |      |                       | V     |

| I <sub>CLAMP</sub> Low     | Clamp Gate Low Input Current                   | V <sub>23</sub> = 2V                                                                          |      | -0.4 |                       | μA    |

| I <sub>CLAMP</sub> High    | Clamp Gate High Input Current                  | V <sub>23</sub> = 3V                                                                          |      | 0.4  |                       | μA    |

| t <sub>CLAMP-VIDEO</sub>   | Time from End of Clamp Pulse to Start of Video | Referenced to Blue, Red and Green inputs                                                      | 50   |      |                       | ns    |

Note 1: Limits of Absolute Maximum Ratings indicate below which damage to the device must not occur.

### System Interface Signal Characteristics (Continued)

- Note 2: Limits of operating ratings indicate required boundaries of conditions for which the device is functional, but may not meet specific performance limits.

- Note 3: All voltages are measured with respect to GND, unless otherwise specified.

- Note 4: Human body model, 100 pF discharged through a 1.5 k $\Omega$  resistor.

- Note 5: Input from signal generator:  $t_r$ ,  $t_f < 1$  ns.

- Note 6: Typical specifications are specified at +25°C and represent the most likely parametric norm.

- Note 7: Tested limits are guaranteed to National's AOQL; (Average Outgoing Quality Level).

- Note 8: The supply current specified is the quiescent current for  $V_{CC}$  and 5V Dig with  $R_L = \infty$ . Load resistors are not required and are not used in the test circuit, therefore all the supply current is used by the pre-amp.

- Note 9: Linearity Error is the maximum variation in step height of a 16 step staircase input signal waveform with a 0.7 V<sub>P-P</sub> level at the input. All 16 steps equal, with each at least 100 ns in duration.

- Note 10:  $dt/dV_{CC} = 200*(t5.5V-t4.5V)/((t5.5V + t4.5V)) %/V$ , where:

- t5.5V is the rise or fall time at  $V_{CC}$  = 5.5V, and t4.5V is the rise or fall time at  $V_{CC}$  = 4.5V.

- Note 11:  $\Delta A_V$  track is a measure of the ability of any two amplifiers to track each other and quantifies the matching of the three gain stages. It is the difference in gain change between any two amplifiers with the contrast set to  $A_VC-50\%$  and measured relative to the  $A_V$  max condition. For example, at  $A_V$  max the three amplifiers' gains might be 12.1 dB, 11.9 dB, and 11.8 dB and change to 2.2 dB, 1.9 dB and 1.7 dB respectively for contrast set to  $A_VC-50\%$ . This yields a typical gain change of 10.0 dB with a tracking change of  $\pm 0.2$  dB.

- Note 12: ABL should provide smooth decrease in gain over the operational range of 0 dB to -5 dB

- $\Delta A_{ABL} = A(V_{ABL} = V_{ABL MAX GAIN}) A(V_{ABL} = V_{ABL MIN GAIN})$

- Beyond -5 dB the gain characteristics, linearity and pulse response may depart from normal values.

- Note 13: Machine Model ESD test is covered by specification EIAJ IC-121-1981. A 200 pF cap is charged to the specific voltage, then discharged directly into the IC with no external series resistor (resistance of discharge path must be under  $50\Omega$ ).

- Note 14: Measure output levels of the other two undriven amplifiers relative to the driven amplifier to determine channel separation. Terminate the undriven amplifier inputs to simulate generator loading. Repeat test at f<sub>IN</sub> = 10 MHz for V<sub>SEP 10 MHZ</sub>.

- Note 15: A minimum pulse width of 200 ns is the guaranteed minimum for a horizontal line of 15 kHz. This limit is guaranteed by design. If a lower line rate is used then a longer clamp pulse may be required.

- Note 16: Adjust input frequency from 10 MHz ( $A_V$  max reference level) to the -3 dB corner frequency ( $f_{-3~dB}$ ).

- Note 17: Once the spot killer has been activated, the LM1237 remains in the off state until V<sub>CC</sub> is cycled (reduced below 0.5V andthen restored to 5V).

### **Hexadecimal and Binary Notation**

Hexadecimal numbers appear frequently throughout this document, representing slave and register addresses, and register values. These appear in the format "0x...". For example, the slave address for writing the registers of the LM1237 is hexadecimal BA, written as 0xBA. On the other hand, binary values, where the individual bit values are shown, are indicated by a trailing "b". For example, 0xBA is equal to 10111010b. A subset of bits within a register is referred to by the bit numbers in brackets following the register value. For example, the OSD contrast bits are the fourth and fifth bits of register 0x8438. Since the first bit is bit 0, the OSD contrast register is 0x8438[4:3].

### **Register Test Settings**

Table 1 shows the definitions of the Test Settings 1–8 referred to in the specifications sections. Each test setting is a combination of five hexadecimal register values, Contrast, Gain (Blue, Red, Green) and DC offset.

**TABLE 1. Test Setting Definitions**

| Control   | No. of Bits |       | Test Settings |       |                       |         |       |       |       |  |

|-----------|-------------|-------|---------------|-------|-----------------------|---------|-------|-------|-------|--|

| Control   | NO. OI BILS | 1     | 2             | 3     | 4                     | 5       | 6     | 7     | 8     |  |

| Contrast  | 7           | 0x7F  | 0x00          | 0x7F  | 0x7F                  | 0x40    | 0x7F  | 0x7F  | 0x7F  |  |

|           |             | (Max) | Min           | (Max) | (Max)                 | (50.4%) | (Max) | (Max) | (Max) |  |

| B, R, G   | 7           | 0x7F  | 0x7F          | 0x7F  | Set V <sub>O</sub> to | 0x7F    | 0x40  | 0x00  | 0x7F  |  |

| Gain      |             | (Max) | (Max)         | (Max) | 2 V <sub>P-P</sub>    | (Max)   | (50%) | (Min) | (Max) |  |

| DC Offset | 3           | 0x00  | 0x05          | 0x07  | 0x05                  | 0x05    | 0x05  | 0x05  | 0x05  |  |

|           |             | (Min) |               | (Max) |                       |         |       |       |       |  |

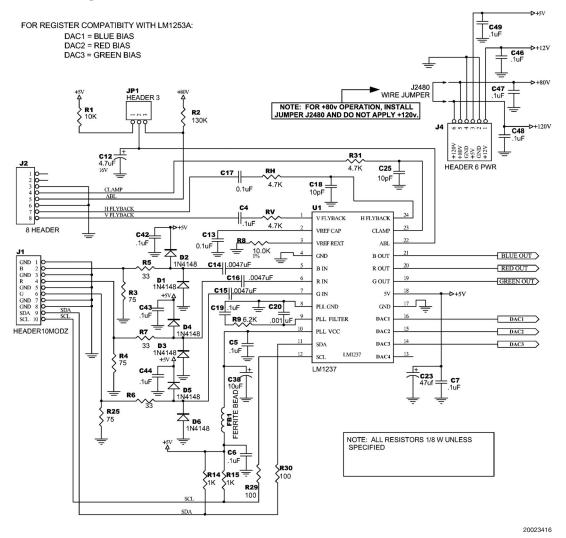

### LM1253A Compatibility

In order to maintain register compatibility with the LM1253A preamplifier datasheet assignments for bias and brightness, the color assignments are recommended as shown in Table 2. If datasheet compatibility is not required, then the DAC assignments can be arbitrary.

TABLE 2. LM1253A Compatibility

|             | DAC Bias Outputs |       |       |            |  |

|-------------|------------------|-------|-------|------------|--|

| LM1237 Pin: | DAC 1            | DAC 2 | DAC 3 | DAC 4      |  |

| Assignment: | Blue             | Green | Red   | Brightness |  |

### **OSD vs Video Intensity**

The OSD amplitude has been increased over the LM1253A level. During monitor alignment, the three gain registers are used to achieve the desired front of screen color balance. This also causes the OSD channels to be adjusted accordingly, since these are inserted into the video channels prior to the gain attenuators. This provides the means to fine tune the intensity of the OSD relative to the video as follows. If a typical starting point for the alignment is to have the gains at maximum (0x7F) and the contrast at 0x55, the resultant OSD intensity will be higher than if the starting point is with the gains at 0x55 and the contrast at maximum (0x7F). This tradeoff allows fine tuning the final OSD intensity relative to the video. In addition, the OSD contrast register, 0x8438 [4:3], provides 4 major increments of intensity. Together, these allow setting the OSD intensity to the most pleasing level.

### Typical Performance Characteristics V<sub>CC</sub> = 5V, T<sub>A</sub> = 25°C unless otherwise specified

#### **System Interface Signals**

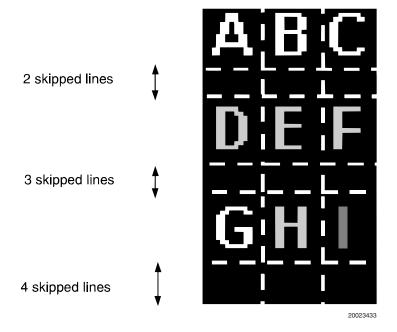

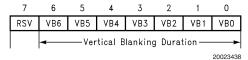

The Horizontal and Vertical Blanking and the Clamping input signals are important for proper functionality of the LM1237. Both blanking inputs must be present for OSD synchronization. In addition, the Horizontal blanking input also assists in setting the proper cathode black level, along with the Clamping pulse. The Vertical blanking input initiates a blanking level at the LM1237 outputs which is programmable from 3 to 127 lines (we recommend at least 10). This can be optionally disabled so there is no vertical blanking.

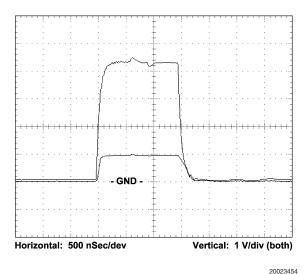

FIGURE 2. Logic Horizontal Blanking

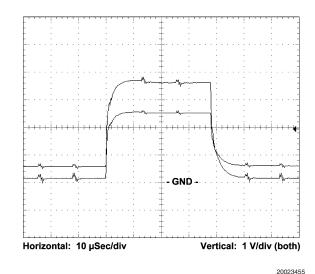

FIGURE 3. Logic Vertical Blanking

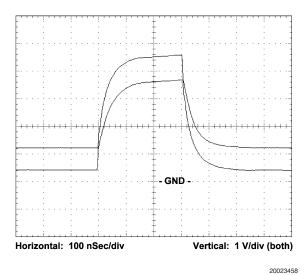

Figure 2 and Figure 3 show the case where the Horizontal and Vertical inputs are logic levels. Figure 2 shows the smaller pin 24 voltage superimposed on the horizontal blanking pulse input to the neck board with  $R_H = 4.7$ K and  $C_{17} = 0.1 \mu F$ . Note where the voltage at pin 24 is clamped to about 1 volt when the pin is sinking current. Figure 3 shows the smaller pin 1 voltage superimposed on the vertical blanking input to the neck board with  $C_4$  jumpered and  $R_V = 4.7$ K. These component values correspond to the application circuit of Figure 15.

# $\textbf{Typical Performance Characteristics} \ \textit{V}_{\textit{CC}} = 5\textit{V}, \ \textit{T}_{\textit{A}} = 25^{\circ}\textit{C} \ \textit{unless otherwise specified (Continued)}$

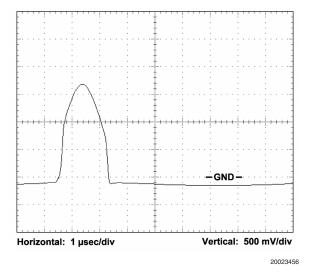

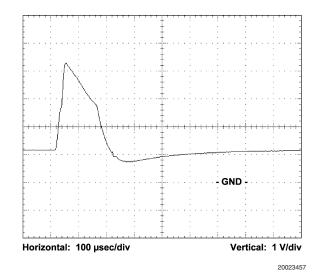

Figure 4 and Figure 5 show the case where the horizontal and vertical inputs are from deflection. Figure 4 shows the pin 24 voltage which is derived from a horizontal flyback pulse of 35 volts peak to peak with R<sub>H</sub> = 8.2K and C<sub>17</sub> jumpered. Figure 5 shows the pin 1 voltage which is derived from a vertical flyback pulse of 55 volts peak to peak with  $C_4 = 1500 pF$  and  $R_V = 120 K$ .

FIGURE 4. Deflection Horizonal Blanking

FIGURE 5. Deflection Vertical Blanking

Figure 6 shows the pin 23 clamp input voltage superimposed on the neck board clamp logic input pulse. R<sub>31</sub> = 1K and should be chosen to limit the pin 23 voltage to about 2.5V peak to peak. This corresponds to the application circuit given in Figure 9.

### **Cathode Response**

Figure 7 shows the response at the red cathode for the application circuit in Figures 9, 10. The input video risetime is 1.5 nanoseconds. The resulting leading edge has a 7.1 nanosecond risetime and a 7.6% overshoot, while the trailing edge has a 7.1 nanosecond risetime and a 6.9% overshoot with an LM2467 driver.

Horizontal: 12.5 nSec/div Vertical: 10 V/div

FIGURE 6. Logic Clamp Pulse

FIGURE 7. Red Cathode Response

7

20023459

### Typical Performance Characteristics $V_{CC} = 5V$ , $T_A = 25^{\circ}C$ unless otherwise specified (Continued)

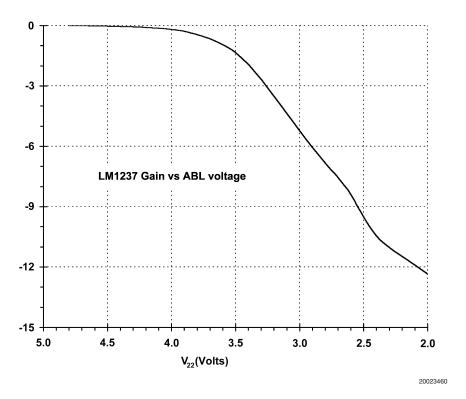

#### **ABL Gain Reduction**

The ABL function reduces the contrast level of the LM1237 as the voltage on pin 22 is lowered from  $V_{CC}$  to around 2 volts. *Figure 8* shows the amount of gain reduction as the voltage is lowered from  $V_{CC}$  (5.0V) to 2V. The gain reduction is small until  $V_{22}$  reaches the knee anound 3.7V, where the slope increases. Many system designs will require about 3 to 5 dB of gain reduction in full beam limiting. Additional attenuation is possible, and can be used in special circumstances. However, in this case, video performance such as video linearity and tracking between channels will tend to depart from normal specifications.

FIGURE 8. ABL Gain Reduction Curve

### **OSD Phase Locked Loop**

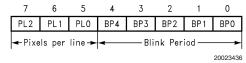

Table 3. OSD Register recommendations shows the recommended horizontal scan rate ranges (in kHz) for each combination of PLL register setting, 0x843E [1:0], and the pixels per line register setting, 0x8401 [7:5]. These ranges are recommended for chip ambient temperatures of 50°C to 70°C. While the OSD PLL will lock for other register combinations and at scan rates outside these ranges, the performance of the loop will be improved if these recommendations are followed. NR means the combination of PLL and PPL is not recommended for any scan rate.

**TABLE 3. OSD Register recommendations**

|       | PPL=0   | PPL=1   | PPL=2   | PPL=3    | PPL=4    | PPL=5    | PPL=6    | PPL=7    |

|-------|---------|---------|---------|----------|----------|----------|----------|----------|

| PLL=1 | 27 - 57 | 26 - 49 | 25 - 45 | 25 - 41  | 25 - 37  | 25 - 34  | 25 - 32  | 25 - 30  |

| PLL=2 | NR      | NR      | 45 - 89 | 41 - 82  | 37 - 75  | 34 - 69  | 32 - 64  | 30 - 60  |

| PLL=3 | NR      | NR      | NR      | 82 - 110 | 75 - 110 | 69 - 110 | 64 - 110 | 60 - 110 |

# Pin Descriptions and Application Information

| Pin<br>No.  | Pin Name                                        | Schematic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-------------|-------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1           | V Flyback                                       | V Flyback  C <sub>4</sub> R <sub>V</sub> TC <sub>24</sub> *ESD Protection  *TOVCC  *TOVCC | Required for OSD synchronization and is also used for vertical blanking of the video outputs. The actual switching threshold is about 35% of $V_{\rm CC}$ . For logic level inputs $C_4$ can be a jumper, but for flyback inputs, an AC coupled differentiator is recommended, where $R_{\rm V}$ is large enough to prevent the voltage at pin 1 from exceeding $V_{\rm CC}$ or going below GND. $C_4$ should be small enough to flatten the vertical rate ramp at pin 1. $C_{24}$ may be needed to reduce noise. |

| 2           | V <sub>REF</sub> Bypass                         | V <sub>REF</sub> Bypass 2 * * * * * * * * to pin 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Provides filtering for the internal voltage which sets the internal bias current in conjunction with R <sub>EXT</sub> . A minimum of 0.1 µF is recommended for proper filtering. This capacitor should be placed as close to pin 2 and the pin 4 ground return as possible.                                                                                                                                                                                                                                       |

| 3           | V <sub>REF</sub> Current Set                    | V <sub>REF</sub> * * * * * * * * * * * * * * * * * * *                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | External resistor, 10k 1%, sets the internal bias current level for optimum performance of the LM1237. This resistor should be placed as close to pin 3 and the pin 4 ground return as possible                                                                                                                                                                                                                                                                                                                   |

| 4           | Analog Ground                                   | 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | This is the ground for the input analog portions of the LM1237 internal circuitry.                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 5<br>6<br>7 | Blue Video In<br>Red Video In<br>Green Video In | Video In Sp.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | These video inputs must be AC coupled with a .0047 $\mu$ F cap. Internal DC restoration is done at these inputs. A series resistor of about 33 $\Omega$ and external ESD protection diodes should also be used for protection from ESD damage.                                                                                                                                                                                                                                                                    |

| 8 10        | Digital Ground<br>PLL V <sub>CC</sub>           | ferrite bead  0.1 μF  10  10  10  10  10  10  10  10  10  1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | The ground pin should be connected to the rest of the circuit ground by a short but independent PCB trace to prevent contamination by extraneous signals. The $V_{\rm CC}$ pin should be isolated from the rest of the $V_{\rm CC}$ line by a ferrite bead and bypassed to pin 8 with an electrolytic capacitor and a high frequency ceramic.                                                                                                                                                                     |

# Pin Descriptions and Application Information (Continued)

| Pin<br>No.           | Pin Name                                                     | Schematic                                          | Description                                                                                                                                                                                                                                                                                                                                                                     |

|----------------------|--------------------------------------------------------------|----------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 9                    | PLL Filter                                                   | 6.2 K 0.1 µF 1 nF  independent ground              | Recommended topology and values are shown to the left. It is recommended that both filter branches be bypassed to the independent ground as close to pin 8 as possible. Great care should be taken to prevent external signals from coupling into this filter from video, I <sup>2</sup> C, etc.                                                                                |

| 11                   | SDA                                                          | 2.2 K Data In SDA 100 * ESD Protection  Data Out   | The I²C compatible data line. A pull-up resistor of about 2 Kohms should be connected between this pin and $V_{\rm CC}$ . A resistor of at least $100\Omega$ should be connected in series with the data line for additional ESD protection.                                                                                                                                    |

| 12                   | SCL                                                          | SCL VCC VCC VCC SCL VCC ***  **ESD Protection      | The I $^2$ C compatible clock line. A pull-up resistor of about 2 k $\Omega$ should be connected between this pin and V $_{CC}$ . A resistor of at least 100 $\Omega$ should be connected in series with the clock line for additional ESD protection.                                                                                                                          |

| 13<br>14<br>15<br>16 | DAC 4 Output<br>DAC 2 Output<br>DAC 3 Output<br>DAC 1 Output | DAC Outputs 13 * * * * * * * * * * * * * * * * * * | DAC outputs for cathode cut-off adjustments and brightness control. DAC 4 can be set to change the outputs of the other three DACs, acting as a brightness control. The DAC values and the special DAC 4 function are set through the $I^2C$ compatible bus. A resistor of at least $100\Omega$ should be connected in series with these outputs for additional ESD protection. |

| 17<br>18             | Ground<br>V <sub>CC</sub>                                    | V <sub>cc</sub> Ο 18 47 μF                         | Ground pin for the output analog portion of the LM1237 circuitry, and power supply pin for both analog and digital sections of the LM1237. Note the recommended charge storage and high frequency capacitors which should be as close to pins 17 and 18 as possible.                                                                                                            |

| 19<br>20<br>21       | Green Output<br>Red Output<br>Blue Output                    | Video Outputs * ESD Protection                     | These are the three video output pins. They are intended to drive the LM246x family of cathode drivers. Nominally, about 2V peak to peak will produce 40V peak to peak of cathode drive.                                                                                                                                                                                        |

# Pin Descriptions and Application Information (Continued)

| Pin<br>No. | Pin Name  | Schematic                                                                                      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|------------|-----------|------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 22         | ABL       | HVT VINT VINT CABL *ESD Protection                                                             | The Automatic Beam Limiter input is biased to the desired beam current limit by R <sub>ABL</sub> and V <sub>BB</sub> and normally keeps D <sub>INT</sub> forward biased. When the current resupplying the CRT capacitance (averaged by C <sub>ABL</sub> ) exceeds this limit, then D <sub>INT</sub> begins to turn off and the voltage at pin 22 begins to drop. The LM1237 then lowers the gain of the three video channels until the beam current reaches an equilibrium value.                                                                                                               |

| 23         | CLAMP     | Clamp<br>Pulse<br>C <sub>25</sub><br>* ESD Protection                                          | This pin accepts either TTL or CMOS logic levels. The internal switching threshold is approximately one-half of $V_{\rm CC}$ . An external series resistor, $R_{\rm 31}$ , of about 1k is recommended to avoid overdriving the input devices. In any event, $R_{\rm EXT}$ must be large enough to prevent the voltage at pin 23 from going higher than $V_{\rm CC}$ or below GND.                                                                                                                                                                                                               |

| 24         | H Flyback | R <sub>34</sub> R <sub>H</sub> C <sub>17</sub> C <sub>8</sub> C <sub>18</sub> **ESD Protection | Proper operation requires current reversal. R <sub>H</sub> should be large enough to limit the peak current at pin 24 to about +4 ma during blanking, and –500 µA during scan. C <sub>17</sub> is usually needed for logic level inputs and should be large enough to make the time constant, R <sub>H</sub> C <sub>17</sub> significantly larger than the horizontal period. R <sub>34</sub> and C <sub>8</sub> are typically 300 ohms and 330 pf when the flyback waveform has ringing and needs filtering. C <sub>18</sub> may be needed to filter extraneous noise and can be up to 100 pF. |

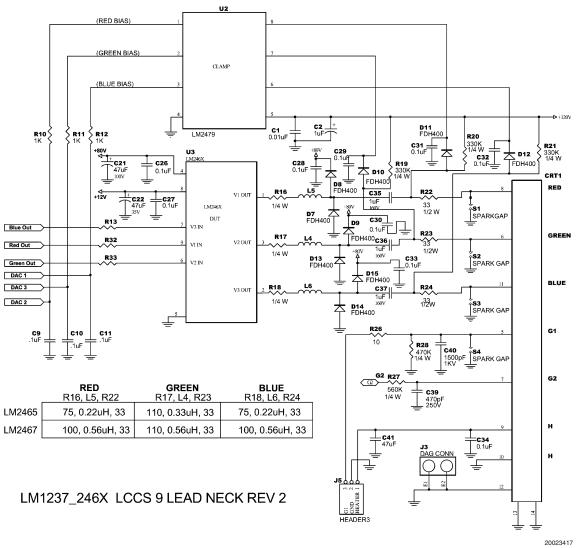

### **Schematic Diagram**

FIGURE 9. LM123x-LM246x Demo Board Schematic

# Schematic Diagram

FIGURE 10. LM123x-LM246x Demo Board Schematic (continued)

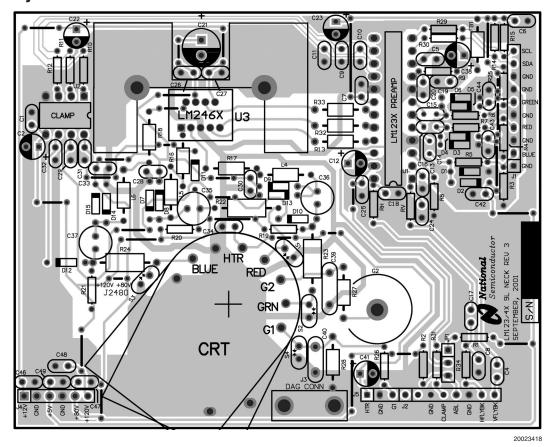

# **PCB Layout**

FIGURE 11. LM123x-LM246x Demo Board Layout

### **OSD Generator Operation**

### **PAGE OPERATION**

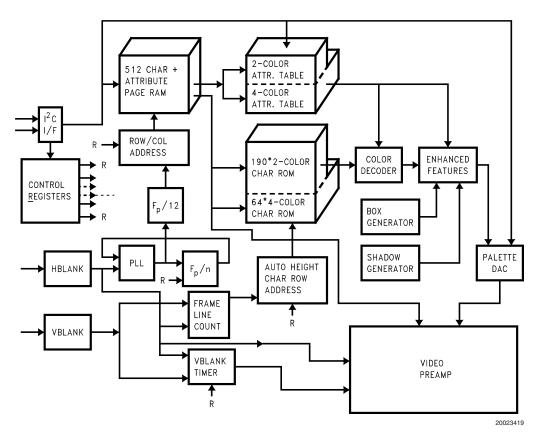

Figure 12. shows the block diagram of the OSD generator.

FIGURE 12. Block Diagram of the OSD Generator

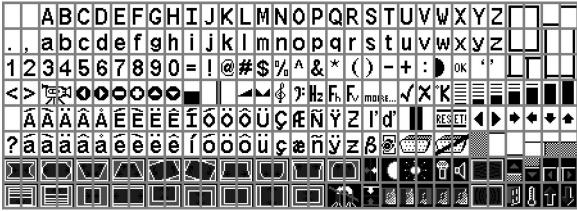

Video information is created using any of the 256 predefined characters stored in the mask programmed ROM. Each character has a unique 8-bit code that is used as its address. Consecutive rows of characters make up the displayed window. These characters can be stored in the page RAM, written under I<sup>2</sup>C compatible commands by the monitor microcontroller. Each row can contain any number of characters up to the limit of the displayable line length, although some restrictions concerning the enhanced features apply on character rows longer than 32 characters.

The number of characters across the width and height of the page can be varied under I<sup>2</sup>C compatible control, but the total number of characters that can be stored and displayed

on the screen is limited to 512 including any character row end characters. The horizontal and vertical start position can also be programmed through the I<sup>2</sup>C compatible bus.

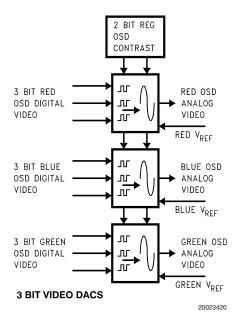

### **OSD VIDEO DAC**

The OSD DAC is controlled by the 9-bit (3x3 bits) OSD video information coming from the pixel serializer look-up table. The look-up table in the OSD palette is programmed to select 4 color levels out of 8 linearly spaced levels per channel. The OSD DAC is shown in Figure 13, where the gain is programmable by the 2-bit OSD CONTRAST register, in 4 stages to give the required OSD signal. The OSD DACs use the reference voltage,  $V_{\rm REF}$ , to bias the OSD outputs.

FIGURE 13. Block Diagram of OSD DACs

#### **OSD VIDEO TIMING**

The OSD SELECT signal switches the source of video information within the preamplifier from external video to the internally generated OSD video.

#### **WINDOWS**

Two separate windows can be opened, utilizing the data stored in the page RAM. Each window has its own horizontal and vertical start position, although the second window should be horizontally spaced at least two character spaces away from the first window, and should never overlap the first window when both windows are on. The OSD window must be placed within the active video.

### CHARACTER CELL

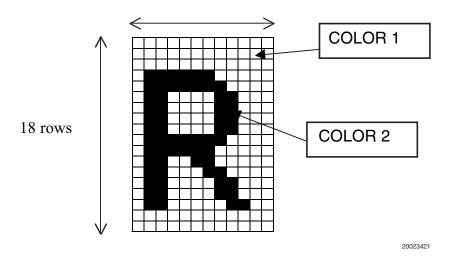

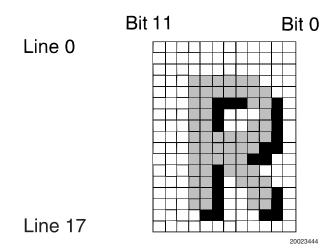

Each character is defined as a 12 wide by 18 high matrix of picture elements, or 'pixels'. The character font is shown in *Figure 25*. There are two types of characters defined in the character ROM:

- Two-color: There are 190 two-color characters. Each pixel of these characters is defined by a single bit value. If the bit value is 0, then the color is defined as 'Color 1' or the 'background' color. If the bit value is 1, then the color is defined as 'Color 2', or the 'foreground' color. An example of a character is shown in *Figure 14*.

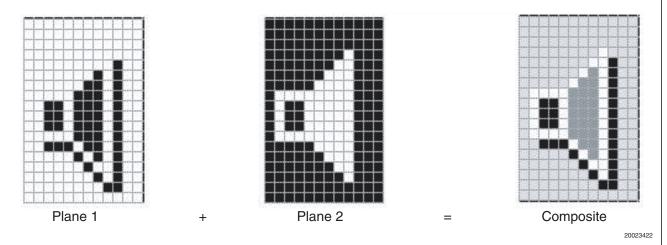

- 2. Four-color: There are 64 four-color characters stored in the character ROM. Each pixel of the four-color character is defined by two bits of information, and thus can define four different colors, Color 1, Color 2, Color 3, and Color 4. Color 1 is defined as the 'background' color. All other colors are considered 'foreground' colors, although for most purposes, any of the four colors may be used in any way. Because each four-color character has two bits, the LM1237 internally has a matrix of two planes of ROM as shown in Figure 15.

### 12 columns

FIGURE 14. A Two-Color Character

FIGURE 15. A Four-Color Character

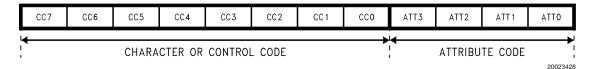

#### **ATTRIBUTE TABLES**

Each character has an attribute value assigned to it in the page RAM. The attribute value is 4 bits wide, making each character entry in the page RAM 12 bits wide in total. The attribute value acts as an address which points to one of 16 entries in either the two-color attribute table RAM or the four-color attribute table RAM. The attribute word in the table contains the coding information which defines which color is represented by color1 and color2 in the two color attribute table and color1, color2, color3, color4 in the four-color attribute table. Each color is defined by a 9-bit value, with 3 bits assigned to each channel of RGB. A dynamic look-up table defines each of the 16 different color combination selections or 'palettes'. As the look-up table can be dynamically coded by the microcontroller over the I<sup>2</sup>C compatible interface, each color can be assigned to any one of 2<sup>9</sup> (i.e.

512) choices. This allows a maximum of 64 different colors to be used within one page using the 4-color characters, with up to 4 different colors within any one character and 32 different colors using the 2-color characters, with 2 different colors within any one character.

#### TRANSPARENT DISABLE

In addition to the 9 lines of video data, a tenth data line is generated by the transparent disable bit. When this line is activated, the black color code will be translated as 'transparent' or invisible. This allows the video information from the PC system to be visible on the screen when this is present. Note that this feature is enabled on any black color in of the first 8 attribute table entries.

#### **ENHANCED FEATURES**

In addition to the wide selection of colors for each character, additional character features can be selected on a character by character basis. There are 3 Enhanced Feature Registers, EF0, EF1 and EF2.

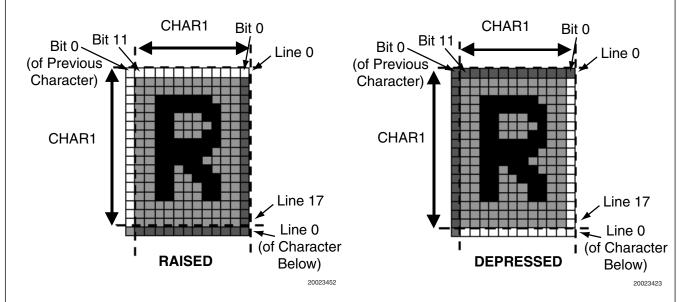

- 1. Button Boxes—The OSD generator examines the character string being displayed and if the 'button box' attributes have been set in the Enhanced feature byte, then a box creator selectively substitutes the character pixels in either or both the top and left most pixel line or column with a button box pixel. The shade of the button box pixel depends upon whether a 'depressed' or 'raised' box is required, and can be programmed through the I<sup>2</sup>C compatible interface. The raised pixel color ('highlight') is defined by the value in the color palette register, EF1 (normally white). The depressed pixel ('lowlight') color by the value in the color palette register EF2 (normally gray). See Figure 16.

- Heavy Button Boxes—When heavy button boxes are selected, the color palette value stored in register EF3 is

- used for the depressed ('lowlight') pixel color instead of the value in register EF2.

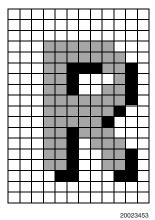

- 3. Shadowing Shadowing can be added to two-color characters by choosing the appropriate attribute value for the character. When a character is shadowed, a shadow pixel is added to the lower right edges of the color 2 image, as shown in *Figure 17*. The color of the shadow is determined by the value in the color palette register EF3 (normally black).

- 4. Bordering—A border can be added to the two-color characters. When a character is bordered, a border pixel is added at every horizontal, vertical or diagonal transition between color 1 and color 2. See *Figure 18*. The color of the border is determined by the value in the color palette register EF3 (normally black).

- 5. Blinking—If blinking is enabled as an attribute, all colors within the character except the button box pixels which have been overwritten will alternately switch to color 1 and then back to the correct color at a rate determined by the microcontroller through the I<sup>2</sup>C compatible interface.

Effect on the screen:

20023424

FIGURE 16. Button Boxes

FIGURE 17. Shadowing

FIGURE 18. Bordering

### Microcontroller Interface

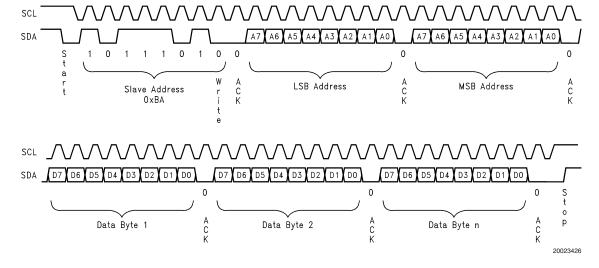

The microcontroller interfaces to the LM1237 preamp via the I<sup>2</sup>C compatible interface. The protocol of the interface begins with a Start Pulse followed by a byte comprised of a seven bit Slave Device Address and a Read/Write bit. Since the first byte is composed of both the address and the read/write bit, the address of the LM1237 for writing is 0xBA (10111010b) and the address for reading is 0xBB (10111011b). The development software provided by National Semiconductor will automatically take care of the difference between the read and write addresses if the target address under the communications tab is set to 0xBA. *Figure 19* and *Figure 20* show a write and read sequence on the I<sup>2</sup>C compatible interface.

#### WRITE SEQUENCE

The write sequence begins with a start condition which consists of the master pulling SDA low while SCL is held high. The slave device address is next sent. The address byte is made up of an address of seven bits (7-1) and the read/write bit (0). Bit 0 is low to indicate a write operation. Each byte that is sent is followed by an acknowledge. When SCL is high the master will release the SDA line. The slave must pull SDA low to acknowledge. The register to be written to is next sent in two bytes, the least significant byte being sent first. The master can then send the data, which consists of one or more bytes. Each data byte is followed by an acknowledge bit. If more than one data byte is sent the data will increment to the next address location. See *Figure 19*.

### Microcontroller Interface (Continued)

FIGURE 19. I<sup>2</sup>C Compatible Write Sequence

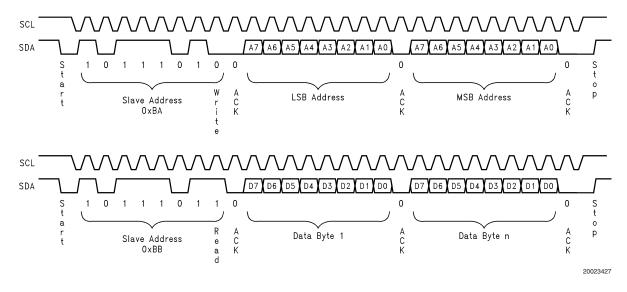

#### **READ SEQUENCE**

Read sequences are comprised of two I<sup>2</sup>C compatible transfer sequences: The first is a write sequence that only transfers the two byte address to be accessed. The second is a read sequence that starts at the address transferred in the previous address only write access and increments to the next address upon every data byte read. This is shown in *Figure 20*. The write sequence consists of the Start Pulse, the Slave Device Address, the Read/Write bit (a zero, indicating a write) and the Acknowledge bit; the next byte is the least significant byte of the address to be accessed, followed by its Acknowledge bit. This is then followed by a byte

containing the most significant address byte, followed by its Acknowledge bit. Then a Stop bit indicates the end of the address only write access. Next the read data access will be performed beginning with the Start Pulse, the Slave Device Address, the Read/Write bit (a one, indicating a read) and the Acknowledge bit. The next 8 bits will be the read data driven out by the LM1237 preamp associated with the address indicated by the two address bytes. Subsequent read data bytes will correspond to the next increment address locations. Data should only be read from the LM1237 when both OSD windows are disabled.

FIGURE 20. I<sup>2</sup>C Compatible Read Sequence

### LM1237 Address Map

### **TABLE 4. Character ROM Address Map**

| Address Range | R/W | Description                                                                                |

|---------------|-----|--------------------------------------------------------------------------------------------|

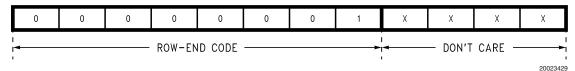

| 0x0000-0x2FFF | R   | ROM Character Fonts, 190 two-color Character Fonts that are read-only. The format          |

|               |     | of the address is as follows:                                                              |

|               |     | A15-A14: Always zeros.                                                                     |

|               |     | A13-A6: Character value (0x00-0xBF are valid values)                                       |

|               |     | A5-A1: Row of the character (0x00-0x11 are valid values)                                   |

|               |     | A0: Low byte of line when a zero. High byte of line when a one.                            |

|               |     | The low byte will contain the first eight pixels of the line with data Bit 0 corresponding |

|               |     | to the left most bit in the Character Font line. The high byte will contain the last four  |

|               |     | pixels and data. Bits 7-4 are "don't cares". Data Bit 3 of the high byte corresponds to    |

|               |     | the right most pixel in the Character Font line.                                           |

| 0x3000-0x3FFF | R   | ROM Character Fonts, 64 four-color Character Fonts that are read-only. The format of       |

|               |     | the address is as follows:                                                                 |

|               |     | A15-A14: Always zeros.                                                                     |

|               |     | A13-A6: Character value (0xC0-0xFF are valid values)                                       |

|               |     | A5-A1: Row of the character (0x00-0x11 are valid values)                                   |

|               |     | A0: Low byte of line when a zero. High byte of line when a one.                            |

|               |     | The low byte will contain the first eight pixels of the line with data Bit 0 corresponding |

|               |     | to the left most bit in the Character Font line. The high byte will contain the last four  |

|               |     | pixels and data Bits 7-4 are "don't cares". Data Bit 3 of the high byte corresponds to     |

|               |     | the right most pixel in the Character Font line.                                           |

|               |     | NOTE: The value of Bit 0 of the Character Font Access Control Register (Address            |

|               |     | 0x8402) is a zero, it indicates that the Bit 0 data value of the four-color pixels is bein |

|               |     | accessed via these addresses. When the value of Bit 0 of the Access Control Regist         |

|               |     | is a one, it indicates that the Bit 1 data value of the four-color pixel is being accessed |

|               |     | via these addresses.                                                                       |

| 0x4000-0x7FFF | _   | Reserved.                                                                                  |

### TABLE 5. Display Page RAM Address Map

| Address Range | R/W | Description                                                                          |

|---------------|-----|--------------------------------------------------------------------------------------|

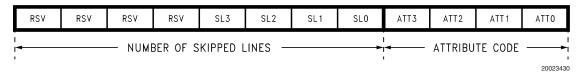

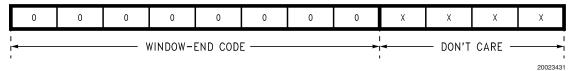

| 0x8000-0x81FF | R/W | Display Page RAM Characters. A total of 512 display characters, skipped line,        |

|               |     | end-of-row and end-of-window character codes may be supported via this range.        |

|               |     | To support skipped lines and character attributes a number of special case rules are |

|               |     | used when writing to this range. (Refer to the Display Page RAM section of this      |

|               |     | document for more details.)                                                          |

# **Preamp Interface Registers**

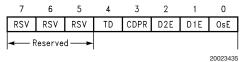

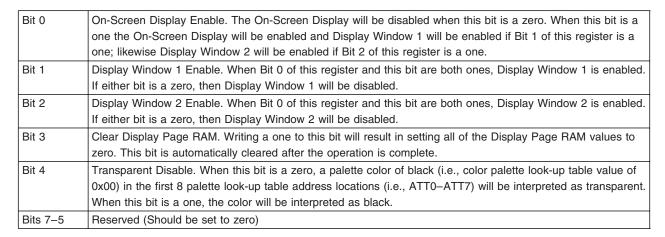

### **TABLE 6. OSD Interface Registers**

| Register         | Address | Default | D7                                       | D6          | D5           | D4    | D3    | D2        | D1           | D0    |

|------------------|---------|---------|------------------------------------------|-------------|--------------|-------|-------|-----------|--------------|-------|

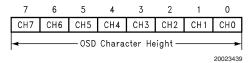

| Fonts - 2 Color  | 0x0000- |         |                                          |             |              | DIVE  | (7:0) |           |              |       |