### DS90CF384A/DS90CF364A

# +3.3V LVDS Receiver 24-Bit Flat Panel Display (FPD) Link – 65 MHz, +3.3V LVDS Receiver 18-Bit Flat Panel Display (FPD) Link – 65 MHz

#### **General Description**

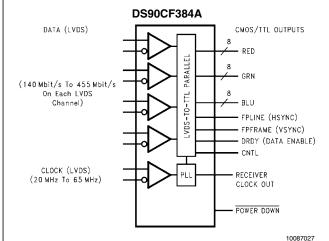

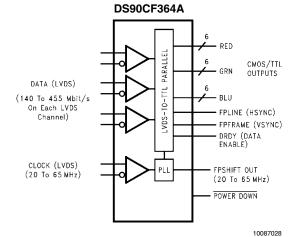

The DS90CF384A receiver converts the four LVDS data streams (Up to 1.8 Gbps throughput or 227 Megabytes/sec bandwidth) back into parallel 28 bits of CMOS/TTL data (24 bits of RGB and 4 bits of Hsync, Vsync, DE and CNTL). Also available is the DS90CF364A that converts the three LVDS data streams (Up to 1.3 Gbps throughput or 170 Megabytes/sec bandwidth) back into parallel 21 bits of CMOS/TTL data (18 bits of RGB and 3 bits of Hsync, Vsync and DE). Both Receivers' outputs are Falling edge strobe. A Rising edge or Falling edge strobe transmitter (DS90C383A/DS90C363A) will interoperate with a Falling edge strobe Receiver without any translation logic.

The DS90CF384A / DS90CF364A devices are enhanced over prior generation receivers and provided a wider data valid time on the receiver output.

This chipset is an ideal means to solve EMI and cable size problems associated with wide, high speed TTL interfaces.

#### **Features**

- 20 to 65 MHz shift clock support

- 50% duty cycle on receiver output clock

- Best-in-Class Set & Hold Times on RxOUTPUTs

- Rx power consumption <142 mW (typ) @65MHz Grayscale

- Rx Power-down mode <200µW (max)</p>

- ESD rating >7 kV (HBM), >700V (EIAJ)

- Supports VGA, SVGA, XGA and Dual Pixel SXGA.

- PLL requires no external components

- Compatible with TIA/EIA-644 LVDS standard

- Low profile 56-lead or 48-lead packages

### **Block Diagrams**

Order Number DS90CF384AMTD See NS Package Number MTD56

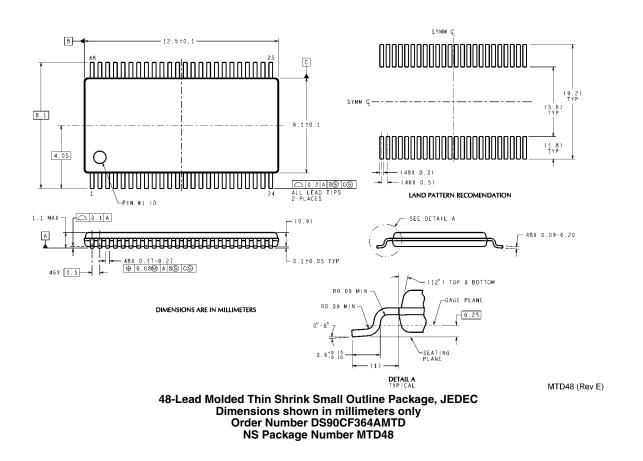

Order Number DS90CF364AMTD See NS Package Number MTD48

TRI-STATE® is a registered trademark of National Semiconductor Corporation.

#### **Absolute Maximum Ratings** (Note 1)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

Solder Reflow Temperature (20 sec for FBGA)

Maximum Package Power Dissipation Capacity @ 25°C MTD56 (TSSOP) Package:

DS90CF384A 1.61 W

MTD48 (TSSOP) Package:

DS90CF364A 1.89 W

Package Derating:

DS90CF384AMTD 12.4 mW/°C above +25°C DS90CF364AMTD 15 mW/°C above +25°C

**ESD Rating**

$\begin{array}{ll} (\mbox{HBM}, \ 1.5 \ \mbox{k}\Omega, \ 100 \ \mbox{pF}) & > 7 \ \mbox{kV} \\ (\mbox{EIAJ}, \ 0\Omega, \ 200 \ \mbox{pF}) & > 700 \mbox{V} \end{array}$

## Recommended Operating Conditions

|                                         | Min | Nom | Max | Units   |  |

|-----------------------------------------|-----|-----|-----|---------|--|

| Supply Voltage (V <sub>CC</sub> )       | 3.0 | 3.3 | 3.6 | V       |  |

| Operating Free Air                      |     |     |     |         |  |

| Temperature (T <sub>A</sub> )           | -10 | +25 | +70 | °C      |  |

| Receiver Input Range                    | 0   |     | 2.4 | V       |  |

| Supply Noise Voltage (V <sub>CC</sub> ) |     |     | 100 | $mV_PP$ |  |

#### **Electrical Characteristics**

Over recommended operating supply and temperature ranges unless otherwise specified.

+220°C

| Symbol          | Parameter                                                                                               | Conditions                                                      | Conditions              |      |       | Max      | Units |

|-----------------|---------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|-------------------------|------|-------|----------|-------|

| CMOS/TT         | L DC SPECIFICATIONS (For Power D                                                                        | own Pin)                                                        |                         |      |       |          |       |

| V <sub>IH</sub> | High Level Input Voltage                                                                                |                                                                 |                         | 2.0  |       | $V_{CC}$ | V     |

| V <sub>IL</sub> | Low Level Input Voltage                                                                                 |                                                                 |                         | GND  |       | 0.8      | V     |

| V <sub>CL</sub> | Input Clamp Voltage                                                                                     | I <sub>CL</sub> = -18 mA                                        |                         |      | -0.79 | -1.5     | ٧     |

| I <sub>IN</sub> | Input Current                                                                                           | $V_{IN} = 0.4V, 2.5V \text{ or } V_{CC}$                        |                         |      | +1.8  | +10      | μΑ    |

|                 |                                                                                                         | V <sub>IN</sub> = GND                                           |                         | -10  | 0     |          | μΑ    |

| CMOS/TT         | L DC SPECIFICATIONS                                                                                     | •                                                               |                         | •    |       |          |       |

| V <sub>OH</sub> | High Level Output Voltage                                                                               | $I_{OH} = -0.4 \text{ mA}$                                      |                         | 2.7  | 3.3   |          | V     |

| V <sub>OL</sub> | Low Level Output Voltage                                                                                | I <sub>OL</sub> = 2 mA                                          |                         |      | 0.06  | 0.3      | V     |

| I <sub>os</sub> | Output Short Circuit Current                                                                            | V <sub>OUT</sub> = 0V                                           |                         |      | -60   | -120     | mA    |

| LVDS RE         | CEIVER DC SPECIFICATIONS                                                                                |                                                                 |                         | •    |       |          |       |

| V <sub>TH</sub> | Differential Input High Threshold                                                                       | $V_{CM} = +1.2V$                                                | V <sub>CM</sub> = +1.2V |      |       | +100     | mV    |

| $V_{TL}$        | Differential Input Low Threshold                                                                        |                                                                 |                         | -100 |       |          | mV    |

| I <sub>IN</sub> | Input Current                                                                                           |                                                                 |                         | ±10  | μΑ    |          |       |

|                 |                                                                                                         | $V_{IN} = +2.4V, V_{CC} = 3.6V$<br>$V_{IN} = 0V, V_{CC} = 3.6V$ |                         |      |       | ±10      | μΑ    |

| RECEIVE         | R SUPPLY CURRENT                                                                                        |                                                                 |                         | ,    |       |          |       |

| ICCRW           | Receiver Supply Current                                                                                 | $C_L = 8 pF,$                                                   | f = 32.5 MHz            |      | 49    | 65       | mA    |

|                 | Worst Case                                                                                              | Worst Case Pattern,                                             | f = 37.5 MHz            |      | 53    | 70       | mA    |

|                 |                                                                                                         | DS90CF384A (Figures 1, 4)                                       | f = 65 MHz              |      | 81    | 105      | mA    |

| ICCRW           | Receiver Supply Current                                                                                 | $C_L = 8 pF,$                                                   | f = 32.5 MHz            |      | 49    | 55       | mA    |

|                 | Worst Case                                                                                              | Worst Case Pattern,                                             | f = 37.5 MHz            |      | 53    | 60       | mA    |

|                 |                                                                                                         | DS90CF364A (Figures 1, 4)                                       | f = 65 MHz              |      | 78    | 90       | mA    |

| ICCRG           | Receiver Supply Current,                                                                                | $C_L = 8 pF,$                                                   | f = 32.5 MHz            |      | 28    | 45       | mA    |

|                 | 16 Grayscale                                                                                            | 16 Grayscale Pattern,                                           | f = 37.5 MHz            |      | 30    | 47       | mA    |

|                 |                                                                                                         | (Figures 2, 3, 4)                                               | f = 65 MHz              |      | 43    | 60       | mA    |

| ICCRZ           | RZ Receiver Supply Current Power Down = Low Power Down Receiver Outputs Stay Low during Power Down Mode |                                                                 |                         |      | 10    | 55       | μΑ    |

|                 |                                                                                                         |                                                                 |                         |      |       |          |       |

**Note 1:** "Absolute Maximum Ratings" are those values beyond which the safety of the device cannot be guaranteed. They are not meant to imply that the device should be operated at these limits. The tables of "Electrical Characteristics" specify conditions for device operation.

Note 2: Typical values are given for  $V_{CC}$  = 3.3V and  $T_A$  = +25C.

Note 3: Current into device pins is defined as positive. Current out of device pins is defined as negative. Voltages are referenced to ground unless otherwise specified (except  $V_{OD}$  and  $\Delta V_{OD}$ ).

#### **Receiver Switching Characteristics**

Over recommended operating supply and temperature ranges unless otherwise specified

| Symbol | Parameter                                                             | Min        | Тур   | Max   | Units |    |

|--------|-----------------------------------------------------------------------|------------|-------|-------|-------|----|

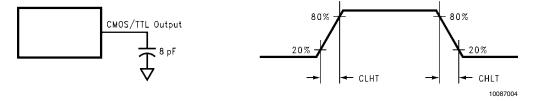

| CLHT   | CMOS/TTL Low-to-High Transition Time (Figure 4)                       |            | 2     | 5     | ns    |    |

| CHLT   | CMOS/TTL High-to-Low Transition Time (Figure 4)                       |            | 1.8   | 5     | ns    |    |

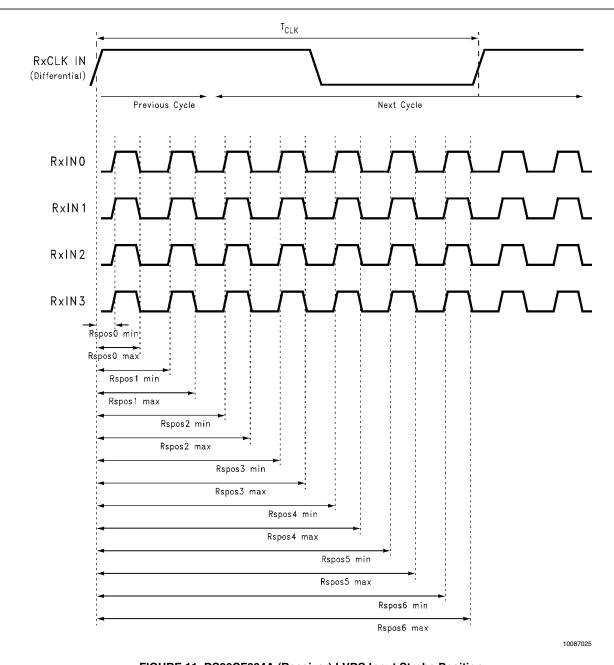

| RSPos0 | Receiver Input Strobe Position for Bit 0 (Figure 11,                  | 1.20       | 1.96  | 2.82  | ns    |    |

|        | Figure 12)                                                            |            |       |       |       |    |

| RSPos1 | Receiver Input Strobe Position for Bit 1                              |            | 6.91  | 7.67  | 8.53  | ns |

| RSPos2 | Receiver Input Strobe Position for Bit 2                              |            | 12.62 | 13.38 | 14.24 | ns |

| RSPos3 | Receiver Input Strobe Position for Bit 3                              |            | 18.33 | 19.09 | 19.95 | ns |

| RSPos4 | Receiver Input Strobe Position for Bit 4                              |            | 24.04 | 24.80 | 25.66 | ns |

| RSPos5 | Receiver Input Strobe Position for Bit 5                              | 29.75      | 30.51 | 31.37 | ns    |    |

| RSPos6 | Receiver Input Strobe Position for Bit 6                              |            | 35.46 | 36.22 | 37.08 | ns |

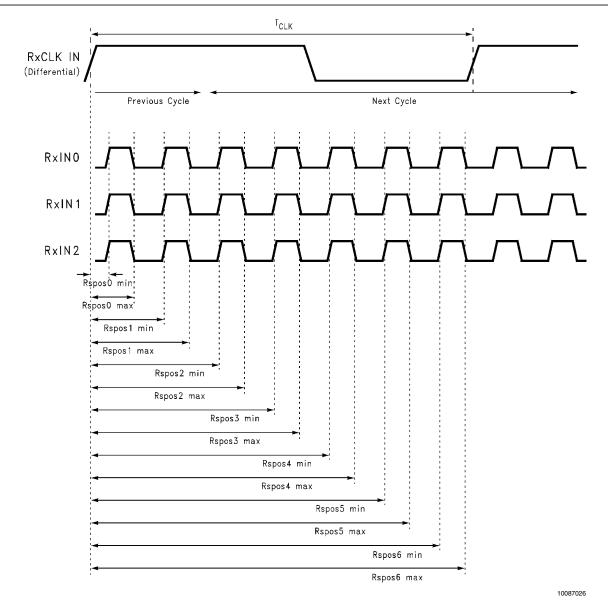

| RSPos0 | Receiver Input Strobe Position for Bit 0 (Figure 11, Figure 12)       | 0.7        | 1.1   | 1.4   | ns    |    |

| RSPos1 | Receiver Input Strobe Position for Bit 1                              | 2.9        | 3.3   | 3.6   | ns    |    |

| RSPos2 | Receiver Input Strobe Position for Bit 2                              |            | 5.1   | 5.5   | 5.8   | ns |

| RSPos3 | Receiver Input Strobe Position for Bit 3                              |            | 7.3   | 7.7   | 8.0   | ns |

| RSPos4 | Receiver Input Strobe Position for Bit 4                              |            | 9.5   | 9.9   | 10.2  | ns |

| RSPos5 | Receiver Input Strobe Position for Bit 5                              | 11.7       | 12.1  | 12.4  | ns    |    |

| RSPos6 | Receiver Input Strobe Position for Bit 6                              | 13.9       | 14.3  | 14.6  | ns    |    |

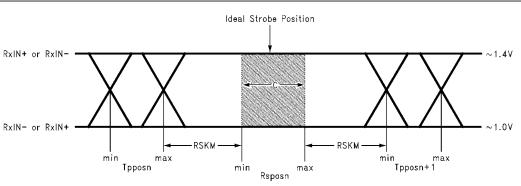

| RSKM   | RxIN Skew Margin (Note 4) (Figure 13)                                 | f = 25 MHz | 750   |       |       | ps |

|        |                                                                       | f = 65 MHz | 500   |       |       | ps |

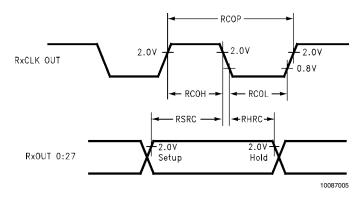

| RCOP   | RxCLK OUT Period (Figure 5)                                           |            | 15    | Т     | 50    | ns |

| RCOH   | RxCLK OUT High Time (Figure 5)                                        | f = 65 MHz | 5.0   | 7.6   | 9.0   | ns |

| RCOL   | RxCLK OUT Low Time (Figure 5)                                         |            | 5.0   | 6.3   | 9.0   | ns |

| RSRC   | RxOUT Setup to RxCLK OUT (Figure 5)                                   |            | 4.5   | 7.3   |       | ns |

| RHRC   | RxOUT Hold to RxCLK OUT (Figure 5)                                    |            | 4.0   | 6.3   |       | ns |

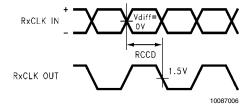

| RCCD   | RxCLK IN to RxCLK OUT Delay @ 25°C, V <sub>CC</sub> = 3.3V (Figure 6) |            |       | 5.0   | 7.5   | ns |

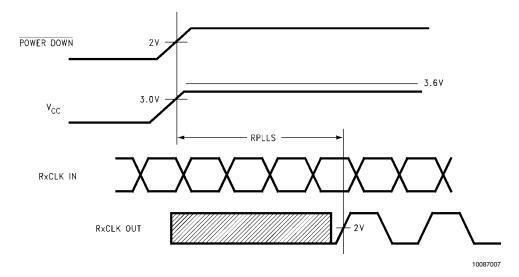

| RPLLS  | Receiver Phase Lock Loop Set (Figure 7)                               |            |       |       | 10    | ms |

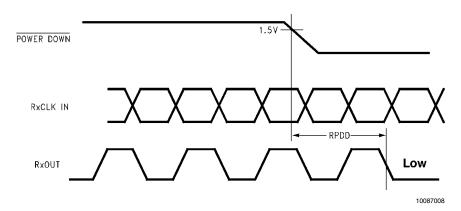

| RPDD   | Receiver Power Down Delay (Figure 10 )                                |            |       |       | 1     | μs |

Note 4: Receiver Skew Margin is defined as the valid data sampling region at the receiver inputs. This margin takes into account the DS90C383B transmitter pulse positions (min and max) and the receiver input setup and hold time (internal data sampling window - RSPos). The RSKM will change when different transmitters are used. This margin allows for LVDS interconnect skew, inter-symbol interference (both dependent on type/length of cable), and clock jitter (less than 250 ps).

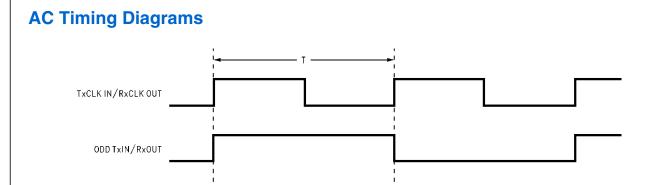

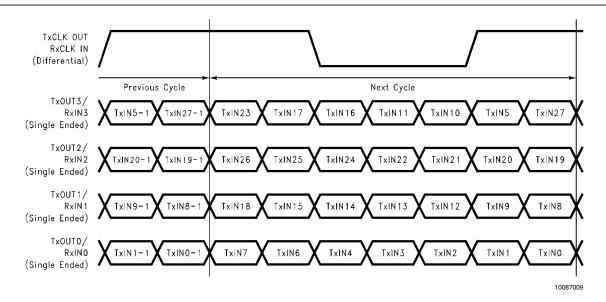

EVEN TxIN/RxOUT

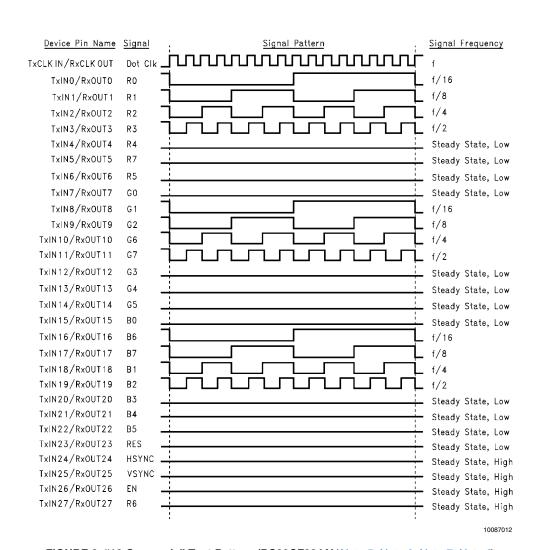

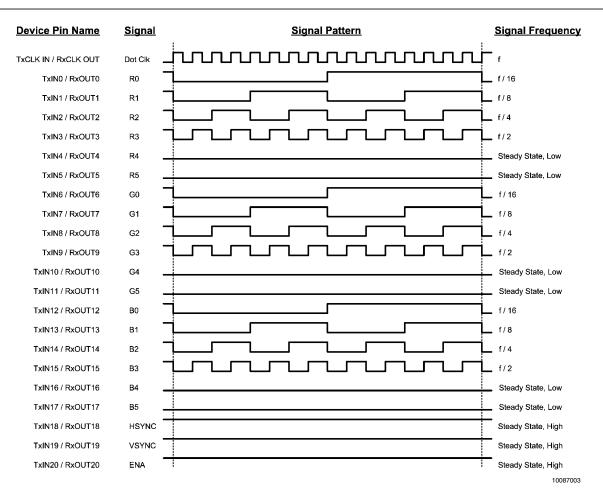

FIGURE 1. "Worst Case" Test Pattern

10087002

FIGURE 2. "16 Grayscale" Test Pattern (DS90CF384A)(Note 5, Note 6, Note 7, Note 8)

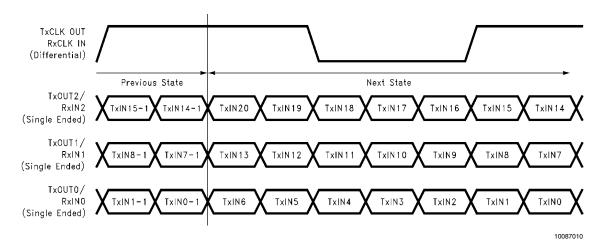

FIGURE 3. "16 Grayscale" Test Pattern (DS90CF364A)(Note 5, Note 6, Note 7, Note 8)

Note 5: The worst case test pattern produces a maximum toggling of digital circuits, LVDS I/O and CMOS/TTL I/O.

Note 6: The 16 grayscale test pattern tests device power consumption for a "typical" LCD display pattern. The test pattern approximates signal switching needed to produce groups of 16 vertical stripes across the display.

Note 7: Figures 1, 3 show a falling edge data strobe (TxCLK IN/RxCLK OUT).

Note 8: Recommended pin to signal mapping. Customer may choose to define differently.

FIGURE 4. DS90CF384A/DS90CF364A (Receiver) CMOS/TTL Output Load and Transition Times

FIGURE 5. DS90CF384A/DS90CF364A (Receiver) Setup/Hold and High/Low Times

FIGURE 6. DS90CF384A/DS90CF364A (Receiver) Clock In to Clock Out Delay

FIGURE 7. DS90CF384A/DS90CF364A (Receiver) Phase Lock Loop Set Time

6

FIGURE 8. 28 Parallel TTL Data Inputs Mapped to LVDS Outputs - DS90CF384A

FIGURE 9. 21 Parallel TTL Data Inputs Mapped to LVDS Outputs - DS90CF364A

FIGURE 10. DS90CF384A/DS90CF364A (Receiver) Power Down Delay

FIGURE 11. DS90CF384A (Receiver) LVDS Input Strobe Position

8

FIGURE 12. DS90CF364A (Receiver) LVDS Input Strobe Position

10087011

C—Setup and Hold Time (Internal data sampling window) defined by Rspos (receiver input strobe position) min and max Tppos—Transmitter output pulse position (min and max)

RSKM = Cable Skew (type, length) + Source Clock Jitter (cycle to cycle) + ISI (Inter-symbol interference)

Cable Skew—typically 10 ps-40 ps per foot, media dependent

Note 9: Cycle-to-cycle jitter is less than 250 ps at 65 MHz.

Note 10: ISI is dependent on interconnect length; may be zero.

FIGURE 13. Receiver LVDS Input Skew Margin

# DS90CF384A Pin Descriptions — 56L TSSOP Package — 24-Bit FPD Link Receiver

| Pin Name             | I/O | No. | Description                                                                                                                                               |

|----------------------|-----|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| RxIN+                | ı   | 4   | Positive LVDS differential data inputs.                                                                                                                   |

| RxIN-                | I   | 4   | Negative LVDS differential data inputs.                                                                                                                   |

| RxOUT                | 0   | 28  | TTL level data outputs. This includes: 8 Red, 8 Green, 8 Blue, and 3 control lines—FPLINE, FPFRAME, DRDY (also referred to as HSYNC, VSYNC, Data Enable). |

| RxCLK IN+            | I   | 1   | Positive LVDS differential clock input.                                                                                                                   |

| RxCLK IN-            | I   | 1   | Negative LVDS differential clock input.                                                                                                                   |

| RxCLK OUT            | 0   | 1   | TTL level clock output. The falling edge acts as data strobe.                                                                                             |

| PWR DOWN             | ı   | 1   | TTL level input. When asserted (low input) the receiver outputs are low.                                                                                  |

| V <sub>CC</sub>      | ı   | 4   | Power supply pins for TTL outputs.                                                                                                                        |

| GND                  | ı   | 5   | Ground pins for TTL outputs.                                                                                                                              |

| PLL V <sub>CC</sub>  | I   | 1   | Power supply for PLL.                                                                                                                                     |

| PLL GND              | T   | 2   | Ground pin for PLL.                                                                                                                                       |

| LVDS V <sub>CC</sub> | I   | 1   | Power supply pin for LVDS inputs.                                                                                                                         |

| LVDS GND             | ı   | 3   | Ground pins for LVDS inputs.                                                                                                                              |

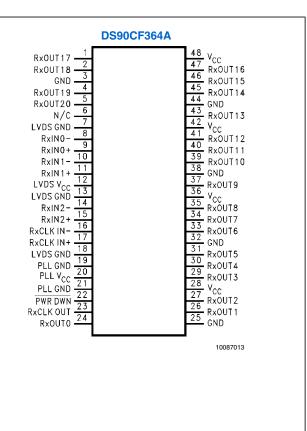

# DS90CF364A Pin Descriptions — 48L TSSOP Package — 18-Bit FPD Link Receiver

| Pin Name             | I/O | No. | Description                                                                                         |  |  |

|----------------------|-----|-----|-----------------------------------------------------------------------------------------------------|--|--|

| RxIN+                | I   | 3   | Positive LVDS differential data inputs.                                                             |  |  |

| RxIN-                | ı   | 3   | Negative LVDS differential data inputs.                                                             |  |  |

| RxOUT                | 0   | 21  | TTL level data outputs. This includes: 6 Red, 6 Green, 6 Blue, and 3 control lines—FPLINE, FPFRAME, |  |  |

|                      |     |     | DRDY (also referred to as HSYNC, VSYNC, Data Enable).                                               |  |  |

| RxCLK IN+            | Ι   | 1   | Positive LVDS differential clock input.                                                             |  |  |

| RxCLK IN-            | Ι   | 1   | Negative LVDS differential clock input.                                                             |  |  |

| RxCLK OUT            | 0   | 1   | TTL level clock output. The falling edge acts as data strobe.                                       |  |  |

| PWR DOWN             | Ι   | 1   | TTL level input. When asserted (low input) the receiver outputs are low.                            |  |  |

| V <sub>CC</sub>      | Ι   | 4   | Power supply pins for TTL outputs.                                                                  |  |  |

| GND                  | I   | 5   | Ground pins for TTL outputs.                                                                        |  |  |

| PLL V <sub>CC</sub>  | Ι   | 1   | Power supply for PLL.                                                                               |  |  |

| PLL GND              | Ι   | 2   | Ground pin for PLL.                                                                                 |  |  |

| LVDS V <sub>CC</sub> | _   | 1   | Power supply pin for LVDS inputs.                                                                   |  |  |

| LVDS GND             | I   | 3   | Ground pins for LVDS inputs.                                                                        |  |  |

|                      |     |     |                                                                                                     |  |  |

### **Pin Diagram for TSSOP Packages**

#### **DS90CF384A** 56 V<sub>CC</sub> 55 RxOUT21 RxOUT20 RxOUT22 -2 RxOUT23 -RxOUT24 -53 RxOUT19 4 GND -52 GND 51 RxOUT18 RxOUT25 6 RxOUT26 -50 RxOUT17 RxOUT27 -8 49 RxOUT16 LVDS GND -48 V<sub>CC</sub> 47 RxOUT15 46 RxOUT14 45 RxOUT13 RxIN0 - 10 RxINO+ 11 RxIN1-RXIN 1 - 12 RXIN 1 + 13 RXIN 1 13 LVDS V<sub>CC</sub> 14 LVDS GND 15 RXIN2 - 16 44 GND 43 RXOUT12 RxOUT11 41 RXOUT11 40 V<sub>CC</sub> 39 RXOUT9 38 RXOUT9 36 RXOUT7 36 RXOUT7 37 RXOUT7 38 RXOUT6 37 RXOUT6 38 RXOUT6 37 RXOUT6 41 $\begin{array}{c} R \times IN2 + \frac{16}{17} \\ R \times CLKIN - \frac{16}{17} \end{array}$ RxCLKIN- 18 RxCLKIN+ 19 RXIN3 - 19 RXIN3 + 20 LVDS GND 21 PLL GND 22 PLL Voc 23 PLL GND - 23 PLL VCC 24 PLL GND 25 PWR DWN 26 RxCLK OUT 27 P>OUT 0 28 - RxOUT5 33 RxOUT4 32 RXOUT3 31 V<sub>CC</sub> 30 RxOUT2 29 RxOUT1 RXOUTO 27 GND 28

10087023

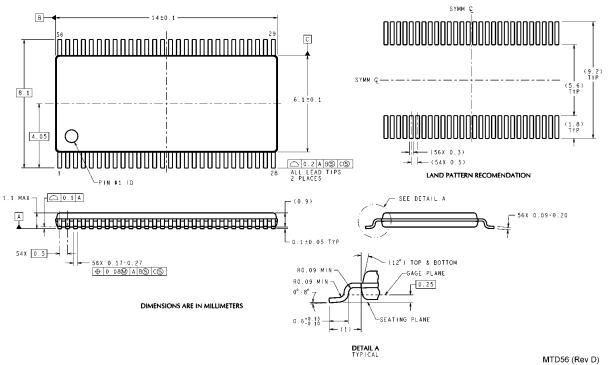

#### Physical Dimensions inches (millimeters) unless otherwise noted

56-Lead Molded Thin Shrink Small Outline Package, JEDEC Dimensions shown in millimeters only Order Number DS90CF384AMTD NS Package Number MTD56

#### **Notes**

For more National Semiconductor product information and proven design tools, visit the following Web sites at: www.national.com

| Pr                             | oducts                       | Design Support                  |                                |  |

|--------------------------------|------------------------------|---------------------------------|--------------------------------|--|

| Amplifiers                     | www.national.com/amplifiers  | WEBENCH® Tools                  | www.national.com/webench       |  |

| Audio                          | www.national.com/audio       | App Notes                       | www.national.com/appnotes      |  |

| Clock and Timing               | www.national.com/timing      | Reference Designs               | www.national.com/refdesigns    |  |

| Data Converters                | www.national.com/adc         | Samples                         | www.national.com/samples       |  |

| Interface                      | www.national.com/interface   | Eval Boards                     | www.national.com/evalboards    |  |

| LVDS                           | www.national.com/lvds        | Packaging                       | www.national.com/packaging     |  |

| Power Management               | www.national.com/power       | Green Compliance                | www.national.com/quality/green |  |

| Switching Regulators           | www.national.com/switchers   | Distributors                    | www.national.com/contacts      |  |

| LDOs                           | www.national.com/ldo         | Quality and Reliability         | www.national.com/quality       |  |

| LED Lighting                   | www.national.com/led         | Feedback/Support                | www.national.com/feedback      |  |

| Voltage References             | www.national.com/vref        | Design Made Easy                | www.national.com/easy          |  |

| PowerWise® Solutions           | www.national.com/powerwise   | Applications & Markets          | www.national.com/solutions     |  |

| Serial Digital Interface (SDI) | www.national.com/sdi         | Mil/Aero                        | www.national.com/milaero       |  |

| Temperature Sensors            | www.national.com/tempsensors | SolarMagic™                     | www.national.com/solarmagic    |  |

| PLL/VCO                        | www.national.com/wireless    | PowerWise® Design<br>University | www.national.com/training      |  |

THE CONTENTS OF THIS DOCUMENT ARE PROVIDED IN CONNECTION WITH NATIONAL SEMICONDUCTOR CORPORATION ("NATIONAL") PRODUCTS. NATIONAL MAKES NO REPRESENTATIONS OR WARRANTIES WITH RESPECT TO THE ACCURACY OR COMPLETENESS OF THE CONTENTS OF THIS PUBLICATION AND RESERVES THE RIGHT TO MAKE CHANGES TO SPECIFICATIONS AND PRODUCT DESCRIPTIONS AT ANY TIME WITHOUT NOTICE. NO LICENSE, WHETHER EXPRESS, IMPLIED, ARISING BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT.

TESTING AND OTHER QUALITY CONTROLS ARE USED TO THE EXTENT NATIONAL DEEMS NECESSARY TO SUPPORT NATIONAL'S PRODUCT WARRANTY. EXCEPT WHERE MANDATED BY GOVERNMENT REQUIREMENTS, TESTING OF ALL PARAMETERS OF EACH PRODUCT IS NOT NECESSARILY PERFORMED. NATIONAL ASSUMES NO LIABILITY FOR APPLICATIONS ASSISTANCE OR BUYER PRODUCT DESIGN. BUYERS ARE RESPONSIBLE FOR THEIR PRODUCTS AND APPLICATIONS USING NATIONAL COMPONENTS. PRIOR TO USING OR DISTRIBUTING ANY PRODUCTS THAT INCLUDE NATIONAL COMPONENTS, BUYERS SHOULD PROVIDE ADEQUATE DESIGN, TESTING AND OPERATING SAFEGUARDS.

EXCEPT AS PROVIDED IN NATIONAL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, NATIONAL ASSUMES NO LIABILITY WHATSOEVER, AND NATIONAL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY RELATING TO THE SALE AND/OR USE OF NATIONAL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

#### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS PRIOR WRITTEN APPROVAL OF THE CHIEF EXECUTIVE OFFICER AND GENERAL COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

Life support devices or systems are devices which (a) are intended for surgical implant into the body, or (b) support or sustain life and whose failure to perform when properly used in accordance with instructions for use provided in the labeling can be reasonably expected to result in a significant injury to the user. A critical component is any component in a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system or to affect its safety or effectiveness.

National Semiconductor and the National Semiconductor logo are registered trademarks of National Semiconductor Corporation. All other brand or product names may be trademarks or registered trademarks of their respective holders.

Copyright© 2011 National Semiconductor Corporation

For the most current product information visit us at www.national.com

National Semiconductor Americas Technical Support Center Email: support@nsc.com Tel: 1-800-272-9959 National Semiconductor Europe Technical Support Center Email: europe.support@nsc.com National Semiconductor Asia Pacific Technical Support Center Email: ap.support@nsc.com National Semiconductor Japan Technical Support Center Email: jpn.feedback@nsc.com