# Monolithic Peak Detector with Reset-and-Hold Mode

PKD01

#### **FEATURES**

Monolithic Design for Reliability and Low Cost High Slew Rate: 0.5 V/ $\mu$ s

**Low Droop Rate**

$T_A = 25^{\circ}\text{C}$ : 0.1 mV/ms  $T_A = 125^{\circ}\text{C}$ : 10 mV/ms Low Zero-Scale Error: 4 mV

Digitally Selected Hold and Reset Modes Reset to Positive or Negative Voltage Levels Logic Signals TTL and CMOS Compatible Uncommitted Comparator On-Chip

Available in Die Form

GENERAL DESCRIPTION

The PKD01 tracks an analog input signal until a maximum amplitude is reached. The maximum value is then retained as a peak voltage on a hold capacitor. Being a monolithic circuit the PKD01 offers significant performance and package density advantages over hybrid modules and discrete designs without sacrificing system versatility. The matching characteristics attained in a monolithic circuit provide inherent advantages when charge injection and droop rate error reduction are primary goals.

Innovative design techniques maximize the advantages of monolithic technology. Transconductance (g<sub>m</sub>) amplifiers were chosen over conventional voltage amplifier circuit building blocks. The g<sub>m</sub> amplifiers simplify internal frequency compensation, minimize acquisition time and maximize circuit accuracy. Their outputs are easily switched by low glitch current steering circuits. The steered outputs are clamped to reduce charge injection errors upon entering the hold mode or exiting the reset mode. The inherently low zero-scale error is further reduced by active Zener-Zap trimming to optimize overall accuracy.

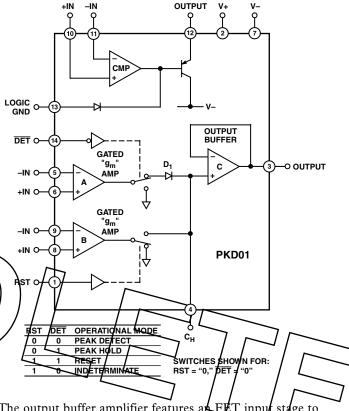

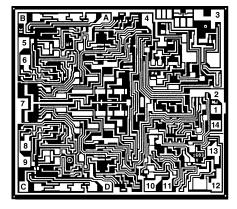

#### FUNCTIONAL BLOCK DIAGRAM

The output buffer amplifier features an FLT input stage to reduce droop rate error during lengthy peak hold periods. A bias current cancellation circuit minimizes droop error at high ambient temperatures.

Through the  $\overline{DET}$  control pin, new peaks may either be detected or ignored. Detected peaks are presented as positive output levels. Positive or negative peaks may be detected without additional active circuits, since Amplifier A can operate as an inverting or noninverting gain stage.

An uncommitted comparator provides many application options. Status indication and logic shaping/shifting are typical examples.

## REV. A

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

## **PKD01-SPECIFICATIONS**

## **ELECTRICAL CHARACTERISTICS** (@ $V_S = \pm 15$ V, $C_H = 1000$ pF, $T_A = 25$ °C, unless otherwise noted.)

|                                                                                                                                                                                                                                                                                        |                                                                                                    |                                                                                                                                                                                                                                                                                                 |                                 | PKD01A/E                                                             |                     |                                  | PKD01F                                                          |                                  |                                                              |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|----------------------------------------------------------------------|---------------------|----------------------------------|-----------------------------------------------------------------|----------------------------------|--------------------------------------------------------------|

| Parameter                                                                                                                                                                                                                                                                              | Symbol                                                                                             | Conditions                                                                                                                                                                                                                                                                                      | Min                             | Typ                                                                  | Max                 | Min                              | Typ                                                             | Max                              | Unit                                                         |

| g <sub>m</sub> AMPLIFIERS A, B Zero-Scale Error Input Offset Voltage Input Bias Current Input Offset Current Voltage Gain Open-Loop Bandwidth Common-Mode Rejection Ratio Power Supply Rejection Ratio Input Voltage Range <sup>1</sup> Slew Rate Feedthrough Error <sup>1</sup>       | $V_{ZS}$ $V_{OS}$ $I_{B}$ $I_{OS}$ $A_{V}$ $BW$ $CMRR$ $PSRR$ $V_{CM}$ $SR$                        | $R_{L} = 10 \text{ k}\Omega, V_{O} = \pm 10 \text{ V}$ $A_{V} = 1$ $-10 \text{ V} \leq V_{CM} \leq +10 \text{ V}$ $\pm 9 \text{ V} \leq V_{S} \leq \pm 18 \text{ V}$ $\Delta V_{IN} = 20 \text{ V}, \text{DET} = 1, \text{RST} = 0$                                                             | 18<br>80<br>86<br>±10           | 2<br>2<br>80<br>20<br>25<br>0.4<br>90<br>96<br>±11<br>0.5<br>80      | 4<br>3<br>150<br>40 | 10<br>74<br>76<br>±10            | 3<br>3<br>80<br>20<br>25<br>0.4<br>90<br>96<br>±11<br>0.5<br>80 | 7<br>6<br>250<br>75              | mV<br>mV<br>nA<br>nA<br>V/mV<br>MHz<br>dB<br>dB<br>V<br>V/µs |

| Acquisition Time to 0.1% Accuracy <sup>1</sup> Acquisition Time to 0.01% Accuracy <sup>1</sup>                                                                                                                                                                                         | t <sub>AQ</sub><br>t <sub>AQ</sub>                                                                 | 20 V Step, A <sub>VCL</sub> = +1<br>20 V Step, A <sub>VCL</sub> = +1                                                                                                                                                                                                                            |                                 | 41<br>45                                                             | 70                  |                                  | 41<br>45                                                        | 70                               | μs<br>μs                                                     |

| COMPARATOR Input Offset Voltage Input Bias Current Input Offset Current Voltage Cain Common-Mode Rejection Ratio Power Supply Rejection Ratio Input Voltage Range <sup>1</sup> Low Output Voltage "OFF" Output Leakage Current Output Short-Circuit Current Response Time <sup>2</sup> | PSRR<br>V <sub>M</sub><br>V <sub>OL</sub>                                                          | 2 k $\Omega$ Pull-Up Resistor to 5 V<br>10 V $\leq$ V <sub>CM</sub> $\leq$ 10 V<br>$\pm$ 9 V $\leq$ V $\leq$ $\pm$ 8 V<br>I <sub>SINK</sub> $\leq$ 5 mA. Logic GND = 0 V<br>V <sub>OUT</sub> $\leq$ V<br>V <sub>OUT</sub> $\leq$ 5 V<br>5 mV Overdrive, 2 k $\Omega$ Pull-Up<br>Resistor to 5 V | 5<br>82<br>#6<br>±11.5<br>-0.02 | 0.5<br>700<br>75<br>7.5<br>106<br>90<br>5 ±12.5<br>+0.15<br>25<br>12 |                     | 3.5<br>82<br>76<br>±11.5<br>-0.2 | 1<br>700<br>75<br>7.5<br>106<br>90<br>5 ±12.5<br>7<br>25<br>12  | 3<br>1000<br>300<br>5 +0.4<br>80 | mV<br>nA<br>nA<br>V/mV<br>dB<br>dB<br>V<br>V<br>uA<br>mlA    |

| DIGITAL INPUTS – RST, DET <sup>2</sup> Logic "1" Input Voltage Logic "0" Input Voltage Logic "1" Input Current Logic "0" Input Current                                                                                                                                                 | $egin{array}{c} V_{\mathrm{H}} \ V_{\mathrm{L}} \ I_{\mathrm{INH}} \ I_{\mathrm{INL}} \end{array}$ | $V_{H} = 3.5 \text{ V}$<br>$V_{L} = 0.4 \text{ V}$                                                                                                                                                                                                                                              | 2                               | 0.02                                                                 | 0.8<br>1<br>10      | 2                                | 0.02<br>1.6                                                     | 0.8<br>1<br>10                   | V<br>V<br>µA<br>µA                                           |

| MISCELLANEOUS Droop Rate <sup>3</sup>                                                                                                                                                                                                                                                  | $V_{\mathrm{DR}}$                                                                                  | $T_J = 25^{\circ}C$ $T_A = 25^{\circ}C$                                                                                                                                                                                                                                                         |                                 | 0.01<br>0.02                                                         | 0.07<br>0.15        |                                  | 0.01<br>0.03                                                    | 0.1<br>0.20                      | mV/ms<br>mV/ms                                               |

| Output Voltage Swing: Amplifier C Short-Circuit Current: Amplifier C Switch Aperture Time Switch Switching Time Slew Rate: Amplifier C                                                                                                                                                 | $V_{\mathrm{OP}}$ $I_{\mathrm{SC}}$ $t_{\mathrm{AP}}$ $t_{\mathrm{S}}$ $t_{\mathrm{S}}$            | $\overline{DET}$ = 1<br>$R_L$ = 2.5 k $\Omega$<br>$R_L$ = 2.5 k $\Omega$                                                                                                                                                                                                                        | ±11.5                           | 15<br>75<br>50<br>2.5                                                | 40                  | ±11                              | ±12 15 75 50 2.5                                                | 40                               | V<br>mA<br>ns<br>ns<br>V/μs                                  |

| Power Supply Current                                                                                                                                                                                                                                                                   | I <sub>SY</sub>                                                                                    | No Load                                                                                                                                                                                                                                                                                         | 1                               | 2.5<br>5                                                             | 7                   |                                  | 2.5<br>6                                                        | 9                                | mA                                                           |

NOTES

Specifications subject to change without notice.

<sup>&</sup>lt;sup>1</sup>Guaranteed by design.

$<sup>^{2}\</sup>overline{\text{DET}} = 1$ , RST = 0.

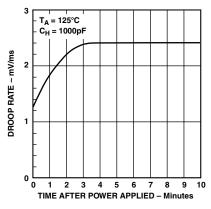

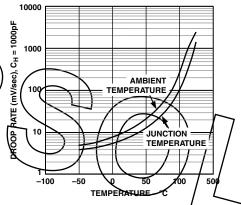

$<sup>^3</sup>$ Due to limited production test times, the droop current corresponds to junction temperature  $(T_J)$ . The droop current vs. time (after power-on) curve clarified this point. Since most devices (in use) are on for more than 1 second, ADI specifies droop rate for ambient temperature  $(T_A)$  also. The warmed-up  $(T_A)$  droop current specification is correlated to the junction temperature  $(T_J)$  value. ADI has a droop current cancellation circuit that minimizes droop current at high temperature. Ambient  $(T_A)$  temperature specifications are not subject to production testing.

PKD01

## **ELECTRICAL CHARACTERISTICS** (@ $V_S = \pm 15$ V, $C_H = 1000$ pF, $-55^{\circ}C \le T_A \le +125^{\circ}C$ for PKD01AY, $-25^{\circ}C \le T_A \le +85^{\circ}C$ for PKD01EY, PKD01EY, PKD01EY, PKD01EY, PKD01EP, PKD01EP, PKD01EP, Unless otherwise noted.)

|                                                                                                                                                                                                                                                                                                                         |                                                                                                                                      |                                                                                                                                                                                                                                                                                                                     | PKD01A/E                     |                                                                                          | PKD01F                                          |                                |                                                                 |                                                   |                                                                      |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|------------------------------------------------------------------------------------------|-------------------------------------------------|--------------------------------|-----------------------------------------------------------------|---------------------------------------------------|----------------------------------------------------------------------|

| Parameter                                                                                                                                                                                                                                                                                                               | Symbol                                                                                                                               | Conditions                                                                                                                                                                                                                                                                                                          | Min                          | Typ                                                                                      | Max                                             | Min                            | Typ                                                             | Max                                               | Unit                                                                 |

| "g <sub>m</sub> " AMPLIFIERS A, B Zero-Scale Error Input Offset Voltage Average Input Offset Drift <sup>1</sup> Input Bias Current Input Offset Current Voltage Gain Common-Mode Rejection Ratio Power Supply Rejection Ratio Input Voltage Range <sup>1</sup> Slew Rate Acquisition Time to 0.1% Accuracy <sup>1</sup> | $\begin{array}{c} V_{ZS} \\ V_{OS} \\ T_{C}V_{OS} \\ I_{B} \\ I_{OS} \\ A_{V} \\ CMRR \\ PSRR \\ V_{CM} \\ SR \\ t_{AQ} \end{array}$ | $R_L = 10 \text{ k}\Omega, V_O = \pm 10 \text{ V}$<br>-10 V \leq V_{CM} \leq +10 V<br>\pm 9 V \leq V_S \leq \pm 18 V<br>20 V Step, A <sub>VCL</sub> = +1                                                                                                                                                            | 7.5<br>74<br>80<br>±10       | $\begin{array}{c} 4\\ 3\\ -9\\ 160\\ 30\\ 9\\ 82\\ 90\\ \pm 11\\ 0.4\\ 60\\ \end{array}$ | 7<br>6<br>-24<br>250<br>100                     | 5<br>72<br>70<br>±10           | 6<br>5<br>-9<br>160<br>30<br>9<br>80<br>90<br>±11<br>0.4<br>60  | 12<br>10<br>-24<br>500<br>150                     | mV<br>mV<br>μV/°C<br>nA<br>nA<br>V/mV<br>dB<br>dB<br>V<br>V/μs<br>μs |

| COMPARATOR Input Offset Voltage Average Input Offset Drift¹ Input Bias Current Input Offset Current Voltage Gain Common-Mode Rejection Ratio Power Supply Rejection Ratio Input Voltage Range¹ Low Output Voltage OFF Output Lealage Current Output Short-Circuit Current Response Time                                 | Vos<br>TCVos<br>I <sub>B</sub><br>I <sub>OS</sub><br>A <sub>V</sub><br>CMRR<br>PSRR<br>Vos<br>I <sub>S</sub>                         | $2 \text{ k}\Omega \text{ Pull-Up Resistor to 5 V}$ $-10 \text{ V} \leq \text{V}_{\text{CM}} \leq +10 \text{ V}$ $\pm 9 \text{ V} \leq \text{V}_{\text{S}} \leq \pm 18 \text{ V}$ $\downarrow$ | 4<br>80<br>72<br>±11<br>-0.2 | 100<br>6.5<br>100<br>82                                                                  | 2.5<br>-6<br>2000<br>600<br>5 +0.4<br>100<br>45 | 2.5<br>80<br>72<br>±11<br>-0.2 | 2<br>-4<br>1100<br>100<br>6.5<br>92<br>86<br>+0.15<br>100<br>10 | 5<br>-6<br>2000<br>600<br>5<br>5+0.4<br>180<br>45 | mV<br>μV/°C<br>nA<br>nA<br>V/mV<br>dB<br>dB<br>V<br>V<br>μA<br>mA    |

| DIGITAL INPUTS – RST, DET <sup>2</sup> Logic "1" Input Voltage Logic "0" Input Voltage Logic "1" Input Current Logic "0" Input Current MISCELLANEOUS Droop Rate <sup>3</sup>                                                                                                                                            | V <sub>H</sub> V <sub>L</sub> I <sub>INH</sub> I <sub>INL</sub>                                                                      | $V_H = 3.5 \text{ V}$ $V_L = 0.4 \text{ V}$ $T_J = \text{Max Operating Temp.}$ $T_A = \text{Max Operating Temp.}$                                                                                                                                                                                                   | 2                            | 0.02<br>2.5                                                                              | 0.8                                             | 72                             | 0.02                                                            | 0.8<br>1<br>15<br>15                              | μΑ<br>μΑ<br>mV/ms                                                    |

| Output Voltage Swing Amplifier C Short-Circuit Current Amplifier C Switch Aperture Time Slew Rate: Amplifier C Power Supply Current                                                                                                                                                                                     | $V_{OP}$ $I_{SC}$ $t_{AP}$ $SR$ $I_{SY}$                                                                                             | $\overline{DET}$ = 1 $R_L$ = 2.5 k $\Omega$ $R_L$ = 2.5 k $\Omega$ No Load                                                                                                                                                                                                                                          | ±11<br>6                     | 2.4<br>±12<br>12<br>75<br>2<br>5.5                                                       | <ul><li>20</li><li>40</li><li>8</li></ul>       | ±10.5                          | 6<br>5 ±12<br>12<br>75<br>2<br>6.5                              | <ul><li>20</li><li>40</li><li>10</li></ul>        | mV/ms V mA ns V/µs mA                                                |

## NOTES

Specifications subject to change without notice.

<sup>&</sup>lt;sup>1</sup>Guaranteed by design.

$<sup>^{2}\</sup>overline{\text{DET}} = 1$ , RST = 0.

$<sup>^3</sup>$ Due to limited production test times, the droop current corresponds to junction temperature  $(T_J)$ . The droop current vs. time (after power-on) curve clarifies this point. Since most devices (in use) are on for more than 1 second, ADI specifies droop rate for ambient temperature  $(T_A)$  also. The warmed-up  $(T_A)$  droop current specification is correlated to the junction temperature  $(T_J)$  value. ADI has a droop current cancellation circuit that minimizes droop current at high temperature. Ambient  $(T_A)$  temperature specifications are not subject to production testing.

### ABSOLUTE MAXIMUM RATINGS1,2

| Supply Voltage                                    |

|---------------------------------------------------|

| Input Voltage Equal to Supply Voltage             |

| Logic and Logic Ground                            |

| Voltage Equal to Supply Voltage                   |

| Output Short-Circuit Duration Indefinite          |

| Amplifier A or B Differential Input Voltage ±24 V |

| Comparator Differential Input Voltage ±24 V       |

| Comparator Output Voltage                         |

| Equal to Positive Supply Voltage                  |

| Hold Consister Short Circuit Dynation Indefinite  |

Hold Capacitor Short-Circuit Duration . . . . . Indefinite Lead Temperature (Soldering, 60 sec) ........... 300°C Storage Temperature Range

PKD01AY, PKD01EY, PKD01FY ..... -65°C to +150°C PKD01EP, PKD01FP ..... -65°C to +125°C

Operating Temperature Range

PKD01AY ..... -55°C to +125°C PKD01EY, PKD01FY ..... -25°C to +85°C PKD01EP, PKD01FP ...... 0°C to 70°C Junction Temperature ..... -65°C to +150°C

NOTES

apply to both DICE and packaged parts, unless <sup>1</sup>Absolute/maximum raxings e noted. otherw

<sup>2</sup>Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those listed in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability

## THERMAL CHARACTERISTIC

| Package Type             | $\theta_{\mathrm{JA}}$ * | $\theta_{\rm JC}$ | Unit ' |

|--------------------------|--------------------------|-------------------|--------|

| 14-Lead Hermetic DIP (Y) | 99                       | 12                | °C/W   |

| 14-Lead Plastic DIP (P)  | 76                       | 33                | °C/W   |

<sup>\*</sup> $\theta_{IA}$  is specified for worst-case mounting conditions, i.e.,  $\theta_{IA}$  is specified for device in socket for cerdip and PDIP packages.

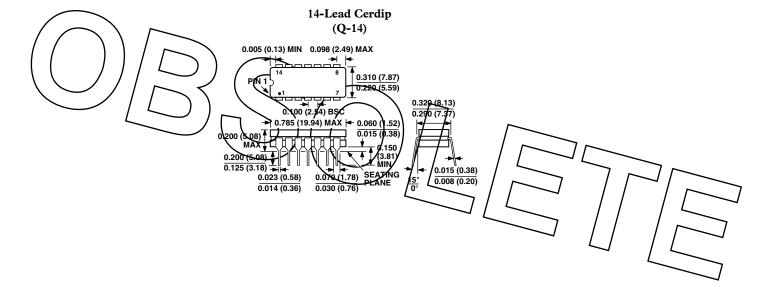

#### ORDERING GUIDE<sup>1</sup>

| Model <sup>2</sup> | Temperature<br>Range | Package<br>Description | Package<br>Option |

|--------------------|----------------------|------------------------|-------------------|

| PKD01AY            | −55°C to +85°C       | Cerdip                 | Q-14              |

| PKD01EY            | −25°C to +85°C       | Cerdip                 | Q-14              |

| PKD01FY            | −25°C to +85°C       | Cerdip                 | Q-14              |

| PKD01EP            | 0°C to 70°C          | Plastic DIP            | N-14              |

| PKD01FP            | 0°C to 70°C          | Plastic DIP            | N-14              |

#### NOTES

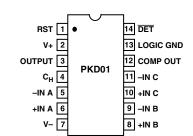

#### PIN CONFIGURATION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the human body and test equipment and can discharge without detection. Although the PKD01 features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high-energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality.

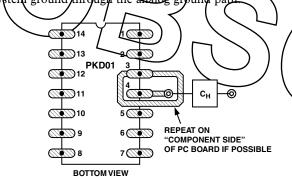

## DICE CHARACTERISTICS

- 1. RST (RESET CONTROL)

- 2. V+

- 3. OUTPUT

- CH (HOLD CAPACITOR)

- 5. INVERTING INPUT (A)

6. NONINVERTING INPUT (A)

- 8. NONINVERTING INPUT (B)

- 9. INVERTING INPUT (B)

10. COMPARATOR NONINVERTING INPUT

- 11. COMPARATOR INVERTING INPUT

- 12. COMPARATOR OUTPUT

- 13. LOGIC GROUND

- DET (PEAK DETECT CONTROL) 14.

- A, B (A) NULL C, D (B) NULL

DIE SIZE 0.090 × 0.100 INCH, 9000 SQ. MILS (2.286 × 2.54mm, 5.8 SQ. mm)

FOR ADDITIONAL DICE INFORMATION REFER TO 1986 DATA BOOK, SECTION 2.

<sup>&</sup>lt;sup>1</sup>Burn-in is available on commercial and industrial temperature range parts in cerdip, plastic DIP, and TO-can packages.

<sup>&</sup>lt;sup>2</sup>For devices processed in total compliance to MIL-STD-883, add /883 after part number. Consult factory for 883 data sheet.

## WAFER TEST LIMITS (@ $V_S = \pm 15$ V, $C_H = 1000$ pF, $T_A = 25^{\circ}$ C, unless otherwise noted.)

| Parameter                                     | Symbol                 | Conditions                                                                                                                   | PKD01N<br>Limit | Unit          |

|-----------------------------------------------|------------------------|------------------------------------------------------------------------------------------------------------------------------|-----------------|---------------|

| "g <sub>m</sub> " AMPLIFIERS A, B             |                        |                                                                                                                              |                 |               |

| Zero-Scale Error                              | $V_{ZS}$               |                                                                                                                              | 7               | mV max        |

| Input Offset Voltage                          | Vos                    |                                                                                                                              | 6               | mV max        |

| Input Bias Current                            | I <sub>B</sub>         |                                                                                                                              | 250             | nA max        |

| Input Offset Current                          | 1                      |                                                                                                                              | 75              | nA max        |

| Voltage Gain                                  | Ios                    | $R_L = 10 \text{ k}\Omega, V_O = \pm 10 \text{ V}$                                                                           | 10              | V/mV min      |

| Common-Mode Rejection Ratio                   | A <sub>V</sub><br>CMRR |                                                                                                                              | 74              | dB min        |

| Power Supply Rejection Ratio                  | PSRR                   | $-10 \text{ V} \le \text{V}_{\text{CM}} \le +10 \text{ V}$<br>$\pm 9 \text{ V} \le \text{V}_{\text{S}} \le \pm 18 \text{ V}$ | 76              | dB min        |

|                                               |                        | $\pm 9 \text{ V} \leq \text{V}_{\text{S}} \leq \pm 10 \text{ V}$                                                             | ±11.5           | V min         |

| Input Voltage Range <sup>1</sup>              | $V_{CM}$               | AV - 20 V DET - 1 DET - 0                                                                                                    |                 | ,             |

| Feedthrough Error                             |                        | $\Delta V_{IN} = 20 \text{ V}, \overline{DET} = 1, RST = 0$                                                                  | 66              | dB min        |

| COMPARATOR                                    |                        |                                                                                                                              |                 |               |

| Input Offset Voltage                          | Vos                    |                                                                                                                              | 3               | mV max        |

| Input Bias Current                            | $I_{\rm B}$            |                                                                                                                              | 1000            | nA max        |

| Input Offset Current                          | Ios                    |                                                                                                                              | 300             | nA max        |

| Voltag <del>e G</del> ain <sup>1</sup>        | $A_{V}$                | 2 kΩ Pull-Up Resistor to 5 V                                                                                                 | 3.5             | V/mV min      |

| Common-Mode Rejection Ratio                   | CMRR                   | $-10 \text{ V} \le \text{V}_{\text{CM}} \le +10 \text{ V}$                                                                   | 82              | dB min        |

| Yower Supply Rejection Ratio                  | PSRR                   | $\pm 9 \text{ V} \le \text{V}_{\text{S}} \le \pm 18 \text{ V}$                                                               | 76              | dB min        |

| Input Voltage Range                           | V <sub>CM</sub>        |                                                                                                                              | ±11.5           | V min         |

| Low Output Wolfage ( )                        | Vol                    | $I_{SINK} \le 5$ mA, Logic GND = 5 V                                                                                         | 0.4             | V max         |

|                                               |                        | SINK S S S S S S S S S S S S S S S S S S S                                                                                   | -0.2            | V min         |

| "OFF" Output Leakage Current                  |                        | $V_{OUT} = 5 V$                                                                                                              | 80              | μA max        |

| Output Short-Circuit Current                  | T <sub>SC</sub>        | V <sub>OUT</sub> = 5 V                                                                                                       | 45              | mA min        |

| o unput onort on put ou                       | 1,20/                  |                                                                                                                              | 7               | mA min        |

| Diametria number nom See 2                    | ackslash               |                                                                                                                              |                 |               |

| DIGITAL INPUTS-RST, $\overline{\text{DET}}^2$ |                        |                                                                                                                              | $\square$       |               |

| Logic "1" Input Voltage                       | $V_{\mathrm{H}}$       |                                                                                                                              |                 | Vmin          |

| Logic "0" Input Voltage                       | $V_{\rm L}$            |                                                                                                                              | 7 0.8 / /       | V/m/ax        |

| Logic "1" Input Current                       | $I_{INH}$              | $V_{\rm H} = 3.5  \text{V}$                                                                                                  | † 1 <i>   </i>  | μA/max        |

| Logic "0" Input Current                       | I <sub>INL</sub>       | $V_L = 0.4 \text{ V}$                                                                                                        | 10 /            | μAmak         |

| MISCELLANEOUS                                 |                        |                                                                                                                              | 7 //            |               |

| Droop Rate <sup>3</sup>                       | $V_{DR}$               | $T_{I} = 25^{\circ}C,$                                                                                                       | 0.1 🛴 /         | nV/ms max     |

| •                                             |                        | $T_A^J = 25^{\circ}C$                                                                                                        | 0.20            | mV/ms max     |

| Output Voltage Swing Amplifier C              | $V_{OP}$               | $R_L = 2.5 \text{ k}\Omega$                                                                                                  | ±11             | V min         |

| Short-Circuit Current Amplifier C             | I <sub>SC</sub>        | E                                                                                                                            | 40              | mA max        |

|                                               | -3C                    |                                                                                                                              | 7               | mA min        |

| Power Supply Current                          | $I_{SY}$               | No Load                                                                                                                      | 9               | mA max        |

|                                               | 31                     |                                                                                                                              |                 |               |

| g <sub>m</sub> AMPLIFIERS A, B                | CD                     |                                                                                                                              | 0.5             | <b>17/110</b> |

| Slew Rate                                     | SR                     | 0.10/ A                                                                                                                      | 0.5             | V/μs          |

| Acquisition Time <sup>1</sup>                 | t <sub>A</sub>         | $0.1\%$ Accuracy, 20 V Step, $A_{VCL} = 1$                                                                                   | 41              | μs            |

|                                               | t <sub>A</sub>         | 0.01% Accuracy, 20 V Step, A <sub>VCL</sub> = 1                                                                              | 45              | μs            |

| COMPARATOR                                    |                        |                                                                                                                              |                 |               |

| Response Time                                 |                        | 5 mV Overdrive, 2 kΩ Pull-Up Resistor to 5 V                                                                                 | 150             | ns            |

| MISCELLANEOUS                                 |                        |                                                                                                                              |                 |               |

| Switch Aperture Time                          | t <sub>AP</sub>        |                                                                                                                              | 75              | ns            |

| Switching Time                                | t <sub>S</sub>         |                                                                                                                              | 50              | ns            |

| Buffer Slew Rate                              | SR                     | $R_L = 2.5 \text{ k}\Omega$                                                                                                  | 2.5             | V/μs          |

| NOTES                                         |                        | <u>L</u> <u>L</u> <u>-</u>                                                                                                   |                 | 1,100         |

#### NOTES

REV. A -5-

<sup>&</sup>lt;sup>1</sup>Guaranteed by design.

$<sup>^{2}\</sup>overline{\text{DET}} = 1$ , RST = 0.

<sup>&</sup>lt;sup>3</sup>Due to limited production test times, the droop current corresponds to junction temperature  $(T_J)$ . The droop current vs. time (after power-on) curve clarifies this point. Since most devices (in use) are on for more than 1 second, ADI specifies droop rate for ambient temperature  $(T_A)$  also. The warmed-up  $(T_A)$  droop current specification is correlated to the junction temperature  $(T_J)$  value. ADI has a droop current cancellation circuit that minimizes droop current at high temperature. Ambient  $(T_A)$  temperature specifications are not subject to production testing.

## **PKD01—Typical Performance Characteristics**

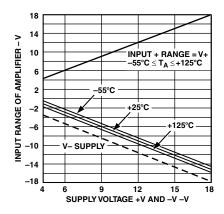

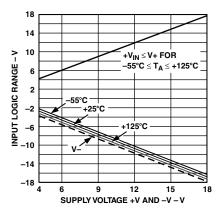

TPC 1. A and B Input Range vs. Supply Voltage

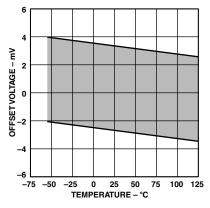

TPC 2. A and B Amplifiers Offset Voltage vs. Temperature

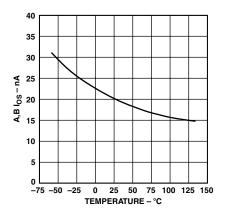

TPC 3. A, B  $I_{OS}$  vs. Temperature

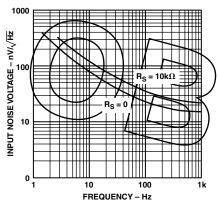

TPC 4. Input Spot Noise vs. Frequency

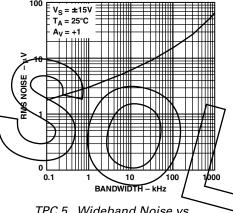

TPC 5. Wideband Noise vs. Bandwidth

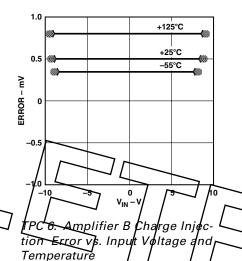

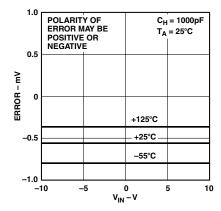

TPC 7. Amplifier A Charge Injection Error vs. Input Voltage and Temperature

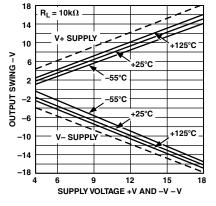

TPC 8. Output Voltage Swing vs. Supply Voltage (Dual Supply Operation)

TPC 9. Output Voltage vs. Load Resistance

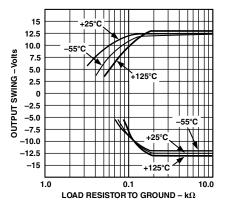

TPC 10. Output Error vs. Frequency and Input Voltage

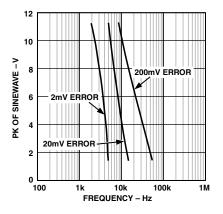

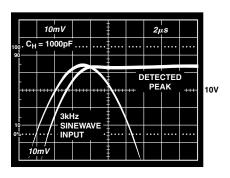

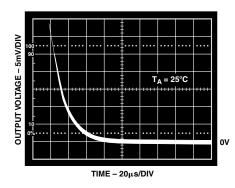

TPC 11. Settling Response

TPC 12. Settling Response

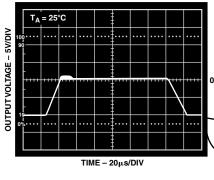

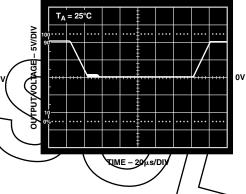

TPC 13. Large-Signal Inverting Response

TPC 14. Large-Signal Noninverting Response

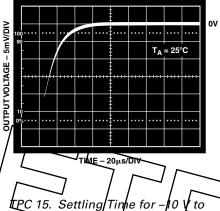

TPC 15. Settling|Tinhe for 0 V Step Input

TPC 16. Settling Time for +10 V to 0 V Step Input

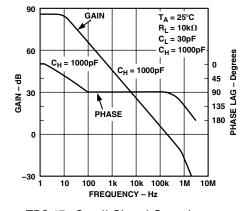

TPC 17. Small-Signal Open-Loop Gain/Phase vs. Frequency

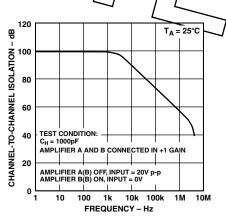

TPC 18. Channel-to-Channel Isolation vs. Frequency

REV. A -7-

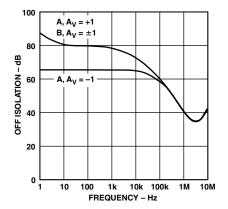

TPC 19. Off Isolation vs. Frequency

TPC 20. Droop Rate vs. Time after Power On

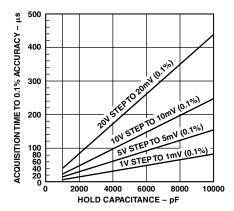

TPC 21. Acquisition Time vs. External Hold Capacitor and Acquisition Step

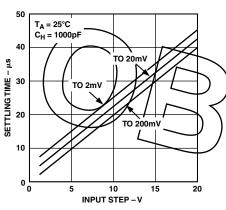

TPC 22. Acquisition Time vs. Input Voltage Step Size

TPC 23. Droop Rate vs. Temperature

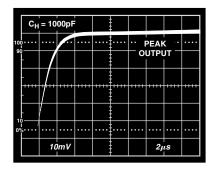

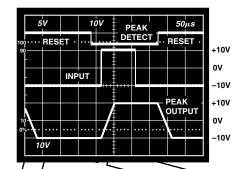

TPC 24. Acquisition of Step Inpu

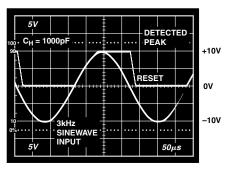

TPC 25. Acquisition of Sine Wave Peak

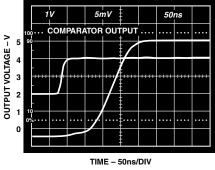

TPC 26. Comparator Output Response Time (2  $k\Omega$  Pull-Up Resistor,  $T_A = 25^{\circ}C$ )

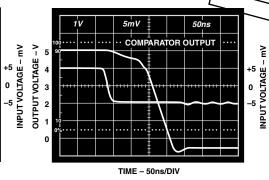

TPC 27. Comparator Output Response Time (2  $k\Omega$  Pull-Up Resistor,  $T_A = 25^{\circ}C$ )

TPC 28. Input Logic Range vs. Supply Voltage

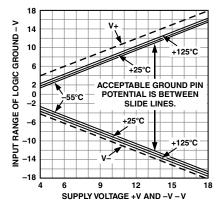

TPC 29. Input Range of Logic Ground vs. Supply Voltage

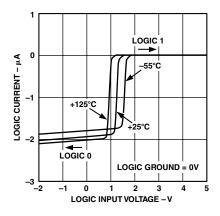

TPC 30. Logic Input Current vs. Logic Input Voltage

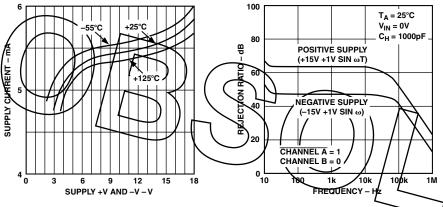

TPC 31. Supply Current vs. Supply Voltage

2

OFFSET VOLTAGE – mV

-2

-50

TPC 32. Hold Mode Power Supply Rejection vs. Frequency

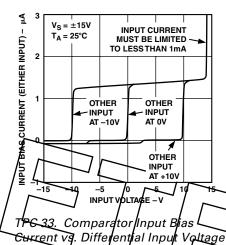

TPC 34. Comparator Offset Voltage vs. Temperature

-25 0 25 50 75 TEMPERATURE - °C

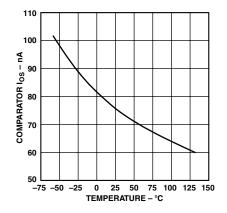

TPC 35. Comparator  $I_{OS}$  vs. Temperature

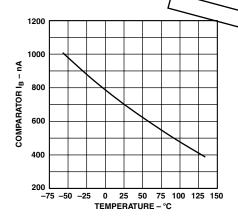

TPC 36. Comparator  $I_B$  vs. Temperature

REV. A -9-

100 125

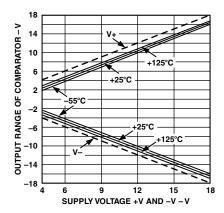

TPC 37. Output Swing of Comparator vs. Supply Voltage

TPC 38. Comparator Response Time vs. Temperature

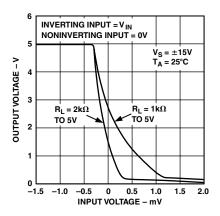

TPC 39. Comparator Transfer Characteristic

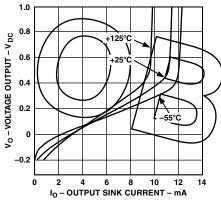

TPC 40. Comparator Output Voltage vs. Output Current and Temperature

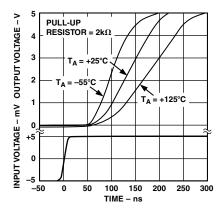

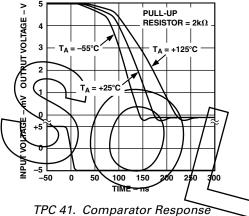

Time vs. Temperature

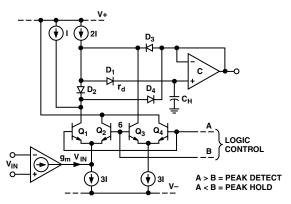

#### THEORY OF OPERATION

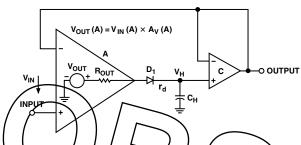

The typical peak detector uses voltage amplifiers and a diode or an emitter follower to charge the hold capacitor,  $C_H$ , indirectionally (see Figure 1). The output impedance of A plus  $D_1$ 's dynamic impedance,  $r_d$ , make up the resistance which determines the feedback loop pole. The dynamic impedance is

$$r_d = \frac{kT}{qI_d}$$

, where  $I_d$  is the capacitor charging current.

The pole moves toward the origin of the S plane as  $I_d$  goes to zero. The pole movement in itself will not significantly lengthen the acquisition time since the pole is enclosed in the system feedback loop.

igure 1. Conventional Voltage Amblifier Peak Detector

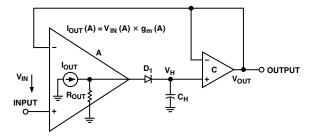

When the moving pole is considered with the typical frequency compensation of voltage amplifiers however, there is aloon stability problem. The necessary compensation can increase the required acquisition time. ADI's approach replace, the input voltage amplifier with a transconductance amplifier (see Figure 2).

The PKD01 transfer function can be reduced to:

$$\frac{V_{OUT}}{V_{IN}} = \frac{1}{1 + \frac{sC_H}{g_m} + \frac{1}{g_m R_{OUT}}} \approx \frac{1}{1 + \frac{sC_H}{g_m}}$$

where:  $g_m \approx 1 \,\mu\text{A/mV}$ ,  $R_{OUT} \approx 20 \,\text{M}\Omega$ .

The diode in series with A's output (see Figure 2) has no effect because it is a resistance in series with a current source. In addition to simplifying the system compensation, the input transconductance amplifier output current is switched by current steering. The steered output is clamped to reduce and match any charge injection.

Figure 2. Transconductance Amplifier Peak Detector

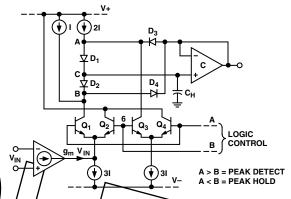

Figure 3 shows a simplified schematic of the reset  $g_m$  amplifier, B. In the track mode,  $Q_1$  and  $Q_4$  are ON and  $Q_2$  and  $Q_3$  are OFF. A current of 2I passes through  $D_1$ , I is summed at B and passes through  $Q_1$ , and is summed with  $g_mV_{IN}$ . The current sink can absorb only 3I, thus the current passing through  $D_2$  can

only be:  $2K - g_m V_{IN}$ . The net current into the hold capacitor node then, is  $g_m V_{IN} [I_H = 2I - (2I - g_m V_{IN})]$ . In the hold mode,  $Q_2$  and  $Q_3$  are ON while  $Q_1$  and  $Q_4$  are OFF. The net current into the top of  $D_1$  is –I until  $D_3$  turns ON. With  $Q_1$  OFF, the bottom of  $D_2$  is pulled up with a current I until  $D_4$  turns ON, thus,  $D_1$  and  $D_2$  are reverse biased by <0.6 V, and charge injection is independent of input level.

The monolithic layout results in points A and B having equal nodal capacitance. In addition, matched diodes  $D_1$  and  $D_2$  have equal diffusion capacitance. When the transconductance amplifier outputs are switched open, points A and B are ramped equally, but in opposite phase. Diode clamps  $D_3$  and  $D_4$  cause the swings to have equal amplitudes. The net charge injection (voltage change) at node C is therefore zero.

Figure \$. Transcorductance Amplifier with Low Glitch

Current Switch

The peak transconductance amplifier, A is shown in Figure 4. Unidirectional hold capacitor charging requires diode  $D_1$  to be connected in series with the output. Upon entering the peak hold mode  $D_1$  is reverse-biased. The voltage clamp limits charge injection to approximately 1 pC and the hold step to 0.0 mV.

Minimizing acquisition time dictates a small  $C_H$  capacitance. A 1000 pF value was selected. Droop rate was also minimized by providing the output buffer with an FET input stage. A current cancellation circuit further reduces droop current and minimizes the gate current's tendency to double for every  $10^{\circ}$  temperature change.

Figure 4. Peak Detecting Transconductance Amplifier with Switched Output

Downloaded from **Elcodis.com** electronic components distributor

### APPLICATIONS INFORMATION

### **Optional Offset Voltage Adjustment**

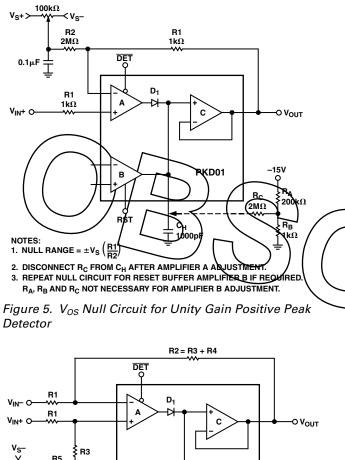

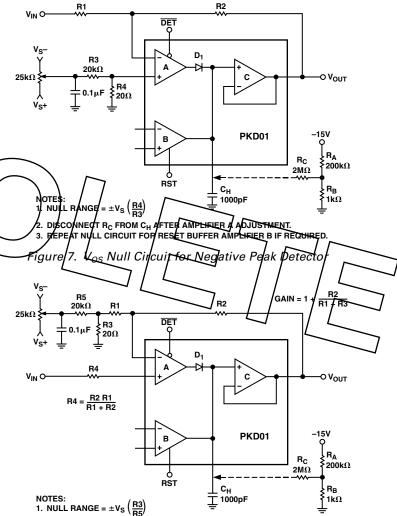

Offset voltage is the primary zero scale error component since a variable voltage clamp limits voltage excursions at D<sub>1</sub>'s anode and reduces charge injection. The PKD01 circuit gain and operational mode (positive or negative peak detection) determine the applicable null circuit. Figures 5 through 8 are suggested circuits. Each circuit also corrects amplifier C offset voltage error.

2. DISCONNECT  $\mathbf{R}_{\mathbf{C}}$  FROM  $\mathbf{C}_{\mathbf{H}}$  AFTER AMPLIFIER A ADJUSTMENT. 3. REPEAT NULL CIRCUIT FOR RESET BUFFER AMPLIFIER B IF REQUIRED.

RST

Figure 6. V<sub>OS</sub> Null Circuit for Differential Peak Detector

PKD01

$C_{H}$ ㅗ C<sub>H</sub> ㅗ 1000pF RΔ

200kΩ

1kΩ

$R_{C}$  2M $\Omega$

A. Nulling Gated Output  $g_m$  Amplifier A. Diode  $D_1$  must be conducting to close the feedback circuit during amplifier A  $V_{OS}$  adjustment. Resistor network  $R_A - R_C$  cause  $D_1$  to conduct slightly. With DET = 0 and  $V_{\rm IN}$  = 0 V, monitor the PKD01 output. Adjust the null potentiometer until  $V_{OUT} = 0 \text{ V}$ . After adjustment, disconnect R<sub>C</sub> from C<sub>H</sub>.

**B.** Nulling Gated  $g_m$  Amplifier B. Set Amplifier B signal input to  $V_{IN}$  = 0 V and monitor the PKD01 output. Set DET = 1, RST = 1 and adjust the null potentiometer for  $V_{OUT} = 0 \text{ V}$ . The circuit gain—inverting or noninverting—will determine which null circuit illustrated in Figures 5 through 8 is applicable.

- 2. DISCONNECT RC FROM  $C_{\rm H}$  AFTER AMPLIFIER A ADJUSTMENT. 3. REPEAT NULL CIRCUIT FOR RESET BUFFER AMPLIFIER B IF REQUIRED.

Figure 8. Vos Null Circuit for Positive Peak Detector with Gain

NOTES: 1. NULL RANGE =  $\pm V_S \left(\frac{R5}{R4}\right) \left(\frac{R1}{R1 + R3}\right)$

NOTES:

### PEAK HOLD CAPACITOR RECOMMENDATIONS

The hold capacitor (C<sub>H</sub>) serves as the peak memory element and compensating capacitor. Stable operation requires a minimum value of 1000 pF. Larger capacitors may be used to lower droop rate errors, but acquisition time will increase.

Zero scale error is internally trimmed for  $C_H = 1000$  pF. Other  $C_H$  values will cause a zero scale shift which can be approximated with the following equation.

$$\Delta V_{ZS}(mV) = \frac{1 \times 10^{3} (pC)}{C_{H}(nF)} - 0.6 \, mV$$

The peak hold capacitor should have very high insulation resistance and low dielectric absorption. For temperatures below 85°C, a polystyrene capacitor is recommended, while a Teflon capacitor is recommended for high temperature environments.

#### CAPACITOR GUARDING AND GROUND LAYOUT

Ground planes are recommended to minimize ground path resistance. Separate analog and digital grounds should be used. The two ground systems are tied together only at the common system ground. This avoids digital currents returning to the system ground through the analog ground path.

Figure 9. C<sub>H</sub> Terminal (Pin 4) Guarding. See Text.

The C<sub>H</sub> terminal (Pin 4) is a high impedance point. To minimize gain errors and maintain the PKD01's inherently low droop rate, guarding Pin 4 as shown in Figure 9 is recommended.

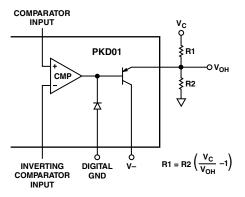

## **COMPARATOR**

The comparator output high level  $(V_{OH})$  is set by external resistors. It is possible to optimize noise immunity while interfacing to all standard logic families—TTL, DTL, and CMOS. Figure 10 shows the comparator output with external level-setting resistors. Table I gives typical R1 and R2 values for common circuit conditions.

The maximum comparator high output voltage  $(V_{\text{OH}})$  should be limited to:

$$V_{OH}$$

(maximum) < V+ -2.0 V

With the comparator in the low state  $(V_{OL})$ , the output stage will be required to sink a current approximately equal to  $V_C/R1$ .

Figure 10. Comparator Output with External Level-Setting Resistors

Table I.

|                |                 |                        |                        | _    | $V_{c}$                       |

|----------------|-----------------|------------------------|------------------------|------|-------------------------------|

| $\mathbf{v_c}$ | V <sub>OH</sub> | R1                     | R2                     | R:   | $1 \approx \frac{r}{I_{SIN}}$ |

| 5              | 3.5             | 2.7 kΩ                 | 6.2 kΩ                 |      |                               |

| 5              | 5.0             | $2.7 \text{ k}\Omega$  | $\infty$               | (    |                               |

| 15             | 3.5             | $4.7 \text{ k}\Omega$  | 1.5 kΩ                 |      | 1                             |

| 15             | 5.0             | $4.7~\mathrm{k}\Omega$ | $2.4 \text{ k}\Omega$  | R2 ≈ | $\overline{V_C}$              |

| 15             | 7.5             | 7.5 kΩ                 | $7.5~\mathrm{k}\Omega$ | ł    | $\frac{r_C}{V_{OH}}$          |

| 15             | 10.0            | 7.5 kΩ                 | 15 kΩ                  | '    | V OH                          |

|                |                 |                        |                        |      |                               |

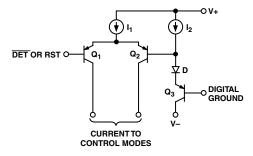

PEAK DETECTOR LOGIC CONTROL (RST, DET)

The transconductance amplifier outputs are controlled by the digital logic signals RST and DET. The PKD01 operational mode is selected by steering the current (L) through Q<sub>1</sub> and Q<sub>2</sub>, thus providing high-speed switching and a predictable logic threshold. The logic threshold voltage is 1.4 V when digital ground is at zero volts.

Other threshold voltages (V<sub>FH</sub>) may be selected by applying the formula:

$V_{TH} \approx 1.4 V + Digital Ground Potential$

For proper operation, digital ground must always be at least 3.5 V below the positive supply and 2.5 V above the negative supply. The RST or DET signal must always be at least 2.8 V above the negative supply.

Operating the digital ground at other than zero volts does influence the comparator output low voltage. The  $V_{\rm OL}$  level is referenced to digital ground and will follow any changes in digital ground potential:

$V_{OL} \approx 0.2 \ V + Digital \ Ground \ Potential.$

Figure 11. Logic Control

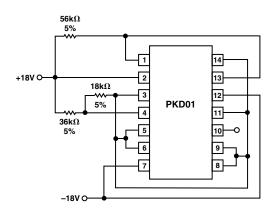

Figure 12. Burn-In Circuit

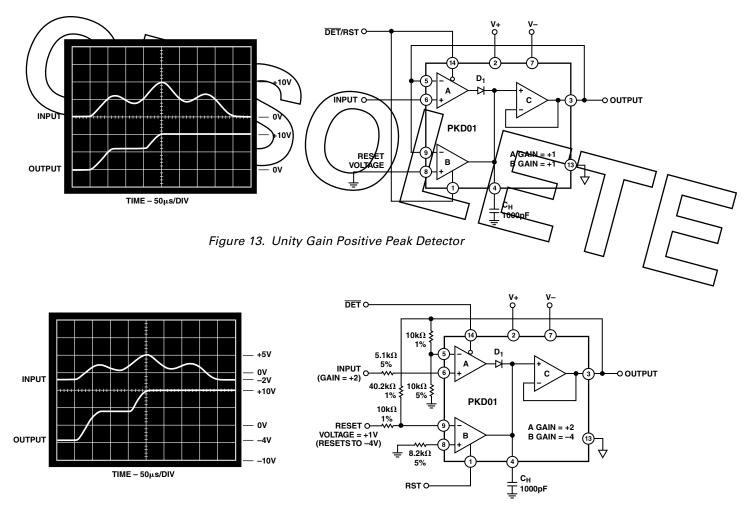

## **Typical Circuit Configurations**

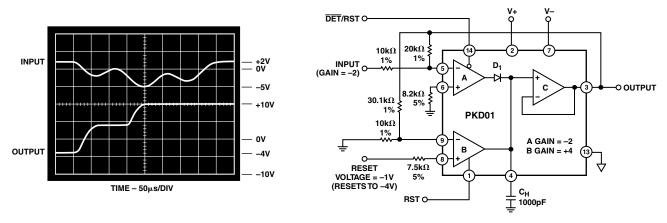

Figure 14. Positive Peak Detector with Gain

Figure 15. Negative Peak Detector with Gain

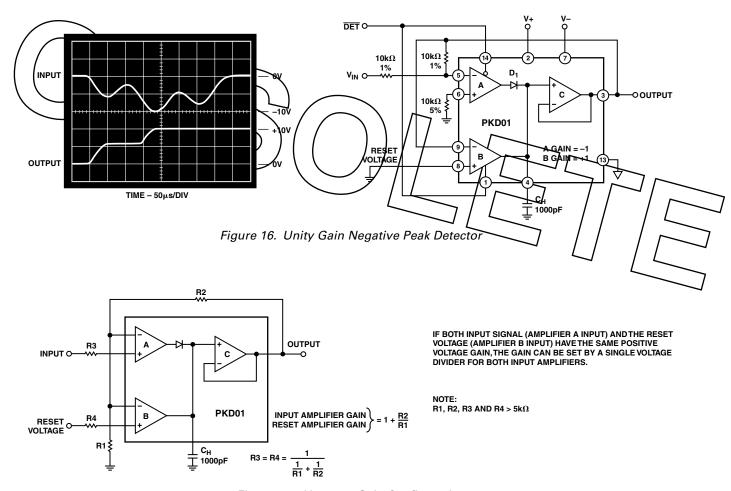

Figure 17. Alternate Gain Configuration

REV. A -15-

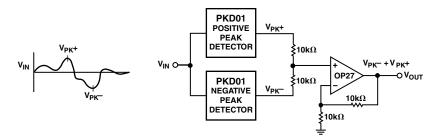

Figure 18. Peak-to-Peak Detector

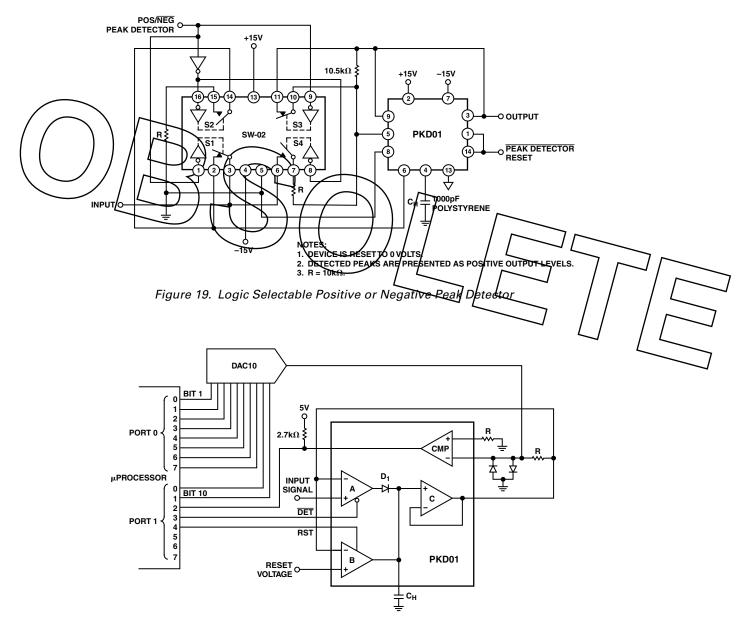

Figure 20. Peak Reading A/D Converter

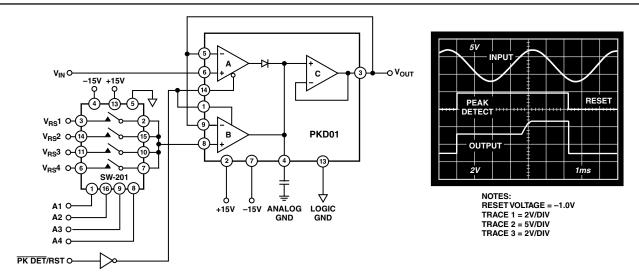

Figure 21. Positive Peak Detector with Selectable Reset Voltage

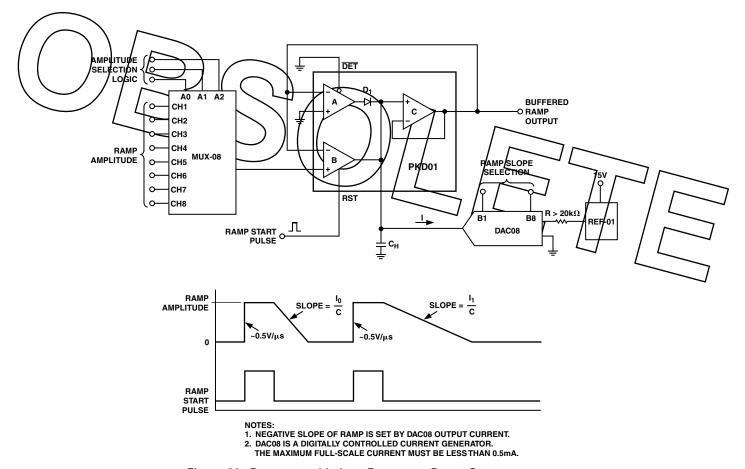

Figure 22. Programmable Low Frequency Ramp Generator

REV. A -17-

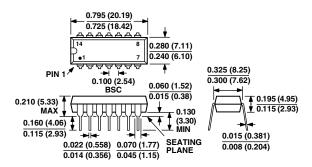

#### **OUTLINE DIMENSIONS**

Dimensions shown in inches and (mm).

## 14-Lead Plastic DIP (PDIP) (N-14)