# ANALOG DEVICES

# Low Cost, Low Power CMOS General-Purpose Dual Analog Front End

# AD73322L

### FEATURES

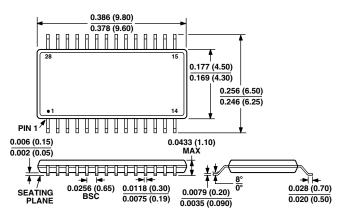

Two 16-Bit A/D Converters Two 16-Bit D/A Converters **Programmable Input/Output Sample Rates** 78 dB ADC SNR 78 dB DAC SNR 64 kS/s Maximum Sample Rate -90 dB Crosstalk Low Group Delay (25 µs Typ per ADC Channel, 50 µs Typ per DAC Channel) **Programmable Input/Output Gain** Flexible Serial Port which Allows Up to Four Dual Codecs to be Connected in Cascade Giving Eight I/O Channels Single (2.7 V to 3.3 V) Supply Operation 50 mW Typ Power Consumption at 3.0 V Temperature Range: -40°C to +105°C **On-Chip Reference** 28-Lead SOIC, TSSOP, and 44-Lead LQFP Packages **APPLICATIONS**

General-Purpose Analog I/O Speech Processing Cordless and Personal Communications Telephony Active Control of Sound and Vibration Data Communications Wireless Local Loop

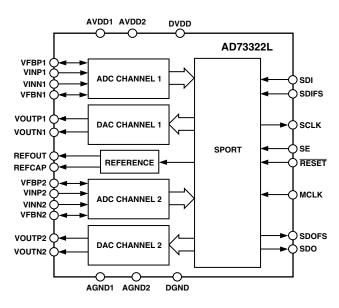

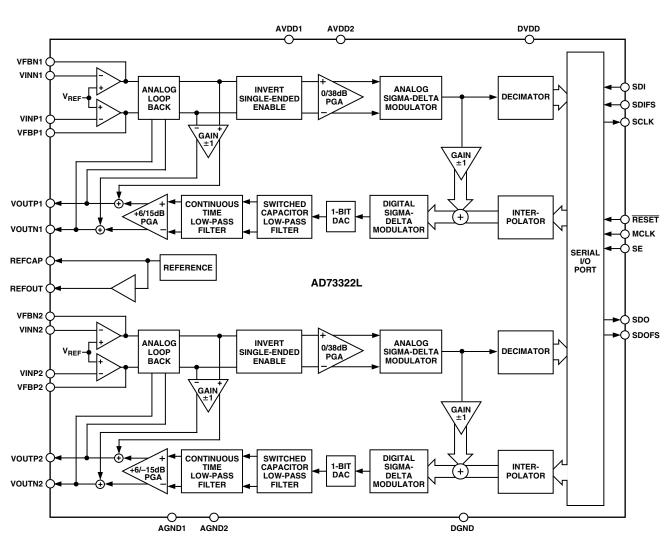

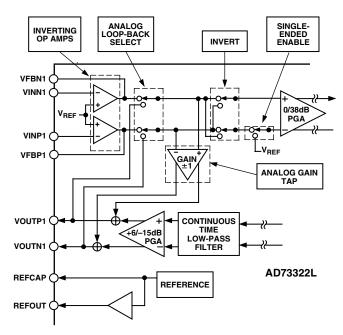

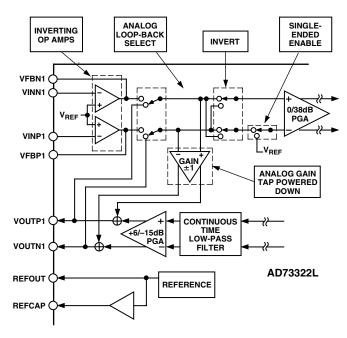

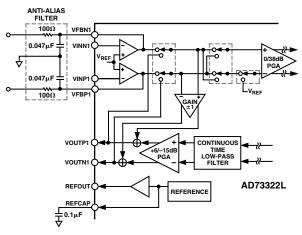

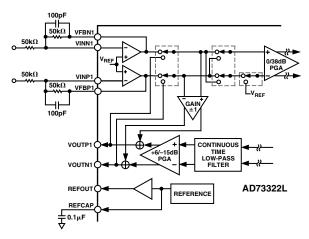

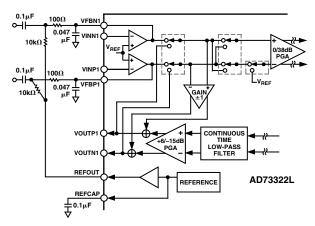

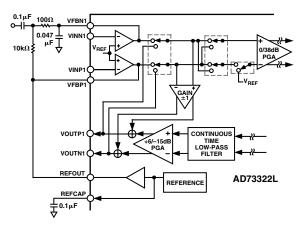

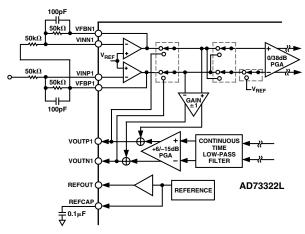

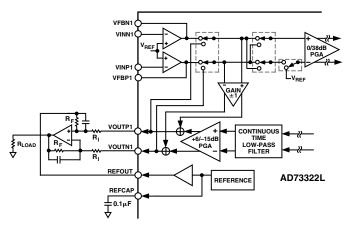

## FUNCTIONAL BLOCK DIAGRAM

## **GENERAL DESCRIPTION**

The AD73322L is a dual front-end processor for general purpose applications including speech and telephony. It features two 16-bit A/D conversion channels and two 16-bit D/A conversion channels. Each channel provides 78 dB signal-to-noise ratio over a voiceband signal bandwidth. It also features an input-to-output gain network in both the analog and digital domains. This is featured on both codecs and can be used for impedance matching or scaling when interfacing to Subscriber Line Interface Circuits (SLICs).

The AD73322L is particularly suitable for a variety of applications in the speech and telephony area, including low bit rate, high quality compression, speech enhancement, recognition and synthesis. The low group delay characteristic of the part makes it suitable for single or multichannel active control applications. The A/D and D/A conversion channels feature programmable input/output gains with ranges 38 dB and 21 dB respectively. An on-chip reference voltage is included to allow single-supply operation.

The sampling rate of the codecs is programmable with four separate settings offering 64 kHz, 32 kHz, 16 kHz, and 8 kHz sampling rates (from a master clock of 16.384 MHz).

A serial port (SPORT) allows easy interfacing of single or cascaded devices to industry standard DSP engines. The SPORT transfer rate is programmable to allow interfacing to both fast and slow DSP engines.

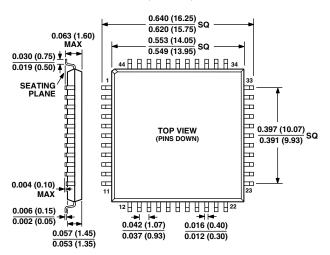

The AD73322L is available in 28-lead SOIC, 28-lead TSSOP, and 44-lead LQFP packages.

## REV.0

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: 781/329-4700 www.analog.com Fax: 781/326-8703 © Analog Devices, Inc., 2001

# $\label{eq:additional} \begin{array}{l} \text{AD73322L-SPECIFICATIONS}^1 & (\text{AVDD} = 3 \ \text{V} \pm 10\%; \ \text{DVDD} = 3 \ \text{V} \pm 10\%; \ \text{DGND} = \text{AGND} = 0 \ \text{V}, \ f_{\text{DMCLK}} = 16.384 \ \text{MHz}, \ f_{\text{SAMP}} = 8 \ \text{kHz}; \ T_{\text{A}} = T_{\text{MIN}} \ \text{to} \ T_{\text{MAX}}, \ \text{unless otherwise noted.} \end{array} \right)$

| A, Y Versio                                           |      |            |      |          |                                                                                                                                                                                            |  |

|-------------------------------------------------------|------|------------|------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Parameter                                             | Min  | Тур        | Max  | Unit     | Test Conditions/Comments                                                                                                                                                                   |  |

| REFERENCE                                             |      |            |      |          |                                                                                                                                                                                            |  |

| REFCAP                                                |      |            |      |          |                                                                                                                                                                                            |  |

| Absolute Voltage, VREFCAP                             | 1.08 | 1.2        | 1.32 | V        |                                                                                                                                                                                            |  |

| REFCAP TC                                             |      | 50         |      | ppm/°C   | 0.1 µF Capacitor Required from                                                                                                                                                             |  |

| REFOUT                                                |      |            |      |          | REFCAP to AGND2                                                                                                                                                                            |  |

| Typical Output Impedance                              |      | 130        |      | Ω        |                                                                                                                                                                                            |  |

| Absolute Voltage, V <sub>REFOUT</sub>                 | 1.08 | 1.2        | 1.32 | V        | Unloaded                                                                                                                                                                                   |  |

| Minimum Load Resistance                               |      | 1          |      | kΩ       |                                                                                                                                                                                            |  |

| Maximum Load Capacitance                              |      | 100        |      | pF       |                                                                                                                                                                                            |  |

| INPUT AMPLIFIER                                       |      |            |      |          |                                                                                                                                                                                            |  |

| Offset                                                |      | $\pm 1.0$  |      | mV       |                                                                                                                                                                                            |  |

| Maximum Output Swing                                  |      | 1.578      |      | V        | Max Output Swing = $(1.578/1.2) \times VREFCAP$                                                                                                                                            |  |

| Feedback Resistance                                   |      | 50         |      | kΩ       | $f_{\rm C}$ = 32 kHz                                                                                                                                                                       |  |

| Feedback Capacitance                                  |      | 100        |      | pF       |                                                                                                                                                                                            |  |

| ANALOG GAIN TAP                                       |      |            |      |          |                                                                                                                                                                                            |  |

| Gain at Maximum Setting                               |      | +1         |      |          |                                                                                                                                                                                            |  |

| Gain at Minimum Setting                               |      | -1         |      |          |                                                                                                                                                                                            |  |

| Gain Resolution                                       |      | 5          |      | Bits     | Gain Step Size = 0.0625                                                                                                                                                                    |  |

| Gain Accuracy                                         |      | $\pm 1.0$  |      | %        | Output Unloaded                                                                                                                                                                            |  |

| Settling Time                                         |      | 1.0        |      | μs       | Tap Gain Change of –FS to +FS                                                                                                                                                              |  |

| Delay                                                 |      | 0.5        |      | μs       |                                                                                                                                                                                            |  |

| ADC SPECIFICATIONS                                    |      |            |      |          | DAC Unloaded                                                                                                                                                                               |  |

| Maximum Input Range at VIN <sup>2, 3</sup>            |      | 1.578      |      | V p-p    | Measured Differentially                                                                                                                                                                    |  |

|                                                       |      | -2.85      |      | dBm      | Max Input = $(1.578/1.2) \times VREFCAP$                                                                                                                                                   |  |

| Nominal Reference Level at VIN                        |      | 1.0954     |      | V p-p    | Measured Differentially                                                                                                                                                                    |  |

| (0 dBm0)                                              |      | -6.02      |      | dBm      |                                                                                                                                                                                            |  |

| Absolute Gain                                         | 2.0  | 0.7        |      | 17       |                                                                                                                                                                                            |  |

| PGA = 0 dB                                            | -2.0 | -0.7       | +0.5 | dB<br>dB | 1.0  kHz, 0  dBm0                                                                                                                                                                          |  |

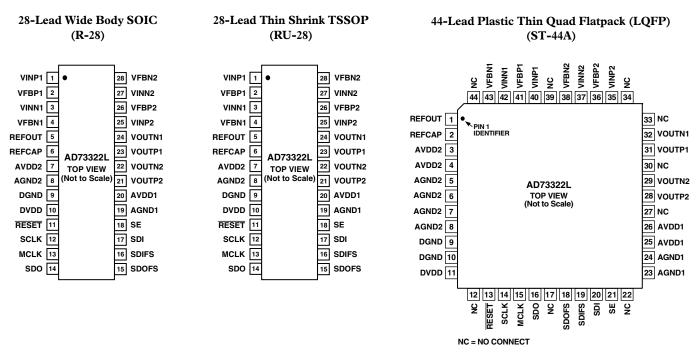

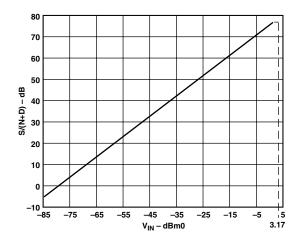

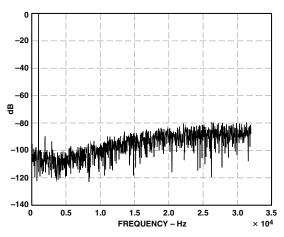

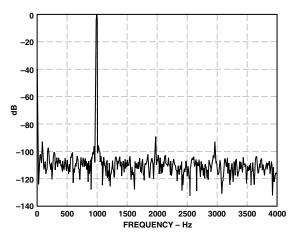

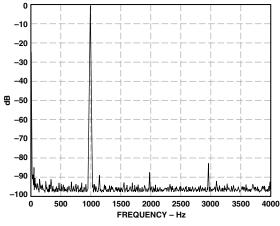

| Gain Tracking Error<br>Signal to (Noise + Distortion) |      | $\pm 0.1$  |      | ub       | 1.0 kHz, +3 dBm0 to -50 dBm0<br>Refer to TPC 1.                                                                                                                                            |  |

| PGA = 0 dB                                            | 70   | 78         |      | dB       | 300 Hz to 3400 Hz; $f_{SAMP} = 8$ kHz, PUIA = 0                                                                                                                                            |  |

| 1011 = 0 db                                           | 10   | 79         |      | dB       | $300 \text{ Hz}$ to $3400 \text{ Hz}$ ; $f_{\text{SAMP}} = 0 \text{ KHz}$ ; $f_{\text{CMP}} = 0$<br>$300 \text{ Hz}$ to $3400 \text{ Hz}$ ; $f_{\text{SAMP}} = 8 \text{ kHz}$ , $PUIA = 1$ |  |

|                                                       |      | 77.5       |      | dB       | $0 \text{ Hz to } f_{\text{SAMP}}/2; f_{\text{SAMP}} = 8 \text{ kHz}$                                                                                                                      |  |

| Total Harmonic Distortion                             |      |            |      |          | S THE CO ISAMP O RELL                                                                                                                                                                      |  |

| PGA = 0 dB                                            |      | -86        | -75  | dB       | 300 Hz to 3400 Hz; f <sub>SAMP</sub> = 8 kHz                                                                                                                                               |  |

| Intermodulation Distortion                            |      | -61        |      | dB       | PGA = 0 dB                                                                                                                                                                                 |  |

| Idle Channel Noise Crosstalk                          |      | -72        |      | dBm0     | PGA = 0 dB                                                                                                                                                                                 |  |

| ADC-to-DAC                                            |      | -107       |      | dB       | ADC Input Signal Level: 1.0 kHz, 0 dBm0                                                                                                                                                    |  |

|                                                       |      |            |      |          | DAC Input at Idle                                                                                                                                                                          |  |

| ADC-to-ADC                                            |      | -92        |      | dB       | ADC1 Input Signal Level: 1.0 kHz, 0 dBm0                                                                                                                                                   |  |

|                                                       |      |            |      |          | ADC2 Input at Idle. Input Amplifiers Bypassed                                                                                                                                              |  |

|                                                       |      | -93        |      | dB       | Input Amplifiers Included in Input Channel                                                                                                                                                 |  |

| DC Offset                                             | -20  | 0          | +20  | mV       | PGA = 0 dB                                                                                                                                                                                 |  |

| Power Supply Rejection                                |      | -65        |      | dB       | Input Signal Level at AVDD and DVDD<br>Piper 1.0 kHz, 100 mV p. p. Sing Waya                                                                                                               |  |

| Group Delay <sup>4, 5</sup>                           |      | 25         |      |          | Pins: 1.0 kHz, 100 mV p-p Sine Wave                                                                                                                                                        |  |

| Input Resistance at PGA <sup>2, 4, 6</sup>            |      | 25<br>20   |      | μs<br>kΩ | Input Amplifiers Bypassed                                                                                                                                                                  |  |

|                                                       |      | 20         |      | 1726     | mpar impiniero Dypassea                                                                                                                                                                    |  |

| DIGITAL GAIN TAP                                      |      | <b>⊥</b> 1 |      |          |                                                                                                                                                                                            |  |

| Gain at Maximum Setting<br>Gain at Minimum Setting    |      | +1<br>-1   |      |          |                                                                                                                                                                                            |  |

| Gain Resolution                                       |      | $^{-1}$ 16 |      | Bits     | Tested to 5 MSBs of Settings                                                                                                                                                               |  |

| Delay                                                 |      | 25         |      | μs       | Includes DAC Delay                                                                                                                                                                         |  |

| Settling Time                                         |      | 100        |      | μs<br>μs | Tap Gain Change from –FS to +FS; Includes                                                                                                                                                  |  |

|                                                       |      |            |      | P        | DAC Settling Time                                                                                                                                                                          |  |

|                                                          | A     | , Y Versi | ons   |       |                                                      |

|----------------------------------------------------------|-------|-----------|-------|-------|------------------------------------------------------|

| Parameter                                                | Min   | Тур       | Max   | Unit  | Test Conditions/Comments                             |

| DAC SPECIFICATIONS                                       |       |           |       |       | DAC Unloaded                                         |

| Maximum Voltage Output Swing <sup>2</sup>                |       |           |       |       |                                                      |

| Single-Ended                                             |       | 1.578     |       | V p-p | PGA = 6 dB                                           |

|                                                          |       | -2.85     |       | dBm   | Max Output = $(1.578/1.2) \times VREFCAP$            |

| Differential                                             |       | 3.156     |       | V p-p | PGA = 6 dB                                           |

|                                                          |       | 3.17      |       | dBm   | Max Output = $2 \times ([1.578/1.2] \times VREFCAP)$ |

| Nominal Voltage Output Swing (0 dBm0)                    |       |           |       |       |                                                      |

| Single-Ended                                             |       | 1.0954    |       | V p-p | PGA = 6 dB                                           |

| 0                                                        |       | -6.02     |       | dBm   |                                                      |

| Differential                                             |       | 2.1909    |       | V p-p | PGA = 6 dB                                           |

|                                                          |       | 0         |       | dBm   |                                                      |

| Output Bias Voltage                                      |       | 1.2       |       | V     | REFOUT Unloaded                                      |

| Absolute Gain                                            | -1.75 | -0.6      | +0.75 | dB    | 1.0 kHz, 0 dBm0; Unloaded                            |

| Gain Tracking Error                                      |       | $\pm 0.1$ |       | dB    | 1.0 kHz, +3 dBm0 to -50 dBm0                         |

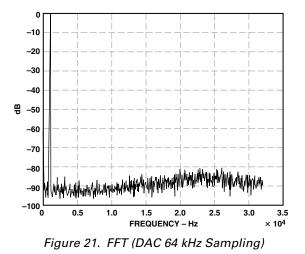

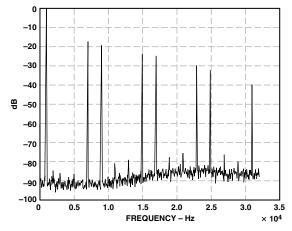

| Signal to (Noise + Distortion) at 0 dBm0                 |       |           |       |       | Refer to TPC 2.                                      |

| PGA = 0 dB                                               | 72    | 78.5      |       | dB    | 300 Hz to 3400 Hz; f <sub>SAMP</sub> = 8 kHz         |

| Total Harmonic Distortion at 0 dBm0                      |       |           |       |       |                                                      |

| PGA = 0 dB                                               |       | -89       | -75   | dB    | 300 Hz to 3400 Hz; f <sub>SAMP</sub> = 8 kHz         |

| Intermodulation Distortion                               |       | -77       |       | dB    | PGA = 0 dB                                           |

| Idle Channel Noise Crosstalk                             |       | -81       |       | dBm0  | PGA = 0 dB                                           |

| DAC-to-ADC                                               |       | -73       |       | dB    | ADC Input Signal Level: AGND; DAC                    |

|                                                          |       |           |       |       | Output Signal Level: 1.0 kHz, 0 dBm0                 |

|                                                          |       |           |       |       | Input Amplifiers Bypassed                            |

|                                                          |       | -74       |       | dB    | Input Amplifiers Included in Input Channel           |

| DAC-to-DAC                                               |       | -102      |       | dB    | DAC1 Output Signal Level: AGND; DAC2                 |

|                                                          |       |           |       |       | Output Signal Level: 1.0 kHz, 0 dBm0                 |

| Power Supply Rejection                                   |       | -65       |       | dB    | Input Signal Level at AVDD and DVDD                  |

|                                                          |       |           |       |       | Pins: 1.0 kHz, 100 mV p-p Sine Wave                  |

| Group Delay <sup>4, 5</sup>                              |       | 25        |       | μs    | Interpolator Bypassed                                |

|                                                          |       | 50        |       | μs    |                                                      |

| Output DC Offset <sup>2, 7</sup>                         | -50   | +5        | +60   | mV    |                                                      |

| Minimum Load Resistance, R <sub>L</sub> <sup>2, 8</sup>  |       |           |       |       |                                                      |

| Single-Ended <sup>4</sup>                                |       | 150       |       | Ω     |                                                      |

| Differential                                             |       | 150       |       | Ω     |                                                      |

| Maximum Load Capacitance, C <sub>L</sub> <sup>2, 8</sup> |       |           |       |       |                                                      |

| Single-Ended                                             |       | 500       |       | pF    |                                                      |

| Differential                                             |       | 100       |       | pF    |                                                      |

| FREQUENCY RESPONSE                                       |       |           |       |       |                                                      |

| (ADC and DAC) <sup>9</sup> Typical Output                |       |           |       |       |                                                      |

| Frequency (Normalized to FS)                             |       |           |       |       |                                                      |

| 0                                                        |       | 0         |       | dB    |                                                      |

| 0.03125                                                  |       | -0.1      |       | dB    |                                                      |

| 0.0625                                                   |       | -0.25     |       | dB    |                                                      |

| 0.125                                                    |       | -0.6      |       | dB    |                                                      |

| 0.1875                                                   |       | -1.4      |       | dB    |                                                      |

| 0.25                                                     |       | -2.8      |       | dB    |                                                      |

| 0.3125                                                   |       | -4.5      |       | dB    |                                                      |

| 0.375                                                    |       | -7.0      |       | dB    |                                                      |

| 0.4375                                                   |       | -9.5      |       | dB    |                                                      |

| > 0.5                                                    |       | < -12.5   | ;     | dB    |                                                      |

| D                                     | ,        | Version |      | <b>TT</b> •. | T                        |

|---------------------------------------|----------|---------|------|--------------|--------------------------|

| Parameter                             | Min      | Тур     | Max  | Unit         | Test Conditions/Comments |

| LOGIC INPUTS                          |          |         |      |              |                          |

| V <sub>INH</sub> , Input High Voltage | DVDD - 0 | .8      | DVDD | V            |                          |

| V <sub>INL</sub> , Input Low Voltage  | 0        |         | 0.8  | V            |                          |

| I <sub>IH</sub> , Input Current       | -10      |         | +10  | μA           |                          |

| C <sub>IN</sub> , Input Capacitance   |          |         | 10   | pF           |                          |

| LOGIC OUTPUT                          |          |         |      |              |                          |

| V <sub>OH</sub> , Output High Voltage | DVDD – ( | ).4     | DVDD | V            | $ IOUT  \le 100 \ \mu A$ |

| V <sub>OL</sub> , Output Low Voltage  | 0        |         | 0.4  | V            | $ IOUT  \le 100 \mu A$   |

| Three-State Leakage Current           | -10      |         | +10  | μΑ           |                          |

| POWER SUPPLIES                        |          |         |      |              |                          |

| AVDD1, AVDD2                          | 2.7      |         | 3.3  | V            |                          |

| DVDD                                  | 2.7      |         | 3.3  | V            |                          |

| $I_{DD}^{10}$                         |          |         |      |              | See Table I              |

NOTES

<sup>1</sup> Operating temperature range as follows: A Grade,  $T_{MIN} = -40^{\circ}$ C,  $T_{MAX} = +85^{\circ}$ C; Y Grade,  $T_{MIN} = -40^{\circ}$ C,  $T_{MAX} = +105^{\circ}$ C. <sup>2</sup> Test conditions: Input PGA set for 0 dB gain, Output PGA set for 6 dB gain, no load on analog outputs (unless otherwise noted).

<sup>3</sup>At input to sigma-delta modulator of ADC.

<sup>4</sup>Guaranteed by design.

<sup>5</sup> Overall group delay will be affected by the sample rate and the external digital filtering.

$^{6}$  The ADC's input impedance is inversely proportional to DMCLK and is approximated by:  $(3.3 \times 10^{11})/DMCLK$ .

<sup>7</sup>Between VOUTP1 and VOUTN1 or between VOUTP2 and VOUTN2.

<sup>8</sup>At VOUT output.

<sup>9</sup> Frequency responses of ADC and DAC measured with input at audio reference level (the input level that produces an output level of -10 dBm0), with 38 dB preamplifier bypassed and input gain of 0 dB. <sup>10</sup>Test Conditions: no load on digital inputs, analog inputs ac-coupled to ground, no load on analog outputs.

Specifications subject to change without notice.

| Conditions        | Analog<br>Current | Digital<br>Current | Total Current<br>(Typ) | Total Current<br>(Max) | SE | MCLK<br>ON | Comments                                       |

|-------------------|-------------------|--------------------|------------------------|------------------------|----|------------|------------------------------------------------|

|                   |                   |                    |                        | (                      |    |            |                                                |

| ADCs On Only      | 3.4               | 6.3                | 9.7                    | 12                     | 1  | YES        | REFOUT Disabled                                |

| DACs On Only      | 8.8               | 6.5                | 15.3                   | 20                     | 1  | YES        | REFOUT Disabled                                |

| ADCs and DACs On  | 11.6              | 7.0                | 18.6                   | 23                     | 1  | YES        | REFOUT Disabled                                |

| ADCs and DACs     |                   |                    |                        |                        |    |            |                                                |

| and Input Amps On | 13.8              | 7.0                | 20.8                   | 26                     | 1  | YES        | REFOUT Disabled                                |

| ADCs and DACs     |                   |                    |                        |                        |    |            |                                                |

| and AGT On        | 13.2              | 7.0                | 20.2                   | 26                     | 1  | YES        | REFOUT Disabled                                |

| All Sections On   | 17.2              | 7.0                | 24.2                   | 31                     | 1  | YES        |                                                |

| REFCAP On Only    | 0.65              | 0                  | 0.67                   | 1.25                   | 0  | NO         | REFOUT Disabled                                |

| REFCAP and        |                   |                    |                        |                        |    |            |                                                |

| REFOUT On Only    | 2.56              | 0                  | 2.57                   | 4.5                    | 0  | NO         |                                                |

| All Sections Off  | 0                 | 1.25               | 1.25                   | 1.8                    | 0  | YES        | MCLK Active Levels Equal to                    |

|                   |                   |                    |                        |                        |    |            | 0 V and DVDD                                   |

| All Sections Off  | 0 μΑ              | 12.5 μA            | 12.7 μΑ                | 40 μΑ                  | 0  | NO         | Digital Inputs Static and Equal to 0 V or DVDD |

Table I. Current Summary (AVDD = DVDD = 3.3 V)

The above values are in mA and are typical values unless otherwise noted.

|         |                                        | 3 V Power Supply<br>5VEN = 0 |

|---------|----------------------------------------|------------------------------|

| VREFCAP |                                        | $1.2 V \pm 10\%$             |

| VREFOUT |                                        | $1.2 \text{ V} \pm 10\%$     |

| ADC     | Maximum Input Range at V <sub>IN</sub> | 1.578 V p-p                  |

|         | Nominal Reference Level                | 1.0954 V p-p                 |

| DAC     | Maximum Voltage Output Swing           |                              |

|         | Single-Ended                           | 1.578 V p-p                  |

|         | Differential                           | 3.156 V p-p                  |

|         | Nominal Voltage Output Swing           |                              |

|         | Single-Ended                           | 1.0954 V p-p                 |

|         | Differential                           | 2.1909 V p-p                 |

|         | Output Bias Voltage                    | VREFOUT                      |

Table II. Signal Ranges

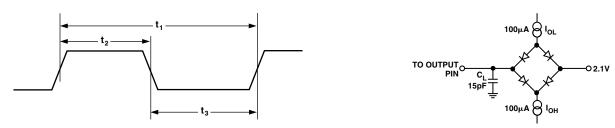

# **TIMING CHARACTERISTICS** (AVDD = 3 V $\pm$ 10%; DVDD = 3 V $\pm$ 10%; AGND = DGND = 0 V; T<sub>A</sub> = T<sub>MIN</sub> to T<sub>MAX</sub>, unless otherwise noted.)

| Parameter       | Limit at<br>$T_A = -40^{\circ}C$ to $+105^{\circ}C$ | Unit   | Description                     |

|-----------------|-----------------------------------------------------|--------|---------------------------------|

| Clock Signals   |                                                     |        | See Figure 1                    |

| t <sub>1</sub>  | 61                                                  | ns min | MCLK Period                     |

| t <sub>2</sub>  | 24.4                                                | ns min | MCLK Width High                 |

| t <sub>3</sub>  | 24.4                                                | ns min | MCLK Width Low                  |

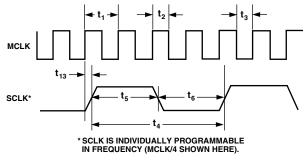

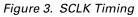

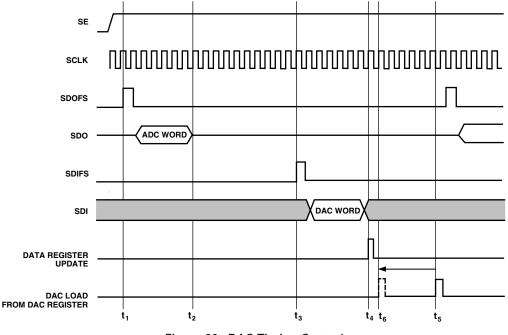

| Serial Port     |                                                     |        | See Figures 3 and 4             |

| t <sub>4</sub>  | t <sub>1</sub>                                      | ns min | SCLK Period                     |

| t <sub>5</sub>  | $0.4 	imes t_1$                                     | ns min | SCLK Width High                 |

| t <sub>6</sub>  | $0.4 	imes t_1$                                     | ns min | SCLK Width Low                  |

| t <sub>7</sub>  | 20                                                  | ns min | SDI/SDIFS Setup Before SCLK Low |

| t <sub>8</sub>  | 0                                                   | ns min | SDI/SDIFS Hold After SCLK Low   |

| t <sub>9</sub>  | 10                                                  | ns max | SDOFS Delay from SCLK High      |

| t <sub>10</sub> | 10                                                  | ns min | SDOFS Hold After SCLK High      |

| t <sub>11</sub> | 10                                                  | ns min | SDO Hold After SCLK High        |

| t <sub>12</sub> | 10                                                  | ns max | SDO Delay from SCLK High        |

| t <sub>13</sub> | 30                                                  | ns max | SCLK Delay from MCLK            |

Specifications subject to change without notice.

Figure 1. MCLK Timing

Figure 2. Load Circuit for Timing Specifications

Figure 4. Serial Port (SPORT)

#### **ABSOLUTE MAXIMUM RATINGS\***

| $(T_A = 25^{\circ}C \text{ unless otherwise noted})$                                                                                     |

|------------------------------------------------------------------------------------------------------------------------------------------|

| AVDD, DVDD to GND                                                                                                                        |

| AGND to DGND                                                                                                                             |

| Digital I/O Voltage to DGND $\dots$ -0.3 V to (DVDD + 0.3 V)                                                                             |

| Analog I/O Voltage to AGND $\dots$ -0.3 V to (AVDD + 0.3 V)                                                                              |

| Operating Temperature Range                                                                                                              |

| Industrial (A Version) $\dots \dots \dots \dots \dots \dots -40^{\circ}$ C to $+85^{\circ}$ C                                            |

| Extended (Y Version) $\dots -40^{\circ}$ C to $+105^{\circ}$ C                                                                           |

| Storage Temperature Range                                                                                                                |

| Maximum Junction Temperature 150°C                                                                                                       |

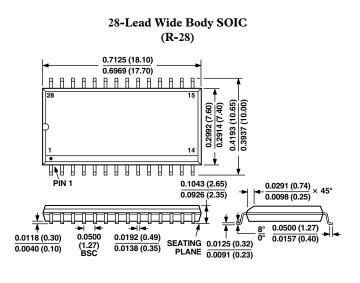

| SOIC, $\theta_{JA}$ Thermal Impedance                                                                                                    |

| Lead Temperature, Soldering                                                                                                              |

| Vapor Phase (60 sec) $\dots \dots \dots$ |

| Infrared (15 sec) 220°C                                                                                                                  |

| LQFP, $\theta_{JA}$ Thermal Impedance                                                                                                    |

| Lead Temperature, Soldering                                                                                                              |

| Vapor Phase (60 sec) $\dots \dots \dots$ |

| Infrared (15 sec) 220°C                                                                                                                  |

|                                                                                                                                          |

| TSSOP, $\theta_{IA}$ Thermal Impedance | 97.9°C/W |

|----------------------------------------|----------|

| Lead Temperature, Soldering            |          |

| Vapor Phase (60 sec)                   | 215°C    |

| Infrared (15 sec)                      | 220°C    |

\*Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those listed in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ORDERING GUIDE**

| Model           | Temperature<br>Range | Package<br>Descriptions | Package<br>Option |

|-----------------|----------------------|-------------------------|-------------------|

| AD73322LAR      | -40°C to +85°C       | Wide Body SOIC          | R-28              |

| AD73322LARU     | -40°C to +85°C       | Thin Shrink TSSOP       | RU-28             |

| AD73322LAST     | -40°C to +85°C       | Plastic Thin Quad       | ST-44A            |

|                 |                      | Flatpack (LQFP)         |                   |

| AD73322LYR      | -40°C to +105°C      | Wide Body SOIC          | R-28              |

| AD73322LYRU     | -40°C to +105°C      | Thin Shrink TSSOP       | RU-28             |

| AD73322LYST     | -40°C to +105°C      | Plastic Thin Quad       | ST-44A            |

|                 |                      | Flatpack (LQFP)         |                   |

| EVAL-AD73322LEB |                      | Evaluation Board        |                   |

#### CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the human body and test equipment and can discharge without detection. Although the AD73322L features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high-energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality.

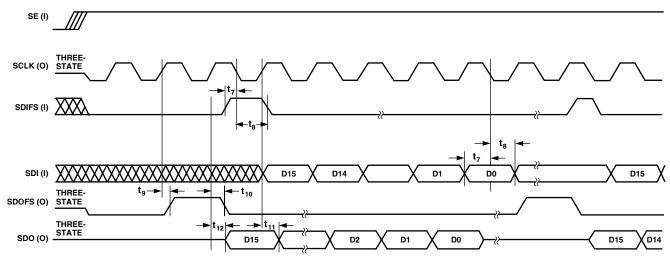

#### **PIN CONFIGURATIONS**

## PIN FUNCTION DESCRIPTIONS

| Mnemonic | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VINP1    | Analog Input to the inverting input amplifier on Channel 1's positive input.                                                                                                                                                                                                                                                                                                                                                                                         |

| VFBP1    | Feedback Connection from the output of the inverting amplifier on Channel 1's positive input. When the input amplifiers are bypassed, this pin allows direct access to the positive input of Channel 1's sigma-delta modulator.                                                                                                                                                                                                                                      |

| VINN1    | Analog Input to the inverting input amplifier on Channel 1's negative input.                                                                                                                                                                                                                                                                                                                                                                                         |

| VFBN1    | Feedback connection from the output of the inverting amplifier on Channel 1's negative input. When the input amplifiers are bypassed, this pin allows direct access to the negative input of Channel 1's sigma-delta modulator.                                                                                                                                                                                                                                      |

| REFOUT   | Buffered Reference Output, which has a nominal value of 1.2 V or 2.4 V, the value being dependent on the status of Bit 5VEN (CRC:7). As the reference is common to the two codec units, the reference value is set by the wired OR of the CRC:7 bits in Control Register C of each channel.                                                                                                                                                                          |

| REFCAP   | A bypass capacitor to AGND2 of 0.1 $\mu$ F is required for the on-chip reference. The capacitor should be fixed to this pin.                                                                                                                                                                                                                                                                                                                                         |

| AVDD2    | Analog Power Supply Connection.                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| AGND2    | Analog Ground/Substrate Connection2.                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| DGND     | Digital Ground/Substrate Connection.                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| DVDD     | Digital Power Supply Connection.                                                                                                                                                                                                                                                                                                                                                                                                                                     |

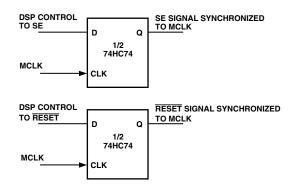

| RESET    | Active Low Reset Signal. This input resets the entire chip, resetting the control registers and clearing the digital circuitry.                                                                                                                                                                                                                                                                                                                                      |

| SCLK     | Serial Clock Output whose rate determines the serial transfer rate to/from the codec. It is used to clock data or control information to and from the serial port (SPORT). The frequency of SCLK is equal to the frequency of the master clock (MCLK) divided by an integer number—this integer number being the product of the external master clock rate divider and the serial clock rate divider.                                                                |

| MCLK     | Master Clock Input. MCLK is driven from an external clock signal.                                                                                                                                                                                                                                                                                                                                                                                                    |

| SDO      | Serial Data Output. Both data and control information may be output on this pin and are clocked on the positive edge of SCLK. SDO is in three-state when no information is being transmitted and when SE is low.                                                                                                                                                                                                                                                     |

| SDOFS    | Framing Signal Output for SDO Serial Transfers. The frame sync is one bit wide and is active one SCLK period before the first bit (MSB) of each output word. SDOFS is referenced to the positive edge of SCLK. SDOFS is in three-state when SE is low.                                                                                                                                                                                                               |

| SDIFS    | Framing Signal Input for SDI Serial Transfers. The frame sync is one bit wide and is valid one SCLK period before the first bit (MSB) of each input word. SDIFS is sampled on the negative edge of SCLK and is ignored when SE is low.                                                                                                                                                                                                                               |

| SDI      | Serial Data Input. Both data and control information may be input on this pin and are clocked on the negative edge of SCLK. SDI is ignored when SE is low.                                                                                                                                                                                                                                                                                                           |

| SE       | SPORT Enable. Asynchronous input enable pin for the SPORT. When SE is set low by the DSP, the output pins of the SPORT are three-stated and the input pins are ignored. SCLK is also disabled internally in order to decrease power dissipation. When SE is brought high, the control and data registers of the SPORT are at their original values (before SE was brought low); however, the timing counters and other internal registers are at their reset values. |

| AGND1    | Analog Ground/Substrate Connection.                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| AVDD1    | Analog Power Supply Connection.                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| VOUTP2   | Analog Output from the Positive Terminal of Output Channel 2.                                                                                                                                                                                                                                                                                                                                                                                                        |

| VOUTN2   | Analog Output from the Negative Terminal of Output Channel 2.                                                                                                                                                                                                                                                                                                                                                                                                        |

| VOUTP1   | Analog Output from the Positive Terminal of Output Channel 1.                                                                                                                                                                                                                                                                                                                                                                                                        |

| VOUTN1   | Analog Output from the Negative Terminal of Output Channel 1.                                                                                                                                                                                                                                                                                                                                                                                                        |

| VINP2    | Analog Input to the inverting input amplifier on Channel 2's positive input.                                                                                                                                                                                                                                                                                                                                                                                         |

| VFBP2    | Feedback connection from the output of the inverting amplifier on Channel 2's positive input. When the input amplifiers are bypassed, this pin allows direct access to the positive input of Channel 2's sigma-delta modulator.                                                                                                                                                                                                                                      |

| VINN2    | Analog Input to the inverting input amplifier on Channel 2's negative input.                                                                                                                                                                                                                                                                                                                                                                                         |

| VFBN2    | Feedback connection from the output of the inverting amplifier on Channel 2's negative input. When the input amplifiers are bypassed, this pin allows direct access to the negative input of Channel 2's sigma-delta modulator.                                                                                                                                                                                                                                      |

## TERMINOLOGY

## Absolute Gain

Absolute gain is a measure of converter gain for a known signal. Absolute gain is measured (differentially) with a 1 kHz sine wave at 0 dBm0 for the DAC and with a 1 kHz sine wave at 0 dBm0 for the ADC. The absolute gain specification is used for gain tracking error specification.

## Crosstalk

Crosstalk is due to coupling of signals from a given channel to an adjacent channel. It is defined as the ratio of the amplitude of the coupled signal to the amplitude of the input signal. Crosstalk is expressed in dB.

## **Gain Tracking Error**

Gain tracking error measures changes in converter output for different signal levels relative to an absolute signal level. The absolute signal level is 0 dBm0 (equal to absolute gain) at 1 kHz for the DAC and 0 dBm0 (equal to absolute gain) at 1 kHz for the ADC. Gain tracking error at 0 dBm0 (ADC) and 0 dBm0 (DAC) is 0 dB by definition.

## **Group Delay**

Group Delay is defined as the derivative of radian phase with respect to radian frequency,  $d\emptyset(f)/df$ . Group delay is a measure of average delay of a system as a function of frequency. A linear system with a constant group delay has a linear phase response. The deviation of group delay from a constant indicates the degree of nonlinear phase response of the system.

## Idle Channel Noise

Idle channel noise is defined as the total signal energy measured at the output of the device when the input is grounded (measured in the frequency range 300 Hz–3400 Hz).

## Intermodulation Distortion

With inputs consisting of sine waves at two frequencies, fa and fb, any active device with nonlinearities will create distortion products at sum and difference frequencies of mfa  $\pm$  nfb where m, n = 0, 1, 2, 3, etc. Intermodulation terms are those for which neither m nor n is equal to zero. For final testing, the second order terms include (fa + fb) and (fa - fb), while the third order terms include (2fa + fb), (2fa - fb), (fa + 2fb) and (fa - 2fb).

## **Power Supply Rejection**

Power supply rejection measures the susceptibility of a device to noise on the power supply. Power supply rejection is measured by modulating the power supply with a sine wave and measuring the noise at the output (relative to 0 dB).

## Sample Rate

The sample rate is the rate at which the ADC updates its output register and the DAC updates its output from its input register. The sample rate can be chosen from a list of four that are fixed relative to the DMCLK. Sample rate is set by programming bits DIR0-1 in Control Register B of each channel.

## SNR+THD

Signal-to-noise ratio plus harmonic distortion is defined to be the ratio of the rms value of the measured input signal to the rms sum of all other spectral components in the frequency range 300 Hz–3400 Hz, including harmonics but excluding dc.

## ABBREVIATIONS

| ADC | Analog-to-Digital | Converter. |

|-----|-------------------|------------|

|-----|-------------------|------------|

- AFE Analog Front End.

- AGT Analog Gain Tap.

- ALB Analog Loop-Back.

- BW Bandwidth.

- CRx A Control Register where x is a placeholder for an alphabetic character (A–E). There are five read/ write control registers on the AD73322L—designated CRA through CRE.

- CRx:n A bit position, where n is a placeholder for a numeric character (0–7), within a control register, where x is a placeholder for an alphabetic character (A–E). Position 7 represents the MSB and Position 0 represents the LSB.

- DAC Digital-to-Analog Converter.

- DGT Digital Gain Tap.

- DLB Digital Loop-Back.

- DMCLK Device (Internal) Master Clock. This is the internal master clock resulting from the external master clock (MCLK) being divided by the on-chip master clock divider.

FS Full Scale.

- FSLB Frame Sync Loop-Back—where the SDOFS of the final device in a cascade is connected to the RFS and TFS of the DSP and the SDIFS of first device in the cascade. Data input and output occur simultaneously. In the case of NonFSLB, SDOFS and SDO are connected to the Rx Port of the DSP while SDIFS and SDI are connected to the Tx Port.

- PGA Programmable Gain Amplifier.

- SC Switched Capacitor.

- SLB Sport Loop-Back.

- SNR Signal-to-Noise Ratio.

- SPORT Serial Port.

- THD Total Harmonic Distortion.

- VBW Voice Bandwidth.

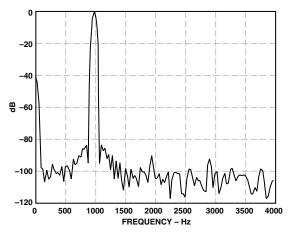

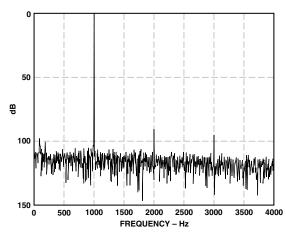

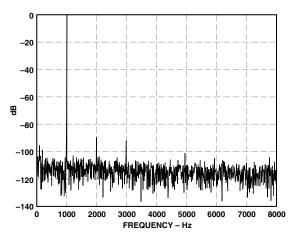

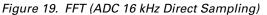

## AD73322L-Typical Performance Characteristics

TPC 1. S/(N+D) vs.  $V_{IN}$  (ADC @ 3 V) over Voiceband Bandwidth (300 Hz–3.4 kHz)

TPC 2. S/(N+D) vs.  $V_{IN}$  (DAC @ 3 V) over Voiceband Bandwidth (300 Hz–3.4 kHz)

Figure 5. Functional Block Diagram

### FUNCTIONAL DESCRIPTION

#### **Encoder Channels**

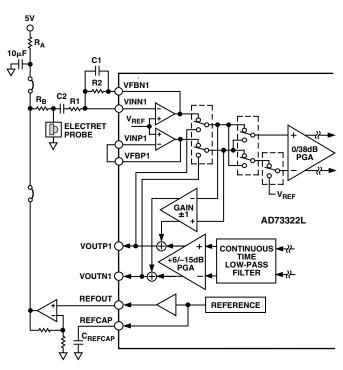

Both encoder channels consist of a pair of inverting op amps with feedback connections that can be bypassed if required, a switched capacitor PGA and a sigma-delta analog-to-digital converter (ADC). An on-board digital filter, which forms part of the sigma-delta ADC, also performs critical system-level filtering. Due to the high level of oversampling, the input antialias requirements are reduced such that a simple single pole RC stage is sufficient to give adequate attenuation in the band of interest.

#### **Programmable Gain Amplifier**

Each encoder section's analog front end comprises a switched capacitor PGA, which also forms part of the sigma-delta modulator. The SC sampling frequency is DMCLK/8. The PGA, whose programmable gain settings are shown in Table III, may be used to increase the signal level applied to the ADC from low output sources such as microphones, and can be used to avoid placing external amplifiers in the circuit. The input signal level to the sigma-delta modulator should not exceed the maximum input voltage permitted.

The PGA gain is set by bits IGS0, IGS1 and IGS2 (CRD:0–2) in control register D.

Table III. PGA Settings for the Encoder Channel

| IGS2 | IGS1 | IGS0 | Gain (dB) |

|------|------|------|-----------|

| 0    | 0    | 0    | 0         |

| 0    | 0    | 1    | 6         |

| 0    | 1    | 0    | 12        |

| 0    | 1    | 1    | 18        |

| 1    | 0    | 0    | 20        |

| 1    | 0    | 1    | 26        |

| 1    | 1    | 0    | 32        |

| 1    | 1    | 1    | 38        |

### ADC

Both ADCs consist of an analog sigma-delta modulator and a digital antialiasing decimation filter. The sigma-delta modulator noise-shapes the signal and produces 1-bit samples at a DMCLK/8 rate. This bitstream, representing the analog input signal, is input to the antialiasing decimation filter. The decimation filter reduces the sample rate and increases the resolution.

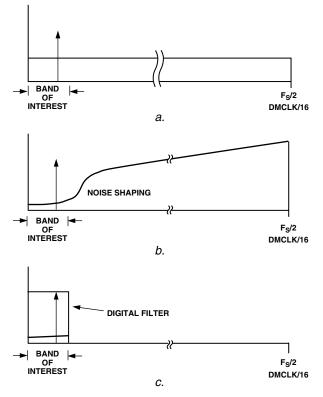

#### Analog Sigma-Delta Modulator

The AD73322L's input channels employ a sigma-delta conversion technique, which provides a high resolution 16-bit output with system filtering being implemented on-chip.

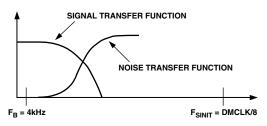

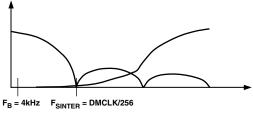

Sigma-delta converters employ a technique known as oversampling, where the sampling rate is many times the highest frequency of interest. In the case of the AD73322L, the initial sampling rate of the sigma-delta modulator is DMCLK/8. The main effect of oversampling is that the quantization noise is spread over a very wide bandwidth, up to  $F_8/2 = DMCLK/16$ (Figure 7a). This means that the noise in the band of interest is much reduced. Another complementary feature of sigma-delta converters is the use of a technique called noise-shaping. This technique has the effect of pushing the noise from the band of interest to an out-of-band position (Figure 7b). The combination of these techniques, followed by the application of a digital filter, sufficiently reduces the noise in band to ensure good dynamic performance from the part (Figure 7c).

Figure 6. Sigma-Delta Noise Reduction

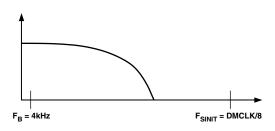

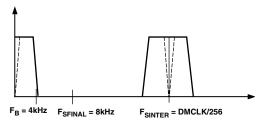

Figure 7 shows the various stages of filtering that are employed in a typical AD73322L application. In Figure 7a we see the transfer function of the external analog antialias filter. Even though it is a single RC pole, its cutoff frequency is sufficiently far away from the initial sampling frequency (DMCLK/8) that it takes care of any signals that could be aliased by the sampling frequency. This also shows the major difference between the initial oversampling rate and the bandwidth of interest. In Figure 7b, the signal and noise-shaping responses of the sigma-delta modulator are shown. The signal response provides further rejection of any high frequency signals while the noise-shaping will push the inherent quantization noise to an out-of-band position. The detail of Figure 7c shows the response of the digital decimation filter (Sinc-cubed response) with nulls every multiple of DMCLK/ 256, which corresponds to the decimation filter update rate for a 64 kHz sampling. The nulls of the Sinc3 response correspond with multiples of the chosen sampling frequency. The final detail in Figure 7d shows the application of a final antialias filter in the DSP engine. This has the advantage of being implemented according to the user's requirements and available MIPS. The filtering in Figures 7a through 7c is implemented in the AD73322L.

a. Analog Antialias Filter Transfer Function

b. Analog Sigma-Delta Modulator Transfer Function

c. Digital Decimator Transfer Function

d. Final Filter LPF (HPF) Transfer Function

### Figure 7. ADC Frequency Responses

#### **Decimation Filter**

The digital filter used in the AD73322L carries out two important functions. Firstly, it removes the out-of-band quantization noise, which is shaped by the analog modulator and secondly, it decimates the high frequency bit stream to a lower rate 16bit word.

The antialiasing decimation filter is a sinc-cubed digital filter that reduces the sampling rate from DMCLK/8 to DMCLK/256, and increases the resolution from a single bit to 15 bits or greater (depending on chosen sampling rate). Its Z transform is given as:

$$[(1 - Z^{-N})/(1 - Z^{-1})]^3$$

where N is set by the sampling rate (N = 32 @ 64 kHz sampling. . . N = 256 @ 8 kHz sampling). Thus when the sampling rate is 64 kHz, a minimal group delay of 25 µs can be achieved.

Word growth in the decimator is determined by the sampling rate. At 64 kHz sampling, where the oversampling ratio between sigma-delta modulator and decimator output equals 32, there are five bits per stage of the three-stage Sinc3 filter. Due to symmetry within the sigma-delta modulator, the LSB will always be a zero; therefore, the 16-bit ADC output word will have 2 LSBs equal to zero, one due to the sigma-delta symmetry and the other being a padding zero to make up the 16-bit word. At lower sampling rates, decimator word growth will be greater than the 16-bit sample word, therefore truncation occurs in transferring the decimator output as the ADC word. For example, at 8 kHz sampling, word growth reaches 24 bits due to the OSR of 256 between sigma-delta modulator and decimator output. This yields eight bits per stage of the three-stage Sinc3 filter.

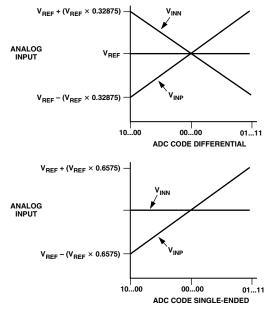

#### **ADC Coding**

The ADC coding scheme is in twos complement format (see Figure 8). The output words are formed by the decimation filter, which grows the word length from the single-bit output of the sigma-delta modulator to a word length of up to 24 bits (depending on decimation rate chosen), which is the final output of the ADC block. In Data Mode this value is truncated to 16 bits for output on the Serial Data Output (SDO) pin.

Figure 8. ADC Transfer Function

In mixed Control/Data Mode, the resolution is fixed at 15 bits, with the MSB of the 16-bit transfer being used as a flag bit to indicate either control or data in the frame.

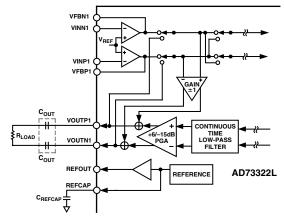

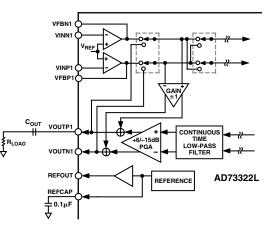

#### **Decoder Channel**

The decoder channels consist of digital interpolators, digital sigma-delta modulators, single-bit digital-to-analog converters (DAC), analog smoothing filters and programmable gain amplifiers with differential outputs.

### DAC Coding

The DAC coding scheme is in twos complement format with 0x7FFF being full-scale positive and 0x8000 being full-scale negative.

### **Interpolation Filter**

The anti-imaging interpolation filter is a sinc-cubed digital filter that up-samples the 16-bit input words from the input sample rate to a rate of DMCLK/8, while filtering to attenuate images produced by the interpolation process. Its Z transform is given as:

$$[(1 - Z^{-N})/(1 - Z^{-1})]^{2}$$

where N is determined by the sampling rate (N = 32 @ 64 kHz. ... N = 256 @ 8 kHz). The DAC receives 16-bit samples from the host DSP processor at the programmed sample rate of DMCLK/N. If the host processor fails to write a new value to the serial port, the existing (previous) data is read again. The data stream is filtered by the anti-imaging interpolation filter, but there is an option to bypass the interpolator for the minimum group delay configuration by setting the IBYP bit (CRE:5) of Control register E. The interpolation filter has the same characteristics as the ADC's antialiasing decimation filter.

The output of the interpolation filter is fed to the DAC's digital sigma-delta modulator, which converts the 16-bit data to 1-bit samples at a rate of DMCLK/8. The modulator noise-shapes the signal so that errors inherent to the process are minimized in the passband of the converter. The bit-stream output of the sigma-delta modulator is fed to the single-bit DAC where it is converted to an analog voltage.

### **Analog Smoothing Filter and PGA**

The output of the single-bit DAC is sampled at DMCLK/8, therefore it is necessary to filter the output to reconstruct the low frequency signal. The decoder's analog smoothing filter consists of a continuous-time filter preceded by a third-order switched-capacitor filter. The continuous-time filter forms part of the output programmable gain amplifier (PGA). The PGA can be used to adjust the output signal level from –15 dB to +6 dB in 3 dB steps, as shown in Table IV. The PGA gain is set by bits OGS0, OGS1 and OGS2 (CRD:4-6) in Control Register D.

Table IV. PGA Settings for the Decoder Channel

| OGS2 | OGS1 | OGS0 | Gain (dB) |  |  |

|------|------|------|-----------|--|--|

| 0    | 0    | 0    | +6        |  |  |

| 0    | 0    | 1    | +3        |  |  |

| 0    | 1    | 0    | 0         |  |  |

| 0    | 1    | 1    | -3        |  |  |

| 1    | 0    | 0    | -6        |  |  |

| 1    | 0    | 1    | -6<br>-9  |  |  |

| 1    | 1    | 0    | -12       |  |  |

| 1    | 1    | 1    | -15       |  |  |

#### **Differential Output Amplifiers**

The decoder has a differential analog output pair (VOUTP and VOUTN). The output channel can be muted by setting the MUTE bit (CRD:7) in Control Register D. The output signal is dc-biased to the codec's on-chip voltage reference.

#### Voltage Reference

The AD73322L reference, REFCAP, is a bandgap reference that provides a low noise, temperature-compensated reference to the DAC and ADC. A buffered version of the reference is also made available on the REFOUT pin and can be used to bias other external analog circuitry. The reference has a default nominal value of 1.2 V.

The reference output (REFOUT) can be enabled for biasing external circuitry by setting the RU bit (CRC:6) of CRC.

### Figure 9. Analog Input/Output Section

### Analog and Digital Gain Taps

The AD73322L features analog and digital feedback paths between input and output. The amount of feedback is determined by the gain setting which is programmed in the control registers. This feature can typically be used for balancing the effective impedance between input and output when used in Subscriber Line Interface Circuit (SLIC) interfacing.

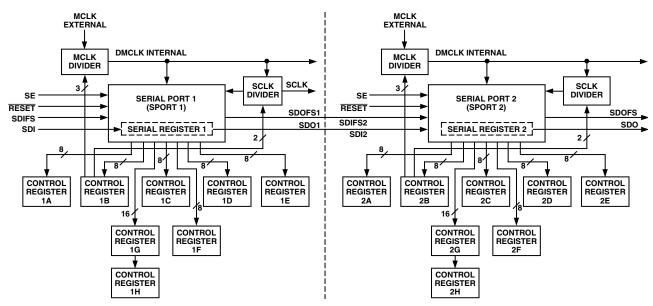

Figure 10. SPORT Block Diagram

### Analog Gain Tap

The analog gain tap is configured as a programmable differential amplifier whose input is taken from the ADC's input signal path. The output of the analog gain tap is summed with the output of the DAC. The gain is programmable using Control Register F (CRF:0-4) to achieve a gain of -1 to +1 in 32 steps with muting being achieved through a separate control setting (Control Register F Bit 7). The gain increment per step is 0.0625. The AGT is enabled by powering-up the AGT control bit in the power control register (CRC:1). When this bit is set (=1) CRF becomes an AGT control register with CRF:0-4 holding the AGT coefficient, CRF:5 becomes an AGT enable and CRF:7 becomes an AGT mute control bit. Control bit CRF:5 connects/ disconnects the AGT output to the summer block at the output of the DAC section while control bit CRF:7 overrides the gain tap setting with a mute, (zero gain) setting. Table V shows the gain versus digital setting for the AGT.

Table V. Analog Gain Tap Settings\*

| AGTC4 | AGTC3 | AGTC2 | AGTC1 | AGTC0 | Gain (dB) |

|-------|-------|-------|-------|-------|-----------|

| 0     | 0     | 0     | 0     | 0     | +1.00     |

| 0     | 0     | 0     | 0     | 1     | +0.9375   |

| 0     | 0     | 0     | 1     | 0     | +0.875    |

| 0     | 0     | 0     | 1     | 1     | +0.8125   |

| 0     | 0     | 1     | 0     | 0     | +0.75     |

| 0     | 1     | 1     | 1     | 1     | +0.0625   |

| 1     | 0     | 0     | 0     | 0     | -0.0625   |

| 1     | 1     | 1     | 0     | 1     | -0.875    |

| 1     | 1     | 1     | 1     | 0     | -0.9375   |

| 1     | 1     | 1     | 1     | 1     | -1.00     |

\*AGT and DGT weights are given for the case of VFBNx (connected to the sigma-delta modulator's positive input) being at a higher potential than VFBPx (connected to the sigma-delta modulator's negative input).

### **Digital Gain Tap**

The digital gain tap features a programmable gain block whose input is taken from the bitstream output of the ADC's sigmadelta modulator. This single bit input (1 or 0) is used to add or subtract a programmable value, which is the digital gain tap setting, to the output of the DAC section's interpolator. The programmable setting has 16-bit resolution and is programmed using the settings in Control Registers G and H. (See Table VI).

| Table VI. | Digital | Gain | Тар | Settings* |

|-----------|---------|------|-----|-----------|

|-----------|---------|------|-----|-----------|

| DGT15-0 (Hex) | Gain     |

|---------------|----------|

| 0x8000        | -1.00    |

| 0x9000        | -0.875   |

| 0xA000        | -0.75    |

| 0xC000        | -0.5     |

| 0xE000        | -0.25    |

| 0x0000        | 0.00     |

| 0x2000        | +0.25    |

| 0x4000        | +0.05    |

| 0x6000        | +0.75    |

| 0x7FFF        | +0.99999 |

\*AGT and DGT weights are given for the case of VFBNx (connected to the sigma-delta modulator's positive input) being at a higher potential than VFBPx (connected to the sigma-delta modulator's negative input).

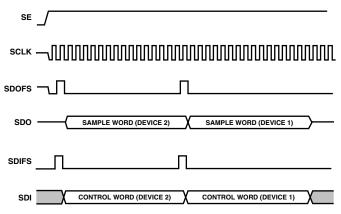

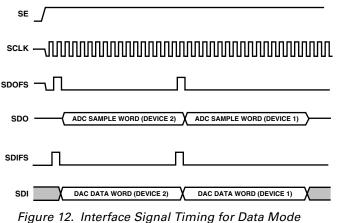

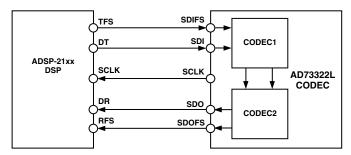

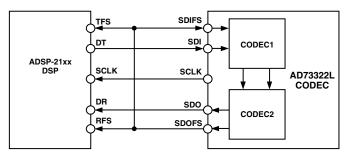

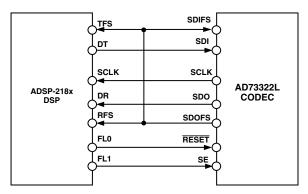

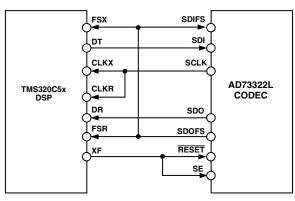

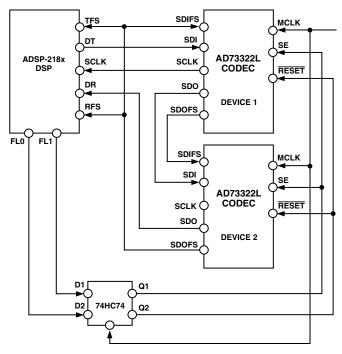

#### Serial Port (SPORT)

The codecs communicate with a host processor via the bidirectional synchronous serial port (SPORT), which is compatible with most modern DSPs. The SPORT is used to transmit and receive digital data and control information. The dual codec is implemented using two separate codec blocks that are internally cascaded with serial port access to the input of Codec1 and the output of Codec2. This allows other single or dual codec devices to be cascaded together (up to a limit of eight codec units). In both transmit and receive modes, data is transferred at the serial clock (SCLK) rate with the MSB being transferred first. Due to the fact that the SPORT of each codec block uses a common serial register for serial input and output, communications between an AD73322L codec and a host processor (DSP engine) must always be initiated by the codecs themselves. In this configuration the codecs are described as being in Master mode. This ensures that there is no collision between input data and output samples.

### **SPORT** Overview

The AD73322L SPORT is a flexible, full-duplex, synchronous serial port whose protocol has been designed to allow up to four AD73322L devices (or combinations of AD73322L dual codecs and AD73311 single codecs up to eight codec blocks) to be connected, in cascade, to a single DSP via a six-wire interface. It has a very flexible architecture that can be configured by programming two of the internal control registers in each codec block. The AD73322L SPORT has three distinct modes of operation: Control Mode, Data Mode and Mixed Control/Data Mode.

NOTE: As each codec has its own SPORT section, the register settings in both SPORTs must be programmed. The registers that control SPORT and sample rate operation (CRA and CRB) must be programmed with the same values, otherwise incorrect operation may occur.

In Control Mode (CRA:0 = 0), the device's internal configuration can be programmed by writing to the eight internal control registers. In this mode, control information can be written to or read from the codec. In Data Mode (CRA:0 = 1), (CRA:1 = 0), information sent to the device is used to update the decoder section (DAC), while the encoder section (ADC) data is read from the device. In this mode, only DAC and ADC data is written to or read from the device. Mixed mode (CRA:0 = 1 and CRA:1 = 1) allows the user to choose whether the information being sent to the device contains either control information or DAC data. This is achieved by using the MSB of the 16-bit frame as a flag bit. Mixed mode reduces the resolution to 15 bits with the MSB being used to indicate whether the information in the 16-bit frame is control information or DAC/ADC data.