# 82563EB/82564EB Gigabit Platform LAN Connect

**Networking Silicon**

#### **Datasheet**

#### **Product Features**

- IEEE 802.3ab compliant

- Robust operation over the installed base of Category-5 (Cat-5) twisted pair cabling

- PICMG 3.1 compliant

- Robust operation in backplane over Ethernet applications.

- Support for cable line lengths greater than 100 m (spec); 123 m physical

- Robust end to end connections over various cable lengths

- Full duplex at 10, 100, or 1000 Mb/s and half duplex at 10 or 100 Mb/s.

- IEEE 802.3ab Auto-negotiation with Next Page support

- Automatic link configuration including speed, duplex, and flow control

- 10/100 downshift

- Automatic link speed adjustment with poor quality cable

- Automatic MDI crossover

- —Helps to correct for infrastructure issues

- Advanced Cable Diagnostics

- -- Improved end-user troubleshooting

- Kumeran interface

- —Low pin count, high speed interface to the Intel® 631xESB/632xESB I/O Controller Hub

- —Allows PHY placement proximity to I/O back panel.

- 7 LED outputs per port (4 configurable plus 3 dedicated)

- —Link and Activity indications (10, 100, 1000 Mb/s) on each port

- Clock supplied to the 631xESB/632xESB

- -Cost optimized design

- Full chip power down

- —Support for lowest power state

- 100 pin TQFP Package

- Smaller footprint and lower power dissipation compared to multi-chip MAC and PHY solutions

- Operating temperature: 0°C to 60° C (maximum) heat sink or forced airflow not required

- —Simple thermal design

- Power Consumption: < 1.0 Watts per port (silicon power)

- Minimize impact of incorporating dual Gigabit instead of Fast Ethernet

- Leaded and lead-free<sup>a</sup> 100-pin TQFL with an Exposed-Pad\*. Devices that are lead-free are marked with a circled "e3" and have a product code: HYXXXXX

a. This device is lead-free. That is, lead has not been intentionally added, but lead may still exist as an impurity at <1000 ppm. The Material Declaration Data Sheet, which includes lead impurity levels and the concentration of other Restriction on Hazardous Substances (RoHS) -banned materials, is available at:

ftp://download.intel.com/design/packtech/material\_content\_IC\_Pack

In addition, this device has been tested and conforms to the same parametric specifications as previous versions of the device. For more information regarding lead-free products from Intel Corporation, contact your Intel Field Sales representative.

316534-004 Revision 2.9

# Revision History

| Date       | Revision | Comments                                                                                                                                                                   |

|------------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Nov 2007   | 2.9      | Updated Tables 19, 20, 23, and 24. Updated Figures 5 and 6.                                                                                                                |

| Oct 2007   | 2.8      | Updated Table 16 "Recommended Operating Conditions".                                                                                                                       |

| April 2007 | 2.7      | Updated Section 4.2, Table 16 "Core Digital Voltage Range".                                                                                                                |

| Feb 2007   | 2.6      | Updated Table 6.                                                                                                                                                           |

| May 2006   | 2.5      | Initial public release.                                                                                                                                                    |

| April 2006 | 2.1      | Removed "Preliminary" from section 4.9 "Power Consumption".  Updated 1.9V external power supply parameters in Tables 16 and 19.                                            |

| Nov 2005   | 2.0      | Initial release (Intel Confidential).                                                                                                                                      |

| Aug 2005   | 1.75     | Added lead-free information. Added measured power consumption values. Updated crystal specifications (drive level now 750 μW). Changed 1.8V power rail references to 1.9V. |

| Dec 2004   | 1.0      | Major revisions in all sections.                                                                                                                                           |

| Sep 2004   | 0.70     | Added power sequencing.                                                                                                                                                    |

| Jul 2004   | 0.51     | Changed pin 51 (page13) from AVDD (1.8V) to AVDDR (3.3V).                                                                                                                  |

| May 2004   | 0.5      | Initial release (Intel Secret).                                                                                                                                            |

#### Legal Notice

INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL® PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN INTEL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER, AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO SALE AND/OR USE OF INTEL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FINTESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

Intel products are not intended for use in medical, life saving, life sustaining, critical control or safety systems, or in nuclear facility applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

This document contains information on products in the design phase of development. The information here is subject to change without notice. Do not finalize a design with this information.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

The 82563EB/82564EB Gigabit Platform LAN Connects discussed in this document may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an ordering number and are referenced in this document, or other Intel literature, may be obtained from:

Intel Corporation P.O. Box 5937

Denver, CO 80217-9808

or call in North America 1-800-548-4725, Europe 44-0-1793-431-155, France 44-0-1793-421-777, Germany 44-0-1793-421-333, other Countries 708-296-9333.

Intel® is a trademark or registered trademark of Intel Corporation or its subsidiaries in the United States and other countries.

\*Other names and brands may be claimed as the property of others.

Copyright © Intel Corporation, 2007

| 1.0 | Introduction                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1  |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|     | 1.1 Document                                                                                                                                                                                                                                                  | Scope                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |    |

|     |                                                                                                                                                                                                                                                               | Documents                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |    |

|     | 1.3 Product Co                                                                                                                                                                                                                                                | des                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 2  |

| 2.0 | Block Diagrams                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 3  |

| 3.0 | Signal Descriptions                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 5  |

|     | 3.1 Signal Type<br>3.2 Shared PH<br>3.3 MDIO Inter<br>3.4 Port A PHY<br>3.5 Port A Kum<br>3.6 Port A LED<br>3.7 Reset, Pow<br>3.8 JTAG and I<br>3.9 Reserved S<br>3.10 Voltage Co<br>3.11 Clock Gene<br>3.12 Power/Grou<br>3.13 Port B PHY<br>3.14 Port B Kum | e Definitions Y Pins face / Interface neran Interface / Ser Down, and Initialization Signals IEEE Interface Signals Introl Pins Interface Interfac | 5  |

| 4.0 | Voltage, Temperatu                                                                                                                                                                                                                                            | ure and Timing Specifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 17 |

|     | 4.2 Recommen 4.3 DC and AC 4.4 Power Sup 4.4.1 Ext 4.4.2 Pov 4.4.3 Inte 4.4.4 Inte 4.5 Link (MDI) 4.6 Kumeran (\$ 4.6.1 Tra 4.6.2 Re 4.6.3 Ele 4.7 Crystal 4.7.1 Ext 4.8 Reset and I                                                                          | aximum Ratings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |    |

| 5.0 | Package and Pinou                                                                                                                                                                                                                                             | it Information                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 37 |

|     |                                                                                                                                                                                                                                                               | formation Decifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |    |

|                | 5.4 | Interface Diagrams                                                 | 43 |

|----------------|-----|--------------------------------------------------------------------|----|

|                | 5.5 | Visual Pin Assignments                                             | 44 |

| <b>Figures</b> |     |                                                                    |    |

| 5              | 1   | 82563EB Dual Port Block Diagram                                    | 3  |

|                | 2   | 82564EB Single Port Block Diagram                                  |    |

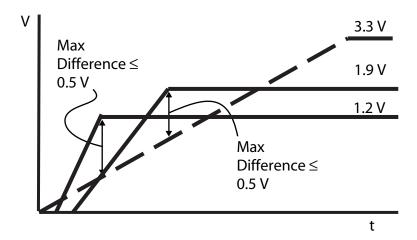

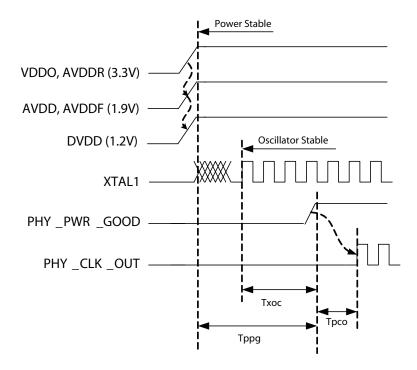

|                | 3   | 82563EB/82564EB power up sequencing with external regulators       | 21 |

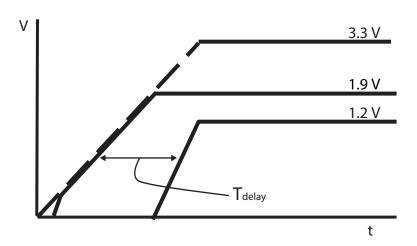

|                | 4   | 82563EB/82564EB power up sequencing with internal regulators       | 23 |

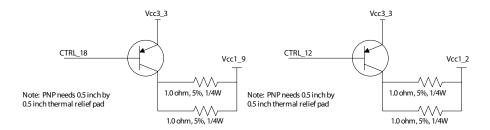

|                | 5   | 82563EB 1.9V and 1.2V internal LVR schematic                       | 26 |

|                | 6   | 82564EB 1.9V and 1.2V internal LVR schematic                       | 26 |

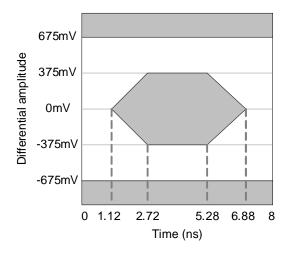

|                | 7   | Kumeran (Serial) Transmit Eye Diagram                              | 28 |

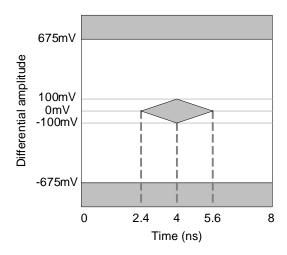

|                | 8   | Kumeran (Serial) Receive Eye Diagram                               |    |

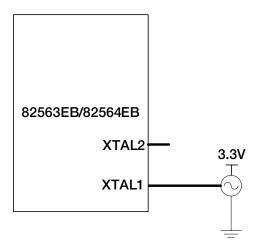

|                | 9   | External Clock Oscillator Connectivity to 82563EB/82564EB          | 31 |

|                | 10  | 82563EB/82564EB Reset Timing                                       | 32 |

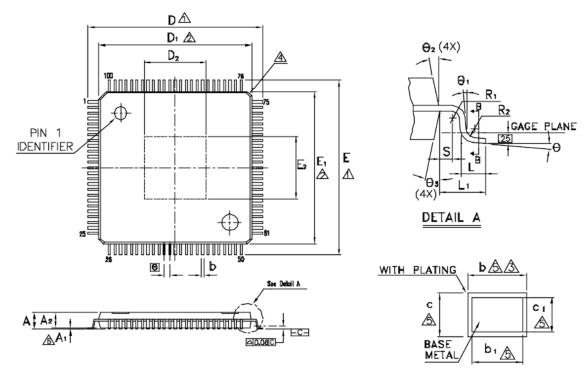

|                | 11  | Mechanical Information                                             | 37 |

|                | 12  | Mechanical Specifications and Notes                                | 38 |

|                | 13  | 82563EB/82564EB Interfaces                                         |    |

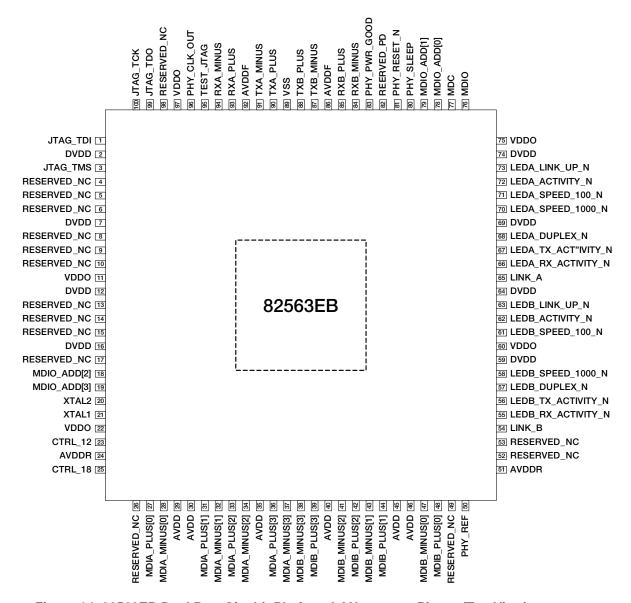

|                | 14  | 82563EB Dual Port Gigabit Platform LAN connect Pinout (Top View)   | 44 |

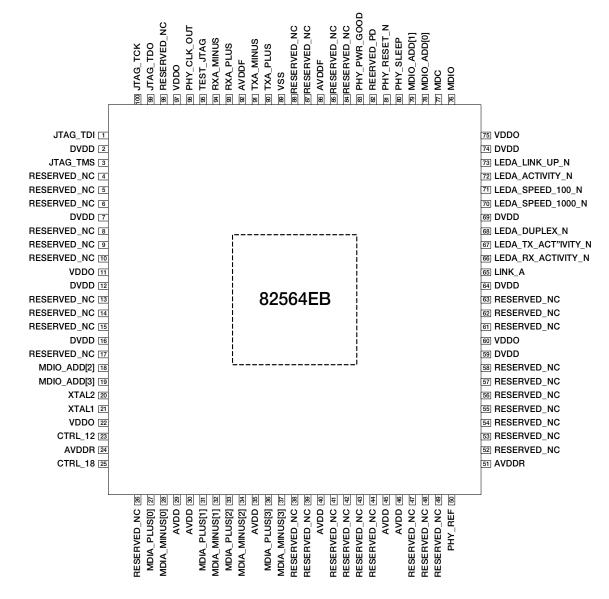

|                | 15  | 82564EB Single Port Gigabit Platform LAN Connect Pinout (Top View) | 45 |

| Tables         |     |                                                                    |    |

|                | 1   | Product Ordering Codes                                             | 2  |

|                | 1   | Shared PHY Pins                                                    |    |

|                | 2   | MDIO Interface Pins                                                | 6  |

|                | 3   | Port A PHY Interface Pins                                          | 7  |

|                | 4   | Port A Kumeran Interface Pins                                      | 8  |

|                | 5   | Port A LEDs                                                        | 8  |

|                | 6   | Reset and Power Down Signals                                       | g  |

|                | 7   | JTAG Signals                                                       | 9  |

|                | 8   | Test Signals                                                       | 10 |

|                | 9   | Voltage Control Pins                                               | 10 |

|                | 10  | Clock Generator Related Signals                                    | 11 |

|                | 11  | Power/Ground Pins                                                  | 11 |

|                | 12  | Port B PHY Interface Pins                                          | 13 |

|                | 13  | Port B Kumeran Interface Pins                                      | 14 |

|                | 14  | Port B LEDs                                                        | 15 |

|                | 15  | Absolute Maximum Ratings                                           | 17 |

|                | 16  | Recommended Operating Conditions                                   |    |

|                | 17  | DC and AC Characteristics                                          |    |

|                | 18  | 3.3V External Power Supply Parameters                              | 19 |

|                | 19  | 1.9V External Power Supply Parameters                              | 19 |

|                | 20  | 1.2V External Power Supply Parameters                              |    |

|                | 21  | 3.3V External Power Supply Parameters                              | 21 |

|                | 22  | 82563EB/82564EB BOM (Bill of                                       |    |

|                |     | Material) of Components for Internal Regulator                     |    |

|                | 23  | 1.9V Internal LVR Specification                                    |    |

|                | 24  | 1.2V Internal LVR Specification                                    |    |

|                | 25  | PNP Specification                                                  |    |

|                | 26  | Link (MDI) Interface Electrical Specification                      |    |

|                | 27  | Kumeran (Serial) Transmit Specifications                           | 27 |

| 28 | Kumeran (Serial) Receive Specifications                              | 28 |

|----|----------------------------------------------------------------------|----|

| 29 | Kumeran (Serial) Electrical Idle Detection                           | 30 |

| 30 | Kumeran (Serial) Electrical Idle Output                              | 30 |

| 31 | Crystal Parameters                                                   | 31 |

| 32 | Specification for External Clock Oscillator                          |    |

| 33 | Reset Specification                                                  | 33 |

| 34 | Power Supply Characteristics - D0a (Both Ports)                      | 34 |

| 35 | Power Supply Characteristics - D3cold - Wake Up Enabled (Both Ports) | 34 |

| 36 | Power Supply Characteristics - Uninitialized/Disabled                | 34 |

| 37 | Power Supply Characteristics - Complete Subsystem                    | 35 |

| 38 | Thermal Characteristics                                              | 39 |

| 39 | 82563EB/82564EB Pinout by Pin Number Order                           | 40 |

|    |                                                                      |    |

Note: This page intentionally left blank.

#### 1.0 Introduction

The Intel® 82563EB Gigabit Platform LAN Connect is a dual, compact Physical Layer Transceiver (PHY) component designed for 10/100/1000 Mb/s operation. This device uses the Kumeran interface port of the 631xESB/632xESB I/O Controller Hub enabling the routing of long distances up to 28 inches (~711 mm). The 82564EB Gigabit Platform LAN Connect is the single port implementation. The Intel® 82563EB and 82564EB allow for Gigabit Ethernet implementations in a very small package; easing routing constraints from the 631xESB/632xESB I/O Controller Hub to the PHY.

The Intel® 82563EB/82564EB devices are based upon proven PHY technology integrated into Intel's Gigabit Ethernet Controllers. The physical layer circuitry provides a standard IEEE 802.3 Ethernet interface for 1000BASE-T, 100BASE-TX, and 10BASE-T applications (802.3, 802.3u, and 802.3ab). The 82563EB/82564EB devices are capable of transmitting and receiving data at rates of 1000 Mb/s, 100 Mb/s, or 10 Mb/s.

#### 1.1 Document Scope

This document contains datasheet specifications for the 82563EB/82564EB Gigabit Platform LAN Connect, including signal descriptions, DC and AC parameters, packaging data, and pinout information.

#### 1.2 Reference Documents

This document assumes that the designer is acquainted with high-speed design and board layout techniques. The following documents provide application information:

- 82563EB/82564EB LAN on Motherboard Design Guide (AP-467), Intel Corporation.

- 82563EB/82564EB Gigabit Platform LAN Connect Specification Update, Intel Corporation.

- 631xESB/632xESB I/O Controller Hub EEPROM Information Guide Application Note (AP-477), Intel Corporation.

- 82571/82572/ESB2 LAN System Manageability Application Note (AP-497), Intel Corporation.

- *IEEE Standard 1149.1*, 2001 Edition (JTAG). Institute of Electrical and Electronics Engineers (IEEE).

- *IEEE Standard* 802.3, 2002 Edition. Incorporates various IEEE Standards previously published separately. Institute of Electrical and Electronic Engineers (IEEE).

- Intel® 631xESB/632xESB I/O Controller Hub External Design Specification (EDS), Volumes 1-3, Intel Corporation.

- Bensley/Bensley-VS Platform Design Guide (PDG), Intel Corporation.

- *PICMG3.1 Ethernet/Fiber Channel Over PICMG 3.0 Draft Specification*, September 4, 2002, Version 0.90. PCI Industrial Computer Manufacturers Group (PICMG).

Software driver developers should contact their local Intel Representatives for programming information.

# 1.3 Product Codes

The following Table 1 lists the product ordering codes for the 82563EB dual port device and the 82564EB single port device.

**Table 1. Product Ordering Codes**

| Device                  | Product Code |

|-------------------------|--------------|

| Dual Port (Leaded)      | HU82563EB    |

| Single Port (Leaded)    | HU82564EB    |

| Dual Port (Lead Free)   | HY82563EB    |

| Single Port (Lead Free) | HY82564EB    |

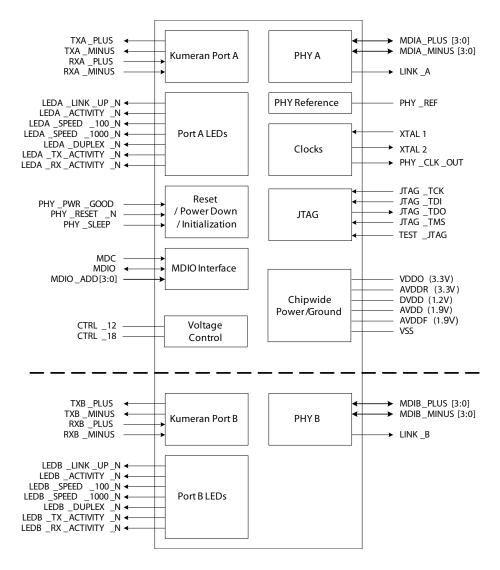

# 2.0 Block Diagrams

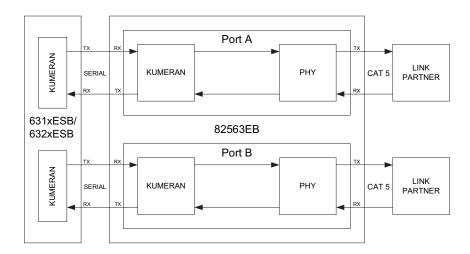

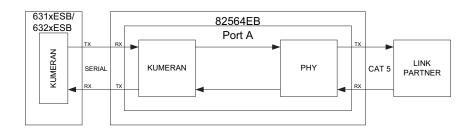

Figure 1. 82563EB Dual Port Block Diagram

Figure 2. 82564EB Single Port Block Diagram

*Note:* This page intentionally left blank.

# 3.0 Signal Descriptions

# 3.1 Signal Type Definitions

The signals of 82563EB/82564EB are defined as follows:

- I: Standard input-only signal

- I (T): Functional input signal implemented as a bidirectional for test

- **O**: Standard output-only signal

- O (T): Functional output signal implemented as a bidirectional for test

- I/O: Bi-directional, tri-state input/output signal

- **A**: Analog signal

- A-in: Analog input signal

- A-o: Analog output signal

- P: Power signal

- G: Ground signal

- NC: No connect (these signals must not be connected to any traces or planes)

- **B:** Input bias

Signals may be further qualified to indicate whether an internal pull-up or pull-down is normally active. Unless otherwise stated, internal pull-up and pull-down impedances are between 50 K $\Omega$ : and 130 K $\Omega$ .

- **PU**: Internal pull-up to VDD

- **PD**: Internal pull-down to VSS

It may be desirable to leave some input signals as no-connects in certain system applications that rely on a device's internal pull-up or pull-down signal to be active. Care should be taken to ensure there are no long traces, such as far-away test points or errant trace routings, on any inputs which rely solely on internal pull-devices. Excess capacitance of dangling traces may generate charge and/or noise on inputs which exceeds the capability of the internal pull-device, leading to unpredictable component behavior.

In addition to a primary type, each pin can be classified according to one of the following sub-types based on its electrical characteristics, such as input and output voltages and drive strengths.

- TTL: TTL compatible inputs

- TTL3: TTL compatible pins with at least 3mA drive strength

- TTL6: TTL compatible pins with at least 6mA drive strength

- TTL8: TTL compatible pins with at least 8mA drive strength

- TTL12:TTL compatible pins with at least 12mA drive strength

# 3.2 Shared PHY Pins

Table 1. Shared PHY Pins

| Signal Name | Pin | Туре | Sub-<br>Type | Description                                                             |

|-------------|-----|------|--------------|-------------------------------------------------------------------------|

| PHY_REF     | 50  | В    | В            | PHY Reference External 4.99 K $\Omega$ ± 1% resistor connection to VSS. |

# 3.3 MDIO Interface

#### Table 2. MDIO Interface Pins

*Note:* For normal operation, the MDIO interface is strapped externally according to Table 39 due to MDIO being an in-band operation.

| Signal Name                                     | Pin                  | Туре      | Sub-<br>Type | Description                                                                                                                                                                                                                                                                                                                                                                                   |

|-------------------------------------------------|----------------------|-----------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MDC                                             | 77                   | I (T)     | TTL          | Management Data Clock This signal is received from the 631xESB/632xESB as a clock timing reference for information transfer on the MDIO signal. It is not required to be a continuous signal and can be frozen when no management data is transferred. This signal has a maximum operating frequency of 2.5 MHz. A 1 - 10 K $\Omega$ ± 5% pull-down resistor should be connected to this pin. |

| MDIO                                            | 76                   | I/O<br>PU | TTL6         | Management Data Input/Output Bi-directional data signal of the management data interface. This pin has an internal pull-up. This signal can be left disconnected (or pulled up) if not used.                                                                                                                                                                                                  |

| MDIO_ADD[0] MDIO_ADD[1] MDIO_ADD[2] MDIO_ADD[3] | 78<br>79<br>18<br>19 | I (T)     | TTL          | Bits 4:1 of MDIO address  These bits are latched at the assertion of PHY_PWR_GOOD or the de-assertion of PHY_RESET_N or PHY_SLEEP. They set the MDIO address as follows:  • bit 1 = MDIO_ADD[0]  • bit 2 = MDIO_ADD[1]  • bit 3 = MDIO_ADD[2]  • bit 4 = MDIO_ADD[3]  A 1-10 kΩ ± 5% pull-down resistor should be connected to each of these pins.                                            |

# 3.4 Port A PHY Interface

*Note:* Port A on the 82563EB/82564EB corresponds to connection to Port 0 on the 631xESB/632xESB.

Table 3. Port A PHY Interface Pins

| Signal Name                   | Pin      | Туре | Sub-<br>Type | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-------------------------------|----------|------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MDIA_PLUS[0]<br>MDIA_MINUS[0] | 27<br>28 | А    | A            | Media Dependent Interface for Port A, bit 0  1000BASE-T:In MDI configuration, MDI[0]+/- corresponds to BI_DA+/- and in MDIX configuration MDI[0]+/- corresponds to BI_DB+/  100BASE-TX:In MDI configuration, MDI[0]+/- is used for the transmit pair and in MDIX configuration MDI[0]+/- is used for the receive pair.  10BASE-T: In MDI configuration, MDI[0]+/- is used for the transmit pair and in MDIX configuration MDI[0]+/- is used for                                      |

| MDIA_PLUS[1]<br>MDIA_MINUS[1] | 31<br>32 | A    | Α            | the receive pair.  Media Dependent Interface for Port A, bit 1  1000BASE-T:In MDI configuration, MDI[1]+/- corresponds to BI_DB+/- and in MDIX configuration MDI[1]+/- corresponds to BI_DA+/  100BASE-TX:In MDI configuration, MDI[1]+/- is used for the receive pair and in MDIX configuration MDI[1]+/- is used for the transmit pair.  10BASE-T: In MDI configuration, MDI[1]+/- is used for the receive pair and in MDIX configuration MDI[1]+/- is used for the transmit pair. |

| MDIA_PLUS[2]<br>MDIA_MINUS[2] | 33<br>34 | А    | Α            | Media Dependent Interface for Port A, bit 2  1000BASE-T:In MDI configuration, MDI[2]+/- corresponds to BI_DC+/- and in MDIX configuration MDI[2]+/- corresponds to BI_DD+/  100BASE-TX:Unused.  10BASE-T: Unused.                                                                                                                                                                                                                                                                    |

| MDIA_PLUS[3]<br>MDIA_MINUS[3] | 36<br>37 | А    | A            | Media Dependent Interface for Port A, bit 3  1000BASE-T:In MDI configuration, MDI[3]+/- corresponds to BI_DD+/- and in MDIX configuration MDI[3]+/- corresponds to BI_DC+/  100BASE-TX:Unused.  10BASE-T: Unused.                                                                                                                                                                                                                                                                    |

| LINK_A                        | 65       | I/O  | TTL8         | PHY A Link Indication  This signal is registered at the rising edge of PHY_PWR_GOOD, and is used to determine the clock speed used for PHY_CLK_OUT. Once PHY_PWR_GOOD is 1, LINK_A will always be an output and indicate link up.                                                                                                                                                                                                                                                    |

# 3.5 Port A Kumeran Interface

Table 4. Port A Kumeran Interface Pins

| Signal Name            | Pin      | Туре | Sub-<br>Type | Description                                                    |

|------------------------|----------|------|--------------|----------------------------------------------------------------|

| TXA_PLUS,<br>TXA_MINUS | 90<br>91 | А-о  | А            | Port A KumeranTX Pair Differential Kumeran Transmit interface. |

| RXA_PLUS,<br>RXA_MINUS | 93<br>94 | A-in | А            | Port A Kumeran RX Pair Differential Kumeran Receive interface. |

# 3.6 Port A LEDs

Table 5. Port A LEDs

| Signal Name       | Pin | Туре | Sub-<br>Type | Description                                                                                                                                                                  |

|-------------------|-----|------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                   |     |      |              | LED 0 – Link Up LED                                                                                                                                                          |

| LEDA_LINK_UP_N    | 73  | 0    | TTL12        | This corresponds to port 0's LED#0 from the 631xESB/632xESB.                                                                                                                 |

|                   |     |      |              | LED 1 – 10 Mbps LED                                                                                                                                                          |

| LEDA_ACTIVITY_N   | 72  | 0    | TTL12        | This corresponds to port 0's LED#1 from the 631xESB/632xESB.                                                                                                                 |

|                   |     |      |              | LED 2 – 100 Mbps LED                                                                                                                                                         |

| LEDA_SPEED_100_N  | 71  | 0    | TTL12        | This corresponds to port 0's LED#2 from the 631xESB/632xESB.                                                                                                                 |

|                   |     |      |              | LED 3 - 1000 Mbps LED                                                                                                                                                        |

| LEDA_SPEED_1000_N | 70  | 0    | TTL12        | This corresponds to port 0's LED#3 from the 631xESB/632xESB.                                                                                                                 |

|                   |     |      |              | LED 4 – Full Duplex LED                                                                                                                                                      |

| LEDA_DUPLEX       | 68  | 0    | TTL12        | This LED will light when port 0's PHY is operating in Full Duplex Mode                                                                                                       |

|                   |     |      |              | LED 5 – Transmit Activity LED                                                                                                                                                |

| LEDA_TX_ACTIVITY  | 67  | 0    | TTL12        | This LED will light when the port 0's PHY transmits a packet                                                                                                                 |

|                   |     |      |              | LED 6 – Receive Activity LED                                                                                                                                                 |

|                   |     |      | TTL12        | This LED will light when the port 0's PHY receives a packet                                                                                                                  |

| LEDA_RX_ACTIVITY  | 66  | 0    |              | This pin also functions as the clock view pin and will output clock signals required for IEEE conformance testing. This pin should have a stuffing option for a test header. |

# 3.7 Reset, Power Down, and Initialization Signals

Table 6. Reset and Power Down Signals

| Signal Name  | Pin | Туре  | Sub-<br>Type | Description                                                                                                                                                                                 |

|--------------|-----|-------|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PHY_PWR_GOOD | 83  | ı     | TTL          | Power Good (Power-On Reset)  The PHY_PWR_GOOD signal indicates good power is available for The device. When set to 0b, the entire chip will be held in a reset state.                       |

| PHY_RESET_N  | 81  | I     | TTL          | Reset When set to 0b, resets the device, including PHY and Kumeran logic. Needs an external pull-up resistor if the signal isn't continuously being driven from an external source.         |

| PHY_SLEEP    | 80  | I (T) | TTL          | Sleep / Power Down This will power down the PHY and the Kumeran of both ports. Needs an external pull-down resistor, if the signal isn't continuously being driven from an external source. |

| TEST_JTAG    | 95  | I PU  | TTL          | Enable JTAG Pin Control This pin should be pulled high through a 1 to 10 K $\Omega$ 5% resistor in normal operation.                                                                        |

# 3.8 JTAG and IEEE Interface

Table 7. JTAG Signals

| Signal Name | Pin | Туре | Sub-<br>Type | Description                                                                                                    |

|-------------|-----|------|--------------|----------------------------------------------------------------------------------------------------------------|

| JTAG_TCK    | 100 | I    | TTL          | JTAG Clock This pin should be pulled high through a 1 to 10 K $\Omega$ 5% resistor in normal operation.        |

| JTAG_TDI    | 1   | I PU | TTL          | JTAG Serial Data Input If not using JTAG, this pin may be pulled high through a 1 to 10 K $\Omega$ 5% resistor |

| JTAG_TDO    | 99  | 0    | TTL3         | JTAG Serial Data Output                                                                                        |

| JTAG_TMS    | 3   | I PU | TTL          | JTAG TMS Input If not using JTAG, this pin may be pulled high through a 1 to 10 K $\Omega$ 5% resistor         |

# 3.9 Reserved Signals

Table 8. Test Signals

| Signal Name | Pin                                                                               | Туре  | Sub-<br>Type | Description                                                                                                                                                       |

|-------------|-----------------------------------------------------------------------------------|-------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RESERVED_NC | 4<br>5<br>6<br>8<br>9<br>10<br>13<br>14<br>15<br>17<br>26<br>49<br>52<br>53<br>98 | NC    | NC           | Reserved No Connect  This pin should be left disconnected in normal operation.  Connecting any of these pins may cause adverse effects and will not be supported. |

| RESERVED_PD | 82                                                                                | I (T) | TTL          | Reserved, Pull-down This signal used in the XOR chain. It should be pulled to VSS via a 1 to10 K $\Omega$ resistor.                                               |

# 3.10 Voltage Control Pins

Table 9. Voltage Control Pins

| Signal Name | Pin | Туре | Sub-<br>Type | Description                                                                                                                          |  |

|-------------|-----|------|--------------|--------------------------------------------------------------------------------------------------------------------------------------|--|

|             |     |      |              | 1.9V LVR Power Output Reference                                                                                                      |  |

| CTRL_18     | 25  | А    | Α            | Voltage control for an external 1.9V PNP transistor in order to produce a linearly-regulated supply.                                 |  |

|             |     |      |              | If the 1.9V internal voltage regulator control circuit is not used, connect the CTRL_18 pin to VSS through a 10 K $\Omega$ resistor. |  |

|             |     |      |              | 1.2V LVR Power Output Reference                                                                                                      |  |

| CTRL_12     | 23  | А    | Α            | Voltage control for an external 1.2V PNP transistor in order to produce a linearly-regulated supply.                                 |  |

|             |     |      |              | If the 1.2V internal voltage regulator control circuit is not used, connect the CTRL_12 pin to VSS through a 10 K $\Omega$ resistor. |  |

# 3.11 Clock Generator Interface

**Table 10. Clock Generator Related Signals**

| Signal Name | Pin      | Туре | Sub-<br>Type | Description                                                                                                                                           |  |

|-------------|----------|------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|             |          |      |              | 25 MHz Clock/Crystal Input 25 MHz +/- 50 ppm input. Can be connected to an oscillator or a                                                            |  |

| XTAL1 21    |          | I    | TTL          | crystal. If using a crystal, XTAL2 must be connected as well. If a crystal is used, it must be placed within ½-inch of the XTAL1 and XTAL2 chip pins. |  |

|             |          |      |              | 25 MHz Crystal Output                                                                                                                                 |  |

| XTAL2       | 20 A-o A |      | А            | Output of internal oscillator circuit used to drive crystal into oscillation. If using an oscillator, XTAL2 is left as a no connect.                  |  |

|             |          |      | TTL8         | Clock Output                                                                                                                                          |  |

|             |          |      |              | Output clock available for use by a 631xESB/632xESB or other component(s).                                                                            |  |

|             |          |      |              | The speed depends on the how LINK_A is sampled at LAN_PWR_GOOD assertion:                                                                             |  |

| DUN CLK OUT | 00       |      |              | If LINK_A is 0b, the clock speed is 62.5 MHz.                                                                                                         |  |

| PHY_CLK_OUT | 96       | 0    |              | If LINK_A is 1b, the clock speed is 25 MHz.                                                                                                           |  |

|             |          |      |              | The output clock can be disabled depending on how LINK_B is sampled at LAN_PWR_GOOD assertion:                                                        |  |

|             |          |      |              | If LINK_B is 0b: Clock output enabled (pulled-down).                                                                                                  |  |

|             |          |      |              | If LINK_B is 1b: Clock output disabled (no connect).                                                                                                  |  |

# 3.12 Power/Ground Pins

Table 11. Power/Ground Pins (Sheet 1 of 2)

| Signal Name | Pin     | Туре | Sub-<br>Type | Description                                                                           |  |  |

|-------------|---------|------|--------------|---------------------------------------------------------------------------------------|--|--|

| VSS         | Central | G    | G            | Ground Exposed-Pad*                                                                   |  |  |

| V 33        | Pad     |      |              | The ground is provided through a large central pad on the bottom side of the package. |  |  |

| VSS         | 89      | G    | G            | Ground                                                                                |  |  |

|             | 11      |      |              |                                                                                       |  |  |

|             | 22      |      |              |                                                                                       |  |  |

| VDDO        | 60      | Р    | Р            | 3.3V I/O Ring Power                                                                   |  |  |

|             | 75      |      |              |                                                                                       |  |  |

|             | 97      |      |              |                                                                                       |  |  |

Table 11. Power/Ground Pins (Sheet 2 of 2)

| Signal Name | Pin                                        | Туре | Sub-<br>Type | Description                              |

|-------------|--------------------------------------------|------|--------------|------------------------------------------|

| DVDD        | 2<br>7<br>12<br>16<br>59<br>64<br>69<br>74 | Р    | Р            | 1.2V Digital Power                       |

| AVDD        | 29<br>30<br>35<br>40<br>45<br>46           | Р    | Р            | 1.9V Analog Power for PHY                |

| AVDDF       | 86<br>92                                   | Р    | Р            | 1.9V Analog Power for Kumeran            |

| AVDDR       | 24<br>51                                   | Р    | Р            | 3.3V Analog Power for Voltage Regulators |

# 3.13 Port B PHY Interface

**Note:** Port B on the 82563EB dual port device corresponds to connection to Port 1 on the 631xESB/632xESB. There is no port B on the 82564EB.

Table 12. Port B PHY Interface Pins (Sheet 1 of 2)

| Signal Name                   | Pin      | Туре | Sub-<br>Type | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Connection on<br>82564EB<br>Single Port Device |

|-------------------------------|----------|------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|

| MDIB_PLUS[0]<br>MDIB_MINUS[0] | 48<br>47 | Α    | A            | Media Dependent Interface for Port B, bit 0  1000BASE-T:In MDI configuration, MDI[0]+/- corresponds to BI_DA+/- and in MDIX configuration MDI[0]+/- corresponds to BI_DB+/  100BASE-TX:In MDI configuration, MDI[0]+/- is used for the transmit pair and in MDIX configuration MDI[0]+/- is used for the receive pair.  10BASE-T: In MDI configuration, MDI[0]+/- is used for the transmit pair and in MDIX configuration MDI[0]+/- is used for the transmit pair and in MDIX configuration MDI[0]+/- is used for the receive pair. | No-connect                                     |

| MDIB_PLUS[1]<br>MDIB_MINUS[1] | 44 43    | Α    | Α            | Media Dependent Interface for Port B, bit 1  1000BASE-T:In MDI configuration, MDI[1]+/- corresponds to BI_DB+/- and in MDIX configuration MDI[1]+/- corresponds to BI_DA+/  100BASE-TX:In MDI configuration, MDI[1]+/- is used for the receive pair and in MDIX configuration MDI[1]+/- is used for the transmit pair.  10BASE-T: In MDI configuration, MDI[1]+/- is used for the receive pair and in MDIX configuration MDI[1]+/- is used for the receive pair and in MDIX configuration MDI[1]+/- is used for the transmit pair.  | No-connect                                     |

Table 12. Port B PHY Interface Pins (Sheet 2 of 2)

| Signal Name                   | Pin       | Туре | Sub-<br>Type | Description                                                                                                                                                                                                                               | Connection on<br>82564EB<br>Single Port Device |

|-------------------------------|-----------|------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|

|                               |           |      |              | Media Dependent Interface for Port B, bit 2                                                                                                                                                                                               |                                                |

| MDIB_PLUS[2]<br>MDIB_MINUS[2] | 42<br>41  | А    | А            | 1000BASE-T:In MDI configuration, MDI[2]+/- corresponds to BI_DC+/- and in MDIX configuration MDI[2]+/- corresponds to BI_DD+/                                                                                                             | No-connect                                     |

|                               |           |      |              | 100BASE-TX:Unused.                                                                                                                                                                                                                        |                                                |

|                               |           |      |              | 10BASE-T: Unused.                                                                                                                                                                                                                         |                                                |

| MDIB_PLUS[3]<br>MDIB_MINUS[3] | 39<br>38  | А    | А            | Media Dependent Interface for Port B, bit 3  1000BASE-T:In MDI configuration,                                                                                                                                                             | No-connect                                     |

|                               |           |      |              | PHY B Link Indication                                                                                                                                                                                                                     |                                                |

| LINK_B                        | 54 I/O TT |      | TTL8         | This signal is registered at the rising edge of PHY_PWR_GOOD, and is used to determine whether PHY_CLK_OUT is output. See the PHY_CLK_OUT pin for details. Once PHY_PWR_GOOD is 1b, LINK_B will always be an output and indicate link up. | See Table 10                                   |

# 3.14 Port B Kumeran Interface

Table 13. Port B Kumeran Interface Pins

| Signal Name           | Pin      | Туре | Sub-<br>Type | Description                                                     | Connection on<br>82564EB<br>Single Port Device |

|-----------------------|----------|------|--------------|-----------------------------------------------------------------|------------------------------------------------|

| TXB_PLUS<br>TXB_MINUS | 88<br>87 | А-о  | Α            | Port B Kumeran TX Pair Differential Kumeran Transmit interface. | No-connect                                     |

| RXB_PLUS<br>RXB_MINUS | 85<br>84 | A-in | Α            | Port B Kumeran RX Pair Differential Kumeran Receive interface.  | No-connect                                     |

# 3.15 Port B LEDs

Table 14. Port B LEDs

| Signal Name           | Pin                                                                                                              | Туре | Sub-<br>Type                                                                             | Description                                                                                     | Connection on<br>82564EB<br>Single Port<br>Device |

|-----------------------|------------------------------------------------------------------------------------------------------------------|------|------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|---------------------------------------------------|

| LEDB_LINK_UP_N        | 63                                                                                                               | 0    | TTL12                                                                                    | LED 0 – Link Up/Activity LED  This corresponds to port 1's LED#0 from the 631xESB/632xESB.      | No-connect                                        |

| LEDB_ACTIVITY_N       | 62                                                                                                               | 0    | TTL12                                                                                    | LED 1 – 10 Mbps LED  This corresponds to port 1's LED#1 from the 631xESB/632xESB.               | No-connect                                        |

| LEDB_SPEED_100_<br>N  | 61                                                                                                               | 0    | TTL12 LED 2 – 100 Mbps LED  This corresponds to port 1's LED#2 from the 631xESB/632xESB. |                                                                                                 | No-connect                                        |

| LEDB_SPEED_1000_<br>N | 58                                                                                                               | 0    | TTL12                                                                                    | LED 3 – 1000 Mbps LED  This corresponds to port 1's LED#3 from the 631xESB/632xESB.             | No-connect                                        |

| LEDB_DUPLEX           | 57                                                                                                               | 0    | TTL12                                                                                    | LED 4 – Full Duplex LED  This LED will light when port 1's PHY is operating in Full Duplex Mode | No-connect                                        |

| LEDB_TX_ACTIVITY      | DB_TX_ACTIVITY 56 O TTL12 LED 5 - Transmit Activity LED This LED will light when port 1's PHY transmits a packet |      | No-connect                                                                               |                                                                                                 |                                                   |

| LEDB_RX_ACTIVITY      | LED 6 – Receive Activity LED  This LED will light when port 1's PHY receives a packet                            |      | No-connect                                                                               |                                                                                                 |                                                   |

*Note:* This page intentionally left blank.

# 4.0 Voltage, Temperature and Timing Specifications

# 4.1 Absolute Maximum Ratings

Table 15. Absolute Maximum Ratings<sup>a</sup>

| Symbol           | Parameter            | Min  | Max                   | Unit |

|------------------|----------------------|------|-----------------------|------|

| V <sub>DD</sub>  | DC supply voltage    | -0.3 | 4.6                   | V    |

| V <sub>IN</sub>  | Input voltage        | -1.0 | V <sub>DD</sub> + 0.3 | V    |

| I <sub>IN</sub>  | DC input pin current | -10  | 10                    | mA   |

| T <sub>STG</sub> | Storage temperature  | -40  | 125                   | °C   |

a. Maximum ratings are referenced to ground (VSS). Permanent device damage is likely to occur if the ratings in this table are exceeded for an indefinite duration. These values should not be used as the limits for normal device operations.

# 4.2 Recommended Operating Conditions

**Table 16. Recommended Operating Conditions**

| Symbol          | Parameter                    | Condition                    | Min  | Тур  | Max  | Unit |

|-----------------|------------------------------|------------------------------|------|------|------|------|

| T <sub>OP</sub> | Operating Temperature        | Convection only <sup>a</sup> | 0    |      | 60   | °C   |