# Datasheet

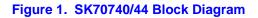

The SK70740 and SK70744 chip set provide full-duplex, T1 (DS-1) transmission over a single twisted pair. The chip set is capable of providing Overlapped PAM Transmission with Interlocking Spectra (OPTIS) power spectral density (PSD). The chip set consists of two ICs that provide the HDSL2 modem solution:

- SK70740HE Analog Front End (AFE)

- SK70744HE Transceiver/Framer

The SK70740 AFE is separated into a transmit and receive channel. In the transmit channel, the AFE receives a pulse width modulated data stream from the digital transceiver. Switched capacitor filters shape the transmitted signal to suppress out-of-band noise. The receive channel consists of an automatic gain control (AGC) stage and an analog to digital (A/D) converter. The dynamic range of the receive channel is over 80 dB.

The core of the SK70744 Transceiver/Framer is a Trellis Coded PAM modulator/demodulator. HDSL2 utilizes shaped PAM-16 modulation to minimize interference into other services. The transmit filter can be programmed through firmware, allowing the transmit power spectrum to be optimized for the regional conditions. In addition, Trellis Coding (TC) and Viterbi Decoding, allows the system to provide high signal to noise margin in the presence of crosstalk noise from other services.

The frame mapping function inserts and recovers the HDSL2 overhead. Interrupt alarms are provided for loss of sync and CRC errors. The system also has read/write register access to the Embedded Operations Channel (EOC) bits within the HDSL2 frame. A synchronous data interface allows use with common T1 framers.

# **Applications**

- T1 transport systems

- Multi-channel digital pair gain systems

- WAN access for LAN routers and switches

# **Product Features**

- Supports ANSI T1E1.418 (HDSL2) specification

- Programmable for either Central Office (H2TU-C) or Remote (H2TU-R) applications

- Operates from a single crystal reference

- High resolution, Delta-Sigma A/D converter

- Integrated access devices

- Wireless access systems

- I/O operates at 3.3 V logic levels and is 5V tolerant

- Intel/Motorola compatible 8-bit microprocessor interface allows rapid setup, acquisition and status monitoring

- Programmable activation controller minimizes load on the system processor

- Internal circuitry for wander reduction

As of January 15, 2001, this document replaces the Level One document SK70740/44 HDSL2 Modem Chip Set Datasheet.

Order Number: 249345-001 January 2001

Information in this document is provided in connection with Intel<sup>®</sup> products. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Intel's Terms and Conditions of Sale for such products, Intel assumes no liability whatsoever, and Intel disclaims any express or implied warranty, relating to sale and/or use of Intel products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. Intel products are not intended for use in medical, life saving, or life sustaining applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

The SK70740/44 may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an ordering number and are referenced in this document, or other Intel literature may be obtained by calling 1-800-548-4725 or by visiting Intel's website at http://www.intel.com.

Copyright © Intel Corporation, 2001

\*Third-party brands and names are the property of their respective owners.

# intപ്രം Contents

| 1.0 | Pin A                                  | Assignments and Signal Descriptions                                                                                                                                                                                                          | 10                         |

|-----|----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

| 2.0 | Gene                                   | eral Functional Description                                                                                                                                                                                                                  | 19                         |

|     | 2.1<br>2.2<br>2.3                      | Overview<br>Transceiver-AFE Interfaces<br>2.2.1 Data Interface<br>2.2.2 Control Interface<br>JTAG Interface                                                                                                                                  | 20<br>20<br>20             |

| 3.0 | AFE                                    | Functional Description                                                                                                                                                                                                                       | 22                         |

|     | 3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6 | Upstream and Downstream Spectrums<br>Transmitter<br>Receiver<br>Line Interface<br>Reference Clock<br>Loopbacks                                                                                                                               | 22<br>23<br>23<br>24<br>25 |

| 4.0 | Tran                                   | sceiver/Framer Functional Description                                                                                                                                                                                                        | 26                         |

|     | 4.1                                    | TDM Interface<br>4.1.1 T1 Transport Operation                                                                                                                                                                                                |                            |

|     | 4.2                                    | T1 Frame Mapping         4.2.1       Transmit Frame Mapping         4.2.2       Receive Frame Mapping                                                                                                                                        | 27                         |

|     | 4.3<br>4.4                             | Frame Synchronization<br>Forward Error Correction (FEC)<br>4.4.1 FEC Encoder<br>4.4.2 FEC Decoder                                                                                                                                            | 32<br>34<br>34             |

|     | 4.5<br>4.6<br>4.7<br>4.8<br>4.9        | PAM TransmitterReceiverClock GenerationNoise Margin and SNR EstimationActivation4.9.1Pre-Activation4.9.2Primary Activation4.9.3Inactive State4.9.4Activating State4.9.5Active State4.9.6FSTAT4.9.7Hold (Pending) State4.9.8Deactivated State |                            |

|     | 4.10<br>4.11<br>4.12<br>4.13           | 4.9.9       Activating State Machine         Activation Frame       Power Down         Power Down       Loopbacks         Microprocessor Interface       Microprocessor Interface                                                            | 43<br>45<br>45             |

| 5.0 | Regi | ster Definitions                                  |

|-----|------|---------------------------------------------------|

|     | 5.1  | AFE Registers                                     |

|     | 5.2  | Transceiver/Framer Registers                      |

|     | 5.3  | PAM Transceiver Registers51                       |

|     |      | 5.3.1 Registers 03h through 09h are Reserved      |

|     |      | 5.3.2 Registers 0Fh through 17h are Reserved54    |

|     |      | 5.3.3 Registers 1Bh through 21h are Reserved54    |

|     |      | 5.3.4 Registers 23h and 24h are Reserved54        |

|     |      | 5.3.5 Registers 26h through 2Ch are Reserved55    |

|     |      | 5.3.6 Registers 34h through 7Fh are Reserved56    |

|     | 5.4  | FEC Registers                                     |

|     |      | 5.4.1 FEC Encoder/Decoder Configuration Registers |

|     |      | 5.4.2 FEC Noise Register                          |

|     |      | 5.4.3 Registers 86h through 92h are Reserved      |

|     |      | 5.4.4 Registers 94h through 9Fh are Reserved      |

|     | 5.5  | Framer Transmit Registers58                       |

|     |      | 5.5.1 Registers ABh through B0h are Reserved      |

|     | 5.6  | Framer Receive Registers63                        |

|     |      | 5.6.1 Receive FIFO Water Level64                  |

|     |      | 5.6.2 PLL Synthesizer Registers                   |

|     |      | 5.6.3 Registers CCh through D1h are Reserved67    |

|     |      | 5.6.4 Registers D6h through DCh are Reserved      |

|     |      | 5.6.5 Registers DF through FF are Reserved        |

| 6.0 | Anal | og Front End Test Specifications                  |

| 7.0 | Tran | sceiver/Framer Test Specifications                |

| 8.0 | Mecl | hanical Specifications                            |

# **Figures**

| 1  | SK70740/44 Block Diagram                               | 9  |

|----|--------------------------------------------------------|----|

| 2  | Analog Front End Pin Assignments                       | 10 |

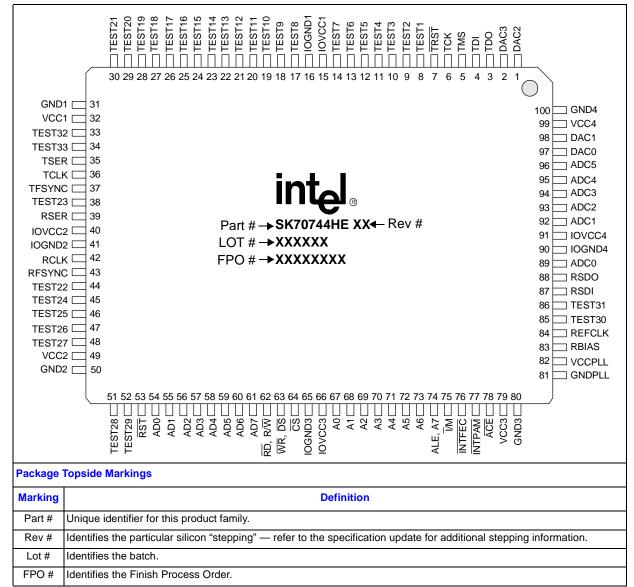

| 3  | Transceiver/Framer Pin Assignments                     | 14 |

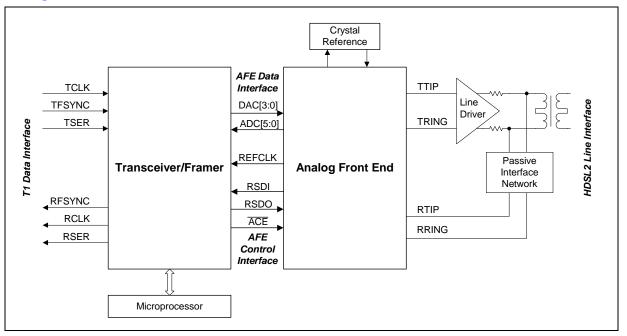

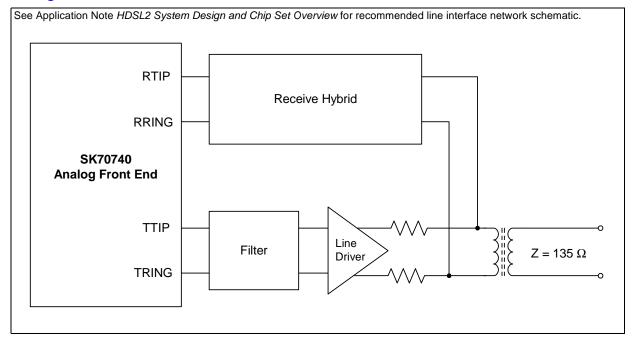

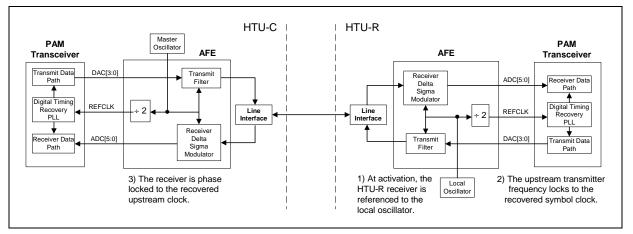

| 4  | HDSL2 Modem                                            | 19 |

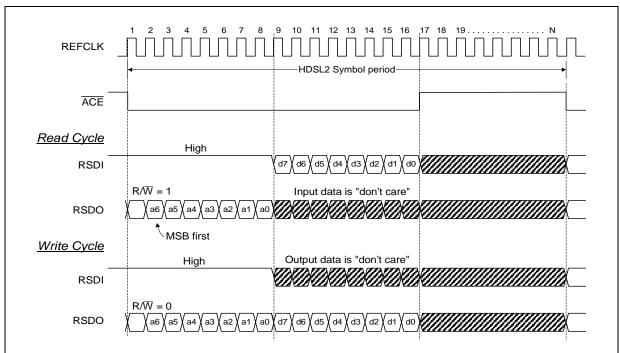

| 5  | Transceiver/AFE Control Interface Data Structure       | 21 |

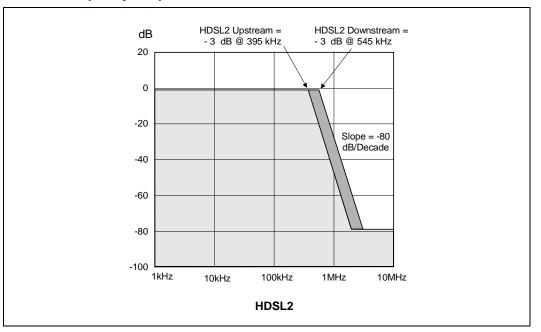

| 6  | Transmit Frequency Response                            |    |

| 7  | Line Interface Network                                 |    |

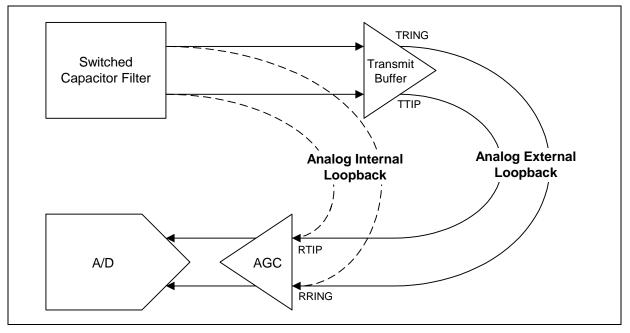

| 8  | Loopback Data Paths                                    | 25 |

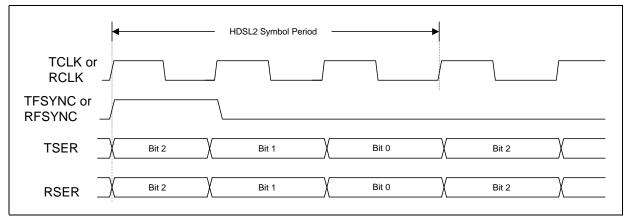

| 9  | Relative Timing for TDM Interface in T1 Transport Mode |    |

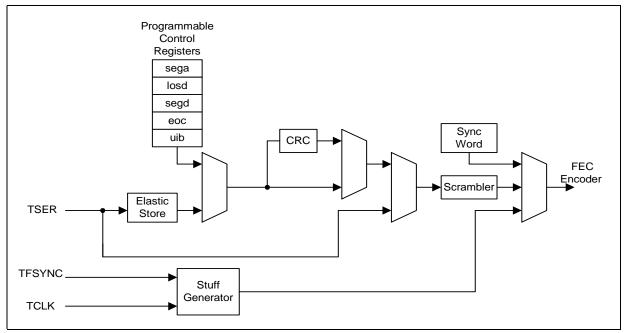

| 10 | Transmit Framer Block Diagram                          |    |

| 11 | HDSL2 Frame Format for T1 Payload                      |    |

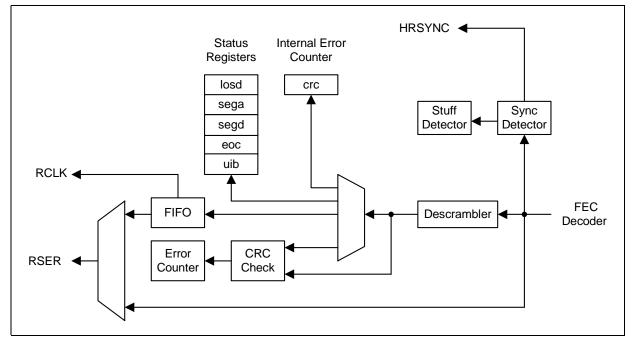

| 12 | Receive Framer Block Diagram                           |    |

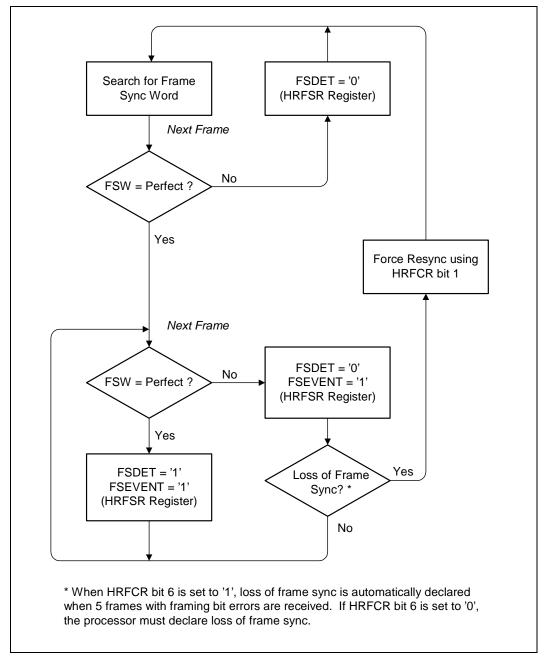

| 13 | Frame Synchronization Operation                        |    |

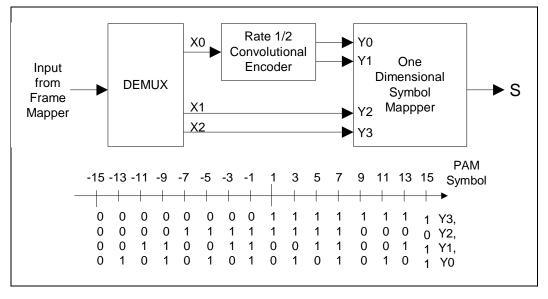

| 14 | FEC Encoder and Symbol Mapping                         |    |

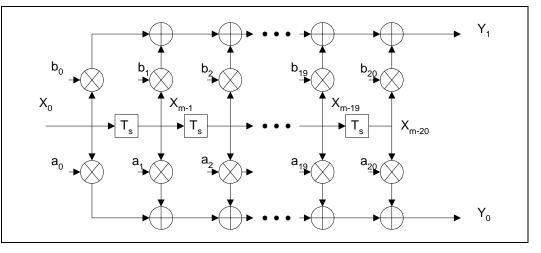

| 15 | Convolutional Encoder                                  | 35 |

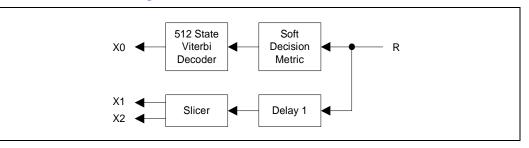

| 16 | FEC Decoder Block Diagram                              |    |

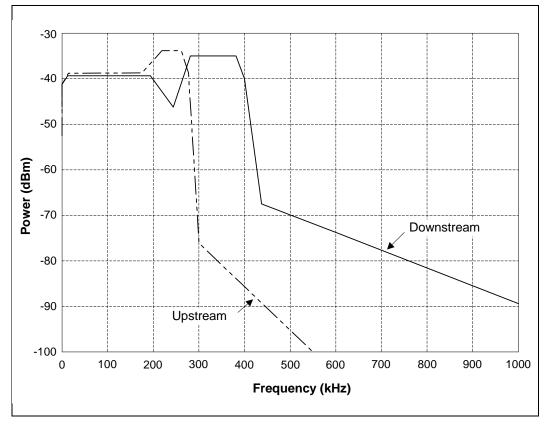

| 17 | HDSL2 PSD Mask for North America                       |    |

| 18 | Clock Generation                                       |    |

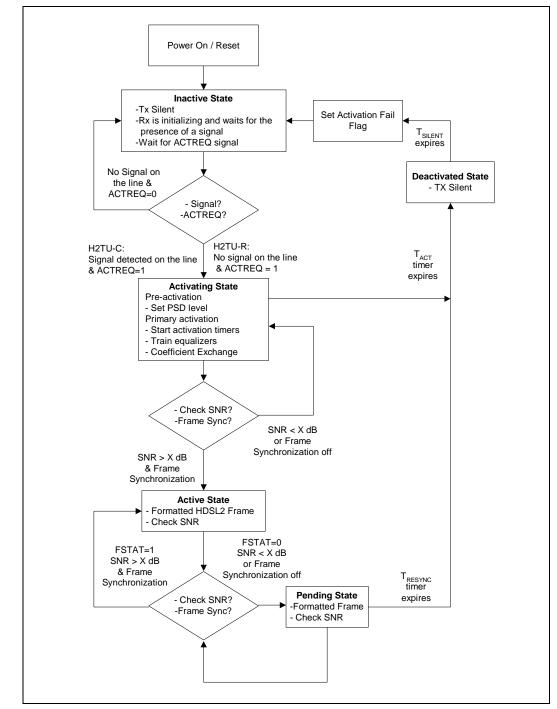

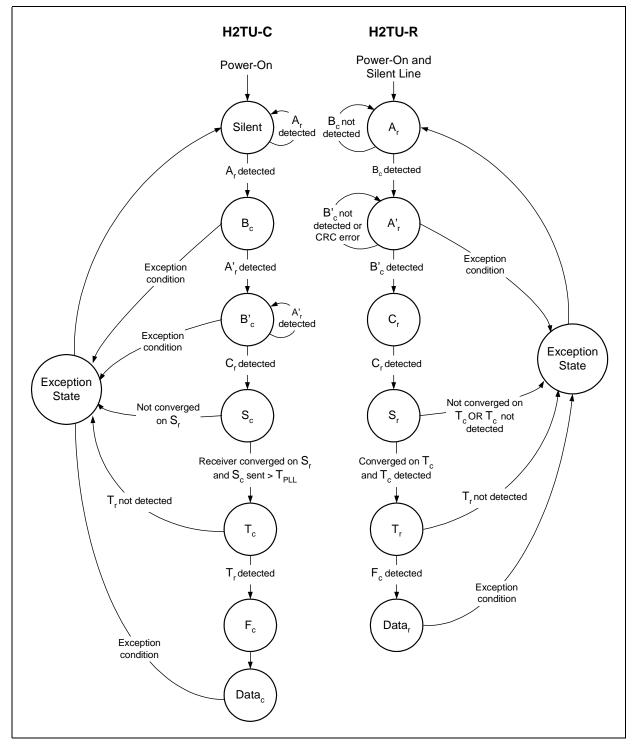

| 19 | Simplified State Transition at Activation    | 40 |

|----|----------------------------------------------|----|

| 20 | Start-Up Sequence                            | 44 |

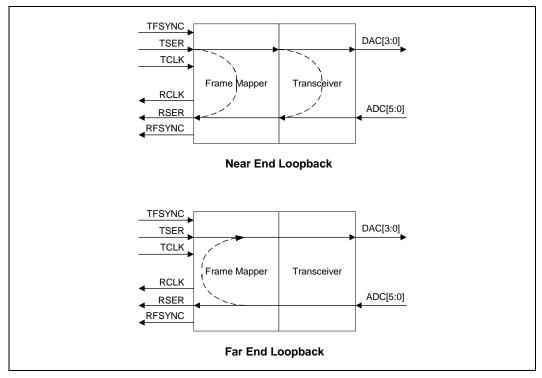

| 21 | System Loopback Options                      | 46 |

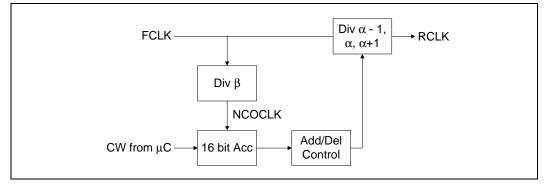

| 22 | RCLK Generation Circuit                      | 66 |

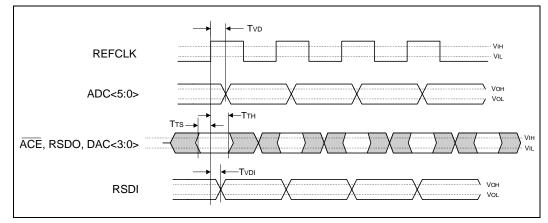

| 23 | AFE Interface Timing                         | 71 |

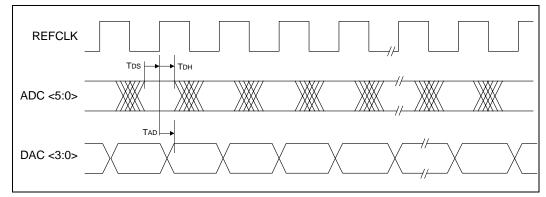

| 24 | AFE Data Interface Relative Timing           | 73 |

| 25 | AFE Control Interface Relative Timing        | 74 |

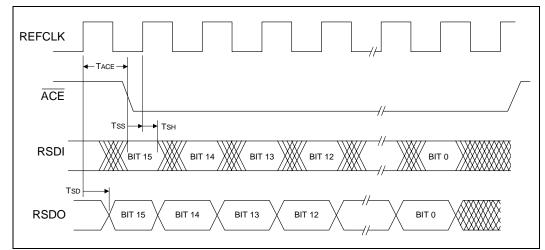

| 26 | TDM Interface Timing - T1 Transport Mode     | 75 |

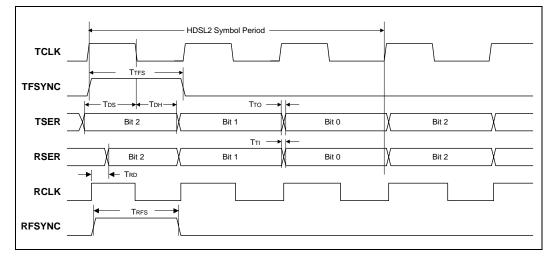

| 27 | Parallel Microprocessor Bus Interface Timing | 77 |

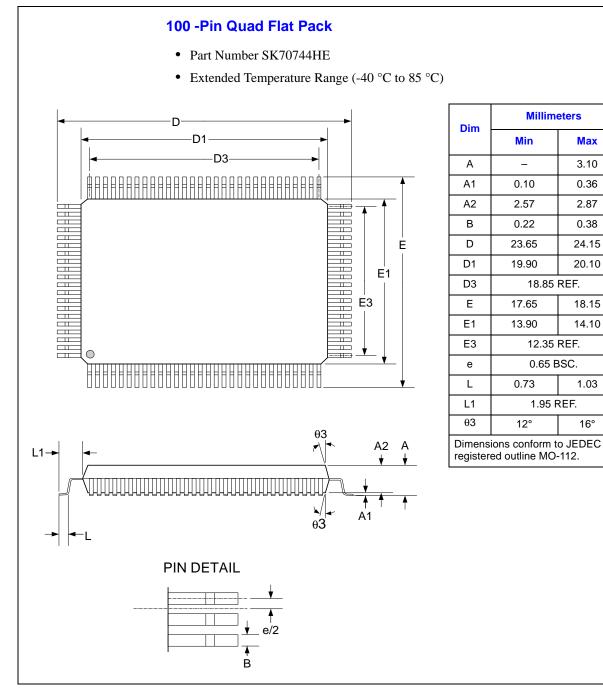

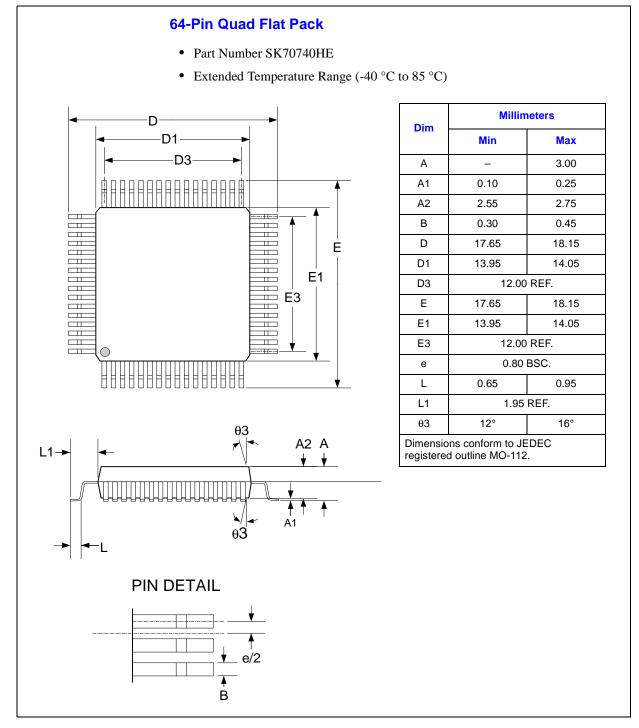

| 28 | 64 Pin QFP Package                           | 78 |

| 29 | 100 Pin QFP Package                          |    |

|    | -                                            |    |

# **Tables**

| 1  | SK70740 Analog Front End Signal Descriptions                         | 11 |

|----|----------------------------------------------------------------------|----|

| 2  | SK70744 Transceiver/Framer Signal Descriptions                       |    |

| 3  | HDSL2 Frame Structure for T1                                         | 29 |

| 4  | HDSL2 Overhead Bit to Register Mapping                               |    |

| 5  | Pre-Activation Frame                                                 |    |

| 6  | Start-up Timers                                                      | 42 |

| 7  | Activation Frame Format (Optional)                                   | 45 |

| 8  | AFE Control Register 1, AR1, R/W, Address = 00h, Default = 00h       | 47 |

| 9  | AFE Control Register 2, AR2, R/W, Address = 01h, Default = 00h       | 48 |

| 10 | Transceiver/Framer Register Categories                               |    |

| 11 | Transceiver/Framer Register Summary                                  | 49 |

| 12 | Main Control Register 0, MAIN0, R/W, Address = 00h, Default = 00h    | 51 |

| 13 | Main Control Register 1, MAIN1, R/W Address = 01h, Default = 20h     | 52 |

| 14 | Activation Mode Control Register, ACT_MODE, R/W, Address = 02h,      |    |

|    | Default = 00h                                                        | 52 |

| 15 | AFE Control Register, AFE_CTL, R/W, Address 0Ah, Default = FFh       | 52 |

| 16 | AFE Address Register, AFE_ADD1 , R/W, Address = 0Bh, Default = 80h   | 52 |

| 17 | Interrupt Mask Register, INT_MSK1, R/W, Address = 0Ch, Default = FFh | 53 |

| 18 | Interrupt State Register, INT_ST1, R/W, Address = 0Dh, Default = 00h | 53 |

| 19 | Hardware Configuration Register, HW_CFG, R, Address = 0Eh,           |    |

|    | Default = F0h                                                        |    |

| 20 | Rate Select 0 Register, RATE_SEL0, R/W, Address = 18h, Default = AAh |    |

| 21 | Rate Select 1 Register, RATE_SEL1, R/W, Address = 19h, Default = AAh |    |

| 22 | Rate Select 2 Register, RATE_SEL2, R/W, Address = 1Ah, Default = ABh |    |

| 23 | TIP/RING Reversal, TIP/RING, R, Address = 22h, Default = 00h         |    |

| 24 | Framer Status Register, FSTAT, R/W, Address = 25h, Default = 00h     |    |

| 25 | AFE Status Register, AFE_STAT, R/W, Address = 2Dh, Default = 00h     |    |

| 26 | Soft Decision (LSB) Register, SFT0, R, Address = 2Eh, Default = 00 h |    |

| 27 | Soft Decision (MSB) Register, SFT1, R, Address = 2Fh, Default = 00h  |    |

| 28 | PLL Control Register, PLL_CTL, R/W, Address = 30h, Default = 00h     |    |

| 29 | Main Control Register 2, MAIN2, R/W, Address = 31h, Default = 01h    | 55 |

| 30 | Miscellaneous Control Register 1, MISC1, R/W, Address = 32h,         |    |

|    | Default = 00h                                                        | 56 |

| 31 | Wander Reduction Control Register, HTMCR, R/W, Address = 33h,        | _  |

|    | Default = 00h                                                        |    |

| 32 | Code Generator Select, CGSEL, R/W, Address = 80h, Default = 00h      | 56 |

| 33       | Code Generator 1, CG1, R/W, Address = 81h, Default = DAh                          |    |

|----------|-----------------------------------------------------------------------------------|----|

| 34       | Code Generator 2, CG2, R/W, Address = 82h Default = CDh                           |    |

| 35       | Code Generator 3, CG3, R/W, Address = 83h, Default = 08h                          |    |

| 36       | FEC Trace Back, FECTB, R/W, Address = 84h, Default = 00h                          |    |

| 37       | FEC Noise, FECNS, R, Address = 85h                                                |    |

| 38       | FEC Control, FECCR, R/W, Address = 93h, Default = 00h                             |    |

| 39       | Framer Payload Rate, PLRATE, R/W, Address = A0h, Default = 18h                    | 58 |

| 40       | Reference Transmit Water Level, HTFWL, R/W, Address = A1h,<br>Default = 2Eh       | 59 |

| 41       | Actual Transmit Water Level, TFWL, R, Address = A2h                               |    |

| 42       | Transmit Control Register, HTFCR, R/W, Address = A3h, Default = 08h               |    |

| 43       | Transmit Test Control Register, HTFTCR, R/W, Address = A4h,<br>Default = 00h      |    |

| 44       | Transmit Data Byte Selection Register, HTFBSR, R/W, Address = A5h, Default = 00   |    |

| 45       | Data Read Sample (High) Register, HTFRSRH, R, Address = A6h                       |    |

| 46       | Data Read Sample (Low) Register, HTFRSRL, R, Address = A7h                        |    |

| 47       | Transmit Frame Control Register, HTFTMR, R/W, Address = A8h,<br>Default = 00h     |    |

| 10       | All 1's / 0's Control                                                             |    |

| 48       | Transmit Sync Word (First 8 bits), HTFFSW1, R/W, Address = A9h                    | 01 |

| 49       | Default = $00h$                                                                   | 61 |

| 50       | Transmit Sync Word (Last 2 bits), HTFFSW2, R/W, Address = AAh                     |    |

| - 4      | Default = 00h                                                                     | 61 |

| 51       | HDSL2 Transmit Overhead Register 1, HTFHOH1, R/W, Address = B1h,<br>Default = 00h | 62 |

| 52       | HDSL2 Transmit Overhead Register 2, HTFHOH2, R/W, Address=B2h,<br>Default=00h     | 62 |

| 53       | HDSL2 Transmit Overhead Register 3, HTFHOH3, R/W, Address = B3h,<br>Default = 00h |    |

| 54       | HDSL2 Transmit Overhead Register 4, HTFHOH4, R/W, Address = B4h,                  | 02 |

| 54       | Default = 00h                                                                     | 63 |

| 55       | Receive Control Register, HRFCR, R/W, Address = C0h, Default 00h                  | 63 |

| 56       | Receive Test Control Register, HRFTCR, R/W, Address = C1h,<br>Default = 00h       | 64 |

| 57       | Receive FIFO Water Level Register, HRFWL, R, Address = C2h                        |    |

| 58       | FIFO Depth Register, HRFFDR, R, Address = C3h                                     |    |

| 59       | Receive Status Register, HRFSR Register, R, Address = C4h                         |    |

| 60       | Receive Timing & Loopback Register, HRFTTCR, R/W, Address = C5h, Default = 00h    |    |

| 61       | NCO Control Register (MSB), HRFNCR1, R/W, Address = C6h,                          |    |

| 62       | Default = 17h<br>NCO Control Register (LSB), HRFNCR2, R/W, Address = C7h,         | 00 |

| 02       | Default = $5Ah$                                                                   | 66 |

| 63       | DPLL Phase Adjustment Register, HRFPAJ, R/W, Address = CAh,                       |    |

| <b>.</b> | Default = 2Ch                                                                     |    |

| 64       | DPLL Clock Division Ratio, HRFPAC, R/W, Address = CBh, Default =15h               |    |

| 65       | CRC Counter Register, HRFCRC, R, Address = C9h                                    |    |

| 66       | HDSL2 Receive Overhead Register 1, HRFHOH1, R, Address = D2h                      |    |

| 67       | HDSL2 Receive Overhead Register 2, HRFHOH2, R, Address = D3h                      |    |

| 68       | HDSL2 Receive Overhead Register 3, HRFHOH3, R, Address = D4h                      | 67 |

### HDSL2 Modem Chip Set — SK70740/44

# intel®

| 69 | HDSL2 Receive Overhead Register 4, HRFHOH4, R, Address = D5h             | 68 |

|----|--------------------------------------------------------------------------|----|

| 70 | Receive Frame Sync Word (First 8 bits), HRFFSW1, R/W, Address = DDh,     |    |

|    | Default = 00h                                                            | 68 |

| 71 | Receive Frame Sync Word & Stuff Bits, HRFFSWSB, R/W, Address = DEh,      |    |

|    | Default = 00h                                                            | 68 |

| 72 | Absolute Maximum Ratings                                                 | 69 |

| 73 | Recommended Operating Conditions                                         | 69 |

| 74 | DC Electrical Characteristics                                            | 69 |

| 75 | Transmitter Electrical Parameters                                        | 70 |

| 76 | Receiver Electrical Parameters                                           | 70 |

| 77 | AFE Interface Timing Specifications (see Figure 23)                      | 70 |

| 78 | Absolute Maximum Ratings                                                 | 72 |

| 79 | Recommended Operating Conditions                                         | 72 |

| 80 | DC Electrical Characteristics                                            | 72 |

| 81 | AFE Data Interface Timing Specifications (see Figure 24)                 | 73 |

| 82 | AFE Control Interface Timing Specifications (see Figure 5 and Figure 25) | 74 |

| 83 | TDM Interface Timing Specifications - T1 Transport Mode (see Figure 26)  | 74 |

| 84 | Transceiver/Framer Reset Timing Specification                            | 75 |

| 85 | Intel Bus Parallel I/O Timing Characteristics (see Figure 27)            |    |

| 86 | Motorola Bus Parallel I/O Timing Characteristics (see Figure 27)         | 76 |

|    |                                                                          |    |

# **Revision History**

| Revision | Date | Description |

|----------|------|-------------|

|          |      |             |

|          |      |             |

|          |      |             |

# 1.0 Pin Assignments and Signal Descriptions

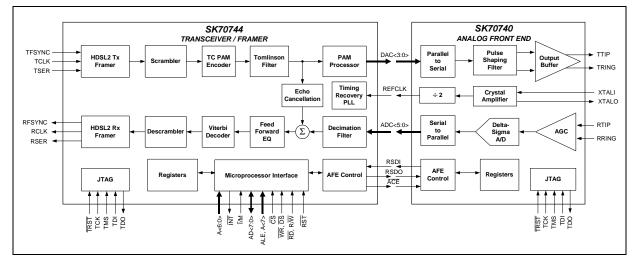

#### Figure 2. Analog Front End Pin Assignments

| Pin                             | Symbol                                                                                                                | I/O <sup>1</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Pin Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|---------------------------------|-----------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 48                              | RBAS                                                                                                                  | AO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | <b>Bias Resistor.</b> External bias resistor connection point for current reference. A 24.9k $\Omega$ resistor and a 0.01 $\mu$ F capacitor should be connected between the RBAS pin and the AGND1 pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 47                              | VREF                                                                                                                  | AO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | <b>Voltage Reference Decoupling.</b> External decoupling pin for internal voltage reference. A 0.47 $\mu$ F decoupling capacitor should be placed between the VREF pin and the AGND1 pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 49                              | XTALI                                                                                                                 | AI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Quartz Crystal or Clock Oscillator. Connect a 21.5 MHz crystal to XTAL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 50                              | XTALO                                                                                                                 | AO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | and XTALO. Alternately, connect a 21.5 MHz clock oscillator to XTALI and ground the XTALO pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 42                              | TTIP                                                                                                                  | AO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Transmit Tip and Ring. Transmit driver outputs. Connect to line driver                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 41                              | TRING                                                                                                                 | AO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | circuit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 30                              | RTIP                                                                                                                  | AI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Receive Tip and Ring. Receiver differential inputs. Connect to line                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 29                              | RRING                                                                                                                 | AI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | driver circuit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 1<br>2<br>3<br>4                | DAC3<br>DAC2<br>DAC1<br>DAC0                                                                                          | DI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | <b>Transmit Data Input.</b> Four-bit parallel input from the Transceiver/<br>Framer. Sampled on the rising edge of REFCLK. Connect to respective<br>Transceiver/Framer pins DAC3 - DAC0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 9<br>10<br>11<br>12<br>13<br>16 | ADC5<br>ADC4<br>ADC3<br>ADC2<br>ADC1<br>ADC0                                                                          | DO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | <b>Receive Data Output.</b> Six bit parallel output from the AFE receive channel to the Transceiver/Framer. This pulse width modulated data is clocked on the rising edge of REFCLK. Connect to respective Transceiver/Framer pins ADC5 - ADC0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 19                              | REFCLK                                                                                                                | DO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | <b>Reference Clock.</b> Clock signal derived from the local crystal. Provide timing reference to the Transceiver/Framer. The frequency of REFCLK is 1/2 the crystal frequency. Connect to Transceiver/Framer REFCLK pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 17                              | RSDO                                                                                                                  | DI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Serial Control Input. Connect to RSDO pin of the Transceiver/Frame.<br>Set-up and operating parameters are transferred to the AFE registers<br>on this line. RSDO is sampled on the rising edge of REFCLK. Timing is<br>shown in Figure 5 on page 21.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 18                              | RSDI                                                                                                                  | DO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | <b>Serial Control Output.</b> Connect to RSDI pin of the Transceiver/Frame AFE register read data is transferred to the Transceiver/Framer on this line. RSDI is updated on the rising edge of REFCLK. Timing is shown in Figure 5 on page 21.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 22                              | ACE                                                                                                                   | DI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | <b>AFE Interface Chip Enable</b> . Connect to ACE pin of the Transceiver/<br>Framer. When Low, enables register data transfer between the AFE and<br>Transceiver/Framer. ACE is sampled on the rising edge of REFCLK.<br>Timing is shown in Figure 5 on page 21.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                 | 48<br>47<br>49<br>50<br>42<br>41<br>30<br>29<br>1<br>2<br>3<br>4<br>9<br>10<br>11<br>12<br>13<br>16<br>19<br>17<br>18 | 48       RBAS         47       VREF         49       XTALI         50       XTALO         42       TTIP         41       TRING         30       RTIP         29       RRING         1       DAC3         2       DAC2         3       DAC1         4       DAC0         9       ADC5         10       ADC4         11       ADC3         12       ADC4         11       ADC3         12       ADC4         11       ADC3         12       ADC4         11       ADC3         12       ADC2         13       ADC1         16       ADC0         19       REFCLK         17       RSDO         18       RSDI | 48         RBAS         AO           47         VREF         AO           49         XTALI         AI           50         XTALO         AO           42         TTIP         AO           41         TRING         AO           41         TRING         AI           20         RRING         AI           1         DAC3         DI           2         DAC2         DI           3         DAC1         DI           4         DAC3         DI           9         ADC3         DI           11         ADC3         DI           12         ADC3         DI           13         ADC1         DO           14         ADC3         DI           15         ADC3         DI           16         ADC4         DI           17         RSDO         DI           18         RSDI         DO |

### Table 1. SK70740 Analog Front End Signal Descriptions

### Table 1. SK70740 Analog Front End Signal Descriptions (Continued)

| Group             | Pin      | Symbol                     | I/O <sup>1</sup> | Pin Description                                                                                                                                                                            |

|-------------------|----------|----------------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                   | 64       | тск                        | DI               | <b>Test Clock</b> . Clock reference that synchronizes internal test operations. This pin has an internal pull-down.                                                                        |

|                   | 58       | TMS                        | DI               | <b>Test Mode Select</b> . Used to control the test logic state machine.<br>Sampled on rising edge of TCK. TMS is pulled-up internally and may be left disconnected.                        |

| JTAG<br>Interface | 63       | TDO                        | DO               | <b>Test Data Output.</b> Three state output used for reading all serial configurations and test data from internal test logic. Updated on falling edge of TCK.                             |

|                   | 59       | TDI                        | DI               | <b>Test Data Input.</b> Used for loading serial instructions and data into internal test logic. Sampled on rising edge of TCK. TDI is pulled-up internally and may be left disconnected.   |

|                   | 60       | TRST                       | DI               | <b>Test Port Reset.</b> This active Low signal resets the JTAG test port controller. If JTAG is not to be used, then connect this pin to GND externally. This pin has an internal pull-up. |

|                   | 6        | DVCC                       | S                | Digital Power Supply. Connect to +3.3 V (± 5%).                                                                                                                                            |

|                   | 5        | DGND                       | S                | Digital Ground. Connect to 0 V. Return path for DVCC.                                                                                                                                      |

|                   | 21<br>62 | IOVCC1<br>IOVCC2           | S                | I/O Positive Supply. Connect both pins to either +3.3 V or +5 V (± 5%).                                                                                                                    |

| Digital<br>Power  | 20<br>61 | IOGND1<br>IOGND2           | S                | I/O Ground. Connect to 0 V. Return path for IOVCC.                                                                                                                                         |

| Supplies          | 8        | TDVCC                      | S                | Transmit Digital Positive Supply. Connect to +5 V ( $\pm$ 5%). Powers the transmit clock generator.                                                                                        |

|                   | 7        | TDGND                      | S                | Transmit Digital Ground. Connect to 0 V. Return path for TDVCC.                                                                                                                            |

|                   | 15       | RDVCC                      | S                | Receive Digital Positive Supply. Connect to +5 V (± 5%).                                                                                                                                   |

|                   | 14       | RDGND                      | S                | Receive Digital Ground. Connect to 0 V. Return path for RDVCC.                                                                                                                             |

|                   |          | ut; DO = Dig<br>nput/Outpu |                  | ttput; DI/O = Digital Input/Output; AI = Analog Input; AO = Analog Output;<br>Supply.                                                                                                      |

| Group             | Pin                        | Symbol                               | I/O <sup>1</sup> | Pin Description                                                                                                    |

|-------------------|----------------------------|--------------------------------------|------------------|--------------------------------------------------------------------------------------------------------------------|

|                   | 36<br>34<br>32<br>27       | RVCC1<br>RVCC2<br>RVCC3<br>RVCC4     | S                | Receive Power Supply. Connect to +5 V (± 5%).                                                                      |

|                   | 35<br>33<br>31<br>28       | RGND1<br>RGND2<br>RGND3<br>RGND4     | S                | RVCC Ground. Connect to 0 V. Return path for RVCC.                                                                 |

| Analog            | 40<br>44<br>54<br>56       | TVCC1<br>TVCC2<br>TVCC3<br>TVCC4     | S                | Transmit Power Supply. Connect to +5 V (± 5%).                                                                     |

| Power<br>Supplies | 39<br>43<br>53<br>55       | TGND1<br>TGND2<br>TGND3<br>TGND4     | S                | TVCC Ground. Connect to 0 V. Return path for TVCC.                                                                 |

|                   | 45<br>52                   | AVCC1<br>AVCC2                       | S                | Analog Power Supply. Connect to +5 V (± 5%).                                                                       |

|                   | 46<br>51                   | AGND1<br>AGND2                       | S                | AVCC Ground. Connect to 0 V. Return path for AVCC.                                                                 |

|                   | 25                         | BVCC                                 | S                | Bulk Power Supply. Connect to +5 V ( $\pm$ 5%). Powers all N-well guard rings to isolate major blocks of the chip. |

|                   | 26                         | BGND                                 | S                | Bulk Ground. Connect to 0 V. Return path for BVCC.                                                                 |

| Factory<br>Test   | 57<br>23<br>24<br>37<br>38 | TMI1<br>TMI2<br>TMI3<br>TMI4<br>TMI5 | -                | Factory Test Mode Interface. Leave floating for normal operation.                                                  |

|                   |                            | ut; DO = Dig<br>nput/Outpu           |                  | ttput; DI/O = Digital Input/Output; AI = Analog Input; AO = Analog Output;<br>Supply.                              |

### Table 1. SK70740 Analog Front End Signal Descriptions (Continued)

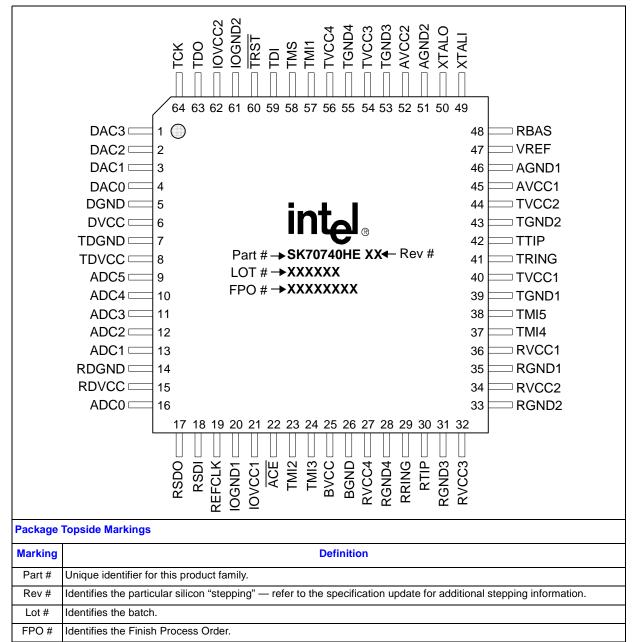

| 53 | RST                                                                            | DI                                                                                                                                                                                                                                   | Reset. Pulse Low to initialize internal circuits.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|----|--------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 83 | RBIAS                                                                          | AI                                                                                                                                                                                                                                   | Bias. Sets internal bias of PLL. Connect to Ground through 15.8k $\Omega$ 1% resistor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 2  | DAC3                                                                           |                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 1  | DAC2                                                                           |                                                                                                                                                                                                                                      | Transmit Data Output. Digital data output to AFE. Clocked out on rising                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 98 | DAC1                                                                           | 00                                                                                                                                                                                                                                   | edge of REFCLK. Connect to respective AFE pins DAC3 - DAC0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 97 | DAC0                                                                           |                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 96 | ADC5                                                                           |                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 95 | ADC4                                                                           |                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 94 | ADC3                                                                           | וח                                                                                                                                                                                                                                   | Receive Data Input. Digital data input from AFE. Sampled on the rising                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 93 | ADC2                                                                           | ы                                                                                                                                                                                                                                    | edge of REFCLK. Connect to respective AFE pins ADC5 - ADC0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 92 | ADC1                                                                           |                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 89 | ADC0                                                                           |                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 84 | REFCLK                                                                         | DI                                                                                                                                                                                                                                   | <b>Reference Clock.</b> Serial clock signal from AFE. Frequency is one half the AFE crystal reference for all rates. Synchronizes data transfers to/from the AFE. Connect to REFCLK pin of the AFE.                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 88 | RSDO                                                                           | DO                                                                                                                                                                                                                                   | <b>Serial Control Output.</b> Connect to RSDO pin of the AFE. Set-up and operating parameters are transferred to the AFE registers on this line. RSDO is sampled on the rising edge of REFCLK. Timing is shown in Figure 5 on page 21.                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 87 | RSDI                                                                           | DI                                                                                                                                                                                                                                   | <b>Serial Control Input.</b> Connect to RSDI pin of the AFE. Read data from the AFE is transferred to the Transceiver/Framer on this line. RSDI is updated on the rising edge of REFCLK. Timing is shown in Figure 5 on page 21.                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 78 | ACE                                                                            | DO                                                                                                                                                                                                                                   | <b>AFE Interface Chip Enable</b> . Connect to ACE pin of the AFE. When held Low, enables register data transfer between the AFE and Transceiver/<br>Framer. ACE is sampled on the rising edge of REFCLK. Timing is shown in Figure 5 on page 21.                                                                                                                                                                                                                                                                                                                                                                                                       |

|    | 83<br>2<br>1<br>98<br>97<br>96<br>95<br>94<br>93<br>92<br>89<br>84<br>88<br>88 | 83     RBIAS       2     DAC3       1     DAC2       98     DAC1       97     DAC0       96     ADC5       95     ADC4       94     ADC3       93     ADC2       92     ADC1       84     REFCLK       88     RSDO       87     RSDI | 83       RBIAS       AI         2       DAC3       1         DAC2       DAC4       1         98       DAC1       DO         96       ADC5       1         95       ADC4       1         94       ADC3       1         80       ADC4       1         81       REFCLK       DI         88       RSDO       DO         87       RSDI       DI |

### Table 2. SK70744 Transceiver/Framer Signal Descriptions

| Group           | Pin      | Symbol                          | I/O <sup>1</sup> | Description                                                                                                                                                                             |  |  |  |  |

|-----------------|----------|---------------------------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

|                 | 61<br>60 | AD7<br>AD6<br>AD5               |                  |                                                                                                                                                                                         |  |  |  |  |

|                 | 59<br>58 | AD5<br>AD4                      |                  |                                                                                                                                                                                         |  |  |  |  |

|                 | 50<br>57 | AD4<br>AD3                      | DI/O             | Address/Data Lines <7:0>. Multiplexed data/address bus in Intel mode.<br>Data bus in Motorola mode.                                                                                     |  |  |  |  |

|                 | 56       | AD3<br>AD2                      |                  |                                                                                                                                                                                         |  |  |  |  |

|                 | 55       | AD2<br>AD1                      |                  |                                                                                                                                                                                         |  |  |  |  |

|                 | 53<br>54 | AD1<br>AD0                      |                  |                                                                                                                                                                                         |  |  |  |  |

|                 | 76       | INTFEC                          | DO               | Interrupt Output from FEC/Framer. Open drain output. Requires an                                                                                                                        |  |  |  |  |

|                 | 10       |                                 | 20               | external 10 kΩ pull up resistor. Goes Low on interrupt.                                                                                                                                 |  |  |  |  |

|                 | 77       | INTPAM                          | DO               | Interrupt Output from PAM Transceiver. Open drain output. Requires an external 10 k $\Omega$ pull up resistor. Goes Low on interrupt.                                                   |  |  |  |  |

|                 | 64       | CS                              | DI               | Chip Select. Pull Low to read or write Transceiver/Framer registers.                                                                                                                    |  |  |  |  |

| μP<br>Interface | 62       | $\overline{RD}, R/\overline{W}$ | DI               | <b>Read Control.</b> Low true read enable in Intel mode. R/W strobe in Motorola mode.                                                                                                   |  |  |  |  |

| Interface       | 63       | $\overline{WR}, \overline{DS}$  | DI               | Write Control. Low true write enable in Intel mode. Low true data strobe in Motorola mode.                                                                                              |  |  |  |  |

|                 | 74       | ALE, A7                         | DI               | Address Latch Enable. In Intel mode, the falling edge latches the address present on multiplexed address/data bus.<br>Address Line 7 in Motorola mode.                                  |  |  |  |  |

|                 |          |                                 |                  |                                                                                                                                                                                         |  |  |  |  |

|                 | 73       | A6                              | DI               |                                                                                                                                                                                         |  |  |  |  |

|                 | 72       | A5                              | DI               |                                                                                                                                                                                         |  |  |  |  |

|                 | 71       | A4                              | DI               | Address Lines <6:0> In Motorola mode. In Intel mode, A0 and A2 must                                                                                                                     |  |  |  |  |

|                 | 70<br>60 | A3<br>A2                        | DI<br>DI         | be grounded to disable a factory test mode and allow normal<br>operation.                                                                                                               |  |  |  |  |

|                 | 69<br>68 | A2<br>A1                        | DI               |                                                                                                                                                                                         |  |  |  |  |

|                 | 67       | A0                              | DI               |                                                                                                                                                                                         |  |  |  |  |

|                 | 75       | Ī/M                             | DI               | <b>Intel / Motorola Select.</b> When Low, the microprocessor interface is configured for the Intel 80C51. When High, the microprocessor interface is configured for the Motorola 68000. |  |  |  |  |

|                 | 35       | TSER                            | DI               | <b>Transmitter Serial Data.</b> NRZ serial data into the HDSL2 frame mapper.<br>Clocked on rising edge of TCLK.                                                                         |  |  |  |  |