# VDSL6100i

Integrated VDSL Modem-on-Chip PEF 22827, Version 1.1

Wireline Communications

Never stop thinking.

ABM®, ACE®, AOP®, ARCOFI®, ASM®, ASP®, DigiTape®, DuSLIC®, EPIC®, ELIC®, FALC®, GEMINAX®, IDEC®, INCA®, IOM®, IPAT®-2, ISAC®, ITAC®, IWE®, IWORX®, MUSAC®, MuSLIC®, OCTAT®, OptiPort®, POTSWIRE®, QUAT®, QuadFALC®, SCOUT®, SICAT®, SICOFI®, SIDEC®, SLICOFI®, SMINT®, SOCRATES®, VINETIC®, 10BaseV®, 10BaseVX® and 10BaseS™ are registered trademarks of Infineon Technologies AG. Microsoft® is a registered trademark of Microsoft Corporation, Linux® of Linus Torvalds, Visio® of Visio Corporation, and FrameMaker® of Adobe Systems Incorporated.

The information in this document is subject to change without notice.

#### Edition 2005-01-30

Published by Infineon Technologies AG, St.-Martin-Strasse 53, 81669 München, Germany

© Infineon Technologies AG 2005.

All Rights Reserved.

#### Attention please!

The information herein is given to describe certain components and shall not be considered as a guarantee of characteristics.

Terms of delivery and rights to technical change reserved.

We hereby disclaim any and all warranties, including but not limited to warranties of non-infringement, regarding circuits, descriptions and charts stated herein.

#### Information

For further information on technology, delivery terms and conditions and prices please contact your nearest Infineon Technologies Office (www.infineon.com).

#### Warnings

Due to technical requirements components may contain dangerous substances. For information on the types in question please contact your nearest Infineon Technologies Office.

Infineon Technologies Components may only be used in life-support devices or systems with the express written approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure of that life-support device or system, or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body, or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.

| VDSL610  | 0i             |                                               |          |

|----------|----------------|-----------------------------------------------|----------|

| Revision | History:       | 2005-01-30                                    | Rev. 1.1 |

| Previous | Version:       | None, First Release                           |          |

| Page     | Subjects (ma   | jor changes since last revision)              |          |

|          | Update of Teri | minology, Register list and definitions, etc. |          |

|          |                |                                               |          |

|          |                |                                               |          |

|          |                |                                               |          |

|          |                |                                               |          |

|          |                |                                               |          |

|          |                |                                               |          |

|          |                |                                               |          |

|          |                |                                               |          |

|          |                |                                               |          |

|          |                |                                               |          |

|          |                |                                               |          |

|          |                |                                               |          |

|          |                |                                               |          |

|          |                |                                               |          |

## **Preface**

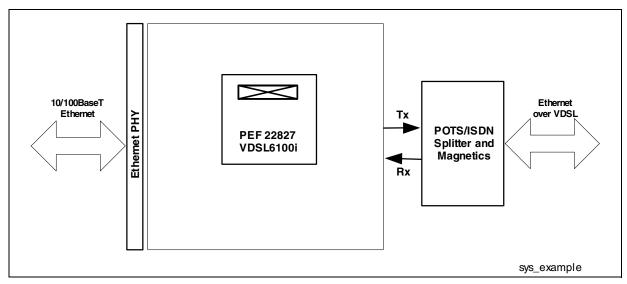

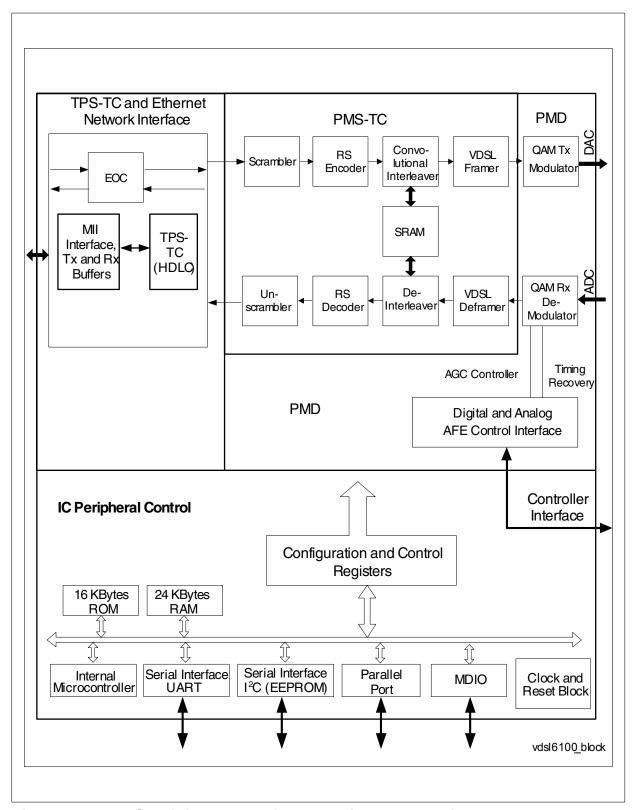

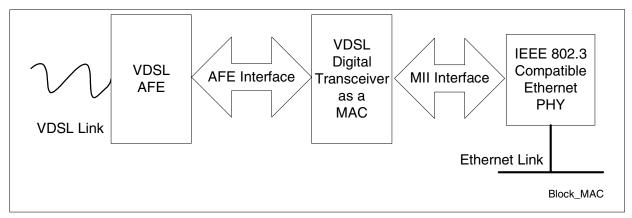

The PEF 22827 is an integrated VDSL modem-on-chip. It combines all the required functionality for standard 4-band VDSL over a twisted pair. This modem-on-chip includes a digital data transceiver supporting Ethernet interface, an analog front end (AFE) handling the VDSL QAM functionality and an internal line driver to provide transmission level to the line.

System functionality complies with ITU-T and ETSI standards for VDSL.

### **About This Document**

This data sheet is organized as follows:

- Product Overview on Page 19, lists the main features and suggests typical applications.

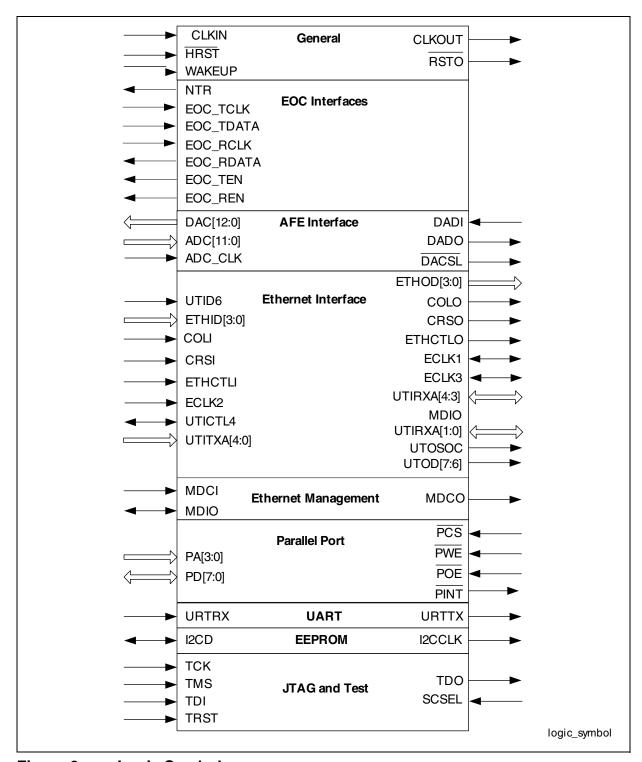

- Pin and Signal Descriptions, starting on Page 22, shows the logic symbol and pin layout, lists all pins, and shows pin to signal assignment in different operation modes.

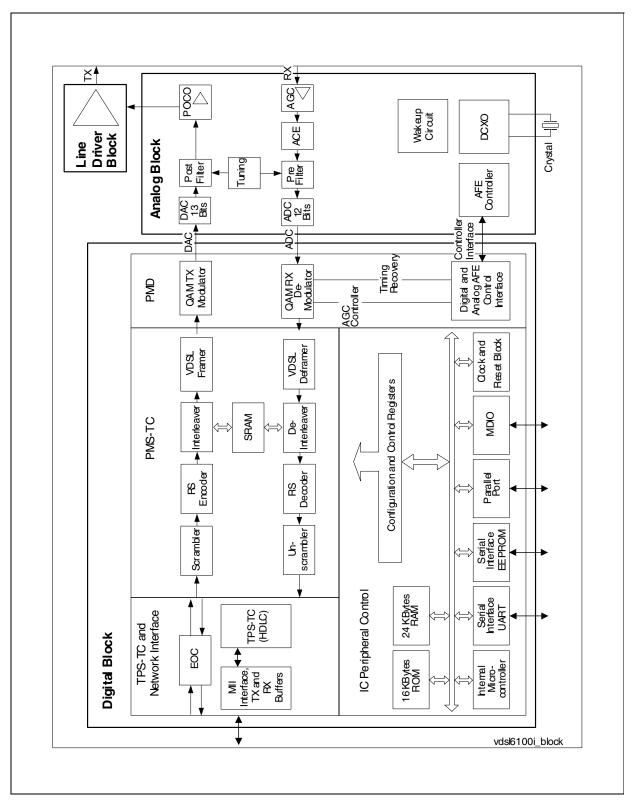

- Functional Overview, starting on Page 55, describes the functions of the PEF 22827 as a whole, followed by the functions of the digital, analog and line driver blocks, in separate sections. Block diagrams and firmware options are included.

- Operation Digital Block, starting on Page 81, describes the operation of the digital block, which controls the analog block. The description includes configuration pins, the system clock, EEPROM, internal RAM management, and the boot process.

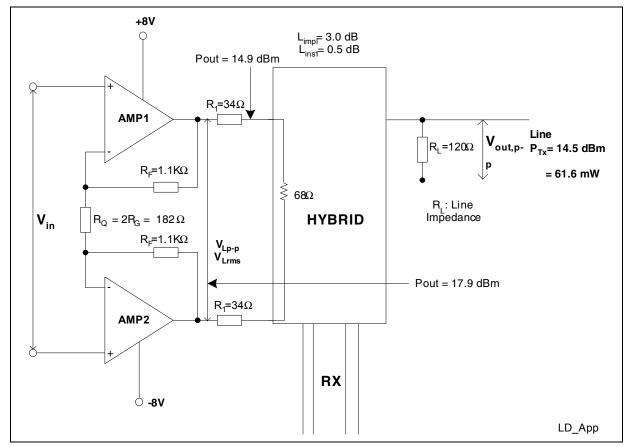

Operation Line Driver describes the computation of line driver gain and the line driver shut down procedure.

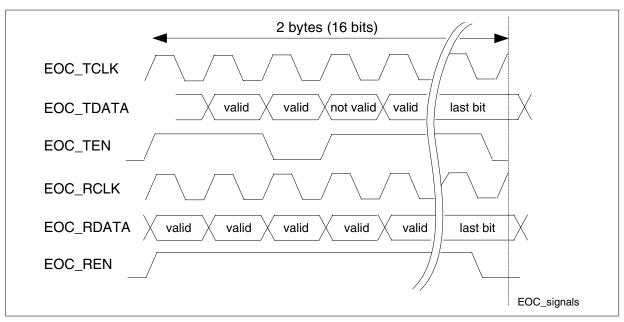

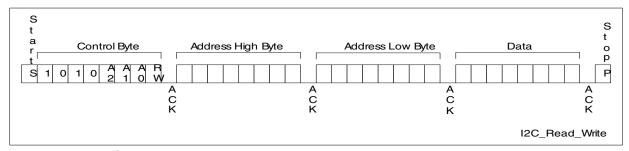

- Interfaces, starting on Page 134, includes the JTAG interface (boundary scan), management, network and EOC interfaces, and the I<sup>2</sup>C interface for EEPROM.

- The Memory and Register Descriptions Digital Block and Memory and Register Descriptions – Analog Block sections, starting on Page 171, describe memory mapping and registers for the digital and analog blocks, respectively. These sections include lists of registers by address and by type, and links to the detailed description of each register.

- Electrical Characteristics Overview, starting on Page 266, specifies maximum ratings, recommended operating conditions, heat dissipation parameters and AC/DC characteristics for the integrated chip first, and then for the digital, analog and line driver blocks.

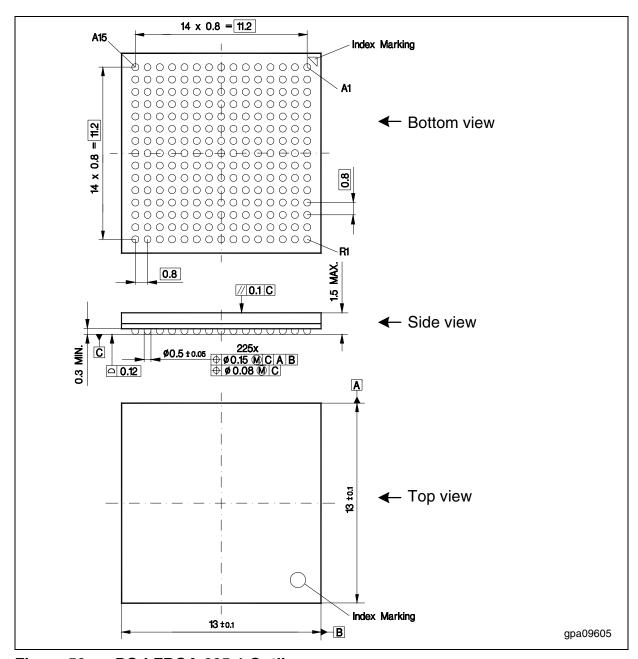

- Package Outline on Page 290.

In addition, for convenience, the following sections are included after the last chapter:

- A Terminology section to help you define acronyms and expressions.

- A References list to help you find information not in this data sheet.

- An Index to help you find specific information.

| Table of                                                                                                                                                          | Contents                                                                                                                                                                                                                                                                                                                                                                                                                           | Page                                                                                                                                                                   |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                   | Preface                                                                                                                                                                                                                                                                                                                                                                                                                            | 4                                                                                                                                                                      |

|                                                                                                                                                                   | About This Document                                                                                                                                                                                                                                                                                                                                                                                                                | 4                                                                                                                                                                      |

| 1<br>1.1<br>1.2<br>1.3                                                                                                                                            | Product OverviewFeaturesPowerTypical Applications                                                                                                                                                                                                                                                                                                                                                                                  | . 20<br>. 21                                                                                                                                                           |

| 2<br>2.1<br>2.2<br>2.3<br>2.3.1<br>2.3.2<br>2.3.3<br>2.3.4<br>2.3.5<br>2.3.6<br>2.3.7<br>2.3.8<br>2.3.9<br>2.4<br>2.4.1<br>2.4.1.1<br>2.4.1.2<br>2.4.1.3<br>2.4.2 | Pin and Signal Descriptions Pin Diagram  Master Pin List Pin Lists by Function General Purpose Pins Analog Interface Pins Embedded Overhead Channel (EOC) and PCM Pins Ethernet Pins Parallel Port Pins UART Pins EEPROM Pins Test Pins Voltage Supply and Ground Pins Pin and Signal Assignment in Different Modes Ethernet Interface Modes MII Modes RMII Modes Serial MII Slave Mode Ethernet Serial Management Interface Modes | <ul> <li>23</li> <li>25</li> <li>39</li> <li>40</li> <li>41</li> <li>43</li> <li>45</li> <li>46</li> <li>46</li> <li>47</li> <li>49</li> <li>50</li> <li>51</li> </ul> |

| 3<br>3.1<br>3.2<br>3.3<br>3.4<br>3.5                                                                                                                              | Functional Overview  Digital Block - Functional Overview  Analog Block - Functional Overview  Line Driver Block - Functional Overview  Functional Block Diagram  JTAG Interface                                                                                                                                                                                                                                                    | . 55<br>. 55<br>. 55<br>. 55                                                                                                                                           |

| 4<br>4.1<br>4.2<br>4.3<br>4.3.1<br>4.3.2<br>4.4<br>4.4.1                                                                                                          | Functional Description – Digital Block  Functional Block Diagram – Digital Block  Firmware  Physical Media Dependent (PMD) Layer  QAM Modulator (Transmitter)  QAM Demodulator (Receiver)  Physical Medium Specific Transmission Convergence (PMS-TC) Layer  Transmission Path Tasks                                                                                                                                               | . 58<br>. 60<br>. 60<br>. 60<br>. 62<br>. 62                                                                                                                           |

| Table of | Contents                                         | Page |

|----------|--------------------------------------------------|------|

| 4.4.1.1  | Scrambling                                       | . 63 |

| 4.4.1.2  | Reed Solomon Encoding                            |      |

| 4.4.1.3  | Interleaving                                     |      |

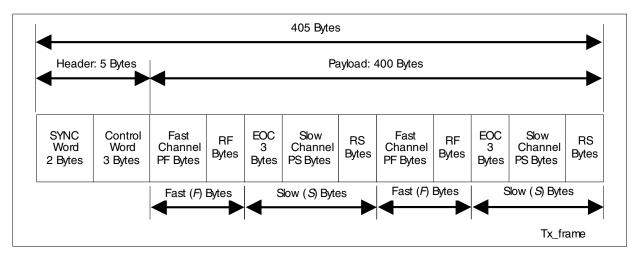

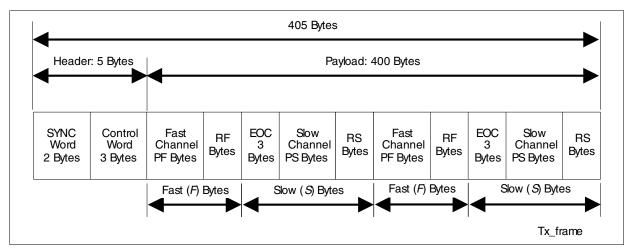

| 4.4.1.4  | Construction of a Transmission Frame             | . 64 |

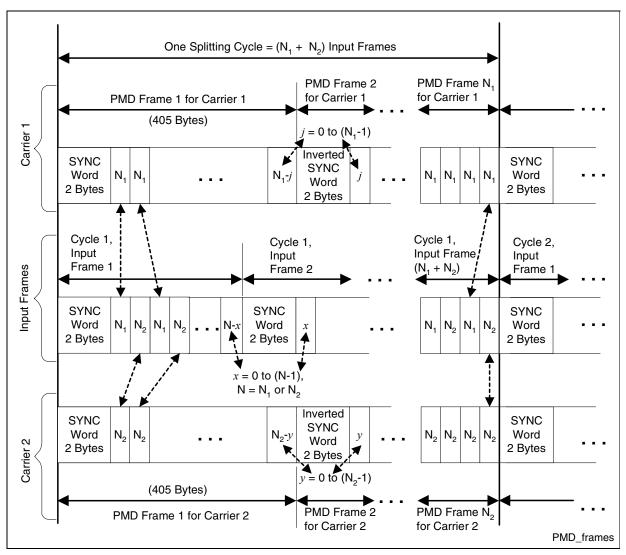

| 4.4.1.5  | Splitting the Transmission Frame into PMD Frames | . 66 |

| 4.4.2    | Reception Path Tasks                             |      |

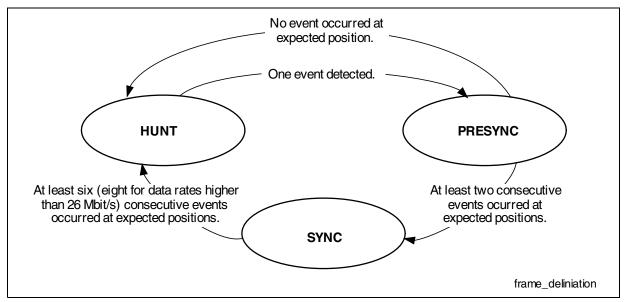

| 4.4.2.1  | Transmission Frame Construction from PMD Frames  | . 68 |

| 4.4.2.2  | De-interleaving                                  | . 68 |

| 4.4.2.3  | Reed Solomon Decoding                            | . 69 |

| 4.4.2.4  | Unscrambling                                     | . 69 |

| 4.4.2.5  | Distribution of Data                             |      |

| 4.5      | Ethernet Network Interfaces and the TPS-TC Layer | . 69 |

| 4.5.1    | Ethernet Encapsulation                           | . 69 |

| 4.5.2    | Bridging                                         | . 70 |

| 4.5.3    | MAC Functions                                    | . 70 |

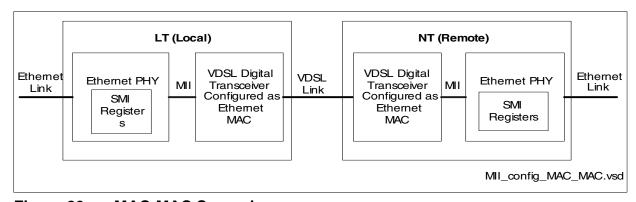

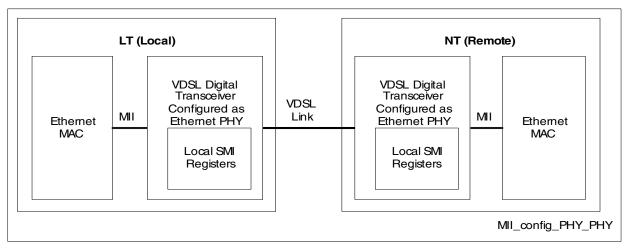

| 4.5.4    | MII Interface and Configuration                  | . 71 |

| 4.5.5    | MIB Support                                      | . 71 |

| 4.5.6    | Speed and Duplex Mode Adaptation                 | . 71 |

| 4.5.7    | Embedded Overhead Channel (EOC)                  | . 71 |

| 4.6      | Management and Control                           | . 72 |

| 4.6.1    | Internal Micro Controller                        | . 72 |

| 4.6.2    | User Registers                                   | . 72 |

| 4.6.3    | Management Interfaces                            | . 72 |

| 4.6.4    | Configuration Pins                               | . 73 |

| 4.6.5    | EEPROM                                           | . 73 |

| 4.6.6    | JTAG Interface                                   | . 73 |

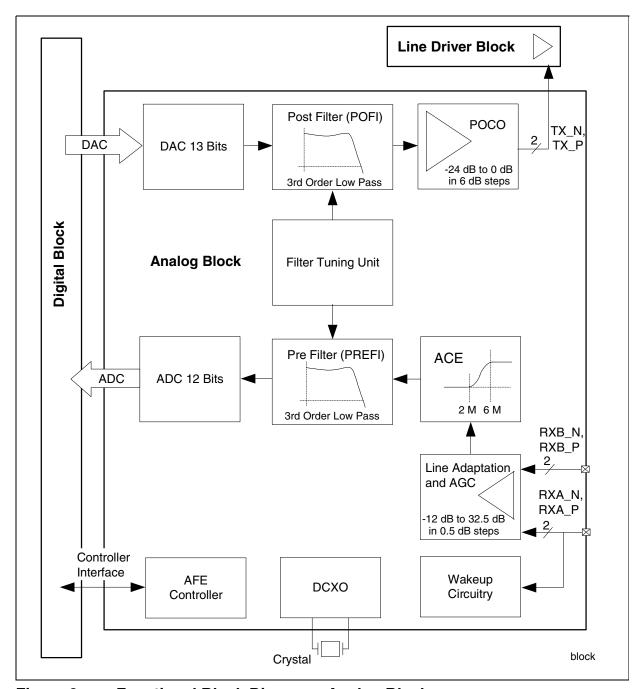

| 5        | Functional Description – Analog Block            | . 74 |

| 5.1      | Classical AFE                                    |      |

| 5.2      | Filterless AFE                                   |      |

| 5.3      | Functional Block Diagram – Analog Block          |      |

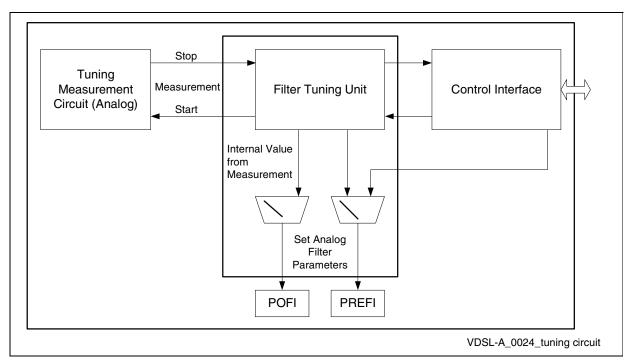

| 5.4      | Filter Tuning Unit                               |      |

| 5.5      | Transmission Path                                | . 77 |

| 5.5.1    | Digital-to-Analog Converter (DAC)                | . 77 |

| 5.5.2    | Post Tuning Filter (POFI)                        |      |

| 5.5.3    | Power Controller                                 |      |

| 5.6      | Receive Path                                     | . 78 |

| 5.6.1    | Automatic Gain Control (AGC)                     | . 78 |

| 5.6.2    | Analog Channel Equalizer                         |      |

| 5.6.3    | Pre-Tuning Filter                                |      |

| 5.6.4    | Analog-to-Digital Converter (ADC)                |      |

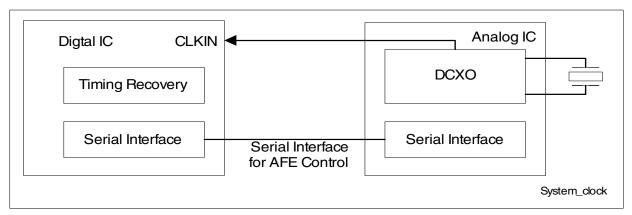

| 5.7      | Clock Generation                                 |      |

| 5.8      | Reset                                            |      |

| Table of         | Contents                                                                                                            | Page  |

|------------------|---------------------------------------------------------------------------------------------------------------------|-------|

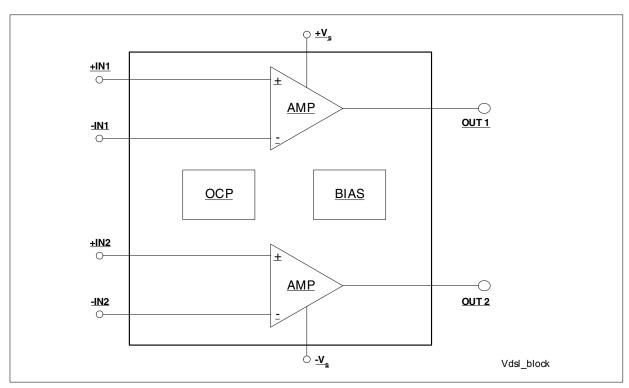

| <b>6</b> 6.1 6.2 | Functional Description – Line Driver Block          Functional Block Diagram – Line Driver          Power Down Mode | 80    |

| 7                | Operation – Digital Block                                                                                           | 81    |

| 7.1              | Configuration Pins During Hard Reset                                                                                | 81    |

| 7.2              | System Clock                                                                                                        | 82    |

| 7.3              | EEPROM                                                                                                              | 83    |

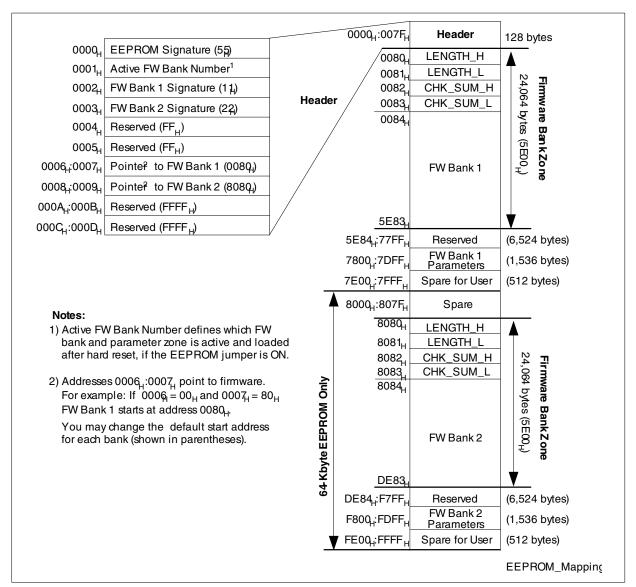

| 7.3.1            | EEPROM Structure                                                                                                    |       |

| 7.3.1.1          | The EEPROM Header                                                                                                   | 84    |

| 7.3.1.2          | Firmware Banks in EEPROM                                                                                            |       |

| 7.3.1.3          | The Parameters Zones in EEPROM                                                                                      | 85    |

| 7.3.1.4          | Spare Zones                                                                                                         | 96    |

| 7.3.2            | Accessing EEPROM                                                                                                    | 97    |

| 7.3.2.1          | Writing to EEPROM                                                                                                   | 97    |

| 7.3.2.2          | Reading from EEPROM                                                                                                 | 97    |

| 7.4              | Internal RAM Management                                                                                             | 98    |

| 7.5              | The Boot Process                                                                                                    |       |

| 7.5.1            | Firmware Download from EEPROM                                                                                       | 99    |

| 7.5.2            | The Boot Loop                                                                                                       | 99    |

| 7.5.2.1          | Download Using Local Interfaces                                                                                     | 99    |

| 7.6              | Application Management                                                                                              | . 100 |

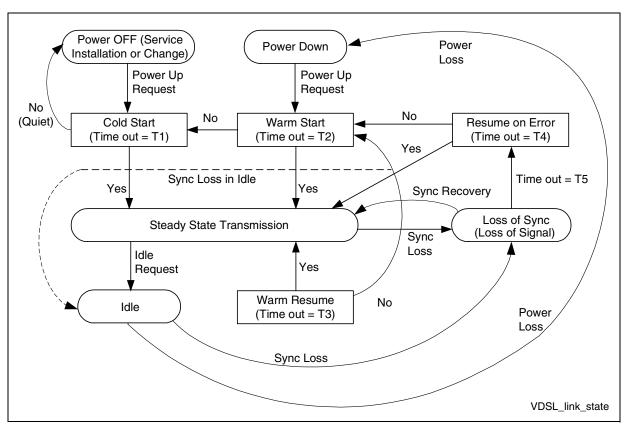

| 7.6.1            | Standard Compliant Links                                                                                            | . 100 |

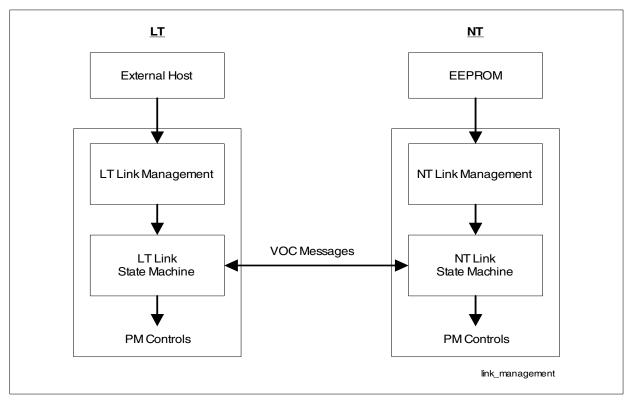

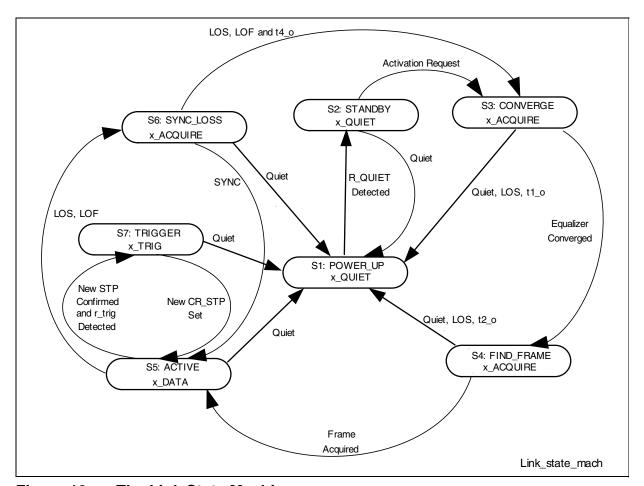

| 7.6.2            | Management of Standard Compliant Links                                                                              | . 101 |

| 7.6.3            | Configuration of Standard Compliant Links                                                                           | . 104 |

| 7.6.4            | Current and Target STPs                                                                                             | . 104 |

| 7.6.4.1          | Modifying STPs                                                                                                      | . 105 |

| 7.6.4.2          | Copying STPs                                                                                                        | . 105 |

| 7.6.4.3          | STP Mapping                                                                                                         | . 105 |

| 7.6.4.4          | Setting the Gross Bit Rate                                                                                          | . 111 |

| 7.6.4.5          | Net Throughput                                                                                                      | . 112 |

| 7.6.4.6          | Setting the Interleaver                                                                                             | . 113 |

| 7.6.4.7          | Calculating Interleaver Protection                                                                                  | . 113 |

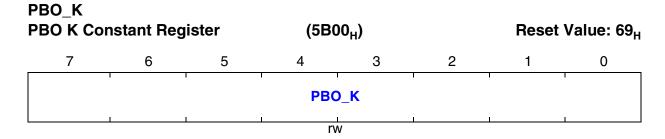

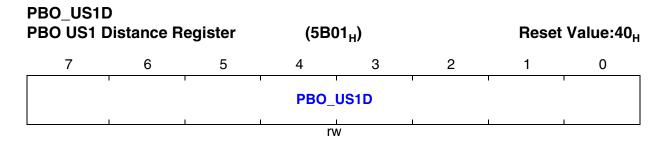

| 7.6.5            | Power Back Off (PBO)                                                                                                | . 115 |

| 7.6.6            | Performance Monitoring for Standard Compliant Links                                                                 | . 116 |

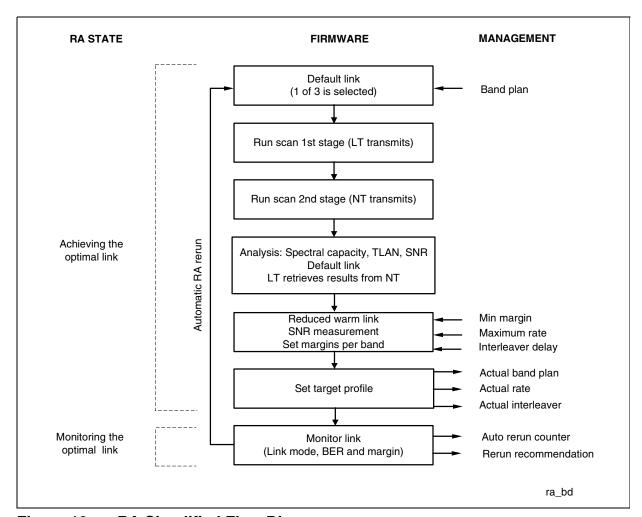

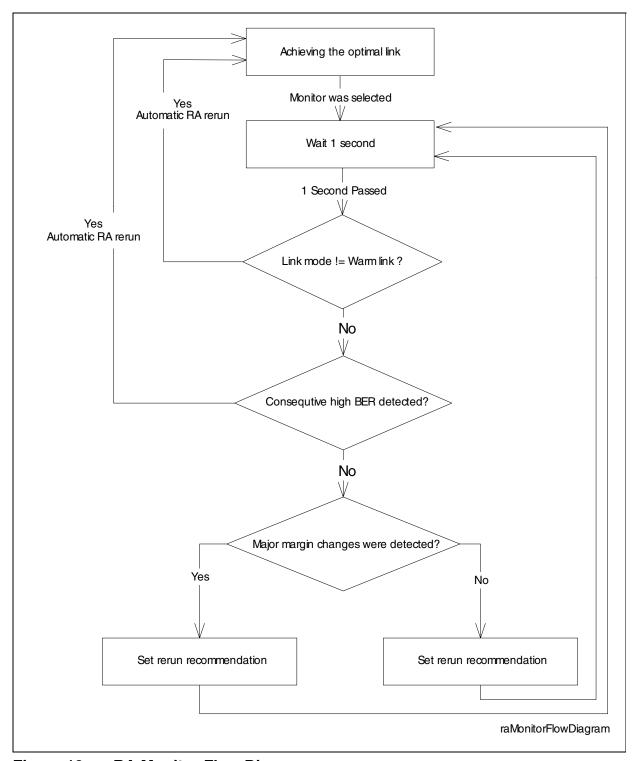

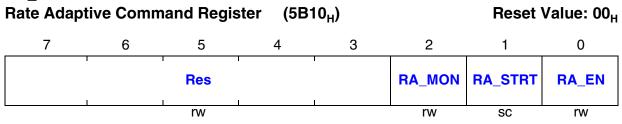

| 7.6.7            | The Rate Adaptive Process                                                                                           | . 117 |

| 7.6.7.1          | The Rate Adaptive Loop                                                                                              | . 117 |

| 7.6.7.2          | Configuring the RA Process                                                                                          | . 121 |

| 7.6.7.3          | Executing the RA Process                                                                                            | . 121 |

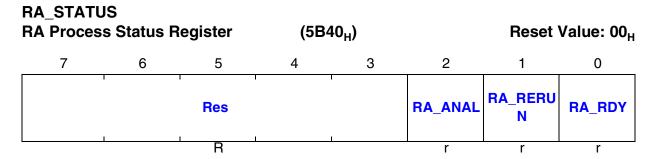

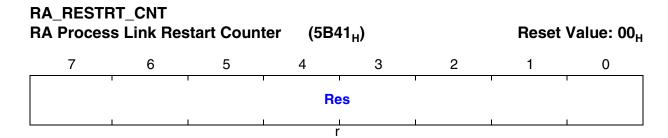

| 7.6.7.4          | Polling the Status of the RA Process                                                                                | . 121 |

| 7.6.7.5          | Selecting an RA Scanning Band Plan                                                                                  |       |

| 7.6.7.6          | Running the RA Process with PBO in Changing Conditions                                                              |       |

| 7.6.7.7          | Running the RA Process with Long Reach VDSL                                                                         | . 122 |

| Table of                                                                                                                                                                                                                                                              | Contents                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Page                                                                                                                                            |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| 7.6.8<br>7.6.9<br>7.6.10<br>7.6.10.1<br>7.6.11<br>7.6.12                                                                                                                                                                                                              | Implementing Long Reach VDSL Manually Accessing the Remote Transceiver Network Interfaces Ethernet Packet Transfer The Dying Gasp Mechanism External Status Signals (LEDs)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 123<br>124<br>124<br>131                                                                                                                        |

| <b>8</b><br>8.1                                                                                                                                                                                                                                                       | Operation – Line Driver                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                 |

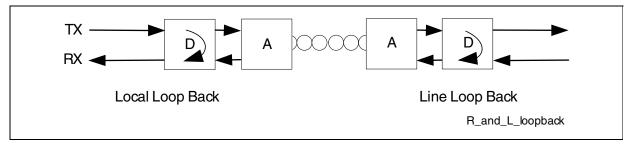

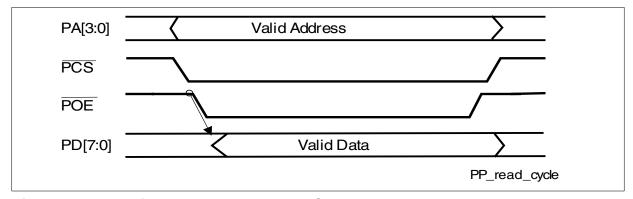

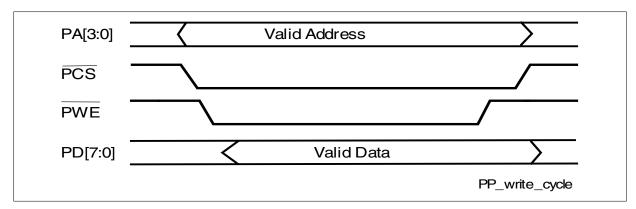

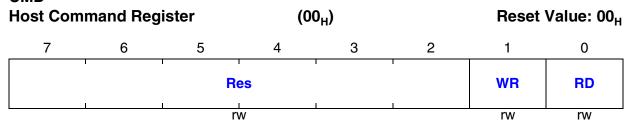

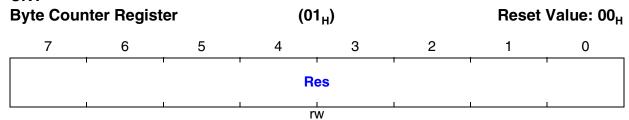

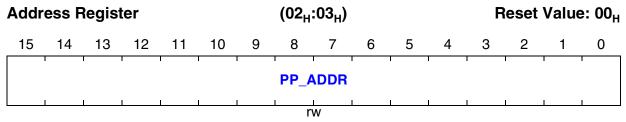

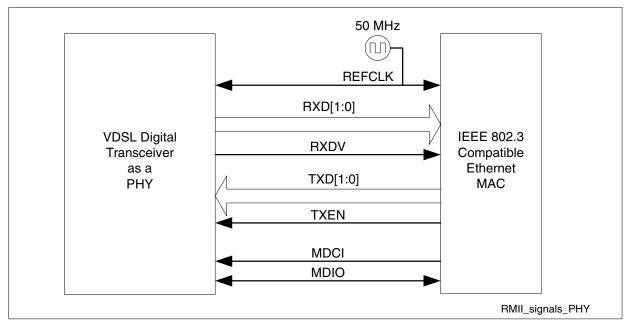

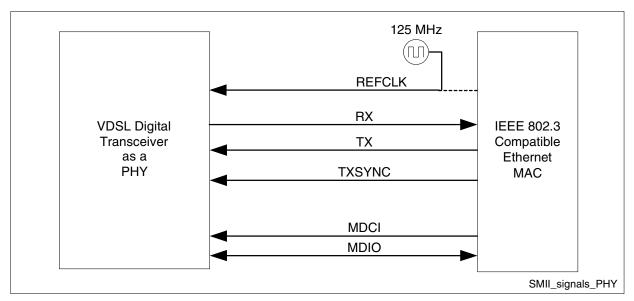

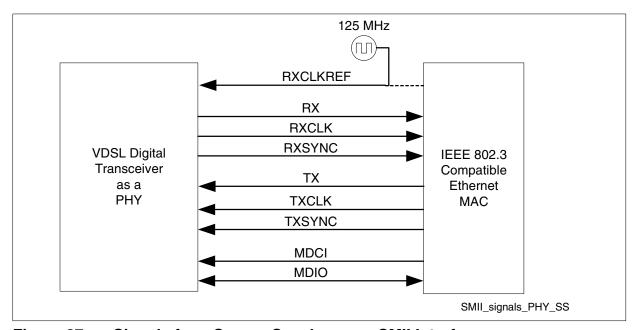

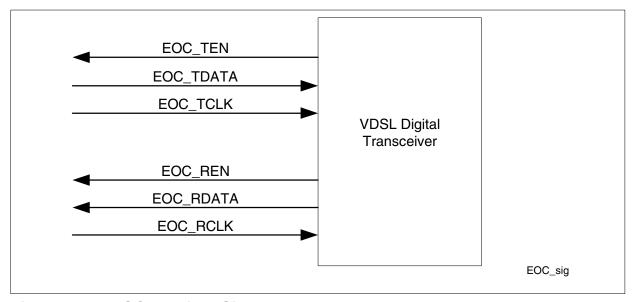

| 9<br>9.1<br>9.2<br>9.2.1<br>9.2.2<br>9.2.2.1<br>9.2.2.2<br>9.2.2.3<br>9.2.2.4<br>9.2.3.1<br>9.2.3.2<br>9.2.3.3<br>9.2.3.4<br>9.2.4<br>9.3<br>9.3.1.1<br>9.3.1.1<br>9.3.1.2<br>9.3.2.1<br>9.3.2.2<br>9.3.2.1<br>9.3.2.3<br>9.3.2.1<br>9.3.2.5<br>9.3.2.6<br>9.4<br>9.5 | Interfaces  JTAG Interface (Boundary Scan)  Management Interfaces  Serial Host Interface  Parallel Host Interface  Parallel Port Signals  Parallel Port Registers  Indirect Read Cycle  Write Cycle  MII Serial Management Interface (SMI)  SMI Frame Structure  SMI Registers (PHY Mode)  Accessing Internal Memory Space through the SMI  SMI Registers (MAC Mode)  Detailed Description of SMI Registers  Network Interfaces  MII Interface  MAC Configuration with MII Interface  PHY Configuration with MII Interface  xMII Interface to a PHY in a MAC Configuration  MII Interface to a PHY in a MAC Configuration  RMII Interface to a PHY in a MAC Configuration  RMII Interface to a MAC in a PHY Configuration  RMII Interface to a MAC in a PHY Configuration  RMII Interface to a MAC in a PHY Configuration  RMII Interface to Source Synchronous SMII Interface  EOC Interface  I²C Interface for EEPROM | 134<br>135<br>136<br>136<br>138<br>141<br>142<br>143<br>144<br>145<br>145<br>156<br>156<br>156<br>160<br>162<br>163<br>164<br>165<br>166<br>167 |

| 10<br>10.1<br>10.2<br>10.3<br>10.4                                                                                                                                                                                                                                    | Memory and Register Descriptions – Digital Block Register Overview – Digital Block Register Lists by Type – Digital Block Detailed Register Descriptions – Digital Block Main Control Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 171<br>177<br>185                                                                                                                               |

| Table of         | Contents                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Page |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

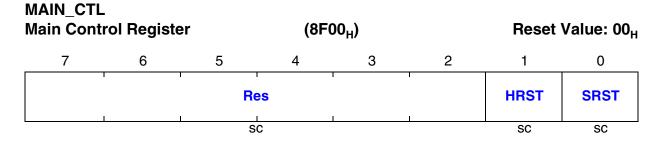

| 10.4.1           | Main Control Register (MAIN_CTL)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 185  |

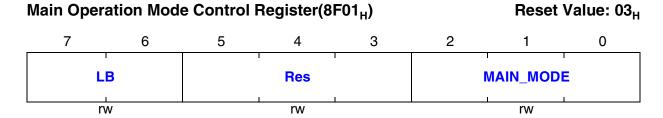

| 10.4.2           | Main Operation Mode Register (MAIN_MODE)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |      |

| 10.4.3           | Link Operation Mode Register (LINK_MODE)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |      |

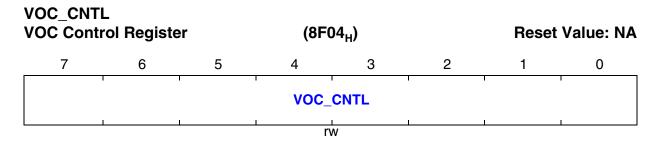

| 10.4.4           | VOC Control Register (VOC_CNTL)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |

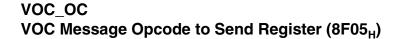

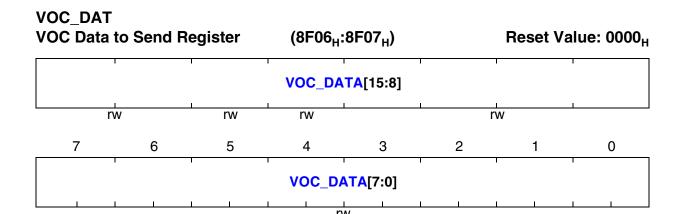

| 10.4.5           | VOC Message Opcode to Send Register (VOC_OC)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |      |

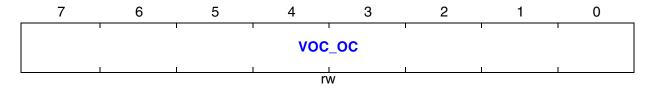

| 10.4.6           | VOC Data to Send Register (VOC_DAT) \(\bigcap \cdot \c |      |

| 10.4.7           | PSD Output Adjustment Register (PSDADJ)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |      |

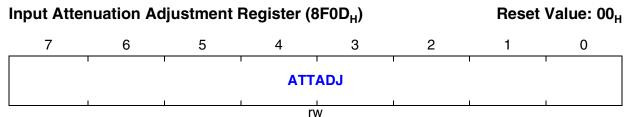

| 10.4.8           | Attenuation Input Adjustment Register (ATTADJ)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 196  |

| 10.5             | Main Status Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |      |

| 10.5.1           | General Status Register 1 (GEN_STATUS1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 197  |

| 10.5.2           | General Status Register 2 (GEN_STATUS2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 198  |

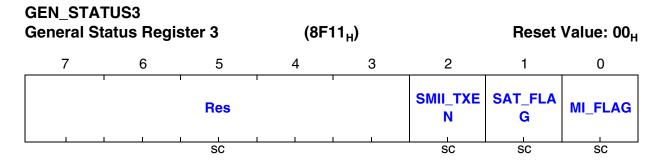

| 10.5.3           | General Status Register 3 (GEN_STATUS3)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 198  |

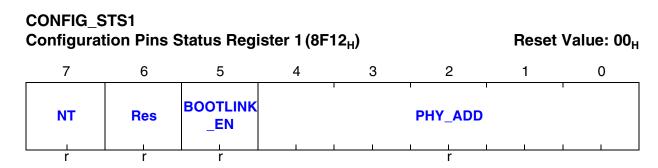

| 10.5.4           | Configuration Pins Status Register 1 (CONFIG_STS1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 199  |

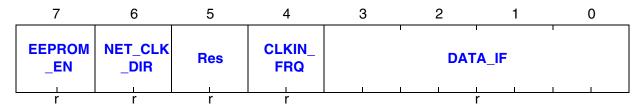

| 10.5.5           | Configuration Pins Status Register 2 (CONFIG_STS2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |      |

| 10.5.6           | SNR for Band 1 (SNR_BAND1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |      |

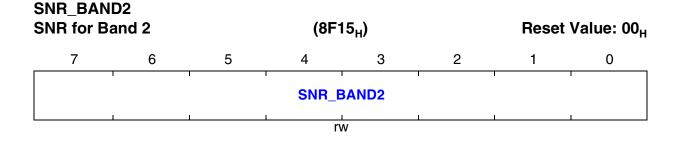

| 10.5.7           | SNR for Band 2 (SNR_BAND2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |      |

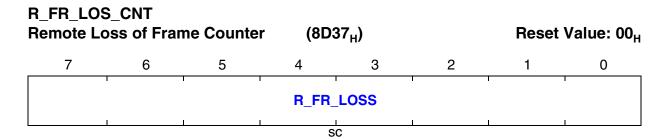

| 10.5.8           | Remote Loss of Frame Counter (R_FR_LOS_CNT)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |      |

| 10.5.9           | Channel Failures Counter (FAIL_CNT)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |      |

| 10.5.10          | Loss of Signal on Bands 1 and 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |

| 10.5.11          | Local Loss of Frame Counter (L_FR_LOS_CNT)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |      |

| 10.5.12          | SNR Margin and BER Overflow Status Register (SNR_BER)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |      |

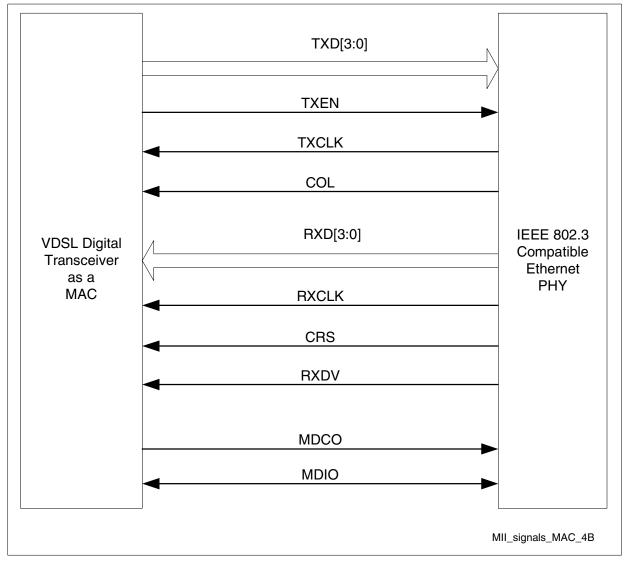

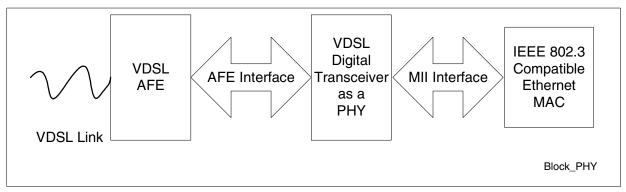

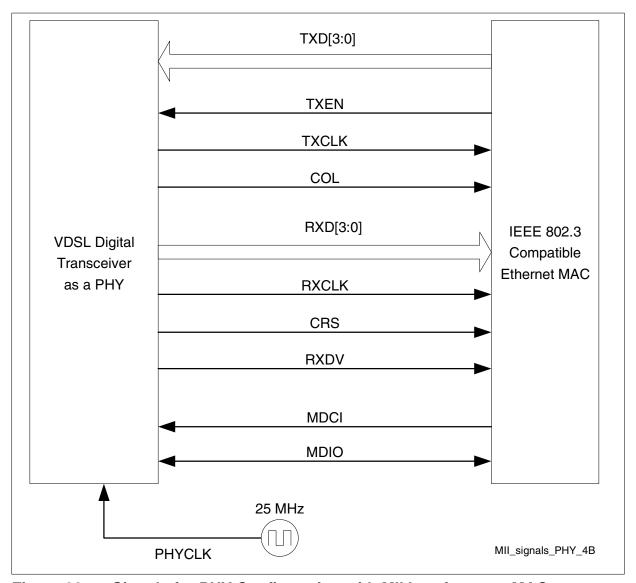

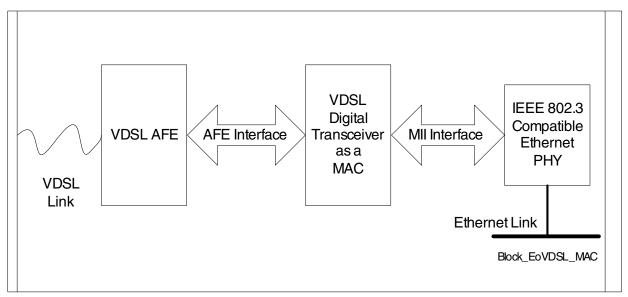

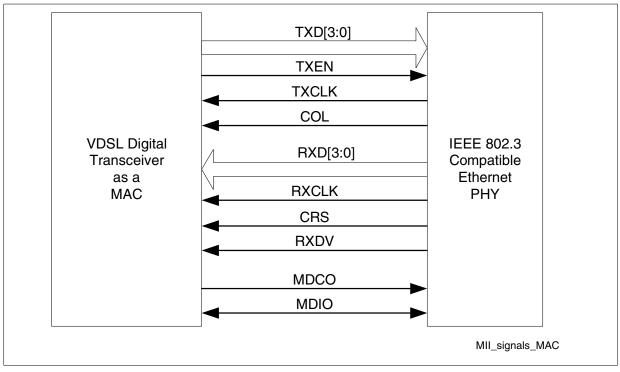

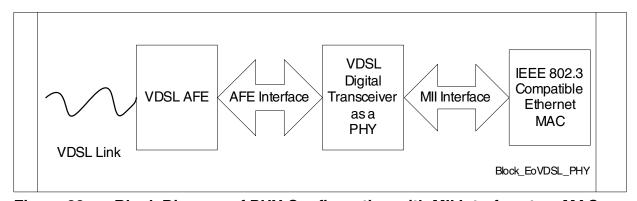

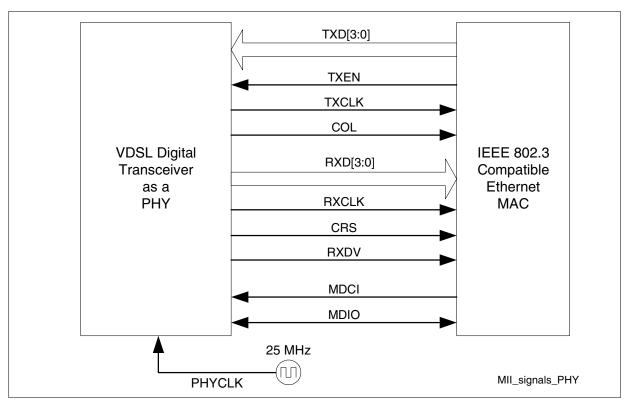

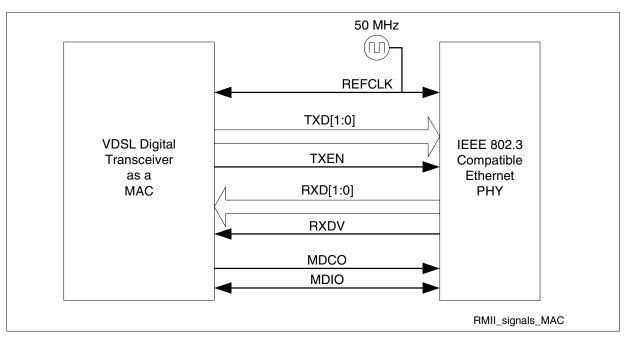

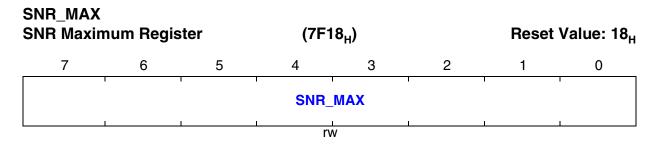

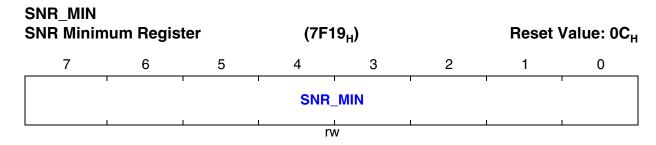

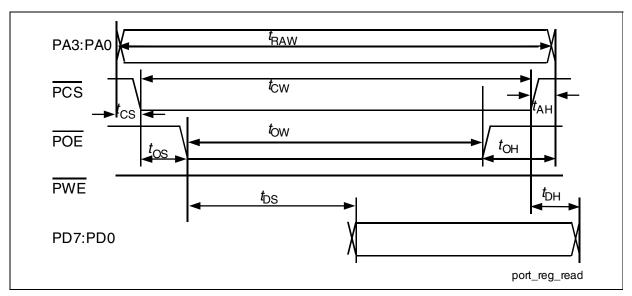

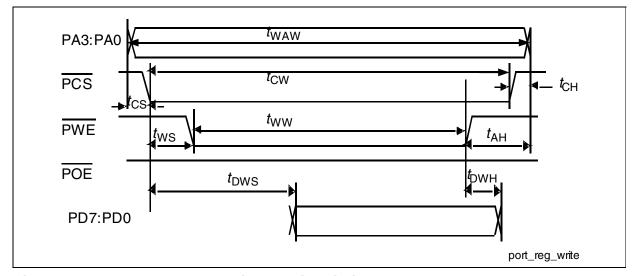

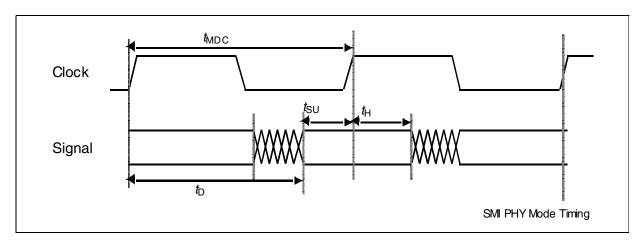

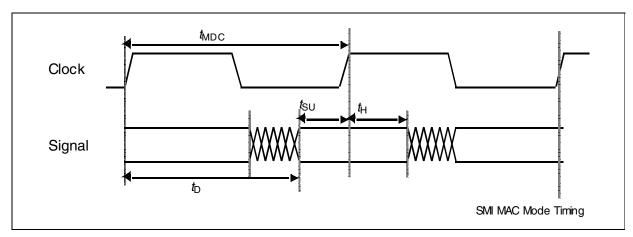

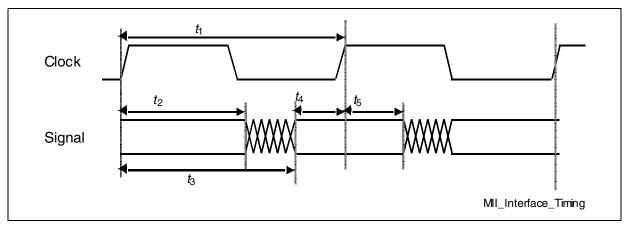

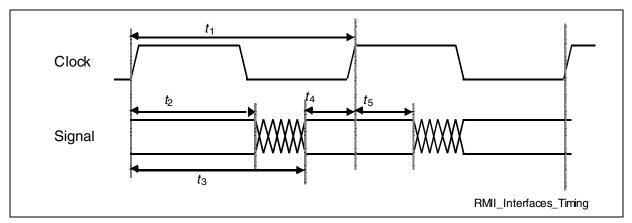

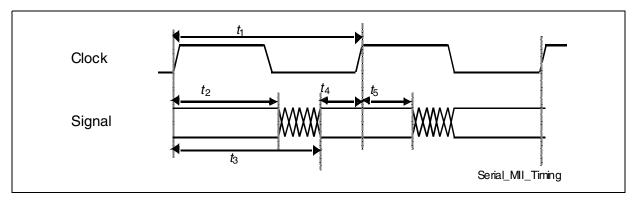

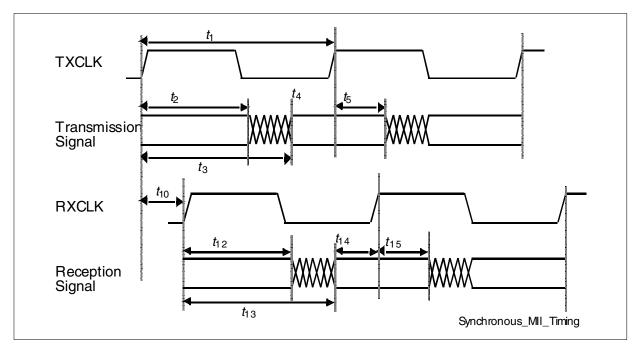

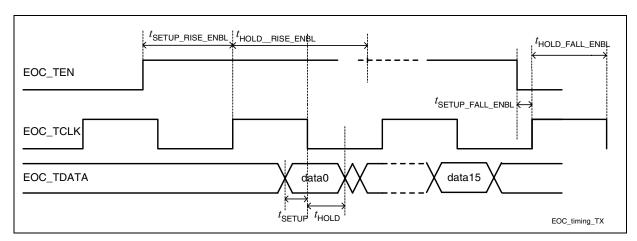

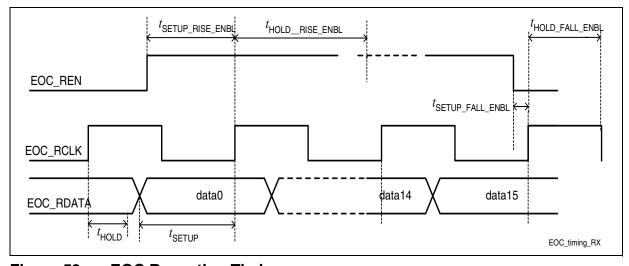

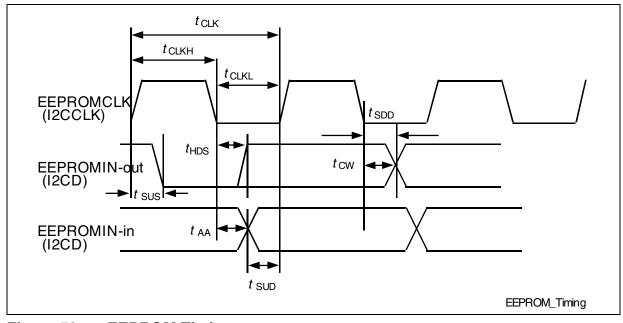

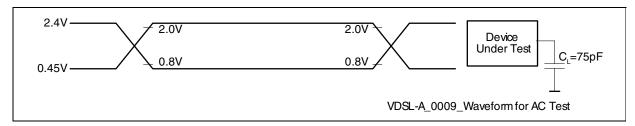

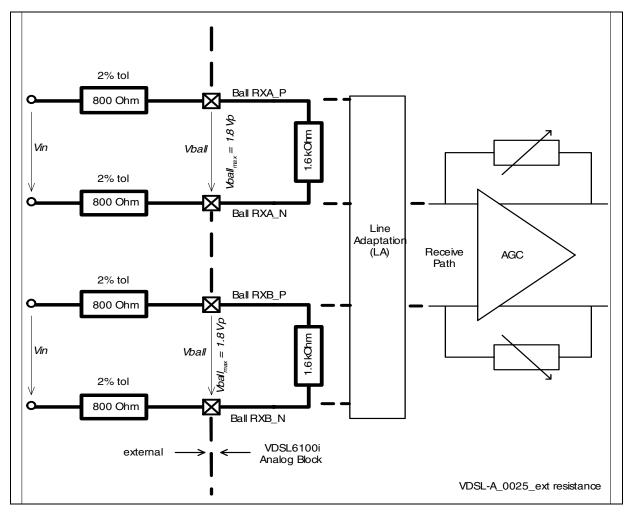

| 10.6             | SNR Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |      |