# **Envoy-CE2 Device**

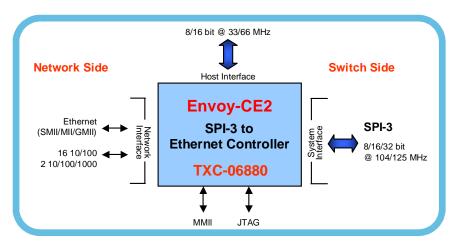

SPI-3 to Ethernet Controller TXC-06880

PRELIMINARY DATA SHEET

TXC-06880-MB, Ed. 4 February 2005

### **FEATURES**

- 2 Configurable Media Access Controllers (MACs)

- Each MAC is configurable as 8 Fast Ethernet ports (10/100 Mbit/s), 2 Fast Ethernet ports with extended buffers or 1 Gigabit Ethernet port (10/100/1000 Mbit/s)

- SPI-3 interface configurable in Link or PHY layer mode, operating at 125 MHz

- Support for Jumbo frames (9600 Bytes) and Super Jumbo frames (12000 Bytes)

- Full and Half Duplex (CSMA/CD) operation (Half Duplex only supported for Fast Ethernet)

- Programmable SPI-3 burst size from 64 to 1024 bytes

- Frame integrity verification (FCS and Frame length checks) and generation

- Packet statistics and Performance monitoring support for RMON per port

- PAUSE frame flow control for Full Duplex mode

- "Raise Carrier" flow control for Half Duplex mode

- · Programmable high and low FIFO watermarks for flow control trigger

- · Automatic PAUSE frame generation and termination

- Filtering of PAUSE frames in Ethernet Ingress or Egress

- Port aggregation from Ethernet to SPI-3, using routing tag encapsulation

- 8/16 bit Microprocessor interface, selectable between Intel or Motorola

- JTAG Boundary Scan (IEEE 1149.1 Standard)

- 580-lead Plastic Ball Grid Array (PBGA) package, 27 mm x 27 mm

#### **APPLICATIONS**

- Metro Edge Routers and Switches

- Ethernet over SONET/SDH Multi-Service Provisioning Platforms (MSPPs)

- IP DSLAMs

- 3G Wireless Base Stations

- 3G Radio Network Controllers (RNCs)

- Multi-Service Access Platforms (MSAPs)

TranSwitch Corporation • 3 Enterprise Drive • Shelton, Connecticut 06484 • USA

Tel: 203-929-8810 • Fax: 203-926-9453 • www.transwitch.com

### - IMPORTANT NOTICE -

TranSwitch Corporation reserves the right to make changes to its products, circuits or documentation described herein without notice.

EXCEPT AS SET FORTH IN A WRITTEN BINDING AGREEMENT BETWEEN TRANSWITCH CORPORATION AND A USER OF ITS PRODUCTS, TRANSWITCH CORPORATION ASSUMES NO LIABILITY FOR (A) CUSTOMER APPLICATIONS, INCLUDING CUSTOMER'S CIRCUITS, FIRMWARE AND SOFTWARE, (B) CUSTOMER PRODUCT DESIGN, (C) TRANSWITCH CORPORATION PRODUCT OR CUSTOMER PRODUCT SOFTWARE PERFORMANCE, (D) USE BY CUSTOMER OF ANY PRODUCT OR RELATED SAMPLE CIRCUIT OR APPLICATION PROVIDED HEREIN OR (E) INFRINGEMENT OF A THIRD PARTY'S PATENTS OR OTHER INTELLECTUAL PROPERTY RIGHTS ARISING OUT OF USE OF ANY AND ALL INFORMATION PROVIDED HEREIN. TRANSWITCH CORPORATION EXPRESSLY DISCLAIMS ALL REPRESENTATIONS AND WARRANTIES RELATED TO THE INFORMATION, PRODUCTS AND SAMPLE APPLICATIONS AND CIRCUITS CONTAINED HEREIN, INCLUDING BUT NOT LIMITED TO THE IMPLIED WARRANTIES OF FITNESS FOR PURPOSE INTENDED, MERCHANTABILITY AND NON-INFRINGEMENT, AND WILL NOT BE LIABLE FOR DIRECT OR INDIRECT DAMAGES RESULTING FROM THEIR USE.

TRANSWITCH DOES NOT OFFER CUSTOMER EITHER AN EXPRESS OR AN IMPLIED LICENSE UNDER ANY PATENT RIGHT, COPYRIGHT, MASK WORK RIGHT, OR OTHER INTELLECTUAL PROPERTY RIGHT COVERING OR RELATED TO ANY DESIGN, COMBINATION, MACHINE OR PROCESS IN WHICH TRANSWITCH CORPORATION'S PRODUCTS OR SERVICES MIGHT BE OR ARE USED, INCLUDING BUT NOT LIMITED TO THE USES DESCRIBED HEREIN. THE CUSTOMER IS URGED TO CONSULT WITH LEGAL COUNSEL BEFORE DECIDING ON A PARTICULAR APPLICATION, CIRCUIT, FIRMWARE OR SOFTWARE WITH ANY OF TRANSWITCH'S PRODUCTS.

TRANSWITCH CORPORATION'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS (OR SIMILAR APPLICATIONS WHERE COMPONENT FAILURE COULD RESULT IN LOSS OF LIFE OR PHYSICAL HARM) WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF TRANSWITCH CORPORATION.

As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

**PRELIMINARY** information documents contain information on products in the sampling, pre-production or early production phases of the product life cycle. Characteristic data and other specifications are subject to change. Contact TranSwitch Applications Engineering for current information on this product.

U.S. Patents No. 4,967,405; 5,040,170; 5,142,529; 5,265,096; 5,331,641; 5,724,362; 6,577,651B1

U.S. and/or foreign patents issued or pending

Copyright © 2005 TranSwitch Corporation

Envoy is a trademark of TranSwitch Corporation

TranSwitch, TXC and PHAST are registered trademarks of TranSwitch Corporation

Downloaded from Elcodis.com electronic components distributor

# **TABLE OF CONTENTS**

| Section                                                                              | Page |

|--------------------------------------------------------------------------------------|------|

| List of Figures                                                                      | 5    |

| List of Data Sheet Changes                                                           | 6    |

| 1.0 Overview                                                                         |      |

| 1.1 Device Description                                                               |      |

| 1.2 Application Example                                                              |      |

| 2.0 Functional Description                                                           | 10   |

| 2.1 Block Diagram                                                                    |      |

| 2.1.1 Media Access Controller (MAC)                                                  |      |

| 2.1.2 Serial Media Independent Interface (SMII)                                      | 12   |

| 2.1.3 Gigabit Media Independent Interface (GMII) & Media Independent Interface (MII) |      |

| 2.1.4 Ethernet Interface Description For Different Modes                             |      |

| 2.1.5 Management Media Independent Interface (MMII) Port                             |      |

| 2.1.6 Ingress & Egress Buffering Mechanism                                           |      |

| 2.1.7 System Packet Interface Level 3 (SPI-3)                                        | 16   |

| 2.1.7.1 PHY Mode                                                                     | 17   |

| 2.1.7.2 Link Mode                                                                    |      |

| 2.1.8 Microprocessor Interface                                                       |      |

| 2.1.9 JTAG Boundary Scan                                                             |      |

| 2.1.9.1 Boundary Scan Operation                                                      |      |

| 2.1.9.2 Boundary Scan Reset                                                          |      |

| 2.1.9.3 Boundary Scan Schematic                                                      | 21   |

| 2.1.9.4 Boundary Scan Chain                                                          | 21   |

| 3.0 Technical Characteristics                                                        | 22   |

| 3.1 lead Diagram                                                                     | 22   |

| 3.2 Lead Descriptions                                                                |      |

| 4.0 Selected Parameter Values                                                        | 40   |

| 4.1 Absolute Maximum Ratings and Environmental Limitations                           |      |

| 4.2 Thermal Characteristics                                                          |      |

| 4.3 Power Requirements                                                               |      |

| 4.4 Input, Output and Input/Output Parameters                                        |      |

| 4.4.1 Input Parameters For LVTTL                                                     |      |

| 4.4.2 Input Parameters For LVTTLpu (internal pull-up resistor)                       |      |

| 4.4.3 Output Parameters For CMOS 8mA                                                 |      |

| 4.4.4 Output Parameters For CMOS 12mA                                                |      |

| 4.4.5 Output Parameters For CMOS 16mA                                                |      |

| 4.4.6 Input/Output Parameters For LVTTL/CMOS 8mA                                     |      |

| 4.4.7 Input/Output Parameters For LVTTL/CMOS 16mA                                    |      |

| 5.0 Timing Characteristics                                                           |      |

| 6.0 Operation                                                                        |      |

| 6.1 SMII/GMII to SPI-3 Flow Functional Operation                                     |      |

| 6.1.1 Receive MAC Data Flow                                                          |      |

| 6.1.2 Receive MAC Checks                                                             |      |

| 6.1.2.1 FCS Check:                                                                   | 59   |

| 6.1.2.2 Frame Length Check:                                                          | 59   |

| 6.1.2.3 Maximum Frame Size Check:                                                    |      |

| 6.1.2.4 Interframe Gap Check:                                                        |      |

| 6.1.2.5 Destination Address Check:                                                   |      |

| 6.1.3 Receive MAC Statistics                                                         |      |

| 6.1.3.1 Counters:                                                                    | 60   |

TXC-06880

| 6.1.4 Ingress FIFO Operations                                                       |     |

|-------------------------------------------------------------------------------------|-----|

| 6.1.4.1 Ingress FIFO Write:                                                         |     |

| 6.1.4.2 Ingress FIFO Read:                                                          |     |

| 6.1.4.3 Ingress FIFO Frame Availability for Transfer (Store and Forward/Streaming): | 61  |

| 6.1.5 SPI-3 Output Operations                                                       | 62  |

| 6.1.5.1 Data Flow Operations:                                                       | 62  |

| 6.1.5.2 SPI-3 Output Interface Frame Format:                                        | 62  |

| 6.2 SPI-3 to SMII/GMII Flow Functional Operation                                    | 63  |

| 6.2.1 SPI-3 Input Operation                                                         |     |

| 6.2.1.1 Input SPI-3 Data Flow:                                                      |     |

| 6.2.1.2 Oversubscription Mode                                                       | 63  |

| 6.2.1.3 Input SPI-3 Interface Frame Format:                                         |     |

| 6.2.2 Egress FIFO Operations                                                        |     |

| 6.2.2.1 Egress FIFO Write:                                                          |     |

| 6.2.2.2 Egress FIFO Frame Availability for Transfer (Store and Forward/Streaming):  |     |

| 6.2.2.3 Egress FIFO Read:                                                           |     |

| 6.2.3 Transmit MAC Data Flow                                                        |     |

| 6.2.4 Transmit MAC Configurable Options and Checks                                  | 67  |

| 6.2.4.1 Frame Check Sequence (FCS) Generation Option:                               |     |

| 6.2.4.2 Pad Short Ethernet Frames Option:                                           |     |

| 6.2.4.3 Frame Length Check:                                                         |     |

| 6.2.4.4 Maximum Frame Size Check:                                                   | 67  |

| 6.2.4.5 Back to Back Interframe Gap Option:                                         |     |

| 6.2.4.6 Source Address Replace Option:                                              |     |

| 6.2.4.7 PAUSE Frame Filter Option:                                                  |     |

| 6.2.4.8 Preamble Length Option:                                                     | 67  |

| 6.2.5 Transmit MAC Statistics                                                       |     |

| 6.2.5.1 Counters:                                                                   |     |

| 6.3 Port Aggregation                                                                |     |

| 6.3.1 Normal vs. Aggregate Mode                                                     |     |

| 6.4 Ethernet Half Duplex                                                            | 69  |

| 6.4.1 Overview                                                                      |     |

| 6.4.2 Carrier Sense                                                                 |     |

| 6.4.3 Collision Detection                                                           |     |

| 6.4.4 Alternate BEB Truncation                                                      |     |

| 6.4.5 Excessive Collisions                                                          |     |

| 6.4.6 Half-Duplex Flow Control                                                      |     |

| 6.5 Ethernet Full Duplex                                                            |     |

| 6.5.1 Overview                                                                      |     |

| 6.5.2 PAUSE Control Frame Reception                                                 |     |

| 6.5.3 PAUSE Control Frame Generation                                                |     |

| 6.5.3.1 Automatic PAUSE Frame Generation                                            |     |

| 6.5.3.2 Host Initiated PAUSE Frame Generation                                       |     |

| 7.0 Memory Maps and Bit Descriptions                                                |     |

| Package Information                                                                 |     |

| Ordering Information                                                                |     |

| Related Products                                                                    |     |

| Standards Documentation Sources                                                     | 118 |

Please note that TranSwitch provides documentation for all of its products. Current editions of many documents are available from the Products page of the TranSwitch Web site at <a href="www.transwitch.com">www.transwitch.com</a>. Customers who are using a TranSwitch Product, or planning to do so, should register with the TranSwitch Marketing Department to receive relevant updated and supplemental documentation as it is issued. They should also contact the Applications Engineering Department to ensure that they are provided with the latest available information about the product, especially before undertaking development of new designs incorporating the product.

# **LIST OF FIGURES**

| Figur | re                                                                     | Page |

|-------|------------------------------------------------------------------------|------|

| 1.    | Flexible Architecture for Ethernet Over SONET/SDH & Router Application | 9    |

| 2.    | Functional Block Diagram of the Envoy-CE2                              | 10   |

| 3.    | GMII (1000 Mbit/s) Only Interface Connection                           | 13   |

| 4.    | MII (10/100 Mbit/s) Only Interface Connection                          | 14   |

| 5.    | GMII/MII (10/100/1000 Mbit/s) Interface Connection                     | 14   |

| 6.    | SMII (10/100 Mbit/s) Interface Connection                              | 15   |

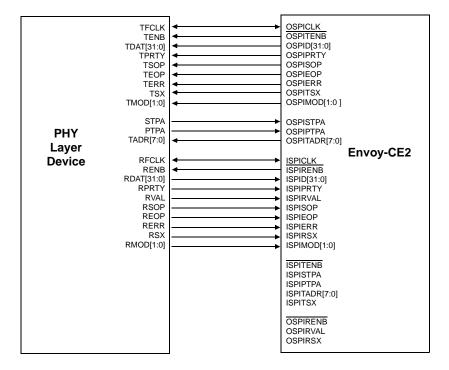

| 7.    | Envoy-CE2 in PHY Layer Mode                                            | 17   |

| 8.    | Envoy-CE2 in Link Layer Mode                                           | 18   |

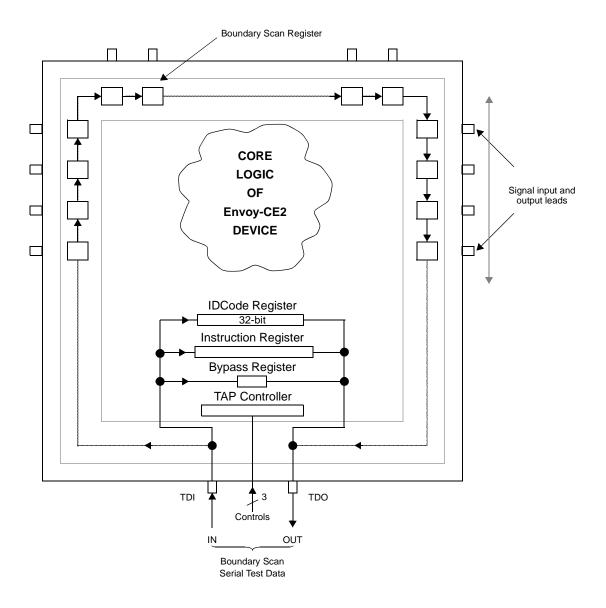

| 9.    | Boundary Scan Schematic                                                | 21   |

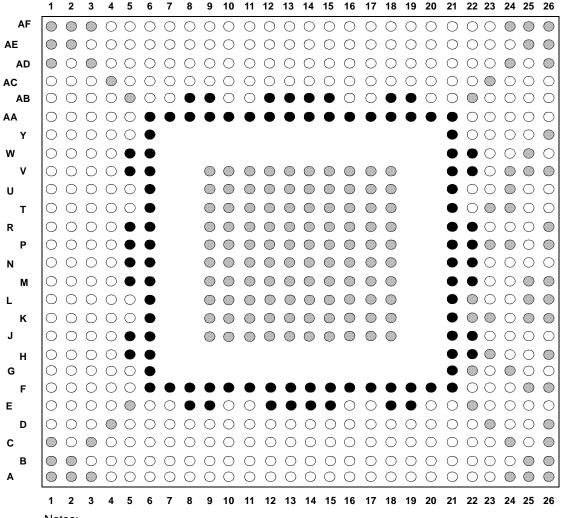

| 10.   | Envoy-CE2 Lead Diagram                                                 | 22   |

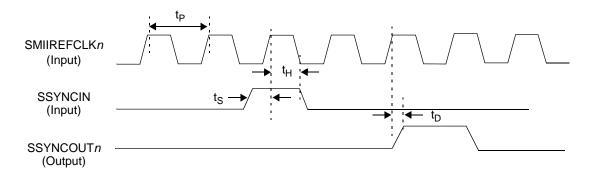

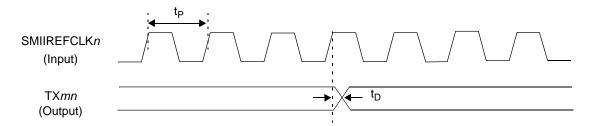

| 11.   | SMII Sync In/Out Timing                                                | 44   |

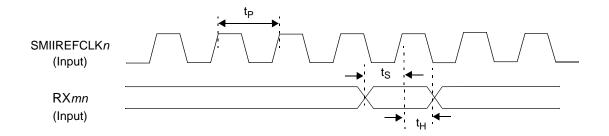

| 12.   | SMII Transmit Interface Timing                                         | 45   |

| 13.   | SMII Receive Interface Timing                                          | 45   |

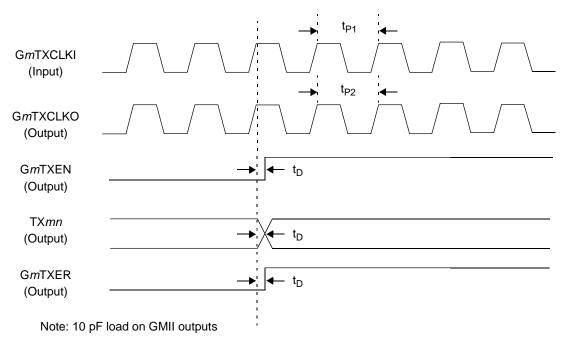

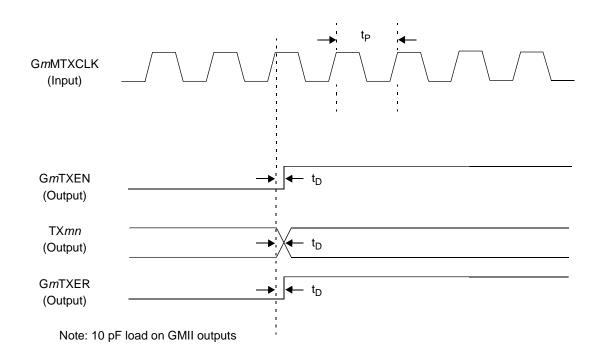

| 14.   | GMII Transmit Interface Timing Using GmTXCLKI                          | 46   |

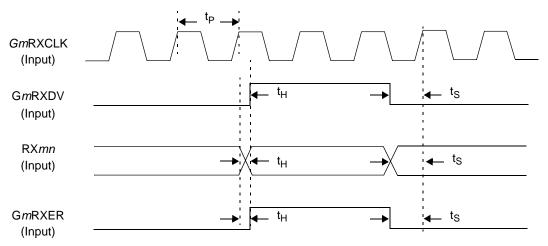

| 15.   | GMII/MII Receive Interface Timing Using GmRXCLK                        | 47   |

| 16.   | MII Transmit Interface Timing Using GmMTXCLK                           | 48   |

| 17.   | Management MII Interface Timing                                        | 49   |

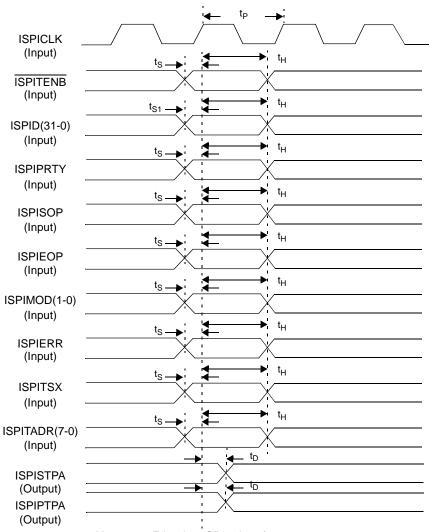

| 18.   | SPI-3 Data Input Interface Timing                                      | 50   |

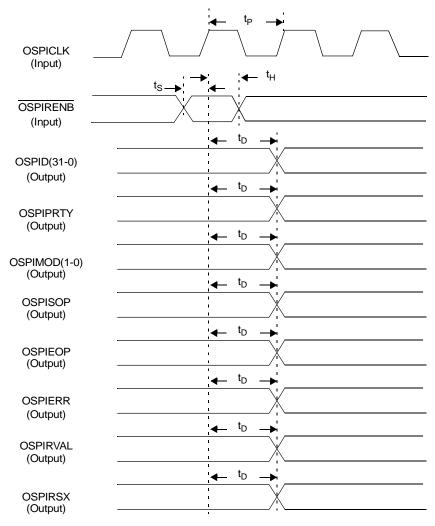

| 19.   | SPI-3 Data Output Interface Timing                                     | 51   |

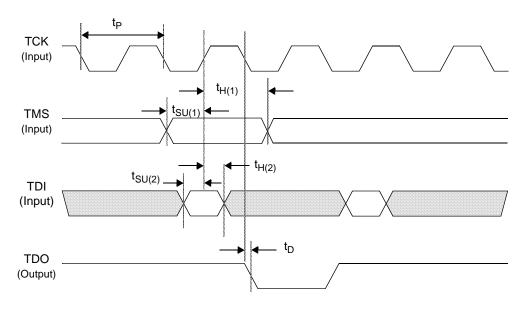

| 20.   | Boundary Scan Timing Diagram                                           | 52   |

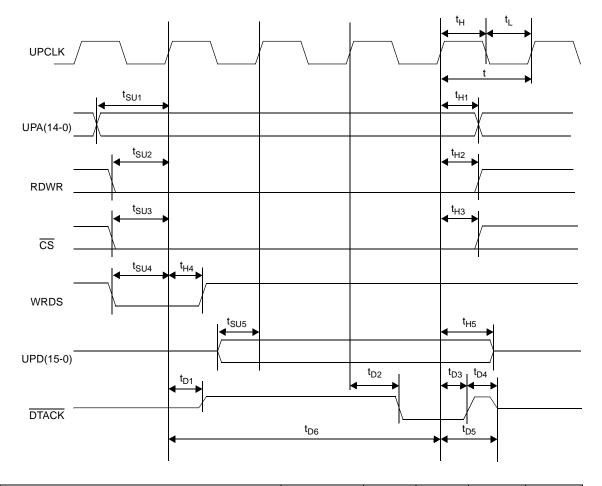

| 21.   | Motorola MPC860 Write Cycle Timing                                     | 53   |

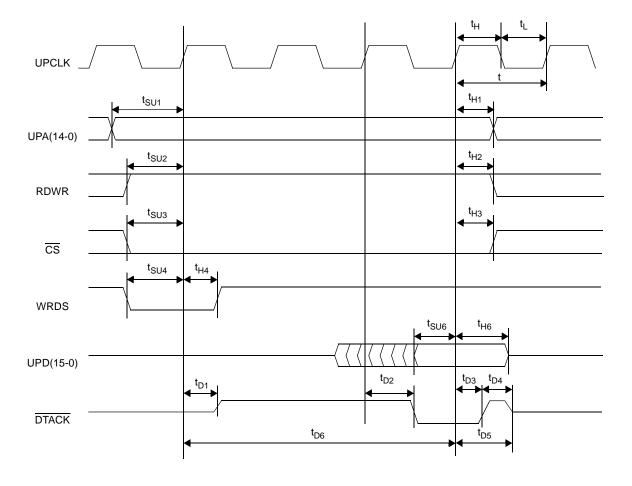

| 22.   | Motorola MPC860 Read Cycle Timing                                      | 55   |

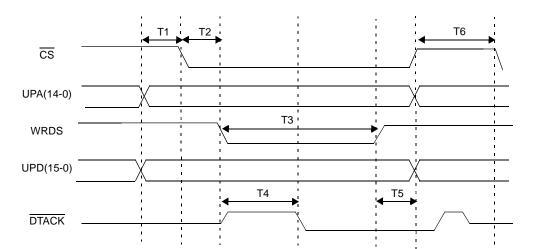

| 23.   | Asynchronous Microprocessor Interface: Intel Write Cycle Timing        | 57   |

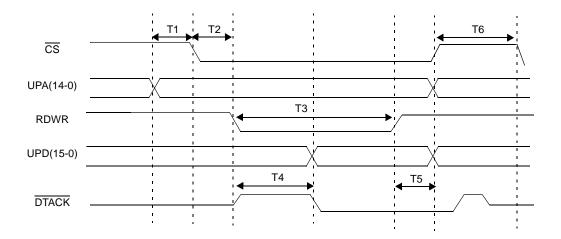

| 24.   | Asynchronous Microprocessor Interface: Intel Read Cycle Timing         | 58   |

| 25.   | Envoy-CE2 Package Diagram                                              | 116  |

DATA SHEET

TXC-06880

# LIST OF DATA SHEET CHANGES

# Section A:

This Section A change list identifies those areas within previous released Envoy-CE2 device Data Sheet **Edition 3**, **January 2005** that have significant differences relative to the second previous released Envoy-CE2 Data Sheet **Edition 2**, **November 2004**.:

| Page<br>Number of<br><u>Updated</u><br><u>Data Sheet</u> | Summary of the Change                                                                                                                                                                      |  |  |  |  |  |

|----------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| All                                                      | Changed edition number and date.                                                                                                                                                           |  |  |  |  |  |

| 3-5                                                      | Updated Table of Contents and List of Figures.                                                                                                                                             |  |  |  |  |  |

| 6                                                        | Added 'List of Data Sheet Changes' section.                                                                                                                                                |  |  |  |  |  |

| 11                                                       | Modified Section 2.1.1.                                                                                                                                                                    |  |  |  |  |  |

| 19                                                       | Modified Section 2.1.9.                                                                                                                                                                    |  |  |  |  |  |

| 49                                                       | Modified Max value of "MDC frequency" for table Figure 17.                                                                                                                                 |  |  |  |  |  |

| 50                                                       | Modified last row for table Figure 18.                                                                                                                                                     |  |  |  |  |  |

| 57                                                       | Modified last column of Symbols "T2", "T3" and "T4" for table Figure 23.                                                                                                                   |  |  |  |  |  |

| 58                                                       | Modified last column of Symbols "T3" and "T4" for table Figure 24.                                                                                                                         |  |  |  |  |  |

| 63                                                       | Modified Section 6.2.1.1 and added Section 6.2.1.2.                                                                                                                                        |  |  |  |  |  |

| 81                                                       | Modified Description for Address "0040".                                                                                                                                                   |  |  |  |  |  |

| 87                                                       | Modified Description for Addresses "2014" and "2040". Changed "STPA Violation Frame Error Enable" to "Reserved. Must be set to 0 for normal operation." in Description for Address "2018". |  |  |  |  |  |

| 87                                                       | Changed "SPI-3 Input Overflow Packet Violation Counter" to "Reserved" in Description and modified "RC" to "RO" in Mode for Address "2068".                                                 |  |  |  |  |  |

| 117                                                      | Modified and added new Part Number. Removed two Related Product devices.                                                                                                                   |  |  |  |  |  |

### Section B:

This Section B change list identifies those areas within this updated Envoy-CE2 device Data Sheet that have significant differences relative to the previous and now superseded Envoy-CE2 Data Sheet:

Updated Envoy-CE2 device Data Sheet: *PRELIMINARY* Edition 4, February 2005 Previous Envoy-CE2 device Data Sheet: *PRODUCT PREVIEW* Edition 3, January 2005

The page numbers indicated below of this updated Data Sheet include changes relative to the previous Data Sheet.

| Page<br>Number of<br><u>Updated</u><br><u>Data Sheet</u> | Summary of the Change                                                        |

|----------------------------------------------------------|------------------------------------------------------------------------------|

| All                                                      | Changed edition number and date. Changed Product Preview to Preliminary.     |

| 3-5                                                      | Updated Table of Contents and List of Figures.                               |

| 6                                                        | Updated 'List of Data Sheet Changes' section.                                |

| 50                                                       | Modified table Parameter column for Figure 18.                               |

| 59                                                       | Modified Section 6.1.2.1, Section 6.1.2.2 and Section 6.1.2.3.               |

| 60                                                       | Modified Section 6.1.2.4 and Section 6.1.2.5.                                |

| 63                                                       | Modified Section 6.2.1.1 and Section 6.2.1.2.                                |

| 67                                                       | Modified Section 6.2.4.7.                                                    |

| 84                                                       | Modified rows for register "2008", "200C", "2014" and "2014".                |

| 86                                                       | Modified Description for Bit Range 7-0 of Address "2008".                    |

| 87                                                       | Modified Description for Bit Range 7-0 of Address "200C", "2014" and "2014". |

| 101                                                      | Modified Bit Range 15-8 Description for Address "4008".                      |

| 106                                                      | Modified Bit "2" Description for Address "4084".                             |

| 107                                                      | Modified Bit "24", "25", "26" and "27" Descriptions for Address "4084".      |

- Overview -

# 1.0 OVERVIEW

# 1.1 DEVICE DESCRIPTION

The Envoy<sup>™</sup>-CE2 is the next generation of powerful Ethernet to SPI-3 Controllers for carrier-class networks. The Envoy-CE2 incorporates two configurable Media Access Controllers (MACs). Each MAC can be configured as a single Gigabit Ethernet (10/100/1000 Mbit/s), dual Fast Ethernet with extended buffers or octal Fast Ethernet (10/100 Mbit/s) interface and is programmable for either full-duplex or half-duplex operation. The Envoy-CE2 supports Super Jumbo (12 KBytes) packets on both Fast Ethernet and Gigabit Ethernet interfaces.

The Envoy-CE2 is designed to interface directly with SPI-3 compliant devices, such as network processors. The support for master mode on the SPI-3 allows glueless interface with standard SPI-3 based GFP/VCAT framers and mappers. On the Ethernet side, the Envoy-CE2 interfaces directly with standard Fast Ethernet and Gigabit Ethernet PHY/SerDes devices via the SMII and GMII. The Envoy-CE2 incorporates on-chip buffering to promote high performance without congestion or loss of data and provides backpressure support on both the Ethernet and SPI-3 interfaces.

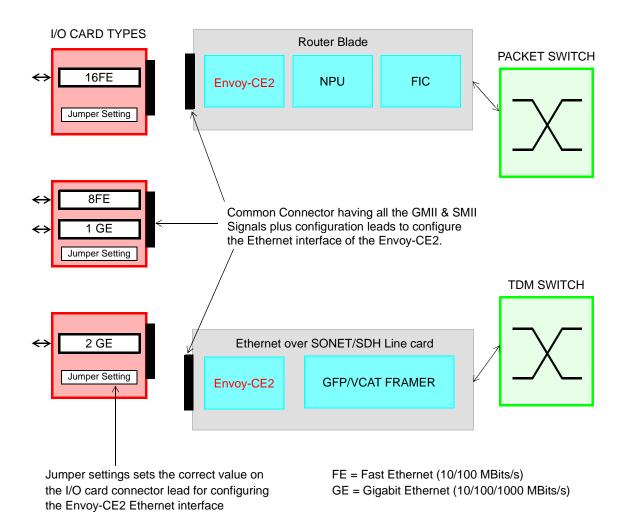

#### 1.2 APPLICATION EXAMPLE

Ethernet is emerging as the Layer 2 Protocol of choice in Enterprise, Access and Metro Networks. This is due to its cost effectiveness, wide spread acceptance and ease of use. The Envoy-CE2 provides a means to connect a cost efficient, switching protocol interface in Ethernet to a Telecom based interface, the OIF SPI-3. Current network processing devices that traditionally have a packet based interface the OIF SPI-3 interface, can now interface to Ethernet based devices using the Envoy-CE2.

Figure 1. Flexible Architecture for Ethernet Over SONET/SDH & Router Application

TXC-06880

TRANSWITCH'

- Functional Description -

# 2.0 FUNCTIONAL DESCRIPTION

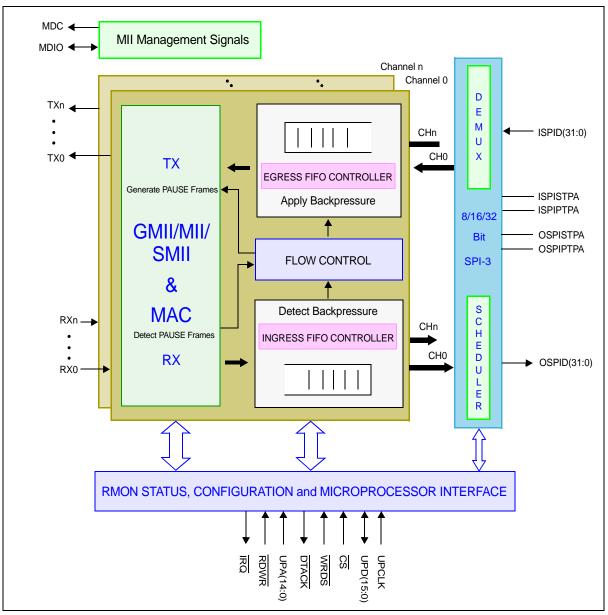

### 2.1 BLOCK DIAGRAM

**Note:** Each MAC is configurable as 8 Fast Ethernet Ports (10/100 Mbit/s), 2 Fast Ethernet Ports with Extended Buffers, or 1 Gigabit Ethernet Port (10/100/1000 Mbit/s)

Figure 2. Functional Block Diagram of the Envoy-CE2

#### 2.1.1 Media Access Controller (MAC)

The Envoy-CE2 has 2 Configurable Media Access Controllers (MACs):

- Configurable MAC A services ports 0 to 7

- Configurable MAC B services ports 8 to 15

### Each MAC can be configured as:

8 Fast Ethernet ports with 7.75 KBytes of Ingress buffering and 4 KBytes of Egress buffering per port supporting 10/100 Mbit/s data rates via SMII.

OR

• 1 Gigabit Ethernet port with 62 KBytes of Ingress buffering and 32 KBytes of Egress buffering per port supporting 10/100/1000 Mbit/s data rates via GMII/MII.

OR

2 Fast Ethernet ports with 31 KBytes of Ingress buffering and 16 KBytes of Egress buffering per port supporting 10/100 Mbit/s data rates via SMII. (Extended SMII Mode).

#### Possible Envoy-CE2 Configurations:

- 16 Fast Ethernet Ports

- 2 Gigabit Ethernet Ports

- 8 Fast Ethernet Ports and 1 Gigabit Ethernet Port

- 4 Fast Ethernet Ports (Extended SMII Mode) with larger buffers (31 KBytes of Ingress Buffering and 16 KBytes of Egress Buffering per port).

The main features supported by each Configurable MAC are:

- Compliant to IEEE 802.3, 802.3i, 802.3u, 802.3x, 802.3z

- Full Duplex and Half Duplex (CSMA/CD) operation per configurable MAC

- Connection to standard 10/100 Mbit/s Fast Ethernet PHY devices via SMII interface

- Connection to Multi-rate 10/100/1000 Mbit/s Gigabit Ethernet PHY devices via GMII/ MII interface

- Frame Integrity Verification (FCS and length checks)

- · Errored Frames can be configured to be filtered

- Programmable Inter-Packet Gap (IPG) between Ethernet frames

- · Programmable maximum frame length

- Minimum frame size = 64 bytes

- Maximum frame size = 12 KBytes

- Support for VLAN tagged frame transmission

- Programmable High and Low FIFO watermarks for space and frame/chunk availability generation

- MAC control sublayer provides support for control frames including PAUSE frames

- Automatic PAUSE Frame Generation and Termination

- 62 KByte ingress FIFO per Configurable MAC

- 32 KByte egress FIFO per Configurable MAC

- · Far end switch side loopback for diagnostic capability

- Packet statistics and performance monitoring support for Remote Network Monitoring (RMON)

DATA SHEET TXC-06880

#### - Functional Description -

### 2.1.2 Serial Media Independent Interface (SMII)

The Serial Media Independent Interface (SMII) is capable of operating at 10/100 Mbit/s mixed mode. The SMII is configurable to operate in either Full Duplex or Half Duplex mode.

Control and Data are transported across the Tx and Rx signals in 10 bit segments. The segments are synchronized using the SYNC signal. From the 10 bits, 2 bits are control and the other 8 bits are data. In 100 Mbit/s mode, every 10 bit segment transfers a new byte of data. In 10 Mbit/s mode, each 10 bit segment is repeated ten times. Please refer to the SMII specification for further details.

Each SMII port is comprised of:

- Two serial data signals (Tx and Rx) per port

- 125 MHz reference clock signal (Clock) per Configurable MAC

- Synchronization signal (SYNC) per Configurable MAC

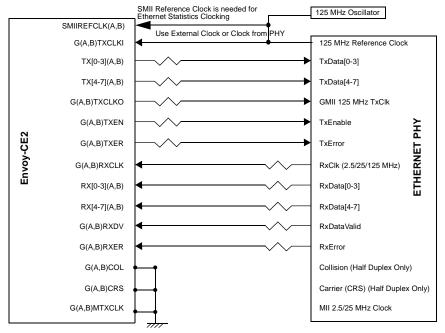

#### 2.1.3 Gigabit Media Independent Interface (GMII) & Media Independent Interface (MII)

The GMII interface of the Envoy-CE2 is capable of operating at 1 Gbit/s. When configured in MII mode, the interface is capable of operating at 10/100 Mbit/s. The GMII/MII ports allow the Envoy-CE2 to connect to Multi-rate Gigabit Ethernet PHY devices.

When configured as GMII, each port is comprised of:

- Two data buses, Transmit and Receive, each 8 bits wide

- · Two clock signals, 1 per direction

- The transmit clock is an output and the receive clock is an input

- An input pad is provided to source the transmit clock from an external oscillator

- Two network status signals (Rx Error and Tx Error)

- Two control signals (Rx Data Valid and Tx Enable)

- · All signals are synchronous to the clock

- Note: The GMII is a 3.3 V interface that will only work with a 3.3 V PHY device.

Note: The GMII is a 3.3 V interface that will only work with a 3.3 V PHY device.

When configured as MII, each port is comprised of:

- Two data buses, Transmit and Receive, each 4 bits wide

- Uses Least Significant Nibble of the GMII bus

- · Two clock signals, 1 per direction

- Both the transmit and receive clocks are inputs to the Envoy-CE2

- Four Status signals (Rx Data Valid, Tx Enable, Carrier sense, and Collision detect)

**Note:** The GMII signal pins are muxed with the SMII signal pins.

The following sequence needs to be performed when switching from GMII mode to MII mode and vice versa:

- Enable Soft Reset for the MAC (Register 0x4000 Bit 31 for Port 0)

- Reprogram Interface Mode Register (Register 0x4004 Bits 8-9)

- · Remove Soft Reset

#### 2.1.4 Ethernet Interface Description For Different Modes

The Envoy-CE2 has 16 Ethernet Ports: Ports 0 to 15. Ports 0 to 7 are assigned to Configurable MAC A (CMAC A) and Ports 8 to 15 are assigned to Configurable MAC B (CMAC B). Each CMAC can be configured as 8 SMII ports, 2 Extended SMII ports (larger buffers) or 1 triple speed GMII/MII port. Device pins CFGCMACA(1:0) and CFGCMACB(1:0) are used to configure CMAC A and CMAC B, respectively.

When CMAC A is configured in GMII/MII mode (CFGCMACA = 01), port 0 will be in GMII or MII mode (MII mode is based on programmable bits "Interface Mode": register 4004 bits 8-9) and ports 1 to 7 are inactive. When CMAC A is configured in Extended SMII mode (CFGCMACA = 10), ports 0 and 4 will be in extended SMII mode and ports 1, 2, 3, 5, 6, and 7 are inactive. When CMAC A is configured in SMII mode (CFGCMACA = 11), ports 0 to 7 will be in SMII mode.

When CMAC B is configured in GMII/MII mode (CFGCMACB = 01), port 8 will be in GMII or MII mode (MII mode is based on programmable bits "Interface Mode": register 4804 bits 8-9) and ports 9 to 15 are inactive. When CMAC B is configured in Extended SMII mode (CFGCMACB = 10), ports 8 and 12 will be in extended SMII mode and ports 9, 10, 11, 13, 14, and 15 are inactive. When CMAC B is configured in SMII mode (CFGCMACB = 11), ports 8 to 15 will be in SMII mode.

Note: Series termination resistor values are dependent on the selection of the Ethernet PHY. Please consult the specification of the Ethernet PHY for series termination resistor values

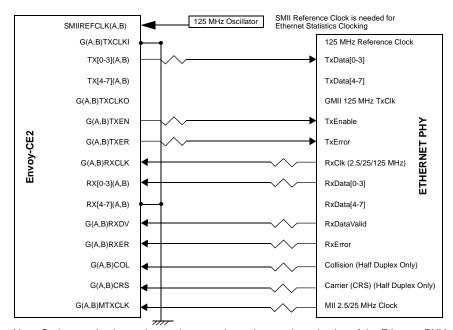

Figure 3. GMII (1000 Mbit/s) Only Interface Connection

TXC-06880

#### - Functional Description -

Note: Series termination resistor values are dependent on the selection of the Ethernet PHY. Please consult the specification of the Ethernet PHY for series termination resistor values

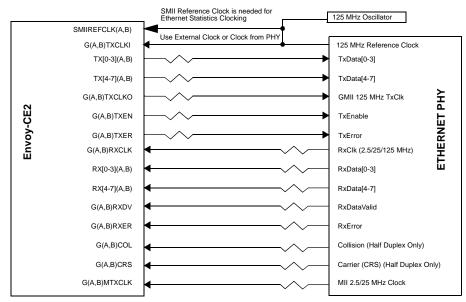

Figure 4. MII (10/100 Mbit/s) Only Interface Connection

Note: Series termination resistor values are dependent on the selection of the Ethernet PHY. Please consult the specification for the Ethernet PHY to determine the series termination resistor values

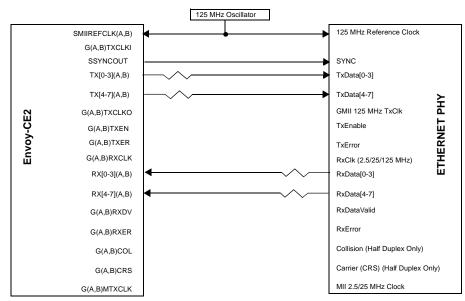

Figure 5. GMII/MII (10/100/1000 Mbit/s) Interface Connection

## - Functional Description -

Note: Series termination resistor values are dependent on the selection of the Ethernet PHY. Please consult the specification for the Ethernet PHY to determine the series termination resistor values

Figure 6. SMII (10/100 Mbit/s) Interface Connection

#### 2.1.5 Management Media Independent Interface (MMII) Port

The MMII port on the Envoy-CE2 is used to configure and retrieve status from the Ethernet PHYs connected to the Envoy-CE2. Multiple PHY devices (up to 32) are programmable via this interface. The Envoy-CE2 MMII interface is compliant to the Management interface outlined in IEEE 802.3u. The device can be configured for preamble suppression at the MMII interface. The frequency of the output clock of the MMII port (MDC) is programmable to UPCLK/n (n = 4, 6, 8, 10, 14, 20, or 28). All data transfers are synchronous to the clock signal and provide support for up to 32 PHYs.

Two additional functions performed by the interface are the Scan function and the Automatic PHY address Increment function. In Scan mode, multiple back-to-back reads can be performed from a particular PHY. When Scan mode and Auto PHY address increment are enabled, back-to-back reads can be performed with the PHY address being incremented after each read. Hence, the PHYs are scanned.

Note: When Scan mode and Auto PHY address increment are enabled, the range of addresses scanned will be between "PHY Address" (Register 0x0048 Bits(8-12)) and PHY number 31.

#### Notes:

- 1. When Scan mode and Auto PHY address increment are enabled, the range of addresses scanned will be between "PHY Address" (Register 0x0048 Bits 8-12) and PHY number 31.

- 2. Envoy's Management Media Independent Interface (MMII) is in Master mode.

DATA SHEET

- Functional Description -

#### 2.1.6 Ingress & Egress Buffering Mechanism

Two buffering mechanisms are provided: **Store and Forward** and **Streaming**. In Store and Forward mode, a complete frame is stored in the Ingress and Egress buffers, before it is transmitted across the SPI-3 and Ethernet interfaces, respectively. In Streaming mode, a programmable number of bytes are stored in the Ingress and Egress buffers, before the frame is transmitted across the SPI-3 and Ethernet interfaces, respectively. Hence for low latency applications, streaming mode provides a solution to transport large frames with smaller buffer space. The Ingress and Egress buffers can be programmed separately.

### 2.1.7 System Packet Interface Level 3 (SPI-3)

The SPI-3 interface operates using an 8, 16, or 32 bit wide pin configurable data bus (TDAT(31-0) and RDAT(31-0)). The minimum clock (TFCLK and RFCLK) rate is 50 MHz and the maximum clock rate is 125 MHz. The device can be pin configured to operate as a Link (Master) or a PHY (Slave) layer device. Multi-PHY (MPHY) and Single-PHY (SPHY) modes of operation are supported (programmable). Packet level transfer mode is supported in Multi-PHY mode only and Byte level transfer mode is supported in both Single-PHY and Multi-PHY modes. On the output interface, chunking is supported where a configured number of bytes (chunk) are transferred by a port from the PHY device to the Link device. Programmable packet available thresholds are provided on the input interface. The SPI-3 interface is divided into the SPI-3 input and the SPI-3 output.

The SPI-3 interface assigns an 8 bit port address with an address range of 0 to 255. The Envoy-CE2 allows programming of an offset base address for the SPI-3 port address assignment. The base address is a 3-bit programmable value and is assigned to the most significant 3 bits of the 8 bit SPI-3 address. Individual SPI-3 port addresses are calculated by adding the (base address x 32) to the logical Ethernet port number. For example, the SPI-3 address of port 11 with a base address of 3 will give a SPI-3 port address of (11 + (3x32)) =107.

#### 2.1.7.1 PHY Mode

In PHY layer mode, the following SPI-3 interface naming convention is used, per the OIF SPI-3 specification. Packets received at the Ethernet receive interface, are stored in the Ingress FIFO and **transmitted** on the **SPI-3 Rx** interface (SPI-3 output for Envoy-CE2). Packets **received** at the **SPI-3 Tx** interface (SPI-3 input for Envoy-CE2), are stored in the Egress FIFO and transmitted on the Ethernet transmit interface.

In PHY layer mode, space availability per channel for Transmit Interface (PTPA/STPA) is asserted when a programmable number of bytes or more, are available for storage in the Egress FIFO. The de-assertion of space availability is also programmable and is indicated when a programmed number of bytes are available for storage in the Egress FIFO (near-full condition). For PTPA, the programmable values for the assertion and de-assertion of the signal are 8 to 2040 bytes. For STPA, the programmable values for assertion and de-assertion are 2 to 255 bytes in 8-bit SPI-3 mode, 4 to 510 bytes in 16-bit SPI-3 mode, and 8 to 1020 bytes in 32-bit SPI-3 mode. In the Receive direction (SPI-3 output), one of the channels will be selected for frame transfer, based on a round robin algorithm. Packet data may be transferred across the Receive Interface in chunks, programmable from 8 to 2040 bytes, in 8 byte increments. In the Receive direction (SPI-3 output), the time between consecutive transfers (pause) is programmable to 0 or 2 cycles.

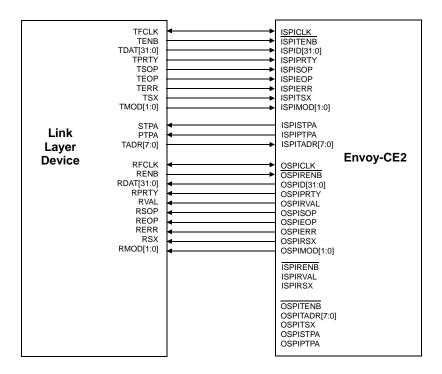

Figure 7. Envoy-CE2 in PHY Layer Mode

TXC-06880

- Functional Description -

#### 2.1.7.2 Link Mode

In Link layer mode, the following SPI-3 interface naming convention is used, per the OIF SPI-3 specification. Packets received at the Ethernet receive interface, are stored in the Ingress FIFO and **transmitted** on the **SPI-3 Tx** interface (SPI-3 output for Envoy-CE2). Packets **received** at the **SPI-3 Rx** interface (SPI-3 input for Envoy-CE2), are stored in the Egress FIFO and transmitted on the Ethernet transmit interface.

At the Transmit Interface (SPI-3 output) in Link layer mode, the device monitors the STPA and PTPA signals for indication of buffer space availability in the PHY device. In the event the PHY device indicates FIFO buffer availability by asserting its Transmit Packet available status signal and there is packet data available for transfer to the port, then Envoy-CE2 will transfer packet data to the PHY port. The transfer may be chunk-based or packet-based. In chunk mode, a specified number of bytes (chunk) is transferred to a PHY device port, before the Envoy-CE2 selects another PHY port for packet data transfer. If an end of packet is encountered, a reselection also occurs. Chunk sizes are programmable from 8 to 2040 bytes, in 8 byte increments. In packet based transfer, Envoy-CE2 will transfer the complete packet to a PHY port and will pause data transmission when the PHY device port indicates its FIFO is almost full by de-asserting its Transmit Packet available signal. Selection of another PHY port is done once a complete packet has been sent to the current PHY port. Port selection is accomplished using the first come, first serve, round robin algorithm. At the Receive interface (SPI-3 input), the PHY device will transfer packet data to the Envoy-CE2, which will globally backpressure the PHY device when any Port's Egress FIFO becomes almost full.

Figure 8. Envoy-CE2 in Link Layer Mode

#### 2.1.8 Microprocessor Interface

The Envoy-CE2 configuration, status, and device management is performed via its microprocessor interface. The interface has a 15 bit wide address bus UPA(14-0) and a pin configurable 8 or 16 bit wide data bus UPD(15-0). It is compatible with standard Intel/Motorola micro-controllers. The interface operates from a minimum clock (UPCLK) frequency of 33 MHz to a maximum clock frequency of 66 MHz.

The following table shows the Pin description for the Host interface in Intel and Motorola modes:

| Envoy-CE2 Pin Name               | Intel Mode Description    | Motorola Mode Description       |

|----------------------------------|---------------------------|---------------------------------|

| Microprocessor Clock (UPCLK)     | Host Interface Clock      | Host Interface Clock            |

| Microprocessor Data Bus (UPD)    | Host Data Bus             | Host Data Bus                   |

| Microprocessor Address Bus (UPA) | Host Address Bus          | Host Address Bus                |

| Chip Select (CS)                 | Device Chip Select        | Device Chip Select              |

| Write/Transfer Start (WRDS)      | Write Strobe (Active Low) | Active Low Transfer Start       |

| Transfer Acknowledge (DTACK)     | Ready                     | Active Low Transfer Acknowledge |

| Read/Write (RDWR)                | Read Strobe (Active Low)  | Read/Write Strobe               |

| Interrupt (IRQ)                  | Interrupt Pin             | Interrupt Pin                   |

All internal registers (control and status) are 32 bits wide. In order to complete a write operation, all 32 bits must be written. All accesses require writing or reading the complete 32 bits. Hence, when performing a write when the Microprocessor Interface is configured as an 8 bit wide bus, it is required to do 4 writes to write to the internal register. Similarly, when doing a read when the bus is configured as an 8 bit wide bus, 4 reads need to be performed to access the register. The diagrams in Figure 21, Figure 22, Figure 23, and Figure 24 illustrate the bus accesses in Motorola and Intel modes for both read and write operations. The minimum CS to DTACK time is 6 UPCLK cycles and the maximum CS to DTACK time is 22 UPCLK cycles.

#### 2.1.9 JTAG Boundary Scan

The IEEE 1149.1 standard defines the requirements of a boundary scan architecture that has been specified by the IEEE Joint Test Action Group (JTAG). Boundary scan is a specialized scan architecture that provides observability and controllability for the interface leads of the device. As shown in Figure 9, one cell of a boundary scan register is assigned to each input or output lead to be observed or tested (bidirectional leads may have two cells). The boundary scan capability is based on a Test Access Port (TAP) controller, instruction and bypass registers, and a boundary scan register path bordering the input and output leads. The boundary scan test bus interface consists of four input signals and an output signal. The four input signals are Test Clock (TCK), Test Mode Select (TMS), Test Data Input (TDI) and

DATA SHEET TXC-06880

#### - Functional Description -

Test Mode Reset (TRST). The output signal is Test Data Output (TDO). In addition to the TAP, a pin is provided (DEVHIZ) to place the output buffers in a high impedance state for systems that do not support the IEEE 1149.1 standard. Boundary scan signal timing is shown in Figure 20.

The TAP controller receives external control information via a Test Clock (TCK) signal and a Test Mode Select (TMS) signal, and sends control signals to the internal scan paths. Detailed information on the operation of this state machine can be found in the IEEE 1149.1 standard. The serial scan path architecture consists of an instruction register, a boundary scan register and a bypass register. These three serial registers are connected in parallel between the Test Data Input (TDI) and Test Data Output (TDO) signals, as shown in Figure 9.

The boundary scan function can be reset and disabled by holding lead  $\overline{TRST}$  low. When boundary scan testing is not being performed the boundary scan register is transparent, allowing the input and output signals to pass to and from the Envoy-CE2 device's internal logic. During boundary scan testing, the boundary scan register may disable the normal flow of input and output signals to allow the device to be controlled and observed via scan operations.

## 2.1.9.1 Boundary Scan Operation

The Envoy-CE2 supports the following boundary scan test instructions:

The EXTEST test instruction provides the ability to test the connectivity of the Envoy-CE2 device to external circuitry.

The SAMPLE/PRELOAD test instruction provides the ability to examine the values of the Input and Output pins without interfering with device operation, and to initialize the Boundary Scan Register with new values for the next operation.

The BYPASS test instruction provides the ability to bypass the Envoy-CE2 boundary scan and instruction registers.

The IDCODE test instruction provides a unique device identification for the Envoy-CE2 device.

The HIGHZ test instruction provides the ability to drive all 3-state outputs and bidirectional pins to their high impedance state.

The CLAMP test instruction provides the ability to drive the component pins of the chip from the boundary scan register, while the bypass register is selected as the serial path between TDI and TDO. The component pins will not switch while the CLAMP instruction is selected.

#### 2.1.9.2 Boundary Scan Reset

Specific control of the  $\overline{TRST}$  lead is required in order to ensure that the boundary scan logic does not interfere with normal device operation. This lead must either be held low, asserted low, or asserted low then high (pulsed low), to asynchronously reset the Test Access Port (TAP) controller during power-up of the Envoy-CE2. If boundary scan testing is to be performed and the lead is held low, then a pull-down resistor value should be chosen which will allow the tester to drive this lead high, but still meet the  $V_{IL}$  requirements listed in the Input, Output and Input/Output Parameters section of this Data Sheet for worst case leakage currents of all devices sharing this pull-down resistor.

## 2.1.9.3 Boundary Scan Schematic

Figure 9. Boundary Scan Schematic

## 2.1.9.4 Boundary Scan Chain

A Boundary Scan Description Language (BSDL) source file for the Envoy-CE2 is available via the Products page of the TranSwitch Internet World Wide Web site at www.transwitch.com.

# 3.0 TECHNICAL CHARACTERISTICS

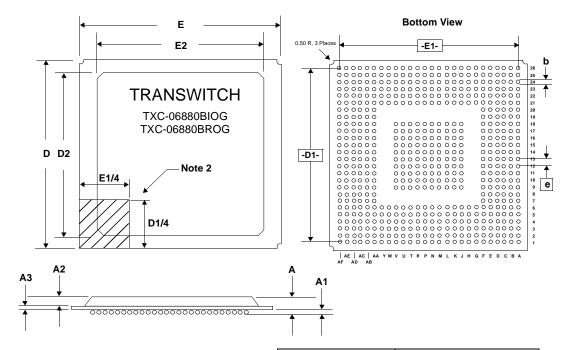

### 3.1 LEAD DIAGRAM

#### **BOTTOM VIEW**

Notes:

- 1. This is the bottom view. The leads are solder balls. See Figure 25 for package information.

- 2. Power supply leads are shown as solid black circles and ground leads are shown as crosshatched circles.

Figure 10. Envoy-CE2 Lead Diagram

#### 3.2 LEAD DESCRIPTIONS

#### POWER SUPPLY, GROUND AND NO CONNECTS

| Symbol | Lead No.                                                                                                                                                                                                                                                          | I/O/P * | Name/Function                                                           |

|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|-------------------------------------------------------------------------|

| VDD18  | AA8, AA9, AA12, AA15,<br>AA18, AA19, AB8, AB9,<br>AB12, AB15, AB18, AB19,<br>E8, E12, E15, E18, E19,<br>F8, F9, E9, F12, F15, F18,<br>F19, H5, H6, H21, H22, J5,<br>J6, J21, J22, M5, M6, M21,<br>M22, R5, R6, R21, R22,<br>V5, V6, V21, V22, W5, W6,<br>W21, W22 | Р       | V <sub>DD18</sub> : +1.8 volt ±5% CMOS core supply voltage.             |

| VDD33  | AA6, AA7, AA10, AA11,<br>AA13, AA14, AA16, AA17,<br>AA20, AA21, AB13, AB14,<br>E13, E14, F6, F7, F10,<br>F11, F13, F14, F16, F17,<br>F20, F21, G21, G6, K6,<br>K21, L6, L21, N5, N6, N21,<br>N22, P5, P6, P21, P22, T6,<br>T21, U6, U21, Y6, Y21                  | Р       | V <sub>DD33</sub> : +3.3 volt ±5% CMOS input/output pad supply voltage. |

Note: VDD18 and VDD33 Power Up Sequence. Because of the multi-power ESD structure used for CMOS I/O cells, there is a parasitic forward diode path from core power rail (V<sub>DD18</sub>) to I/O power rail (V<sub>DD33</sub>). So, if V<sub>DD18</sub> is powered up earlier than V<sub>DD33</sub>, there will be current flowing through the parasitic diode that may trigger latch-up. To avoid this problem, users can take either one of the approaches below:

- (1) Power Up VDD33 First. Turning on V<sub>DD33</sub> first, prevents the parasitic diode from turning on. For example, power up V<sub>DD33</sub> first and then V<sub>DD18</sub>. Note: TranSwitch does not recommend powering up V<sub>DD33</sub> seconds earlier than V<sub>DD18</sub> for reliability reasons. This is because the un-powered V<sub>DD18</sub> may result in short circuit current (crowbar current) on the CMOS I/O cell's post-driver for unknown state. Bus conflict may also occur when only V<sub>DD33</sub> is powered on. The maximum interval that  $V_{DD18}$  must be powered up after  $V_{DD33}$ , depends on the slew rate of power ramp-up in the customer's application.

- (2) Place a Schottky Diode Between VDD18 and VDD33. If we can ensure that the parasitic diode does not turn on, we can even power up lower voltage first. This can be done by inserting an external diode between V<sub>DD18</sub> and V<sub>DD33</sub> on the board. By connecting the Schottky diode with anode to lower voltage rail (V<sub>DD18</sub>) and cathode to higher voltage rail (V<sub>DD33</sub>), we can force the latter to ramp up with the former with the voltage drop (Schottky diode Vt=150mV~200mV) less than the threshold voltage of the parasitic diode (parasitic diode Vt=500mV~600mV). This prevents from turning on the parasitic diode between power rails, avoiding latch up. The external diode will be turned off when V<sub>DD33</sub> is powered up to its normal voltage.

\*Note: I = Input; O = Output; P = Power; T = Tristate

# TXC-06880

### - Technical Characteristics -

| VSS A1, A2, A3, A24, A25, A26, P VSS: Ground 0 (zero) volts reference. AB5, AB22, AC4, AC23, |  |

|----------------------------------------------------------------------------------------------|--|

| AB5 AB22 AC4 AC23                                                                            |  |

| ADJ, ADZZ, ADT, ADZJ,                                                                        |  |

| AD1, AD3, AD24, AD26,                                                                        |  |

| AE1, AE2, AE25, AE26,                                                                        |  |

| AF1, AF2, AF3, AF24,                                                                         |  |

| AF25, AF26, B1, B2, B25,                                                                     |  |

| B26, C1, C3, C24, C26,                                                                       |  |

| D4, D23, D26, E5, E22,                                                                       |  |

| F25, F26, G22, G24, H23,                                                                     |  |

| H26, J9, J10, J11, J12,                                                                      |  |

| J13, J14, J15, J16, J17,                                                                     |  |

| J18, K9, K10, K11, K12,                                                                      |  |

| K13, K14, K15, K16, K17,                                                                     |  |

| K18, K22, K23, K25, K26,                                                                     |  |

| L9, L10, L11, L12, L13,                                                                      |  |

| L14, L15, L16, L17, L18,                                                                     |  |

| L22, L25, L26, M9, M10,                                                                      |  |

| M11, M12, M13, M14, M15,                                                                     |  |

| M16, M17, M18, M25,                                                                          |  |

| M26, N9, N10, N11, N12,                                                                      |  |

| N13, N14, N15, N16, N17,                                                                     |  |

| N18, P9, P10, P11, P12,                                                                      |  |

| P13, P14, P15, P16, P17,                                                                     |  |

| P18, P23, P24, P26, R9,                                                                      |  |

| R10, R11, R12, R13, R14,                                                                     |  |

| R15, R16, R17, R18, R26,<br>T9, T10, T11, T12, T13,                                          |  |

| T14, T15, T16, T17, T18,                                                                     |  |

| T23, T24, U9, U10, U11,                                                                      |  |

| U12, U13, U14, U15, U16,                                                                     |  |

| U17, U18, U24, V9, V10,                                                                      |  |

| V11, V12, V13, V14, V15,                                                                     |  |

| V16, V17, V18, V24, V25,                                                                     |  |

| V26, W25, Y26                                                                                |  |

| Symbol | Lead No.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | I/O/P * | Name/Function                                                                                                                                                                                                                                                                                                                                                                             |

|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NC     | A5, A20, A22, A23, AA25, AC8, AC17, AC22, AD2, AD4, AD10, AD13, AD23, AD25, AE3, AE8, AE19, AE20, AE24, AF8, AF17, B3, B4, B10, B21, B22, B24, C2, C9, C12, C20, C21, C23, C25, D1, D2, D3, D7, D11, D13, D15, D16, D17, D19, D20, D24, E1, E4, E6, E7, E16, E20, E23, E25, E26, F5, F22, F23, F24, G2, G23, G25, G26, H24, H25, J23, J24, J25, J26, K24, L2, L23, L24, M3, M23, M24, N23, N24, N25, N26, P25, R4, R23, R24, R25, T22, T25, T26, U5, U22, U23, U24, U26, V23, W2, W24, W26, Y1, Y25 |         | No Connect: NC leads are not to be connected, not even to another NC lead, but must be left floating. Connection of NC leads may impair performance or cause damage to the device. Some NC leads may be assigned functions in future upgrades of the device. Backwards compatibility of the upgraded device in existing applications may rely upon these leads having been left floating. |

# RESET AND TEST LEADS (INCLUDING TEST ACCESS PORT FOR BOUNDARY SCAN)

| Symbol | Lead No. | I/O  | Туре         | Name/Function                                                                                                                                                                                                                            |

|--------|----------|------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TDO    | D21      | O(T) | CMOS<br>4 mA | <b>Test Data Output:</b> Boundary scan output for data and test instructions from internal test registers.                                                                                                                               |

| TRST   | C22      | I    | LVTTLpu      | Test Mode Reset: A 1 microsecond (minimum) low on this lead resets the boundary scan; recommended for use after power-up initialization as well. This lead should be held low whenever boundary scan operations are not being performed. |

| TMS    | B23      | _    | LVTTLpu      | Test Mode Select: Boundary scan test mode select. This signal must be pulled high. 4.7k $\Omega$ pull-up recommended.                                                                                                                    |

| TDI    | E21      | I    | LVTTLpu      | Test Data Input: Boundary scan input for data and test instructions. 4.7k $\Omega$ pull-up recommended.                                                                                                                                  |

| TCK    | D22      | I    | LVTTLpu      | <b>Test Clock:</b> Boundary scan clock. Input signals are clocked in on its rising edge.                                                                                                                                                 |

# DATA SHEET TXC-06880

- Technical Characteristics -

| Symbol  | Lead No. | I/O | Туре  | Name/Function                                                                                                                                                                                                                                                                                   |

|---------|----------|-----|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RESET   | B16      | I   | LVTLL | Hardware Reset: An active low pulse with minimum width of 1 ms which must be applied after power is applied to reset all registers, counters, and FIFOs. The reset is asynchronous going into the reset state, but requires all external clocks to be active and stable during the reset state. |

| TSTMODE | A17      | I   | LVTTL | <b>Test Mode:</b> For TranSwitch testing purposes only. Tie to V <sub>DD33</sub> . Active low to enable device test.                                                                                                                                                                            |

| SCAN    | C16      | Ι   | LVTTL | <b>SCAN Test:</b> For TranSwitch testing purposes only. Tie to V <sub>SS</sub> . Active high to enable device internal scan test.                                                                                                                                                               |

| TEST1   | B17      | I   | LVTTL | <b>Test1:</b> For TranSwitch testing purposes only. Tie to $V_{SS}$ .                                                                                                                                                                                                                           |

| DEVHIZ  | C17      | I   | LVTTL | <b>Device High Impedance:</b> Active low to set all outputs (except TDO) to high impedance state. Tie to V <sub>DD33</sub> .                                                                                                                                                                    |

# INTEL/MOTOROLA HOST INTERFACE

| Symbol | Lead No. | I/O/P* | Туре          | Name/Function                                                                                                                                                                                                                                                                                                                                                  |

|--------|----------|--------|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| UPCLK  | C15      | I      | LVTTL         | Microprocessor Clock: This clock should come from the microprocessor being interfaced to this device. For Intel and Motorola modes, it is recommended that this lead be connected to the microprocessor bus clock. In Motorola mode, this clock must be synchronous to the microprocessor bus clock. Maximum frequency of 66 MHz, minimum frequency of 33 MHz. |

| CS     | A4       | I      | LVTTL         | <b>Chip Select:</b> Chip select lead from Host. Active low assertion.                                                                                                                                                                                                                                                                                          |

| DTACK  | A16      | 0      | CMOS<br>24 mA | Transfer Acknowledge: Active low signal indicating normal completion of the bus transfer. This output requires an external pull-up resistor.  Note: Device asserts this high before tri-stating to improve acknowledge timing.                                                                                                                                 |

| Symbol                                                                                     | Lead No.                                                                                         | I/O/P* | Туре                    | Name/Function                                                                                                                                                             |

|--------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|--------|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| UPA14 UPA13 UPA12 UPA11 UPA10 UPA9 UPA8 UPA7 UPA6 UPA5 UPA5 UPA4 UPA3 UPA2 UPA1 UPA0       | A15<br>D14<br>C14<br>B14<br>A13<br>B13<br>C13<br>A12<br>B12<br>A11<br>D12<br>B11<br>C11<br>A10   |        | LVTTL                   | Microprocessor Address Bus: 15-bit address bus used by the Host Processor for accessing the Envoy-CE2 for a read/write cycle. UPA14 is the Most Significant Bit (MSB).    |

| UPD15 UPD14 UPD13 UPD12 UPD11 UPD10 UPD9 UPD8 UPD7 UPD6 UPD5 UPD5 UPD4 UPD3 UPD2 UPD1 UPD0 | C10<br>E11<br>A9<br>D10<br>B9<br>A8<br>E10<br>B8<br>D9<br>A7<br>C8<br>B7<br>A6<br>D8<br>C7<br>B6 | I/O    | LVTTL/<br>CMOS<br>16 mA | Microprocessor Data Bus: Bi-directional 16-bit data bus used for transferring data between the Envoy-CE2 and the Host Processor. UPD15 is the Most Significant Bit (MSB). |

| WRDS                                                                                       | B5                                                                                               | I      | LVTTL                   | Write/Transfer Start: In Intel Mode, this pin is used for the Write signal and in Motorola mode, this pin is used for the active low Transfer start signal.               |

| RDWR                                                                                       | C6                                                                                               | I      | LVTTL                   | Read/Write: In Intel Mode, this pin is used for the Read signal and in Motorola mode, this pin controls type of data transfer (Write = 0/Read = 1).                       |

| ĪRQ                                                                                        | B15                                                                                              | O(T)   | CMOS<br>16mA            | Interrupt: Active low level-based interrupt to Host processor.                                                                                                            |

DATA SHEET

TXC-06880

- Technical Characteristics -

# COMMON SMII INTERFACES PINS FOR ALL SMII PORTS (Ports 0 to 15) including extended SMII ports

| Symbol   | Lead No. | I/O/P* | Туре  | Name/Function                                                                                                                       |

|----------|----------|--------|-------|-------------------------------------------------------------------------------------------------------------------------------------|

| SSYNCIN  | D25      | -      | LVTTL | Synchronization Input Pulse: Global input signal that occurs every 10 SMIIREFCLK clock cycles and marks the start of data segments. |

| SSYNCDIR | E24      | 1      | LVTTL | <b>Synchronization Pulse Direction:</b> Determines the source of the synchronization pulse.                                         |

|          |          |        |       | 0 - The synchronization pulse will be taken from an internally generated source                                                     |

|          |          |        |       | 1 - The synchronization pulse to the 8 SMII ports will be taken from SSYNCIN                                                        |

# SMII INTERFACE PINS FOR Configurable MAC A (Ports 0 to 7). Extended SMII Ports are Ports 0 and 4

| Symbol      | Lead No. | I/O/P* | Туре         | Name/Function                                                                                                                                                                       |

|-------------|----------|--------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SMIIREFCLKA | F1       | I      | LVTTL        | SMII Reference Clock for Configurable MAC A: 125 MHz Clock. Must be active to support the Ethernet statistics registers of CMAC A - even when the CMAC is configured for GMII Mode. |

| SSYNCOUTA   | H4       | 0      | CMOS<br>12mA | Synchronization Output Pulse for Configurable MAC A: Global output signal that occurs every 10 SMIIREFCLKA clock cycles and marks the start of data segments.                       |

| TX0A        | НЗ       | 0      | CMOS<br>12mA | Transmit Data Port 0: SMII port 0 data out signal.                                                                                                                                  |

| RX0A        | G1       | I      | LVTTL        | Receive Data Port 0: SMII port 0 data in signal.                                                                                                                                    |

| TX1A        | J4       | 0      | CMOS<br>12mA | Transmit Data Port 1: SMII port 1 data out signal.                                                                                                                                  |

| RX1A        | H2       | I      | LVTTL        | Receive Data Port 1: SMII port 1 data in signal.                                                                                                                                    |

| TX2A        | K5       | 0      | CMOS<br>12mA | Transmit Data Port 2: SMII port 2 data out signal.                                                                                                                                  |

| RX2A        | J3       | I      | LVTTL        | Receive Data Port 2: SMII port 2 data in signal.                                                                                                                                    |

| TX3A        | H1       | 0      | CMOS<br>12mA | Transmit Data Port 3: SMII port 3 data out signal.                                                                                                                                  |

| RX3A        | J2       | I      | LVTTL        | Receive Data Port 3: SMII port 3 data in signal.                                                                                                                                    |

| TX4A        | K4       | 0      | CMOS<br>12mA | Transmit Data Port 4: SMII port 4 data out signal.                                                                                                                                  |

| RX4A        | J1       | I      | LVTTL        | Receive Data Port 4: SMII port 4 data in signal.                                                                                                                                    |

#### **Symbol** Lead No. I/O/P\* **Type** Name/Function TX5A L5 **CMOS** Transmit Data Port 5: SMII port 5 data out signal. 0 12mA RX5A **K**3 **LVTTL** Receive Data Port 5: SMII port 5 data in signal. Ι TX6A K2 0 **CMOS** Transmit Data Port 6: SMII port 6 data out signal 12mA LVTTL RX6A L4 I Receive Data Port 6: SMII port 6 data in signal. TX7A K1 0 **CMOS** Transmit Data Port 7: SMII port 7 data out signal. 12mA RX7A L3 **LVTTL** Receive Data Port 7: SMII port 7 data in signal. 1

- Technical Characteristics -

# SMII INTERFACE PINS FOR Configurable MAC B (Ports 8 to 15). Extended SMII Ports are Ports 8 and 12

| Symbol      | Lead No. | I/O/P* | Туре         | Name/Function                                                                                                                                                                       |

|-------------|----------|--------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SMIIREFCLKB | P4       | _      | LVTTL        | SMII Reference Clock for Configurable MAC B: 125 MHz Clock. Must be active to support the Ethernet statistics registers of CMAC B - even when the CMAC is configured for GMII Mode. |

| SSYNCOUTB   | P3       | 0      | CMOS<br>12mA | Synchronization Output Pulse for Configurable MAC B: Global output signal that occurs every 10 SMIIREFCLKB clock cycles and marks the start of data segments.                       |

| TX0B        | R1       | 0      | CMOS<br>12mA | Transmit Data Port 8: SMII port 8 data out signal.                                                                                                                                  |

| RX0B        | R2       | I      | LVTTL        | Receive Data Port 8: SMII port 8 data in signal.                                                                                                                                    |

| TX1B        | R3       | 0      | CMOS<br>12mA | Transmit Data Port 9: SMII port 9 data out signal.                                                                                                                                  |

| RX1B        | T1       | I      | LVTTL        | Receive Data Port 9: SMII port 9 data in signal.                                                                                                                                    |

| TX2B        | T2       | 0      | CMOS<br>12mA | Transmit Data Port 10: SMII port 10 data out signal.                                                                                                                                |

| RX2B        | T3       | I      | LVTTL        | Receive Data Port 10: SMII port 10 data in signal.                                                                                                                                  |

| TX3B        | U1       | 0      | CMOS<br>12mA | Transmit Data Port 11: SMII port 11 data out signal.                                                                                                                                |

| RX3B        | T4       | I      | LVTTL        | Receive Data Port 11: SMII port 11 data in signal.                                                                                                                                  |

| TX4B        | U2       | 0      | CMOS<br>12mA | Transmit Data Port 12: SMII port 12 data out signal.                                                                                                                                |

| RX4B        | U3       | 1      | LVTTL        | Receive Data Port 12: SMII port 12 data in signal.                                                                                                                                  |

| Symbol | Lead No. | I/O/P* | Туре         | Name/Function                                        |

|--------|----------|--------|--------------|------------------------------------------------------|

| TX5B   | T5       | 0      | CMOS<br>12mA | Transmit Data Port 13: SMII port 13 data out signal. |

| RX5B   | V1       | I      | LVTTL        | Receive Data Port 13: SMII port 13 data in signal.   |

| TX6B   | U4       | 0      | CMOS<br>12mA | Transmit Data Port 14: SMII port 14 data out signal. |

| RX6B   | V2       | I      | LVTTL        | Receive Data Port 14: SMII port 14 data in signal.   |

| TX7B   | W1       | 0      | CMOS<br>12mA | Transmit Data Port 15: SMII port 15 data out signal. |

| RX7B   | V3       | I      | LVTTL        | Receive Data Port 15: SMII port 15 data in signal.   |

# GMII/MII INTERFACE PINS FOR GMII Port 0 (Configurable MAC A) (SMIIREFCLKA must be active)

| Symbol      | Lead No. | I/O/P* | Туре         | Name/Function                                                                                                                                                                       |

|-------------|----------|--------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SMIIREFCLKA | F1       | I      | LVTTL        | SMII Reference Clock for Configurable MAC A: 125 MHz Clock. Must be active to support the Ethernet statistics registers of CMAC A - even when the CMAC is configured for GMII Mode. |