# INTEL & LXT386 QUAD T1/E1/J1 Transceiver

# Datasheet

The LXT386 is a quad short haul Pulse Code Modulation (PCM) transceiver for use in both 1.544 Mbps (T1) and 2.048 Mbps (E1) applications. It incorporates four independent receivers and four independent transmitters in a single PBGA-160 or LQFP-100 package.

The transmit drivers provide low impedance independent of the transmit pattern and supply voltage variations. The LXT386 transmits shaped waveforms meeting G.703 and T1.102 specifications. The LXT386 exceeds the latest transmit return loss specifications, such as ETSI ETS-300166.

The LXT386's differential receiver architecture provides high noise interference margin and is able to work with up to 12 dB of cable attenuation. The digital clock recovery PLL and jitter attenuator are referenced to a low frequency 1.544 MHz or 2.048 MHz clock.

The LXT386 incorporates an advanced crystal-less jitter attenuator switchable between the receive and transmit path. The jitter attenuation performance meets the latest international specifications such as CTR12/13. The jitter attenuation performance was optimized for Synchronous Optical NETwork/Synchronous Digital Hierarchy (SONET/SDH) applications.

The LXT386 can be configured as a 3 channel transceiver with G.772 compliant non intrusive protected monitoring points. It uses a single 3.3V supply for low power consumption.

The constant delay characteristic of the LXT386 JA as well as a power down mode of all transmitters allows the implementation of Hitless Protection Switching (HPS) applications without the use of relays.

# **Applications**

- SONET/SDH tributary interfaces

- Digital cross connects

- Public/private switching trunk line interfaces

- Microwave transmission systems

- M13, E1-E3 MUX

# intel

Information in this document is provided in connection with Intel<sup>®</sup> products. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Intel's Terms and Conditions of Sale for such products, Intel assumes no liability whatsoever, and Intel disclaims any express or implied warranty, relating to sale and/or use of Intel products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. Intel products are not intended for use in medical, life saving, or life sustaining applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

The LXT386 may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an ordering number and are referenced in this document, or other Intel literature may be obtained by calling 1-800-548-4725 or by visiting Intel's website at http://www.intel.com.

Copyright © Intel Corporation, 2005

\*Third-party brands and names are the property of their respective owners.

# int<sub>el</sub>。 Contents

| 1.0 | Feat  | Jres7                                         |

|-----|-------|-----------------------------------------------|

| 2.0 | Pin A | ssignments and Signal Description9            |

| 3.0 | Func  | tional Description22                          |

|     | 3.1   | Initialization22                              |

|     |       | 3.1.1 Reset Operation                         |

|     | 3.2   | Receiver24                                    |

|     |       | 3.2.1 Loss of Signal Detector25               |

|     |       | 3.2.1.1 E1 Mode25                             |

|     |       | 3.2.1.2 T1 Mode                               |

|     |       | 3.2.1.3 Data Recovery Mode                    |

|     |       | 3.2.2 Alarm Indication Signal (AIS) Detection |

|     |       | 3.2.2.1 E1 Mode                               |

|     |       | 3.2.2 T1 Mode                                 |

|     | 3.3   | Transmitter                                   |

|     | 3.5   | 3.3.1 Transmit Pulse Shaping                  |

|     |       | 3.3.1.1 Hardware Mode                         |

|     |       | 3.3.1.2 Host Mode                             |

|     |       | 3.3.2 Transmit Pulse Shaping                  |

|     |       | 3.3.2.1 Output Driver Power Supply            |

|     |       | 3.3.2.2 Power Sequencing                      |

|     | 3.4   | Driver Failure Monitor                        |

|     | 3.5   | Line Protection                               |

|     | 3.6   | Jitter Attenuation                            |

|     | 3.7   | Loopbacks                                     |

|     |       | 3.7.1 Analog Loopback                         |

|     |       | 3.7.2 Digital Loopback                        |

|     |       | 3.7.3 Remote Loopback                         |

|     |       | 3.7.4 Transmit All Ones (TAOS)                |

|     | 3.8   | G.772 Performance Monitoring                  |

|     | 3.9   | Hitless Protection Switching (HPS)            |

|     | 3.10  | Operation Mode Summary                        |

|     | 3.11  | Interfacing with 5V logic                     |

|     | 3.12  | Parallel Host Interface                       |

|     |       | 3.12.1 Motorola Interface                     |

|     |       | 3.12.2 Intel Interface40                      |

|     | 3.13  | Interrupt Handling41                          |

|     |       | 3.13.1 Interrupt Enable                       |

|     |       | 3.13.2 Interrupt Clear                        |

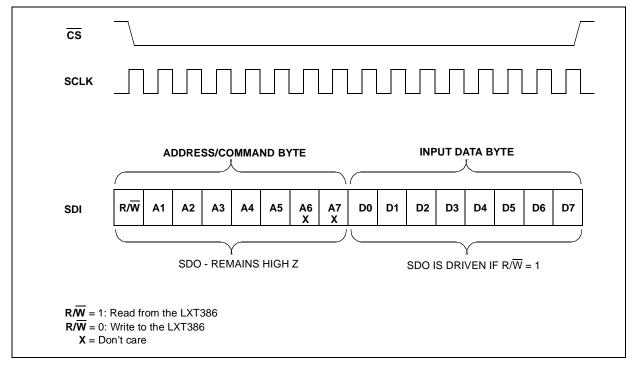

|     | 3.14  | Serial Host Mode42                            |

| 4.0 | Regi  | ster Descriptions                             |

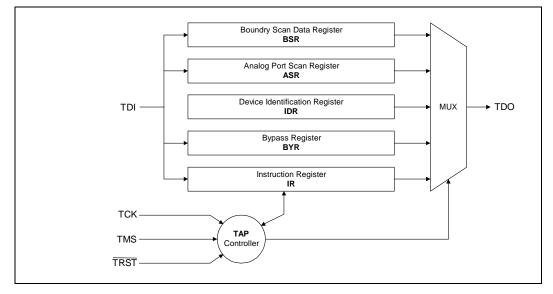

| 5.0 | JTAC  | Boundary Scan                                 |

|     | 5.1   | Overview                                      |

|     | 5.2   | Architecture                                  |

# intel®

|     | 5.3  | TAP Controller                        | 51 |

|-----|------|---------------------------------------|----|

|     | 5.4  | JTAG Register Description             | 53 |

|     |      | 5.4.1 Boundary Scan Register (BSR)    | 53 |

|     | 5.5  | Device Identification Register (IDR)  | 56 |

|     |      | 5.5.1 Bypass Register (BYR)           | 56 |

|     |      | 5.5.2 Analog Port Scan Register (ASR) | 57 |

|     |      | 5.5.3 Instruction Register (IR)       | 58 |

| 6.0 | Test | Specifications                        | 59 |

|     | 6.1  | Recommendations and Specifications    | 81 |

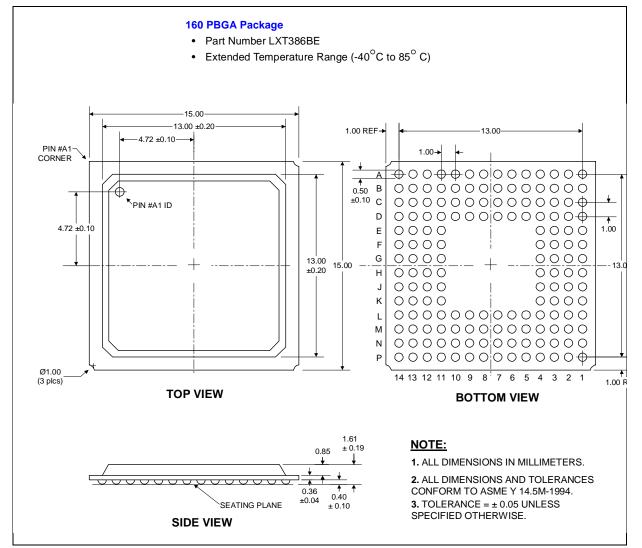

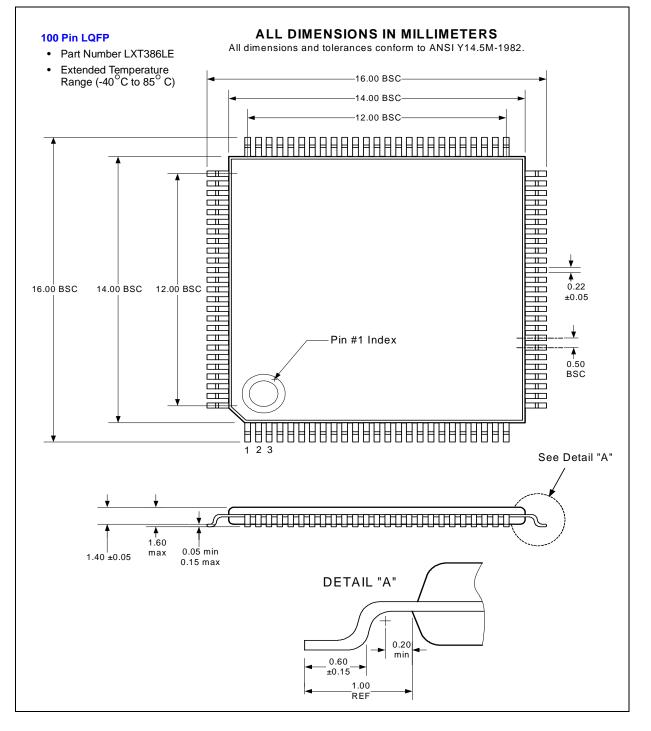

| 7.0 | Mec  | hanical Specifications                | 82 |

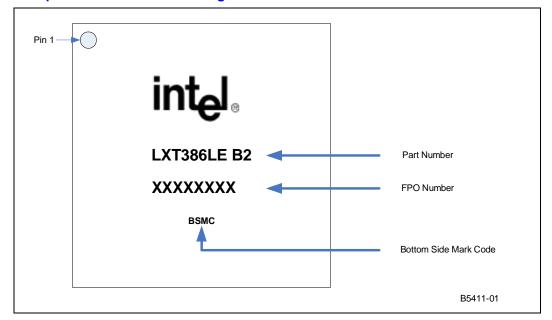

|     | 7.1  | Top Label Markings                    |    |

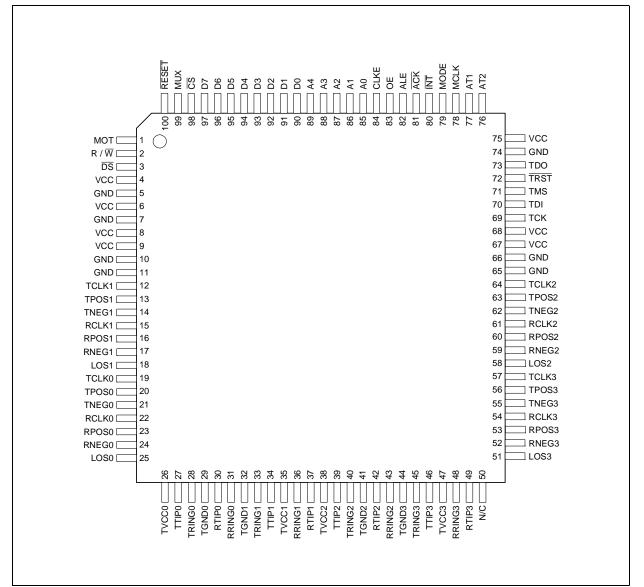

| 8.0 | Proc | duct Ordering Information             | 85 |

| 9.0 | Pack | kage Information                      |    |

|     |      |                                       |    |

# **Figures**

| 1  | LXT386 Block Diagram                                            | 7  |

|----|-----------------------------------------------------------------|----|

| 2  | LXT386 Detailed Block Diagram                                   | 8  |

| 3  | LXT386 Low-Profile Quad Flat Package (LQFP) 100 Pin Assignments |    |

| 4  | LXT386 Plastic Ball Grid Array (PBGA) 160 Ball Assignments      | 10 |

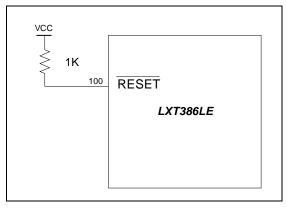

| 5  | Pullup Resistor to RESET                                        | 23 |

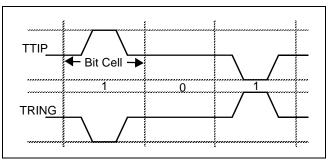

| 6  | 50% AMI Encoding                                                | 27 |

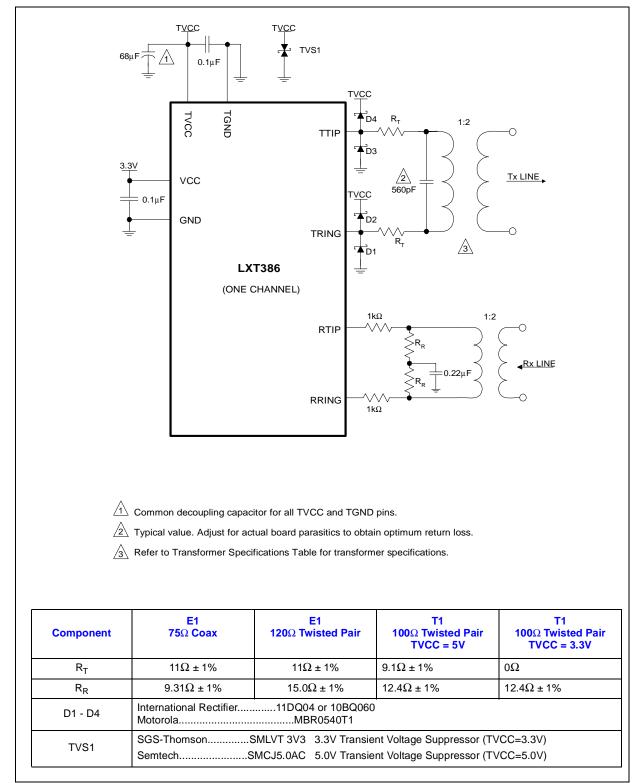

| 7  | External Transmit/Receive Line Circuitry                        | 31 |

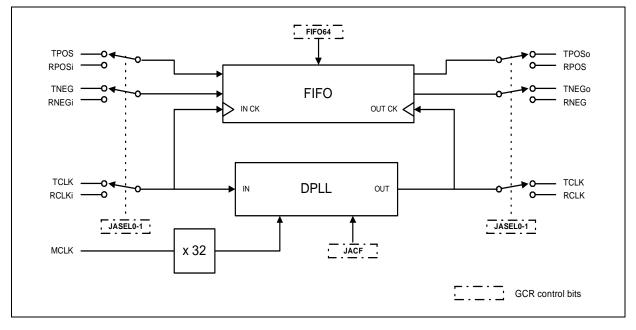

| 8  | Jitter Attenuator Loop                                          | 33 |

| 9  | Analog Loopback                                                 | 34 |

| 10 | Digital Loopback                                                | 34 |

| 11 | Remote Loopback                                                 | 35 |

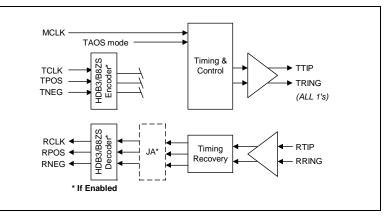

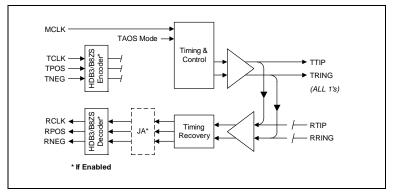

| 12 | TAOS Data Path                                                  | 36 |

| 13 | TAOS with Analog Loopback                                       | 36 |

| 14 | Serial Host Mode Timing                                         | 42 |

| 15 | LXT386 JTAG Architecture                                        | 50 |

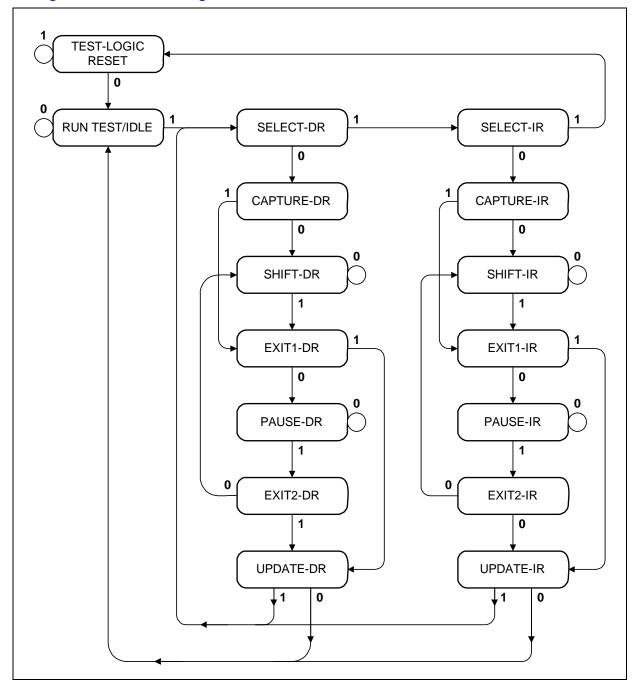

| 16 | JTAG State Diagram                                              | 52 |

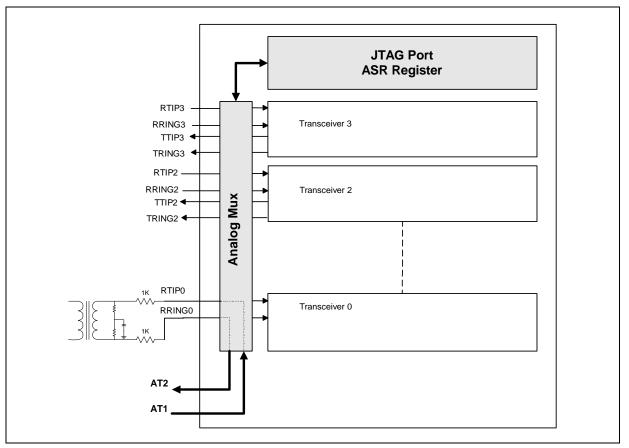

| 17 | Analog Test Port Application                                    | 58 |

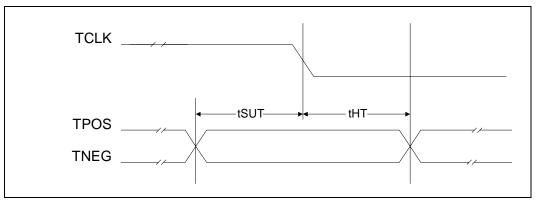

| 18 | Transmit Clock Timing Diagram                                   | 65 |

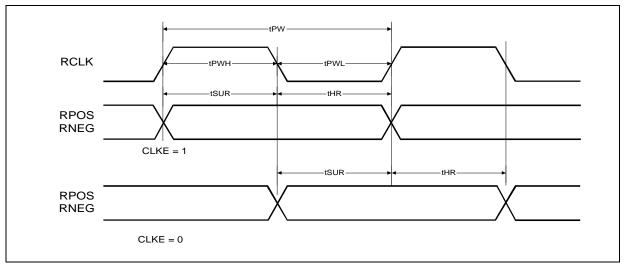

| 19 | Receive Clock Timing Diagram                                    | 66 |

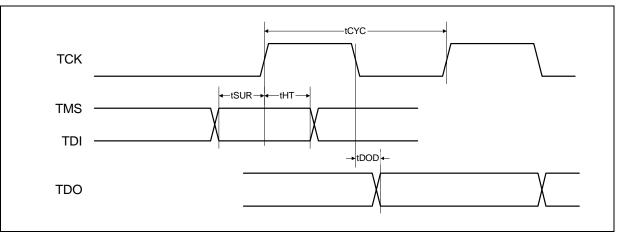

| 20 | JTAG Timing                                                     | 67 |

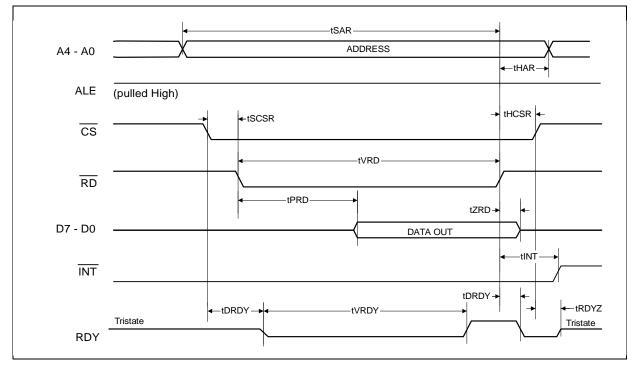

| 21 | Non-Multiplexed Intel Mode Read Timing                          | 68 |

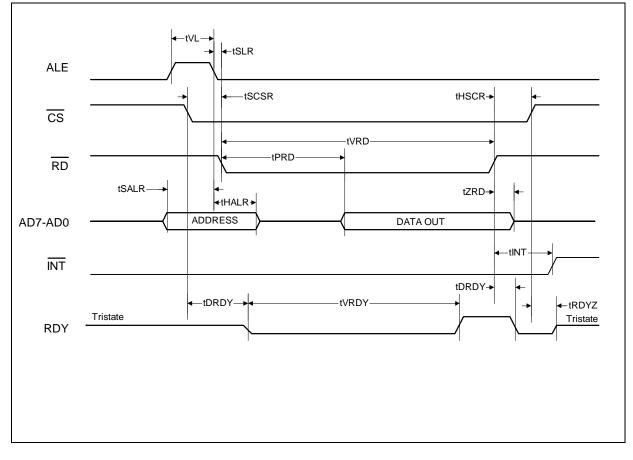

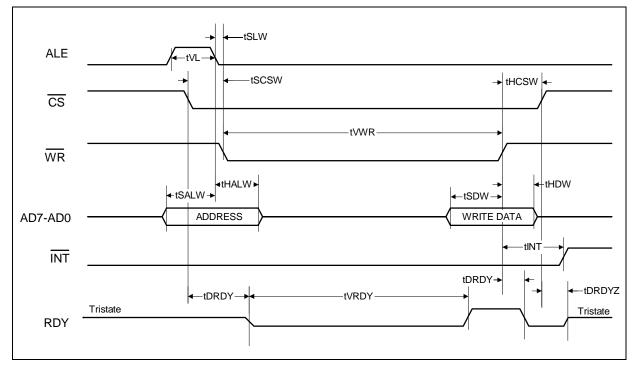

| 22 | Multiplexed Intel Read Timing                                   |    |

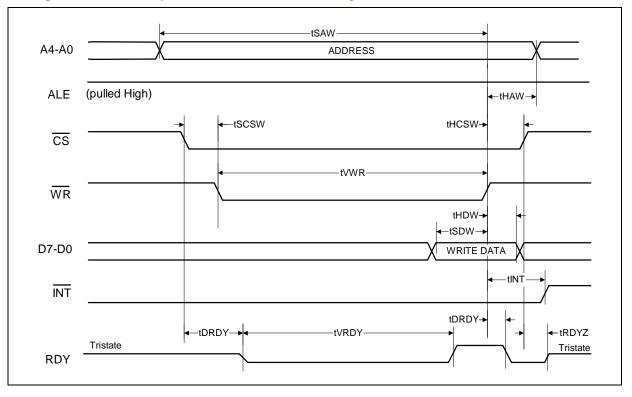

| 23 | Non-Multiplexed Intel Mode Write Timing                         | 70 |

| 24 | Multiplexed Intel Mode Write Timing                             | 71 |

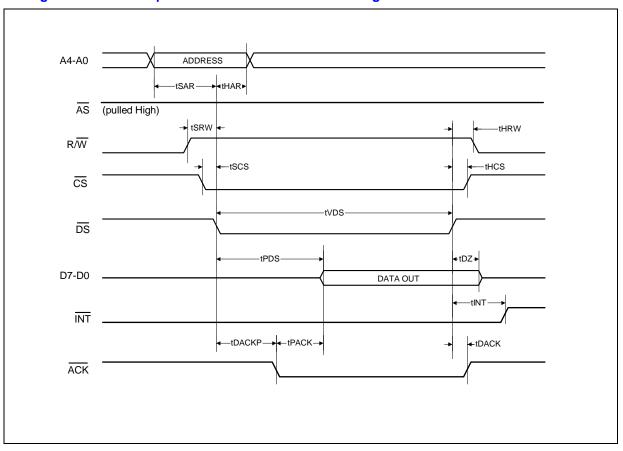

| 25 | Non-Multiplexed Motorola Mode Read Timing                       | 72 |

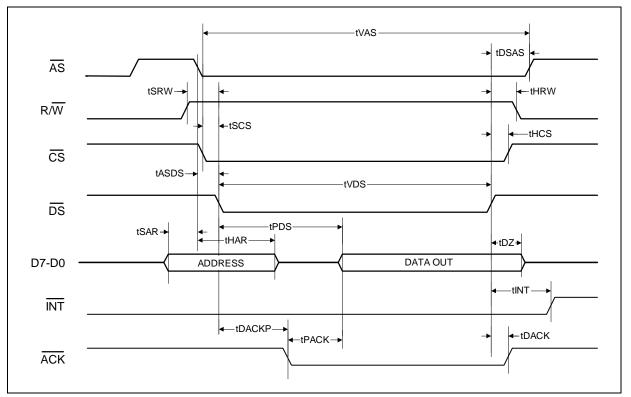

| 26 | Multiplexed Motorola Mode Read Timing                           | 73 |

| 27 | Non-Multiplexed Motorola Mode Write Timing                      | 74 |

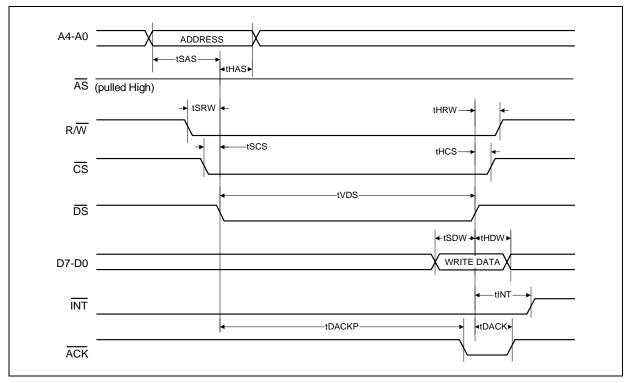

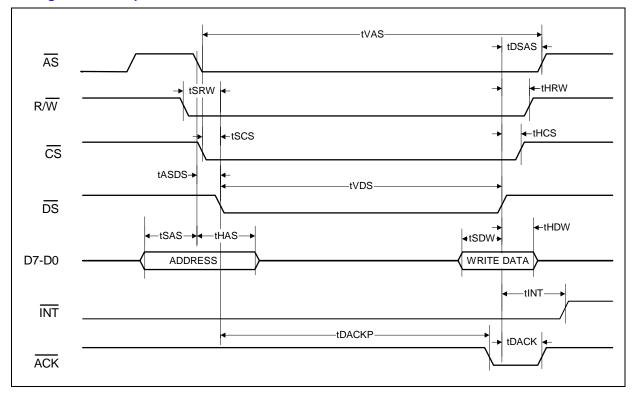

| 28 | Multiplexed Motorola Mode Write Timin                           | 75 |

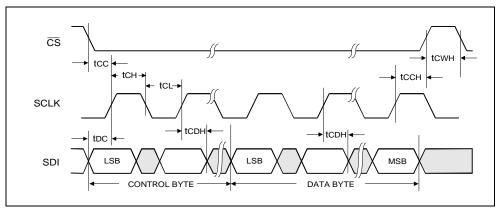

| 29 | Serial Input Timing                                             | 76 |

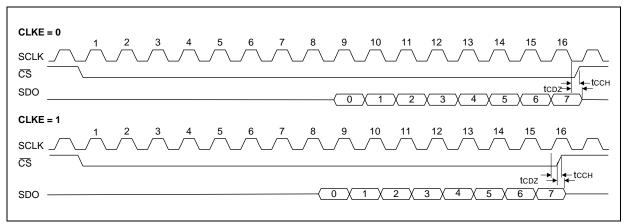

| 30 | Serial Output Timing                                            | 76 |

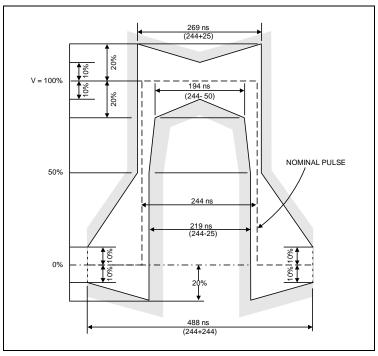

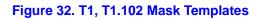

| 31 | E1, G.703 Mask Templates                                         | 77 |

|----|------------------------------------------------------------------|----|

| 32 | T1, T1.102 Mask Templates                                        |    |

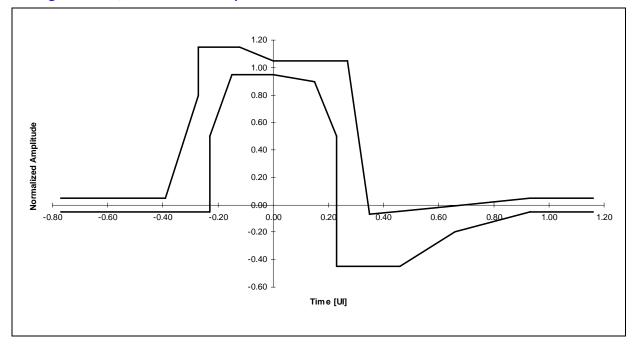

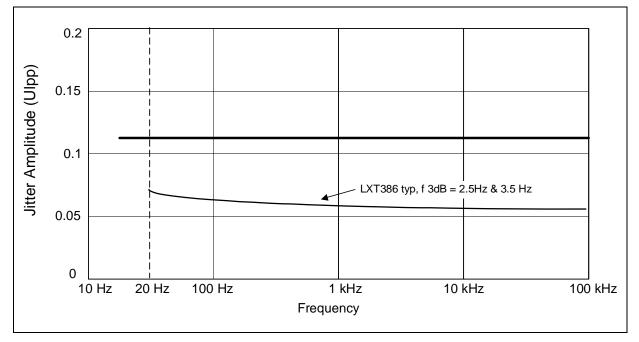

| 33 | LXT386 Jitter Tolerance Performance                              | 79 |

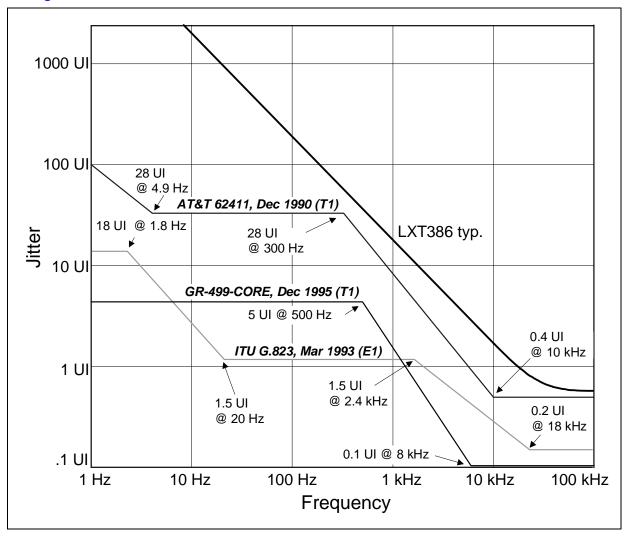

| 34 | Jitter Transfer Performance                                      | 80 |

| 35 | Output Jitter for CTR12/13 applications                          | 81 |

| 36 | 60 Plastic Ball Grid Array (PBGA) Package Dimensions             |    |

| 37 | 100 Pin Low Quad Flat Packages (LQFP) Dimensions                 |    |

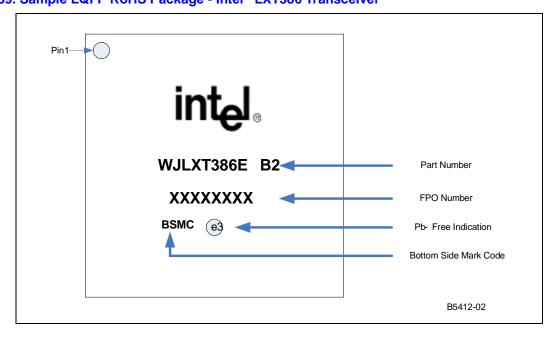

| 38 | Sample LQFP Non-RoHS Package - Intel® LXT386 Transceiver         |    |

| 39 | Sample LQFP RoHS Package - Intel <sup>®</sup> LXT386 Transceiver |    |

| 40 | Order Matrix                                                     |    |

|    |                                                                  |    |

# **Tables**

| 1  | Pin Assignments and Signal Descriptions              |    |

|----|------------------------------------------------------|----|

| 2  | Line Length Equalizer Inputs                         |    |

| 3  | Jitter Attenuation Specifications                    |    |

| 4  | Operation Mode Summary                               |    |

| 5  | Microprocessor Parallel Interface Selection          |    |

| 6  | Serial and Parallel Port Register Addresses          |    |

| 7  | Register Bit Names                                   |    |

| 8  | ID Register, ID (00H)                                |    |

| 9  | Analog Loopback Register, ALOOP (01H)                |    |

| 10 | Remote Loopback Register, RLOOP (02H)                |    |

| 11 | TAOS Enable Register, TAOS (03H)                     |    |

| 12 | LOS Status Monitor Register, LOS (04H)               | 45 |

| 13 | DFM Status Monitor Register, DFM (05H)               | 45 |

| 14 | LOS Interrupt Enable Register, LIE (06H)             | 45 |

| 15 | DFM Interrupt Enable Register, DIE (07H)             | 45 |

| 16 | LOS Interrupt Status Register, LIS (08H)             | 46 |

| 17 | DFM Interrupt Status Register, DIS (09H)             | 46 |

| 18 | Software Reset Register, RES (0AH)                   | 46 |

| 19 | Performance Monitoring Register, MON (0BH)           | 46 |

| 20 | Digital Loopback Register, DL (0CH)                  | 46 |

| 21 | LOS/AIS Criteria Register, LCS (0DH)                 | 46 |

| 22 | Automatic TAOS Select Register, ATS (0EH)            |    |

| 23 | Global Control Register, GCR (0FH)                   |    |

| 24 | Pulse Shaping Indirect Address Register, PSIAD (10H) |    |

| 25 | Pulse Shaping Data Register, PSDAT (11H)             |    |

| 26 | Output Enable Register, OER (12H)                    |    |

| 27 | AIS Status Monitor Register, AIS (13H)               |    |

| 28 | AIS Interrupt Enable Register, AISIE (14H)           |    |

| 29 | AIS Interrupt Status Register, AISIS (15H)           |    |

| 30 | TAP State Description                                |    |

| 31 | Device Identification Register (IDR)                 |    |

| 32 | Analog Port Scan Register – ASR                      |    |

| 33 | Instruction Register – IR                            |    |

| 34 | Absolute Maximum Ratings                             |    |

| 35 | Recommended Operating Conditions                     |    |

| 36 | DC Characteristics                                   |    |

| 37 | E1 Transmit Transmission Characteristics             |    |

|    |                                                      |    |

| 38 | E1 Receive Transmission Characteristics       | 61 |

|----|-----------------------------------------------|----|

| 39 | T1 Transmit Transmission Characteristics      | 62 |

| 40 | T1 Receive Transmission Characteristics       | 63 |

| 41 | Jitter Attenuator Characteristics             | 64 |

| 42 | Analog Test Port Characteristics              | 65 |

| 43 | Transmit Timing Characteristics               | 65 |

| 44 | Receive Timing Characteristics                | 66 |

| 45 | JTAG Timing Characteristics                   | 67 |

| 46 | Intel Mode Read Timing Characteristics        | 67 |

| 47 | Intel Mode Write Timing Characteristics       |    |

| 48 | Motorola Bus Read Timing Characteristics      | 71 |

| 49 | Motorola Mode Write Timing Characteristics    | 73 |

| 50 | Serial I/O Timing Characteristics             | 75 |

| 51 | Transformer Specifications3                   | 76 |

| 52 | G.703 2.048 Mbit/s Pulse Mask Specifications  |    |

| 53 | T1.102 1.544 Mbit/s Pulse Mask Specifications | 77 |

| 54 | Product Ordering Information                  | 85 |

# **Revision History**

| Date     | Revision | Description                                                                                                            |

|----------|----------|------------------------------------------------------------------------------------------------------------------------|

| Nov 2005 | 002      | Added Reduction of Hazardous Substances package information, starting at Section 7.1, "Top Label Markings" on page 84. |

| Nov 2000 | 001      | Initial release                                                                                                        |

# intel®

# **1.0 Features**

- Single rail 3.3V supply with 5V tolerant inputs

- Low power consumption of 150mW per channel (typical)

- Superior crystal-less jitter attenuator

- Meets ETSI CTR12/13, ITU G.736, G.742, G.823 and AT&T Pub 62411 specifications

- Optimized for SONET/SDH applications, meets ITU G.783 mapping jitter specification

- Constant throughput delay jitter attenuator

- Hitless Protection Switching (HPS) for 1 to 1 protection without relays

- HDB3, B8ZS, or AMI line encoder/decoder

- Provides protected monitoring points per ITU G.772

- Analog/digital and remote loopback testing functions

- LOS per ITU G.775, ETS 300 233 and T1.231

- 8 bit parallel or 4 wire serial control interface

- Hardware and Software control modes

- JTAG Boundary Scan test port per IEEE 1149.1

- 160 PBGA and 100 pin LQFP packages

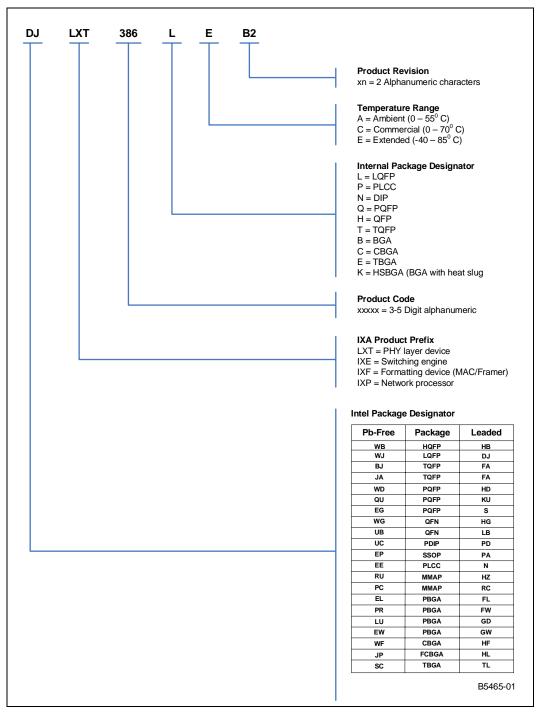

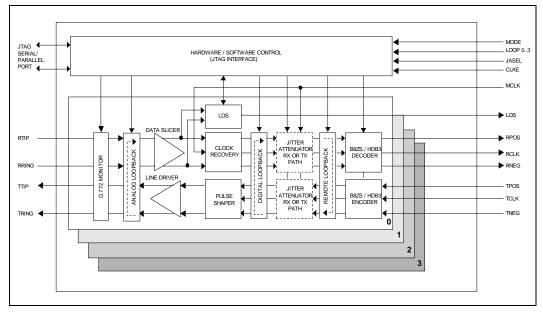

#### Figure 1. LXT386 Block Diagram

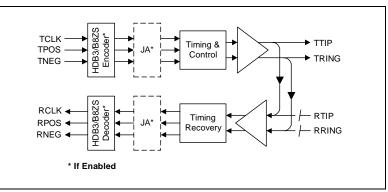

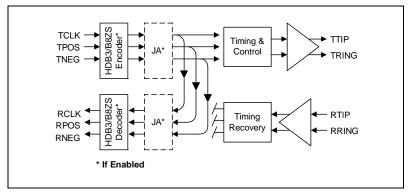

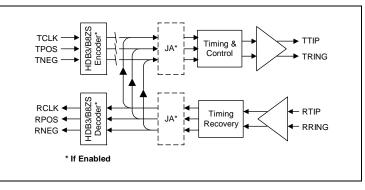

Figure 2. LXT386 Detailed Block Diagram

int

# 2.0 Pin Assignments and Signal Description

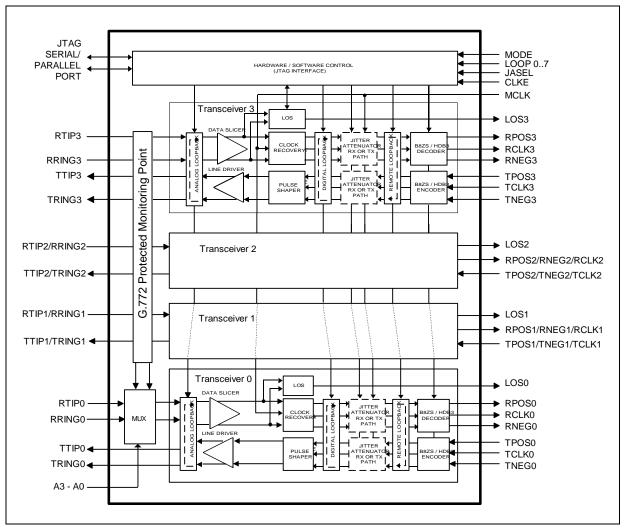

Figure 3 shows the pin assignments for LQFP packages. For current package markings, see Section 7.1, "Top Label Markings" on page 84 and the sections that follow.

Datasheet

intel

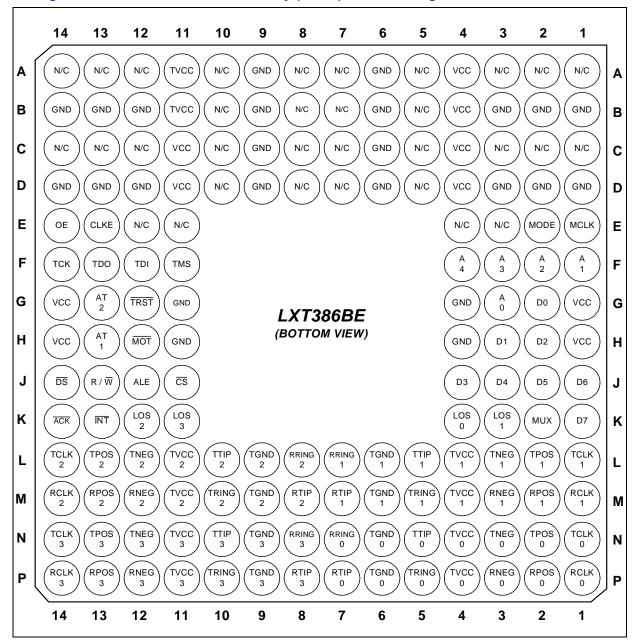

Figure 4. LXT386 Plastic Ball Grid Array (PBGA) 160 Ball Assignments

# intel

|               | LQFP                       | Symbol            | I/O <sup>1</sup> | Description                                                                                                                                                                                                              |  |  |  |

|---------------|----------------------------|-------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|               |                            |                   |                  | Master Clock. MCLK is an independent, free-running reference clock. It's frequency should be 1.544 MHz for T1 operation and 2.048 MHz for E1 operation.                                                                  |  |  |  |

|               |                            |                   |                  | This reference clock is used to generate several internal reference signals:                                                                                                                                             |  |  |  |

|               |                            |                   |                  | Timing reference for the integrated clock recovery unit                                                                                                                                                                  |  |  |  |

|               |                            |                   |                  | Timing reference for the integrated digital jitter attenuator                                                                                                                                                            |  |  |  |

|               |                            |                   |                  | Generation of RCLK signal during a loss of signal condition                                                                                                                                                              |  |  |  |

| E1            | 78                         | MCLK              | DI               | Reference clock during a blue alarm transmit all ones condition                                                                                                                                                          |  |  |  |

| <b>L</b> 1    | 10                         | WIGER             |                  | Reference timing for the parallel processor wait state generation logi                                                                                                                                                   |  |  |  |

|               |                            |                   |                  | If MCLK is High, the PLL clock recovery circuit is disabled. In this mode, the LXT386 operates as simple data receiver.                                                                                                  |  |  |  |

|               | 79                         |                   |                  | If MCLK is Low, the complete receive path is powered down and the output pins RCLK, RPOS and RNEG are switched to Tri-state mode.                                                                                        |  |  |  |

|               |                            |                   |                  | MCLK is not required if LXT386 is used as a simple analog front-end without clock recovery and itter attenuation.                                                                                                        |  |  |  |

|               |                            |                   |                  | Note that wait state generation via RDY/ACK is not available if MCLK is not provided.                                                                                                                                    |  |  |  |

|               |                            |                   | DI               | <b>Mode Select</b> . This pin is used to select the operating mode of the LXT386. In Hardware Mode, the parallel processor interface is disabled and hardwired pins are used to control configuration and report status. |  |  |  |

|               |                            |                   |                  | In Parallel Host Mode, the parallel port interface pins are used to control configuration and report status.                                                                                                             |  |  |  |

|               |                            |                   |                  | In Serial Host Mode the serial interface pins: SDI, SDO, SCLK and $\overline{\text{CS}}$ are used.                                                                                                                       |  |  |  |

| E2            |                            | MODE              |                  | MODE Operating Mode                                                                                                                                                                                                      |  |  |  |

|               |                            |                   |                  | L Hardware Mode                                                                                                                                                                                                          |  |  |  |

|               |                            |                   |                  | H Parallel Host Mode                                                                                                                                                                                                     |  |  |  |

|               |                            |                   |                  | Vcc/2 Serial Host Mode                                                                                                                                                                                                   |  |  |  |

|               |                            |                   |                  |                                                                                                                                                                                                                          |  |  |  |

|               |                            |                   |                  | For Serial Host Mode, the pin should connected to a resistive divider consisting of two 10 k $\Omega$ resistors across Vcc and Ground.                                                                                   |  |  |  |

| F4            | 89                         | A4                | DI               | Address Select. In host mode, this pin is Address 4 input pin. In hardward mode this pin must be connected to Ground.                                                                                                    |  |  |  |

| . DI: Digital | Input: DO: Di              | gital Output: DI/ | 0: Digital       | Bidirectional Port; AI: Analog Input; AO: Analog Output S: Power Supply;                                                                                                                                                 |  |  |  |

| N.C.: Not (   | Connected.<br>s "Not Conne |                   |                  | ······································                                                                                                                                                                                   |  |  |  |

## Table 1. Pin Assignments and Signal Descriptions (Sheet 1 of 11)

## Table 1. Pin Assignments and Signal Descriptions (Sheet 2 of 11)

| Ball #<br>PBGA | Pin #<br>LQFP                                 | Symbol | I/O <sup>1</sup> |                                                                                                            |                                                                                                                               |                                                                                                                       | Descript                                                                                                 | ion                                                                                                                                                                                                                                                                                                               |

|----------------|-----------------------------------------------|--------|------------------|------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                |                                               |        |                  | intrusive m<br>internally c<br>routes the e<br>circuits. Th<br>activating t<br>order for th<br>data can be | Mode<br>e mode th<br>onitoring.<br>onnected<br>data from<br>e data on<br>he remote<br>is operatio<br>e observer<br>e Low, the | ese pins a<br>During pri<br>to a speci<br>the select<br>the moniti<br>loopback<br>on to take<br>d at the Ri<br>LXT386 | are used t<br>otection m<br>fic transm<br>ed port to<br>or port ca<br>for chann<br>place). In<br>CLK0/RP | Inputs.<br>o select a specific port for non<br>nonitoring receiver 0 inputs are<br>it or receive port. Receiver 0<br>its data and clock recovery<br>n be routed to TTIP0/TRING0 by<br>nel 0 (TCLK0 must be active in<br>addition, the recovered clock and<br>OS0/RNEG0 outputs.<br>red as a quad line transceiver |

|                |                                               |        |                  | A3                                                                                                         | A2                                                                                                                            | A1                                                                                                                    | AO                                                                                                       | Selection                                                                                                                                                                                                                                                                                                         |

|                |                                               |        |                  | 0                                                                                                          | 0                                                                                                                             | 0                                                                                                                     | 0                                                                                                        | No Protection Monitoring                                                                                                                                                                                                                                                                                          |

|                |                                               |        |                  | 0                                                                                                          | 0                                                                                                                             | 0                                                                                                                     | 1                                                                                                        | Receiver 1                                                                                                                                                                                                                                                                                                        |

|                |                                               |        |                  | 0                                                                                                          | 0                                                                                                                             | 1                                                                                                                     | 0                                                                                                        | Receiver 2                                                                                                                                                                                                                                                                                                        |

| F3             | 88                                            | A3     | DI               | 0                                                                                                          | 0                                                                                                                             | 1                                                                                                                     | 1                                                                                                        | Receiver 3                                                                                                                                                                                                                                                                                                        |

| F2             | 87                                            | A2     | DI               | 0                                                                                                          | 1                                                                                                                             | 0                                                                                                                     | 0                                                                                                        | Reserved                                                                                                                                                                                                                                                                                                          |

| F1             | 86                                            | A1     | DI               | 0                                                                                                          | 1                                                                                                                             | 0                                                                                                                     | 1                                                                                                        | Reserved                                                                                                                                                                                                                                                                                                          |

| G3             | 85                                            | A0     | DI               | 0                                                                                                          | 1                                                                                                                             | 1                                                                                                                     | 0                                                                                                        | Reserved                                                                                                                                                                                                                                                                                                          |

|                |                                               |        |                  | 0                                                                                                          | 1                                                                                                                             | 1                                                                                                                     | 1                                                                                                        | Reserved                                                                                                                                                                                                                                                                                                          |

|                |                                               |        |                  | 1                                                                                                          | 0                                                                                                                             | 0                                                                                                                     | 0                                                                                                        | No Protection Monitoring                                                                                                                                                                                                                                                                                          |

|                |                                               |        |                  | 1                                                                                                          | 0                                                                                                                             | 0                                                                                                                     | 1                                                                                                        | Transmitter 1                                                                                                                                                                                                                                                                                                     |

|                |                                               |        |                  | 1                                                                                                          | 0                                                                                                                             | 1                                                                                                                     | 0                                                                                                        | Transmitter 2                                                                                                                                                                                                                                                                                                     |

|                |                                               |        |                  | 1                                                                                                          | 0                                                                                                                             | 1                                                                                                                     | 1                                                                                                        | Transmitter 3                                                                                                                                                                                                                                                                                                     |

|                |                                               |        |                  | 1                                                                                                          | 1                                                                                                                             | 0                                                                                                                     | 0                                                                                                        | Reserved                                                                                                                                                                                                                                                                                                          |

|                |                                               |        |                  | 1                                                                                                          | 1                                                                                                                             | 0                                                                                                                     | 1                                                                                                        | Reserved                                                                                                                                                                                                                                                                                                          |

|                |                                               |        |                  | 1                                                                                                          | 1                                                                                                                             | 1                                                                                                                     | 0                                                                                                        | Reserved                                                                                                                                                                                                                                                                                                          |

|                |                                               |        |                  | 1                                                                                                          | 1                                                                                                                             | 1                                                                                                                     | 1                                                                                                        | Reserved                                                                                                                                                                                                                                                                                                          |

|                |                                               |        |                  | to analog lo<br><u>Host Mode</u>                                                                           | tiplexed h                                                                                                                    | node.                                                                                                                 |                                                                                                          | when the respective channel is set<br>s function as non-multiplexed                                                                                                                                                                                                                                               |

| N.C.: Not      | Input; DO: Dig<br>Connected.<br>Is "Not Conne | -      | <br>O: Digital   |                                                                                                            |                                                                                                                               | Analog Inp                                                                                                            | out; AO: A                                                                                               | nalog Output S: Power Supply;                                                                                                                                                                                                                                                                                     |

# intel®

| Ball #<br>PBGA | Pin #<br>LQFP                               | Symbol                 | I/O <sup>1</sup>                                                                                                                                                                                                                                                                | Description                        |                                                     |                                                                                                                                                                         |  |  |

|----------------|---------------------------------------------|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|-----------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|                |                                             |                        |                                                                                                                                                                                                                                                                                 | Loopback Mode                      | e Select/Paral                                      | lel Data bus.                                                                                                                                                           |  |  |

|                |                                             |                        |                                                                                                                                                                                                                                                                                 | When a non-mu<br>function as a bi- |                                                     | processor interface is selected, these pins t data port.                                                                                                                |  |  |

|                |                                             |                        |                                                                                                                                                                                                                                                                                 |                                    |                                                     | essor interface is selected, these pins carr<br>d address inputs A0 -A7.                                                                                                |  |  |

|                |                                             |                        |                                                                                                                                                                                                                                                                                 | In serial Mode, I                  | 00-7 should be                                      | grounded.                                                                                                                                                               |  |  |

|                |                                             |                        |                                                                                                                                                                                                                                                                                 | Hardware Mode                      | <u>:</u>                                            |                                                                                                                                                                         |  |  |

|                |                                             |                        |                                                                                                                                                                                                                                                                                 | In hardware mod<br>open (unconnec  |                                                     | works in normal operation if this pin is lef                                                                                                                            |  |  |

| G2<br>H3       | 90<br>91                                    | D0/LOOP0<br>D1/LOOP1   | DI/O<br>DI/O                                                                                                                                                                                                                                                                    | data on TPOS a<br>RRING is looped  | nd TNEG is igr<br>d around and re<br>ode, the pulse | pback mode if LOOP is Low. In this mode,<br>hored and data received on RTIP and<br>etransmitted on TTIP and TRING. Note: in<br>template cannot be guaranteed while in a |  |  |

| H2             | 92                                          | D2/LOOP2               | DI/O                                                                                                                                                                                                                                                                            | The LXT386 ent                     | ers analog loca                                     | al loopback mode if LOOP=1 and                                                                                                                                          |  |  |

| J4             | 93                                          | D3/LOOP3               | DI/O         DLOOP=0. In this mode, data received on RTIP and RRING is ignor<br>and data transmitted on TTIP and TRING is internally looped around<br>routed back to the receive inputs.           DI/O         The LXT386 enters digital local loopback if LOOP=1 and DLOOP=1. |                                    |                                                     |                                                                                                                                                                         |  |  |

| J3             | 94                                          | D4/DLOOP0              |                                                                                                                                                                                                                                                                                 |                                    |                                                     |                                                                                                                                                                         |  |  |

| J2<br>J1       | 95<br>96                                    | D5/DLOOP1<br>D6/DLOOP2 |                                                                                                                                                                                                                                                                                 |                                    |                                                     |                                                                                                                                                                         |  |  |

| 51<br>K1       | 90<br>97                                    | D7/DLOOP3              | DI/O                                                                                                                                                                                                                                                                            | this mode, data<br>RCLK/RPOS/RN    |                                                     | LK/TPOS/TNEG is digitally looped back t                                                                                                                                 |  |  |

|                | 0.                                          | DIIDLOOF               | 2.0                                                                                                                                                                                                                                                                             |                                    | 120.                                                |                                                                                                                                                                         |  |  |

|                |                                             |                        |                                                                                                                                                                                                                                                                                 | LOOP                               | DLOOP                                               | Operating Mode                                                                                                                                                          |  |  |

|                |                                             |                        |                                                                                                                                                                                                                                                                                 | Open                               | х                                                   | Normal Mode                                                                                                                                                             |  |  |

|                |                                             |                        |                                                                                                                                                                                                                                                                                 | 0                                  | х                                                   | Remote Loopback                                                                                                                                                         |  |  |

|                |                                             |                        |                                                                                                                                                                                                                                                                                 | 1                                  | 0                                                   | Analog Local Loopback                                                                                                                                                   |  |  |

|                |                                             |                        |                                                                                                                                                                                                                                                                                 | 1                                  | 1                                                   | Digital Local Loopback                                                                                                                                                  |  |  |

|                |                                             |                        |                                                                                                                                                                                                                                                                                 | impedano<br>signals w              | ce state. There                                     | s are left open, they stay in a high<br>fore, the layout design should not route<br>ons near the LOOP pins. This practice will<br>pling.                                |  |  |

| L1             | 12                                          | TCLK1                  | DI                                                                                                                                                                                                                                                                              | Transmit Clock                     |                                                     |                                                                                                                                                                         |  |  |

| L2             | 13                                          | TPOS1/                 | DI                                                                                                                                                                                                                                                                              | Transmit Positi                    | ve Data.                                            |                                                                                                                                                                         |  |  |

| LZ             | 13                                          | TDATA1                 | DI                                                                                                                                                                                                                                                                              | Transmit Data.                     |                                                     |                                                                                                                                                                         |  |  |

| 10             |                                             | TNEG1/                 | DI                                                                                                                                                                                                                                                                              | Transmit Negat                     | ive Data.                                           |                                                                                                                                                                         |  |  |

| L3             | 14                                          | UBS1                   | DI                                                                                                                                                                                                                                                                              | Unipolar/Bipola                    | ar Select.                                          |                                                                                                                                                                         |  |  |

| M1             | 15                                          | RCLK1                  | DO                                                                                                                                                                                                                                                                              | Receive Clock.                     |                                                     |                                                                                                                                                                         |  |  |

| M2             | 16                                          | RPOS1/                 | DO                                                                                                                                                                                                                                                                              | Receive Positiv                    | e Data.                                             |                                                                                                                                                                         |  |  |

|                | 10                                          | RDATA1                 | DO                                                                                                                                                                                                                                                                              | Receive Data.                      |                                                     |                                                                                                                                                                         |  |  |

| М3             | 17                                          | RNEG1/                 | DO                                                                                                                                                                                                                                                                              | Receive Negati                     | ve Data.                                            |                                                                                                                                                                         |  |  |

| UNIO           | 17                                          | BPV1                   | DO                                                                                                                                                                                                                                                                              | Bipolar Violation Detect.          |                                                     |                                                                                                                                                                         |  |  |

| K3             | 18                                          | LOS1                   | DO                                                                                                                                                                                                                                                                              | Loss of Signal.                    |                                                     |                                                                                                                                                                         |  |  |

| N.C.: Not      | Input; DO: Di<br>Connected.<br>s "Not Conne | •                      | ): Digital                                                                                                                                                                                                                                                                      | Bidirectional Port;                | Al: Analog Inp                                      | ut; AO: Analog Output S: Power Supply;                                                                                                                                  |  |  |

#### Table 1. Pin Assignments and Signal Descriptions (Sheet 3 of 11)

#### Table 1. Pin Assignments and Signal Descriptions (Sheet 4 of 11)

| Ball #<br>PBGA | Pin #<br>LQFP                               | Symbol              | I/O <sup>1</sup> | Description                                                                                                                               |                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                             |  |

|----------------|---------------------------------------------|---------------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|--|

|                |                                             |                     |                  | TNEG are san<br>drivers enter a<br>clock cycles th<br>pulse widths a<br>When pulse sh<br>LXT384 device<br>a programmab<br>To prevent this | pled on the<br>low power l<br>e pulse sha<br>re determine<br>aping is disa<br>by leaving<br>le ASIC mig<br>, clock one c | ormal operation TCLK is active, and TPC<br>falling edge of TCLK. If TCLK is Low, the<br>nigh Z mode. If TCLK is High for more th<br>ping circuit is disabled and the transmit of<br>ed by the TPOS and TNEG duty cycles.<br>abled, it is possible to overheat and dama<br>transmit inputs high continuously. For ex<br>ht leave all outputs high until it is prograr<br>of these signals: TPOS, TNEG, TCLK or I<br>ne of these signals low: TPOS, TNEG, TC | e outp<br>nan 16<br>outpu<br>age th<br>xamp<br>mmeo<br>MCLh |  |

| N1             | 19                                          | TCLK0               | DI               | тс                                                                                                                                        | LK                                                                                                                       | Operating Mode                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                             |  |

|                |                                             |                     |                  | Clo                                                                                                                                       | ked No                                                                                                                   | rmal operation                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                             |  |

|                |                                             |                     |                  |                                                                                                                                           | H TA                                                                                                                     | OS (if MCLK supplied)                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                             |  |

|                |                                             |                     |                  |                                                                                                                                           |                                                                                                                          | able transmit pulse shaping (when<br>CLK is not available)                                                                                                                                                                                                                                                                                                                                                                                                 |                                                             |  |

|                |                                             |                     |                  |                                                                                                                                           | _ Dri                                                                                                                    | ver outputs enter tri-state                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                             |  |

| N2             | 20                                          | 20 TPOS0/<br>TDATA0 | DI<br>DI         |                                                                                                                                           | ative Data.<br>Mar Select.<br>Are active hig                                                                             | h NRZ inputs. TPOS indicates the transmission of a new second second second second second second second second                                                                                                                                                                                                                                                                                                                                             |                                                             |  |

|                |                                             |                     |                  | TPOS                                                                                                                                      | TNEG                                                                                                                     | Selection                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                             |  |

|                |                                             |                     |                  | 0                                                                                                                                         | 0                                                                                                                        | Space                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                             |  |

|                |                                             |                     |                  | 1                                                                                                                                         | 0                                                                                                                        | Positive Mark                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                             |  |

|                |                                             |                     |                  | 0                                                                                                                                         | 1                                                                                                                        | Negative Mark                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                             |  |

|                |                                             |                     |                  | 1                                                                                                                                         | 1                                                                                                                        | Space                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                             |  |

| N3             | 21                                          | TNEG0/<br>UBS0      | DI<br>DI         | cycles, unipola<br>encoding/deco                                                                                                          | IBS is pullec<br>ar I/O is sele<br>ding is dete                                                                          | I High for more than 16 consecutive TCL<br>cted. In unipol <u>ar mode</u> , B8ZS/HDB3 or <i>A</i><br>rmined by the CODEN pin (hardware mo<br>CR register (software mode).                                                                                                                                                                                                                                                                                  | ٩MI                                                         |  |