# **Cortina Systems<sup>®</sup> LXT332 Dual T1/E1** Line Interface Unit with Crystal-less Jitter Attenuation

## Datasheet

The Cortina Systems<sup>®</sup> LXT332 Dual T1/E1 Line Interface Unit with Crystal-less Jitter Attenuation (LXT332) is a fully integrated Dual Line Interface Unit (DLIU) for both 1.544 Mbps (T1) and 2.048 Mbps (E1) applications. It features B8ZS/HDB3 encoders and decoders, and a constant low output impedance transmitter for high return loss. Transmit pulse shape is selectable for various line lengths and cable types.

The LXT332 incorporates an advanced crystal-less digital jitter attenuator, switchable to either the transmit or receive side. This eliminates the need for an external quartz crystal. It offers both a serial interface (SIO) for microprocessor control and a hardware control mode for stand-alone operation.

The LXT332 offers a variety of advanced diagnostic and performance monitoring features. It uses an advanced double-poly, double-metal CMOS process and requires only a single 5-volt power supply.

# **Applications**

- PCM/Voice Channel Banks

- Data Channel Bank/Concentrator

- T1/E1 multiplexer

- Digital Access and Cross-connect Systems (DACS)

# **Product Features**

- Digital (crystal-less) jitter attenuation, selectable for receive or transmit path, or may be disabled

- High transmit and receive return loss

- Constant low output impedance transmitter with programmable equalizer shapes pulses to meet DSX-1 pulse template from 0 to 655 ft.

- Meets or exceeds industry specifications including ITU G.703, ANSI T1.403, AT&T Pub 62411 and ITU-T G.742

- Compatible with most industry standard framers

- Computer to PBX interface (CPI & DMI)

- SONET/SDH Multiplexers

- Interfacing Customer Premises Equipment to a CSU

- Digital Loop Carrier (DLC) terminals

- Complete line driver, data recovery and clock recovery functions

- Minimum receive signal of 500 mV, with selectable slicer levels to improve SNR

- Local, remote, and dual loopback functions

- Built-In Self Test with QRSS Pattern Generator

- Transmit/Receive performance monitors with Driver Fail Monitor (DFM) and Loss of Signal (LOS) outputs

- Receiver jitter tolerance 0.4 UI from 40 kHz to 100 kHz

- Available in 44-pin PLCC and 44-pin QFP packages

\*Other names and brands may be claimed as the property of others.

© Cortina Systems, Inc. 2007

# Contents

| 1.0 | Block      | c Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                              | . 6                                  |

|-----|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|

| 2.0 | Over       | view                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 7                                    |

| -   | 2.1<br>2.2 | Standard LXT332 Features         2.1.1       Tri-state Outputs         2.1.2       Bipolar or Unipolar Data I/O.         2.1.3       B8ZS or HDB3 Zero Suppression         2.1.4       Selectable Jitter Attenuation         2.1.5       Dual Loopback         Additional Host-Mode Features         2.2.1       High Frequency Clocks         2.2.2       Bipolar Violation Insertion         2.2.3       Built-In Self Test (QRSS)         2.2.4       AIS Detection | 7<br>7<br>7<br>7<br>7<br>7<br>7<br>7 |

| 3.0 | Pin A      | ssignments and Signal Descriptions                                                                                                                                                                                                                                                                                                                                                                                                                                     | .9                                   |

| 4.0 | Func       | tional Description                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 17                                   |

|     | 4.1<br>4.2 | Receiver<br>Transmitter<br>4.2.1 Bipolar Violation Insertions<br>4.2.2 Pulse Shape                                                                                                                                                                                                                                                                                                                                                                                     | 18<br>18                             |

|     | 4.3        | Driver Failure Monitor                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                      |

|     | 4.4        | Jitter Attenuation                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                      |

|     | 4.5        | Built-In Self Test                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                      |

|     | 4.6<br>4.7 | Operating Modes                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                      |

|     | 4.7        | 4.7.1 Serial Input Word                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                      |

|     |            | 4.7.2 Serial Output Word                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                      |

|     |            | 4.7.3 Interrupt Handling                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                      |

|     | 4.8        | Hardware Mode Control                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                      |

|     | 4.9        | Diagnostic Mode Operation                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                      |

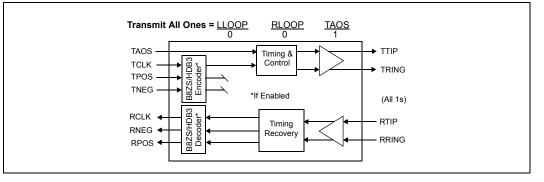

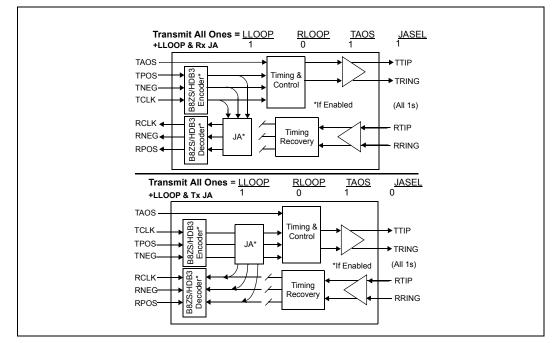

|     |            | <ul> <li>4.9.1 Transmit All Ones (See Figure 8)</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                              |                                      |

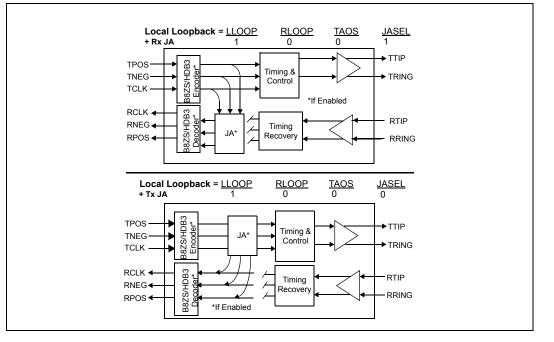

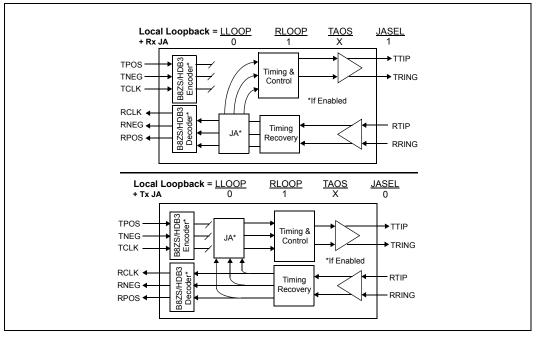

|     |            | <ul> <li>4.9.2 Local Loopback (See Figure 9 and Figure 10)</li> <li>4.9.3 Remote Loopback (See Figure 11)</li> </ul>                                                                                                                                                                                                                                                                                                                                                   |                                      |

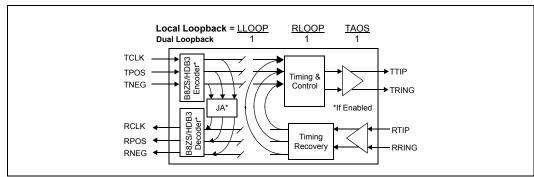

|     |            | 4.9.4 Dual Loopback (See Figure 12)                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                      |

|     |            | 4.9.5 QRSS Built-In Self Test - Host Mode                                                                                                                                                                                                                                                                                                                                                                                                                              |                                      |

|     | 4.10       | Initialization/Reset Operation                                                                                                                                                                                                                                                                                                                                                                                                                                         | 29                                   |

| 5.0 | Appli      | cation Information                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                      |

|     | 5.1        | Power Requirements                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                      |

|     | 5.2        | Transformers                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                      |

|     | 5.3        | Line Protection                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                      |

|     | 5.4<br>5.5 | 1.544 Mbps T1 Applications                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                      |

|     | 0.0        | 2.048 Mbps E1/CEPT Interface Applications                                                                                                                                                                                                                                                                                                                                                                                                                              |                                      |

|     |            | 5.5.2 E1 Twisted-Pair Applications                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                      |

| 6.0 | Test       | Specifications                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                      |

| 7.0 | Mechanical Specifications | 43 | 3 |

|-----|---------------------------|----|---|

|-----|---------------------------|----|---|

# **Figures**

| 1  | Block Diagram                                                      | 6  |

|----|--------------------------------------------------------------------|----|

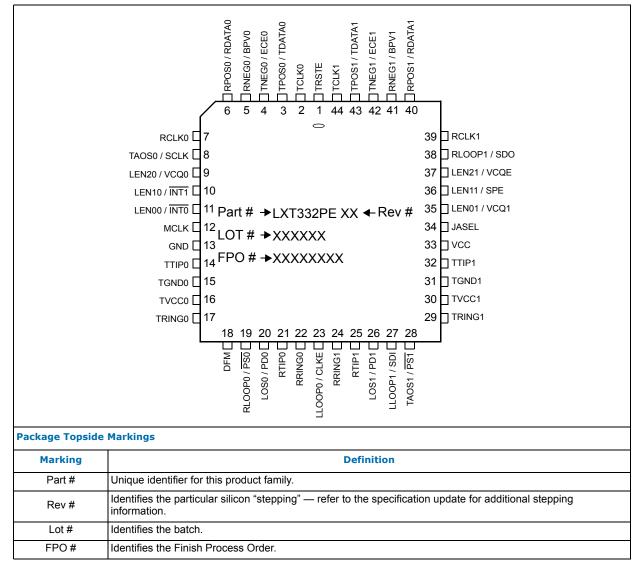

| 2  | Pin Assignments (Frame Graphic) and Package Markings (PLCC)        | 9  |

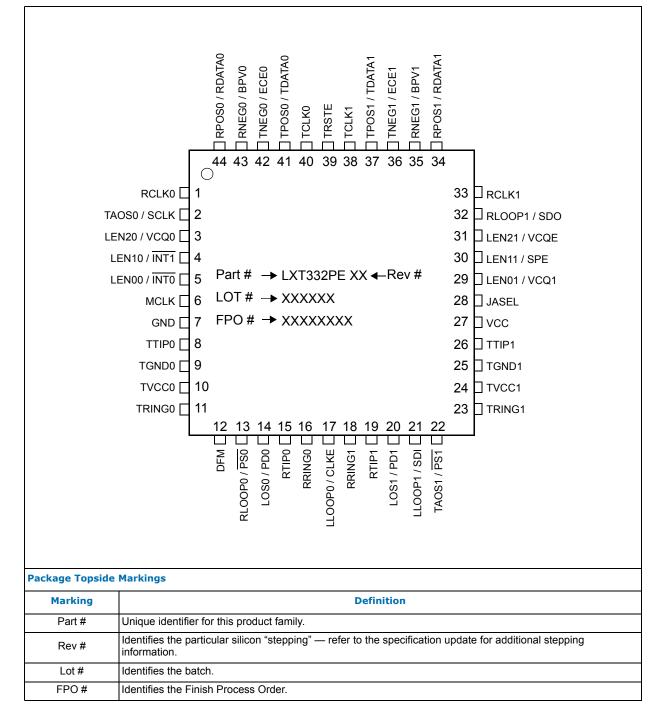

| 3  | Pin Assignments (Frame Graphic) and Package Markings (QFP Package) |    |

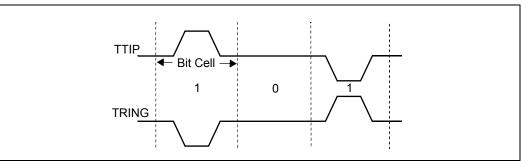

| 4  | 50% AMI Coding                                                     |    |

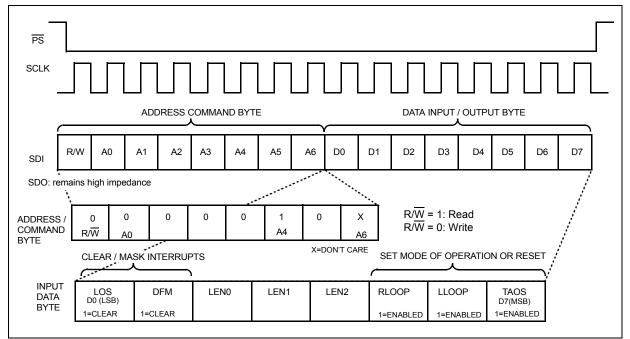

| 5  | SIO Write Operation                                                | 23 |

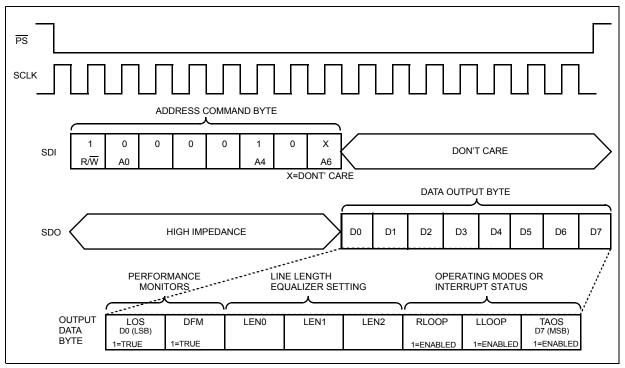

| 6  | SIO Read Operation                                                 | 23 |

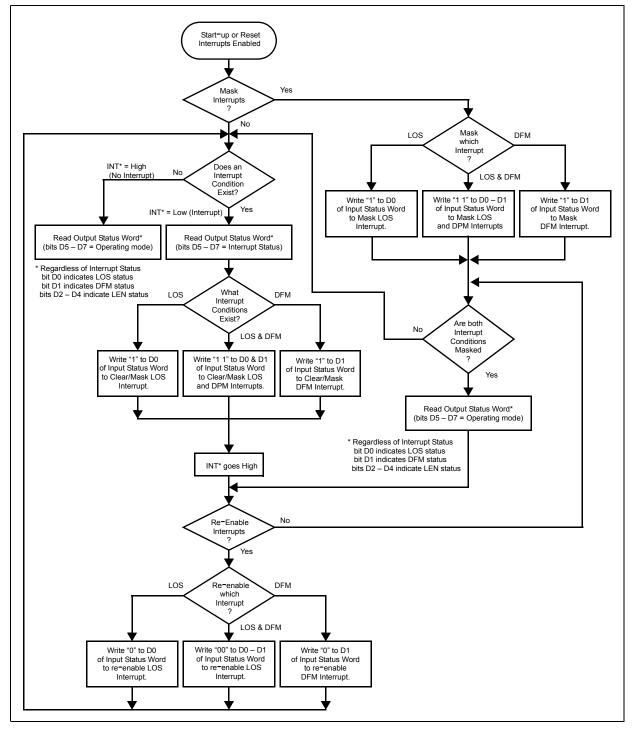

| 7  | Interrupt Handling                                                 | 24 |

| 8  | TAOS Data Path                                                     | 26 |

| 9  | TAOS with LLOOP & Selectable JA                                    |    |

| 10 | Local Loopback - Selectable JA                                     | 27 |

| 11 | Remote Loopback - Selectable JA                                    | 28 |

| 12 | Dual Loopback                                                      | 28 |

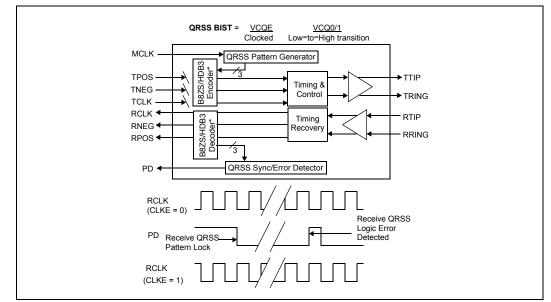

| 13 | QRSS BIST                                                          | 29 |

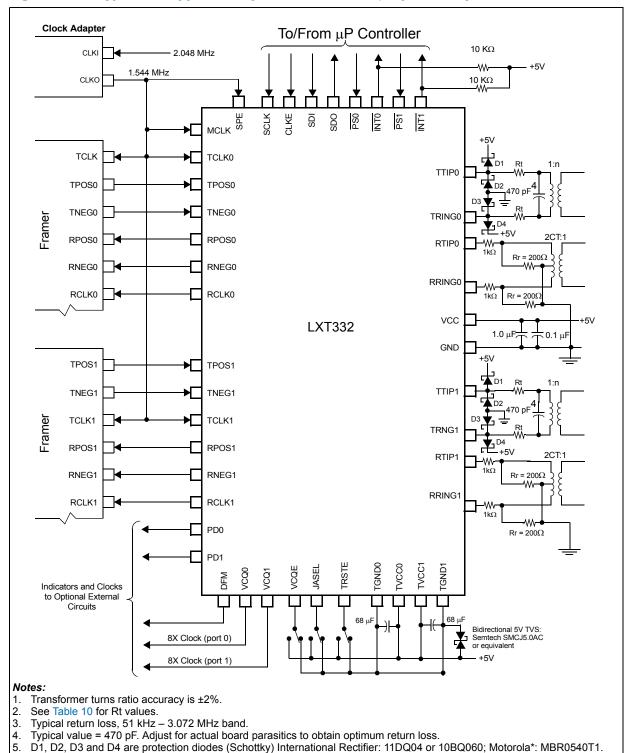

| 14 | Typical T1 Application (Host Control Mode, Bipolar I/O)            | 33 |

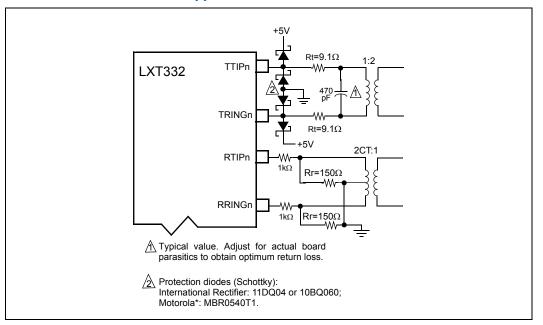

| 15 | Line Interface for E1 Coax Applications                            | 34 |

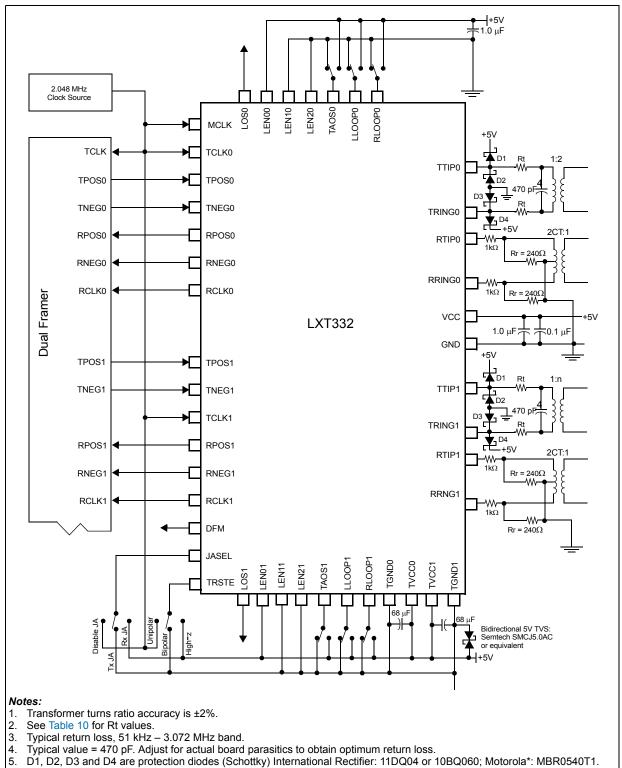

| 16 | Typical E1 120 W Application (Hardware Control Mode)               | 35 |

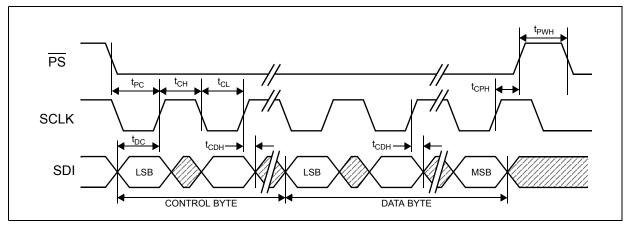

| 17 | Serial Data Input Timing Diagram                                   |    |

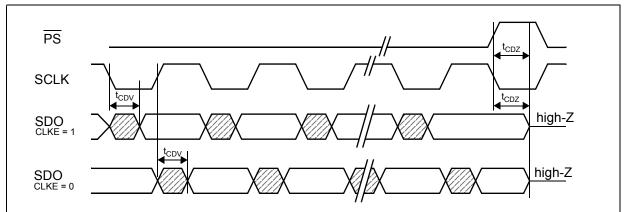

| 18 | Serial Data Output Timing Diagram                                  |    |

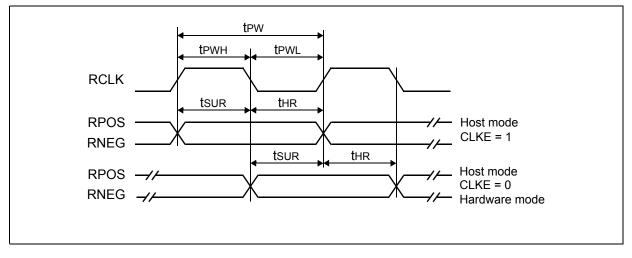

| 19 | Receive Clock Timing                                               |    |

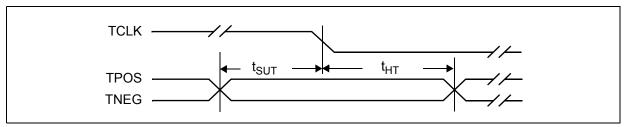

| 20 | Transmit Clock Timing                                              | 40 |

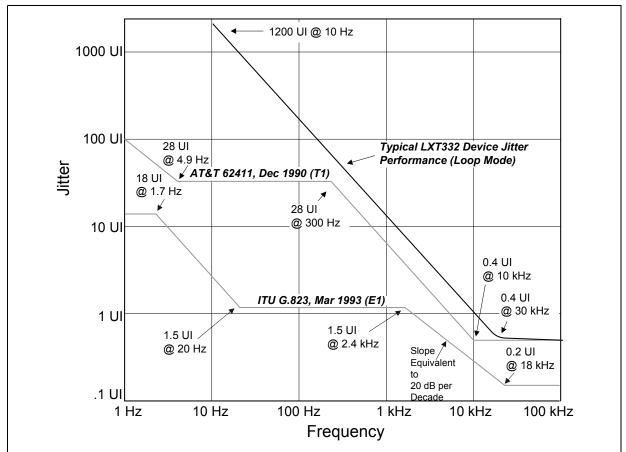

| 21 | Typical Receiver Input Jitter Tolerance (Loop Mode)                | 41 |

| 22 | Typical Jitter Transfer Performance                                | 42 |

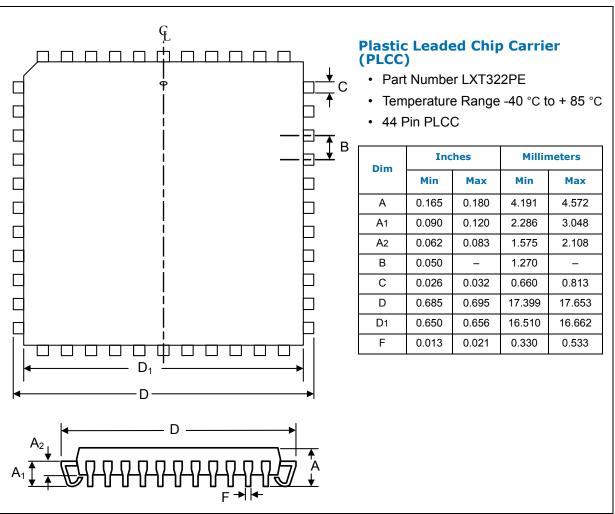

| 23 | PLCC Package Specifications                                        | 43 |

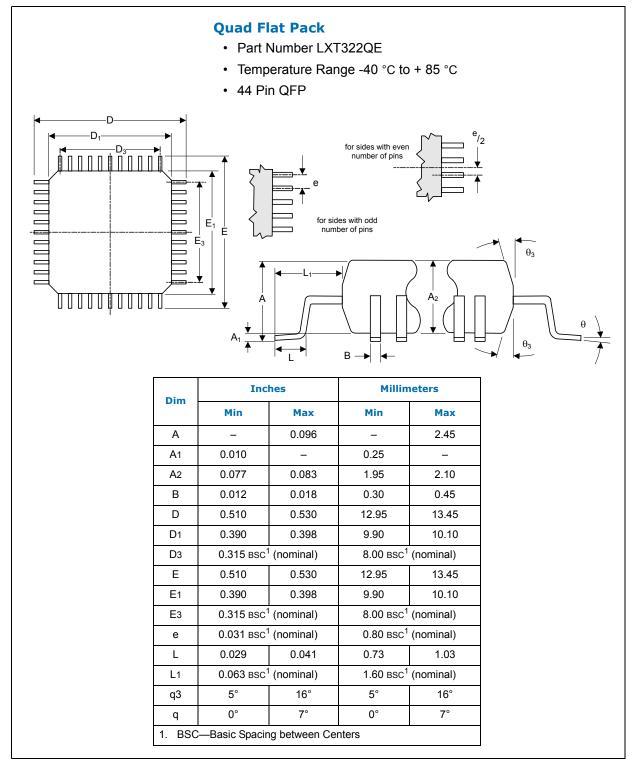

| 24 | QFP Package Specifications                                         |    |

# **Tables**

| 1<br>2 | Host Mode and Bipolar Host Mode Pin Descriptions<br>Unipolar Host Mode Pin Descriptions <sup>1</sup>                          | 11 |

|--------|-------------------------------------------------------------------------------------------------------------------------------|----|

| 2      | Unipolar Host Mode Pill Descriptions                                                                                          | 14 |

| 4      | Hardware Mode and Bipolar Hardware Mode Pin Descriptions <sup>1</sup><br>Unipolar Hardware Mode Pin Descriptions <sup>1</sup> | 16 |

| 5      | Equalizer Control Inputs                                                                                                      | 19 |

| 6      | CLKE Settings                                                                                                                 | 21 |

| 7      | SIO Input Bit Settings (See Figure 5)                                                                                         |    |

| 8      | Serial Data Output Bit Coding (See Figure 6)                                                                                  |    |

| 9      | Recommended Transformer Values                                                                                                |    |

| 10     | Transformer Combinations                                                                                                      | 32 |

| 11     | Absolute Maximum Ratings                                                                                                      | 36 |

| 12     | Recommended Operating Conditions                                                                                              | 36 |

| 13     | Electrical Characteristics (Over Recommended Operating Conditions)                                                            | 36 |

| 14     | Analog Specifications (Over Recommended Operating Conditions)                                                                 | 37 |

| 15     | Serial I/O Timing Characteristics (See Figure 17 and Figure 18)                                                               | 38 |

| 16     | Receive Timing Characteristics (See Figure 19)                                                                                | 40 |

| 17     | Master Clock and Transmit Timing Characteristics (See Figure 20)                                                              | 40 |

# **Revision History**

#### Revision 2.0 Revision Date: 26 June 2007

First release of this document from Cortina Systems, Inc.

Revision 001 Revision Date: January 2001

Initial release.

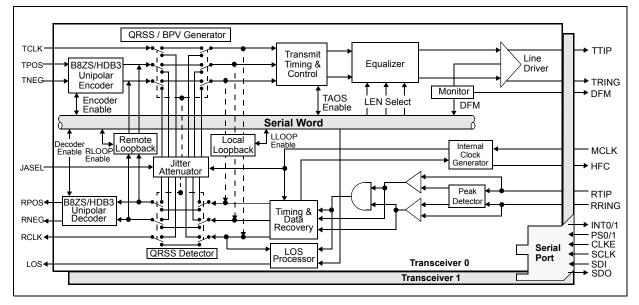

# **1.0 Block Diagram**

#### Figure 1 Block Diagram

# 2.0 Overview

In addition to the inherent advantages of a dual LIU, the LXT332 also provides several advanced features that are not available in other LXT300-series devices. All of the added features are easily implemented. Many require only a clock pulse to change from one mode to another. Some features are available in Host mode only.

# 2.1 Standard LXT332 Features

#### 2.1.1 Tri-state Outputs

All LXT332 output pins can be forced to tri-state (high-Z). Tri-state is controlled by the TRSTE pin.

## **2.1.2 Bipolar or Unipolar Data I/O**

The LXT332 to framer interface can be either bipolar (default) or unipolar (selectable). The unipolar I/O mode is selected by applying MCLK to the TRSTE pin.

#### 2.1.3 B8ZS or HDB3 Zero Suppression

The LXT332 incorporates zero suppression encoders and decoders for use in the unipolar data I/O mode. The encoders/decoders can be activated or deactivated by changing the logic level on the re-mapped TNEG pin.

#### 2.1.4 Selectable Jitter Attenuation

Jitter attenuation can be placed in either the transmit or receive path or deactivated. The Jitter Attenuation Select (JASEL) pin selects the jitter attenuation path. No crystal is required.

#### 2.1.5 Dual Loopback

Dual Loopback (DLOOP) enables simultaneous loopbacks to both the framer and the line. The TCLK, TPOS and TNEG framer inputs are routed through the jitter attenuator and looped back to the RCLK, RPOS and RNEG outputs. The RTIP/RRING line inputs are looped back through the timing recovery block and line driver onto the TTIP/TRING outputs.

## 2.2 Additional Host-Mode Features

#### 2.2.1 High Frequency Clocks

The LXT332 provides a pair of high frequency clock outputs, one for each LIU. These 8x clocks (12.352 MHz for T1, 16.384 MHz for E1) are tied to the de-jittered clock from the JA of the respective LIU.

#### 2.2.2 Bipolar Violation Insertion

The same pins which provide the high frequency clocks can also be used to insert bipolar violations into the outgoing data stream. Violations can be inserted into each LIU port independently.

## 2.2.3 Built-In Self Test (QRSS)

The LXT332 can generate and transmit a Quasi Random Signal Source (QRSS) pattern to Built-In Self Test (BIST) applications. Logic errors and bipolar violations can be inserted into the QRSS output. The LXT332 also detects QRSS pattern synchronization and reports bit errors in the received QRSS pattern data stream.

## **2.2.4 AIS Detection**

The LXT332 detects the AIS alarm signal on the receive side independent of the loopback modes. When AIS is detected (less than 3 zeros in 2048 bits), the LXT332 provides an indicator output.

# **3.0 Pin Assignments and Signal Descriptions**

Figure 2 and Figure 3 identify the pins and signals for the PLCC and QFP packages, respectively. Note that many pins have two functions. The active function is determined by the particular mode of operation selected. Table 1 describes the Host mode signal functions, except signals that change when in Unipolar Host mode. Table 2 describes signal functions that change when in Unipolar Most mode. Table 3 describes all Hardware mode signal functions, except signals that change when in Unipolar Most mode. Table 4 describes signal functions that change when Unipolar Hardware mode is selected.

#### Table 1Host Mode and Bipolar Host Mode Pin Descriptions (Sheet 1 of 3)

| Pin<br>QFP | Pin<br>PLCC            | Symbol             | <b>I/O</b> <sup>1</sup> | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|------------|------------------------|--------------------|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|            |                        |                    |                         | <b>Tristate Output Enable.</b> When held High, forces all output pins to high-Z (tri-state). When held Low, Bipolar I/O mode is selected. In this mode, the framer interface is bipolar (TPOS/TNEG and RPOS/RNEG), and the B8ZS/HDB3 encoders are disabled.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 39         | 1                      | TRSTE              | DI                      | When clocked by MCLK, Unipolar I/O mode is selected. In this mode, the framer interface is unipolar (TDATA and RDATA), and the TNEG and RNEG pins are re-mapped. The TNEG pins are re-mapped as Encoder Enables (ECE) to individually enable the B8ZS/HDB3 encoder/decoder for each port. The RNEG pins are re-mapped as Bipolar Violation (BPV) indicators to report BPVs detected at the respective ports.                                                                                                                                                                                                                                                                                                                                                         |

| 40         | 2                      | TCLK0              | DI                      | <b>Transmit Clock - Port 0.</b> 1.544 MHz for T1, 2.048 MHz for E1. The port 0 transmit data inputs are sampled on the falling edge of TCLK0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 41         | 3                      | TPOS0<br>(Bipolar) | DI                      | <b>Transmit Positive and Negative Data - Port 0.</b> In the Bipolar I/O mode, these pins are the positive and negative sides of a bipolar input pair for port 0. Data to be transmitted                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 42         | 4                      | TNEG0<br>(Bipolar) | DI                      | onto the twisted-pair line is input at these pins.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 43         | 5                      | RNEG0<br>(Bipolar) | DO                      | <b>Receive Positive and Negative Data - Port 0.</b> In the Bipolar I/O mode, these pins are the data outputs from port 0. A signal on RNEG corresponds to receipt of a negative                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 44         | 6                      | RPOS0<br>(Bipolar) | DO                      | pulse on RTIP/RRING. A signal on RPOS corresponds to receipt of a positive pulse on RTIP/RRING. RNEG/RPOS outputs are Non Return-to-Zero (NRZ). The CLKE pin determines the clock edge at which these outputs are stable and valid.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 1          | 7                      | RCLK0              | DO                      | <b>Receive Clock - Port 0.</b> Normally, this clock is recovered from the input signal. Under Loss of Signal (LOS) conditions, RCLK0 is derived from MCLK.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 2          | 8                      | SCLK               | DI                      | Serial Clock. SCLK shifts data into or out of the serial interface register of the selected port.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|            |                        |                    |                         | Violation Insert, High Frequency Clock, or QRSS - Port 0. The function of this pin is selected by the VCQE pin.<br>When VCQE is High, the Bipolar Violation (BPV) insertion function is selected. VCQ0 is an input that is sampled on the falling edge of TCLK0 to control BPV insertion. When VCQ0 is High, a BPV is inserted at the next available mark transmitted from port 0. A Low-to-High transition is required for each subsequent BPV insertion. B8ZS and HDB3 zero suppression codes are not violated.<br>When VCQ0 is Low, the High Frequency Clock (HFC) function is selected. VCQ0                                                                                                                                                                     |

| 3          | 9                      | VCQ0               | DI/O                    | outputs a HFC (12.352 MHz for T1, 16.384 MHz for E1) tied to the jitter attenuated clock of the port 0. If no JA clock is available, the HFC is locked to the 8x receive timing recovery clock.<br>When VCQE is clocked with MCLK, the Quasi Random Signal Source (QRSS) function is selected. A High on VCQ0 enables the QRSS detection circuit and causes the LXT332 to transmit the QRSS pattern onto the twisted-pair line from port 0. For error-free QRSS transmission, TPOS0 must be held Low. To insert errors into the pattern, TPOS0 must transition from Low to High (TPOS0 is sampled on the falling edge of MCLK). A Low to High transition is required for each subsequent violation insertion. B8ZS and HDB3 zero suppression codes are not violated. |

| 4<br>5     | 10<br>11               | INT1<br>INT0       | DO<br>DO                | <b>Interrupt Outputs.</b> The interrupt outputs go Low to flag the host processor that the respective port has changed state. INT0 and INT1 are open drain outputs. Each interrupt signal must be tied to VCC through a resistor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 6          | 12                     | MCLK               | DI                      | <b>Master Clock.</b> The master clock (1.544 MHz for T1, 2.048 MHz for E1) must be independent, free-running, continuously active and jitter free for receiver operation. Note that MCLK cannot be derived from RCLK because during a Loss of Signal (LOS) condition, transceiver timing is based on MCLK.                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 7          | 13                     | GND                | S                       | Ground. Ground return for the VCC power supply.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|            | = Digital Inp<br>oply. | out; DO = Dig      | ital Outp               | ut; DI/O = Digital Input/Output; AI = Analog Input; AO = Analog Output; S = Power                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

#### Table 1Host Mode and Bipolar Host Mode Pin Descriptions (Sheet 2 of 3)

| Pin<br>QFP | Pin<br>PLCC | Symbol          | <b>I/O</b> <sup>1</sup> | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|------------|-------------|-----------------|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 8<br>11    | 14<br>17    | TTIP0<br>TRING0 | AO<br>AO                | <b>Transmit Tip and Ring - Port 0.</b> These pins are differential driver outputs designed to drive a 35 - 200 $\Omega$ load. Line matching resistors and transformers can be selected to give the desired pulse height. See Table 10 and Figure 14 through Figure 16 for details                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 9          | 15          | TGND0           | S                       | Ground - Port 0 Transmit Driver. Ground return for the TVCC0 power supply.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 10         | 16          | TVCC0           | S                       | + 5 VDC - Port 0 Transmit Driver. TVCC0 must not vary from TVCC1 or VCC by more than ± 0.3 V.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 12         | 18          | DFM             | DO                      | <b>Driver Failure Monitor.</b> This signal goes High to indicate a driver output short in one or both ports.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 13         | 19          | PS0             | DI                      | <b>Port Select - Port 0.</b> This signal selects the serial interface registers for port 0. For each read or write operation, PS0 must transition from High to Low, and remain Low.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 14         | 20          | PD0             | DO                      | Pattern Detect - Port 0. Unless the QRSS function is selected by the VCQE pin, PD0 functions as an Alarm Indication Signal (AIS). The AIS pattern is detected by the receiver, independent of any loopback mode. PD0 goes High when less than three zeros have been detected in any string of 2048 bits. PD0 returns Low when the received signal contains more than three zeros in 2048 bits.<br>If the QRSS function is enabled by the VCQE pin, PD0 remains High until pattern sync is reached with the received signal. Once pattern lock is obtained, PD0 goes Low. The sync/out-of-sync criteria is: less than 3/4 errors in 128 bits. After sync acquisition, bit errors cause PD0 to go High for half a clock cycle. PD0 can be used to trigger an |

|            |             |                 |                         | external error counter.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 15<br>16   | 21<br>22    | RTIP0<br>RRING0 | AI<br>AI                | <b>Receive Tip and Ring - Port 0.</b> These pins comprise the receive line interface and should be connected to the line through a center-tapped 1:2 transformer. See Figure 14 through Figure 16 for details.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 17         | 23          | CLKE            | DI                      | <b>Clock Edge Select.</b> When CLKE is High, RPOS/RNEG or RDATA outputs are valid on the falling edge of RCLK, and SDO is valid on the rising edge of SCLK.<br>When CLKE is Low, RPOS/RNEG or RDATA outputs are valid on the rising edge of RCLK, and SDO is valid on the falling edge of SCLK.                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 18<br>19   | 24<br>25    | RRING1<br>RTIP1 | AI<br>AI                | <b>Receive Tip and Ring - Port 1.</b> These pins comprise the receive line interface and should be connected to the line through a center-tapped 1:2 transformer. See Figure 14 through Figure 16 for details.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 20         | 26          | PD1             | DO                      | Pattern Detect - Port 1. Reports AIS and QRSS pattern reception. See PD0 signal description for details.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 21         | 27          | SDI             | DI                      | Serial Data Input. Write data to the LXT332 registers is input on this pin. SDI is sampled on the rising edge of SCLK.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 22         | 28          | PS1             | DI                      | <b>Port Select - Port 1.</b> Selects the serial interface registers for port 1. For each read or write operation, PS1 must transition from High to Low, and remain Low.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 23<br>26   | 29<br>32    | TRING1<br>TTIP1 | AO<br>AO                | <b>Transmit Tip and Ring - Port 1.</b> These pins are differential driver outputs designed to drive a 35 - 200 $\Omega$ load. Line matching resistors and transformers can be selected to give the desired pulse height. See Table 10 and Figure 14 through Figure 16 for details                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 24         | 30          | TVCC1           | S                       | + 5 VDC - Port 1 Transmit Driver. TVCC1 must not vary from TVCC0 or VCC by more than ± 0.3 V.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 25         | 31          | TGND1           | S                       | Ground - Port 1 Transmit Driver. Ground return for the TVCC1 power supply.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 27         | 33          | VCC             | S                       | +5 VDC. Power supply for all circuits except the transmit drivers.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 28         | 34          | JASEL           | DI                      | <b>Jitter Attenuation Select.</b> When JASEL is High, the Jitter Attenuation (JA) circuits are placed in the receive paths. When JASEL is Low, the JA circuits are placed in the transmit paths. When JASEL is clocked with MCLK, the JA circuits are disabled.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Table 1 | Host Mode and B     | Bipolar Host Mode F | Pin Descriptions ( | Sheet 3 of 3) |

|---------|---------------------|---------------------|--------------------|---------------|

|         | Incort incare and a |                     |                    |               |

| 35       | VCQ1                                         | DI/O                                                                                                                 | Violation Insert, High Frequency Clock, or QRSS - Port 1. The function of this pin is selected by the VCQE pin. Refer to VCQ0 signal description for details.                                                                                                                                                                                                                                   |

|----------|----------------------------------------------|----------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 36       | SPE                                          | DI                                                                                                                   | Serial Port Enable. When clocked with MCLK, Host mode is enabled. In Host mode the LXT332 is controlled by a $\mu$ P via the serial port.                                                                                                                                                                                                                                                       |

| 37       | VCQE                                         | DI                                                                                                                   | Violation Insert, High Frequency Clock, QRSS Enable. When set High, selects the Bipolar Violation (BPV) insertion function on VCQ0 and VCQ1. When set Low, selects the High Frequency Clock (HFC) function on VCQ0 and VCQ1. When clocked with MCLK, selects the Quasi Random Signal Source (QRSS) function on VCQ0 and VCQ1, and enables the QRSS Generate and Detect function on PD0 and PD1. |

| 38       | SDO                                          | DO                                                                                                                   | <b>Serial Data Output.</b> This pin carries read data from the LXT332 registers. When CLKE is High, SDO is valid on the rising edge of SCLK. When CLKE is Low, SDO is valid on the falling edge of SCLK.                                                                                                                                                                                        |

| 39       | RCLK1                                        | DO                                                                                                                   | <b>Receive Clock - Port 1.</b> Normally, this clock is recovered from the port 1 input signal.<br>Under Loss of Signal (LOS) conditions, RCLK1 is derived from MCLK.                                                                                                                                                                                                                            |

| 40<br>41 | RPOS1<br>(Bipolar)<br>RNEG1<br>(Bipolar)     | DO<br>DO                                                                                                             | <b>Receive Positive and Negative Data - Port 1.</b> In the Bipolar I/O mode, these pins are the data outputs from port 1. See RPOS0 and RNEG0 for signal descriptions.                                                                                                                                                                                                                          |

| 42<br>43 | TNEG1<br>(Bipolar)<br>TPOS1<br>(Bipolar)     | DI<br>DI                                                                                                             | <b>Transmit Positive and Negative Data - Port 1.</b> In the Bipolar I/O mode, these pins are the positive and negative sides of a bipolar input pair for port 1. Data to be transmitted onto the twisted-pair line is input at these pins.                                                                                                                                                      |

| 44       | TCLK1                                        | DI                                                                                                                   | Transmit Clock - Port 1. 1.544 MHz for T1, 2.048 MHz for E1. The port 1 transmit data inputs are sampled on the falling edge of TCLK1.                                                                                                                                                                                                                                                          |

|          | 36<br>37<br>38<br>39<br>40<br>41<br>42<br>43 | 36SPE36SPE37VCQE38SDO39RCLK140RPOS1<br>(Bipolar)<br>4141RNEG1<br>(Bipolar)42TNEG1<br>(Bipolar)<br>TPOS1<br>(Bipolar) | 36SPEDI36SPEDI37VCQEDI38SDODO39RCLK1DO40RPOS1<br>(Bipolar)DO41RNEG1<br>(Bipolar)DO42TNEG1<br>(Bipolar)DI43TPOS1<br>(Bipolar)DI                                                                                                                                                                                                                                                                  |

## Table 2Unipolar Host Mode Pin Descriptions1 (Sheet 1 of 2)

| Pin<br>QFP | Pin<br>PLCC   | Symbol | <b>I/O</b> <sup>2</sup> | Description                                                                                                                                                          |

|------------|---------------|--------|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 41         | 3             | TDATA0 | DI                      | <b>Transmit Data - Port 0.</b> In the Unipolar I/O mode, the data to be transmitted onto the twisted-pair line from port 0 is input at this pin.                     |

| 42         | 4             | ECE0   | DI                      | <b>Encoder Enable - Port 0.</b> In the Unipolar I/O mode, a High on this pin enables the B8ZS or HDB3 encoder/decoder for port 0.                                    |

| 43         | 5             | BPV0   | DO                      | <b>Bipolar Violation - Port 0.</b> In the Unipolar I/O mode, this pin goes High to indicate that a bipolar violation was detected at port 0.                         |

| 44         | 6             | RDATA0 | DO                      | <b>Receive Data - Port 0.</b> In the Unipolar I/O mode, RDATA0 is a Non Return-to-Zero (NRZ) output. CLKE determines the RCLK0 edge that RDATA0 is stable and valid. |

| 34         | 40            | RDATA1 | DO                      | <b>Receive Data - Port 1.</b> In the Unipolar I/O mode, RDATA1 is a Non Return-to-Zero (NRZ) output. CLKE determines the RCLK1 edge that RDATA1 is stable and valid. |

|            | igital Input; |        |                         | ange function in Unipolar Host mode and functions of pins unique to Bipolar mode.<br>DI/O = Digital Input/Output; AI = Analog Input; AO = Analog Output; S = Power   |

## Table 2Unipolar Host Mode Pin Descriptions<sup>1</sup> (Sheet 2 of 2)

| Pin<br>QFP | Pin<br>PLCC   | Symbol | <b>I/O</b> <sup>2</sup> | Description                                                                                                                                                         |

|------------|---------------|--------|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 35         | 41            | BPV1   | DO                      | <b>Bipolar Violation - Port 1.</b> In the Unipolar I/O mode, this pin goes High to indicate that a bipolar violation is detected at port 1.                         |

| 36         | 42            | ECE1   | DI                      | <b>Encoder Enable - Port 1.</b> In the Unipolar I/O mode, a High on this pin enables the B8ZS or HDB3 encoder/decoder for port 1.                                   |

| 37         | 43            | TDATA1 | DI                      | <b>Transmit Data - Port 1.</b> In the Unipolar I/O mode, the data to be transmitted onto the twisted-pair line from port 1 is input at this pin.                    |

|            | igital Input; |        |                         | hange function in Unipolar Host mode and functions of pins unique to Bipolar mode.<br>DI/O = Digital Input/Output; AI = Analog Input; AO = Analog Output; S = Power |

#### Table 3Hardware Mode and Bipolar Hardware Mode Pin Descriptions<sup>1</sup> (Sheet 1 of 3)

| Pin<br>QFP         | Pin<br>PLCC                | Symbol                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | <b>I/O</b> <sup>2</sup> | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|--------------------|----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 39                 | 1                          | TRSTE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | DI                      | <b>Tristate Output Enable.</b> When held High, forces all output pins to high-Z (tri-state). When held Low, Bipolar I/O mode is selected. In this mode, the framer interface is bipolar (TPOS/TNEG and RPOS/RNEG), and the B8ZS/HDB3 encoders are disabled. When clocked by MCLK, Unipolar I/O mode is selected. In this mode, the framer interface is unipolar (TDATA and RDATA), and the TNEG and RNEG pins are re-mapped. The TNEG pins are re-mapped as Encoder Enables (ECE) to individually enable the B8ZS/HDB3 encoder/decoder for each port. The RNEG pins are re-mapped as Bipolar Violation (BPV) indicators to report BPVs detected at the respective ports. |

| 40                 | 2                          | TCLK0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | DI                      | <b>Transmit Clock - Port 0.</b> 1.544 MHz for T1, 2.048 MHz for E1. The port 0 transmit data inputs are sampled on the falling edge of TCLK0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |