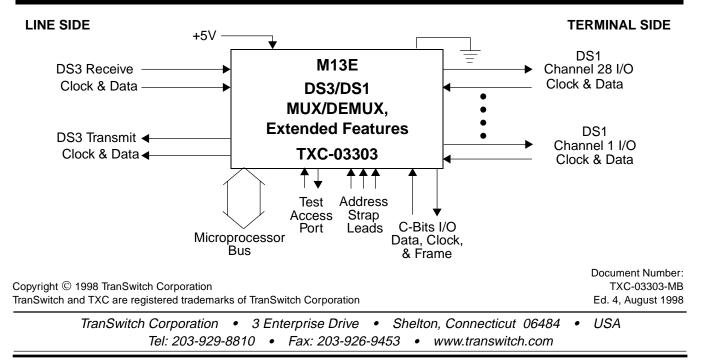

M13E Device **RAN SWITCH**<sup>®</sup> DS3/DS1 MUX/DEMUX, Extended Features TXC-03303

DATA SHEET

#### **FEATURES**

- Multiplexes/demultiplexes 28 DS1 signals to/from a DS3 signal.

- M13 or C-bit parity mode operation

- FEBE, C, or P-bit parity error insertion capability

- DS3 idle signal generators

- DS1 idle signal (QRS, AIS or ESF) generators

- DS3 LOS, LOF, P-bit parity, C-bit parity, AIS and idle detectors

- Receive or transmit DS1 LOS detectors

- DS2 LOF detectors

- External interface for receiving 14 C-bits and transmitting either 13 or 14 C-bits based on a control bit setting

- DS3 and DS2 X-bit access

- DS3 transmit and receive selectable AIS generation and detection

- Supports Intel, Motorola, or multiplexed microprocessor interfaces.

- DS2 Tx/Rx X-bit control/status

- Test Access Port for boundary scan

- Single +5V, ±5% power supply

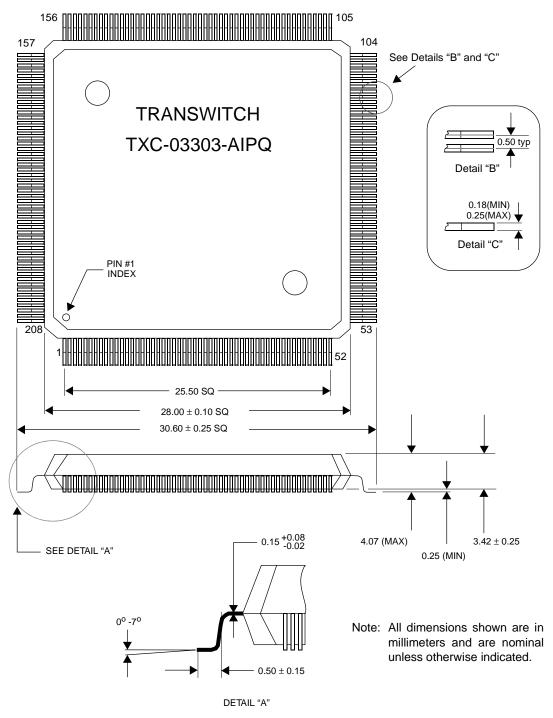

- 208-pin plastic quad flat package

#### DESCRIPTION

The M13E CMOS VLSI device provides the functions needed to multiplex and demultiplex 28 independent DS1 signals to and from a DS3 signal with either an M13 or Cbit frame format. It includes some extended features relative to the M13 device. The M13E line side signals typically interface with a TranSwitch ART or ARTE device, DS3LIM-SN Module or other line circuitry; terminal side signals interface with commercially available DS1 line interface devices. A DS1 line interface device containing an internal dejitter buffer is recommended.

The M13E provides an external transmit (13 or 14 bits) and receive (14 bits) interface for the 21 C-bits while operating in the C-bit parity mode. The FEAC channel (C3) can be accessed via the external interface or the M13E memory. The M13E memory map contains 35, 8-bit register locations for software control, performance counters, and alarm reporting. The microprocessor interface provides for connection to an Intel or Motorola-compatible microprocessor, or for use of a multiplexed address/data bus.

#### APPLICATIONS

- Single-board M13 multiplexer

- Compact add/drop mux

- Fractional T3

- DCS and EDSX

- CSU/DSU

TRANSWITCH

#### TABLE OF CONTENTS

| Section                                                | <u>Page</u> |

|--------------------------------------------------------|-------------|

| Block Diagram                                          | 5           |

| Block Diagram Description                              | 5           |

| Pin Diagram                                            | 8           |

| Pin Descriptions                                       |             |

| Absolute Maximum Ratings and Environmental Limitations | 17          |

| Thermal Characteristics                                | 17          |

| Power Requirements                                     | 17          |

| Input, Output and I/O Parameters                       |             |

| Timing Characteristics                                 | 20          |

| Operation                                              | 31-55       |

| Memory Map                                             | 31          |

| Memory Map Descriptions                                |             |

| Initialization Sequence                                | 48          |

| System Considerations                                  | 48          |

| Throughput Delays                                      | 48          |

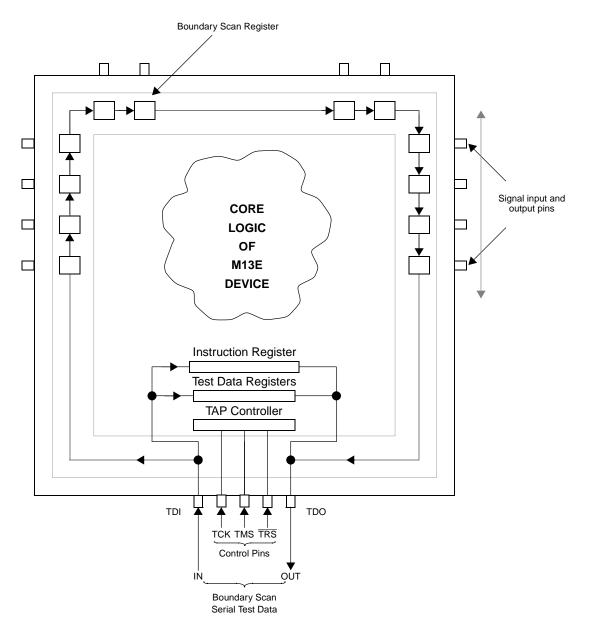

| Test Access Port                                       |             |

| Package Information                                    | 56          |

| Ordering Information                                   | 57          |

| Related Products                                       | 57          |

| Standards Documentation Sources                        |             |

| List of Data Sheet Changes                             | 60          |

| Documentation Update Registration Form*                | 65          |

\* Please note that TranSwitch provides documentation for all of its products. Customers who are using a TranSwitch Product, or planning to do so, should register with the TranSwitch Marketing Department to receive relevant updated and supplemental documentation as it is issued. They should also contact the Applications Engineering Department to ensure that they are provided with the latest available information about the product, especially before undertaking development of new designs incorporating the product.

TRANSWITCH

#### LIST OF FIGURES

| Figure 1.  | M13E TXC-03303 Block Diagram                               | 5  |

|------------|------------------------------------------------------------|----|

| Figure 2.  | C-Bit Assignments                                          | 7  |

| Figure 3.  | M13E TXC-03303 Pin Diagram                                 | 8  |

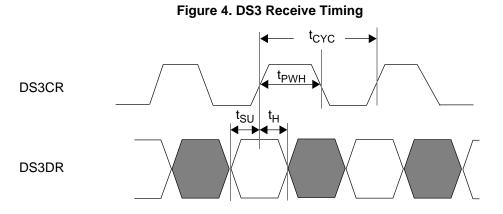

| Figure 4.  | DS3 Receive Timing                                         |    |

| Figure 5.  | DS3 Transmit Timing                                        | 20 |

| Figure 6.  | DS1 Receive Timing                                         | 21 |

| Figure 7.  | DS1 Transmit Timing                                        | 21 |

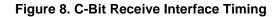

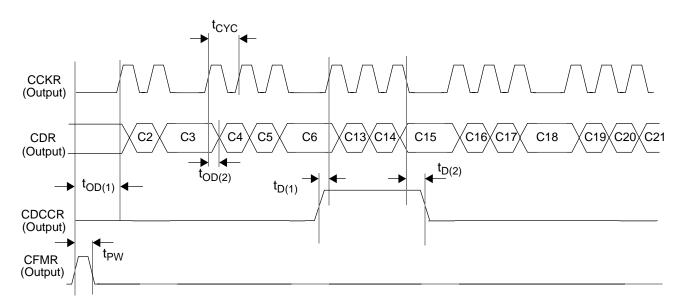

| Figure 8.  | C-Bit Receive Interface Timing                             | 22 |

| Figure 9.  | C-Bit Transmit Interface Timing                            |    |

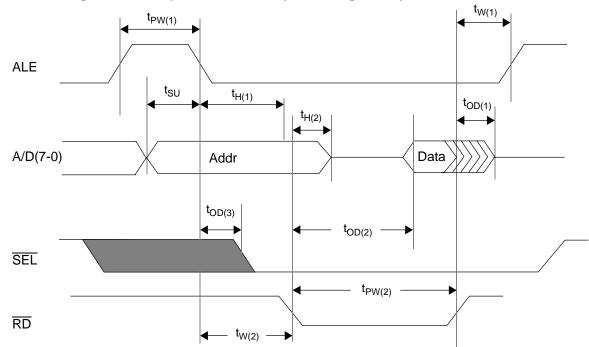

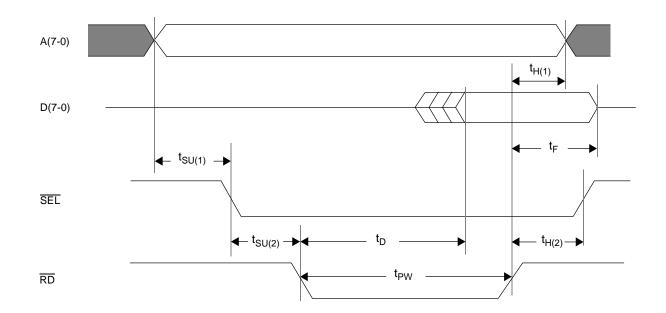

| Figure 10. | Microprocessor Read Cycle Timing - Multiplexed Interface . | 24 |

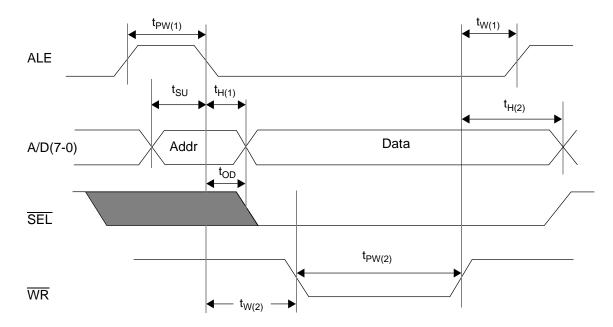

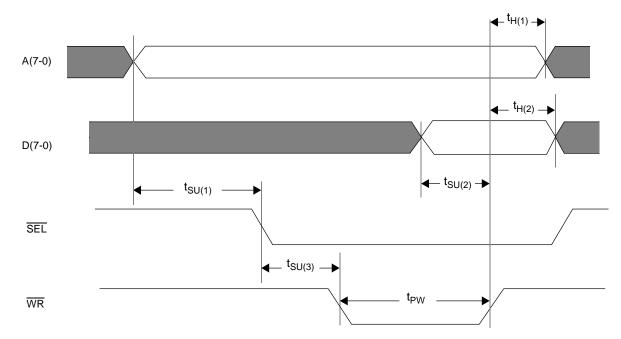

| Figure 11. | Microprocessor Write Cycle Timing - Multiplexed Interface  |    |

| Figure 12. | Microprocessor Read Cycle Timing - Intel Interface         |    |

| Figure 13. | Microprocessor Write Cycle Timing - Intel Interface        | 27 |

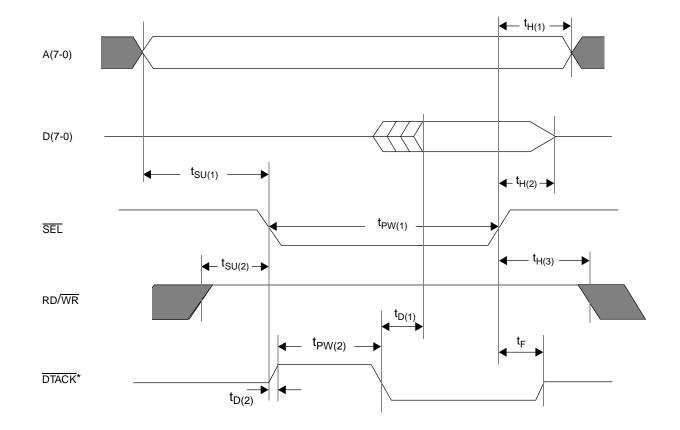

| Figure 14. | Microprocessor Read Cycle Timing - Motorola Interface      |    |

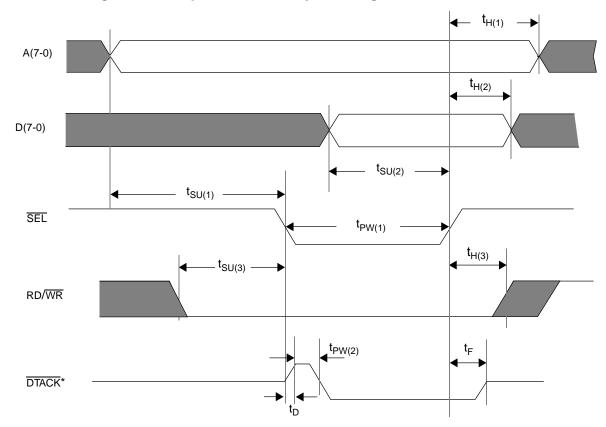

| Figure 15. | Microprocessor Write Cycle Timing - Motorola Interface     |    |

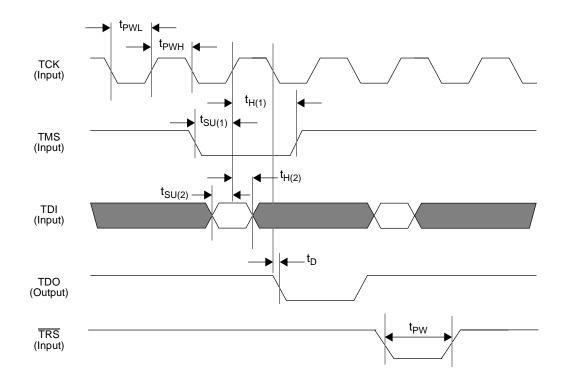

| Figure 16. | Boundary Scan Timing                                       |    |

| Figure 17. | Boundary Scan Schematic                                    | 50 |

| Figure 18. | M13E TXC-03303 208-pin Plastic Quad Flat Package           | 56 |

TRANSWITCH

This page has been intentionally left blank.

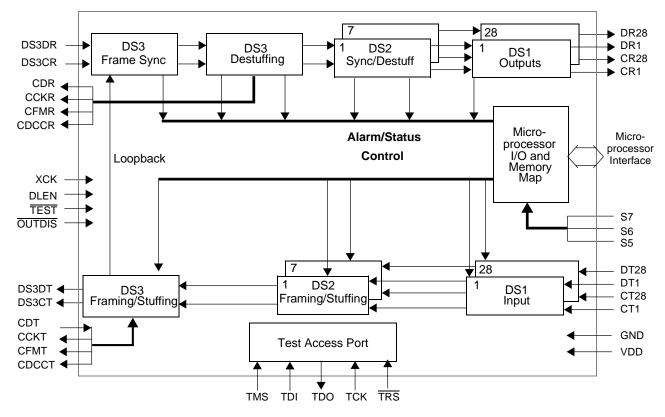

**BLOCK DIAGRAM**

ІТСН

Figure 1. M13E TXC-03303 Block Diagram

#### **BLOCK DIAGRAM DESCRIPTION**

Figure 1 shows a simplified block diagram of the M13E and its signal leads. In the receive direction, DS3 data (DS3DR) is clocked into the M13E on positive transitions of the DS3 input clock (DS3CR). The data and clock signals may be derived from any line interface device such as TranSwitch's ART, ARTE or DS3LIM-SN, or from other line circuitry.

The DS3 Frame Sync Block searches for and locks to the DS3 frame, as specified in Bellcore's TR-TSY-000499, "Transport System Generic Requirements," and in ANSI's T1.107-1988 and supplement T1.107a-1990. The M13E receiver monitors the DS3 signal for out of frame, loss of signal, a DS3 AIS, DS3 idle signal, P-bit parity, the state of the X-bits, and loss of clock. The DS3 AIS detection mechanism is software selectable, with a choice of six detectors. These range from full compliance to T1.107/107a to unframed all ones AIS detection. Control bits are also provided in memory which allows all, some of, or none of the DS3 alarms to cause the insertion of AIS into the receive DS1 channels.

In the M13 mode, destuffing from DS3 to DS2 is performed based on the states of the C-bits in the DS3 subframes. If two or three of the C-bits in a subframe are ones, the associated stuff bit is interpreted as being a stuff bit and is removed from the data stream and discarded.

In the C-bit parity mode, the C-bits are allocated for network performance. The M13E performs Far End Alarm and Control (FEAC) detection, C-bit parity error detection, and Far End Block Error (FEBE) detection. FEAC loopback requests and alarm/status information is provided in the memory map. In addition, the states of 14 C-bits (C2, C3, C4, C5, C6, C13, C14, C15, C16, C17, C18, C19, C20, and C21) are provided at a serial interface (CDR), along with an output clock signal (CCKR), framing pulse (CFMR), and data link indicator pulse (CDCCR). The data link indicator pulse identifies the location of the data link bits, C13, C14, and C15.

The M13E synchronizes and extracts the 28 DS1 channels from the seven DS2 channels. Each of the DS2 channels is monitored for out of frame. The M13E may generate AIS in each of the DS1 signal tributaries corresponding to the DS2 channel(s) that lost frame, depending on the DS1 AIS alarm insertion control bits. DS2 to DS1 destuffing is based on the states of the three C-bits in each DS2 subframe. If two or three of the C-bits in one of the DS2 subframes are ones, the stuff bit for that subframe is discarded. In the M13 mode, the DS2 C-bits or stuffing bits are used for DS1 remote loopback requests. The M13E provides control bits in the memory map for selecting the remote loopback detection mechanism. The destuffing operation is still active during loopback request and operation. In addition to DS2 synchronization, destuffing, and remote loopback detection, the M13E also extracts the seven DS2 X-bits.

An option is provided that allows the received or transmitted DS1 channels to be monitored for loss of signal. Receive data for each of the DS1 channels (DRn) is clocked out of the M13E on positive transitions of the associated clock signal (CRn). In addition, the M13E provides a stable DS1 clock signal for the data signals received during AIS periods.

In the transmit direction, DS1 transmit data (DTn) is clocked into the M13E on positive transitions of the clock input (CTn) for each of the 28 DS1 channels. A DS1 Input Block, which consists of a FIFO and supporting logic, is provided for each DS1 channel. Under software control, the M13E can invert the transmit data signals, or the clock signals, for all 28 DS1 channels. The data inversion feature provides compatibility with certain T1 line interface devices, while the clock inversion feature allows back-to-back M13 operation.

The DS1 Input Block is also used to insert one of three idle patterns from a common generator into a DS1 bit stream, under software control. The selection of the idle pattern is common to all 28 DS1 channels. The idle patterns are: a QRS, an Extended Super Frame DS1 (ESF) format with all ones in channels 1 through 28, and an AIS format (all ones).

Each DS1 signal is multiplexed into the respective DS2 frame, with the stuff bits inserted based on the fill level of an internal FIFO. When the fill of the FIFO drops below half full, a stuff bit is inserted into the DS1 bit stream in the DS2 signal. The DS2 signal is formed by combining four DS1 signals. In each frame there are 287 data bit positions and one stuff bit per DS1 channel (for a DS1 total of 1152 bits) and 24 overhead bits, for a frame total of 1176 bits. The overhead bits are used for framing, X-bit channel and stuff control.

The DS3 signal is partitioned into M-frames of 4760 bits each. The M-frames are divided into seven M-subframes having 680 bits each. Each M-subframe is further divided into eight blocks of 85 bits each. Each block uses 84 bits for payload and one bit for frame overhead. There are 56 overhead bits in each M-frame: the M-frame alignment uses three bits, the M-subframe alignment (F-bits) uses 28 bits, 21 bits are defined as C-bits, two bits are assigned for parity, and two bits are assigned for the X-bit channel.

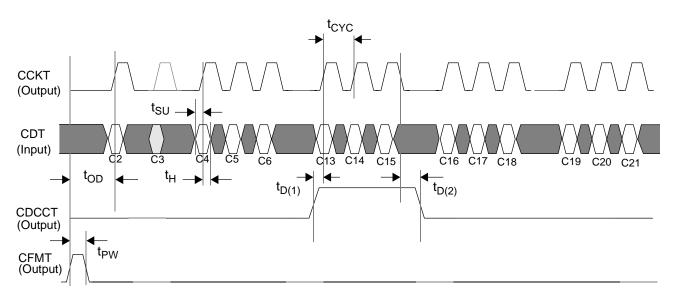

The DS3 frame is constructed and timed according to the operating mode, i.e., C-bit parity mode or M13 mode. In the C-bit parity mode, all seven of the DS2 stuff bits are fixed as stuff, resulting in 7 pseudo DS2 frames of 671 bits per DS2 frame in each DS3 frame, for a DS2 rate of 6.3062723 Mbit/s. Since stuffing always occurs, the 21 C-bits are assigned for other functions, as shown in Figure 2. A C-bit interface is provided for transmitting 13 or 14 C-bits (C2, C3-depending on the state of bit 7 of register 19H (C3CLKI), C4, C5, C6, C13, C14, C15, C16, C17, C18, C19, C20, C21). The external transmit C-bit interface consists of a serial data input (CDT), an output clock (CCKT), a data link indicator pulse (CDCCT), and an output framing pulse (CFMT). The data link indicator pulse identifies the location of the three data link bits, C13, C14, and C15. In addition, a control bit is provided in the memory map which enables the M13E to generate an extra clock cycle during the C3 bit time. A receive C-bit interface is provided for extraction of 14 C-bits (C2, C3, C4, C5, C6, C13, C14, C15, C16, C17, C18, C19, C20, C21). The receive C-bit interface consists of a serial data output (CDR), an output clock (CCKR), a data link indicator pulse (CDCCR), and an output framing pulse (CFMR). The data link indicator pulse (CDCCR), and an output framing pulse (CFMR). The data link indicator pulse identifies the location of the three data link framing pulse (CFMR). The data link indicator pulse identifies the location of the three data link indicator pulse (CFMR). The data link indicator pulse identifies the location of the three data link framing pulse (CFMR). The data link indicator pulse identifies the location of the three data link C-bits, C13, C14, and C15.

| C1   | C2*  | C3** | C1 = C-bit parity mode<br>C2 = Reserved<br>C3 = Far End Alarm & Control (FEAC) |

|------|------|------|--------------------------------------------------------------------------------|

| C4*  | C5*  | C6*  | Not defined, set to one                                                        |

| C7   | C8   | C9   | C-Parity bits                                                                  |

| C10  | C11  | C12  | Far End Block Error (FEBE)                                                     |

| C13* | C14* | C15* | Maintenance data link (28 kbit/s)                                              |

| C16* | C17* | C18* | Not defined, set to one                                                        |

| C19* | C20* | C21* | Not defined, set to one                                                        |

WITCH

\*These bits are provided at the C-bit interface in the C-bit mode

\*\* Always provided at the receive C-bit interface in the C-bit mode

#### Figure 2. C-Bit Assignments

Of the eight remaining C-bits, C1 is used as an identification channel; C3 is defined as a Far End Alarm and Control (FEAC) bit and is controlled via the memory map; C7, C8, and C9 are used for C-bit parity; and the remaining three bits, C10, C11, and C12, are used to transmit a FEBE indication. A FEBE is automatically transmitted if a C-bit parity error or framing error is received.

Fixed DS2 to DS3 stuffing is used for M23 multiplexing at a rate of seven stuffs for every 18 DS3 stuff opportunities. This yields a DS2 frequency of +2.6 ppm above the desired frequency of 6.312 Mbit/s. After adding this to the tolerance of the DS3 clock signal,  $\pm$ 20 ppm, the frequency is still within the  $\pm$ 32 ppm allowed for a DS2 signal.

Under software control, the M13E can generate DS3 idle and AIS signals, and loop back the transmitted DS3 signal to the receiver for test purposes. Other functions provided by the M13E include: DS1 loopback capability, and transmit clock failure protection. The microprocessor interface is selectable via two external hardware straps. Interface options are: Multiplexed, Intel compatible, or Motorola compatible.

TRANSWITCH<sup>®</sup>

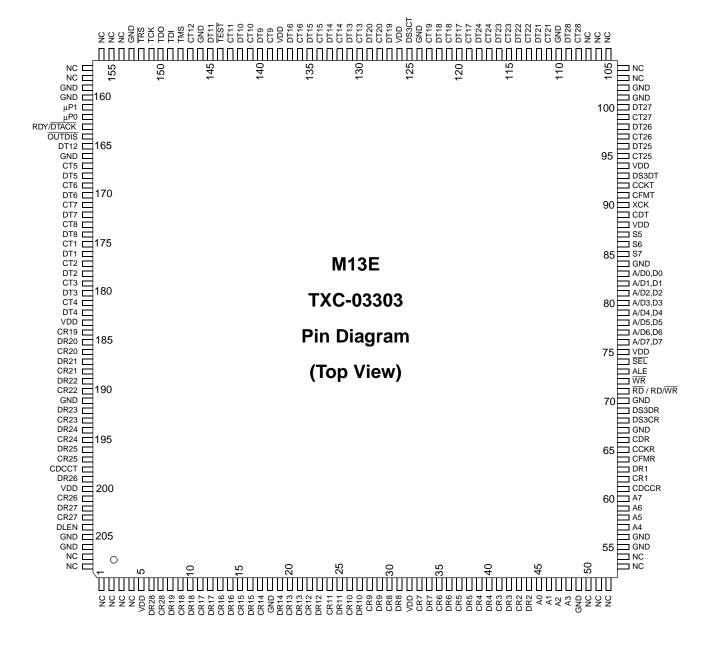

#### **PIN DIAGRAM**

Figure 3. M13E TXC-03303 Pin Diagram

#### **PIN DESCRIPTIONS**

#### POWER SUPPLY, GROUND, AND NO CONNECT

| Symbol | Pin No.                                                                                         | I/O/P* | Туре | Name/Function                                                                                                                                                                                        |

|--------|-------------------------------------------------------------------------------------------------|--------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VDD    | 5, 32, 75, 88, 94,<br>126, 138, 183, 200                                                        | Р      |      | <b>VDD:</b> +5-volt supply voltage, ±5%.                                                                                                                                                             |

| GND    | 18, 49, 55, 56, 67, 70,<br>84, 101, 102, 110, 124,<br>146, 153, 159, 160,<br>166, 191, 205, 206 | Ρ      |      | Ground: 0 volts reference                                                                                                                                                                            |

| NC     | 1-4, 50-54, 103-107,<br>154-158, 207, 208                                                       |        |      | <b>No Connect:</b> NC pins are not to be con-<br>nected, not even to another NC pin, but must<br>be left floating. Connection of NC pins may<br>impair performance or cause damage to the<br>device. |

\*Note: I = Input; O = Output; P = Power

#### DS1 RECEIVE INTERFACES

| Symbol | Pin No. | I/O/P | Type * | Name/Function                                             |

|--------|---------|-------|--------|-----------------------------------------------------------|

| CR1    | 62      | 0     | TTL2mA | Receive Clock Channels 1 - 28: Receive data is            |

| CR2    | 43      |       |        | clocked out of the M13E on positive transitions. The      |

| CR3    | 41      |       |        | clock for the first DS1 channel corresponds to CR1, while |

| CR4    | 39      |       |        | the clock for the last DS1 channel corresponds to CR28.   |

| CR5    | 37      |       |        | The DS1 clock signals are derived from the DS3 clock      |

| CR6    | 35      |       |        | signal (DS3CR). During periods of DS3/DS2 out of frame    |

| CR7    | 33      |       |        | or AIS, the M13E provides a DS1 clock signal for clock-   |

| CR8    | 30      |       |        | ing out AIS which is derived from the XCK clock (pin 90). |

| CR9    | 28      |       |        |                                                           |

| CR10   | 26      |       |        |                                                           |

| CR11   | 24      |       |        |                                                           |

| CR12   | 22      |       |        |                                                           |

| CR13   | 20      |       |        |                                                           |

| CR14   | 17      |       |        |                                                           |

| CR15   | 15      |       |        |                                                           |

| CR16   | 13      |       |        |                                                           |

| CR17   | 11      |       |        |                                                           |

| CR18   | 9       |       |        |                                                           |

| CR19   | 184     |       |        |                                                           |

| CR20   | 186     |       |        |                                                           |

| CR21   | 188     |       |        |                                                           |

| CR22   | 190     |       |        |                                                           |

| CR23   | 193     |       |        |                                                           |

| CR24   | 195     |       |        |                                                           |

| CR25   | 197     |       |        |                                                           |

| CR26   | 201     |       |        |                                                           |

| CR27   | 203     |       |        |                                                           |

| CR28   | 7       |       |        |                                                           |

\*See Input, Output and I/O Parameters section below for Type definitions.

| Symbol | Pin No. | I/O/P | Type * | Name/Function                                       |

|--------|---------|-------|--------|-----------------------------------------------------|

| DR1    | 63      | 0     | TTL2mA | Receive Data DS1 Channels 1 - 28: Demultiplexed DS1 |

| DR2    | 44      |       |        | channels. The first DS1 channel corresponds to DR1, |

| DR3    | 42      |       |        | while the last DS1 channel corresponds to DR28.     |

| DR4    | 40      |       |        |                                                     |

| DR5    | 38      |       |        |                                                     |

| DR6    | 36      |       |        |                                                     |

| DR7    | 34      |       |        |                                                     |

| DR8    | 31      |       |        |                                                     |

| DR9    | 29      |       |        |                                                     |

| DR10   | 27      |       |        |                                                     |

| DR11   | 25      |       |        |                                                     |

| DR12   | 23      |       |        |                                                     |

| DR13   | 21      |       |        |                                                     |

| DR14   | 19      |       |        |                                                     |

| DR15   | 16      |       |        |                                                     |

| DR16   | 14      |       |        |                                                     |

| DR17   | 12      |       |        |                                                     |

| DR18   | 10      |       |        |                                                     |

| DR19   | 8       |       |        |                                                     |

| DR20   | 185     |       |        |                                                     |

| DR21   | 187     |       |        |                                                     |

| DR22   | 189     |       |        |                                                     |

| DR23   | 192     |       |        |                                                     |

| DR24   | 194     |       |        |                                                     |

| DR25   | 196     |       |        |                                                     |

| DR26   | 199     |       |        |                                                     |

| DR27   | 202     |       |        |                                                     |

| DR28   | 6       |       |        |                                                     |

#### **DS1 TRANSMIT INTERFACES**

| Symbol     | Pin No. | I/O/P | Туре | Name/Function                                            |

|------------|---------|-------|------|----------------------------------------------------------|

| CT1        | 175     | I     | TTL  | Transmit DS1 Clocks Channels 1 - 28: Transmit data is    |

| CT2        | 177     |       |      | clocked into the M13E on positive transitions. The clock |

| CT3        | 179     |       |      | for the first DS1 channel corresponds to CT1, while the  |

| CT4        | 181     |       |      | clock for the last DS1 channel corresponds to CT28.      |

| CT5        | 167     |       |      |                                                          |

| CT6        | 169     |       |      |                                                          |

| CT7        | 171     |       |      |                                                          |

| CT8        | 173     |       |      |                                                          |

| CT9        | 139     |       |      |                                                          |

| CT10       | 141     |       |      |                                                          |

| CT11       | 143     |       |      |                                                          |

| CT12       | 147     |       |      |                                                          |

| CT13       | 130     |       |      |                                                          |

| CT14       | 132     |       |      |                                                          |

| CT15       | 134     |       |      |                                                          |

| CT16       | 136     |       |      |                                                          |

| (continued |         |       |      |                                                          |

| next page) |         |       |      |                                                          |

#### M13E TXC-03303

## TRANSWITCH

| Symbol | Pin No. | I/O/P | Туре | Name/Function                                          |

|--------|---------|-------|------|--------------------------------------------------------|

| CT17   | 119     |       | TTL  | Transmit DS1 Clocks (continued from previous page)     |

| CT18   | 121     |       |      |                                                        |

| CT19   | 123     |       |      |                                                        |

| CT20   | 128     |       |      |                                                        |

| CT21   | 111     |       |      |                                                        |

| CT22   | 113     |       |      |                                                        |

| CT23   | 115     |       |      |                                                        |

| CT24   | 117     |       |      |                                                        |

| CT25   | 95      |       |      |                                                        |

| CT26   | 97      |       |      |                                                        |

| CT27   | 99      |       |      |                                                        |

| CT28   | 108     |       |      |                                                        |

| DT1    | 176     | I     | TTL  | Transmit Data DS1 Channels 1 - 28: The first DS1       |

| DT2    | 178     |       |      | channel corresponds to DT1, while the last DS1 channel |

| DT3    | 180     |       |      | corresponds to DT28.                                   |

| DT4    | 182     |       |      |                                                        |

| DT5    | 168     |       |      |                                                        |

| DT6    | 170     |       |      |                                                        |

| DT7    | 172     |       |      |                                                        |

| DT8    | 174     |       |      |                                                        |

| DT9    | 140     |       |      |                                                        |

| DT10   | 142     |       |      |                                                        |

| DT11   | 145     |       |      |                                                        |

| DT12   | 165     |       |      |                                                        |

| DT13   | 131     |       |      |                                                        |

| DT14   | 133     |       |      |                                                        |

| DT15   | 135     |       |      |                                                        |

| DT16   | 137     |       |      |                                                        |

| DT17   | 120     |       |      |                                                        |

| DT18   | 122     |       |      |                                                        |

| DT19   | 127     |       |      |                                                        |

| DT20   | 129     |       |      |                                                        |

| DT21   | 112     |       |      |                                                        |

| DT22   | 114     |       |      |                                                        |

| DT23   | 116     |       |      |                                                        |

| DT24   | 118     |       |      |                                                        |

| DT25   | 96      |       |      |                                                        |

| DT26   | 98      |       |      |                                                        |

| DT27   | 100     |       |      |                                                        |

| DT28   | 109     |       |      |                                                        |

#### **DS3 INTERFACE**

| Symbol | Pin No. | I/O/P | Туре   | Name/Function                                                                                                                                                                                                                                                                                                                                  |

|--------|---------|-------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DS3CR  | 68      | I     | CMOS   | <b>DS3 Receive Clock:</b> A 44.736 MHz clock that is used to clock DS3 data into the M13E. This clock is used as the time base for demultiplexing the DS3 data. When the loop timing feature is active (a one written into bit 3 (LPTIME) in 02H), or when the DS3 external transmit clock (XCK) fails, this clock becomes the transmit clock. |

| DS3DR  | 69      | I     | CMOS   | <b>DS3 Receive Data:</b> Receive 44.736 Mbit/s data is clocked into the M13E on positive transitions of the receive clock (DS3CR).                                                                                                                                                                                                             |

| DS3CT  | 125     | 0     | TTL8mA | <b>DS3 Transmit Clock:</b> A 44.736 MHz clock which is derived from the external transmit clock input signal (XCK). It is used to clock DS3 data from the M13E.                                                                                                                                                                                |

| DS3DT  | 93      | 0     | TTL8mA | <b>DS3 Transmit Data:</b> Transmit C-bit parity or M13 format-<br>ted DS3 data is clocked out of the M13E on positive tran-<br>sitions of the transmit clock (DS3CT).                                                                                                                                                                          |

\_\_\_\_\_

#### MICROPROCESSOR INTERFACE

| Symbol              | Pin No.        | I/O/P | Туре   | Name/Function                                                                                                                                                                                                                                                                                                                                                                   |

|---------------------|----------------|-------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A(7-4)<br>A(3-0)    | 60-57<br>48-45 | I     | TTLp   | Address Bus (Intel/Motorola): These are active high<br>address line inputs that are used by the microprocessor<br>for accessing the M13E registers for a read/write cycle.<br>A7 is the most significant bit. These leads are disabled<br>when the multiplexed interface is selected.                                                                                           |

| A/D (7-0)<br>D(7-0) | 76-83          | I/O   | TTL8mA | Address/Data Bus (Multiplexed), Data Bus (Intel/<br>Motorola): For a multiplexed interface, these bidirec-<br>tional leads constitute address/data buses for accessing<br>the M13E registers. For either the Intel or Motorola inter-<br>face, these bidirectional leads are used for transferring<br>data. The most significant bit is A/D7 or D7.                             |

| SEL                 | 74             | I     | TTL    | <b>Select:</b> A low enables data transfers between the micro-<br>processor and the M13E registers during a read/write<br>bus cycle.                                                                                                                                                                                                                                            |

| RD/WR               | 71             | I     | TTL    | <b>Read (Intel/Multiplexed) or Read/Write (Motorola):</b><br>Intel/Multiplexed - An active low signal generated by the<br>microprocessor for reading the M13E register locations.<br>Motorola - An active high signal generated by the micro-<br>processor for reading the M13E register locations. An<br>active low signal is used to write to the M13E register<br>locations. |

| Symbol        | Pin No.    | I/O/P | Туре   |                                                                                                                                                                                                 | Na                                                                        | me/Function                                                                                                                                                                                                                                         |

|---------------|------------|-------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ALE           | 73         | I     | TTL    | Address Latch Enable (Multiplexed): An active high<br>enable signal generated by the microprocessor. The fall-<br>ing transition is used to store an address during a read/<br>write bus cycle. |                                                                           |                                                                                                                                                                                                                                                     |

| WR            | 72         | I     | TTL    | low signal gei                                                                                                                                                                                  | nerated by                                                                | ed): Intel/Multiplexed - An active<br>y the microprocessor for writing to<br>tions. Motorola - not used.                                                                                                                                            |

| RDY/<br>DTACK | 163        | Ο     | TTL8mA | ola): Intel - TI<br>Intel micropro<br>resistor is req<br>low signal ind<br>valid. During                                                                                                        | ne M13E<br>cessor is<br>uired. Mo<br>icates the<br>a write bu<br>ceptance | Transfer Acknowledge (Motor-<br>is always ready. Connection to ar<br>optional. If connected, a pull-up<br>torola - During a read bus cycle, a<br>information on the data bus is<br>s cycle, a low signal acknowl-<br>of data. A pull-up resistor is |

| μΡ0<br>μΡ1    | 162<br>161 | I     | TTLp   |                                                                                                                                                                                                 | or interfa                                                                | face Type Select: The type of ce selected by these two bits is v:                                                                                                                                                                                   |

|               |            |       |        | μP1                                                                                                                                                                                             | μP0                                                                       | Interface                                                                                                                                                                                                                                           |

|               |            |       |        | 1                                                                                                                                                                                               | 1                                                                         | Multiplexed <sup>1</sup>                                                                                                                                                                                                                            |

|               |            |       |        | 1                                                                                                                                                                                               | 0                                                                         | Multiplexed <sup>2</sup>                                                                                                                                                                                                                            |

|               |            |       |        | 0                                                                                                                                                                                               | 0                                                                         | Intel Compatible                                                                                                                                                                                                                                    |

|               |            |       |        | 0                                                                                                                                                                                               | 1                                                                         | Motorola Compatible                                                                                                                                                                                                                                 |

|               |            |       |        | address/data<br>and write.<br>The Intel com                                                                                                                                                     | leads, se<br>patible in<br>leads, eig                                     | ce consists of eight bidirectional<br>lect, address latch enable, read,<br>terface (80X86 family) consists o<br>ght bidirectional data leads, select                                                                                                |

|               |            |       |        | sists of eight                                                                                                                                                                                  | address l                                                                 | le interface (680X0 family) con-<br>eads, eight bidirectional data<br>e, and data transfer acknowledge                                                                                                                                              |

Note 1: When μP1 and μP0 are both set to 1 only registers 00H - 1FH are accessible, to maintain backwards compatibility with previous devices. Address straps S5 - S7 are active.

Note 2: When  $\mu$ P1 = 1 and  $\mu$ P0 = 0 all registers are accessible. Only address straps S6 and S7 are active.

| <b>TRANSWITCH</b> <sup>•</sup> |

|--------------------------------|

|                                |

| Symbol | Pin No.    | I/O/P | Туре | Name/Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|--------|------------|-------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| S(7-5) | 85, 86, 87 | I     | TTLp | Address Straps: When the Intel, Motorola, or Multiplexed ( $\mu$ P1 = 1 and $\mu$ P0 = 0) microprocessor interfaces are selected, the two address straps, S7 and S6, allow the M13E to be partitioned as a segment of memory. The straps define the address offset of the device. The address register is partitioned as shown below. The data register pointed to by the 6 LSBs is only accessed if the 2 MSBs match the address straps.Address register partition for Intel, Motorola, or Multiplexed ( $\mu$ P1 = 1 and $\mu$ P0 = 0) microprocessor interfaces:Bit 76M13ERegisterAddressAddressWhen the multiplexed microprocessor interface is selected, by setting $\mu$ P1 = 1 and $\mu$ P0 = 1, the three address straps, S7, S6, and S5, allow the M13E to be partitioned as a segment of memory. The straps define the offset of the device. The address register is partitioned as shown below. The data register pointed to by the five LSBs is only accessed if the three MSBs match the address straps.Address register partition for the multiplexed microprocessor interface to by the five LSBs is only accessed if the three MSBs match the address straps.Address register partition for the multiplexed microprocessor interface when $\mu$ P1 = 1 and $\mu$ P0 = 1:Bit 76M13ERegisterAddressAddress |

#### **RECEIVE C-BIT INTERFACE**

| Symbol | Pin No. | I/O/P | Туре   | Name/Function                                                                                                                                                                                                                                                                                                                                                                                               |

|--------|---------|-------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CCKR   | 65      | 0     | TTL8mA | <b>Receive C-Bit Clock:</b> A gapped clock signal is provided for clocking out the selected receive C-bit data. Data (CDR) is clocked out on positive transitions.                                                                                                                                                                                                                                          |

| CDR    | 66      | 0     | TTL8mA | <b>Receive C-Bit Data:</b> The following C-bits are provided at this interface: C2, C3, C4, C5, C6, C13, C14, C15, C16, C17, C18, C19, C20, and C21.                                                                                                                                                                                                                                                        |

| CFMR   | 64      | 0     | TTL8mA | <b>Receive C-Bit Framing Pulse:</b> This positive framing pulse occurs prior to the C2 bit.                                                                                                                                                                                                                                                                                                                 |

| CDCCR  | 61      | 0     | TTL8mA | <b>Receive Data Link Indication:</b> A positive pulse that identifies the location of the three data link C-bits (C13, C14, and C15). The receive C-bit clock (CCKR) may be and-gated with this signal to provide a gapped data link clock signal for loading the three C-bits from the C-bit data (CDR) into external circuitry. This signal is enabled by placing a high on the signal lead labeled DLEN. |

#### TRANSMIT C-BIT INTERFACE

| Symbol | Pin No. | I/O/P | Туре   | Name/Function                                                                                                                                                                                                                                                                                                                  |

|--------|---------|-------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ССКТ   | 92      | 0     | TTL8mA | <b>Transmit C-Bit Clock:</b> A gapped clock signal is provided for clocking in selected transmit C-bit data (CDT). Data is clocked into the M13E on positive transitions.                                                                                                                                                      |

| CDT    | 89      | I     | TTL    | <b>Transmit C-Bit Data:</b> The transmit gapped clock (CCKT) is provided for clocking in the following C-bits: C2, C3 (depending on the setting of bit 7 of register 19H, C3CLKI), C4, C5, C6, C13, C14, C15, C16, C17, C18, C19, C20, and C21. An unused C-bit should be transmitted as a one.                                |

| CFMT   | 91      | 0     | TTL8mA | <b>Transmit C-Bit Framing Pulse:</b> This positive framing pulse occurs prior to the C2 bit.                                                                                                                                                                                                                                   |

| CDCCT  | 198     | 0     | TTL8mA | <b>Transmit Data Link Indication:</b> A positive pulse that identifies the location of the three data link C-bits (C13, C14, and C15). The transmit C-bit clock (CCKT) may be and-gated with this signal to provide a gapped data link clock signal. This signal is enabled by placing a high on the signal lead labeled DLEN. |

#### **CONTROL PINS**

| Symbol | Pin No. | I/O/P | Туре | Name/Function                                                                                                                                                                                                                                                                                                      |

|--------|---------|-------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OUTDIS | 164     | I     | TTLp | <b>Outputs Disable:</b> A low causes all M13E outputs and bidirectional signal leads to be set to a high impedance state for test purposes except the CDCCR and CDCCT pins. The CDCCR and CDCCT pins can be tri-stated by applying a low to the DLEN pin. This lead is provided with an internal pull-up resistor. |

| DLEN   | 204     | I     | TTLp | <b>Data Link Enable:</b> Normally left open. A high enables the transmit and receive data link indication signals, CDCCT and CDCCR. The data link indication signals identify the location of the three data link C-bits (C13, C14, and C15).                                                                      |

| TEST   | 144     | I     | TTLp | TranSwitch Test Pin: Leave open.                                                                                                                                                                                                                                                                                   |

#### EXTERNAL CLOCK

| Symbol | Pin No. | I/O/P | Туре | Name/Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|--------|---------|-------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ХСК    | 90      | I     | CMOS | <b>External Transmit Clock:</b> An external clock having a frequency of 44.736 MHz and a stability of $\pm 20$ ppm is required to meet DSX-3 cross-connect requirements. The clock duty cycle should be kept to $(50 \pm 5)$ %. The transmit clock is also used to operate the M13E microprocessor interface. The M13E monitors this clock for transitions. When a clock failure is detected, the M13E automatically switches to the receive clock (DS3CR) for multiplexer and microprocessor operation. Receive loop timing (a one written to bit 3, LPTIME, in 02H) also causes the receive clock to become the transmit clock. |

#### **TEST ACCESS PORT**

| Symbol | Pin No. | I/O/P | Туре   | Name/Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|--------|---------|-------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TMS    | 148     | I     | TTLp   | <b>Test Mode Select:</b> The signal present on this lead is used to control boundary scan test operations.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| TDI    | 149     | Ι     | TTLp   | <b>Test Data Input:</b> Serial data input for boundary scan test messages.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| TDO    | 150     | 0     | TTL8mA | <b>Test Data Output:</b> Serial data output whose information is clocked out on negative transitions of TCK.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| тск    | 151     | I     | TTLp   | <b>Test Clock:</b> The input clock for boundary scan testing.<br>The TDI and TMS states are clocked in on positive tran-<br>sitions.                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| TRS    | 152     | Ι     | TTLp   | <b>Test Reset:</b> When an active low signal is applied to this pin, the M13E Test Access Port (TAP) controller resets and the boundary scan is disabled. The controller is also reset by writing F0H followed by 00H to the initialization register 1FH or by holding the TMS signal lead high for at least five rising clock transitions of TCK. During power-up of the M13E, this pin must be held low, to reset the TAP controller. Failure to do so may cause the TAP controller to take control of the M13E output pins. When the boundary scan feature is not used, this pin must be held low. |

#### **ABSOLUTE MAXIMUM RATINGS AND ENVIRONMENTAL LIMITATIONS**

| Parameter                          | Symbol          | Min  | Мах                   | Unit   | Conditions                        |

|------------------------------------|-----------------|------|-----------------------|--------|-----------------------------------|

| Supply voltage                     | V <sub>DD</sub> | -0.3 | +7.0                  | V      | Note 1                            |

| DC input voltage                   | V <sub>IN</sub> | -0.5 | V <sub>DD</sub> + 0.5 | V      | Note 1                            |

| Storage temperature range          | Τ <sub>S</sub>  | -55  | 150                   | °C     | Note 1                            |

| Ambient operating temperature      | T <sub>A</sub>  | -40  | 85                    | °C     | 0 ft/min linear airflow           |

| Component Temperature x Time       | TI              |      | 270 x 5               | °C x s | Note 1                            |

| Moisture Exposure Level            | ME              | 5    |                       | Level  | per EIA/JEDEC<br>JESD22-A112-A    |

| Relative Humidity, during assembly | RH              | 30   | 60                    | %      | Note 2                            |

| Relative Humidity, in-circuit      | RH              | 0    | 100                   | %      | non-condensing                    |

| ESD Classification                 | ESD             |      | <u>+</u> 2000         | V      | per MIL-STD-833D<br>Method 3015.7 |

Notes:

1. Conditions exceeding the Min or Max values may cause permanent failure. Exposure to conditions near the Min or Max values for extended periods may impair device reliability.

2. Pre-assembly storage in non-drypack conditions is not recommended. Please refer to the instructions on the "CAUTION" label on the drypack bag in which devices are supplied.

#### THERMAL CHARACTERISTICS

| Parameter                                   | Min | Тур | Max | Unit | Test Conditions         |

|---------------------------------------------|-----|-----|-----|------|-------------------------|

| Thermal resistance -<br>junction to ambient |     | 40  | 42  | °C/W | 0 ft/min linear airflow |

#### POWER REQUIREMENTS

| Parameter       | Min  | Тур | Max  | Unit | Test Conditions  |

|-----------------|------|-----|------|------|------------------|

| V <sub>DD</sub> | 4.75 | 5.0 | 5.25 | V    |                  |

| I <sub>DD</sub> |      |     | 133  | mA   |                  |

| P <sub>DD</sub> |      |     | 700  | mW   | Inputs switching |

#### INPUT, OUTPUT AND I/O PARAMETERS

#### INPUT PARAMETERS FOR CMOS

| Parameter             | Min  | Тур | Max  | Unit | Test Conditions                         |

|-----------------------|------|-----|------|------|-----------------------------------------|

| V <sub>IH</sub>       | 3.15 |     |      | V    | 4.75 <u>&lt;</u> V <sub>DD</sub> ≤ 5.25 |

| V <sub>IL</sub>       |      |     | 1.65 | V    | 4.75 <u>&lt;</u> V <sub>DD</sub> ≤ 5.25 |

| Input leakage current |      |     | 10   | μΑ   | V <sub>DD</sub> = 5.25                  |

| Input capacitance     |      | 3.5 |      | pF   |                                         |

#### INPUT PARAMETERS FOR TTL

| Parameter             | Min | Тур | Max | Unit | Test Conditions                         |

|-----------------------|-----|-----|-----|------|-----------------------------------------|

| V <sub>IH</sub>       | 2.0 |     |     | V    | 4.75 <u>&lt;</u> V <sub>DD</sub> ≤ 5.25 |

| V <sub>IL</sub>       |     |     | 0.8 | V    | 4.75 <u>&lt;</u> V <sub>DD</sub> ≤ 5.25 |

| Input leakage current |     |     | 10  | μΑ   | V <sub>DD</sub> = 5.25                  |

| Input capacitance     |     | 5.5 |     | pF   |                                         |

#### INPUT PARAMETERS FOR TTLp

| Parameter             | Min | Тур | Max | Unit | Test Conditions                             |

|-----------------------|-----|-----|-----|------|---------------------------------------------|

| V <sub>IH</sub>       | 2.0 |     |     | V    | 4.75 <u>&lt;</u> V <sub>DD</sub> ≤ 5.25     |

| V <sub>IL</sub>       |     |     | 0.8 | V    | 4.75 <u>≤</u> V <sub>DD</sub> <u>≤</u> 5.25 |

| Input leakage current |     | 0.5 | 1.4 | mA   | V <sub>DD</sub> = 5.25; Input = 0 V         |

| Input capacitance     |     | 5.5 |     | pF   |                                             |

Note: Input has a 9K (nominal) internal pull-up resistor.

#### OUTPUT PARAMETERS FOR TTL2mA

| Parameter         | Min                   | Тур  | Max  | Unit | Test Conditions                                |

|-------------------|-----------------------|------|------|------|------------------------------------------------|

| V <sub>OH</sub>   | V <sub>DD</sub> - 0.5 |      |      | V    | V <sub>DD</sub> = 4.75; I <sub>OH</sub> = -1.0 |

| V <sub>OL</sub>   |                       |      | 0.4  | V    | V <sub>DD</sub> = 4.75; I <sub>OL</sub> = 2.0  |

| I <sub>OL</sub>   |                       |      | 2.0  | mA   |                                                |

| I <sub>OH</sub>   |                       |      | -1.0 | mA   |                                                |

| t <sub>RISE</sub> | 5.0                   | 11.0 | 20.0 | ns   | C <sub>LOAD</sub> = 15 pF                      |

| t <sub>FALL</sub> | 2.0                   | 4.0  | 8.0  | ns   | C <sub>LOAD</sub> = 15 pF                      |

#### **INPUT/OUTPUT PARAMETERS FOR TTL8mA**

| Parameter             | Min                   | Тур | Max  | Unit | Test Conditions                                   |

|-----------------------|-----------------------|-----|------|------|---------------------------------------------------|

| V <sub>IH</sub>       | 2.0                   |     |      | V    | 4.75 <u>&lt;</u> V <sub>DD</sub> <u>&lt;</u> 5.25 |

| V <sub>IL</sub>       |                       |     | 0.8  | V    | 4.75 <u>&lt;</u> V <sub>DD</sub> <u>≤</u> 5.25    |

| Input leakage current |                       |     | 10   | μA   | V <sub>DD</sub> = 5.25                            |

| Input capacitance     |                       | 5.5 |      | pF   |                                                   |

| V <sub>OH</sub>       | V <sub>DD</sub> - 0.5 |     |      | V    | V <sub>DD</sub> = 4.75; I <sub>OH</sub> = -4.0    |

| V <sub>OL</sub>       |                       |     | 0.4  | V    | V <sub>DD</sub> = 4.75; I <sub>OL</sub> = 8.0     |

| I <sub>OL</sub>       |                       |     | 8.0  | mA   |                                                   |

| I <sub>ОН</sub>       |                       |     | -4.0 | mA   |                                                   |

| t <sub>RISE</sub>     | 2.4                   | 4.9 | 7.0  | ns   | C <sub>LOAD</sub> = 25 pF                         |

| t <sub>FALL</sub>     | 1.1                   | 1.8 | 2.5  | ns   | C <sub>LOAD</sub> = 25 pF                         |

### TIMING CHARACTERISTICS

**ITCH**°

TRAI

Detailed timing diagrams for the M13E are illustrated in Figures 4 through 16, with values of the timing intervals tabulated below each diagram. All output times are measured with a maximum 75 pF load capacitance. Timing parameters are measured at voltage levels of  $(V_{IH} + V_{IL})/2$  for input signals or  $(V_{OH} + V_{OL})/2$  for output signals.

| Parameter                                              | Symbol           | Min  | Тур   | Max | Unit |

|--------------------------------------------------------|------------------|------|-------|-----|------|

| DS3CR clock period                                     | t <sub>CYC</sub> | 20.0 | 22.35 |     | ns   |

| DS3CR duty cycle (t <sub>PWH</sub> /t <sub>CYC</sub> ) |                  | 45   | 50    | 55  | %    |

| DS3DR set-up for DS3CR↑                                | t <sub>SU</sub>  | -1.0 |       |     | ns   |

| DS3DR hold time after DS3CR↑                           | t <sub>H</sub>   | 6.0  |       |     | ns   |

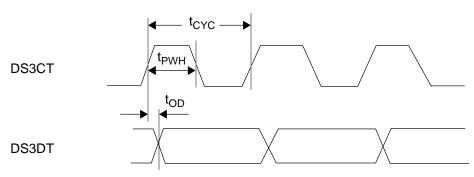

#### Figure 5. DS3 Transmit Timing

| Parameter                                              | Symbol           | Min  | Тур   | Max | Unit |

|--------------------------------------------------------|------------------|------|-------|-----|------|

| DS3CT clock period                                     | t <sub>CYC</sub> | 20.0 | 22.35 |     | ns   |

| DS3CT duty cycle (t <sub>PWH</sub> /t <sub>CYC</sub> ) |                  | 45   | 50    | 55  | %    |

| DS3DT output delay after DS3CT↑                        | t <sub>OD</sub>  | 2.5  |       | 8.0 | ns   |

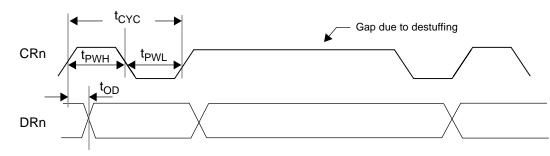

#### Figure 6. DS1 Receive Timing

| Parameter                 | Symbol           | Min                | Тур | Max                | Unit |

|---------------------------|------------------|--------------------|-----|--------------------|------|

| CR clock period           | t <sub>CYC</sub> | 585                |     | 1300               | ns   |

| CR high time              | t <sub>PWH</sub> | 14 DS3CR<br>Cycles |     | 21 DS3CR<br>Cycles | ns   |

| CR low time               | t <sub>PWL</sub> | 14 DS3CR<br>Cycles |     | 14 DS3CR<br>Cycles | ns   |

| DR output delay after CR↑ | t <sub>OD</sub>  | -12                |     | 10                 | ns   |

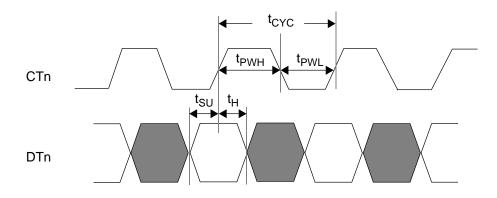

#### Figure 7. DS1 Transmit Timing

| Parameter                                           | Symbol           | Min | Тур | Max   | Unit |

|-----------------------------------------------------|------------------|-----|-----|-------|------|

| CT clock period                                     | t <sub>CYC</sub> | 583 | 648 | 712.8 | ns   |

| CT high time                                        | t <sub>PWH</sub> | 174 | 324 | 453   | ns   |

| CT low time                                         | t <sub>PWL</sub> | 174 | 324 | 453   | ns   |

| CT duty cycle (t <sub>PWH</sub> /t <sub>CYC</sub> ) |                  | 30  | 50  | 70    | %    |

| DT set-up time to CT↑                               | t <sub>SU</sub>  | 4   |     |       | ns   |

| DT hold time after CT↑                              | t <sub>H</sub>   | 6   |     |       | ns   |

Note: Each DS1 input can be asynchronous with respect to another DS1 channel. The diagram above is shown for INVCK = 0. When INVCK = 1 DTn is clocked into the M13E on the falling edges of their corresponding CTn signals. The timing parameters in the table above do not change when INVCK = 1 except that  $t_{SU}$  and  $t_{H}$  are measured with respect to the falling edges of the CTn signals.

<u>TranSwitch</u>

| Parameter                                        | Symbol             | Min | Тур  | Max | Unit |

|--------------------------------------------------|--------------------|-----|------|-----|------|

| CCKR clock period                                | t <sub>CYC</sub>   |     | 3800 |     | ns   |

| CCKR output delay after CFMR↑                    | t <sub>OD(1)</sub> |     | 3800 |     | ns   |

| CDR output delay after CCKR↑                     | t <sub>OD(2)</sub> | 0   | 13   | 20  | ns   |

| CCKR↑ delay after CDCCR↑                         | t <sub>D(1)</sub>  |     | 1900 |     | ns   |

| $CDCCR \downarrow$ delay after $CCKR \downarrow$ | t <sub>D(2)</sub>  |     | 3800 |     | ns   |

| CFMR pulse width (high)                          | t <sub>PW</sub>    |     | 1900 |     | ns   |

<u>TranSwitch</u>

#### Figure 9. C-Bit Transmit Interface Timing

Note 1: A C-bit must be transmitted as a one when not needed.

<u>TranSwitch</u>`

Note 2: Following normal power-up procedures, bit 7 in register 19H will be set to "0" and the extra clock pulse for the C3 bit in the CCKT clock will be present. If bit 7 is then set to "1," the extra C3 bit clock pulse will not be present.

| Parameter                                        | Symbol            | Min | Тур  | Max | Unit |

|--------------------------------------------------|-------------------|-----|------|-----|------|

| CCKT clock period                                | t <sub>CYC</sub>  |     | 3800 |     | ns   |

| CDT set-up time to CCKT↑                         | t <sub>SU</sub>   | 25  |      |     | ns   |

| CDT hold time after CCKT↑                        | t <sub>H</sub>    | 40  |      |     | ns   |

| CCKT output delay after CFMT↑                    | t <sub>OD</sub>   |     | 3800 |     | ns   |

| CCKT↑ delay after CDCCT↑                         | t <sub>D(1)</sub> |     | 1900 |     | ns   |

| CDCCT $\downarrow$ delay after CCKT $\downarrow$ | t <sub>D(2)</sub> |     | 3800 |     | ns   |

| CFMT pulse width                                 | t <sub>PW</sub>   |     | 1900 |     | ns   |

| Parameter                                                                  | Symbol             | Min | Тур | Max | Unit |

|----------------------------------------------------------------------------|--------------------|-----|-----|-----|------|

| ALE pulse width                                                            | t <sub>PW(1)</sub> | 95  |     |     | ns   |

| ALE wait after RD ↑                                                        | t <sub>W(1)</sub>  | 20  |     |     | ns   |

| A/D(7-0) address set-up time to ALE $\downarrow$                           | t <sub>SU</sub>    | 30  |     |     | ns   |

| A/D(7-0) address hold time after ALE $\downarrow$                          | t <sub>H(1)</sub>  | 25  |     |     | ns   |

| A/D(7-0) address hold time after $\overline{\text{RD}}\downarrow$          | t <sub>H(2)</sub>  |     |     | 20  | ns   |

| A/D(7-0) data output delay (to tri-state) after $\overline{RD}$ $\uparrow$ | t <sub>OD(1)</sub> | 10  |     | 50  | ns   |

| A/D(7-0) data valid delay after $\overline{\text{RD}}\downarrow$           | t <sub>OD(2)</sub> |     |     | 150 | ns   |

| $\overline{SEL}\downarrow$ delay after $ALE\downarrow$                     | t <sub>OD(3)</sub> |     |     | 80  | ns   |

| RD pulse width                                                             | t <sub>PW(2)</sub> | 180 |     |     | ns   |

| $\overline{RD}$ wait after ALE $\downarrow$                                | t <sub>W(2)</sub>  | 25  |     |     | ns   |

Note: The transmit clock (XCK) or receive clock (DS3CR) must be present for the microprocessor bus interface to operate.

<u>TranSwitch</u>

#### Figure 11. Microprocessor Write Cycle Timing - Multiplexed Interface

| Parameter                                                       | Symbol             | Min | Тур | Max | Unit |

|-----------------------------------------------------------------|--------------------|-----|-----|-----|------|

| ALE pulse width                                                 | t <sub>PW(1)</sub> | 95  |     |     | ns   |

| ALE wait after WR ↑                                             | t <sub>W(1)</sub>  | 20  |     |     | ns   |

| A/D(7-0) address set-up time to ALE $\downarrow$                | t <sub>SU</sub>    | 30  |     |     | ns   |

| A/D(7-0) address hold time after ALE $\downarrow$               | t <sub>H(1)</sub>  | 25  |     |     | ns   |

| A/D(7-0) data hold time after $\overline{\text{WR}}$ $\uparrow$ | t <sub>H(2)</sub>  | 20  |     |     | ns   |

| SEL output delay after ALE $\downarrow$                         | t <sub>OD</sub>    |     |     | 80  | ns   |

| WR pulse width                                                  | t <sub>PW(2)</sub> | 200 |     |     | ns   |

| $\overline{WR}$ wait after ALE $\downarrow$                     | t <sub>W(2)</sub>  | 25  |     |     | ns   |

Note: The transmit clock (XCK) or receive clock (DS3CR) must be present for the microprocessor bus interface to operate.

<u>TranSwitch</u>`

#### Figure 12. Microprocessor Read Cycle Timing - Intel Interface

| Parameter                                                           | Symbol             | Min | Тур | Max | Unit |

|---------------------------------------------------------------------|--------------------|-----|-----|-----|------|

| A(7-0) address hold time after $\overline{RD}$                      | t <sub>H(1)</sub>  | 0   |     |     | ns   |

| A(7-0) address set-up time to $\overline{\text{SEL}}\downarrow$     | t <sub>SU(1)</sub> | 20  |     |     | ns   |

| D(7-0) data valid delay after $\overline{RD}\downarrow$             | t <sub>D</sub>     |     |     | 60  | ns   |

| D(7-0) data float time after $\overline{RD}$                        | t <sub>F</sub>     |     |     | 80  | ns   |

| RD pulse width                                                      | t <sub>PW</sub>    | 80  |     |     | ns   |

| $\overline{SEL}\downarrow$ set-up time to $\overline{RD}\downarrow$ | t <sub>SU(2)</sub> | 10  |     |     | ns   |

| SEL <sup>↑</sup> hold time after RD <sup>↑</sup>                    | t <sub>H(2)</sub>  | 0   |     |     | ns   |

Note: The transmit clock (XCK) or receive clock (DS3CR) must be present for the microprocessor bus interface to operate.

<u>TranSwitch</u>

M13E TXC-03303

Figure 13. Microprocessor Write Cycle Timing - Intel Interface

| Parameter                                                           | Symbol             | Min | Тур | Max | Unit |

|---------------------------------------------------------------------|--------------------|-----|-----|-----|------|

| A(7-0) address hold time after $\overline{WR}^{\uparrow}$           | t <sub>H(1)</sub>  | 0   |     |     | ns   |

| A(7-0) address set-up time to $\overline{\text{SEL}}\downarrow$     | t <sub>SU(1)</sub> | 20  |     |     | ns   |

| D(7-0) data valid set-up time to $\overline{WR}$                    | t <sub>SU(2)</sub> | 20  |     |     | ns   |

| D(7-0) data hold time after $\overline{WR}^{\uparrow}$              | t <sub>H(2)</sub>  | 5   |     |     | ns   |

| $\overline{SEL}\downarrow$ set-up time to $\overline{WR}\downarrow$ | t <sub>SU(3)</sub> | 10  |     |     | ns   |

| WR pulse width                                                      | t <sub>PW</sub>    | 80  |     |     | ns   |

Note: The transmit clock (XCK) or receive clock (DS3CR) must be present for the microprocessor bus interface to operate.

<u>TranSwitch'</u>

#### Figure 14. Microprocessor Read Cycle Timing - Motorola Interface

| Parameter                                                             | Symbol             | Min | Тур | Мах | Unit |

|-----------------------------------------------------------------------|--------------------|-----|-----|-----|------|

| A(7-0) address hold time after $\overline{SEL}^{\uparrow}$            | t <sub>H(1)</sub>  | 0   |     |     | ns   |

| A(7-0) address valid set-up time to $\overline{\text{SEL}}\downarrow$ | t <sub>SU(1)</sub> | 20  |     |     | ns   |

| D(7-0) data valid delay after $\overline{\text{DTACK}}\downarrow$     | t <sub>D(1)</sub>  |     | 16  | 21  | ns   |

| D(7-0) data hold time after $\overline{SEL}$                          | t <sub>H(2)</sub>  |     |     | 42  | ns   |