# M13X Device TRANSWITCH DS3/DS1 MUX/DEMUX, Enhanced Features TXC-03305

DATA SHEET

#### FEATURES I

- Multiplexes/demultiplexes 28 DS1 signals to/from a DS3 signal

- Integrated dejitter buffers to GR-499-CORE for all receive DS1 outputs, with bypass option

- M13 or C-bit parity format mode operation

- FEBE, C, or P-bit parity error insertion capability

- DS3 idle signal generators

- DS1 idle signal (QRS, AIS or ESF) generators

- DS3 LOS, LOF, P-bit parity, C-bit parity, AIS and idle detectors

- Integrated PMDL controller

- Receive or transmit DS1 LOS detectors

- DS2 LOF detectors

- External interface for receiving 14 C-bits and transmitting either 13 or 14 C-bits based on a control bit setting

- DS3 and DS2 X-bit access

- DS3 transmit and receive selectable AIS generation and detection

- Supports Intel, Motorola, or multiplexed microprocessor interfaces, and includes interrupt

- DS2 transmit/receive X-bit control/status

- 8 or 16-bit wide performance counters

- Reset lead

- Test Access Port for boundary scan

- Single +5V, ±5% power supply

- 208-lead Small Outline Plastic BGA package or 208-lead PQFP package (for M13E replacement)

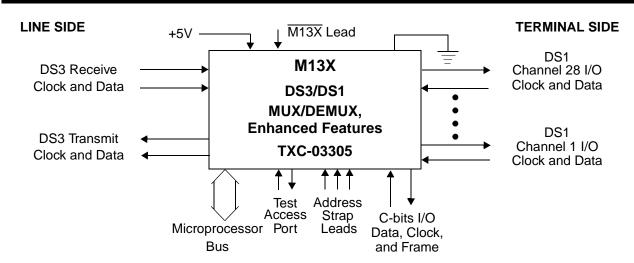

#### **DESCRIPTION**

The M13X CMOS VLSI device provides the functions needed to multiplex and demultiplex 28 independent DS1 signals to and from a DS3 signal with either an M13 or C-bit frame format. It includes some enhanced features relative to the M13E device. A lead (M13X) is provided for selecting functional and software backwards compatibility with the M13E device (TXC-03303). The M13X line side signals typically interface with a TranSwitch ART, ARTE or DART device, a DS3LIM-SN module or other DS3 line circuitry. Terminal side signals interface with commercially available DS1 line interface devices or a TranSwitch T1Fx8 device for DS1 framing. The output DS1 signals can optionally be dejittered via integrated delitter buffers (D18a). The D18a made to delite the delitered via integrated dejitter buffers (DJBs). The DJBs meet and exceed the requirements specified in GR-499-CORE, 1998.

The M13X provides an external transmit (13 or 14 bits) and receive (14 bits) interface for the 21 C-bits while operating in the C-bit parity mode. The FEAC channel (C3) can be accessed via the external interface or the M13X memory. An integrated PMDL controller is provided for transmitting and receiving HDLC encapsulated PMDL messages. Buffering of PMDL messages is provided in the transmit and receive directions. Message lengths of arbitrary size can be transmitted or received. The M13X memory map contains up to 64 8-bit register locations for software control, performance counters, and alarm reporting. The microprocessor interface provides for connection to an Intel or Motorola-compatible microprocessor, or for use of a multiplexed address/data bus. An interrupt lead with programmable polarity is provided.

#### APPLICATIONS

- Single-board M13 multiplexer

- Compact add/drop mux

- Fractional T3

- Channelized T3

Copyright © 2000 TranSwitch Corporation M13X is a trademark of TranSwitch Corporation TranSwitch and TXC are registered trademarks of TranSwitch Corporation

Document Number: TXC-03305-MB Ed. 4, September 2000

TranSwitch Corporation • 3 Enterprise Drive • Shelton, Connecticut 06484 USA Tel: 203-929-8810 • Fax: 203-926-9453 • www.transwitch.com

# **TABLE OF CONTENTS**

| Section                                                                                                                                                                                                                                                                                                                               | Page                                              |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|

| Block Diagram                                                                                                                                                                                                                                                                                                                         | 4                                                 |

| Block Diagram Description                                                                                                                                                                                                                                                                                                             |                                                   |

| Lead Diagrams                                                                                                                                                                                                                                                                                                                         |                                                   |

| Lead Descriptions                                                                                                                                                                                                                                                                                                                     |                                                   |

| Power Supply, Ground, and no Connect                                                                                                                                                                                                                                                                                                  |                                                   |

| Ds1 Receive Interfaces                                                                                                                                                                                                                                                                                                                |                                                   |

| Ds1 Transmit Interfaces                                                                                                                                                                                                                                                                                                               |                                                   |

| Ds3 Interface                                                                                                                                                                                                                                                                                                                         |                                                   |

| Microprocessor Interface                                                                                                                                                                                                                                                                                                              |                                                   |

| Transmit C-bit Interface                                                                                                                                                                                                                                                                                                              |                                                   |

| Control Leads                                                                                                                                                                                                                                                                                                                         | 21                                                |

| External Clock                                                                                                                                                                                                                                                                                                                        | 21                                                |

| Test Access Port                                                                                                                                                                                                                                                                                                                      |                                                   |

| Scan Test Leads                                                                                                                                                                                                                                                                                                                       |                                                   |

| Absolute Maximum Ratings And Environmental Limitations                                                                                                                                                                                                                                                                                |                                                   |

| Thermal Characteristics                                                                                                                                                                                                                                                                                                               |                                                   |

| Power Requirements                                                                                                                                                                                                                                                                                                                    |                                                   |

| Input, Output and Input/Output Parameters                                                                                                                                                                                                                                                                                             |                                                   |

| Timing Characteristics                                                                                                                                                                                                                                                                                                                |                                                   |

| Operation                                                                                                                                                                                                                                                                                                                             |                                                   |

| M13X Lead                                                                                                                                                                                                                                                                                                                             |                                                   |

| Resets                                                                                                                                                                                                                                                                                                                                |                                                   |

| Integrated DJB Devices                                                                                                                                                                                                                                                                                                                |                                                   |

| Jitter Tolerance                                                                                                                                                                                                                                                                                                                      |                                                   |

| Jitter Transfer                                                                                                                                                                                                                                                                                                                       |                                                   |

| Jitter Generation                                                                                                                                                                                                                                                                                                                     |                                                   |

| Jitter Enhancement                                                                                                                                                                                                                                                                                                                    |                                                   |

| Residual Jitter                                                                                                                                                                                                                                                                                                                       |                                                   |

| Interrupts                                                                                                                                                                                                                                                                                                                            |                                                   |

| PMDL Operation                                                                                                                                                                                                                                                                                                                        |                                                   |

| Counters                                                                                                                                                                                                                                                                                                                              |                                                   |

| C-bit Interfaces                                                                                                                                                                                                                                                                                                                      |                                                   |

| Test Access Port                                                                                                                                                                                                                                                                                                                      |                                                   |

| Software Initialization Sequence                                                                                                                                                                                                                                                                                                      |                                                   |

| System Considerations                                                                                                                                                                                                                                                                                                                 |                                                   |

| Memory Map                                                                                                                                                                                                                                                                                                                            |                                                   |

| Memory Map Descriptions                                                                                                                                                                                                                                                                                                               |                                                   |

| Application Diagram                                                                                                                                                                                                                                                                                                                   |                                                   |

| Package Information                                                                                                                                                                                                                                                                                                                   |                                                   |

| Ordering Information                                                                                                                                                                                                                                                                                                                  |                                                   |

| Related Products                                                                                                                                                                                                                                                                                                                      |                                                   |

| Standards Documentation Sources                                                                                                                                                                                                                                                                                                       |                                                   |

| List of Data Sheet Changes                                                                                                                                                                                                                                                                                                            |                                                   |

| Documentation Update Registration Form *                                                                                                                                                                                                                                                                                              |                                                   |

| * Please note that TranSwitch provides documentation for all of its products. Custo                                                                                                                                                                                                                                                   | mers who are                                      |

| using a TranSwitch Product, or planning to do so, should register with the TranSwi<br>Department to receive relevant updated and supplemental documentation as it is<br>should also contact the Applications Engineering Department to ensure that they<br>with the latest available information about the product, especially before | itch Marketing<br>is issued. They<br>are provided |

| development of new designs incorporating the product.                                                                                                                                                                                                                                                                                 |                                                   |

# **LIST OF FIGURES**

| Figure                                                      | Page |

|-------------------------------------------------------------|------|

| 1M13X TXC-03305 Block Diagram                               | 4    |

| 2C-Bit Assignments                                          | 7    |

| 3M13X TXC-03305 Lead Diagram for PBGA Package               | 8    |

| 4M13X TXC-03305 Lead Diagram for PQFP Package               | 9    |

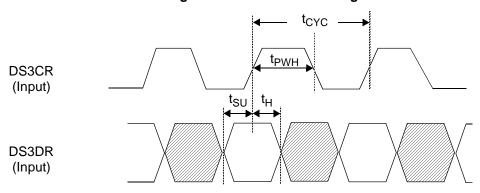

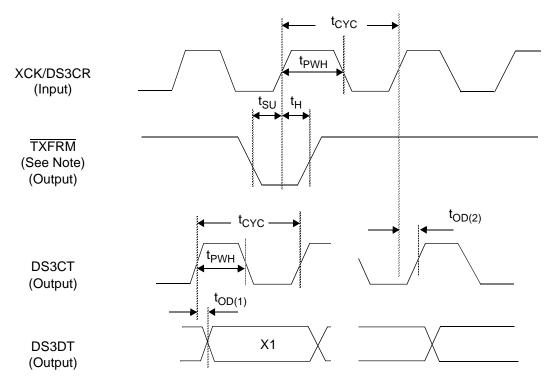

| 5DS3 Receive Timing                                         | 26   |

| 6DS3 Transmit Timing                                        | 27   |

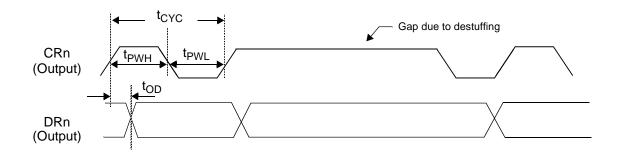

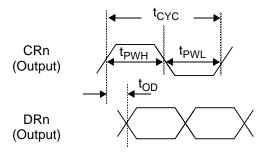

| 7DS1 Receive Timing with DJBs Disabled                      | 28   |

| 8DS1 Receive Timing with DJBs Enabled                       | 28   |

| 9DS1 Transmit Timing                                        | 29   |

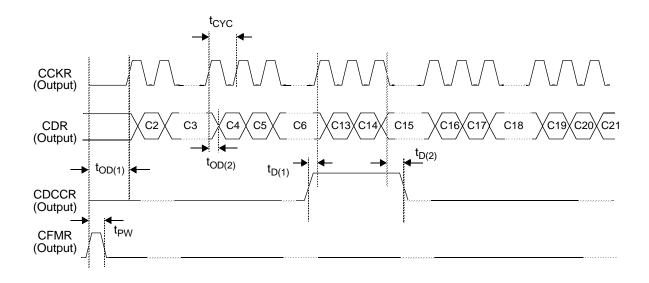

| 10C-Bit Receive Interface Timing                            | 30   |

| 11C-Bit Transmit Interface Timing                           | 31   |

| 12Microprocessor Read Cycle Timing - Multiplexed Interface  | 32   |

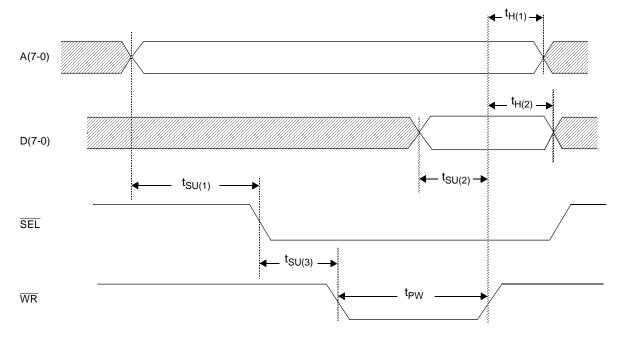

| 13Microprocessor Write Cycle Timing - Multiplexed Interface | 33   |

| 14Microprocessor Read Cycle Timing - Intel Interface        | 34   |

| 15Microprocessor Write Cycle Timing - Intel Interface       | 35   |

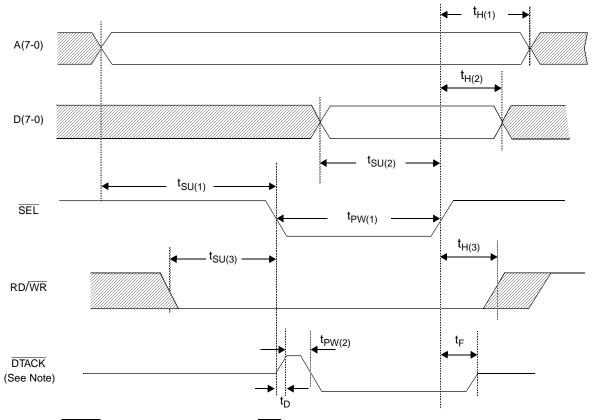

| 16Microprocessor Read Cycle Timing - Motorola Interface     | 36   |

| 17Microprocessor Write Cycle Timing - Motorola Interface    | 37   |

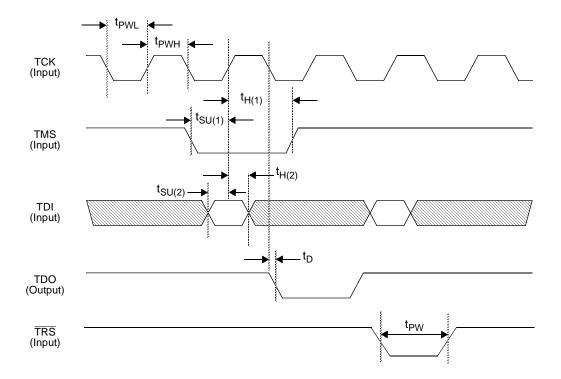

| 18Boundary Scan Timing                                      | 38   |

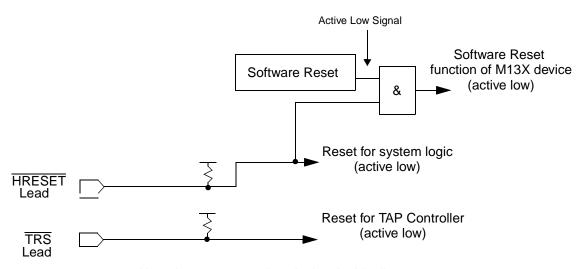

| 19M13X Reset Structure                                      | 40   |

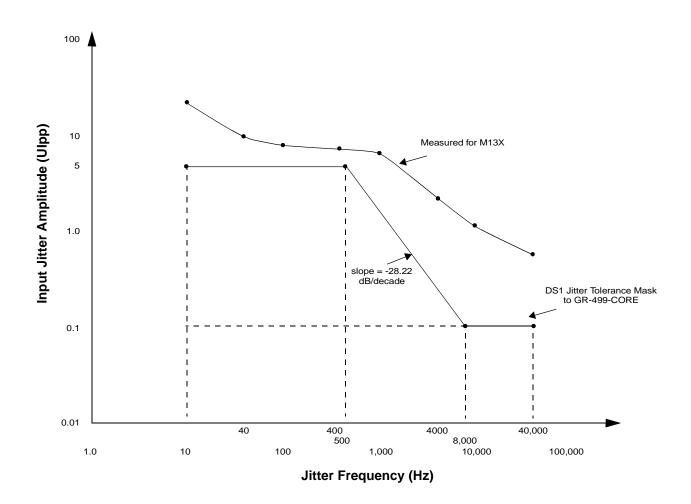

| 20DS1 Input Jitter Tolerance                                | 43   |

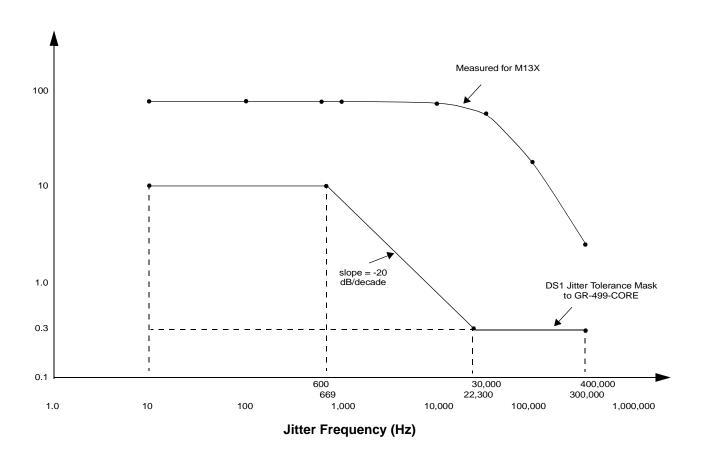

| 21DS3 Input Jitter Tolerance                                | 44   |

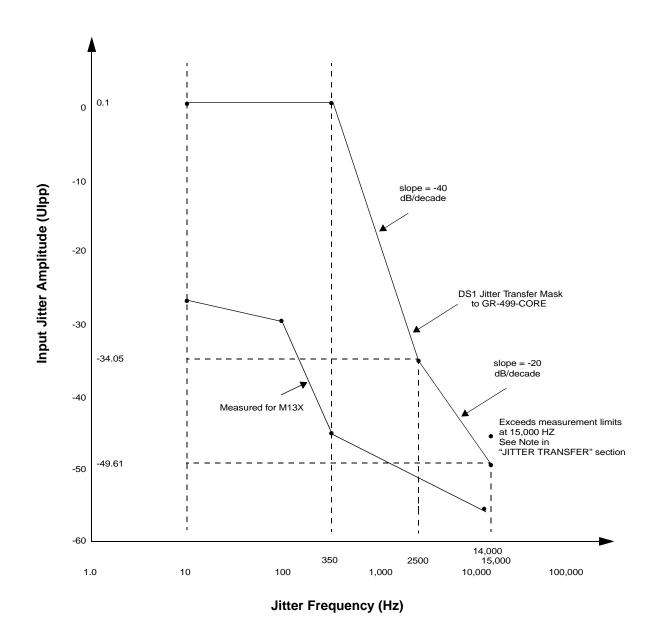

| 22DS3 to DS1 Interface Jitter Transfer Limits               | 46   |

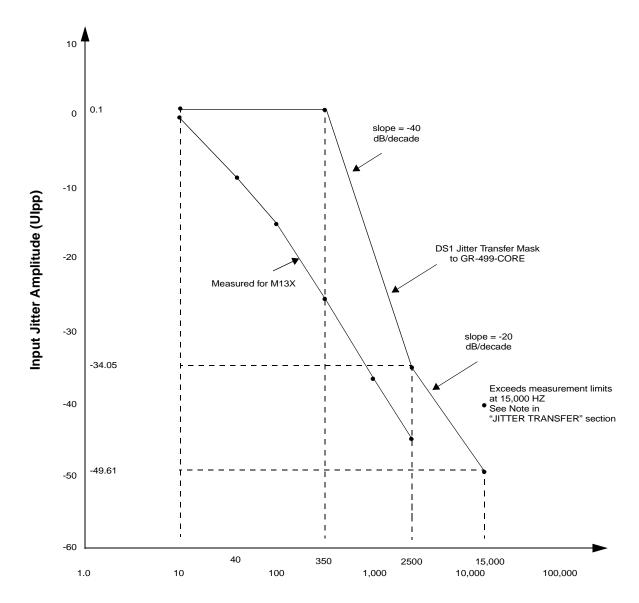

| 23DS1 to DS1 Jitter Transfer Limits                         | 47   |

| 24HDLC Format                                               | 50   |

| 25Boundary Scan Schematic                                   | 58   |

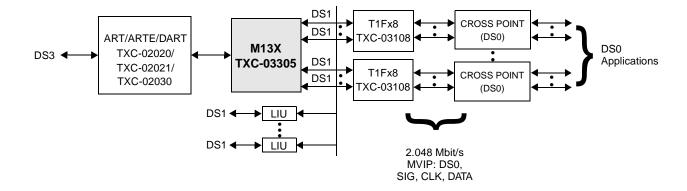

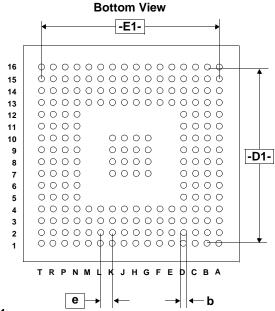

| 26Example Channelized T3 Application                        | 95   |

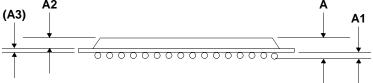

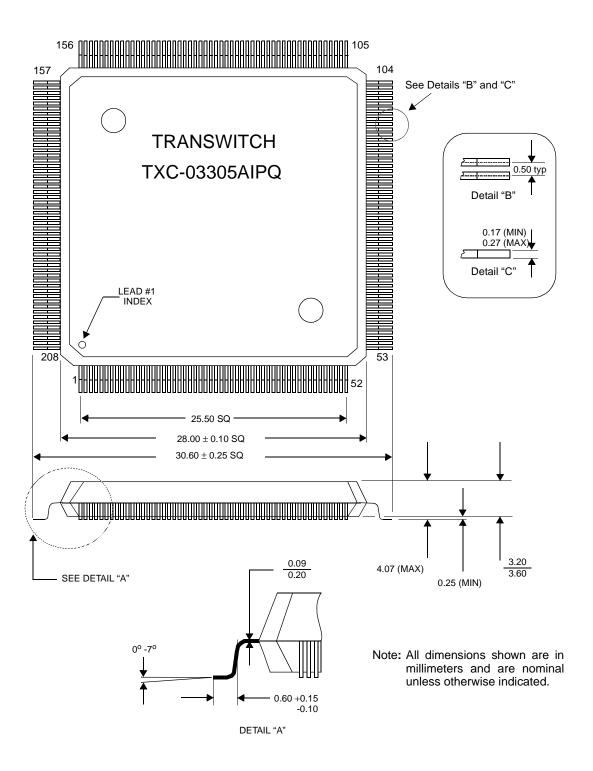

| 27M13X TXC-03305 208-Lead Plastic Ball Grid Array Package   | 96   |

| 28M13X TXC-03305 208-Lead Plastic Quad Flat Package         | 97   |

### **BLOCK DIAGRAM**

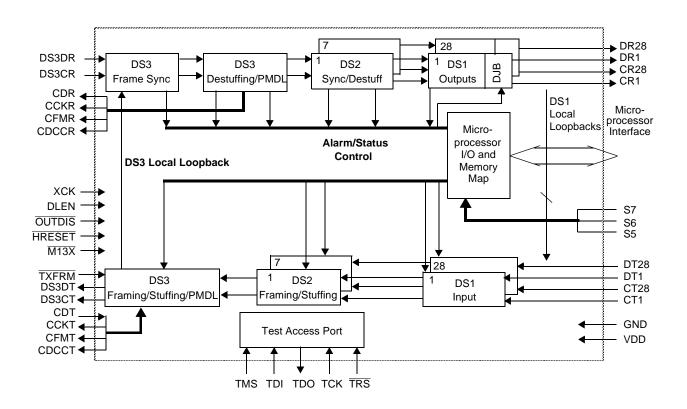

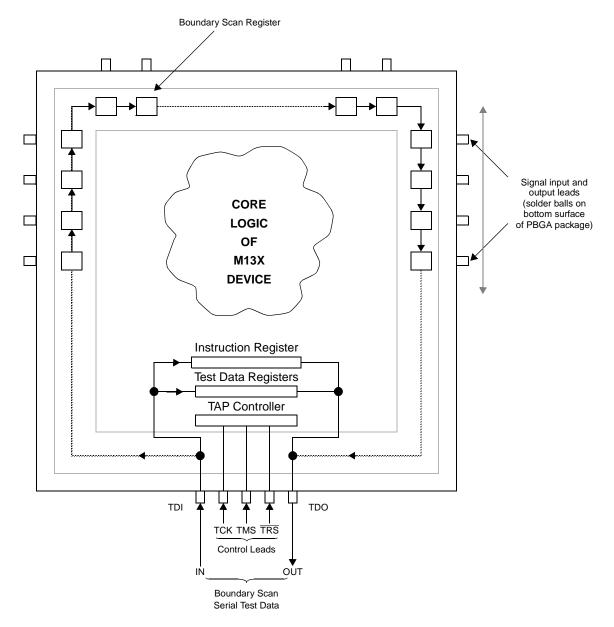

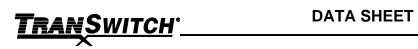

A block diagram for the M13X device is shown in Figure 1 below.

Figure 1. M13X TXC-03305 Block Diagram

#### **BLOCK DIAGRAM DESCRIPTION**

Figure 1 shows a simplified block diagram of the M13X and its signal leads. The M13X is packaged in a 208-lead small outline Plastic Ball Grid Array (PBGA) package or a 208-lead Plastic Quad Flat Package (PQFP). The PQFP version is intended to be used as a replacement for TranSwitch's M13E device (TXC-03303-AIPQ) and is not recommended for new designs. The PBGA version is intended for new designs.

The M13X in the PBGA or PQFP packages, with the exception of the boundary scan, can be configured to be functionally compatible with, and have the same memory map as, the M13E device, by applying a high to the  $\overline{\text{M13X}}$  lead. The enhanced features included in the M13X can be enabled by applying a low to the  $\overline{\text{M13X}}$  lead. These enhanced M13X features are:

- Transmit/receive PMDL (Path Maintenance Data Link) controller

- · Interrupt request lead with programmable polarity and associated interrupt mask bits

- · Integrated dejitter buffer (DJB) on all receive DS1 outputs with optional bypass capability

- 16-bit performance counters.

- NEW bit in register 1DH does not become set to one again after it is cleared when a constant FEAC message is received.

When the  $\overline{\text{M13X}}$  lead is set to high, the M13X enhanced features listed above are disabled and cannot be accessed.

In the receive direction, DS3 data (DS3DR) is clocked into the M13X on rising edges of the DS3 input clock (DS3CR). The data and clock signals may be derived from any line interface unit such as TranSwitch's ART, ARTE, DART or DS3LIM-SN, or from other line circuitry.

The DS3 Frame Sync block searches for and locks to the DS3 frame, as specified in Bellcore GR-499-CORE "Transport System Generic Requirements," and in ANSI T1.107-1995. The M13X receiver monitors the DS3 signal for out of frame, loss of signal, a DS3 AIS, DS3 idle signal, P-bit parity, the state of the X-bits, and loss of clock. The DS3 AIS detection mechanism is software selectable, with a choice of six detectors. These range from full compliance to T1.107-1995 to unframed all ones AIS detection. Control bits are also provided in memory which allow all, some of, or none of the DS3 alarms to cause the insertion of AIS into the receive DS1 channels.

In the M13 format mode, destuffing from DS3 to DS2 is performed based on the states of the C-bits in the DS3 subframes. If two or three of the C-bits in a subframe are ones, the associated stuff bit is interpreted as being a stuff bit and is removed from the data stream and discarded.

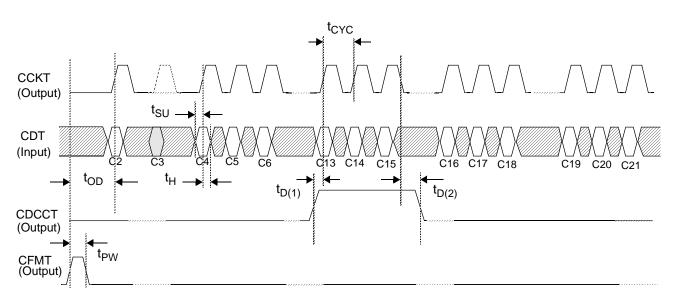

In the C-bit parity mode, the C-bits are allocated for network performance. The M13X performs Far End Alarm and Control (FEAC) detection, C-bit parity error detection, and Far End Block Error (FEBE) detection. FEAC loopback requests and alarm/status information are provided in the memory map. In addition, the states of 14 C-bits (C2, C3, C4, C5, C6, C13, C14, C15, C16, C17, C18, C19, C20, and C21) are provided at a serial interface (CDR), along with an output clock signal (CCKR), framing pulse (CFMR), and data link indicator pulse (CDCCR). The data link indicator pulse identifies the location of the data link bits, C13, C14, and C15. If the M13X lead is tied low, the receive PMDL (Path Maintenance Data Link) controller can be enabled via a control bit. The receive PMDL controller is used to extract PMDL messages of any length. FCS error detection, ABORT detection, End of Message, Start of Message, Invalid Frame Detected, and receive PMDL FIFO status can be monitored via the microprocessor interface.

The M13X synchronizes and extracts the 28 DS1 channels from the seven DS2 channels. Each of the DS2 channels is monitored for out of frame. The M13X may generate AIS in each of the DS1 signal tributaries corresponding to the DS2 channel(s) that lost frame, depending on the DS1 AIS alarm insertion control bits. DS2 to DS1 destuffing is based on the states of the three C-bits in each DS2 subframe. If two or three of the C-bits in one of the DS2 subframes are ones, the stuff bit for that subframe is discarded. In the M13 format mode, the DS2 C-bits or stuffing bits are used for DS1 remote loopback requests for either the M13 or C-bit Parity format

modes. The M13X provides control bits in the memory map for selecting the remote loopback detection mechanism. The destuffing operation is still active during loopback request and operation. In addition to DS2 synchronization, destuffing, and remote loopback request detection, the M13X also extracts the seven DS2 X-bits and provides them to a register.

An option is provided that allows the received or transmitted DS1 channels to be monitored for loss of signal. Receive data for each of the DS1 channels (DRn) is clocked out of the M13X on rising edges of the associated clock signal (CRn), where n = 1 - 28. In addition, the M13X provides a stable DS1 clock signal for the data signals received during AIS periods. When the  $\overline{M13X}$  lead is held low, dejitter buffers (DJBs) can be enabled via a control bit to dejitter the receive DS1 outputs. The DJBs meet and exceed GR-499-CORE specifications.

In the transmit direction, DS1 transmit data (DTn) is clocked into the M13X on rising edges of the clock input (CTn) for each of the 28 DS1 channels. A DS1 Input block, which consists of a FIFO and supporting logic, is provided for each DS1 channel. Under software control, the M13X can invert the transmit data signals, or the clock signals, for all 28 DS1 channels. The data inversion feature provides compatibility with certain T1 line interface devices, while the clock inversion feature allows back-to-back M13X operation.

The DS1 Input block is also used to insert one of three idle patterns from a common generator into a DS1 bit stream, under software control. The selection of the idle pattern is common to all 28 DS1 channels. The idle patterns are: a QRS, an Extended Super Frame DS1 (ESF) format with all ones in DS0 channels 1 through 24, and an AIS format (all ones).

Each DS1 signal is multiplexed into the respective DS2 frame, with the stuff bits inserted based on the fill level of an internal FIFO. When the fill of the FIFO drops below half full, a stuff bit is inserted into the DS1 bit stream in the DS2 signal. The DS2 signal is formed by combining four DS1 signals. In each frame there are 287 data bit positions and one stuff bit per DS1 channel (for a DS1 total of 1152 bits) and 24 overhead bits, for a frame total of 1176 bits. The overhead bits are used for framing, X-bit channel and stuff control.

The DS3 signal is partitioned into M-frames of 4760 bits each. The M-frames are divided into seven M-sub-frames having 680 bits each. Each M-subframe is further divided into eight blocks of 85 bits each. Each block uses 84 bits for payload and one bit for frame overhead. There are 56 overhead bits in each M-frame: the M-frame alignment uses three bits, the M-subframe alignment (F-bits) uses 28 bits, 21 bits are defined as C-bits, two bits are assigned for parity, and two bits are assigned for the X-bit channel. A frame synch input, TXFRM, is provided and can optionally be used to align the DS3 overhead bits in the DS3DT output.

The DS3 frame is constructed and timed according to the operating mode, i.e., C-bit parity mode or M13 format mode. In the C-bit parity mode, all seven of the DS2 stuff bits are always fixed as stuff, resulting in 7 pseudo DS2 frames of 671 bits per DS2 frame in each DS3 frame, for a DS2 rate of 6.3062723 Mbit/s. Since stuffing always occurs, the 21 C-bits are assigned for other functions, as shown in Figure 2. A C-bit interface is provided for transmitting 13 or 14 C-bits (C2, C3-depending on the state of bit 7 of register 19H (C3CLKI), C4, C5, C6, C13, C14, C15, C16, C17, C18, C19, C20, C21). The external transmit C-bit interface consists of a serial data input (CDT), an output clock (CCKT), a data link indicator pulse (CDCCT), and an output framing pulse (CFMT). The data link indicator pulse identifies the location of the three data link bits, C13, C14, and C15. In addition, a control bit is provided in the memory map which enables the M13X to generate an extra clock cycle during the C3 bit time. When the M13X lead is tied low, the transmit PMDL controller can be enabled through software control. The transmit PMDL controller supports transmission of HDLC (High Level Data Link Control) encapsulated messages of arbitrary length. Interrupt request bits are provided for signaling transmit PMDL FIFO and message status. When the transmit PMDL controller is enabled, C13, C14, and C15 on the transmit C-bit interface are ignored; instead, C13, C14, and C15 are sourced from the transmit PMDL controller.

A receive C-bit interface is provided for extraction of 14 C-bits (C2, C3, C4, C5, C6, C13, C14, C15, C16, C17, C18, C19, C20, C21). The receive C-bit interface consists of a serial data output (CDR), an output clock (CCKR), a data link indicator pulse (CDCCR), and an output framing pulse (CFMR). The data link indicator pulse identifies the location of the three data link C-bits, C13, C14, and C15.

| C1     | C2*    | C3**   | C1 = C-bit parity mode                |

|--------|--------|--------|---------------------------------------|

|        |        |        | C2 = Reserved                         |

|        |        |        | C3 = Far End Alarm and Control (FEAC) |

| C4*    | C5*    | C6*    | Not defined, set to 1                 |

| C7     | C8     | C9     | C-bit Parity bits                     |

| C10    | C11    | C12    | Far End Block Error (FEBE)            |

| C13*** | C14*** | C15*** | Maintenance data link (28 kbit/s)     |

| C16*   | C17*   | C18*   | Not defined, set to 1                 |

| C19*   | C20*   | C21*   | Not defined, set to 1                 |

- \* These bits are always provided at the C-bit interface in the C-bit mode.

- \*\* This bit is always provided at the receive C-bit interface in the C-bit mode. This bit is optionally processed at the transmit C-bit interface.

- \*\*\* These bits are always provided at the receive C-bit interface in the C-bit mode. In the transmit direction these bits can optionally be supplied via the integrated PMDL controller.

Figure 2. C-Bit Assignments

Of the eight remaining C-bits, C1 is used as an identification channel; C3 is defined as a Far End Alarm and Control (FEAC) bit and is controlled via the memory map; C7, C8, and C9 are used for C-bit parity; and the remaining three bits, C10, C11, and C12, are used to transmit a FEBE indication. A FEBE is automatically transmitted if a C-bit parity error or framing error is received.

Fixed DS2 to DS3 stuffing is used for M23 multiplexing at a rate of seven stuffs for every 18 DS3 stuff opportunities. This yields a DS2 frequency of  $\pm$ 2.6 ppm above the desired frequency of 6.312 Mbit/s. After adding this to the tolerance of the DS3 clock signal,  $\pm$ 20 ppm, the frequency is still within the  $\pm$ 32 ppm allowed for a DS2 signal.

Under software control, the M13X can generate DS3 idle and AIS signals, and loop back the transmitted DS3 signal to the receiver for test purposes. Other functions provided by the M13X include: DS1 loopback capability, and transmit clock failure protection. The microprocessor interface is selectable via two external hardware straps. Interface options are: Multiplexed, Intel compatible, or Motorola compatible. An interrupt request lead with programmable polarity is provided and can be used when the M13X lead is tied low.

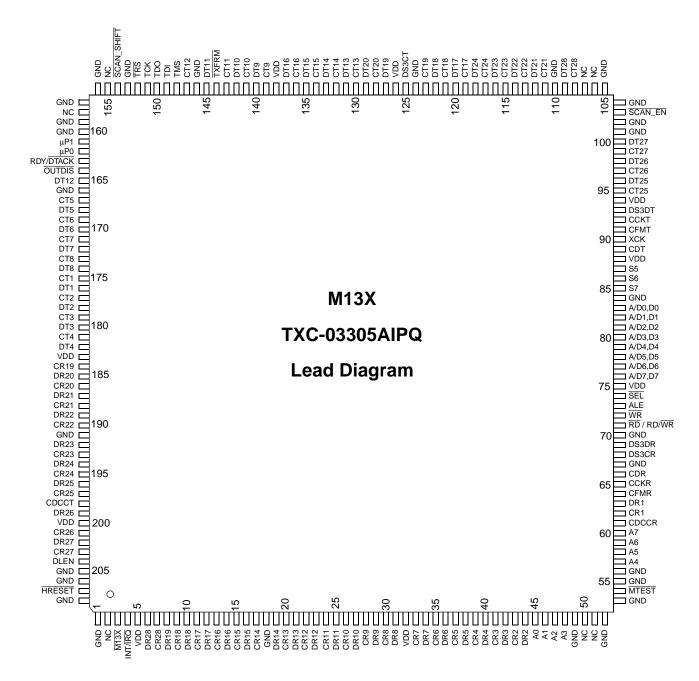

#### **LEAD DIAGRAMS**

The M13X is available in both plastic ball grid array (PBGA) and plastic quad flat package (PQFP) packages, as shown in Figures 3, 4, 27 and 28.

|   | A2     | NC     | A5   | CDCCE | R CFMR | DCCCD | NC       | SEL     | A/D4 D4   | A/D0,D0   | S5       | CFMT | CT25   | DT25     | DT26   | CT27    |

|---|--------|--------|------|-------|--------|-------|----------|---------|-----------|-----------|----------|------|--------|----------|--------|---------|

| т |        |        |      |       | CFMR   | DSSCR |          |         |           |           |          | CFMT | C125   |          |        |         |

| R | A1     | A3     | A4   | A6    | DR1    | GND   | NC       | ALE     | A/D3,D3   | SCAN_EN   | VDD      | CCKT | VDD    | CT26     | DT27   | DT28    |

| Р | DR2    | A0     | GND  | A7    | CCKR   | DS3DR | RD,RD/W  | VDD     | A/D5,D5   | A/D1,D1   | \$6      | XCK  | DS3DT  | CT28     | GND    | CT21    |

| N | DR3    | CR2    | CR3  | CR1   | CDR    | NC    | WR       | A/D7,D7 | 7 A/D6,D6 | 6 A/D2,D2 | \$7<br>( | CDT  | CT23   | CT22     | DT21   | DT22    |

| м | CR4    | DR4    | DR5  | CR5   |        |       |          |         |           |           |          |      | CT17   | DT24     | DT23   | CT24    |

| L | CR6    | DR6    | DR7  | CR7   |        |       |          |         |           |           |          |      | CT19   | DT18     | DT17   | CT18    |

|   | VDD    | MTEST  | NC   | DR8   |        |       | ALL 16 C | F THES  | E BALLS A | ARE GND   |          |      | DT19   | VDD      | NC     | DS3CT   |

| κ | VDD    | MIESI  |      |       |        |       |          |         |           |           |          |      |        |          |        |         |

| J | DR9    | CR8    | CR9  | DR10  |        |       |          |         |           |           |          |      | DT13   | CT13     | CT20   | DT20    |

| н | CR11   | DR12   | DR11 | CR10  |        |       |          |         |           |           |          |      | CT14   | DT14     | DT15   | CT15    |

| G | CR13   | DR14   | DR13 | CR12  |        |       |          |         |           |           |          |      | CT16   | DT16     | NC     | VDD     |

| F | DR15   | CR15   | CR14 | NC    |        |       |          |         |           |           |          |      | NC     | СТ9      | CT10   | DT9     |

| E | DR17   | CR17   | CR16 | DR16  |        |       |          |         |           |           |          |      | DT10   | CT11     | DT11   | TXFRM   |

| D | CR18   | CR28   | DR19 | DR18  | DR25   | DR23  | DR21     | VDD     | DT4       | DT2       | NC       | CT7  | CT5    | GND      | CT12   | TMS     |

| С | VDD    | DR28   | M13X | VDD   | CR25   | CR23  | CR21     | CR19    | CT4       | CT2       | DT8      | DT6  | DT12   | GND      | TDO    | TDI     |

| В | NT/ĪRQ | HRESET | DLEN | DR27  | DR26   | CR24  | CR22     | CR20    | DT3       | CT1       | DT7      | DT5  | OUTDIS | μP0 S0   | CAN_SH | IFT TCK |

| А | GND    | NC (   | CR27 | CR26  | CDCCT  | DR24  | DR22     | DR20    | СТ3       | DT1       | CT8      | CT6  | GND F  | RDY/DTAC |        | TRS     |

|   | 1      | 2      | 3    | 4     | 5      | 6     | 7        | 8       | 9         | 10        | 11       | 12   | 13     | 14       | 15     | 16      |

Note: This a bottom view of the M13X 208-lead plastic ball grid array package. All leads are solder balls. Some lead symbols may be abbreviated. See Figure 27 for package dimension information. This diagram is rotated relative to the bottom view shown in Figure 27.

Figure 3. M13X TXC-03305 Lead Diagram for PBGA Package

Note: This a top view of the M13X 208-lead plastic quad flat package. Some lead symbols may be abbreviated. See Figure 28 for package dimension information.

Figure 4. M13X TXC-03305 Lead Diagram for PQFP Package

# **LEAD DESCRIPTIONS**

All TTL8mA I/Os are slew rate controlled except for the DS3DT and DS3CT outputs.

# POWER SUPPLY, GROUND, AND NO CONNECT

| Symbol | Lead No.<br>BGA                                                                               | Lead No.<br>PQFP | I/O/P* | Type** | Name/Function                                                                                                                                                                                                                                                                            |

|--------|-----------------------------------------------------------------------------------------------|------------------|--------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VDD    | D8, G16,                                                                                      | 126, 138,        | Р      |        | VDD: +5-volt supply voltage, ±5%.                                                                                                                                                                                                                                                        |

| GND    | C14, D14,<br>G7, G8,<br>G9, G10,<br>H7, H8,<br>H9, H10,<br>J7, J8, J9,<br>J10, K7,<br>K8, K9, | 55, 56,          | P      |        | Ground: 0 volts reference.                                                                                                                                                                                                                                                               |

| NC     | A2, D11,<br>F4, F13,<br>G15, K3,<br>K15, N6,<br>R7, T2,<br>T7                                 | 106, 107,        |        |        | No Connect: NC leads are not to be connected, not even to another NC lead, but must be left floating. Connection of NC leads may impair performance or cause damage to the device. If future revisions of the device are made, then these leads may have functions associated with them. |

Notes for lead descriptions tables:

<sup>\*</sup> I = Input; O = Output; P = Power

<sup>\*\*</sup> See Input, Output and Input//Output Parameters section below for Type definitions.

# **DS1 RECEIVE INTERFACES**

| Symbol | Lead No.<br>BGA | Lead No.<br>PQFP | I/O/P | Туре   | Name/Function                                         |

|--------|-----------------|------------------|-------|--------|-------------------------------------------------------|

| CR1    | N4              | 62               | 0     | TTL2mA | Receive DS1 Clocks, Channels 1 - 28: Receive          |

| CR2    | N2              | 43               |       |        | data is clocked out of the M13X on rising edges of    |

| CR3    | N3              | 41               |       |        | these clocks. The clock for the first DS1 channel     |

| CR4    | M1              | 39               |       |        | corresponds to CR1, while the clock for the last      |

| CR5    | M4              | 37               |       |        | DS1 channel corresponds to CR28. During normal        |

| CR6    | L1              | 35               |       |        | operation, the DS1 clock signals are derived from     |

| CR7    | L4              | 33               |       |        | the DS3 clock signal (DS3CR) and are stretched        |

| CR8    | J2              | 30               |       |        | due to overhead and stuff bit removal. When the       |

| CR9    | J3              | 28               |       |        | M13X lead is tied low and the DJB control bit is set  |

| CR10   | H4              | 26               |       |        | to a 1, the internal DJB circuits will be enabled,    |

| CR11   | H1              | 24               |       |        | which will reduce the amount that these clocks are    |

| CR12   | G4              | 22               |       |        | stretched, thereby reducing their jitter. During cer- |

| CR13   | G1              | 20               |       |        | tain DS3 alarm conditions (programmable via           |

| CR14   | F3              | 17               |       |        | 1TAIS1 and 1TAIS0, bits 5 and 4 in register 20H)      |

| CR15   | F2              | 15               |       |        | the M13X provides a DS1 clock signal for clocking     |

| CR16   | E3              | 13               |       |        | out AIS which is derived from the XCK clock lead.     |

| CR17   | E2              | 11               |       |        |                                                       |

| CR18   | D1              | 9                |       |        |                                                       |

| CR19   | C8              | 184              |       |        |                                                       |

| CR20   | B8              | 186              |       |        |                                                       |

| CR21   | C7              | 188              |       |        |                                                       |

| CR22   | B7              | 190              |       |        |                                                       |

| CR23   | C6              | 193              |       |        |                                                       |

| CR24   | B6              | 195              |       |        |                                                       |

| CR25   | C5              | 197              |       |        |                                                       |

| CR26   | A4              | 201              |       |        |                                                       |

| CR27   | A3              | 203              |       |        |                                                       |

| CR28   | D2              | 7                |       |        |                                                       |

| Symbol | Lead No.<br>BGA | Lead No.<br>PQFP | I/O/P | Туре   | Name/Function                                                         |

|--------|-----------------|------------------|-------|--------|-----------------------------------------------------------------------|

| DR1    | R5              | 63               | 0     | TTL2mA | Receive DS1 Data, Channels 1 - 28: Demulti-                           |

| DR2    | P1              | 44               |       |        | plexed DS1 channels. The first DS1 channel corre-                     |

| DR3    | N1              | 42               |       |        | sponds to DR1, while the last DS1 channel                             |

| DR4    | M2              | 40               |       |        | corresponds to DR28. During normal operation                          |

| DR5    | М3              | 38               |       |        | these data outputs are stretched due to overhead                      |

| DR6    | L2              | 36               |       |        | and stuff bit removal. When the $\overline{\text{M13X}}$ lead is tied |

| DR7    | L3              | 34               |       |        | low and the DJB bit is set to a 1, the internal DJB                   |

| DR8    | K4              | 31               |       |        | circuits will be enabled, which will reduce the                       |

| DR9    | J1              | 29               |       |        | amount that these data outputs are stretched,                         |

| DR10   | J4              | 27               |       |        | thereby reducing their jitter.                                        |

| DR11   | H3              | 25               |       |        |                                                                       |

| DR12   | H2              | 23               |       |        |                                                                       |

| DR13   | G3              | 21               |       |        |                                                                       |

| DR14   | G2              | 19               |       |        |                                                                       |

| DR15   | F1              | 16               |       |        |                                                                       |

| DR16   | E4              | 14               |       |        |                                                                       |

| DR17   | E1              | 12               |       |        |                                                                       |

| DR18   | D4              | 10               |       |        |                                                                       |

| DR19   | D3              | 8                |       |        |                                                                       |

| DR20   | A8              | 185              |       |        |                                                                       |

| DR21   | D7              | 187              |       |        |                                                                       |

| DR22   | A7              | 189              |       |        |                                                                       |

| DR23   | D6              | 192              |       |        |                                                                       |

| DR24   | A6              | 194              |       |        |                                                                       |

| DR25   | D5              | 196              |       |        |                                                                       |

| DR26   | B5              | 199              |       |        |                                                                       |

| DR27   | B4              | 202              |       |        |                                                                       |

| DR28   | C2              | 6                |       |        |                                                                       |

# **DS1 TRANSMIT INTERFACES**

| Symbol | Lead No.<br>BGA | Lead No.<br>PQFP | I/O/P | Туре | Name/Function                                         |

|--------|-----------------|------------------|-------|------|-------------------------------------------------------|

| CT1    | B10             | 175              | I     | TTL  | Transmit DS1 Clocks, Channels 1 - 28: Transmit        |

| CT2    | C10             | 177              |       |      | data is clocked into the M13X on either the rising or |

| CT3    | A9              | 179              |       |      | falling edges of these clocks, depending on the set-  |

| CT4    | C9              | 181              |       |      | ting of the INVCK bit. The clock for the first DS1    |

| CT5    | D13             | 167              |       |      | channel corresponds to CT1, while the clock for the   |

| CT6    | A12             | 169              |       |      | last DS1 channel corresponds to CT28.                 |

| CT7    | D12             | 171              |       |      |                                                       |

| CT8    | A11             | 173              |       |      |                                                       |

| CT9    | F14             | 139              |       |      |                                                       |

| CT10   | F15             | 141              |       |      |                                                       |

| CT11   | E14             | 143              |       |      |                                                       |

| CT12   | D15             | 147              |       |      |                                                       |

| CT13   | J14             | 130              |       |      |                                                       |

| CT14   | H13             | 132              |       |      |                                                       |

| CT15   | H16             | 134              |       |      |                                                       |

| CT16   | G13             | 136              |       |      |                                                       |

| CT17   | M13             | 119              |       |      |                                                       |

| CT18   | L16             | 121              |       |      |                                                       |

| CT19   | L13             | 123              |       |      |                                                       |

| CT20   | J15             | 128              |       |      |                                                       |

| CT21   | P16             | 111              |       |      |                                                       |

| CT22   | N14             | 113              |       |      |                                                       |

| CT23   | N13             | 115              |       |      |                                                       |

| CT24   | M16             | 117              |       |      |                                                       |

| CT25   | T13             | 95               |       |      |                                                       |

| CT26   | R14             | 97               |       |      |                                                       |

| CT27   | T16             | 99               |       |      |                                                       |

| CT28   | P14             | 108              |       |      |                                                       |

| Symbol | Lead No.<br>BGA | Lead No.<br>PQFP | I/O/P | Туре | Name/Function                                  |

|--------|-----------------|------------------|-------|------|------------------------------------------------|

| DT1    | A10             | 176              | l     | TTL  | Transmit DS1 Data, Channels 1 - 28: The first  |

| DT2    | D10             | 178              |       |      | DS1 channel corresponds to DT1, while the last |

| DT3    | B9              | 180              |       |      | DS1 channel corresponds to DT28.               |

| DT4    | D9              | 182              |       |      |                                                |

| DT5    | B12             | 168              |       |      |                                                |

| DT6    | C12             | 170              |       |      |                                                |

| DT7    | B11             | 172              |       |      |                                                |

| DT8    | C11             | 174              |       |      |                                                |

| DT9    | F16             | 140              |       |      |                                                |

| DT10   | E13             | 142              |       |      |                                                |

| DT11   | E15             | 145              |       |      |                                                |

| DT12   | C13             | 165              |       |      |                                                |

| DT13   | J13             | 131              |       |      |                                                |

| DT14   | H14             | 133              |       |      |                                                |

| DT15   | H15             | 135              |       |      |                                                |

| DT16   | G14             | 137              |       |      |                                                |

| DT17   | L15             | 120              |       |      |                                                |

| DT18   | L14             | 122              |       |      |                                                |

| DT19   | K13             | 127              |       |      |                                                |

| DT20   | J16             | 129              |       |      |                                                |

| DT21   | N15             | 112              |       |      |                                                |

| DT22   | N16             | 114              |       |      |                                                |

| DT23   | M15             | 116              |       |      |                                                |

| DT24   | M14             | 118              |       |      |                                                |

| DT25   | T14             | 96               |       |      |                                                |

| DT26   | T15             | 98               |       |      |                                                |

| DT27   | R15             | 100              |       |      |                                                |

| DT28   | R16             | 109              |       |      |                                                |

# **DS3 INTERFACE**

| Symbol | Lead No.<br>BGA | Lead No.<br>PQFP | I/O/P | Туре                | Name/Function                                                                                                                                                                                                                                                                                                                                                                            |

|--------|-----------------|------------------|-------|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DS3CR  | T6              | 68               | I     | CMOS                | DS3 Receive Clock: A 44.736 MHz clock that is used to clock DS3 data into the M13X. This clock is used as the time base for demultiplexing the DS3 data. When the loop timing feature is active (a 1 written into bit 3 (LPTIME) in 02H), or when the DS3 external transmit clock (XCK) fails, this clock becomes the transmit clock.                                                    |

| DS3DR  | P6              | 69               | I     | CMOS                | <b>DS3 Receive Data:</b> Receive 44.736 Mbit/s data is clocked into the M13X on rising edges of the receive clock (DS3CR).                                                                                                                                                                                                                                                               |

| DS3CT  | K16             | 125              | 0     | TTL8mA <sup>1</sup> | DS3 Transmit Clock: A 44.736 MHz clock which is derived from the external transmit clock input signal (XCK) or from the DS3 Receive Clock (DS3CR) when loop timing mode is enabled or when the XCK clock fails. It is used to clock DS3 data from the M13X.                                                                                                                              |

| DS3DT  | P13             | 93               | 0     | TTL8mA <sup>2</sup> | <b>DS3 Transmit Data:</b> Transmit C-bit parity or M13 formatted DS3 data is clocked out of the M13X on rising edges of the transmit clock (DS3CT).                                                                                                                                                                                                                                      |

| TXFRM  | E16             | 144              | I     | TTLp                | Transmit DS3 Frame Synchronization Pulse: An active low pulse that is sampled on the rising edge of the transmit DS3 clock (XCK or DS3CR), and is used to align the transmit DS3 frame. The X1 bit of the transmit DS3 frame is three clocks delayed with respect to the TXFRM. The use of this lead is optional. If it is not used then it must either be left floating or pulled high. |

- 1. DS3CT is not slew rate limited.

- 2. DS3DT is not slew rate limited.

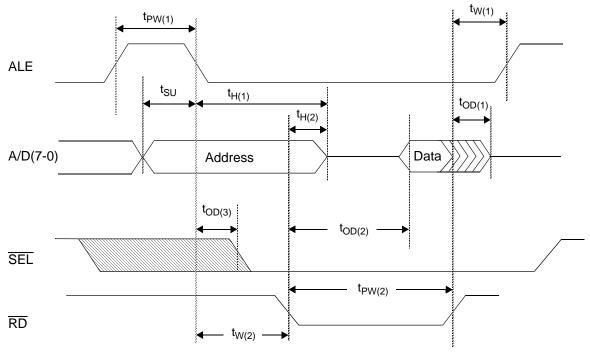

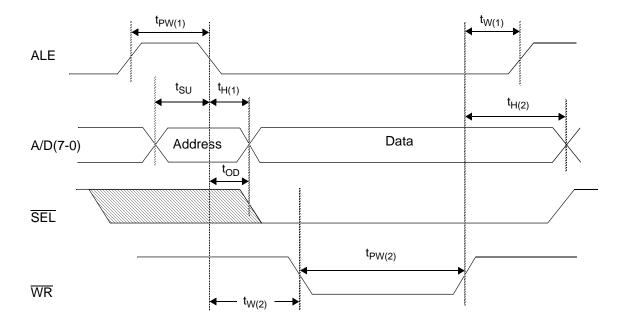

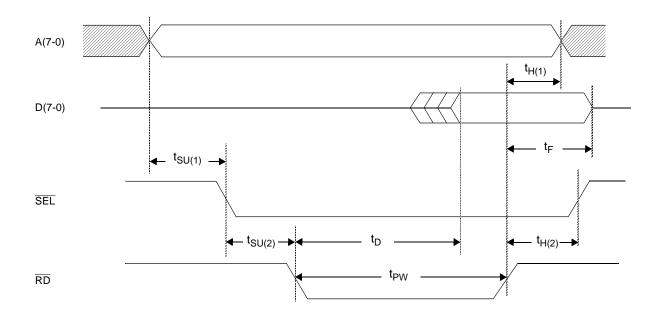

### **MICROPROCESSOR INTERFACE**

| Symbol     | Lead No.<br>BGA | Lead No.<br>PQFP | I/O/P | Туре |                                                |                                                                                                                  |                                                                                                                                                                              | Name/Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|------------|-----------------|------------------|-------|------|------------------------------------------------|------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| μP1<br>μP0 | A15<br>B14      | 161<br>162       | I     | TTLp | mid                                            | croproc                                                                                                          |                                                                                                                                                                              | Interface Type Select: The type of terface selected by these two bits is below:                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|            |                 |                  |       |      |                                                | μP1                                                                                                              | μΡ0                                                                                                                                                                          | Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|            |                 |                  |       |      | Ē                                              | High                                                                                                             | High                                                                                                                                                                         | Multiplexed (only allowed when M13X lead is high)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|            |                 |                  |       |      |                                                | High                                                                                                             | Low                                                                                                                                                                          | Multiplexed                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|            |                 |                  |       |      |                                                | Low                                                                                                              | Low                                                                                                                                                                          | Intel Compatible                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|            |                 |                  |       |      |                                                | Low                                                                                                              | High                                                                                                                                                                         | Motorola Compatible                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|            |                 |                  |       |      | ena 0) adde wa de the ena dev  µP sib the tion | able, re = H,H dress s sist be I rds corvices we same ables fivice, while (1-0) = le, additionality in e Intel e | ead, write<br>only add<br>straps St<br>eft floati<br>mpatibility<br>with the<br>packag<br>unctional<br>hich has<br>H,L only<br>ress strat<br>lead do<br>register<br>compatil | ata leads, select, address latche and interrupt request. When μP(1-dress range 00H-1FH is accessible, 5-S7 are active, and the M13X leading or tied high. This enables backty of the 208-lead PQFP packaged predecessor M13E device that has ge and lead assignments. It also a 160-lead PQFP package. When y address range 00H-3FH is accested as S6-S7 are active and the state of etermines whether the M13X functions 25H-3FH is enabled or disabled. The package interface (80X86 family) consists eads, eight bidirectional data leads, |

|            |                 |                  |       |      | The<br>sis                                     | e Motor<br>ts of e                                                                                               | rola com                                                                                                                                                                     | , ready and interrupt request.  patible interface (680X0 family) con- lress leads, eight bidirectional data d/write, data transfer acknowledge                                                                                                                                                                                                                                                                                                                                                                                                |

|            |                 |                  |       |      | For<br>reg                                     | r both t<br>gisters (<br>gisters                                                                                 | he Intel<br>00H-24H<br>00H-3F                                                                                                                                                | and Motorola compatible interfaces, and Motorola compatible interfaces, are accessible if M13X is high and H are accessible if M13X is low. 6-S7 are active.                                                                                                                                                                                                                                                                                                                                                                                  |

| Symbol                                 | Lead No.<br>BGA                        | Lead No.<br>PQFP                       | I/O/P | Туре         | Name/Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|----------------------------------------|----------------------------------------|----------------------------------------|-------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| \$7<br>\$6<br>\$5                      | N11,<br>P11,<br>T11                    | 85,<br>86,<br>87                       |       | TTLp         | Address Straps: When the Intel, Motorola, or Multiplexed ( $\mu$ P1 is high and $\mu$ P0 is low) microprocessor interfaces are selected, the two address straps, S7 and S6, allow the M13X to be partitioned as a segment of memory. The straps define the address offset of the device. The address register is partitioned as shown below. The data register pointed to by the 6 least significant bits is only accessed if the 2 most significant bits match the address straps.  Address register partition for Intel, Motorola, or Multiplexed ( $\mu$ P1 is high and $\mu$ P0 is low) microprocessor interfaces:  When the multiplexed microprocessor interface is selected, by setting $\mu$ P1 high and $\mu$ P0 high, the three address straps, S7, S6, and S5, allow the M13X to be partitioned as a segment of memory. The straps define the offset of the device. The address register is partitioned as shown below. The data register pointed to by the five least significant bits is only accessed if the three most significant bits match the address straps.  Address register partition for the multiplexed microprocessor interface when $\mu$ P1 is high and $\mu$ P0 is high:  Bit 7 6 5  M13X Register  Address Address |

| A7                                     | P4                                     | 60                                     | ı     | TTLp         | Address Bus (Intel/Motorola):                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| A6<br>A5<br>A4<br>A3<br>A2<br>A1<br>A0 | R4<br>T3<br>R3<br>R2<br>T1<br>R1<br>P2 | 59<br>58<br>57<br>48<br>47<br>46<br>45 | •     | , ι τ. τ. τ. | Multiplexed - These leads are disabled when the multiplexed interface is selected.  Intel/Motorola - These are active high address line inputs that are used by the microprocessor for accessing the M13X registers for a read/write cycle. A7 is the most significant bit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |