# ET4148-50 Single-Chip 48 x 1 Gbit/s + 2 x 10 Gbits/s Layer 2+ Ethernet Switch

## Features

- Forty-eight 10/100/1000 Mbits/s Ethernet ports:

- Forty-four-ports supporting 6-pin SGMII interfaces to GbE copper PHYs

- Four combo ports supporting either SGMII interface or SerDes interface

- Two 10 Gbits/s Ethernet ports with XAUI interfaces:

Direct SerDes connection to local stacking ports

Connects to external 10G PHY for longer reach

- Connects to external TOG PHT for longer reach

- Aggregate 104 Mpackets/s switching capacity (wire speed operation)

- 32-bit, 66 MHz PCI<sup>™</sup> processor interface

- Three MDIO interfaces

- Integrated packet buffer memory

- Integrated address table memories:

8192 Layer 2 MAC addresses

- Full *IEEE*<sup>®</sup> 802.1d<sup>®</sup> bridging

- Extensive VLAN support:

- Port-based VLANs

- Port-/protocol-based VLANs

- 4K VLAN IDs, 256 active VLANs

- Per VLAN rapid-spanning tree

- L2/L3/L4 classification for access control list (ACL) and quality of service (QoS)

- Jumbo frame size up to 16 Kbytes

- Advanced traffic management functions:

- 802.3x flow control

- Traffic shaping and scheduling

- Traffic policing

- Broadcast/multicast storm control

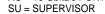

- Eight queues per port

- Link aggregation and mirroring across stacking ports (10 Gbits/s ports)

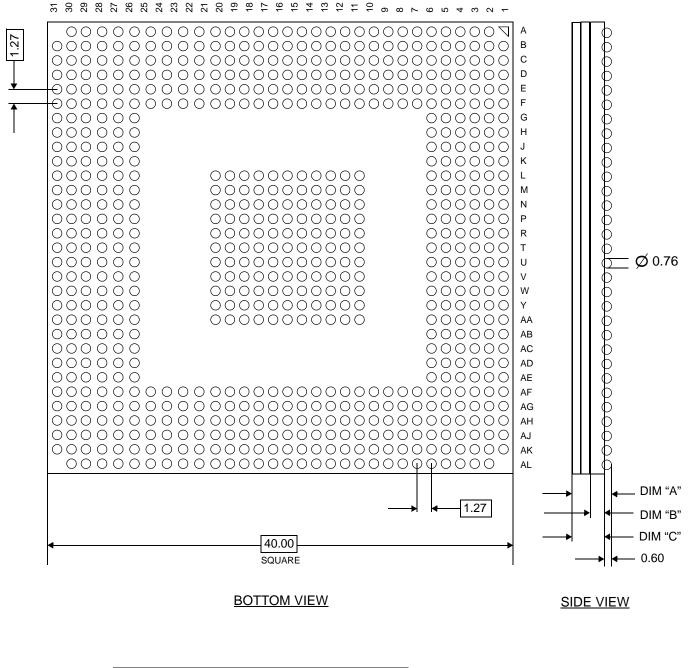

- 717-FCBGA package

## Benefits

- True switch-on-a-chip technology enables system vendors to build competitive 48 + 2 gigabit Ethernet switches

- Integrated memories and SerDes and uplink/stacking ports for lower system power, cost, and PCB area

- Flexible L2/L3/L4 ACL supporting enhanced network security

- Supports native IPv4 and IPv6 prefix and host address matches

- Comprehensive QoS features and wire speed performance supporting enterprise desktop aggregation switching application

- Seamless interface and common API with Agere *TruePHY*<sup>™</sup> multiport PHY

# **Target Applications**

- Fully managed Layer +2 gigabit Ethernet desktop switches

- 48 + 2 gigabit Ethernet switch in stand-alone or stackable configuration

- High-density gigabit Ethernet fabric switches

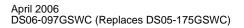

# **Block Diagram**

Figure 1. Block Diagram

# Description

The ET4148-50 is part of Agere's FMS gigabit Ethernet switch product family. The ET4148-50 is a highly integrated and fully featured Layer 2 Ethernet bridge with integrated MACs, packet buffers, and address tables. When combined with six ET1081 Octal PHYs, the ET4148-50 enables the implementation of a minimal component system that translates to low cost and high reliability. The ET4148-50 contains 48 IEEE 802.3z 10/100/1000 Mbits/s Ethernet MACs. The MACs connect to external ET1081 PHYs via 6-pin LVDS SGMII interfaces. Optionally, four of the MACs can be connected to external fiber PHYs via SerDes interfaces. Two 802.3ae Ethernet MACs provide the ET4148-50 with connectivity to 10 Gbits/s networks, uplinks, and stacking interfaces.

The ET4148-50 features an integrated L2/L3/L4 packet classification engine. The result of each packet classification is used to determine the packet's quality of service treatment and access control. Access to the network by individual desktops can be controlled by L2 MAC address and TCP/IP layer provisioning. Each port supports up to eight traffic class queues. Each packet is assigned to a class queue based on the 802.1p coding or IP TOS/DSCP. Incoming traffic is policed to ensure the optimum use of network resources. Outgoing traffic is scheduled or shaped according to the traffic class and network resource usage.

Integrated address tables and packet buffers enable full bandwidth bridging on all ports with any legitimate frame length. All internal operations are at wire speed.

The integrated XAUI SerDes interface supports direct local stacking ports. Optionally, external 10G PHY such as CX-4 or fiber can be used to extend the stacking and uplink port reach.

A reference system design kit is available for the ET4148-50. For more detailed product and reference design information, please contact Agere's local sales office.

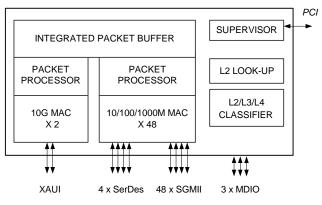

# System Diagram

Figure 2. System Diagram

# **Table of Contents**

### Contents

| Features                                              | 1  |

|-------------------------------------------------------|----|

| Benefits                                              | 1  |

| Target Applications                                   | 1  |

| Block Diagram                                         |    |

| Description                                           |    |

| System Diagram                                        |    |

| Pin Descriptions                                      |    |

| Memory Map                                            |    |

| Functional Description                                |    |

| Packet Reception                                      |    |

| VLAN Assignment                                       |    |

| Access Control                                        |    |

| Bridging                                              |    |

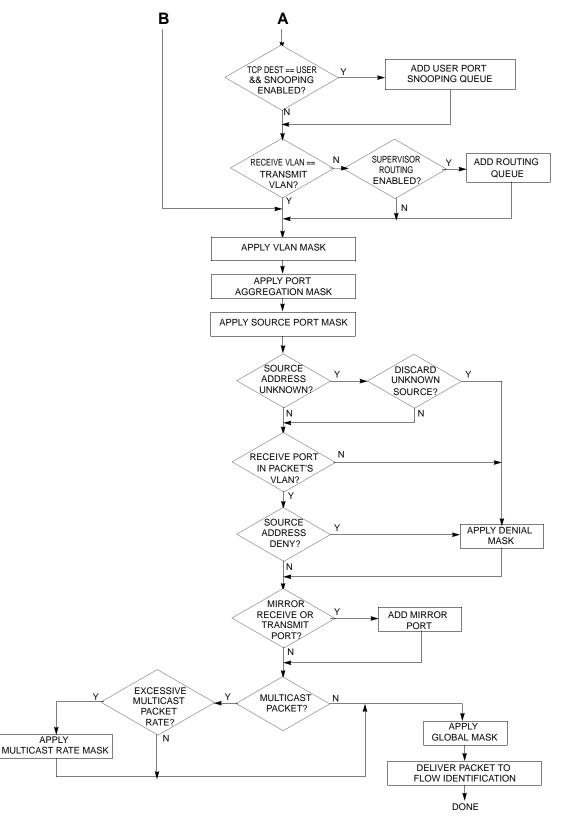

| Flow Identification                                   |    |

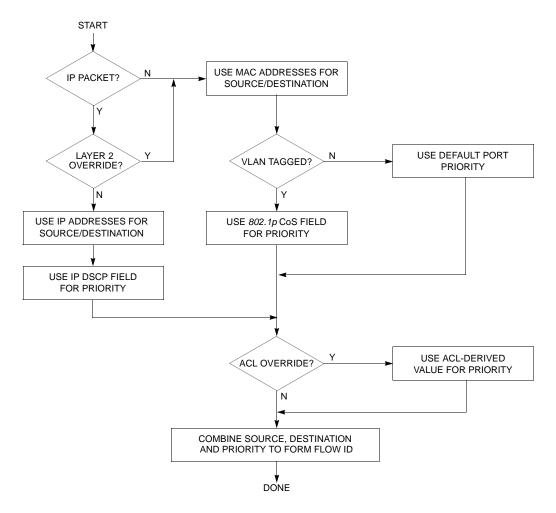

| Policing                                              |    |

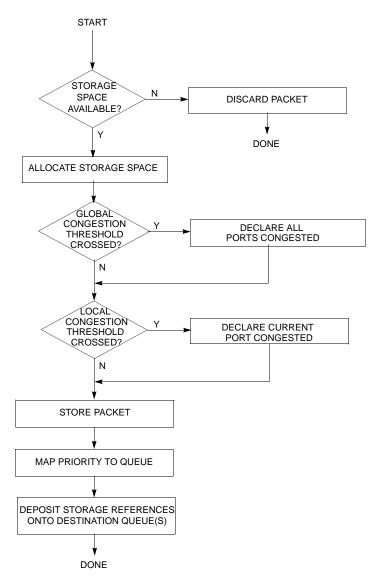

| Storage                                               |    |

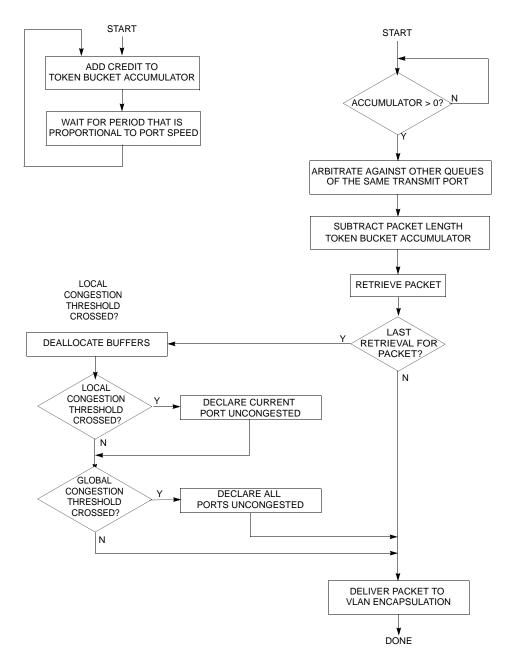

| Retrieval                                             |    |

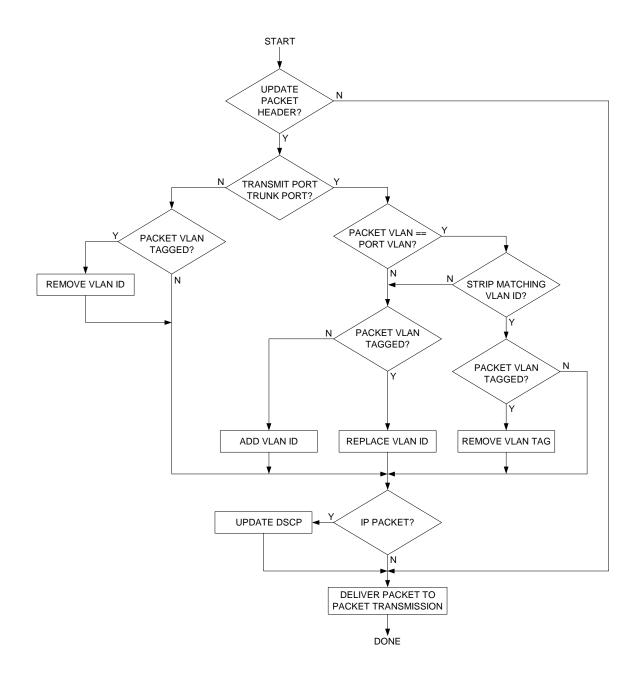

| VLAN Encapsulation                                    |    |

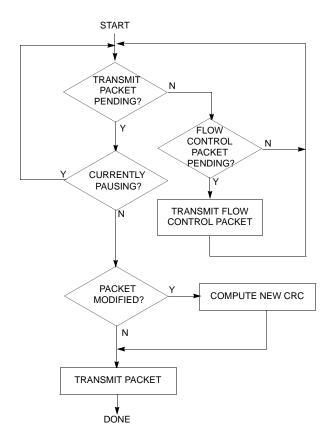

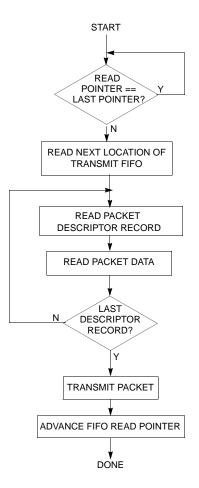

| Packet Transmission                                   |    |

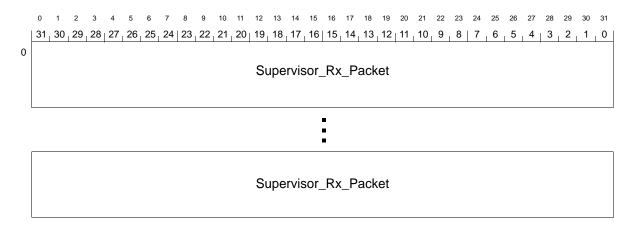

| Supervisor Packet Reception                           |    |

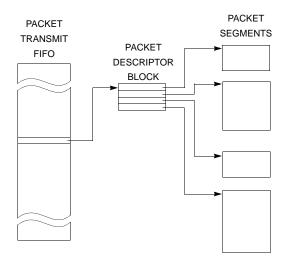

| Supervisor Packet Transmission                        |    |

| Data Structures                                       |    |

| Supervisor_Rx_Fifo_{07}                               |    |

| Supervisor_Rx_Pilo_{07}                               |    |

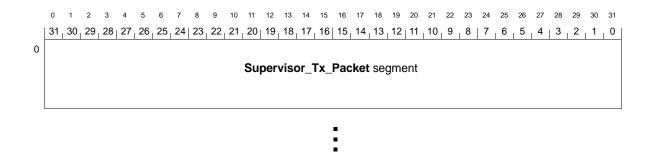

| Supervisor_Tx_Packet                                  |    |

| Supervisor_Tx_Descriptor                              |    |

|                                                       |    |

| Supervisor_Tx_Packet<br>Supervisor_Tx_Packet_Segment  |    |

|                                                       |    |

| Electrical Specifications<br>Absolute Maximum Ratings |    |

| 5                                                     |    |

| ESD Protection                                        |    |

| Recommended Operating Conditions                      |    |

| Power Supply Consumption                              |    |

| Thermal Characteristics                               |    |

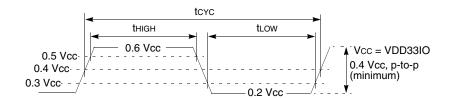

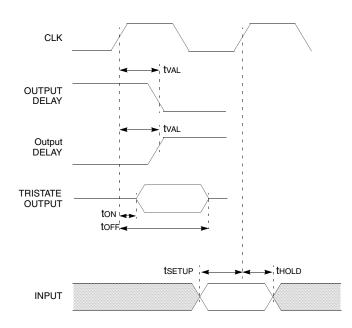

| PCI I/O Specification                                 |    |

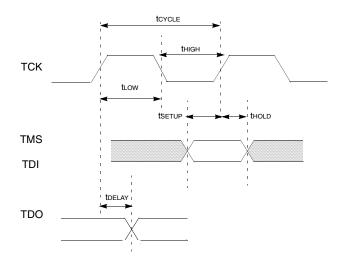

| JTAG I/O Specification                                |    |

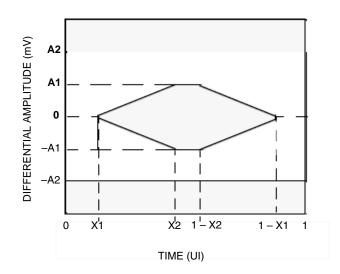

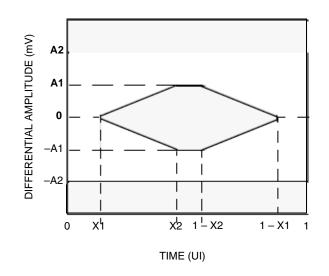

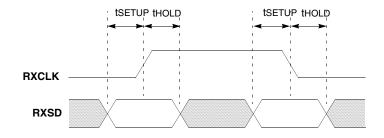

| SGMII I/O Transmit Specifications                     |    |

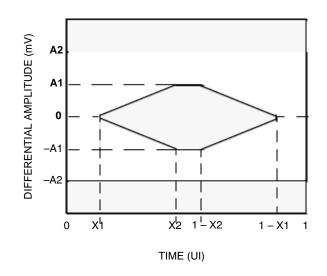

| SGMII I/O Receive Specifications                      |    |

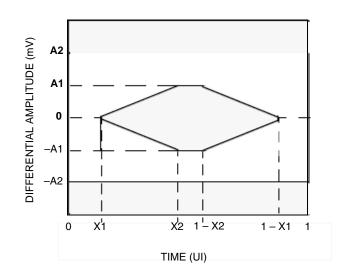

| SFP—1.25 Gbits/s SerDes Specifications                |    |

| 10G—3.125 Gbits/s SerDes Specifications               |    |

| Timing Diagrams                                       |    |

| Physical Dimensions                                   |    |

| Appendix A: Registers                                 |    |

| Registers, Records, and Fields                        |    |

| Instance Numbering                                    |    |

| Line Caching                                          |    |

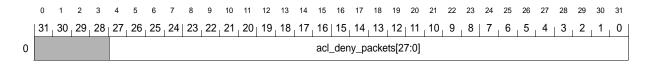

| Acl_Deny_Packets                                      |    |

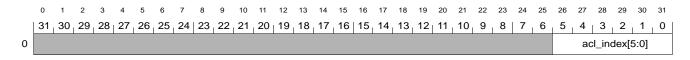

| Acl_En                                                |    |

| Acl_lp_Addr_Ace_Map_Index_Table                       |    |

| Acl_lp_Addr_Ace_Map_Table                             |    |

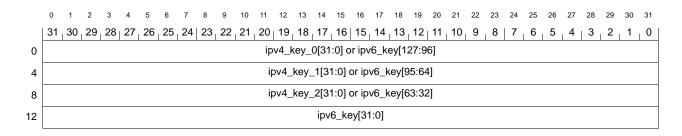

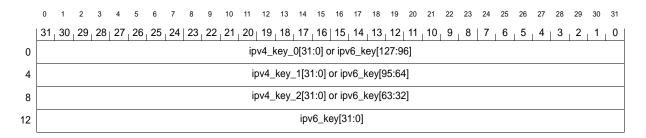

| Acl_lp_Key_Table_0                                    | 76 |

#### Contents

| Ad In Koy Table 1                | 77  |

|----------------------------------|-----|

| Acl_lp_Key_Table_1               |     |

| Acl_Ip_Key_Table_2               |     |

| Acl_lp_Key_Table_3               |     |

| Acl_lp_Key_Table_4               |     |

| Acl_lp_Key_Table_5               |     |

| Acl_lp_Key_Table_6               |     |

| Acl_lp_Key_Table_7               |     |

| Acl_Ip_Key_Table_8               |     |

| Acl_Mode                         |     |

| Acl_Port_Ace_Map_Index_Table     |     |

| Acl_Port_Ace_Map_Table           |     |

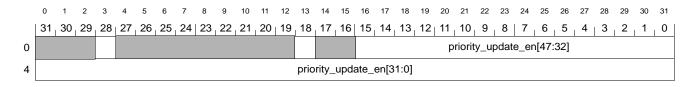

| Acl_Priority_Update_En           |     |

| Acl_Protocol_Ace_Map_Index_Table |     |

| Acl_Protocol_Ace_Map_Table       |     |

| Acl_Protocol_Table               |     |

| Acl_Result_Table                 | 93  |

| Acl_Tcp_Key_Table_0              |     |

| Acl_Tcp_Key_Table_1              |     |

| Acl_Tcp_Key_Table_2              | 96  |

| Acl_Tcp_Key_Table_3              | 97  |

| Acl_Tcp_Key_Table_4              | 98  |

| Acl_Vlan_Index_Table             |     |

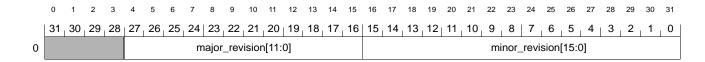

| Device_Version                   |     |

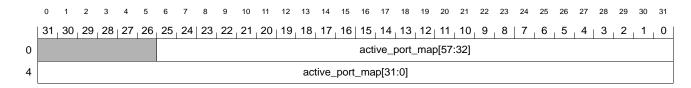

| Layer_2_Active_Port_Map          |     |

| Layer_2_Aggregation_Mask_Table   |     |

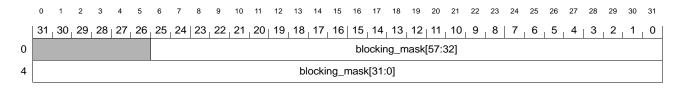

| Layer_2_Blocking_Mask            |     |

| Layer_2_Current_Time             |     |

| Layer_2_Dest_Map_Table           |     |

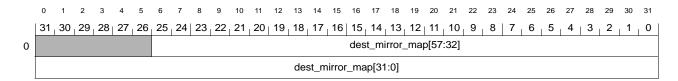

| Layer_2_Dest_Mirror_Map          |     |

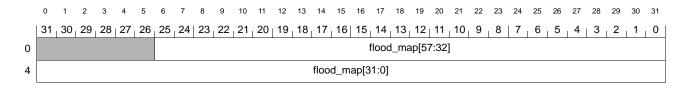

| Layer_2_Flood_Map                |     |

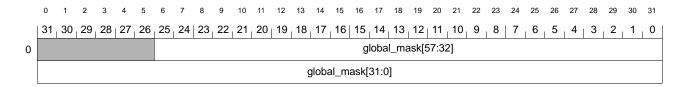

| Layer_2_Global_Mask              |     |

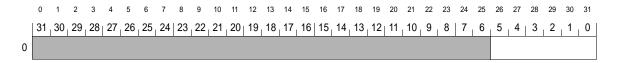

| Layer_2_Igmp_Snooping_Port       | 109 |

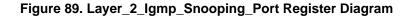

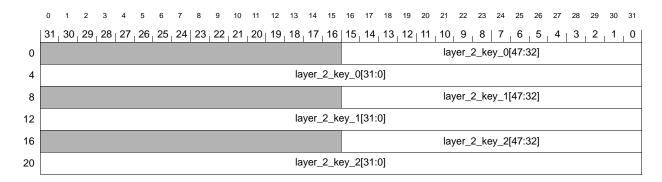

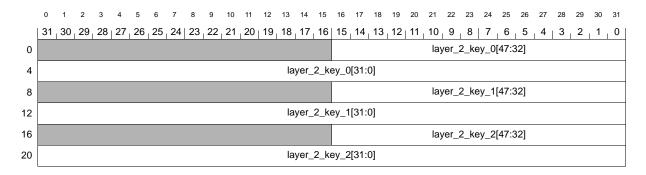

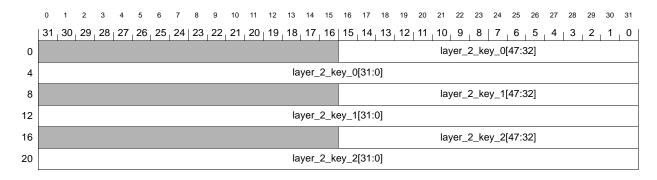

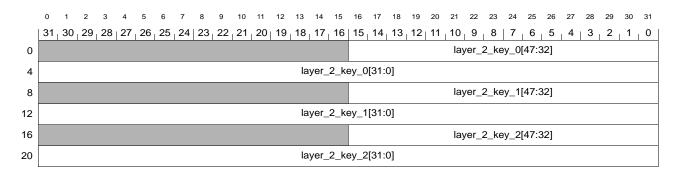

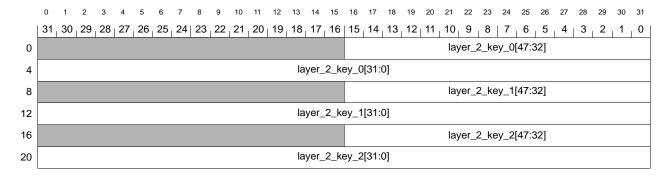

| Layer_2_Key_Table_0              |     |

| Layer_2_Key_Table_1              |     |

| Layer_2_Key_Table_1              |     |

| Layer_2_Key_Table_3              |     |

| Layer_2_Key_Table_5              |     |

| Layer_2_Key_Table_5              |     |

|                                  |     |

| Layer_2_Key_Table_6              |     |

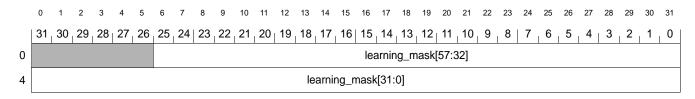

| Layer_2_Learning_Mask            |     |

| Layer_2_Learning_Port            |     |

| Layer_2_Logical_Port_Table       |     |

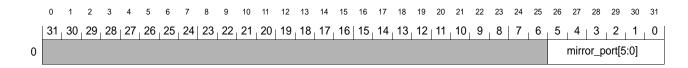

| Layer_2_Mirror_Port              |     |

| Layer_2_Mode                     |     |

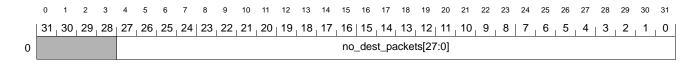

| Layer_2_No_Dest_Packets          |     |

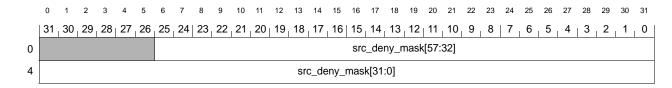

| Layer_2_Src_Deny_Mask            |     |

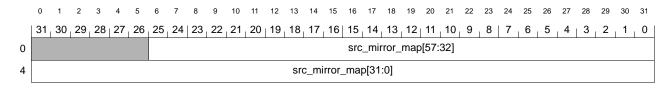

| Layer_2_Src_Mirror_Map           |     |

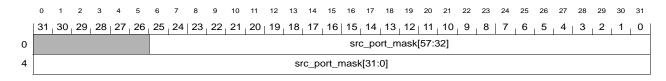

| Layer_2_Src_Port_Mask_Table      |     |

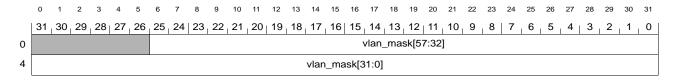

| Layer_2_Supervisor_Route_Port    |     |

| Layer_2_Time_Stamp_Table         |     |

| Layer_2_User_Port                | 129 |

#### Contents

| Layer_2_User_Port_Snooping_Port                             |       |

|-------------------------------------------------------------|-------|

| Layer_2_Vlan_Mask_Table                                     |       |

| Layer_2_Vlan_Port_State_Table                               |       |

| Mac_Global_Mode                                             |       |

| Mac_Mode_{04}                                               |       |

| Mac_Mode_{56}                                               |       |

| Mac_Status_{04}                                             |       |

| Mdio_Control                                                |       |

| Mdio_Mode                                                   |       |

| Mdio_Status                                                 |       |

| Multicast_Rate_Accumulator                                  |       |

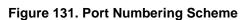

| Multicast_Rate_Decrement_Period                             | . 148 |

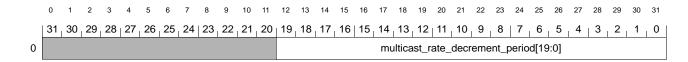

| Multicast_Rate_Discard_Mask                                 |       |

| Multicast_Rate_Limit                                        | . 150 |

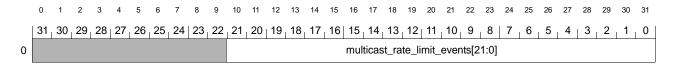

| Multicast_Rate_Limit_Events                                 | . 151 |

| Multicast_Rate_Mode                                         | . 152 |

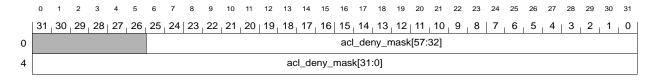

| Packet_Buffer_Acl_Deny_Mask                                 | . 153 |

| Packet_Buffer_Acl_Log_Port                                  | . 154 |

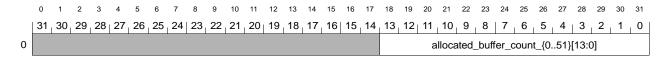

| Packet_Buffer_Allocated_Buffer_Count                        | . 155 |

| Packet_Buffer_Channel_Congestion_Threshold                  | . 156 |

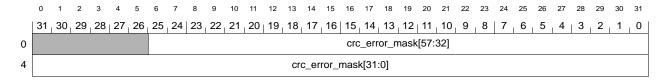

| Packet_Buffer_Crc_Error_Mask                                | . 157 |

| Packet_Buffer_Descriptor_Congestion_Threshold               | . 158 |

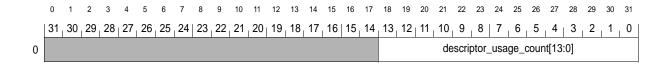

| Packet Buffer Descriptor Usage Count                        | . 159 |

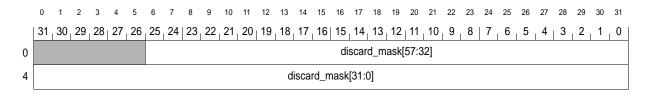

| Packet Buffer Discard Mask                                  | . 160 |

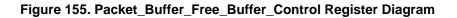

| Packet Buffer Free Buffer Control                           | . 161 |

| Packet Buffer Free Buffer Count Even                        | . 162 |

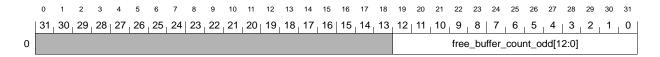

| Packet_Buffer_Free_Buffer_Count_Odd                         |       |

| Packet_Buffer_Free_Descriptor_Control                       |       |

| Packet_Buffer_Global_Congestion_Threshold                   |       |

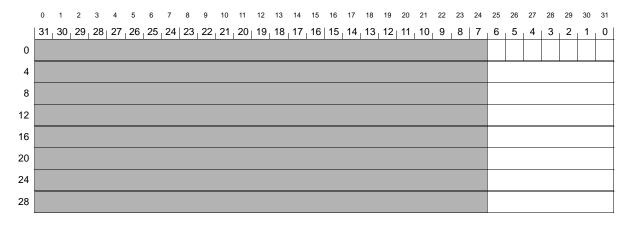

| Packet_Buffer_Ind                                           |       |

| Packet Buffer Mode                                          |       |

| Packet_Buffer_Packet_Drop_Count                             |       |

| Packet_Buffer_Parity_Error_Info                             |       |

| Packet_Buffer_Port_Speed                                    |       |

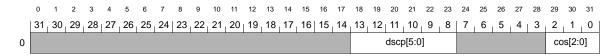

| Packet_Buffer_Priority_Table                                |       |

| Packet_Buffer_Queue_Buffer_Limit (Revision C Only)          |       |

| Packet_Buffer_Queue_Buffers_{03} (Revision C Only)          | .175  |

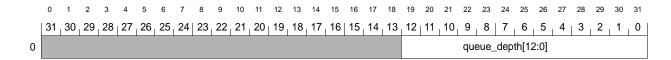

| Packet_Buffer_Queue_Depth_{03} (Revision C Only)            |       |

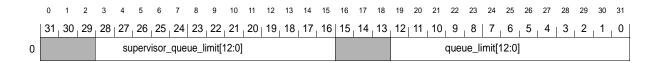

| Packet_Buffer_Queue_Limit (Revision C Only)                 |       |

| Packet_Buffer_Queue_Management_Thresholds (Revision C Only) | 180   |

| Packet_Buffer_Queue_Status                                  |       |

| Packet_Buffer_Queue_Weight                                  |       |

| Packet_Buffer_Scrub                                         |       |

| Packet_Buffer_Shaper_Accumulator_Even                       | 184   |

| Packet_Buffer_Shaper_Accumulator_Odd                        |       |

| Packet_Buffer_Shaper_Delta_Even                             |       |

| Packet_Buffer_Shaper_Delta_Odd                              |       |

| Packet_Buffer_Shaper_Limit                                  |       |

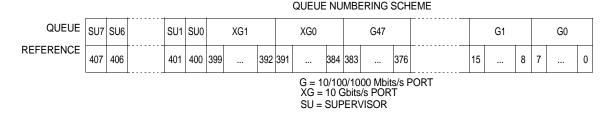

| Policer_Accumulator_Table_{04}                              |       |

| Policer_Accumulator_Table_{04}                              |       |

| Policer_Delta_Table_{04}                                    |       |

|                                                             | . 131 |

#### Contents

| Policer_Delta_Table_{56}              |     |

|---------------------------------------|-----|

| Policer_Flow_Id_Table_{04}            | 194 |

| Policer_Flow_Id_Table_{56}            | 195 |

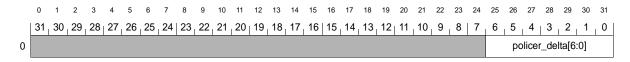

| Policer_Flow_Mode_Table_{04}          | 196 |

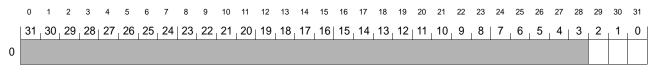

| Policer_Flow_Mode_Table_{56}          | 197 |

| Policer_Limit_Table_{04}              | 198 |

| Policer_Limit_Table_{56}              | 199 |

| Policer_Mode_{04}                     | 200 |

| Policer_Mode_{56}                     | 201 |

| Policer_Statistics_{0.4}              | 202 |

| Policer_Statistics_{56}               |     |

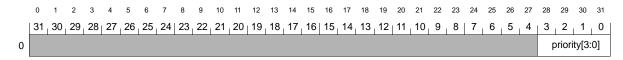

| Port_Mode_{04}                        |     |

| Port_Mode_{56}                        |     |

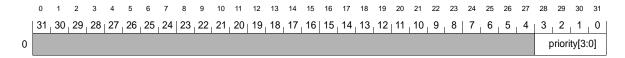

| Priority_Decode_Table_{04}            |     |

| Priority_Decode_Table_{56}            |     |

| Priority_Encode_Table_{04}            |     |

| Priority_Encode_Table_{56}            |     |

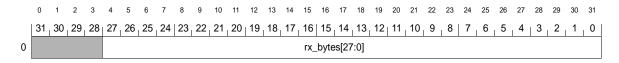

| Rx_Bytes                              |     |

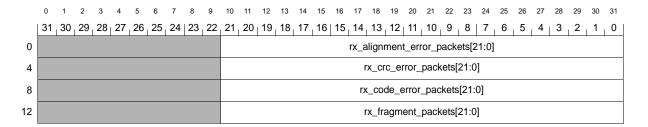

| Rx_Error_Packets                      |     |

| Rx_Length_Histogram                   |     |

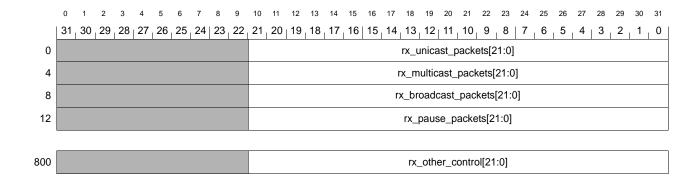

| Rx_Packets                            |     |

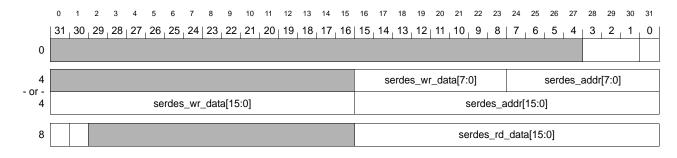

| Serdes_Control_{4}                    |     |

| Serdes_Control_{5}                    |     |

| Supervisor_Endian                     |     |

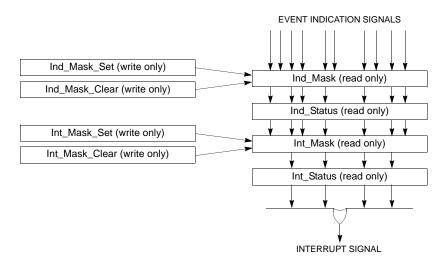

| Supervisor_Ind                        |     |

| Supervisor_Ind_Mask                   |     |

| Supervisor_Ind_Mask_Clear             |     |

| Supervisor_Ind_Mask_Set               |     |

| Supervisor_Int                        |     |

| Supervisor_Int_Mask                   |     |

| Supervisor_Int_Mask_Clear             |     |

| Supervisor_Int_Mask_Set               |     |

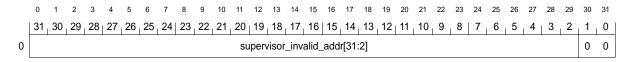

| Supervisor_Invalid_Addr               |     |

| Supervisor_Maximum_Packet_Length      |     |

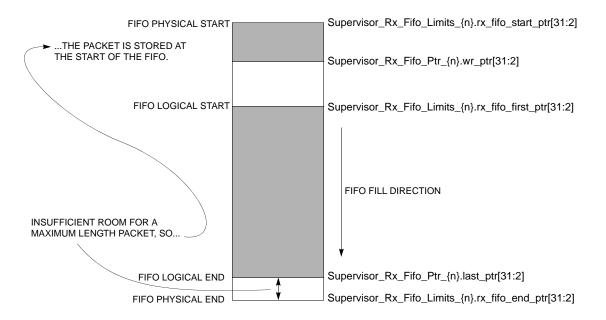

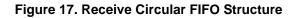

| Supervisor_Rx_Fifo_Limits             |     |

| Supervisor_Rx_Fifo_Ptr                |     |

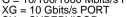

| Supervisor_Statistics_Transfer_Addr   |     |

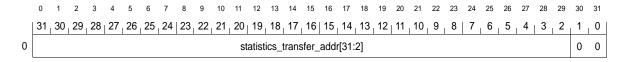

| Supervisor_Statistics_Transfer_Status |     |

| Supervisor_Tx_Fifo_Limits             |     |

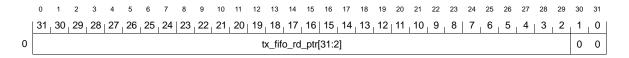

| Supervisor_Tx_Fifo_Ptr                |     |

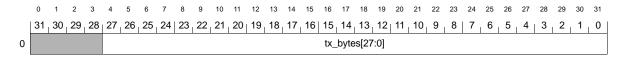

| Tx_Bytes                              |     |

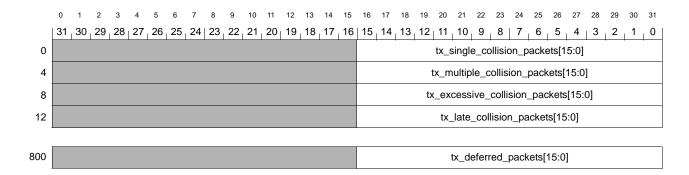

| Tx_Collision_Histogram                |     |

| Tx_Length_Histogram                   |     |

| Tx_Packets                            |     |

| Tx_Total_Collisions                   |     |

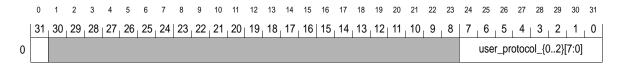

| User_Protocol_{04}                    |     |

| User_Protocol_{56}                    |     |

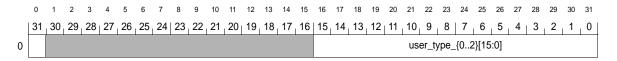

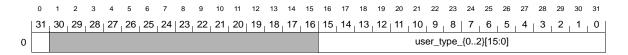

| User_Type_{04}                        |     |

| User_Type_{56}                        |     |

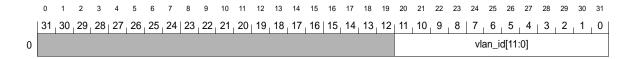

| Vlan_Id_Table_{04}                    |     |

| Vlan_Id_Table_{56}                    |     |

|                                       |     |

#### Contents

| Vlan_Index_Table_{04}         |  |

|-------------------------------|--|

| Vlan_Index_Table_{56}         |  |

| Vlan_Port_Protocol_Table_{04} |  |

| Vlan_Port_Protocol_Table_{56} |  |

| Appendix B: Configuration     |  |

| General                       |  |

| Packet Buffer                 |  |

| Ethernet Interfaces           |  |

| Bridging                      |  |

| Access Control Lists          |  |

| Quality of Service            |  |

| Other Networking Functions    |  |

| Statistics                    |  |

| Other Device Functions        |  |

| Ordering Information          |  |

| Related Documentation         |  |

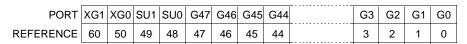

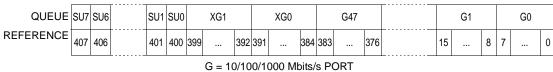

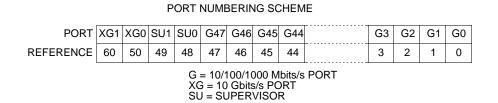

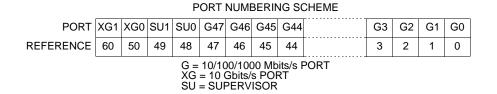

# **Pin Descriptions**

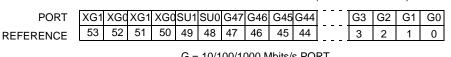

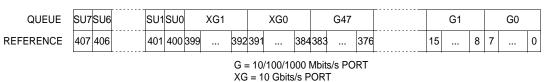

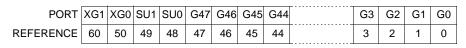

The ET4148-50 pins are summarized in the following series of tables. Each table is dedicated to a single interface type.

#### Table 1. 1 Gbit/s Ethernet SGMII Pins

| Pin Name           | Туре           | Pin #s                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Description                                                             |

|--------------------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|

| RXCLK(47:00)_(P/N) | LVDS<br>input  | 47{AL13, AL12}, 46{AF13, AF12}, 45{AL11, AL10}, 44{AJ10,<br>AJ9}, 43{AF10, AF9}, 42{AJ7, AJ6}, 41{AF8, AF7},<br>40{AJ5, AJ4}, 39{AK1, AJ1}, 38{AG4, AF4}, 37{AG2, AF2},<br>36{AE4, AD4}, 35{AE1, AD1}, 34{AB2, AA2}, 33{AA5, Y5},<br>32{AA1, Y1}, 31{Y4, W4}, 30{V3, U3}, 29{T3, R3}, 28{R4, P4},<br>27{N4, M4}, 26{N2, M2}, 25{L4, K4}, 24{K1, J1}, 23{J5, H5},<br>22{G2, F2}, 21{H6, G6}, 20{E2, D2}, 19{B3, B4}, 18{D5, D6},<br>17{A4, A5}, 16{D7, D8}, 15{A7, A8}, 14{D10, D11}, 13{A9, A10},<br>12{B12, B13}, 11{E13, E14}, 10{C14, C15}, 09{C16, C17},<br>08{F17, F18}, 07{B19, B20}, 06{F19, F20}, 05{B21, B22},<br>04{C22, C23}, 03{E23, E24}, 02{C25, C26}, 01{D26, D27},<br>00{C27, C28} | SGMII receive<br>clock differential<br>pairs.                           |

| RXSD(47:00)_(P/N)  | LVDS<br>input  | 47(AH13, AH12), 46{AJ12, AJ11}, 45{AH11, AH10}, 44{AL9,<br>AL8}, 43{AH8, AH7}, 42{AL5, AL4}, 41{AH6, AH5},<br>40{AL3, AL2}, 39{AH3, AG3}, 38{AF5, AE5}, 37{AF3, AE3},<br>36{AC6, AB6}, 35{AC3, AB3}, 34{AA3, Y3}, 33{Y6, W6},<br>32{Y2, W2}, 31{V6, U6}, 30{T1, R1}, 29{P1, N1}, 28{R6, P6},<br>27{N6, M6}, 26{M1, L1}, 25{K3, J3}, 24{H1, G1}, 23{K6, J6},<br>22{E1, D1}, 21{G5, F5}, 20{C1, B1}, 19{C4, C5}, 18{F7, F8},<br>17{C6, C7}, 16{F9, F10}, 15{C9, C10}, 14{F12, F13},<br>13{C11, C12}, 12{A13, A14}, 11{F14, F15}, 10{D15, D16},<br>09{D17, D18}, 08{D19, D20}, 07{A20, A21}, 06{D21, D22},<br>05{A22, A23}, 04{B23, B24}, 03{F22, F23}, 02{A27, A28},<br>01{E25, E26}, 00{A29, A30}   | SGMII receive<br>data differential<br>pairs.                            |

| TXSD(47:00)_(P/N)  | LVDS<br>output | 47{AK11, AK12}, 46{AG11, AG12}, 45{AK9, AK10}, 44{AG8,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | SGMII transmit<br>data differential<br>pairs.                           |

| REFCLK25_(2:0)     | CMOS<br>input  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Reference clock<br>for SGMII ports.<br>Each should be<br>set to 25 MHz. |

#### Table 2. 1 Gbit/s Ethernet SFP Pins

| Pin Name           | Туре          | Pin #s                                                            | Description                                                                                   |

|--------------------|---------------|-------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|

| RXSSD(47:44)_(P,N) | CML input     | 47{AJ19, AJ20}, 46{AL18, AL19},<br>45{AJ16, AJ17}, 44{AL15, AL16} | SFP SerDes receive differential pair.                                                         |

| TXSSD(47:44)_(P,N) | CML<br>output | 47{AF19, AF20}, 46{AH18, AH19},<br>45{AF16, AF17}, 44{AH15, AH16} | SFP SerDes transmit differential pair.                                                        |

| REFCLK_3_(P,N)     | CML input     | {AJ14, AJ15}                                                      | SFP SerDes differential clock<br>input—LVDS or LVPECL levels<br>compatible. 125 MHz nominal.  |

| RESP_3             | REF           | AK15                                                              | SFP SerDes reference resistor connection. Tie to VSSRESP_3 through a 1.5 k $\Omega$ resistor. |

| VSSRESP_3          | REF           | AK14                                                              | GND connection for RESP_3.                                                                    |

#### Table 3. 10 Gbit/s Ethernet XAUI Pins

| Pin Name           | Туре          | Pin #s                                                    | Description                                                                                              |

|--------------------|---------------|-----------------------------------------------------------|----------------------------------------------------------------------------------------------------------|

| RXSD48_(3:0)_(P,N) | CML input     | 03{U29, T29}, 02{U27, T27}, 01{V31,<br>U31}, 00{V28, U28} | 10 Gbits/s SerDes receive differential pairs. A port consists of four 3.125 Gbits/s pairs.               |

| RXSD49_(3:0)_(P,N) | CML input     | 03{P27, N27}, 02{P29, N29}, 01{R28,<br>P28}, 00{R31, P31} | 10 Gbits/s SerDes receive differential pairs. A port consists of four 3.125 Gbits/s pairs.               |

| TXSD48_(3:0)_(P,N) | CML<br>output | 03{J31, H31}, 02{L29, K29}, 01{M28,<br>L28}, 00{M31, L31} | 10 Gbits/s SerDes transmit differen-<br>tial pairs. A port consists of four 3.125<br>Gbits/s pairs.      |

| TXSD49_(3:0)_(P,N) | CML<br>output | 03{H26, G26}, 02{H29, G29}, 01{J28,<br>H28}, 00{L26, K26} | 10 Gbits/s SerDes transmit differen-<br>tial pairs. A port consists of four 3.125<br>Gbits/s pairs.      |

| REFCLK_4_(P,N)     | CML input     | {Y29, W29}                                                | 10 Gbits/s SerDes differential clock<br>input—LVDS or LVPECL levels com-<br>patible. 156.25 MHz nominal. |

| RESP_4             | REF           | V26                                                       | 10 Gbits/s SerDes reference resistor connection. Tie to VSSRESP_4 through a 1.5 k $\Omega$ resistor.     |

| VSSRESP_4          | REF           | Y27                                                       | GND connection for RESP_4.                                                                               |

#### Table 4. Supervisor PCI Pins

| Pin Name   | Туре                        | Pin #s                                                                                                                                                                                                                                                                                                                                                       | Description                                             |

|------------|-----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|

| PCI_RST_N  | CMOS input                  | AA27                                                                                                                                                                                                                                                                                                                                                         | PCI reset. Active-low.                                  |

| PCI_CLK    | CMOS input                  | AL28                                                                                                                                                                                                                                                                                                                                                         | PCI bus clock.                                          |

| AD(31:0)   | CMOS I/O                    | 31{AB30}, 30{AB28}, 29{AA26},<br>28{AC30}, 27{AC31}, 26{AB26},<br>25{AC27}, 24{AD31}, 23{AC29},<br>22{AD28}, 21{AD27}, 20{AC26},<br>19{AD26}, 18{AE27}, 17{AF31},<br>16{AE29}, 15{AH29}, 14{AJ30},<br>13{AJ31}, 12{AK31}, 11{AL30},<br>10{AK29}, 09{AL29}, 08{AK28},<br>07{AJ28}, 06{AG25}, 05{AK27},<br>04{AF25}, 03{AH27}, 02{AG26},<br>01{AJ27}, 00{AH26} | <i>PCI</i> address and data bus.                        |

| CBE[3:0]_N | CMOS I/O                    | 3{AD30}, 2{AE30}, 1{AH30}, 0{AA29}                                                                                                                                                                                                                                                                                                                           | <i>PCI</i> command and byte-enable signals. Active-low. |

| PAR        | CMOS I/O                    | AG29                                                                                                                                                                                                                                                                                                                                                         | PCI parity signal.                                      |

| FRAME_N    | CMOS I/O                    | AE26                                                                                                                                                                                                                                                                                                                                                         | PCI cycle frame signal. Active-low.                     |

| IRDY_N     | CMOS I/O                    | AF30                                                                                                                                                                                                                                                                                                                                                         | PCI initiator ready signal. Active-low.                 |

| TRDY_N     | CMOS I/O                    | AF29                                                                                                                                                                                                                                                                                                                                                         | PCI target ready signal. Active-low.                    |

| DEVSEL_N   | CMOS I/O                    | AF27                                                                                                                                                                                                                                                                                                                                                         | PCI device select signal. Active-low.                   |

| STOP_N     | CMOS I/O                    | AG28                                                                                                                                                                                                                                                                                                                                                         | PCI stop signal. Active-low.                            |

| PERR_N     | CMOS I/O                    | AG31                                                                                                                                                                                                                                                                                                                                                         | PCI parity error signal. Active-low.                    |

| SERR_N     | CMOS I/O                    | AG30                                                                                                                                                                                                                                                                                                                                                         | PCI system error signal. Active-low.                    |

| IDSEL      | CMOS input                  | AD29                                                                                                                                                                                                                                                                                                                                                         | PCI initialization device select signal.                |

| REQ_N      | CMOS output                 | AB31                                                                                                                                                                                                                                                                                                                                                         | PCI bus request signal. Active-low.                     |

| GNT_N      | CMOS input                  | AB29                                                                                                                                                                                                                                                                                                                                                         | PCI bus grant signal. Active-low.                       |

| INTA_N     | CMOS output<br>(open drain) | AA28                                                                                                                                                                                                                                                                                                                                                         | PCI interrupt. Active-low.                              |

| LOCK_N     | CMOS input                  | AF28                                                                                                                                                                                                                                                                                                                                                         | PCI lock signal. Active-low.                            |

#### Table 5. Miscellaneous Pins

| Pin Name       | Туре                     | Pins #s                                                                                           | Description                                                                                                                                                                                                                                                                                                      |

|----------------|--------------------------|---------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TDI            | CMOS input               | E31                                                                                               | JTAG serial data in.                                                                                                                                                                                                                                                                                             |

| ТСК            | CMOS input               | E30                                                                                               | JTAG clock.                                                                                                                                                                                                                                                                                                      |

| TMS            | CMOS input               | D31                                                                                               | JTAG test mode select.                                                                                                                                                                                                                                                                                           |

| TRST_N         | CMOS input               | E29                                                                                               | JTAG test reset. Active-low. Pull low for normal operation.                                                                                                                                                                                                                                                      |

| TDO            | CMOS output              | C31                                                                                               | JTAG serial data out.                                                                                                                                                                                                                                                                                            |

| MDIO_C22_(1:0) | CMOS I/O<br>(open drain) | 1{AL24}, 0{AK22}                                                                                  | Serial management data I/O signal.<br>Clause 22 compatible.                                                                                                                                                                                                                                                      |

| MDC_C22_(1:0)  | CMOS output              | 1{AH22}, 0{AG22}                                                                                  | Serial management clock signal.<br>Clause 22 compatible.                                                                                                                                                                                                                                                         |

| MDIO_C45       | CMOS I/O<br>(open drain) | AL25                                                                                              | Serial management data I/O signal.<br>Clause 45 compatible.                                                                                                                                                                                                                                                      |

| MDC_C45        | CMOS output              | AK24                                                                                              | Serial management clock signal.<br>Clause 45 compatible.                                                                                                                                                                                                                                                         |

| SE             | CMOS input               | AJ26                                                                                              | Reserved—scan enable. Pull low for normal operation.                                                                                                                                                                                                                                                             |

| TM(2:0)        | CMOS input               | 2{D29}, 1{C30}, 0{B31}                                                                            | Reserved—test mode select. Pull low for normal operation.                                                                                                                                                                                                                                                        |

| TST(9:0)       | CMOS output              | 9{AK25}, 8{AF22}, 7{AJ24},<br>6{AH24}, 5{AJ25}, 4{AL26},<br>3{AG23}, 2{AH23}, 1{AF24},<br>0{AJ23} | Reserved—test mode output. Leave unconnected.                                                                                                                                                                                                                                                                    |

| VM(1:0)        | CMOS output              | 1{Y28}, 0{Y30}                                                                                    | Reserved—voltage monitor output.<br>Leave unconnected.                                                                                                                                                                                                                                                           |

| RREF(2:0)      | REF                      | 2{AF14}, 1{T4}, 0{B16}                                                                            | Bias reference—pull to ground with individual 2.49 k $\Omega$ resistors.                                                                                                                                                                                                                                         |

| VREF           | REF                      | C2                                                                                                | Reference voltage—set to 1.23 V. ± 1%.                                                                                                                                                                                                                                                                           |

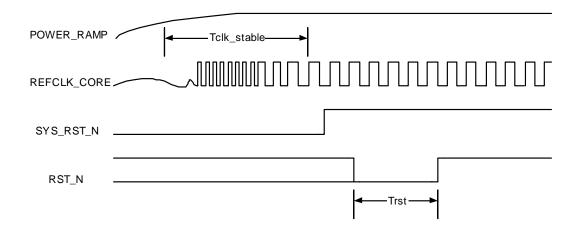

| RST_N          | CMOS input               | AA31                                                                                              | Chip reset, active-low. During pow-<br>erup, this signal should be held low<br>for at least 200 ns after power has<br>ramped and REFCLK_CORE<br>(25 MHz) is stable. If the system is<br>already powered up and stable, the<br>signal may be pulsed low for 200 ns<br>or more. See Device Reset in<br>Appendix B. |

| REFCLK_CORE    | CMOS input               | AJ22                                                                                              | Reference clock for the core of the chip. 25 MHz.                                                                                                                                                                                                                                                                |

#### Table 6. Power and Ground

| Pin Name            | Туре | Pin Numbers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Description                                            |

|---------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|

| VDD12_CORE          | PWR  | M15, M13, M11, L20, L18, L16, L14, L12, AA20,<br>AA14, AA12, P13, P11, N20, N18, N16, N14, N12,<br>M21, M19, M17, T15, T13, T11, R18, R16, R14,<br>R12, P19, P17, P15, V17, V15, V13, V11, U18,<br>U16, U14, U12, T19, T17, Y15, Y13, Y11, W20,<br>W18, W16, W14, W12, V21, V19, Y21, Y19                                                                                                                                                                                                                                 | Core power supply. 1.2 V,<br>nominal.                  |

| VSS_CORE            | GND  | AD3, AC28, AB5, AA21, AA19, AA15, AA13, AA11, A6, A26, AK8, Y26, Y20, Y14, Y12, W3, W21, W19, W17, W15, W13, W11, V20, V18, V16, V14, V12, U5, U19, U17, U15, U13, U11, T18, T16, T14, T12, R19, R17, R15, R13, R11, P18, P16, P14, P12, N3, N21, N19, N17, N15, AJ13, AH31, AH28, AH25, AG5, AG10, AF6, AF26, AF23, AF1, C13, B30, B2, B18, AL27, AK30, AK23, AK2, AJ8, AJ3, E22, E15, E10, D4, D28, C8, C3, C29, C24, C19, L17, L15, L13, L11, K5, H3, F6, F1, E5, E27, N13, N11, M20, M18, M16, M14, M12, L21, L2, L19 | Core ground.                                           |

| VDD15L              | PWR  | AF11, AK7, AE2, AA6, T6, L6,<br>J4, D9, D14, B17, F21, B25                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Analog power supply for<br>SGMII I/O. 1.5 V, nominal.  |

| VDD33               | PWR  | D30, AK26, AJ29, AG27, AG24,<br>AF21, AE31, AE28, AB27, AA30                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Power supply. 3.3 V nominal.                           |

| VDD33L              | PWR  | V4, P3, K2, F16, F11, D23,<br>C18, B7, AK13, AH9, AH4, AC4                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Power supply. SGMII I/O.<br>3.3 V, nominal.            |

| AVDD12_PLL          | PWR  | AG14, U1, A15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Analog power supply for<br>SGMII PLLs. 1.2 V, nominal. |

| AGND_PLL            | GND  | AG13, T2, A17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Analog ground for SGMII<br>PLLs.                       |

| AVDD12_PLL_CORE     | PWR  | AL23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Analog power supply for core<br>PLLs. 1.2 V, nominal.  |

| AGND_PLL_CORE       | GND  | AL22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Analog ground for core PLLs.                           |

| VDDIB_(47:44)       | PWR  | AK20, AK19, AK17, AK16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Analog input buffer power supply. 1.5 V, nominal.      |

| VDDOB_(47:44)       | PWR  | AG20, AG19, AG17, AG16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Analog output buffer power supply. 1.5 V, nominal.     |

| VDDIB_(49:48)_(3:0) | PWR  | N26, N30, P26, P30, T30, T26, U30, U26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Analog input buffer power supply. 1.5 V, nominal.      |

| VDDOB_(49:48)_(3:0) | PWR  | G27, G30, H27, K27, H30, K30, L27, L30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Analog output buffer power supply. 1.5 V, nominal.     |

| VDD_3               | PWR  | AL21, AL14, AJ21, AJ18, AH20, AH14,<br>AG21, AF18, Y17, AA18, AA16                                                                                                                                                                                                                                                                                                                                                                                                                                                        | SFP power supply. 1.2 V, nominal.                      |

| VDD_4               | PWR  | W31, W28, W26, V29, T31, T28, R29, R26, N31,<br>N28, M29, M26, K31, K28, J29, J26, G31, G28,<br>F29, F26, U20, T21, R20, P21                                                                                                                                                                                                                                                                                                                                                                                              | XAUI power supply. 1.2 V, nominal.                     |

| VSS_3               | GND  | AA17, AL20, AL17, AK21, AK18, AH21,<br>AH17, AG18, AG15, Y18, Y16                                                                                                                                                                                                                                                                                                                                                                                                                                                         | SFP ground.                                            |

| VSS_4               | GND  | Y31, W30, W27, V30, V27, R30, R27, M30, M27,<br>J30, J27, F31, F30, F28, F27, E28, U21, T20, R21,<br>P20                                                                                                                                                                                                                                                                                                                                                                                                                  | XAUI ground.                                           |

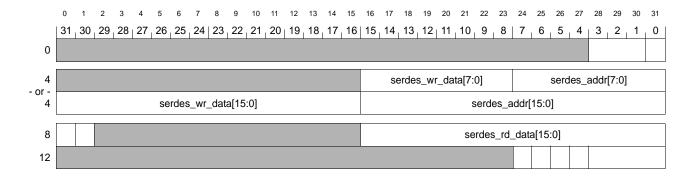

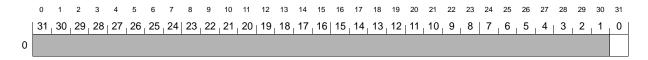

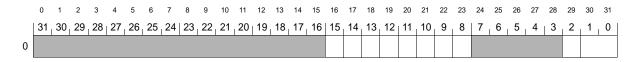

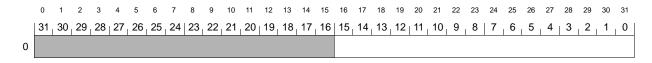

## **Memory Map**

The following table lists all of the ET4148-50's registers in the order that they appear in the address space allocated to the device. The base addresses listed below must be added to the base address configured for the device in order to arrive at the actual physical address of each register.

#### Table 7. Memory Map

| Base Address | Size   | Register Name                    |

|--------------|--------|----------------------------------|

| 0x0000_0000  | 131072 | Acl_lp_Addr_Ace_Map_Index_Table  |

| 0x0002_0000  | 65536  | Acl_Port_Ace_Map_Index_Table     |

| 0x0003_0000  | 16384  | Acl_lp_Key_Table_8               |

| 0x0003_4000  | 16384  | Acl_Result_Table                 |

| 0x0003_8000  | 16384  | Acl_lp_Key_Table_5               |

| 0x0003_c000  | 8192   | Acl_lp_Addr_Ace_Map_Table        |

| 0x0003_e000  | 4096   | Acl_lp_Key_Table_4               |

| 0x0003_f000  | 4096   | Acl_Tcp_Key_Table_4              |

| 0x0004_0000  | 2048   | Acl_Port_Ace_Map_Table           |

| 0x0004_0800  | 2048   | Acl_lp_Key_Table_7               |

| 0x0004_1000  | 1024   | Acl_Vlan_Index_Table             |

| 0x0004_1400  | 1024   | Acl_Protocol_Ace_Map_Table       |

| 0x0004_1800  | 1024   | Acl_lp_Key_Table_6               |

| 0x0004_1c00  | 1024   | Acl_lp_Key_Table_3               |

| 0x0004_2000  | 512    | Acl_Tcp_Key_Table_3              |

| 0x0004_2200  | 256    | Acl_Protocol_Table               |

| 0x0004_2300  | 64     | Acl_lp_Key_Table_2               |

| 0x0004_2480  | 32     | Acl_lp_Key_Table_1               |

| 0x0004_24c0  | 32     | Acl_Tcp_Key_Table_1              |

| 0x0004_24e0  | 16     | Acl_lp_Key_Table_0               |

| 0x0004_24f0  | 8      | Acl_Tcp_Key_Table_0              |

| 0x0004_24f8  | 4      | Acl_Mode                         |

| 0x0004_2500  | 8      | Acl_En                           |

| 0x0004_2508  | 8      | Acl_Deny_Packets                 |

| 0x0004_2510  | 8      | Acl_Priority_Update_En           |

| 0x0004_2800  | 2048   | Acl_Protocol_Ace_Map_Index_Table |

| 0x0004_3000  | 128    | Acl_Tcp_Key_Table_2              |

| 0x0004_4000  | 2048   | Rx_Length_Histogram              |

| 0x0004_4800  | 2048   | Tx_Length_Histogram              |

| 0x0004_5000  | 1024   | Tx_Collision_Histogram           |

| 0x0004_5400  | 256    | Tx_Total_Collisions              |

| 0x0004_5800  | 1024   | Rx_Error_Packets                 |

| 0x0004_5c00  | 1024   | Rx_Packets                       |

| 0x0004_6000  | 1024   | Tx_Packets                       |

| 0x0004_6400  | 256    | Rx_Bytes                         |

| 0x0004_6500  | 256    | Tx_Bytes                         |

| 0x0004_8000  | 16384  | Vlan_Index_Table_0               |

| 0x0004_c000  | 4096   | Policer_Flow_Id_Table_0          |

| 0x0004_d000  | 1024   | Vlan_Id_Table_0                  |

| 0x0004_d400  | 512    | Policer_Accumulator_Table_0      |

Agere Systems Inc.

#### Table 7. Memory Map (continued)

| Base Address | Size  | Register Name               |

|--------------|-------|-----------------------------|

| 0x0004_d600  | 512   | Policer_Delta_Table_0       |

| 0x0004_d800  | 512   | Policer_Flow_Mode_Table_0   |

| 0x0004_da00  | 512   | Policer_Limit_Table_0       |

| 0x0004_dc00  | 512   | Vlan_Port_Protocol_Table_0  |

| 0x0004_de00  | 256   | Priority_Encode_Table_0     |

| 0x0004_df00  | 128   | Priority_Decode_Table_0     |

| 0x0004_df80  | 64    | Port_Mode_0                 |

| 0x0004_dfc0  | 16    | User_Protocol_0             |

| 0x0004_dfd0  | 16    | User_Type_0                 |

| 0x0004_dfe0  | 4     | Policer_Mode_0              |

| 0x0004_e000  | 1024  | Policer_Statistics_0        |

| 0x0005_0000  | 16384 | Vlan_Index_Table_1          |

| 0x0005_4000  | 4096  | Policer_Flow_Id_Table_1     |

| 0x0005_5000  | 1024  | Vlan_Id_Table_1             |

| 0x0005_5400  | 512   | Policer_Accumulator_Table_1 |

| 0x0005_5600  | 512   | Policer_Delta_Table_1       |

| 0x0005_5800  | 512   | Policer_Flow_Mode_Table_1   |

| 0x0005_5a00  | 512   | Policer_Limit_Table_1       |

| 0x0005_5c00  | 512   | Vlan_Port_Protocol_Table_1  |

| 0x0005_5e00  | 256   | Priority_Encode_Table_1     |

| 0x0005_5f00  | 128   | Priority_Decode_Table_1     |

| 0x0005_5f80  | 64    | Port_Mode_1                 |

| 0x0005_5fc0  | 16    | User_Protocol_1             |

| 0x0005_5fd0  | 16    | User_Type_1                 |

| 0x0005_5fe0  | 4     | Policer_Mode_1              |

| 0x0005_6000  | 1024  | Policer_Statistics_1        |

| 0x0005_8000  | 16384 | Vlan_Index_Table_2          |

| 0x0005_c000  | 4096  | Policer_Flow_Id_Table_2     |

| 0x0005_d000  | 1024  | Vlan_Id_Table_2             |

| 0x0005_d400  | 512   | Policer_Accumulator_Table_2 |

| 0x0005_d600  | 512   | Policer_Delta_Table_2       |

| 0x0005_d800  | 512   | Policer_Flow_Mode_Table_2   |

| 0x0005_da00  | 512   | Policer_Limit_Table_2       |

| 0x0005_dc00  | 512   | Vlan_Port_Protocol_Table_2  |

| 0x0005_de00  | 256   | Priority_Encode_Table_2     |

| 0x0005_df00  | 128   | Priority_Decode_Table_2     |

| 0x0005_df80  | 64    | Port_Mode_2                 |

| 0x0005_dfc0  | 16    | User_Protocol_2             |

| 0x0005_dfd0  | 16    | User_Type_2                 |

| 0x0005_dfe0  | 4     | Policer_Mode_2              |

| 0x0005_e000  | 1024  | Policer_Statistics_2        |

| 0x0006_0000  | 16384 | Vlan_Index_Table_3          |

| 0x0006_4000  | 4096  | Policer_Flow_Id_Table_3     |

#### Table 7. Memory Map (continued)

| Base Address | Size  | Register Name               |

|--------------|-------|-----------------------------|

| 0x0006_5000  | 1024  | Vlan_Id_Table_3             |

| 0x0006_5400  | 512   | Policer_Accumulator_Table_3 |

| 0x0006_5600  | 512   | Policer_Delta_Table_3       |

| 0x0006_5800  | 512   | Policer_Flow_Mode_Table_3   |

| 0x0006_5a00  | 512   | Policer_Limit_Table_3       |

| 0x0006_5c00  | 512   | Vlan_Port_Protocol_Table_3  |

| 0x0006_5e00  | 256   | Priority_Encode_Table_3     |

| 0x0006_5f00  | 128   | Priority_Decode_Table_3     |

| 0x0006_5f80  | 64    | Port_Mode_3                 |

| 0x0006_5fc0  | 16    | User_Protocol_3             |

| 0x0006_5fd0  | 16    | User_Type_3                 |

| 0x0006_5fe0  | 4     | Policer_Mode_3              |

| 0x0006_6000  | 1024  | Policer_Statistics_3        |

| 0x0006_8000  | 16384 | Vlan_Index_Table_4          |

| 0x0006_c000  | 4096  | Policer_Flow_Id_Table_4     |

| 0x0006_d000  | 1024  | Vlan_Id_Table_4             |

| 0x0006_d400  | 512   | Policer_Accumulator_Table_4 |

| 0x0006_d600  | 512   | Policer_Delta_Table_4       |

| 0x0006_d800  | 512   | Policer_Flow_Mode_Table_4   |

| 0x0006_da00  | 512   | Policer_Limit_Table_4       |

| 0x0006_dc00  | 512   | Vlan_Port_Protocol_Table_4  |

| 0x0006_de00  | 256   | Priority_Encode_Table_4     |

| 0x0006_df00  | 128   | Priority_Decode_Table_4     |

| 0x0006_df80  | 64    | Port_Mode_4                 |

| 0x0006_dfc0  | 16    | User_Protocol_4             |

| 0x0006_dfd0  | 16    | User_Type_4                 |

| 0x0006_dfe0  | 4     | Policer_Mode_4              |

| 0x0006_e000  | 1024  | Policer_Statistics_4        |

| 0x0007_0000  | 16384 | Vlan_Index_Table_5          |

| 0x0007_4000  | 4096  | Policer_Flow_Id_Table_5     |

| 0x0007_5000  | 1024  | Vlan_Id_Table_5             |

| 0x0007_5400  | 512   | Policer_Accumulator_Table_5 |

| 0x0007_5600  | 512   | Policer_Delta_Table_5       |

| 0x0007_5800  | 512   | Policer_Flow_Mode_Table_5   |

| 0x0007_5a00  | 512   | Policer_Limit_Table_5       |

| 0x0007_5c00  | 32    | Vlan_Port_Protocol_Table_5  |

| 0x0007_5e00  | 256   | Priority_Encode_Table_5     |

| 0x0007_5f00  | 128   | Priority_Decode_Table_5     |

| 0x0007_5f80  | 4     | Port_Mode_5                 |

| 0x0007_5fc0  | 16    | User_Protocol_5             |

| 0x0007_5fd0  | 16    | User_Type_5                 |

| 0x0007_5fe0  | 4     | Policer_Mode_5              |

| 0x0007_6000  | 1024  | Policer_Statistics_5        |

Agere Systems Inc.

### Table 7. Memory Map (continued)

| Base Address | Size   | Register Name                  |

|--------------|--------|--------------------------------|

| 0x0007_8000  | 16384  | Vlan_Index_Table_6             |

| 0x0007_c000  | 4096   | Policer_Flow_Id_Table_6        |

| 0x0007_d000  | 1024   | Vlan_Id_Table_6                |

| 0x0007_d400  | 512    | Policer_Accumulator_Table_6    |

| 0x0007_d600  | 512    | Policer_Delta_Table_6          |

| 0x0007_d800  | 512    | Policer_Flow_Mode_Table_6      |

| 0x0007_da00  | 512    | Policer_Limit_Table_6          |

| 0x0007_dc00  | 32     | Vlan_Port_Protocol_Table_6     |

| 0x0007_de00  | 256    | Priority_Encode_Table_6        |

| 0x0007_df00  | 128    | Priority_Decode_Table_6        |

| 0x0007_df80  | 4      | Port_Mode_6                    |

| 0x0007_dfc0  | 16     | User_Protocol_6                |

| 0x0007_dfd0  | 16     | User_Type_6                    |

| 0x0007_dfe0  | 4      | Policer_Mode_6                 |

| 0x0007_e000  | 1024   | Policer_Statistics_6           |

| 0x0008_0000  | 131072 | Layer_2_Key_Table_6            |

| 0x000a_0000  | 65536  | Layer_2_Vlan_Port_State_Table  |

| 0x000b_0000  | 32768  | Layer_2_Key_Table_5            |

| 0x000b_8000  | 32768  | Layer_2_Time_Stamp_Table       |

| 0x000c_0000  | 8192   | Layer_2_Key_Table_4            |

| 0x000c_2000  | 4096   | Layer_2_Dest_Map_Table         |

| 0x000c_3000  | 2048   | Layer_2_Key_Table_3            |

| 0x000c_3800  | 2048   | Layer_2_Vlan_Mask_Table        |

| 0x000c_4000  | 512    | Layer_2_Key_Table_2            |

| 0x000c_4200  | 512    | Layer_2_Src_Port_Mask_Table    |

| 0x000c_4400  | 128    | Layer_2_Key_Table_1            |

| 0x000c_4480  | 64     | Layer_2_Aggregation_Mask_Table |

| 0x000c_4500  | 256    | Layer_2_Logical_Port_Table     |

| 0x000c_4600  | 32     | Layer_2_Key_Table_0            |

| 0x000c_4620  | 8      | Layer_2_Active_Port_Map        |

| 0x000c_4628  | 8      | Layer_2_Blocking_Mask          |

| 0x000c_4630  | 8      | Layer_2_Dest_Mirror_Map        |

| 0x000c_4638  | 8      | Layer_2_Flood_Map              |

| 0x000c_4640  | 8      | Layer_2_Global_Mask            |

| 0x000c_4648  | 8      | Layer_2_Learning_Mask          |

| 0x000c_4650  | 8      | Layer_2_Src_Deny_Mask          |

| 0x000c_4658  | 8      | Layer_2_Src_Mirror_Map         |

| 0x000c_4660  | 4      | Layer_2_Current_Time           |

| 0x000c_4664  | 4      | Layer_2_Igmp_Snooping_Port     |

| 0x000c_4668  | 4      | Layer_2_Learning_Port          |

| 0x000c_466c  | 4      | Layer_2_Mirror_Port            |

| 0x000c_4674  | 4      | Layer_2_Supervisor_Route_Port  |

| 0x000c_4678  | 4      | Layer_2_User_Port              |

#### Table 7. Memory Map (continued)

| Base Address | Size | Register Name                              |

|--------------|------|--------------------------------------------|

| 0x000c_467c  | 4    | Layer_2_User_Port_Snooping_Port            |

| 0x000c_4680  | 4    | Layer_2_No_Dest_Packets                    |

| 0x000c_4700  | 244  | Layer_2_Mode                               |

| 0x000c_4800  | 8    | Multicast_Rate_Discard_Mask                |

| 0x000c_4808  | 4    | Multicast_Rate_Limit                       |

| 0x000c_480c  | 4    | Multicast_Rate_Decrement_Period            |

| 0x000c_4810  | 4    | Multicast_Rate_Limit_Events                |

| 0x000c_4814  | 4    | Multicast_Rate_Accumulator                 |

| 0x000c_4818  | 4    | Multicast_Rate_Mode                        |

| 0x000c_8000  | 64   | Mac_Mode_0                                 |

| 0x000c_8050  | 4    | Mac_Status_0                               |

| 0x000c_8080  | 64   | Mac_Mode_1                                 |

| 0x000c_80d0  | 4    | Mac_Status_1                               |

| 0x000c_8100  | 64   | Mac_Mode_2                                 |

| 0x000c_8150  | 4    | Mac_Status_2                               |

| 0x000c_8180  | 64   | Mac_Mode_3                                 |

| 0x000c_81d0  | 4    | Mac_Status_3                               |

| 0x000c_8200  | 64   | Mac_Mode_4                                 |

| 0x000c_8240  | 12   | Serdes_Control_4                           |

| 0x000c_8250  | 4    | Mac_Status_4                               |

| 0x000c_8280  | 16   | Serdes_Control_5                           |

| 0x000c_8290  | 4    | Mac_Mode_5                                 |

| 0x000c_82d0  | 4    | Mac_Mode_6                                 |

| 0x000c_8300  | 4    | Mdio_Control                               |

| 0x000c_8304  | 4    | Mdio_Status                                |

| 0x000c_8308  | 4    | Mdio_Mode                                  |

| 0x000c_8310  | 16   | Mac_Global_Mode                            |

| 0x000c_8320  | 4    | Device_Version                             |

| 0x000c_a000  | 2048 | Packet_Buffer_Queue_Weight                 |

| 0x000c_a800  | 1024 | Packet_Buffer_Shaper_Accumulator_Even      |

| 0x000c_ac00  | 1024 | Packet_Buffer_Shaper_Accumulator_Odd       |

| 0x000c_b000  | 1024 | Packet_Buffer_Shaper_Delta_Even            |

| 0x000c_b400  | 1024 | Packet_Buffer_Shaper_Delta_Odd             |

| 0x000c_b800  | 256  | Packet_Buffer_Channel_Congestion_Threshold |

| 0x000c_b900  | 256  | Packet_Buffer_Allocated_Buffer_Count       |

| 0x000c_ba00  | 256  | Packet_Buffer_Queue_Status                 |

| 0x000c_bb00  | 64   | Packet_Buffer_Packet_Drop_Count            |

| 0x000c_bb40  | 32   | Packet_Buffer_Ind                          |

| 0x000c_bb60  | 16   | Packet_Buffer_Descriptor_Usage_Count       |

| 0x000c_bb70  | 4    | Packet_Buffer_Free_Buffer_Control          |

| 0x000c_bb74  | 4    | Packet_Buffer_Free_Descriptor_Control      |

| 0x000c_bb78  | 4    | Packet_Buffer_Parity_Error_Info            |

| 0x000c_bb80  | 4    | Packet_Buffer_Scrub                        |

Agere Systems Inc.

#### Table 7. Memory Map (continued)

| Base Address    | Size | Register Name                                               |

|-----------------|------|-------------------------------------------------------------|

| 0x000c_bb84     | 4    | Packet_Buffer_Free_Buffer_Count_Even                        |

| 0x000c_bb88     | 4    | Packet_Buffer_Free_Buffer_Count_Odd                         |

| 0x000c_bc00     | 64   | Packet_Buffer_Priority_Table                                |

| 0x000c_bc40     | 8    | Packet_Buffer_Acl_Deny_Mask                                 |

| 0x000c_bc48     | 8    | Packet_Buffer_Crc_Error_Mask                                |

| 0x000c_bc50     | 8    | Packet_Buffer_Discard_Mask                                  |

| 0x000c_bc58     | 4    | Packet_Buffer_Acl_Log_Port                                  |

| 0x000c_bc5c     | 4    | Packet_Buffer_Descriptor_Congestion_Threshold               |

| 0x000c_bc60     | 4    | Packet_Buffer_Global_Congestion_Threshold                   |

| 0x000c_bc64     | 4    | Packet_Buffer_Mode                                          |

| 0x000c_bc68     | 4    | Packet_Buffer_Shaper_Limit                                  |

| 0x000c_bd00     | 192  | Packet_Buffer_Port_Speed                                    |

| 0x000c_c400     | 64   | Supervisor_Rx_Fifo_Ptr                                      |

| 0x000c_c440     | 8    | Supervisor_Tx_Fifo_Ptr                                      |

| 0x000c_c448     | 4    | Supervisor_Ind                                              |

| 0x000c_c44c     | 4    | Supervisor_Ind_Mask                                         |

| 0x000c_c450     | 4    | Supervisor_Ind_Mask_Clear                                   |

| 0x000c_c454     | 4    | Supervisor_Ind_Mask_Set                                     |

| 0x000c_c458     | 4    | Supervisor_Int                                              |

| 0x000c_c45c     | 4    | Supervisor_Int_Mask                                         |

| 0x000c_c460     | 4    | Supervisor_Int_Mask_Clear                                   |

| 0x000c_c464     | 4    | Supervisor_Int_Mask_Set                                     |

| 0x000c_c468     | 4    | Supervisor_Invalid_Addr                                     |

| 0x000c_c46c     | 4    | Supervisor_Statistics_Transfer_Addr                         |

| 0x000c_c470     | 4    | Supervisor_Statistics_Transfer_Status                       |

| 0x000c_c480     | 128  | Supervisor_Rx_Fifo_Limits                                   |

| 0x000c_c500     | 32   | Supervisor_Tx_Fifo_Limits                                   |

| 0x000c_c520     | 4    | Supervisor_Endian                                           |

| 0x000c_c540     | 32   | Supervisor_Maximum_Packet_Length                            |

| 0x000c_d000     | 428  | Packet_Buffer_Queue_Depth_0 (revision C only)               |

| 0x000c_d200     | 428  | Packet_Buffer_Queue_Depth_1 (revision C only)               |

| 0x000c_d400     | 428  | Packet_Buffer_Queue_Depth_2 (revision C only)               |

| 0x000c_d600     | 428  | Packet_Buffer_Queue_Depth_3 (revision C only)               |

| 0x000c_da00     | 424  | Packet_Buffer_Queue_Buffer_0 (revision C only)              |

| 0x000c_dc00     | 424  | Packet_Buffer_Queue_Buffer_1 (revision C only)              |

| 0x000c_de00     | 424  | Packet_Buffer_Queue_Buffer_2 (revision C only)              |

| 0x000c_e000     | 424  | Packet_Buffer_Queue_Buffer_3 (revision C only)              |

| 0x000c_e200     | 4    | Packet_Buffer_Queue_Buffer_Limit (revision C only)          |

| <br>0x000c_e204 | 4    | Packet_Buffer_Queue_Limit (revision C only)                 |

| 0x000c_e208     | 4    | Packet_Buffer_Queue_Management_Thresholds (revision C only) |

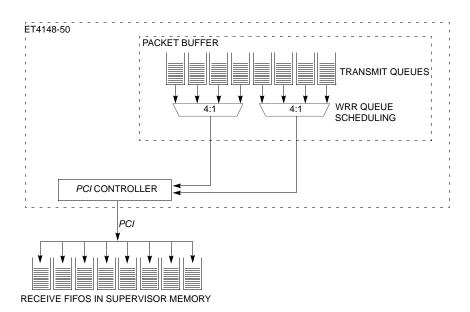

## **Functional Description**

This chapter describes the packet-handling processes embedded within the ET4148-50.

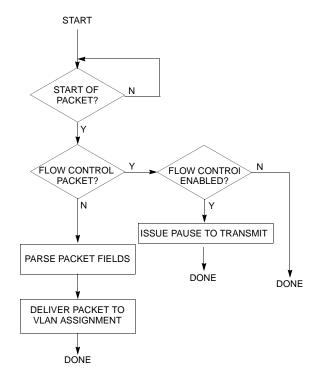

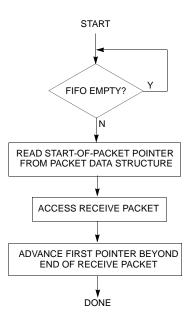

#### Packet Reception

The packet reception process quite simply receives packets from the attached network, immediately processes control packets, parses the remaining packets, and delivers the received packets to the next process.

Figure 3. Packet Reception Process

The packet reception process is rather straight forward. If a receive packet is a flow-control packet and flow control is enabled, an indication is provided to the MAC's corresponding transmit function that causes it to cease transmitting for a specified period of time. All other packets are parsed and then passed along to the VLAN assignment process.

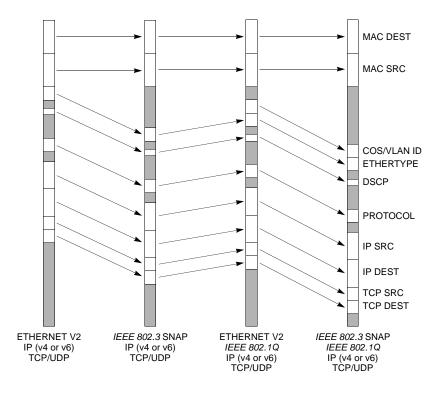

The following figure shows the various packet formats that are supported by the ET4148-50's parser function.

### Packet Reception (continued)

**Figure 4. Packet Formats**

The packet reception process automatically restarts after each packet.

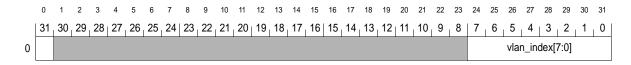

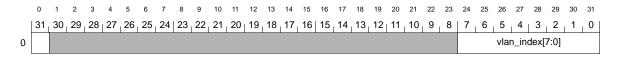

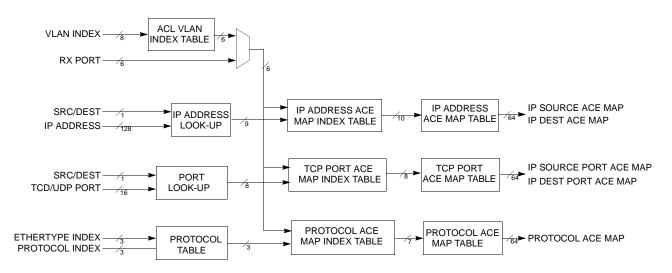

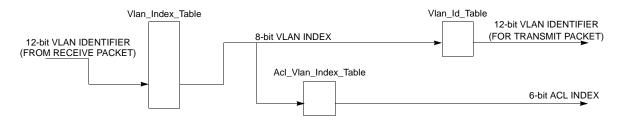

#### **VLAN Assignment**

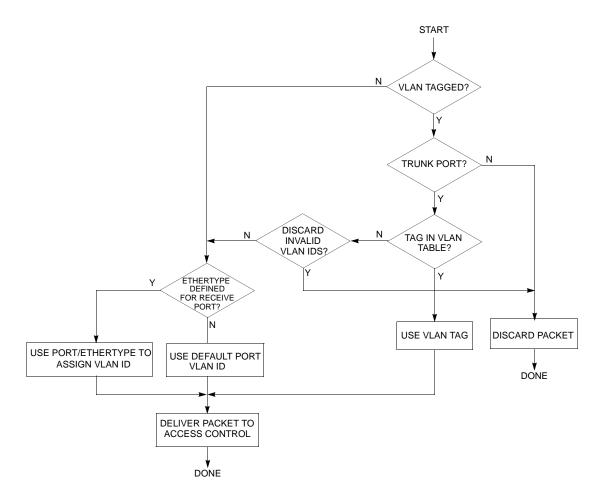

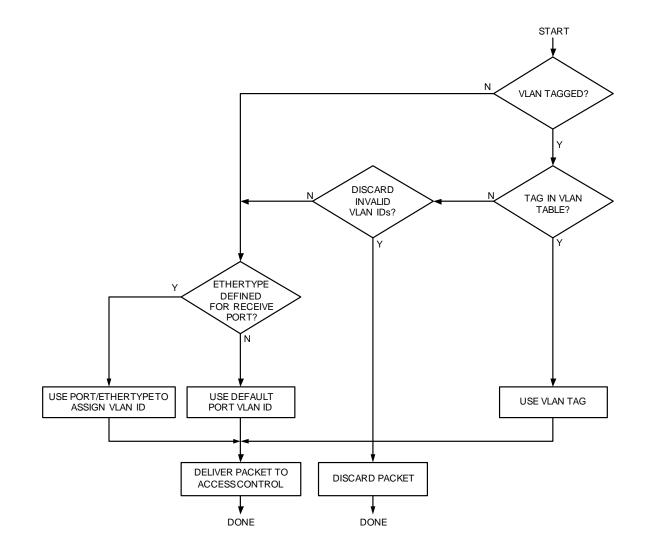

All packets received by the ET4148-50 are assigned to a VLAN. Some packets are received with a VLAN tag in place. For the remainder of the packets, other aspects of the packets must be used to determine to which VLAN the packet is to be assigned.

Figure 5. VLAN Assignment Process—Revisions B and B1

In version B and B1, VLAN tagged packets may only be received by those Ethernet ports that are configured as trunk ports. If a tagged packet is received via an access port, it is discarded. In version C, VLAN tagged packets may be received by either access-configured or trunk-configured Ethernet ports. The VLAN identifiers in tagged packets must also exist in the ET4148-50's VLAN index table. Packets with invalid VLAN tags may be optionally discarded. If packets with invalid VLAN tags are not discarded, they are treated as if they are untagged packets.

For untagged packets, an attempt is made to assign the packet to a VLAN based on its combination of receive port and ethertype. If the combination found in the receive packet is not present in the port/protocol tables, then the receive port's default VLAN identifier is used for the receive packet.

Upon completion of the VLAN assignment process, the packet is delivered to the access control process.

## VLAN Assignment (continued)

Figure 6. VLAN Assignment Process—Revision C

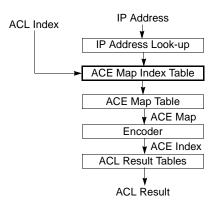

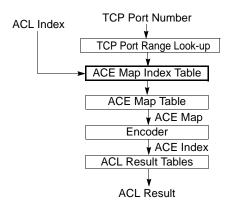

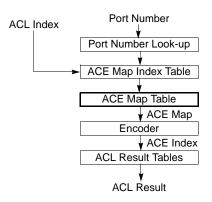

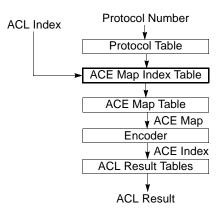

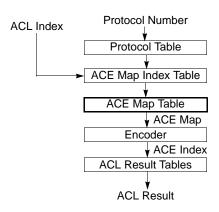

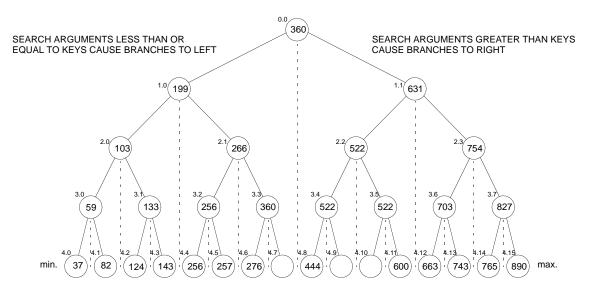

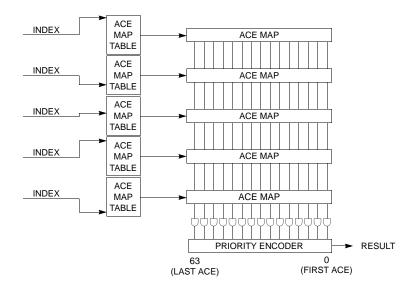

### Access Control

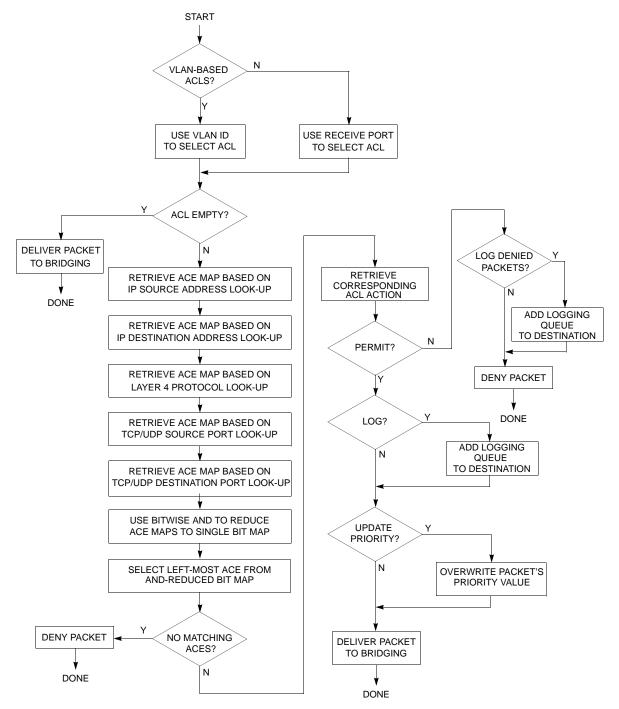

The access control process examines certain fields within each receive packet and determines whether or not the packets should be granted access to the ET4148-50 and its attached networks.

Figure 7. Access Control Process

### Access Control (continued)

Receive packets are associated with access control lists (ACLs) based on either their receive port or the VLAN to which they've been assigned. If the ACL associated with a receive packet is empty, then the packet is automatically permitted to be received and processed normally. No further action is taken by the ACL process in this case.

For a nonempty ACL, each of the packet's fields that make up the ACL 5-tuple are submitted to a look-up, which ultimately results in the gathering of five access control entry (ACE) map values. These ACE maps indicate which of the ACEs that make up the ACL have criteria that are satisfied by the corresponding field in the receive packet.

For example, a TCP destination port value of 3,027 may satisfy one rule that stipulates a range of 3,000 to 4,000 and another that specifies all values less than 7,000. In this example, 2 bits in the corresponding ACE map are asserted with each bit indicating which ACE has matching criteria.

Once all five ACE maps have been retrieved, they are ANDed together in a bitwise fashion to indicate those ACEs where all five criteria are satisfied by the fields in the receive packet. The leftmost bit in the resulting ACE map indicates the first ACE in the ACL that matches all of the criteria. In the case where multiple ACEs match the against the receive packet, it is the one that appears first in the ACL that is applied to the receive packet.

The actions that may be carried out as a result of a matching ACE are as follows:

- 1. Packet denial or permission

- 2. Packet logging

- 3. Priority reassignment

The ET4148-50 may also be configured to automatically log all denied packets.

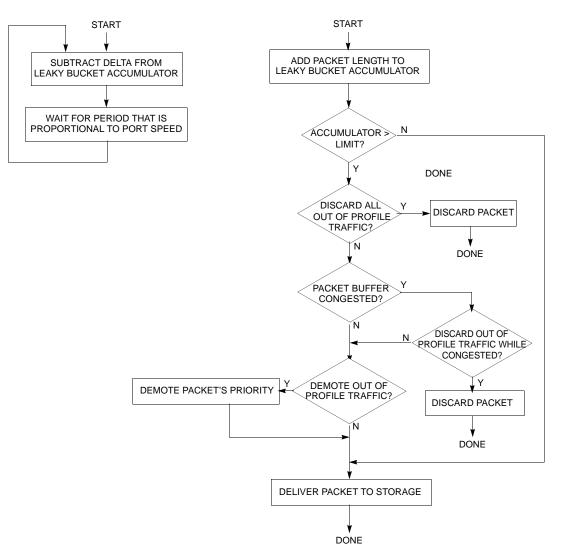

### Bridging

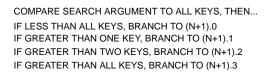

The ET4148-50's bridging process utilizes Layer 2 information from the packet as a primary means for determining the destination or destinations of a receive packet.

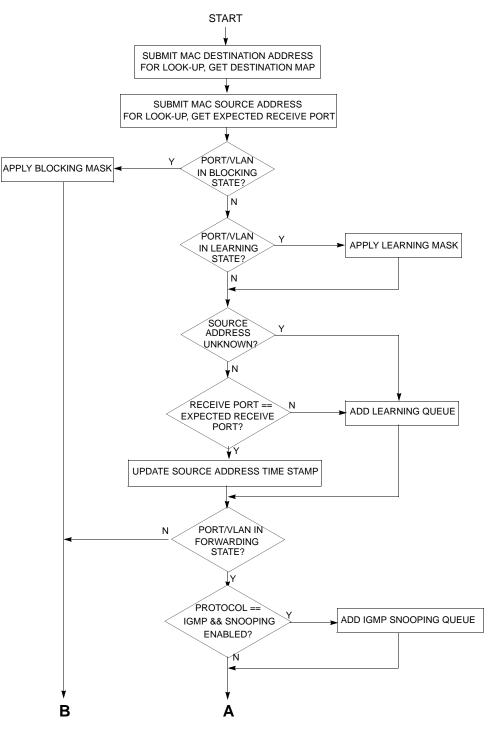

Figure 8. Bridging Process (Part 1)

#### Bridging (continued)

Figure 9. Bridging Process (Part 2)

Agere Systems Inc.

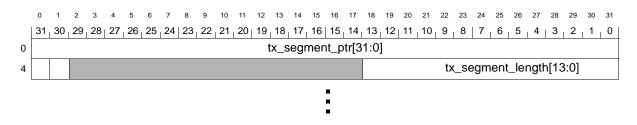

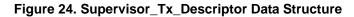

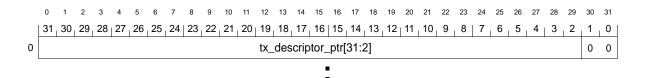

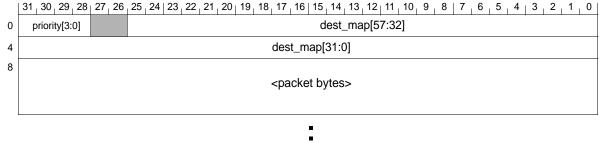

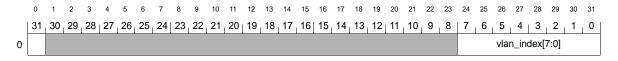

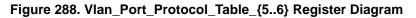

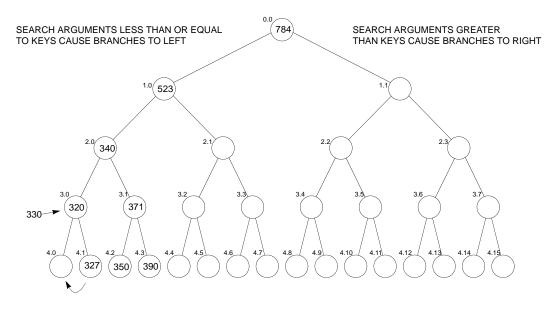

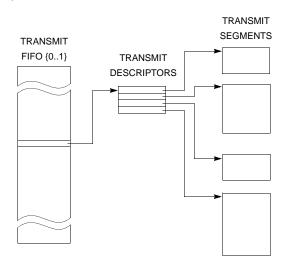

#### Bridging (continued)