# Old Company Name in Catalogs and Other Documents

On April 1<sup>st</sup>, 2010, NEC Electronics Corporation merged with Renesas Technology Corporation, and Renesas Electronics Corporation took over all the business of both companies. Therefore, although the old company name remains in this document, it is a valid Renesas Electronics document. We appreciate your understanding.

Renesas Electronics website: http://www.renesas.com

April 1<sup>st</sup>, 2010 Renesas Electronics Corporation

Issued by: Renesas Electronics Corporation (http://www.renesas.com)

Send any inquiries to http://www.renesas.com/inquiry.

# Notice

- 1. All information included in this document is current as of the date this document is issued. Such information, however, is subject to change without any prior notice. Before purchasing or using any Renesas Electronics products listed herein, please confirm the latest product information with a Renesas Electronics sales office. Also, please pay regular and careful attention to additional and different information to be disclosed by Renesas Electronics such as that disclosed through our website.

- Renesas Electronics does not assume any liability for infringement of patents, copyrights, or other intellectual property rights of third parties by or arising from the use of Renesas Electronics products or technical information described in this document. No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of Renesas Electronics or others.

- 3. You should not alter, modify, copy, or otherwise misappropriate any Renesas Electronics product, whether in whole or in part.

- 4. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation of these circuits, software, and information in the design of your equipment. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from the use of these circuits, software, or information.

- 5. When exporting the products or technology described in this document, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations. You should not use Renesas Electronics products or the technology described in this document for any purpose relating to military applications or use by the military, including but not limited to the development of weapons of mass destruction. Renesas Electronics products and technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations.

- 6. Renesas Electronics has used reasonable care in preparing the information included in this document, but Renesas Electronics does not warrant that such information is error free. Renesas Electronics assumes no liability whatsoever for any damages incurred by you resulting from errors in or omissions from the information included herein.

- 7. Renesas Electronics products are classified according to the following three quality grades: "Standard", "High Quality", and "Specific". The recommended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below. You must check the quality grade of each Renesas Electronics product before using it in a particular application. You may not use any Renesas Electronics product for any application categorized as "Specific" without the prior written consent of Renesas Electronics. Further, you may not use any Renesas Electronics. Renesas Electronics shall not be in any way liable for any damages or losses incurred by you or third parties arising from the use of any Renesas Electronics product for an application categorized as "Specific" or for which the product is not intended where you have failed to obtain the prior written consent of Renesas Electronics. The quality grade of each Renesas Electronics product is "Standard" unless otherwise expressly specified in a Renesas Electronics data sheets or data books, etc.

- "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; and industrial robots.

- "High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control systems; anti-disaster systems; anticrime systems; safety equipment; and medical equipment not specifically designed for life support.

- "Specific": Aircraft; aerospace equipment; submersible repeaters; nuclear reactor control systems; medical equipment or systems for life support (e.g. artificial life support devices or systems), surgical implantations, or healthcare intervention (e.g. excision, etc.), and any other applications or purposes that pose a direct threat to human life.

- 8. You should use the Renesas Electronics products described in this document within the range specified by Renesas Electronics, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas Electronics shall have no liability for malfunctions or damages arising out of the use of Renesas Electronics products beyond such specified ranges.

- 9. Although Renesas Electronics endeavors to improve the quality and reliability of its products, semiconductor products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Further, Renesas Electronics products are not subject to radiation resistance design. Please be sure to implement safety measures to guard them against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas Electronics product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or system manufactured by you.

- 10. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. Please use Renesas Electronics products in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. Renesas Electronics assumes no liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 11. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written consent of Renesas Electronics.

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products, or if you have any other inquiries.

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its majorityowned subsidiaries.

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

**User's Manual**

# μ**PD4991A**

# 4-bit Parallel I/O Calendar Clock

Document No. S12923EJ2V0UM00 (2nd edition) Date Published November 1997 N

© NEC Corporation 1992 Printed in Japan [MEMO]

No part of this document may be copied or reproduced in any form or by any means without the prior written consent of NEC Corporation. NEC Corporation assumes no responsibility for any errors which may appear in this document.

NEC Corporation does not assume any liability for infringement of patents, copyrights or other intellectual property rights of third parties by or arising from use of a device described herein or any other liability arising from use of such device. No license, either express, implied or otherwise, is granted under any patents, copyrights or other intellectual property rights of NEC Corporation or others.

While NEC Corporation has been making continuous effort to enhance the reliability of its semiconductor devices, the possibility of defects cannot be eliminated entirely. To minimize risks of damage or injury to persons or property arising from a defect in an NEC semiconductor device, customers must incorporate sufficient safety measures in its design, such as redundancy, fire-containment, and anti-failure features.

NEC devices are classified into the following three quality grades:

"Standard", "Special", and "Specific". The Specific quality grade applies only to devices developed based on a customer designated "quality assurance program" for a specific application. The recommended applications of a device depend on its quality grade, as indicated below. Customers must check the quality grade of each device before using it in a particular application.

- Standard: Computers, office equipment, communications equipment, test and measurement equipment, audio and visual equipment, home electronic appliances, machine tools, personal electronic equipment and industrial robots

- Special: Transportation equipment (automobiles, trains, ships, etc.), traffic control systems, anti-disaster systems, anti-crime systems, safety equipment and medical equipment (not specifically designed for life support)

- Specific: Aircrafts, aerospace equipment, submersible repeaters, nuclear reactor control systems, life support systems or medical equipment for life support, etc.

The quality grade of NEC devices is "Standard" unless otherwise specified in NEC's Data Sheets or Data Books. If customers intend to use NEC devices for applications other than those specified for Standard quality grade, they should contact an NEC sales representative in advance.

Anti-radioactive design is not implemented in this product.

[MEMO]

# TABLE OF CONTENTS

| CHAPTE | ER 1 OUTLINE OF $\mu$ PD4991A                                                       |  |  |  |  |  |  |  |

|--------|-------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| 1.1    | Features                                                                            |  |  |  |  |  |  |  |

| 1.2    | Pin Configuration                                                                   |  |  |  |  |  |  |  |

| 1.3    | Block Diagram                                                                       |  |  |  |  |  |  |  |

| 1.4    | Oscillation Stage and 15-stage Divider 11                                           |  |  |  |  |  |  |  |

| 1.5    | Mode and Register Configuration                                                     |  |  |  |  |  |  |  |

| 1.6    | Cautions (Be sure to observe the following.)                                        |  |  |  |  |  |  |  |

|        | 5,                                                                                  |  |  |  |  |  |  |  |

| СНАРТ  | ER 2 OPERATIONS                                                                     |  |  |  |  |  |  |  |

|        |                                                                                     |  |  |  |  |  |  |  |

| 2.1    | Write Timing 1                                                                      |  |  |  |  |  |  |  |

| 2.2    | Read Timing 1                                                                       |  |  |  |  |  |  |  |

| 2.3    | Mode Details 1                                                                      |  |  |  |  |  |  |  |

|        | 2.3.1 BASIC TIME MODE (MODE REG. $\leftarrow$ 0H or 3H)                             |  |  |  |  |  |  |  |

|        | 2.3.2 ALARM SET & TP1 CONTROL MODE (MODE REG. $\leftarrow$ 1)                       |  |  |  |  |  |  |  |

|        | 2.3.3 ALARM SET & TP2 CONTROL MODE (MODE REG. $\leftarrow$ 2)                       |  |  |  |  |  |  |  |

|        | 2.3.4 TEST MODE                                                                     |  |  |  |  |  |  |  |

| СНАРТЕ | ER 3 ACCESS PROCEDURE                                                               |  |  |  |  |  |  |  |

| 3.1    | Writing and Reading Time                                                            |  |  |  |  |  |  |  |

|        | 3.1.1 Setting time                                                                  |  |  |  |  |  |  |  |

|        | 3.1.2 Reading time                                                                  |  |  |  |  |  |  |  |

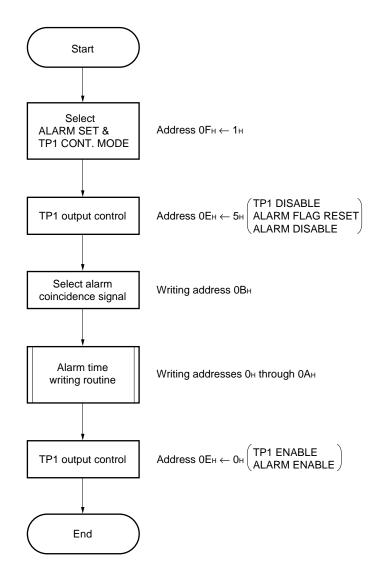

| 3.2    | Setting Alarm Time 4                                                                |  |  |  |  |  |  |  |

| 3.3    | Setting Interval Timer 4                                                            |  |  |  |  |  |  |  |

|        |                                                                                     |  |  |  |  |  |  |  |

| CHAPTE | ER 4 ELECTRICAL SPECIFICATIONS AND INTERFACE                                        |  |  |  |  |  |  |  |

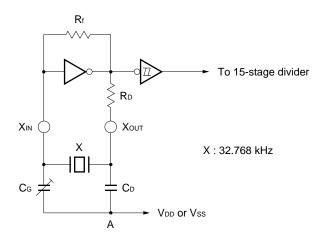

|        | Crustel Operilletion Circuit                                                        |  |  |  |  |  |  |  |

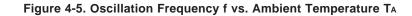

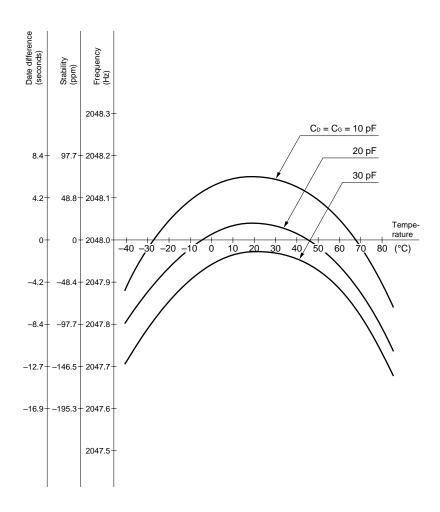

|        | Crystal Oscillation Circuit    4      Oscillation Characteristics and Accuracy    4 |  |  |  |  |  |  |  |

| 4.2    |                                                                                     |  |  |  |  |  |  |  |

|        | 4.2.1 Dependency on capacitance 4                                                   |  |  |  |  |  |  |  |

|        | 4.2.2 Dependency on temperature                                                     |  |  |  |  |  |  |  |

| 4.0    | 4.2.3 Dependency on supply voltage                                                  |  |  |  |  |  |  |  |

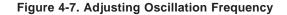

| 4.3    | Adjusting Oscillation Frequency                                                     |  |  |  |  |  |  |  |

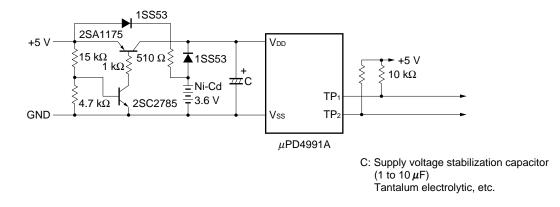

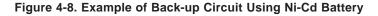

| 4.4    | Back-up Circuit                                                                     |  |  |  |  |  |  |  |

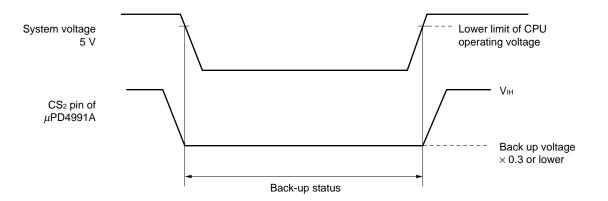

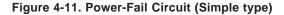

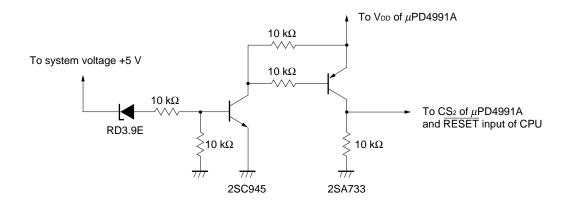

| 4.5    | Power-fail Circuit                                                                  |  |  |  |  |  |  |  |

| APPENDIX    |                                                    | 57 |

|-------------|----------------------------------------------------|----|

| Appendix 1. | Specifications of $\mu$ PD4991A                    | 57 |

| Appendix 2. | Package Drawing                                    | 60 |

| Appendix 3. | Differences between $\mu$ PD4991 and $\mu$ PD4991A | 62 |

# Caution

The application circuits and their parameters are for reference only and are not intended for use in actual design-ins.

# CHAPTER 1 OUTLINE OF $\mu$ PD4991A

The  $\mu$ PD4991A is an IC for inputting/outputting 4-bit parallel time data and calendar data in a microcontroller system and has 1 channel for an alarm function.

This IC has seven types of internal counters: year, month, date, day of week, hour, minute, and second. The hour counter can be used in two modes: 12-hour and 24-hour modes. Month, date, day of week, minute, and second can be specified for the alarm function.

Because the operating voltage range of this IC is very wide, from 2.0 to 5.5 V (4.5 to 5.5 V when the IC is accessed), commercially available dry cells, mercury cells, lithium batteries, Ni-Cd batteries, and super capacitors (electric double-layer capacitors) can be used as back-up batteries.

The  $\mu$ PD4991A is suitable for systems requiring a watch function, such as personal computers, word processors, FAXes, ECRs, and POSs.

#### 1.1 Features

- Time (hour, minute, and second) and calendar (leap year, year, month, date, and day of week) counters

- · Alarm function (month, date, day of week, hour, minute, and second)

- · Seven alarm coincidence signals and five interval timers

- Automatic identification and user-setting of leap year (up to 2099)

- 12- and 24-hour modes selectable

- High speed response (cycle time: 150 ns)

- Low current consumption (2 μA Typ. at back up)

- Address bus: 4 bits, data bus: 4 bits

- Upward-compatible with µPD4991 in function and characteristics (For details, refer to Appendix 3.)

#### **Basic Specifications**

- Reference frequency (crystal oscillation) ....... 32.768 kHz

- Data format ..... BCD

- Data function

Year, month, date, day of week, hour, minute, and second counters

Leap year is automatically identified or can be set by the user.

Years are set in 2-digit units.

Hours can be indicated in 12- or 24-hour mode.

- Data input/output (D<sub>3</sub>, D<sub>2</sub>, D<sub>1</sub>, D<sub>0</sub>)

- 4-bit parallel input/output

Data is input/output by enabling writing with the WE signal and enabling reading with the OE signal.

Mode selection

The mode is selected by setting the address to 0FH and writing data.

- Timing pulse output (TP1, TP2)

- TP1 ... Alarm coincidence signal output

2048, 1024, 64, 16, 1 Hz, or 1-pulse output (H  $\rightarrow$  L) selectable

- TP2 ... Interval timer signal output

- 60, 30, 10, 1, or 0.1 s selectable

- Chip select (CS1, CS2)

All input signals except X<sub>IN</sub> are disabled when  $\overline{CS_1} = "H"$  and  $CS_2 = "L"$ . All input signals are selected when  $\overline{CS_1} = "L"$  and  $CS_2 = "H"$ .

# 1.2 Pin Configuration

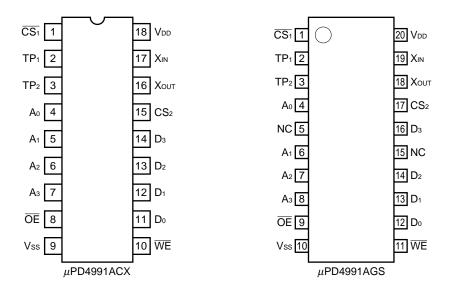

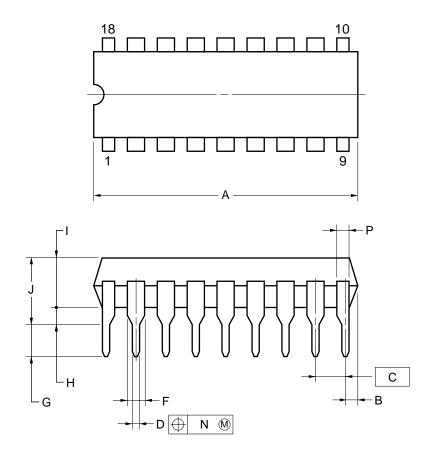

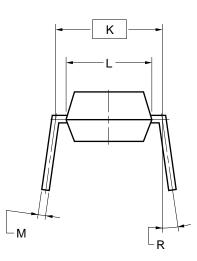

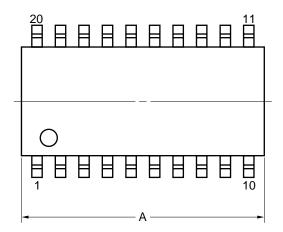

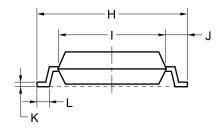

The  $\mu$ PD4991A is available in two packages: 18-pin DIP and 20-pin SOP. Figure 1-1 shows the pin configuration. Ordering information is given below. Table 1-1 lists the function of each pin.

# **Ordering information**

| Part Number     | Package                      |

|-----------------|------------------------------|

| $\mu$ PD4991ACX | 18-pin plastic DIP (300 mil) |

| $\mu$ PD4991AGS | 20-pin plastic SOP (300 mil) |

# Figure 1-1. Pin Configuration (Top View)

| Pin Name              | Symbol          | Pin No. |     | Function                                                                                                               |

|-----------------------|-----------------|---------|-----|------------------------------------------------------------------------------------------------------------------------|

|                       |                 | DIP     | SOP |                                                                                                                        |

| Chip select           | CS <sub>1</sub> | 1       | 1   | When $\overline{CS_1}$ = "L" and $CS_2$ = "H", the $\mu$ PD4991A can transfer data with                                |

|                       | CS <sub>2</sub> | 15      | 17  | a CPU.                                                                                                                 |

| Timing pulse 1        | TP1             | 2       | 2   | Outputs an alarm coincidence signal.                                                                                   |

| Timing pulse 2        | TP2             | 3       | 3   | Outputs an interval timer signal                                                                                       |

| Address input         | Ao              | 4       | 4   | Specifies the internal address of the $\mu$ PD4991A.                                                                   |

|                       | A1              | 5       | 6   |                                                                                                                        |

|                       | A2              | 6       | 7   |                                                                                                                        |

|                       | Aз              | 7       | 8   |                                                                                                                        |

| Read control input    | ŌĒ              | 8       | 9   | While $\overline{OE}$ = "L", the contents specified by the address bus are read to the data bus.                       |

| Ground pin            | Vss             | 9       | 10  |                                                                                                                        |

| Write control input   | WE              | 10      | 11  | The contents of the data bus are written to an address specified by the address bus when $\overline{\text{WE}}$ rises. |

| Data bus pin          | Do              | 11      | 12  | Bidirectional 4-bit bus which inputs/outputs watch data.                                                               |

|                       | D1              | 12      | 13  |                                                                                                                        |

|                       | D2              | 13      | 14  |                                                                                                                        |

|                       | Dз              | 14      | 16  |                                                                                                                        |

| Crystal signal pin    | Хоит            | 16      | 18  | Oscillation inverter output                                                                                            |

| Crystal signal pin    | Xin             | 17      | 19  | Oscillation inverter input                                                                                             |

| Positive power supply | Vdd             | 18      | 20  |                                                                                                                        |

#### Table 1-1. Pin Functions

# 1.3 Block Diagram

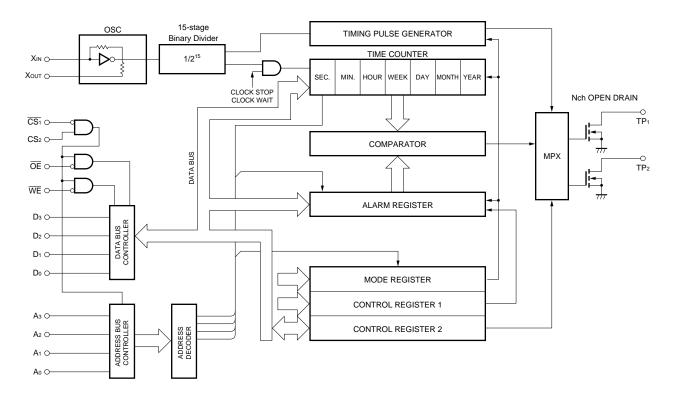

Figure 1-2 shows the block diagram of the  $\mu$ PD4991A.

Figure 1-2. Block Diagram

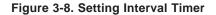

# 1.4 Oscillation Stage and 15-stage Divider

A clock of 32.768 kHz is generated by using a 32.768-kHz crystal resonator and a CMOS inverter crystal oscillation circuit. This clock is divided by 15 to create a 1 Hz (1 second) time counter.

#### 1.5 Mode and Register Configuration

The  $\mu$ PD4991A uses 13 data registers as time counters and 11 data registers to store alarm times. In addition, it also has six control/status registers for controlling the watch, alarm, and interval timer, and one mode register to specify the operation mode.

The  $\mu$ PD4991A has the following three modes.

# 1. BASIC TIME MODE

Data write or read between the timer counter and CPU Command specification for control registers 1 and 2

#### 2. ALARM SET & TP1 CONTROL MODE

Data setting to alarm register TP1 function setting Leap year identification Command specification for control registers 1 and 2

# 3. ALARM SET and TP2 CONTROL MODE

Data setting to alarm register TP2 function setting 12-/24-hour mode selection Command specification for control registers 1 and 2

These modes can be selected by writing mode data (refer to **Table 2-1**) to address = 0F<sub>H</sub>. Once a mode has been set, it remains valid until changed.

Table 1-2 shows the correspondence between registers and addresses.

| A    | DDRESS  | BASIC TIME MODE     | TP 1 CONT.MODE                      | TP 2 CONT.MODE                            |  |  |  |

|------|---------|---------------------|-------------------------------------|-------------------------------------------|--|--|--|

| HEX  | MSB LSB | (TIME COUNTER)      | (ALARM REGISTER)                    | (ALARM REGISTER)                          |  |  |  |

| 0 н  | 0,0,0,0 | Second, units digit | Second,                             | units digit                               |  |  |  |

| 1 н  | 0,0,0,1 | Second, tens digit  | Second,                             | tens digit                                |  |  |  |

| 2 н  | 0,0,1,0 | Minute, units digit | Minute, u                           | units digit                               |  |  |  |

| 3 н  | 0,0,1,1 | Minute, tens digit  | Minute,                             | tens digit                                |  |  |  |

| 4 н  | 0,1,0,0 | Hour, units digit   | Hour, u                             | nits digit                                |  |  |  |

| 5 н  | 0,1,0,1 | Hour, tens digit    | Hour, tens digit                    |                                           |  |  |  |

| 6 н  | 0,1,1,0 | Day of week digit   | of week digit Day of week digit     |                                           |  |  |  |

| 7 н  | 0,1,1,1 | Date, units digit   | Date, units digit Date, units digit |                                           |  |  |  |

| 08 н | 1,0,0,0 | Date, tens digit    | Date, te                            | ens digit                                 |  |  |  |

| 09 н | 1,0,0,1 | Month, units digit  | Month, u                            | units digit                               |  |  |  |

| 0А н | 1,0,1,0 | Month, tens digit   | Month, t                            | ens digit                                 |  |  |  |

| 0В н | 1,0,1,1 | Year, units digit   | TP1 FUNCTION CONT.                  | TP2 FUNCTION CONT.                        |  |  |  |

| 0С н | 1,1,0,0 | Year, tens digit    | Leap year counter                   | 12-/24-hour mode, leap year valid/invalid |  |  |  |

| 0D н | 1,1,0,1 |                     | CONTROL REGISTER 1                  |                                           |  |  |  |

| 0Е н | 1,1,1,0 | CONTROL REGISTER 2  |                                     |                                           |  |  |  |

| 0F н | 1,1,1,1 | MODE REGISTER       |                                     |                                           |  |  |  |

# Table 1-2. Registers and Their Addresses

# 1.6 Cautions (Be sure to observe the following.)

- Before writing the time, be sure to stop the watch. For details, refer to 3.1.1 Setting time.

- If the 12-hour mode has been changed to the 24-hour mode or vice versa, be sure to rewrite the hour counter.

For details, refer to (3) 12-/24-hour mode and leap year identification in 2.3.3 ALARM SET & TP2 CONTROL MODE.

- 3. Before changing the setting of the leap year counter, be sure to rewrite the year counter. For details, refer to (3) Leap year counter in 2.3.2 ALARM SET & TP1 CONTROL MODE.

- When accessing CONTROL REGISTER 2 to write during alarm coincidence, first set the alarm flag, and then access the register.

For details, refer to (3) and (4) CONTROL REGISTER 2 in 2.3.1 BASIC TIME MODE.

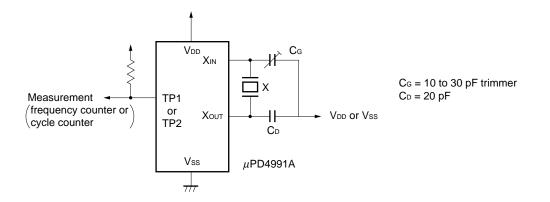

- 5. Use TP1 or TP2 output, not XIN or XOUT, for adjustment of the oscillation frequency. For details, refer to **4.3 Adjusting Oscillation Frequency**.

- Be sure to keep CS<sub>2</sub> low while the CPU is in the back-up status. For details, refer to 4.5 Power-Fail Circuit.

- 7. Because only two digits are supported for the year code, use only the low-order 2 digits of the year when using the Western calendar.

The  $\mu$ PD4991A correctly counts time even when the year changes from 1999 to 2000.

This IC can automatically identify a leap year up till 2099. Although 2100 is not a leap year, the IC identifies this year as a leap year. However, if the user specifies a leap year, the other functions of this IC can continue to be used without any problem.

The application circuit and circuit constants in this document are shown for your reference only and are not intended to be used for mass production of an application system. The characteristic examples and application examples shown in this document are also for your reference only. When you design an actual application set, confirm that there are no operational problems. [MEMO]

# **CHAPTER 2 OPERATIONS**

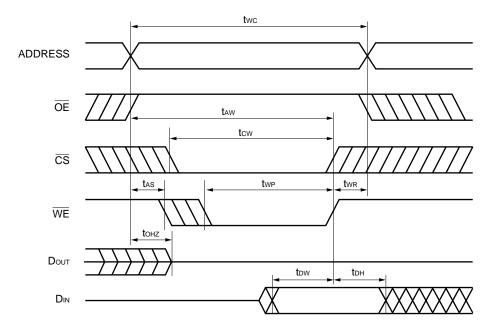

#### 2.1 Write Timing

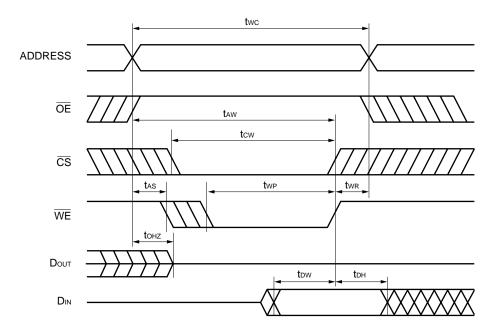

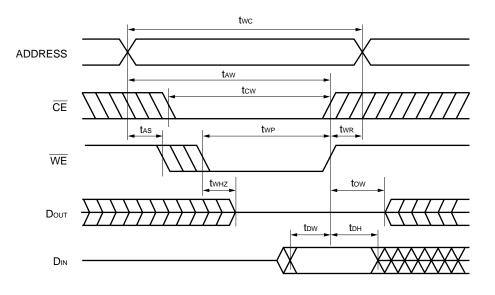

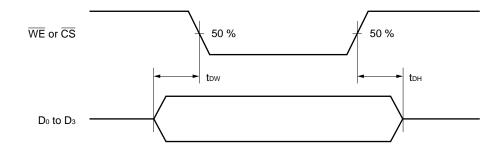

Address A<sub>0</sub> through A<sub>3</sub> and data D<sub>0</sub> through D<sub>3</sub> are written to the IC when  $\overline{WE}$  (write enable) is made high while  $\overline{CS_1}$  = "L" and  $CS_2$  = "H" (chip select status).

WE takes precedence over  $\overline{OE}$  (read enable). Therefore, data can be written by asserting  $\overline{WE}$  only when data is to be written, even when  $\overline{OE}$  is always "L".

Figures 2-1 and 2-2 show the write timing. To change the setting of the time counter, it is necessary to RESET/ STOP the CLK. A correct value may not be written to the time counter if data is written to the time counter while it is operating. The other registers, however, are not affected.

Figure 2-1. Write Cycle Timing 1

Figure 2-2. Write Cycle Timing 2 ( $\overline{OE} = V_{IL}$ )

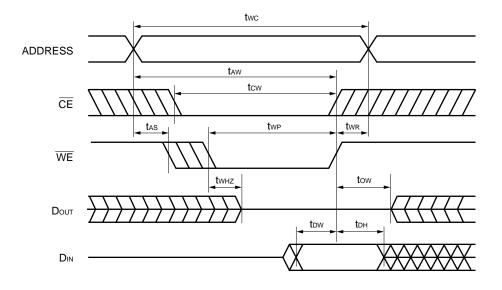

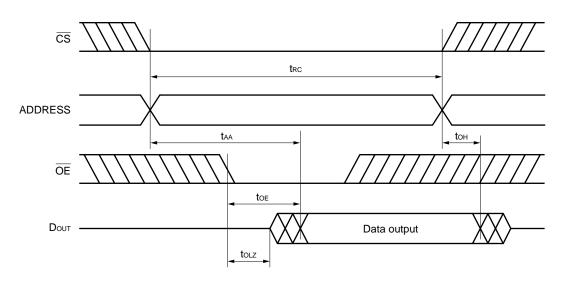

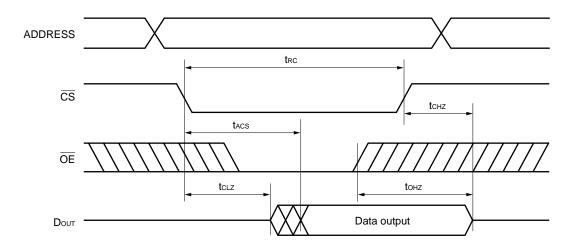

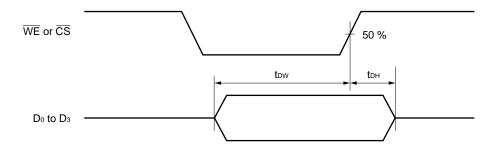

# 2.2 Read Timing

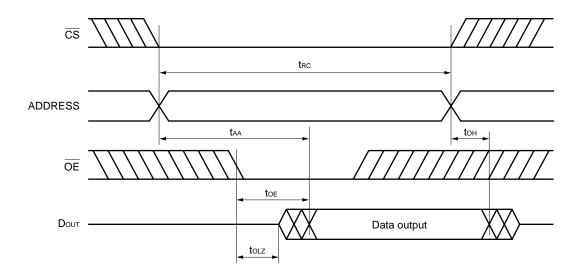

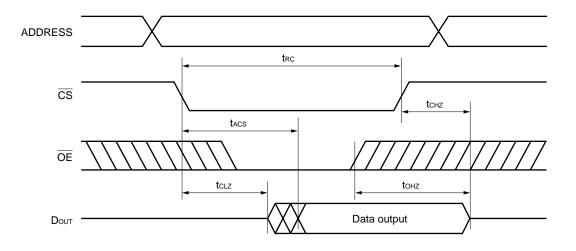

The contents of address A<sub>0</sub> through A<sub>3</sub> are output to data D<sub>0</sub> through D<sub>3</sub> when  $\overline{OE}$  (read enable) is made low while  $\overline{CS_1}$  = "L" and  $\overline{CS_2}$  = "H" (chip select status).

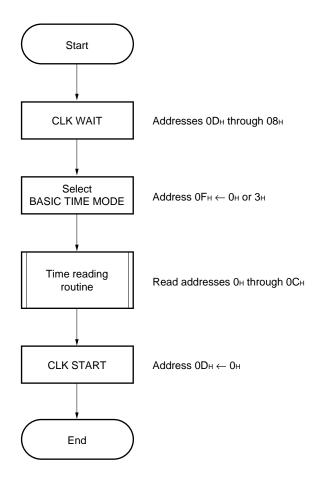

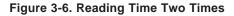

Figures 2-3 and 2-4 show the read timing. When a write-only (W/O) register is read, 0FH is read to the data bus. Because the value of the time counter is updated when a carry occurs from the 1-second digit, read the value of the time counter in accordance with the guidance in CHAPTER 3.

Figure 2-3. Read Cycle Timing 1

Figure 2-4. Read Cycle Timing 2

# 2.3 Mode Details

The registers assigned to addresses 0<sub>H</sub> through 0C<sub>H</sub> and the operation performed differ depending on the data written to address 0F<sub>H</sub>.

The  $\mu$ PD4991A has the following four major modes.

- BASIC TIME MODE (MODE REG. ← 0н or 3н)

In this mode, the timer counter can be accessed. Usually, this mode is used.

- (2) TP1 CONTROL MODE (MODE REG.  $\leftarrow$  1 $_{\rm H}$ )

This mode is used to set alarm times and select an alarm output.

(3) TP2 CONTROL MODE (MODE REG.  $\leftarrow$  2H)

This mode is used to set alarm times and select an interval timer.

(4) TEST MODE (MODE REG.  $\leftarrow$  08 $\mu$  through 0F $\mu$ )

This mode is used to test the functions of the time counter and alarm interval timer. When this mode is set, the time is fast-forwarded. Therefore, this mode is not used in normal operation. Table 2-1 lists the modes.

| Table 2-1. | μ <b>ΡD4991A</b> | Mode List | (address = 0Fн) |

|------------|------------------|-----------|-----------------|

|------------|------------------|-----------|-----------------|

X: Don't Care

| Value Assigned to Mode Register |                                                | to Mode Register | Operation Mode                | Operation                                                                                                       |

|---------------------------------|------------------------------------------------|------------------|-------------------------------|-----------------------------------------------------------------------------------------------------------------|

| HEX                             |                                                | D3 D2 D1 D0      |                               |                                                                                                                 |

| 4н0                             | н                                              | 0, X, 0, 0       | BASIC TIME                    | Sets and reads time data. Setting accuracy: 15.625 ms                                                           |

| 5н 1                            | н 1 н 0, X, 0, 1 ALARM SET<br>&<br>TP1 CONTROL |                  | &                             | Sets alarm timer, selects TP1 output mode, and sets and reads leap year counter.                                |

| 6н2                             | н                                              | 0, X, 1, 0       | ALARM SET<br>&<br>TP2 CONTROL | Sets alarm timer, selects TP2 output mode, selects 12- or 24-hour mode, and validates or invalidates leap year. |

| 7н3                             | н                                              | 0, X, 1, 1,      | BASIC TIME                    | Same as MODE REG. $\leftarrow$ 0H. Setting accuracy: 30.52 $\mu$ s                                              |

| 08 н                            | )8 н 1, 0, 0, 0, TEST<br>(BASIC TIME)          |                  |                               | Tests time counter.<br>However, alarm and interval timer functions (TP1 and TP2) are undefined.                 |

| 09 н                            |                                                | 1, 0, 0, 1       | TEST<br>(BASIC TIME)          |                                                                                                                 |

| 0А н                            |                                                | 1, 0, 1, 0       | TEST<br>(BASIC TIME)          |                                                                                                                 |

| 0В н                            |                                                | 1, 0, 1, 1,      | TEST<br>(ALARM SET)           | Tests alarm register and leap year counter.                                                                     |

| 0С н                            |                                                | 1, 1, 0, 0       | TEST<br>(ALARM SET)           | Tests alarm register and selects 12- or 24-hour mode.                                                           |

| 0D н                            | 0D н 1, 1, 0, 1 TEST<br>(ALARM & TF            |                  | TEST<br>(ALARM & TP1)         | Tests alarm timer and TP1 output.                                                                               |

| 0E н                            | 0Е н 1, 1, 1, 0 TEST<br>(ALARM & TP2)          |                  | -                             | Tests alarm timer.                                                                                              |

| 0F н                            |                                                | 1, 1, 1, 1       | TEST<br>(ALARM & TP2)         | Tests interval timer and TP2 output.                                                                            |

#### 2.3.1 BASIC TIME MODE (MODE REG. $\leftarrow$ 0 $\mu$ or 3 $\mu$ )

In this mode, addresses 0H through 0CH are used as time counters to/from which time can be written or read (refer to **Table 2-2**).

Because a leap year cannot be identified or set and the 12- or 24-hour mode cannot be selected in this mode, setting related to a leap year and selection of the hour mode must be made in advance in TP1 CONTROL MODE or TP2 CONTROL MODE.

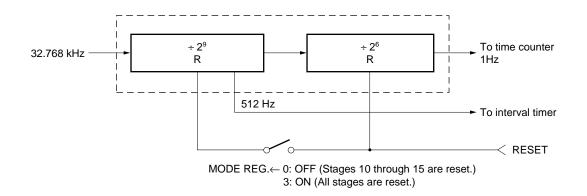

TIME RESET and  $\pm$ 30 sec ADJ. differ in operation depending on whether the MODE REGISTER is set to "0" or "3".

When TIME RESET or  $\pm$ 30 sec ADJ. is executed, the 15-stage divider that creates the 1 second pulse which is supplied to the timer counter is reset. If the MODE REGISTER is set to "0", only stages 10 through 15 of the 15-stage divider are reset. Consequently, an error of up to 15.625 ms occurs.

If the MODE REGISTER is set to "3", all the stages of the 15-stage divider are reset, and an error of up to  $30.52 \,\mu s$  occurs. Because stages 1 through 9 of the 15-stage divider are used as the first stages of the interval timer, an error of up to 1.95 ms occurs in the interval timer if all the stages of the divider are reset.

Figure 2-5. Block Diagram of 15-Stage Divider

| Table 2-2. Register | Assignment in | BASIC | TIME MODE |

|---------------------|---------------|-------|-----------|

|                     | 7.00.g.m.o    |       |           |

| Address | Register              |                                                              | Description                                                                                                              |                    |               |             |  |  |

|---------|-----------------------|--------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|--------------------|---------------|-------------|--|--|

| 0 н     | Second, units digit   | Directly connected to time counter and updated in real-time. |                                                                                                                          |                    |               |             |  |  |

| 1 н     | Second, tens digit    |                                                              | Data format is BCD.                                                                                                      |                    |               |             |  |  |

| 2 н     | Minute, units digit   |                                                              | f time that does not exist is set (e.g., minute 70, hour 30, 13 p.m., February 30,<br>etc.), then the wrong time is set. |                    |               |             |  |  |

| 3 н     | Minute, tens digit    | ,                                                            |                                                                                                                          |                    |               |             |  |  |

| 4 н     | Hour, units digit     | . ,                                                          | <b>Note)</b> The second highest bit $D_2$ of the 10-hour digit functions as $\overline{AM}/PM$ flag in 12-               |                    |               |             |  |  |

| 5 н     | Hour, tens digit      | hour mode                                                    | e (e.g., 5 p.m. is                                                                                                       | s indicated as hou | r 45).        |             |  |  |

| 6 н     | Day of week digit     |                                                              | D3                                                                                                                       | D <sub>2</sub>     | D1            | Do          |  |  |

| 7 н     | Date, units digit     | 12-hour mode                                                 | Х                                                                                                                        | AM/PM flag         | Data          | Data        |  |  |

| 08 н    | Date, tens digit      | R/W                                                          |                                                                                                                          |                    |               |             |  |  |

| 09 н    | Month, units digit    |                                                              |                                                                                                                          |                    |               |             |  |  |

| 0А н    | Month, tens digit     |                                                              |                                                                                                                          |                    |               |             |  |  |

| 0B н    | Year, units digit     |                                                              |                                                                                                                          |                    |               |             |  |  |

| 0С н    | Year, tens digit      |                                                              |                                                                                                                          |                    |               |             |  |  |

| 0D н    | CONTROL<br>REGISTER 1 |                                                              | D3                                                                                                                       | D <sub>2</sub>     | D1            | Do          |  |  |

|         |                       | W/O                                                          | CLK                                                                                                                      | CLK                | ±30 s         | TIME        |  |  |

|         |                       |                                                              | WAIT                                                                                                                     | STOP               | ADJ.          | RESET       |  |  |

| 0E н    | CONTROL               |                                                              | D3                                                                                                                       | D2                 | D1            | Do          |  |  |

|         | REGISTER 2            | Write                                                        | 0                                                                                                                        | Alarm              | Alarm         | TP1         |  |  |

|         |                       |                                                              |                                                                                                                          | Disable            | Flag          | Disable     |  |  |

|         |                       | Write                                                        | 1                                                                                                                        | INT                | INT           | TP2         |  |  |

|         |                       |                                                              |                                                                                                                          | STOP               | RESET         | Disable     |  |  |

|         |                       | Read                                                         | Х                                                                                                                        | Busy               | Alarm<br>Flag | TP2<br>Flag |  |  |

| 0F н    | MODE<br>REGISTER      | W/O. Refer to <b>Mc</b>                                      | de List.                                                                                                                 |                    |               | 1           |  |  |

X: Don't Care W/O: Write only

#### (1) Time counter (addresses 0н through 0Сн)

This counter stores time data in BCD format. If time that does not exist is set, the wrong time is indicated. Be sure to set correct data. The day counter takes a value from 0 to 6. The user can specify which value takes which day (Monday through Sunday). Tables 2-3 and 2-4 show correspondence between time and data.

| TIME COUNTER        | DATA | TIME COUNTER       | DATA |

|---------------------|------|--------------------|------|

| Second, units digit | 0–9  | Date, units digit  | 0–9  |

| Second, tens digit  | 0–5  | Date, tens digit   | 0–3  |

| Minute, units digit | 0–9  | Month, units digit | 0–9  |

| Minute, tens digit  | 0–5  | Month, tens digit  | 0–1  |

| Hour, units digit   | 0–9  | Year, units digit  | 0–9  |

| Hour, tens digit    | 0–5  | Year, tens digit   | 0–9  |

| Day of week digit   | 0–6  |                    |      |

| Table | 2-3.        | Time    | Counter | Data |

|-------|-------------|---------|---------|------|

| Table | <b>Z</b> U. | 1 IIIIC | oounter | Dutu |

| Time    | 24-Hour Mode | 12-Hour Mode | Time    | 24-Hour Mode | 12-Hour Mode |

|---------|--------------|--------------|---------|--------------|--------------|

| 1 a.m.  | 01 H         | 01 H         | 1 p.m.  | 13 H         | 41 H         |

| 2 a.m.  | 02 H         | 02 H         | 2 p.m.  | 14 H         | 42 H         |

| 3 a.m.  | 03 H         | 03 H         | 3 p.m.  | 15 H         | 43 H         |

| 4 a.m.  | 04 H         | 04 H         | 4 p.m.  | 16 H         | 44 H         |

| 5 a.m.  | 05 H         | 05 H         | 5 p.m.  | 17 H         | 45 H         |

| 6 a.m.  | 06 H         | 06 H         | 6 p.m.  | 18 H         | 46 H         |

| 7 a.m.  | 07 H         | 07 H         | 7 p.m.  | 19 H         | 47 H         |

| 8 a.m.  | 08 H         | 08 H         | 8 p.m.  | 20 H         | 48 H         |

| 9 a.m.  | 09 H         | 09 H         | 9 p.m.  | 21 H         | 49 H         |

| 10 a.m. | 10 H         | 10 H         | 10 p.m. | 22 H         | 50 H         |

| 11 a.m. | 11 H         | 11 H         | 11 p.m. | 23 H         | 51 H         |

| 12 a.m. | 12 H         | 52 H         | 12 p.m. | 00 H         | 12 H         |

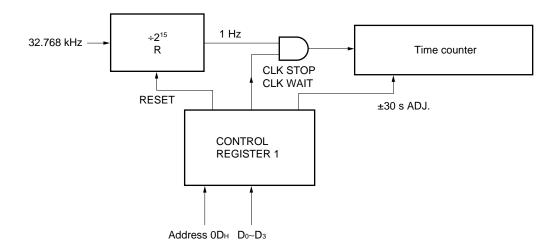

# (2) CONTROL REGISTER 1 (address: 0DH)

This register controls clock supply to the timer counter, makes adjustments of  $\pm 30$  seconds, and resets the 15-stage divider. Figure 2-6 shows the configuration of the control register 1, and Table 2-5 shows the commands of the register.

#### Figure 2-6. Configuration of Control Register 1

#### Table 2-5. CONTROL REGISTER 1 Command List (W/O)

| HEX | D3 D2 D1 D0 | Command             | Operation                             |

|-----|-------------|---------------------|---------------------------------------|

| 0 н | 0, 0, 0, 0  | CLOCK START         | Starts time counter.                  |

| 1 н | 0, 0, 0, 1  | CLOCK RESET START   | Resets and then starts time counter.  |

| 2 н | 0, 0, 1, 0  | $\pm 30$ sec ADJUST | Makes adjustment of $\pm 30$ seconds. |

| 4 н | 0, 1, 0, 0  | CLOCK STOP          | Stops time counter (when written).    |

| 8 н | 1, 0, 0, 0  | CLOCK WAIT          | Stops time counter (when read).       |

# (a) CLOCK RESET START (15-stage divider reset)

This command resets the 15-stage divider. When the MODE REGISTER is set to 0, stages 10 through 15 of the divider are reset; when the MODE REGISTER is set to 3, all the stages are reset. A carry occurs in the time counter about 1 second after this command has been executed.

This command is used when time data is written.

# (b) ±30 sec ADJUST (±30-second adjustment)

This command resets the second counter (to 00 seconds).

If this command is executed when the value of the second counter between 00 and 29, it is reset to 00 without the units digit for minutes being affected. If it is executed when the second counter between 30 and 59, the counter is reset to 00 and the units digit for minutes is incremented by one.

This adjustment is carried across all the digits.

Example: 9 hours 59 minutes 45 seconds  $\rightarrow$  10 hours 00 minutes 00 seconds

#### (c) CLOCK STOP and CLOCK WAIT (stops time counter)

Both these commands disable input of the clock (1 Hz) to the watch counter and stop the watch. CLOCK STOP is used when time data is **written** (be sure to stop the watch when writing time data). CLOCK WAIT is used when time data is **read**. This is to prevent a new count from occurring and the CPU from reading wrong data when time data is read. Time data can be also read by using the BUSY signal or by reading the time data two times, without using CLOCK WAIT.

If the clock input is resumed within 0.5 seconds after the watch has been stopped by CLOCK STOP or CLOCK WAIT, the real time is not delayed (if a carry occurs from 1-second digit while the watch is stopped, adjustment of +1 second is made after the clock input is resumed).

# (3) CONTROL REGISTER 2 (address 0EH) [during write]

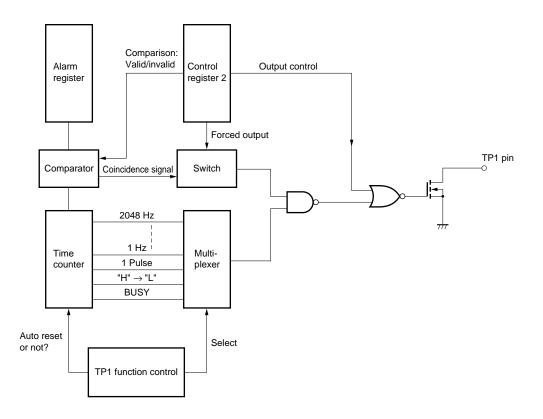

This register controls the alarm signal output to TP1 and the interval signal output to TP2. Figure 2-7 shows the diagram of the TP pin control block, and Table 2-6 lists the commands of CONTROL REGISTER 2.

#### Alarm signal control block

#### Interval timer control block

Table 2-6. CONTROL REGISTER 2 Command List (W/O)

| D <sub>3</sub> | D2       | D1       | Do      |

|----------------|----------|----------|---------|

| 0              | ALARM    | ALARM    | TP1     |

|                | DISABLE  | FLAG     | DISABLE |

| 1              | INTERVAL | INTERVAL | TP2     |

|                | STOP     | RESET    | DISABLE |

#### (a) TP1 control (when $D_3 = 0$ )

# i) TP1 DISABLE (D<sub>0</sub>)

This bit controls output of TP1. When this bit is set, TP1 is forcibly turned OFF (high impedance) regardless of the other operations.

# ii) ALARM FLAG (D1)

This flag forcibly sets the alarm coincidence/non-coincidence status.

When this bit is set, the alarm coincidence status is set; when it is reset, the alarm non-coincidence status is set.

# iii) ALARM DISABLE (D2)

This bit makes valid/invalid the alarm register and the result of comparison by the time counter. When this bit is set, the result of comparison of alarm is ignored and the ALARM FLAG is not affected. If ALARM DISABLE and ALARM FLAG are set, therefore, the alarm signal can be always output to TP1.

#### (b) TP2 control (when $D_3 = 1$ )

#### i) TP2 DISABLE (D<sub>0</sub>)

This bit controls output of TP2. When this bit is set, TP2 is forcibly turned off (high impedance) regardless of the other operations.

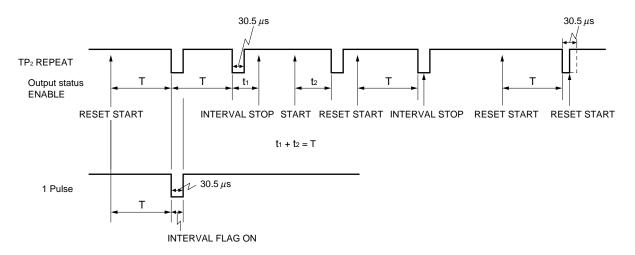

#### ii) INTERVAL RESET (D1)

When this bit is set, the interval timer is reset.

# iii) INTERVAL STOP (D2)

When this bit is set, the interval timer is stopped. If TP2 is low, however, the interval timer is stopped  $30.5 \ \mu s$  after the low period.

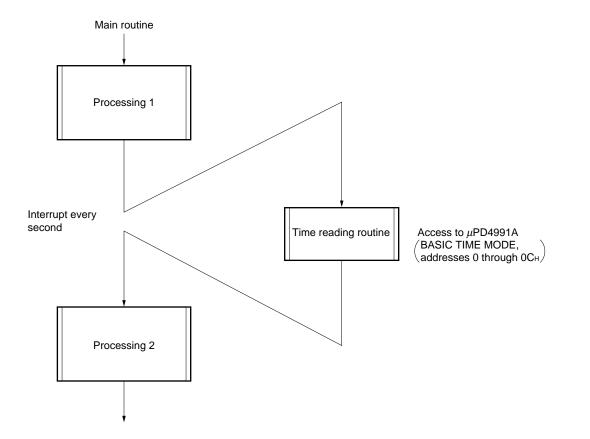

#### (4) CONTROL REGISTER 2 (address 0EH) [during read]

Control register 2 is used to monitor the BUSY signal, interval signal, and alarm status.

#### Table 2-7. CONTROL REGISTER 2 Status (R/O)

| D <sub>3</sub> | D2   | D1    | Do       |

|----------------|------|-------|----------|

| Х              | BUSY | ALARM | INTERVAL |

|                | FLAG | FLAG  | FLAG     |

#### (a) BUSY FLAG

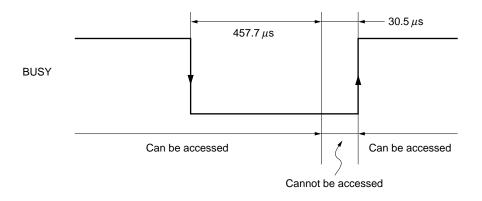

This is the count flag of the time counter. When this bit is 1, the time counter is in a count period. For details, refer to (d) BUSY signal in 2.3.2 (2).

#### (b) ALARM FLAG

When this bit is 1, it indicates an alarm coincidence status; when it is 0, it indicates an alarm noncoincidence status.

#### (c) INTERVAL FLAG

When this bit is 1, the interval output of TP2 is L; when it is 0, the interval output of TP2 is H.

#### Caution

If data is written to CONTROL REGISTER 2 in the alarm coincidence status, the ALARM FLAG may be reset. To access CONTROL REGISTER 2 to write, therefore, be sure to check whether the alarm coincidence or non-coincidence status is set (by reading the ALARM FLAG). In the alarm coincidence status, set the ALARM FLAG, and then access CONTROL REGISTER 2 to write.

#### 2.3.2 ALARM SET & TP1 CONTROL MODE (MODE REG. $\leftarrow$ 1)

In this mode, addresses 0<sub>H</sub> through 0A<sub>H</sub> are used as alarm registers that are used to set and check alarm times. Address 0B<sub>H</sub> is used as a control register that selects an alarm coincidence signal to be output to TP1, and address 0C<sub>H</sub> is used as a leap year counter. Addresses 0D<sub>H</sub> through 0F<sub>H</sub> are used in the same way as in the BASIC TIME MODE (refer to **Table 2-8**).

| Address | Register                | Description                                                                                                                                                               |

|---------|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0 н     | Second, units digit     | Alarm register                                                                                                                                                            |

| 1 н     | Second, tens digit      | Sets and checks alarm time.                                                                                                                                               |

| 2 н     | Minute, units digit     | When these registers are set to $0F_{H}$ , the digit corresponding to each register is<br>assumed to coincide with the value of the time counter. When the alarm function |

| 3 н     | Minute, tens digit      | is not used, these registers can be used as a back-up memory of 4 bits x 11 words                                                                                         |

| 4 н     | Hour, units digit       | (in which case alarm must be disabled).                                                                                                                                   |

| 5 н     | Hour, tens digit        |                                                                                                                                                                           |

| 6 н     | Day of week digit       |                                                                                                                                                                           |

| 7 н     | Date, units digit       |                                                                                                                                                                           |

| 08 н    | Date, tens digit        |                                                                                                                                                                           |

| 09 н    | Month, units digit      |                                                                                                                                                                           |

| 0А н    | Month, tens digit       |                                                                                                                                                                           |

| 0В н    | TP1 FUNCTION<br>CONTROL | W/O. Selects TP1 output waveform.                                                                                                                                         |

| 0С н    | Leap year counter       | D3      D2      D1      D0      0н of this register indicates                                                                                                             |

|         |                         | R/W  X  Leap year counter  a leap year. This register    takes a value of 0H to 3H.                                                                                       |

| 0D н    | CONTROL<br>REGISTER 1   | Same in BASIC TIME MODE                                                                                                                                                   |

| 0Е н    | CONTROL<br>REGISTER 2   |                                                                                                                                                                           |

| 0F н    | MODE<br>REGISTER        |                                                                                                                                                                           |

#### Table 2-8. Register Assignment in ALARM SET & TP1 CONTROL MODE

X: Don't Care W/O: Write only

#### (1) Alarm registers (addresses 0H through 0AH)

Alarm time can be set in units from months to seconds. The contents written to the alarm registers are compared with the time counter each time a carry occurs from the second digits. If an alarm register is set to 0FH, the corresponding digit is assumed to coincide with the value of the time counter. When all the digits coincide, the ALARM FLAG is set, and the output waveform selected by TP1 FUNCTION CONTROL register is output under control of CONTROL REGISTER 1.

If 0F<sub>H</sub> is written to some of the alarm registers, the following operations can be performed.

| Month,     | Month,      | Date,      | Date,       | Day of     | Hour,      | Hour,       | Minute,    | Minute,     | Second,    | Second,     |

|------------|-------------|------------|-------------|------------|------------|-------------|------------|-------------|------------|-------------|

| tens digit | units digit | tens digit | units digit | week digit | tens digit | units digit | tens digit | units digit | tens digit | units digit |

| 0Fн        | 0Fн         | 0Fн        | 0Fн         | 0Fн        | 0Fн        | 0Fн         | 0 н        | 0 н         | 0 н        | 0Fн         |

#### Example 1. Alarm coincides with the value of the time counter for 10 seconds every hour

From 00 minutes 0 seconds to 00 minutes 09 seconds the alarm value coincides with the value of the time counter.

Example 2. Alarm coincides with the value of the time counter for 24 hours on the first day of every month.

| Month,     | Month,      | Date,      | Date,       | Day of     | Hour,      | Hour,       | Minute,    | Minute,     | Second,    | Second,     |

|------------|-------------|------------|-------------|------------|------------|-------------|------------|-------------|------------|-------------|

| tens digit | units digit | tens digit | units digit | week digit | tens digit | units digit | tens digit | units digit | tens digit | units digit |

| 0Fн        | 0Fн         | 0 н        | 1 н         | 0Fн        | 0Fн        | 0FH         | 0Fн        | 0Fн         | 0Fн        | 0Fн         |

#### (2) TP1 FUNCTION CONTROL REGISTER (address 0BH)

These registers select the waveform that is to be output to TP1 (refer to Table 2-9).

|      | DATA Operation  |            | Operation                               | Description                                                                                 |

|------|-----------------|------------|-----------------------------------------|---------------------------------------------------------------------------------------------|

| HE   | HEX D3 D2 D1 D0 |            |                                         |                                                                                             |

| 08 н | 0 н             | X, 0, 0, 0 | 2048 Hz                                 | Output at duty factor of 50%                                                                |

| 09 н | 1 н             | X, 0, 0, 1 | 1024 Hz                                 |                                                                                             |

| 0Ан  | 2 н             | X, 0, 1, 0 | 64 Hz                                   |                                                                                             |

| 0Вн  | 3 н             | X, 0, 1, 1 | 16 Hz                                   |                                                                                             |

| 0Сн  | 4 н             | X, 1, 0, 0 | 1 Hz                                    |                                                                                             |

| 0Dн  | 5 н             | X, 1, 0, 1 | 1 pulse                                 | 1-shot output with a pulse width of 30.5 $\mu$ s during L period                            |

| 0Ен  | 6 н             | X, 1, 1, 0 | $``H" \to ``L"$                         | "L" during coincidence                                                                      |

|      | 7 н             | 0, 1, 1, 1 | BUSY                                    | 1-second count flag                                                                         |

|      |                 | 0, X, X, X | Alarm coincidence<br>with auto reset    | Resets ALARM FLAG and stops alarm output in case of alarm non-coincidence                   |

|      |                 | 1, X, X, X | Alarm coincidence<br>without auto reset | Once alarm coincidence has occurred, continues output even if alarm non-coincidence occurs. |

#### Table 2-9. TP1 FUNCTION CONTROL REGISTERS

X: Don't Care

# (a) 1- to 2048-Hz output

These registers output a waveform with a duty factor of 50%. This waveform is always output to TP1 if the alarm is disabled and forced coincidence is selected by CONTROL REGISTER 2 (address  $0EH \leftarrow 6H$ ).

#### (b) 1-pulse output

This register outputs a low-active pulse only once (pulse width:  $30.5 \ \mu s$ ).

(c) "H"  $\rightarrow$  "L"

This register goes from H to L on alarm coincidence. It keeps L in the case of alarm non-coincidence.

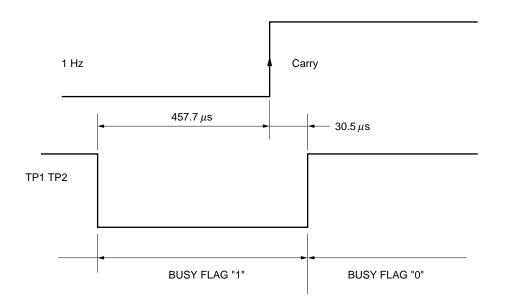

#### (d) BUSY signal

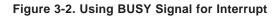

This is the count flag of the time counter. A carry occurs in the time counter 457.7  $\mu$ s after the BUSY signal has risen. If the value of the time counter is read while a carry occurs, the correct value may not be read. For details, refer to CHAPTER 3 ACCESS PROCEDURE.

#### Figure 2-8. BUSY Signal

#### Internal time counter

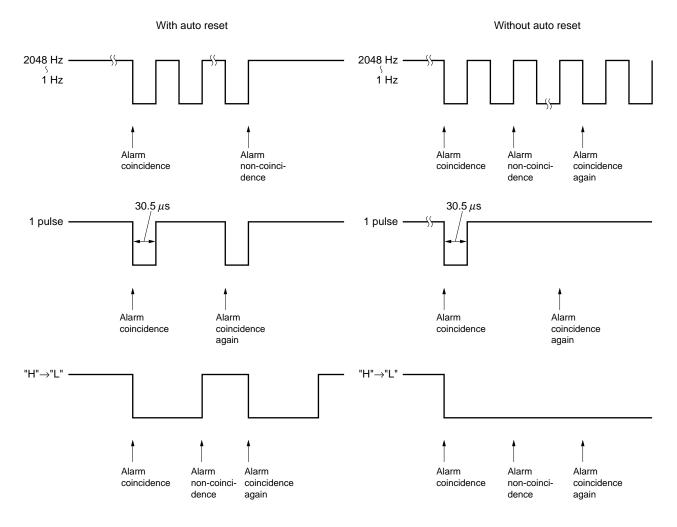

#### (e) Alarm flag with auto reset

When alarm coincidence occurs, the  $\mu$ PD4991A sets the ALARM FLAG and outputs an alarm signal to TP1. When alarm no longer coincides with the value of the time counter, and if the alarm coincidence with auto reset function is selected, the  $\mu$ PD4991A resets the ALARM FLAG and stops output from TP1 (restores to the H level).

If the alarm coincidence with auto reset function is not selected, TP1 output is not stopped. To stop it, write 0 to the ALARM FLAG of CONTROL REGISTER 2. This operation is illustrated in Figure 2-9.

#### Figure 2-9. TP1 Output Waveform

#### (3) Leap year counter (low-order 2 bits of address 0CH)

This counter takes a value of 0H to 3H and is synchronized with the year counter. When the value of the leap counter is 0H, a leap year is identified. If the leap year identification function is enabled, the last day of February in the leap year is 29.

Usually, the leap year counter is automatically set when the lower 2 digits of a year is written in the BASIC TIME MODE. Therefore, the user does not have to write a leap year. The  $\mu$ PD4991A operates from 1901 to 2099 without adjustment.

If a year other than a Western calender year is written to the year counter, the leap year counter may be rewritten after the year counter has been written (if the year is Showa in the Japanese calender, for example, divide the Showa year by 4 and add 1 to the result. Write this year to the leap year counter. Unless the year counter is rewritten, leap years will be automatically identified after that.)

If the year is Heisei, write the year to the year counter. The leap year counter does not have to be rewritten.

# (4) CONTROL REGISTER 1

This register controls the clock of the time counter in the same manner as in the BASIC TIME MODE.

# (5) CONTROL REGISTER 2

This register controls output of TP1 and TP2, alarm coincidence, and the clock to the interval timer, in the same manner as in the BASIC TIME MODE.

# (6) MODE REGISTER

This register determines the operation mode of the  $\mu$ PD4991A in the same manner as in the BASIC TIME MODE.

# 2.3.3 ALARM SET & TP2 CONTROL MODE (MODE REG. $\leftarrow$ 2)

In this mode, addresses 0H through 0AH are used as alarm registers (in the same manner as in the TP1 CONTROL MODE). Address 0BH is used as a control register that selects an interval signal to be output to TP2, and address 0CH is used to select 12- or 24-hour mode and enables or disables the leap year identification function. Addresses 0DH through 0FH are used in the same way as in the BASIC TIME MODE (refer to **Table 2-10**).

# Table 2-10. Register Assignment in ALARM SET & TP2 CONTROL MODE

| Address | Register                                                  | Description                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |  |  |  |

|---------|-----------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|--|

| 0 н     | Second, units digit                                       | Alarm register                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |  |  |  |

| 1 н     | Second, tens digit                                        | Sets and checks alarm time.                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |  |  |  |

| 2 н     | Minute, units digit                                       | When these registers are set to $0F_{H}$ , the digit corresponding to each register is assumed to coincide with the value of the time counter. When the alarm function is not used, these registers can be used as a back-up memory of 4 bits $\times$ 11 words (same as in TP1 CONTROL MODE). |  |  |  |  |  |  |  |  |  |

| 3 н     | Minute, tens digit                                        |                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |  |  |  |

| 4 н     | Hour, units digit                                         |                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |  |  |  |

| 5 н     | Hour, tens digit                                          |                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |  |  |  |

| 6 н     | Day of week digit                                         |                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |  |  |  |

| 7 н     | Date, units digit                                         |                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |  |  |  |

| 08 н    | Date, tens digit                                          |                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |  |  |  |

| 09 н    | Month, units digit                                        |                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |  |  |  |

| 0А н    | Month, tens digit                                         |                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |  |  |  |

| 0В н    | TP1 FUNCTION<br>CONTROL                                   | W/O. Selects TP2 output waveform.                                                                                                                                                                                                                                                              |  |  |  |  |  |  |  |  |  |

| 0С н    | Selects 12- or 24-hour                                    | D <sub>3</sub> D <sub>2</sub> D <sub>1</sub> D <sub>0</sub>                                                                                                                                                                                                                                    |  |  |  |  |  |  |  |  |  |

|         | mode and enables/<br>disables leap year<br>identification | R/W 12/24H mode Leap year X X<br>identification<br>disable                                                                                                                                                                                                                                     |  |  |  |  |  |  |  |  |  |

| 0D н    | CONTROL<br>REGISTER 1                                     | Same as in BASIC TIME MODE                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |  |  |  |

| 0Е н    | CONTROL<br>REGISTER 2                                     |                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |  |  |  |

| 0F н    | MODE<br>REGISTER                                          |                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |  |  |  |

X: Don't Care W/O: Write only

# (1) Alarm registers (addresses 0H through 0AH)

These registers operate in the same manner as in the TP1 CONTROL MODE. Refer to 2.3.2 (1).

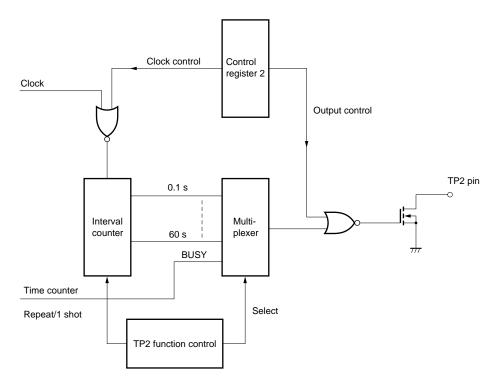

# (2) TP2 FUNCTION CONTROL REGISTER (address 0BH)

These registers select the waveform that is to be output to TP2.

|      | DATA            |            | Operation        | Description                                                            |

|------|-----------------|------------|------------------|------------------------------------------------------------------------|

| HE   | HEX D3 D2 D1 D0 |            |                  |                                                                        |

| 08 н | 0 н             | X, 0, 0, 0 | 0.1 sec INTERVAL | Interval timer output with pulse width of 30.5 $\mu$ s during L period |

| 09 н | 1н              | X, 0, 0, 1 | 1 sec INTERVAL   |                                                                        |

| 0А н | 2 н             | X, 0, 1, 0 | 10 sec INTERVAL  |                                                                        |

| 0В н | 3 н             | X, 0, 1, 1 | 30 sec INTERVAL  |                                                                        |

| 0С н | 4 н             | X, 1, 0, 0 | 60 sec INTERVAL  |                                                                        |

|      | 7 н             | 0, 1, 1, 1 | BUSY signal      | Count flag of time counter                                             |

|      |                 | 0, X, X, X | INTERVAL REPEAT  | Successively performs interval output                                  |

|      |                 | 1, X, X, X | INTERVAL 1 SHOT  | Performs interval output in only one cycle                             |

#### Table 2-11. TP2 FUNCTION CONTROL REGISTER

X: Don't Care

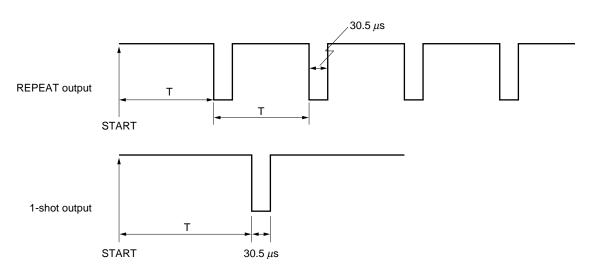

#### (a) 0.1- to 60-sec INTERVAL output

These registers output an interval signal with a cycle of 0.1 to 60 seconds and a pulse width of 30.5  $\mu$ s during the L period.

# (b) BUSY

This is the count flag of the time counter and is the same as the BUSY signal in the TP1 CONTROL MODE.

# (c) INTERVAL REPEAT/INTERVAL 1 SHOT

These registers control the repetition of the interval signal. Figure 2-10 shows the differences between the two.

#### Figure 2-10. TP2 Output Waveform

If CONTROL REGISTER 2 described earlier is used, the control operation shown in Figure 2-11 can be performed.

Figure 2-11. Interval Signal Output Example

**Note** If the output status is disabled, the output is turned off (high impedance) regardless of the status of TP2.

#### Caution

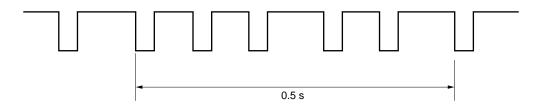

The interval output is produced not once in a cycle of 0.1 s but in five times, as shown below.

Figure 2-12. 0.1-Second Interval Output

#### (3) 12-/24-hour mode and leap year identification (address 0CH)

#### Table 2-12. 12-/24-Hour Mode and Leap Year Identification Command (R/W)

| D <sub>3</sub>   | D <sub>2</sub>           | D1 | Do |

|------------------|--------------------------|----|----|

| 12-/24-hour mode | Leap year identification | Х  | Х  |

X: Don't Care

#### (a) 12-/24-hour mode selection

This bit selects the 12-hour mode when it is 0; when it is 1, the 24-hour mode is selected. In the 12-hour mode, the second highest bit (D<sub>2</sub>) of the tens digit of hour serves as the  $\overline{AM}$ /PM flag.

| Example |         | Hour, tens digit |    |      |         | Hour, units digit |    |    |    |      |  |

|---------|---------|------------------|----|------|---------|-------------------|----|----|----|------|--|

|         |         | Dз               | D2 | D1   | Do      | Dз                | D2 | D1 | Do | HEX  |  |

|         | 5 a.m.  | 0                | 0  | -    | 0       | 0                 | 1  | 0  | 1  | 05 н |  |

|         |         |                  |    | AM/I | PM flag |                   |    |    |    |      |  |

|         | 5 p.m.  | 0                | 1  | 0    | 0       | 0                 | 1  | 0  | 1  | 45 н |  |

|         | 11 a.m. | 0                | 0  | 0    | 1       | 0                 | 0  | 0  | 1  | 11 н |  |

|         | 11 p.m. | 0                | 1  | 0    | 1       | 0                 | 0  | 0  | 1  | 51 н |  |

#### Caution

If the mode is changed between the 12- and 24-hour modes, the hour counter must be rewritten (if this flag is changed after data has been written to the hour counter, the value of the hour counter may be lost).

#### (b) Leap year identification

When this bit is set to 1, the leap year identification function is disabled. As a result, the end of February is 28 even if the value of the leap year counter is xx00.

#### 2.3.4 TEST MODE

This mode is to test the functions of the  $\mu$ PD4991A. In the TEST mode, a total of eight modes can be selected: three TEST (BASIC TIME) MODEs in which the time counter is read/written, two TEST (ALARM SET & TP1 CONT.) MODEs of the alarm timer, and three TEST (ALARM SET & TP2 CONT.) MODEs of the interval timer.

In each mode, the clock is input to the counter differently. For details, refer to **Table 2-13. Test Modes of**  $\mu$ **PD4991A**. Note that **some functions are disabled in the test mode**. Because the test mode is to test the functions, continous operation is not guaranteed if the device is normally used in the test mode.

| Value Se | t to Mode Register                                          | Operation Mode                       | Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

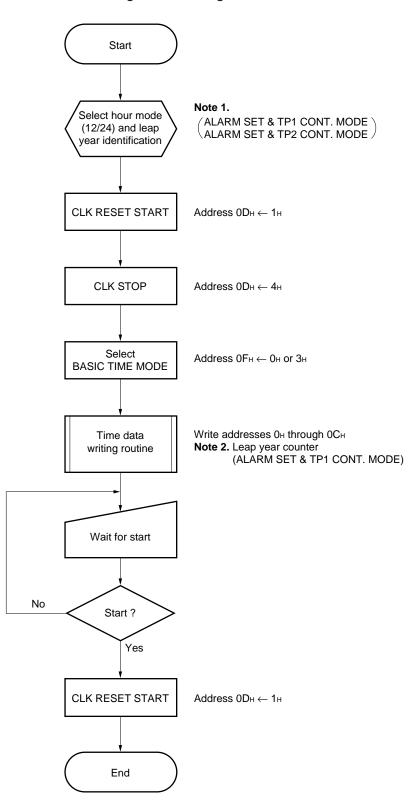

|----------|-------------------------------------------------------------|--------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|