#

## 3.3 V/2.5 V 1:15 PECL/LVCMOS Clock Fanout Buffer

**MPC9449**

The MPC9449 is a 3.3 V or 2.5 V compatible, 1:15 clock fanout buffer targeted for high performance clock tree applications. With output frequencies up to 200 MHz and output skews less than 200 ps the device meets the needs of the most demanding clock applications.

#### Features

- 15 LVCMOS compatible clock outputs

- Two selectable LVCMOS and one differential LVPECL compatible clock inputs

- Selectable output frequency divider (divide-by-one and divide-by-two)

- Maximum clock frequency of 200 MHz

- Maximum clock skew of 200 ps

- · High-impedance output control

- 3.3 V or 2.5 V power supply

- · Drives up to 30 series terminated clock lines

- Ambient temperature range –40°C to +85°C

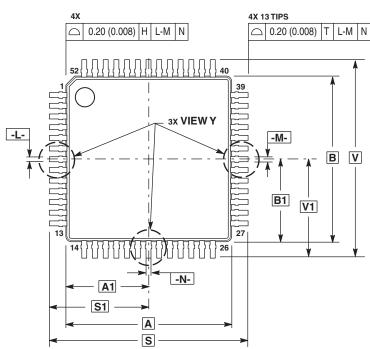

- 52-lead LQFP packaging

- 52-lead Pb-free package available

- Supports clock distribution in networking, telecommunication and computing applications

- Pin and function compatible to MPC949

#### **Functional Description**

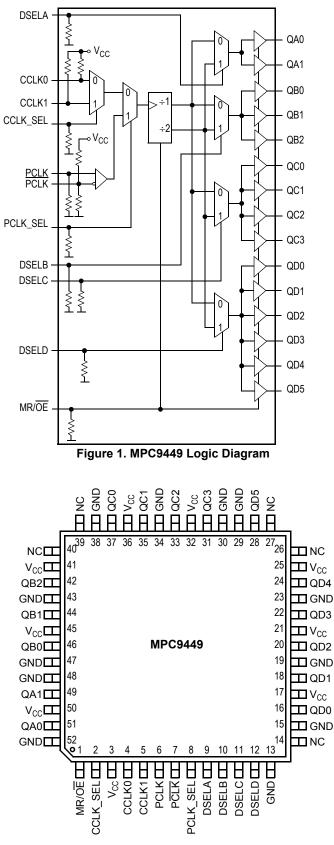

The MPC9449 is specifically designed to distribute LVCMOS compatible clock signals up to a frequency of 200 MHz. The device has 15 identical outputs,

organized in four output banks. Each output bank provides a retimed or

frequency divided copy of the input signal with a near zero skew. The output buffer supports driving of 50  $\Omega$  terminated transmission lines on the incident edge: each output is capable of driving either one parallel terminated or two series terminated transmission lines.

Two selectable LVCMOS compatible clock inputs are available. This feature supports redundant differential clock sources. In addition, the MPC9449 accepts one differential PECL clock signal. The DSELx pins choose between division of the input reference frequency by one or two. The frequency divider can be set individually for each of the four output banks. Applying the OE control will force the outputs into high-impedance mode.

All inputs have an internal pull-up or pull-down resistor preventing unused and open inputs from floating. The device supports a 2.5 V or 3.3 V power supply and an ambient temperature range of –40°C to +85°C. The MPC9449 is pin and function compatible but performance-enhanced to the MPC949. The device is packaged in a 52-lead LQFP package.

1

PACKAGE DIMENSIONS

Figure 2. PC9449 52-Lead Package Pinout (Top View)

IDT™ / ICS™ 1:15 PECL/LVCMOS CLOCK FANOUT BUFFER

#### Table 1. Function Table

| Control                       | Default    | 0                                            | 1                                 |

|-------------------------------|------------|----------------------------------------------|-----------------------------------|

| PCLK_SEL                      | 0          | LVCMOS clock input selected (CCLK0 or CCLK1) | PCLK differential input selected  |

| CCLK_SEL                      | 0          | CCLK0 selected                               | CCLK1 selected                    |

| DSELA, DSELB,<br>DSELC, DSELD | 0 0<br>0 0 | ÷1                                           | ÷2                                |

| MR/OE                         | 1          | Outputs enabled                              | Outputs disabled (high impedance) |

#### Table 2. Pin Configuration

| Pin                        | I/O    | Туре            | Function                                                                                                                           |

|----------------------------|--------|-----------------|------------------------------------------------------------------------------------------------------------------------------------|

| PCLK, PCLK                 | Input  | LVPECL          | Differential LVPECL clock input                                                                                                    |

| CCLK0, CCLK1               | Input  | LVCMOS          | LVCMOS clock inputs                                                                                                                |

| PCLK_SEL                   | Input  | LVCMOS          | LVPECL clock input select                                                                                                          |

| CCLK_SEL                   | Input  | LVCMOS          | LVCMOS clock input select                                                                                                          |

| DSELA, DSELB, DSELC, DSELD | Input  | LVCMOS          | Clock divider selection                                                                                                            |

| MR/OE                      | Input  | LVCMOS          | Output enable/disable (high-impedance tristate)                                                                                    |

| QA0-1, QB0-2, QC0-3, QD0-5 | Output | LVCMOS          | Clock outputs                                                                                                                      |

| GND                        | Supply | Ground          | Negative power supply (GND)                                                                                                        |

| V <sub>CC</sub>            | Supply | V <sub>CC</sub> | Positive power supply for I/O and core. All $V_{\rm CC}$ pins must be connected to the positive power supply for correct operation |

#### **Table 3. General Specifications**

| Symbol          | Characteristics                   | Min  | Тур             | Max | Unit | Condition  |

|-----------------|-----------------------------------|------|-----------------|-----|------|------------|

| V <sub>TT</sub> | Output Termination Voltage        |      | $V_{CC} \div 2$ |     | V    |            |

| MM              | ESD Protection (Machine Model)    | 200  |                 |     | V    |            |

| HBM             | ESD Protection (Human Body Model) | 2000 |                 |     | V    |            |

| LU              | Latch-Up Immunity                 | 200  |                 |     | mA   |            |

| C <sub>PD</sub> | Power Dissipation Capacitance     |      | 12              |     | pF   | Per output |

| C <sub>IN</sub> | Input Capacitance                 |      | 4.0             |     | pF   | Inputs     |

#### Table 4. Absolute Maximum Ratings<sup>(1)</sup>

| Symbol           | Characteristics     | Min  | Мах                  | Unit | Condition |

|------------------|---------------------|------|----------------------|------|-----------|

| V <sub>CC</sub>  | Supply Voltage      | -0.3 | 3.8                  | V    |           |

| V <sub>IN</sub>  | DC Input Voltage    | -0.3 | V <sub>CC</sub> +0.3 | V    |           |

| V <sub>OUT</sub> | DC Output Voltage   | -0.3 | V <sub>CC</sub> +0.3 | V    |           |

| I <sub>IN</sub>  | DC Input Current    |      | ±20                  | mA   |           |

| I <sub>OUT</sub> | DC Output Current   |      | ±50                  | mA   |           |

| Τ <sub>S</sub>   | Storage Temperature | -65  | 125                  | °C   |           |

1. Absolute maximum continuous ratings are those maximum values beyond which damage to the device may occur. Exposure to these conditions or conditions beyond those indicated may adversely affect device reliability. Functional operation at absolute-maximum-rated conditions is not implied.

| Symbol                          | Characteristics                       | Min | Тур     | Max                   | Unit   | Condition                                          |

|---------------------------------|---------------------------------------|-----|---------|-----------------------|--------|----------------------------------------------------|

| V <sub>IH</sub>                 | Input High Voltage                    | 2.0 |         | V <sub>CC</sub> + 0.3 | V      | LVCMOS                                             |

| V <sub>IL</sub>                 | Input Low Voltage                     |     |         | 0.8                   | V      | LVCMOS                                             |

| V <sub>OH</sub>                 | Output High Voltage                   | 2.4 |         |                       | V      | I <sub>OH</sub> = -24 mA <sup>(1)</sup>            |

| V <sub>PP</sub>                 | Peak-to-Peak Input Voltage PCLK, PCLK | 250 |         |                       | mV     | LVPECL                                             |

| V <sub>CMR</sub> <sup>(2)</sup> | Common Mode Range PCLK, PCLK          | 1.0 |         | V <sub>CC</sub> -0.6  | V      | LVPECL                                             |

| V <sub>OL</sub>                 | Output Low Voltage                    |     |         | 0.55<br>0.30          | V<br>V | I <sub>OL</sub> = 24 mA<br>I <sub>OL</sub> = 12 mA |

| Z <sub>OUT</sub>                | Output Impedance                      |     | 14 – 17 |                       | Ω      |                                                    |

| I <sub>IN</sub>                 | Input Current                         |     |         | ±200                  | μA     | $V_{IN} = V_{CC}$ or GND                           |

| I <sub>CCQ</sub>                | Maximum Quiescent Supply Current      |     |         | 10                    | mA     | All $V_{CC}$ Pins                                  |

#### Table 5. DC Characteristics (V<sub>CC</sub> = 3.3 V $\pm$ 5%, T<sub>A</sub> = -40°C to 85°C)

1. The MPC9449 is capable of driving 50  $\Omega$  transmission lines on the incident edge. Each output drives one 50  $\Omega$  parallel terminated transmission line to a termination voltage of V<sub>TT</sub>. Alternatively, the device drives up to two 50  $\Omega$  series terminated transmission lines.

V<sub>CMR</sub> (DC) is the crosspoint of the differential input signal. Functional operation is obtained when the crosspoint is within the V<sub>CMR</sub> range and the input swing lies within the V<sub>PP</sub> (DC) specification.

| Symbol                           | I Characteristics                                                |                                                                                    | Min        | Тур        | Max                                 | Unit                             | Condition               |

|----------------------------------|------------------------------------------------------------------|------------------------------------------------------------------------------------|------------|------------|-------------------------------------|----------------------------------|-------------------------|

| V <sub>PP</sub>                  | Peak-to-Peak Input Voltage                                       | PCLK, PCLK                                                                         | 400        |            | 1000                                | mV                               | LVPECL                  |

| V <sub>CMR</sub> <sup>(2)</sup>  | Common Mode Range                                                | PCLK, PCLK                                                                         | 1.0        |            | V <sub>CC</sub> -0.6                | V                                | LVPECL                  |

| f <sub>max</sub>                 | Output Frequency                                                 |                                                                                    | 0          |            | 200                                 | MHz                              |                         |

| f <sub>ref</sub>                 | Input Frequency                                                  |                                                                                    | 0          |            | 200                                 | MHz                              |                         |

| t <sub>P, REF</sub>              | Reference Input Pulse Width                                      |                                                                                    | 1.5        |            |                                     | ns                               |                         |

| t <sub>r</sub> , t <sub>f</sub>  | CCLK0, CCLK1 Input Rise/Fall Tir                                 | ne                                                                                 |            |            | 1.0                                 | ns                               | 0.8 to 2.0 V            |

| t <sub>sk(O)</sub>               | Output-to-Output Skew<br>Same Frequency<br>Different Frequencies | Qa outputs<br>Qb outputs<br>Qc outputs<br>Qd outputs<br>All outputs<br>All outputs |            |            | 50<br>50<br>50<br>100<br>200<br>300 | ps<br>ps<br>ps<br>ps<br>ps<br>ps |                         |

| t <sub>sk(PP)</sub>              | Device-to-Device Skew                                            |                                                                                    |            | 2.5        |                                     | ns                               |                         |

| t <sub>sk(P)</sub>               | Output Pulse Skew                                                |                                                                                    |            |            | 250                                 | ps                               | DC <sub>REF</sub> = 50% |

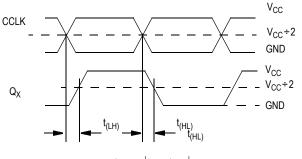

| t <sub>PLH</sub> , <sub>HL</sub> | Propagation Delay CCLK0 or 0                                     | CCLK1 to any Q<br>PCLK to any Q                                                    | 1.0<br>1.0 | 3.0<br>3.0 | 5.0<br>5.0                          | ns<br>ns                         |                         |

| t <sub>PLZ, HZ</sub>             | Output Disable Time                                              | OE to any Q                                                                        |            |            | 11                                  | ns                               |                         |

| t <sub>PZL, LZ</sub>             | Output Enable Time                                               | OE to any Q                                                                        |            |            | 11                                  | ns                               |                         |

| t <sub>r</sub> , t <sub>f</sub>  | Output Rise/Fall Time <sup>(3)</sup>                             |                                                                                    | 0.1        |            | 1.0                                 | ns                               | 0.55 to 2.4 V           |

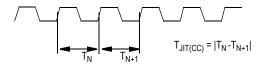

| t <sub>JIT(CC)</sub>             | Cycle-to-Cycle Jitter                                            | RMS (1 σ)                                                                          |            | TBD        |                                     | ps                               |                         |

#### Table 6. AC Characteristics ( $V_{CC}$ = 3.3 V ± 5%, $T_A$ = -40°C to 85°C)<sup>(1)</sup>

1. AC characteristics apply for parallel output termination of 50  $\Omega$  to V\_TT.

V<sub>CMR</sub> (AC) is the crosspoint of the differential input signal. Normal AC operation is obtained when the crosspoint is within the V<sub>CMR</sub> range and the input swing lies within the V<sub>PP</sub> (AC) specification. Violation of V<sub>CMR</sub> or V<sub>PP</sub> impacts propagation delay.

3. An input rise/fall time greater than that specified may be used, but AC characteristics are not guaranteed under such a condition.

| Symbol                          | Characteristics                       | Min  | Тур   | Max                   | Unit | Condition                               |

|---------------------------------|---------------------------------------|------|-------|-----------------------|------|-----------------------------------------|

| V <sub>IH</sub>                 | Input High Voltage                    | 1.7  |       | V <sub>CC</sub> + 0.3 | V    | LVCMOS                                  |

| V <sub>IL</sub>                 | Input Low Voltage                     | -0.3 |       | 0.7                   | V    | LVCMOS                                  |

| V <sub>PP</sub>                 | Peak-to-Peak Input Voltage PCLK, PCLK | 250  |       |                       | mV   | LVPECL                                  |

| V <sub>CMR</sub> <sup>(1)</sup> | Common Mode Range PCLK, PCLK          | 1.0  |       | V <sub>CC</sub> -0.6  | V    | LVPECL                                  |

| V <sub>OH</sub>                 | Output High Voltage                   | 1.8  |       |                       | V    | I <sub>OH</sub> = –15 mA <sup>(2)</sup> |

| V <sub>OL</sub>                 | Output Low Voltage                    |      |       | 0.6                   | V    | I <sub>OL</sub> = 15 mA                 |

| Z <sub>OUT</sub>                | Output Impedance                      |      | 17–20 |                       | Ω    |                                         |

| I <sub>IN</sub>                 | Input Current <sup>(3)</sup>          |      |       | ±200                  | μA   | $V_{IN}$ = $V_{CC}$ or GND              |

| I <sub>CC</sub>                 | Maximum Quiescent Supply Current      |      |       | 10                    | mA   | All $V_{CC}$ Pins                       |

#### Table 7. DC Characteristics ( $V_{CC}$ = 2.5 V ± 5%, $T_A$ = -40°C to 85°C)

1. V<sub>CMR</sub> (DC) is the crosspoint of the differential input signal. Functional operation is obtained when the crosspoint is within the V<sub>CMR</sub> range and the input swing lies within the V<sub>PP</sub> (DC) specification.

2. The MPC9449 is capable of driving 50  $\Omega$  transmission lines on the incident edge. Each output drives one 50  $\Omega$  parallel terminated transmission line to a termination voltage of V<sub>TT</sub>.

3. Inputs have pull-down or pull-up resistors affecting the input current.

#### Symbol Characteristics Min Max Unit Condition Тур LVPECL V<sub>PP</sub> Peak-to-Peak Input Voltage PCLK, PCLK 400 1000 mV $V_{CMR}^{(2)}$ Common Mode Range PCLK, PCLK 1.2 V<sub>CC</sub>-0.6 V LVPECL 200 MHz **Output Frequency** 0 f<sub>max</sub> Input Frequency 0 200 MHz f<sub>ref</sub> Reference Input Pulse Width 1.5 ns t<sub>P, REF</sub> tr, tf CCLK Input Rise/Fall Time 1.0 ns 0.7 to 1.7 V Output-to-Output Skew Qa outputs 50 t<sub>sk(O)</sub> ps Qb outputs 50 ps Qc outputs 50 ps Qd outputs 100 ps Same Frequency All outputs 200 ps **Different Frequencies** All outputs 300 ps Device-to-Device Skew 5.0 ns t<sub>sk(PP)</sub> Output Pulse Skew 350 DC<sub>REF</sub> = 50% ps t<sub>SK(P)</sub> Propagation Delay 70 CCLK0 or CCLK1 to any Q 1.0 3.5 t<sub>PLH, HL</sub> ns PCLK to any Q 1.0 3.5 7.0 ns **Output Disable Time** OE to any Q 11 ns t<sub>PLZ, HZ</sub> **Output Enable Time** OE to any Q 11 ns t<sub>PZL, LZ</sub> t<sub>r</sub>, t<sub>f</sub> Output Rise/Fall Time<sup>(3)</sup> 0.1 1.0 ns 0.6 to 1.8 V Cycle-to-Cycle Jitter RMS (1 σ) TBD ps t<sub>JIT(CC)</sub>

#### Table 8. AC Characteristics (V<sub>CC</sub> = 2.5 V $\pm$ 5%, T<sub>A</sub> = -40°C to 85°C)<sup>(1)</sup>

1. AC characteristics apply for parallel output termination of 50  $\Omega$  to V\_TT.

V<sub>CMR</sub> (AC) is the crosspoint of the differential input signal. Normal AC operation is obtained when the crosspoint is within the V<sub>CMR</sub> range and the input swing lies within the V<sub>PP</sub> (AC) specification. Violation of V<sub>CMR</sub> or V<sub>PP</sub> impacts propagation delay.

3. An input rise/fall time greater than that specified may be used, but AC characteristics are not guaranteed under such a condition.

#### APPLICATIONS INFORMATION

#### **Driving Transmission Lines**

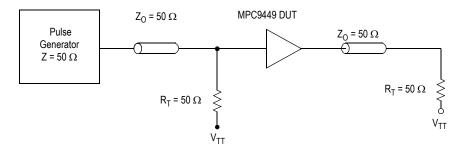

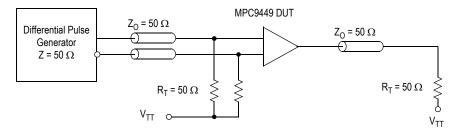

The MPC9449 clock driver was designed to drive high speed signals in a terminated transmission line environment. To provide the optimum flexibility to the user the output drivers were designed to exhibit the lowest impedance possible. With an output impedance of less than 20  $\Omega$  the drivers can drive either parallel or series terminated transmission lines. For more information on transmission lines the reader is referred to Freescale Semiconductor application note AN1091. In most high performance clock networks point-to-point distribution of signals is the method of choice. In a point-to-point scheme either series terminated or parallel terminated transmission lines the signal at the end of the line with a 50  $\Omega$  resistance to  $V_{\rm CC}$ +2.

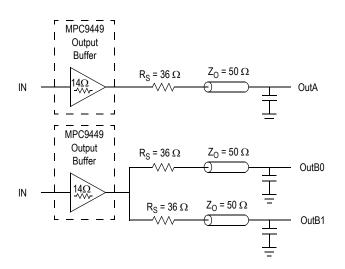

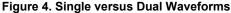

This technique draws a fairly high level of DC current and thus only a single terminated line can be driven by each output of the MPC9449 clock driver. For the series terminated case however there is no DC current draw, thus the outputs can drive multiple series terminated lines. Figure 3 illustrates an output driving a single series terminated line versus two series terminated lines in parallel. When taken to its extreme the fanout of the MPC9449 clock driver is effectively doubled due to its capability to drive multiple lines.

Figure 3. Single versus Dual Transmission Lines

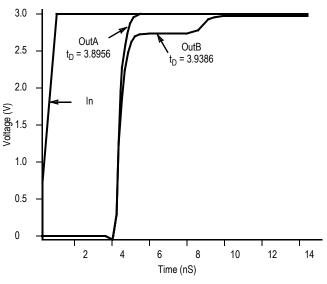

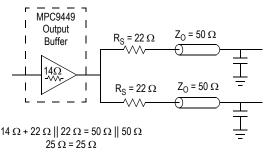

The waveform plots in Figure 4 show the simulation results of an output driving a single line versus two lines. In both cases the drive capability of the MPC9449 output buffer is more than sufficient to drive 50  $\Omega$  transmission lines on the incident edge. Note from the delay measurements in the simulations a delta of only 43 ps exists between the two differently loaded outputs. This suggests that the dual line driving need not be used exclusively to maintain the tight output-to-output skew of the MPC9449. The output waveform in Figure 4 shows a step in the waveform, this step is caused by the impedance mismatch seen looking into the driver. The parallel combination of the 36  $\Omega$  series resistor plus the

output impedance does not match the parallel combination of the line impedances. The voltage wave launched down the two lines will equal:

$$V_{L} = V_{S} (Z_{0} \div (R_{S} + R_{0} + Z_{0}))$$

$$Z_{0} = 50 \Omega \parallel 50 \Omega$$

$$R_{S} = 36 \Omega \parallel 36 \Omega$$

$$R_{0} = 14 \Omega$$

$$V_{L} = 3.0 (25 \div (18 + 17 + 25))$$

$$= 1.31 V$$

At the load end the voltage will double, due to the near unity reflection coefficient, to 2.6 V. It will then increment towards the quiescent 3.0 V in steps separated by one round trip delay (in this case 4.0 ns).

1. Final skew data pending specification.

Since this step is well above the threshold region it will not cause any false clock triggering, however designers may be uncomfortable with unwanted reflections on the line. To better match the impedances when driving multiple lines the situation in Figure 5 should be used. In this case the series terminating resistors are reduced such that when the parallel combination is added to the output buffer impedance the line impedance is perfectly matched.

Figure 5. Optimized Dual Line Termination

6

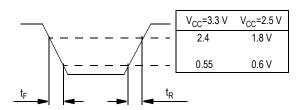

Figure 6. CCLK MPC9449 AC Test Reference for V<sub>CC</sub> = 3.3 V and V<sub>CC</sub> = 2.5 V

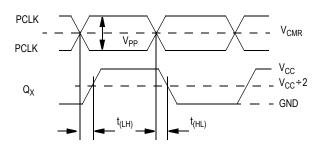

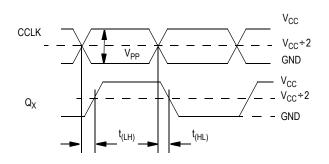

Figure 7. PCLK MPC9449 AC Test Reference

The pin-to-pin skew is defined as the worst case difference in propagation delay between any similar delay path within a single device

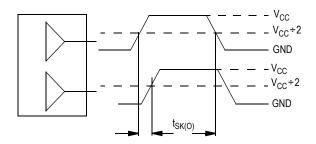

#### Figure 8. Output-to-Output Skew t<sub>SK(O)</sub>

#### Figure 10. Propagation Delay (t<sub>PD</sub>) Test Reference

Figure 12. Output Transition Time Test Reference

Figure 9. Propagation Delay (t<sub>PD</sub>) Test Reference

t<sub>SK(P)</sub>= |t<sub>PLH</sub>-t<sub>PLH</sub> |

#### Figure 11. Propagation Delay t<sub>SK(P)</sub> Test Reference

The variation in cycle time of a signal between adjacent cycles, over a random sample of adjacent cycle pairs

> Figure 13. Cycle-to-Cycle Jitter Figure 14

8

#### MPC9449 3.3V/2.5V 1:15 PECL/LVCMOS CLOCK FANOUT BUFFER

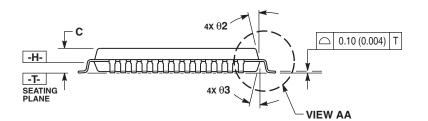

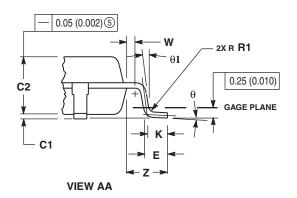

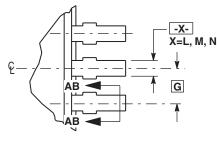

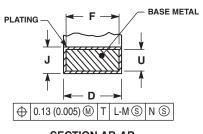

#### PACKAGE DIMENSIONS

SECTION AB-AB ROTATED 90° CLOCKWISE

NOTES:

- CONTROLLING DIMENSIONS: MILLIMETER. 1. 2. DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982. 3. DATUM PLANE -H- IS LOCATED AT BOTTOM OF

- DATIOM PLANE -H-IS LOCATED AT BOTTOM OF LEAD AND IS COINCIDENT WITH THE LEAD WHERE THE LEAD EXITS THE PLASTIC BODY AT THE BOTTOM OF THE PARTING LINE.

DATUMS -L., -M- AND N-N-TO BE DETERMINED AT DATUM PLANE -H-.

- 5. DIMENSIONS S AND V TO BE DETERMINED AT

- DIMENSIONS A AND B DO NOT INCLUDE MOLD SEATING PLANE -T.

DIMENSIONS A AND B DO NOT INCLUDE MOLD PROTRUSION. ALLOWABLE PROTRUSION IS 0.25 (0.010) PER SIDE. DIMENSIONS A AND B DO INCLUDE MOLD MISMATCH AND ARE DETERMINED AT DATUM PLANE -H-.

- DIMENSION D DOES NOT INCLUDE DAMBAR PROTRUSION. DAMBAR PROTRUSION SHALL NOT CAUSE THE LEAD WIDTH TO EXCEED 0.46 (0.018). MINIMUM SPACE BETWEEN PROTRUSION AND ADJACENT LEAD OR PROTRUSTION 0.07 (0.003).

|            | MILLIM    | ETERS     | INCHES        |       |  |

|------------|-----------|-----------|---------------|-------|--|

| DIM        | MIN       | MAX       | MIN           | MAX   |  |

| Α          | 10.00 BSC |           | 0.394 BSC     |       |  |

| A1         | 5.00 BSC  |           | 0.197 BSC     |       |  |

| В          | 10.00     | BSC       | 0.394         | BSC   |  |

| B1         | 5.00      | BSC       | 0.197         | BSC   |  |

| С          |           | 1.70      |               | 0.067 |  |

| C1         | 0.05      | 0.20      | 0.002         | 0.008 |  |

| C2         | 1.30      | 1.50      | 0.051         | 0.059 |  |

| D          | 0.20      | 0.40      | 0.008         | 0.016 |  |

| Е          | 0.45      | 0.75      | 0.018         | 0.030 |  |

| F          | 0.22      | 0.35      | 0.009         | 0.014 |  |

| G          | 0.65 BSC  |           | 0.026 BSC     |       |  |

| J          | 0.07      | 0.20      | 0.003         | 0.008 |  |

| κ          | 0.50      | REF       | 0.020 REF     |       |  |

| <b>R1</b>  | 0.08      | 0.20      | 0.003         | 0.008 |  |

| s          | 12.00 BSC |           | 0.472         | BSC   |  |

| S1         | 6.00      | 6.00 BSC  |               | BSC   |  |

| U          | 0.09      | 0.16      | 0.004         | 0.006 |  |

| V          | 12.00     | 12.00 BSC |               | BSC   |  |

| V1         | 6.00      | BSC       | 0.236         | BSC   |  |

| W          | 0.20      | REF       | 0.008         | REF   |  |

| Ζ          | 1.00      | REF       | REF 0.039 REF |       |  |

| θ          | 0°        | 7°        | 0°            | 7°    |  |

| θ1         | 0°        |           | 0°            |       |  |

| θ2         | 12°       | REF       | 12° REF       |       |  |

| θ <b>3</b> | 12°       | REF       | 12°           | REF   |  |

#### CASE 848D-03 **ISSUE D 52-LEAD LQFP PACKAGE**

### Innovate with IDT and accelerate your future networks. Contact:

#### For Sales

800-345-7015 408-284-8200 Fax: 408-284-2775

#### For Tech Support

netcom@idt.com 480-763-2056

#### **Corporate Headquarters**

Integrated Device Technology, Inc. 6024 Silver Creek Valley Road San Jose, CA 95138 United States 800 345 7015 +408 284 8200 (outside U.S.)

#### Asia Pacific and Japan

Integrated Device Technology Singapore (1997) Pte. Ltd. Reg. No. 199707558G 435 Orchard Road #20-03 Wisma Atria Singapore 238877 +65 6 887 5505

#### Europe

IDT Europe, Limited 321 Kingston Road Leatherhead, Surrey KT22 7TU England +44 (0) 1372 363 339 Fax: +44 (0) 1372 378851

© 2006 Integrated Device Technology, Inc. All rights reserved. Product specifications subject to change without notice. IDT and the IDT logo are trademarks of Integrated Device Technology, Inc. Accelerated Thinking is a service mark of Integrated Device Technology, Inc. All other brands, product names and marks are or may be trademarks or registered trademarks used to identify products or services of their respective owners. Printed in USA