# Features

- Backscatter-based UHF RFID IC (860 MHz to 960 MHz) Supporting Current and Future Radio Regulations

- Support for All Data Structures Defined in ISO/IEC 18000-6, ISO/IEC 15961, ISO/IEC 15963, GS1

- Passive Backscatter-communication–based Data Carrier IC

12 μW RF Power Required for Minimum Communication Feasibility

- Memory Programming Possible in Atomic and Global Mode

- Programmable Trigger Functionality

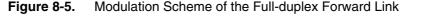

- PR-ASK/ASK Modulation Combined with Pulse Interval Encoding (PIE) Style in the Forward Direction to Enable Maximum Power Transport Combined with High Blocking Resistance

- Short, Long, and Temporary Commands

- Synchronous Return Link to Achieve Highest SNR

- 2PSK for the Backscatter Data Stream to Achieve Highest SNR

- Full-duplex and Half-duplex Communication Modes

- Several Closed-loop Possibilities to Enable

- Adaptive Speed During Read and Anticollision Procedures

- Fast Programming

- Communication Speed 5 Kbits/s to 60 Kbits/s, Fully Controlled by the Reader

- Different Speed Factors Possible in Forward and Return Link

- Two Kinds of Anticollision Procedures Implemented

- Deterministic and Slotted Aloha Anticollision Procedure

- Group\_selection Commands Supporting =, <, and > Comparisons

- Wake-up Commands

- All Procedures Support 16-bit Random Values for Access Control Mechanisms

- No Unique Data Structures are Needed to Enable Both Anticollision Procedures

- Parallel Handling of Different Structures, and Opening of Migration Paths for Private Structures

- Applications in Open Data Systems as well as in Closed Systems

- Maximum ID is Limited Only by the User Memory Space (1024 Bits + 256 Bits)

- Both Procedures Also Support Virgin-tag Initialization During Anticollision

- High-efficiency Commands to Increase and Adapt Anticollision Speed

# 1. Description

ATA5590 is a wireless data carrier IC. The IC is powered by the RF field transmitted by a reader. The carrier frequency is typically in the UHF region. The functionality of the IC is controlled by the reader. The IC returns the required information back to the reader using a backscatter modulation technique; it is a passive UHF transponder device based on the experience of the EU-funded project Palomar (IST1999-10339).

The main challenge for ATA5590 was to enable applications for open data management systems while considering legacy data systems.

1.3-kbit UHF R/W IDIC<sup>®</sup> with Anti-collision Function

# ATA5590 TAGIDU<sup>™</sup>

4817C-RFID-03/07

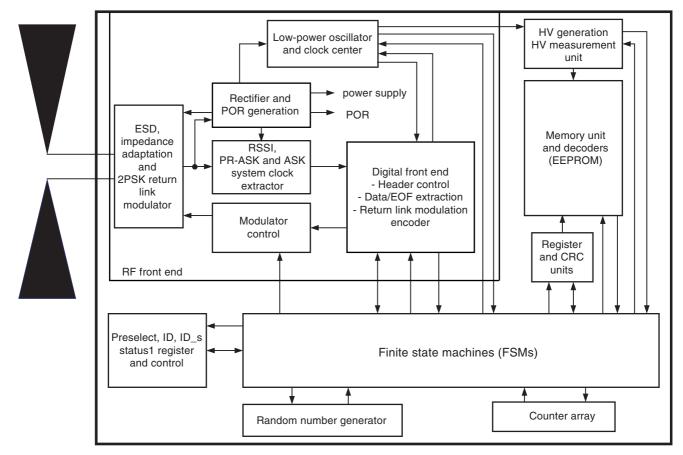

Figure 1-1. Block Diagram of the ATA5590

# 1.1 Parameters of the Link

| Parameter                              | Parameter Value                                       | Comment                                                                                                |  |

|----------------------------------------|-------------------------------------------------------|--------------------------------------------------------------------------------------------------------|--|

| Forward link encoding                  | Pulse interval modulated code                         | To generate the boundaries between the bits and symbols                                                |  |

| Forward link modulation                | PR-ASK and ASK                                        |                                                                                                        |  |

| Forward modulation index m             | PR-ASK: 100%<br>ASK: > 80%                            |                                                                                                        |  |

| Forward link data rate                 | 5 Kbits/s to 60 Kbits/s                               |                                                                                                        |  |

| Forward link bit ordering              | MSB first                                             |                                                                                                        |  |

| Type of communication                  | Half duplex or full duplex                            |                                                                                                        |  |

| Type of command                        | Short commands<br>Long commands<br>Temporary commands |                                                                                                        |  |

| Return link data rate                  | 5 Kbits/s to 60 Kbits/s                               | Independent from forward data rate                                                                     |  |

| Return link modulation                 | 2PSK                                                  | To achieve higher SNR and lower BER<br>values than ASK<br>To achieve longer communication<br>distances |  |

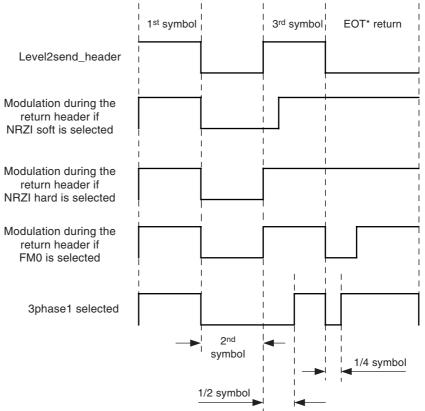

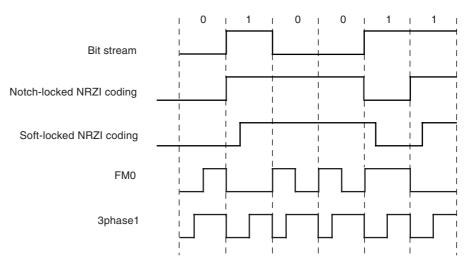

| Return link encoding for data encoding | FM0<br>3phase1<br>NRZI<br>Soft NRZI                   | Spectrum and edge management during<br>the return link header section controlled<br>by the reader      |  |

| Error and ready signalling             | Sub-carrier OSC / 4<br>Sub-carrier OSC / 8            | Sub-carrier modulation used for error and ready signalling                                             |  |

| Return link bit ordering               | MSB first                                             |                                                                                                        |  |

| Return link transmission mode          | Synchronous                                           | Including loop functions                                                                               |  |

Table 1-1.

Parameters of the RF Link

| Parameter                                                              | Description                                                                                                                                                                                                      | Comment                                                                                                                                                           |

|------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Error detection forward<br>link                                        | Header plausibility check<br>2-bit CRC for command frame<br>16-bit CRC over the whole frame<br>Bit length check<br>Loop function for CRC<br>Once received, a decoded bit is<br>backscattered in full duplex mode | To be synchronized to the reader, the<br>header_ok check and the command CRC<br>have to be received successfully; then<br>the tag can communicate with the reader |

| Error detection return link                                            | 16-bit CRC<br>CRC length is adaptive, also in loop<br>mode                                                                                                                                                       |                                                                                                                                                                   |

| Error code during return<br>link                                       | Inside the 8-bit status2 transfer                                                                                                                                                                                | Data CRC wrong<br>Bit length coding wrong<br>Page locked (for programming)                                                                                        |

| Error coding if forward<br>CRC was correct but<br>command unknown      | Disabling full duplex in the forward<br>direction and sub-carrier (OSC / 4)<br>during the first symbol after EOF1                                                                                                | No error code (status2) is backscattered<br>Tag is silent during return link, and<br>becomes asynchronous to the reader                                           |

| Error coding if memory<br>address is unknown but<br>command was known. | Sub-carrier modulation (OSC / 4)<br>during the first header symbol of the<br>return link                                                                                                                         | No error code (status2) is backscattered<br>Tag is silent during the rest of the return<br>link                                                                   |

| Error coding if program procedure is failed                            | Sub-carrier: OSC / 8                                                                                                                                                                                             | Sub-carrier modulation is active until the return link header                                                                                                     |

| Address overflow during deterministic arbitration                      | Sub-carrier modulation OSC / 4                                                                                                                                                                                   | Sub-carrier is active if the arbitration was<br>started and the arbitration pointer (one bit<br>before the contents is backscattered) is<br>outside the memory    |

| Parameter                                                                  | Description                                                                   | Comment                                                                                                 |  |

|----------------------------------------------------------------------------|-------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|--|

| Group management                                                           | System supports several group<br>commands incluiding<br>=<br>≤<br>≥ decisions | The following commands are able to consider group command results                                       |  |

| Collision arbitration                                                      | Deterministic modified binary tree<br>Aloha                                   | All support non-unique data structures;<br>Deterministic procedures can point to<br>any memory location |  |

| Collision management                                                       | Deterministic: full duplex<br>communication<br>Aloha: slot based              | Single selection of a procedure or a mixture is possible                                                |  |

| Slots for Aloha                                                            | 32 Main slots +<br>Deterministic sub-slots                                    |                                                                                                         |  |

| Collision arbitration<br>linearity (deterministic)                         | >> 2 <sup>1286</sup>                                                          |                                                                                                         |  |

| Maximum tag inventory<br>capability                                        |                                                                               | The deterministic-based algorithm is not limited                                                        |  |

| Maximum size of the<br>memory                                              | 1344 bits                                                                     |                                                                                                         |  |

| Memory addressing                                                          | Blocks of 32 bits<br>Pages of 128 bits                                        |                                                                                                         |  |

| Protection against<br>overprogramming                                      | Lock bit                                                                      | One lock bit per page located within the page itself                                                    |  |

| Tag identifier (Tag_ID)     Default: 96 bits       Maximum size: 1270 bits |                                                                               | The memory size is limited only by the max. ID size                                                     |  |

| Table 1-3. | Anticollision and Memory Parameters |

|------------|-------------------------------------|

|            | , and onlot and memory r drameters  |

# 1.2 Abbreviations

| 2PSK         | 2-state phase-shift keying                                                 |

|--------------|----------------------------------------------------------------------------|

| AFI          | Application family identifier                                              |

| Ant          | Antenna (pad)                                                              |

| ASK          | Amplitude shift keying                                                     |

| Clk          | Clock                                                                      |

| CRC          | Cyclic redundancy check                                                    |

| CW           | Continuous wave                                                            |

| DSF          | Data storage format                                                        |

| DSFID        | Data storage format identifier                                             |

| EEPROM       | Electrically erasable programmable memory                                  |

| EOF          | End of frame                                                               |

| EOT          | End of transmission                                                        |

| ESD          | Electrostatic discharge                                                    |

| Forward link | Reader to tag communication, to transport the command and the parameters   |

| GND          | Ground (potential on-chip)                                                 |

| ID           | Identifier                                                                 |

| ID_s         | Identified and silent (internal status information of the tag)             |

| I/O          | Input and output (pad)                                                     |

| HBM          | Human body model (ESD characteristic)                                      |

| LSB          | Least significant bit                                                      |

| MHz          | Megahertz                                                                  |

| MSB          | Most significant bit                                                       |

| NRZ          | No return to zero                                                          |

| NRZI         | No return to zero inverted                                                 |

| PR-ASK       | Phase reversal–Amplitude-shift keying                                      |

|              | The phase of the carrier is switched by $180^\circ$ to generate a boundary |

|              | signal for a symbol                                                        |

| Pre          | Pre_select (status information)                                            |

| PIE          | Pulse interval encoding                                                    |

| Return link  | The time after the tag has received a command and its parameters           |

| RF           | Radio frequency                                                            |

| RFID         | Radio frequency identification device                                      |

| RFU          | Reserved for further use                                                   |

| RTF          | Reader talks first                                                         |

| Trigger      | Trigger signalling                                                         |

| TTF          | Tag talks first                                                            |

| VDD          | Supply voltage (on-chip)                                                   |

# 2. Overview

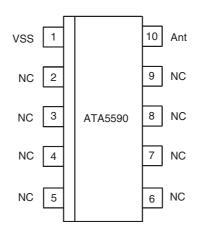

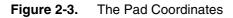

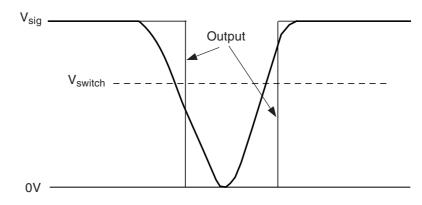

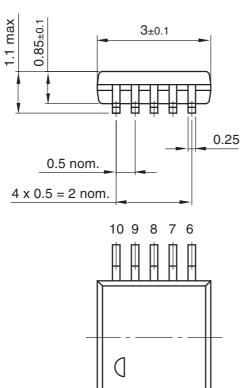

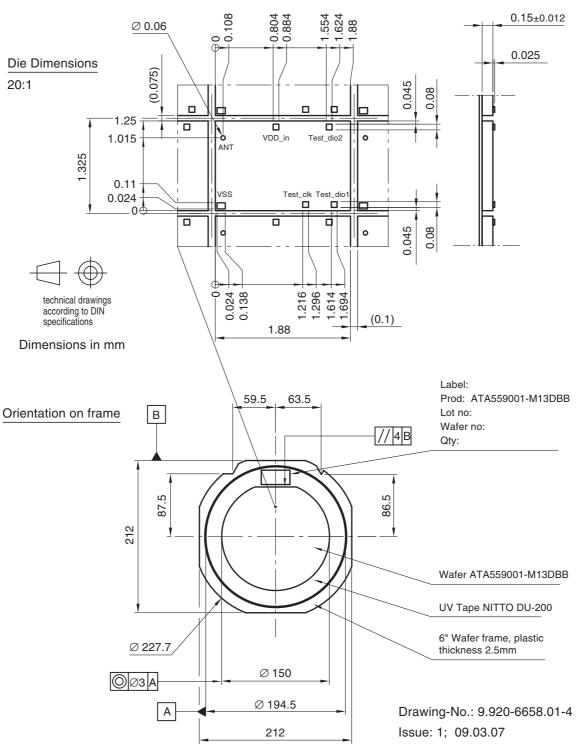

# 2.1 Pinning

### Table 2-1.Pin Description

| Pin | Symbol | Function      |  |

|-----|--------|---------------|--|

| 1   | VSS    | Antenna_gnd   |  |

| 2   | NC     | Not connected |  |

| 3   | NC     | Not connected |  |

| 4   | NC     | Not connected |  |

| 5   | NC     | Not connected |  |

| 6   | NC     | Not connected |  |

| 7   | NC     | Not connected |  |

| 8   | NC     | Not connected |  |

| 9   | NC     | Not connected |  |

| 10  | Ant    | Antenna       |  |

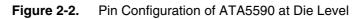

| Pad       | Function      | Physical Construction | Comment                     |

|-----------|---------------|-----------------------|-----------------------------|

| Ant       | Antenna       | RF in                 | Diameter of opening 60 µm   |

| VSS       | Antenna_gnd   | RF Ground             |                             |

| VDD_in    | Test pad      | Output                | VDD after the rectifier     |

| Test_Clk  | Test clock in | Input                 | Notch input                 |

| Test_dio1 | Test pad      | In/out open drain     | For control and observation |

| Test_dio2 | Test pad      | In/out open drain     | For control and observation |

ATA5590

## 2.2 Main Parameters of the Die

| Table 2-3. | Main Frequenc | v-independent | Parameters at 25°C |

|------------|---------------|---------------|--------------------|

|            | mannininini   | ,             |                    |

| Parameter                                            | Condition/Comment                              | Typical         | Value |

|------------------------------------------------------|------------------------------------------------|-----------------|-------|

| Shortest PIE time                                    | To define a "0"                                | 8 + notch time  | μs    |

| Longest PIE time                                     | To define EOF                                  | 88 + notch time | ms    |

| Storage time of status bits:<br>pre_select, ID, ID_s | Without external power, 1.3V, 25°C             | 8               | s     |

| Programming time <sup>1</sup>                        | 2V VDD, 32 bits<br>t = 0 for this special case | 9 + t           | ms    |

Note: 1. Timing calculation is based on an oscillator frequency of 420 kHz. The timing value of t depends on the RF field strength, and will be dynamically adjusted.

| Parameter                       | Condition/Comment                     | Typical                   | Value |  |

|---------------------------------|---------------------------------------|---------------------------|-------|--|

| Input impedance <sup>1, 2</sup> | 11 µW RF power,<br>modulation state 1 | 6.7 – j216 (6970 – j216)  | Ω     |  |

|                                 | Modulation state 2                    | 6.1 – j202 (6695 – j202)  | Ω     |  |

| Input impedance <sup>1, 2</sup> | 25 μW RF power,<br>programming        | 12.3 – j217 (3840 – j217) | Ω     |  |

Notes: 1. For packaged parts, the imaginary part decreases as a function of the housing and bonding technology.

2. Impedance is calculated as a series impedance of R and C. Values in () are the values for an equivalent parallel circuit.

| Table 2-5.         Main Frequency-dependent Parameters at 25°C and 9 |

|----------------------------------------------------------------------|

|----------------------------------------------------------------------|

| Parameter                       | Condition/Comment                        | Typical                   | Value |

|---------------------------------|------------------------------------------|---------------------------|-------|

| Input impedance <sup>1, 2</sup> | 12 μW RF power, no<br>modulation state 1 | 6.9 – j205 (6097 – j205)  | Ω     |

|                                 | Modulation state 2                       | 6.4 – j191 (5706 – j191)  | Ω     |

| Input impedance <sup>1, 2</sup> | 26 μW RF power,<br>programming           | 10.3 – j191 (3552 – j191) | Ω     |

Notes: 1. For packaged parts, the imaginary part decreases as a function of the housing and bonding technology.

2. Impedance is calculated as a series impedance of R and C. Values in () are the values for an equivalent parallel circuit.

| Parameter                       | Condition/Comment                     | Typical                  | Value |  |  |

|---------------------------------|---------------------------------------|--------------------------|-------|--|--|

| Input impedance <sup>1, 2</sup> | 13 μW RF power,<br>modulation state 1 | 6.6 – j196 (5827 – j196) | Ω     |  |  |

|                                 | Modulation state 2                    | 6.1 – j182 (5436 – j182) | Ω     |  |  |

| Input impedance <sup>1, 2</sup> | 27 μW RF power,<br>programming        | 9.7 – j182 (3424 – j182) | Ω     |  |  |

**Table 2-6.**Main Frequency-dependent Parameters at 25°C and 960 MHz

Notes: 1. For packaged parts, the imaginary part decreases as a function of the housing and bonding technology.

2. Impedance is calculated as a series impedance of R and C. Values in () are the values for an equivalent parallel circuit.

**Table 2-7.**Main Frequency-dependent Parameters at 25°C and 2450 MHz

| Parameter                       | Conditions/Comment                    | Typical     | Value |

|---------------------------------|---------------------------------------|-------------|-------|

| Input impedance <sup>1, 2</sup> | 49 µW RF power,<br>modulation state 1 | 4.0 – j84.8 | Ω     |

|                                 | Modulation state 2                    | 3.8 – j79.2 | Ω     |

| Input impedance <sup>1, 2</sup> | 85 μW RF power,<br>programming        | 4.6 – j85   | Ω     |

Notes: 1. For packaged parts, the imaginary part decreases as a function of the housing and bonding technology.

2. Impedance is calculated as a series impedance of R and C. Values in () are the values for an equivalent parallel circuit.

## 2.3 Functional Changes and New Features Relative to ATA5590 Version 1

| Function Level                                                   | Short Description                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |  |

|------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Modulation coding<br>FM0                                         | The modulation now changes at each bit boundary.                                                                                                                                                                                                                                     |  |  |  |  |  |  |  |

| Selected access<br>mode during<br>deterministic<br>anticollision | If the tag is selected by a group select command which was sent before an anticollision command, the anticollision command will now based on this selection. The read and program commands which follow will not; they wil be based only on the selection of the arbitration result. |  |  |  |  |  |  |  |

| Test pads' behavior                                              | Both I/O pads are now usable in both directions.                                                                                                                                                                                                                                     |  |  |  |  |  |  |  |

Table 2-8.

ATA5590 Version 1 Errata Fixed in this Version

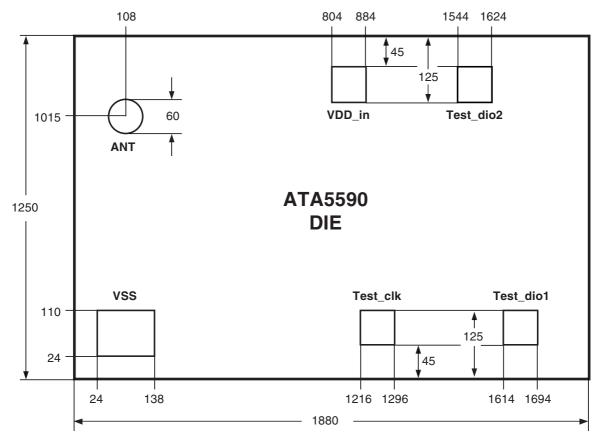

# 3. Memory

ATA5590 is a wireless data carrier IC with a UHF carrier and backscatter-based link mechanism. Data is stored in an EEPROM, and the content is under the control of manufacturers and the end user.

ATA5590 contains an EEPROM to store a Tag\_ID, system-related information, and user-controllable data. The memory access is controlled by commands transmitted by the reader. Additionally, the manufacturer area is controlled by a security mechanism which is destroyed after sawing.

The memory itself is split in 2 parts:

- The user memory (1 Kbit)

- The control memory (320 bits) containing the Tag\_ID and other sequences such as AFI, DSFID, etc.

ATA5590 does not protect data against reading but does protect against overwriting. To protect data against reading, the user should use encryption. For decryption, the user could use, for example, the user-controlled system information page (control memory) to store a pointer to an external device or memory to retrieve the key and the information regarding the algorithm used over a secure connection.

The memory is organized in pages of 128 bits. Each page is organized in blocks of 32 bits. For programming, each block must be programmed separately. The page is protected against overwriting by a lock bit which is located at the MSB position (bit 31 of page 3). Therefore, the lock bit should be set in an additional step or as the last command during the programming of a page.

The system memory supports:

- A Tag\_ID page, which can also be related to an object to which the tag is attached

- A user system-information page

- Two manufacturer system-information blocks

### 3.1 Tag\_ID Page

Some short commands address the Tag\_ID page automatically. In the default configuration, the Tag\_ID is used to create a link between the tag and, for example, an item. Nevertheless, the user is free to store such an ID at other locations of the memory as well. The following description applies to the default configuration.

The Tag\_ID and the type of the ID construction shall be programmed before using the tag in the application. During programming, it can be locked against over-programming. After locking, the Tag\_ID is a fixed value. Nevertheless, it is also possible to program virgin tags one by one out of a bulk arrangement by using the separation ability of the anticollision procedure.

The length of the ID depends on the type (structure definition) of the ID. By default, a 96-bit field is reserved (ID page) plus an 8-bit value to define the structure of the ID (DSFID).

The Tag\_ID is located in the system memory area, and can be addressed directly (control memory page address 0) or via the symbolic address 0h.

If more than 96 bits are needed, the user is free to store the rest of the structure in the user memory, because deterministic anticollision and group-selection routines are able to include the neighbor pages of the ID page (user memory) in the arbitration frame.

#### 3.1.1 **AFI** Identifier

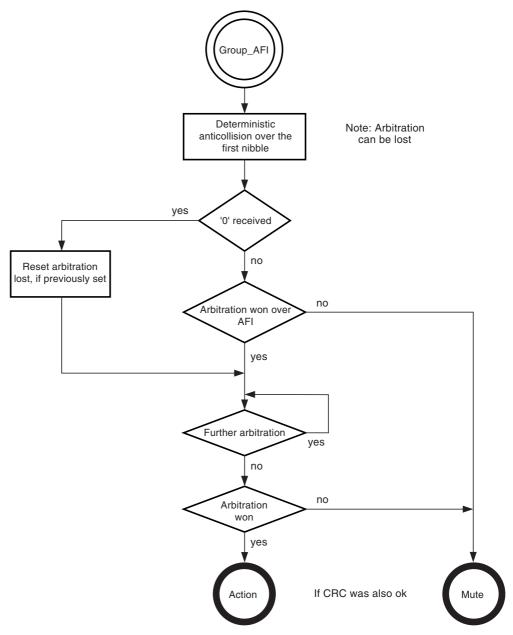

The Application Family Identifier (AFI) supports a common group-selection mechanism. It is an 8-bit value. The structure and the function are described in ISO 18000-6, and based on ISO/IEC 15962.

The AFI frame shall be used as a low-level hierarchical selection mechanism to separate RF tags. ATA5590 supports this mechanism as a first group-selection mechanism, including a joker mechanism. Therefore, the reader can select a tag using this special family structure code. The joker mechanism is based on the value 00h. If this code is received by the tag, it is selected automatically.

#### **DSF** Information 3.1.2

The data storage format is defined within an 8-bit value. The structure is defined in ISO/IEC 15962 section 7.2.5.

| Bit 7  | Bit 6  | Bit 5 | Bit 4 | Bit 3 | Bit 2       | Bit 1 | Bit 0 |

|--------|--------|-------|-------|-------|-------------|-------|-------|

| Access | method | RFU   |       |       | Data format |       |       |

Storage Schema of the DSF Information

Numbering of the access method is defined in ISO/IEC 15961, section 7.1.2.4. The data structure describes a method, whether or not there is a directory structure on-chip, or how the data is organized.

The first 13 values for the data format are described in ISO/IEC 15961, section 7.1.2.5. The DSFID is a special output of this common definition, describing only the Tag ID structure.

The DSFID information links the data format on a one-to-one basis with the AFI structure, which enables higher-level and lower-level selection processes.

#### 3.1.3 DSFID

ATA5590 supports a DSF mechanism according to ISO/IEC 15962 and ISO/IEC 15961 to define the structure of the ID (DSFID). The 8-bit value is stored by default in the lower byte of the upper block of the Tag\_ID page.

#### 3.1.4 Default Storage Scheme for the Tag ID Page

Table 3-1.

Different Tag\_ID structures are supported by ATA5590. These structures can be defined by the DSFID information. Arbitration, non-unique and private structures are also supported.

ATA5590 supports anticollision procedures which are based on this Tag\_ID, whereas the default anticollision procedure starts with the DSFID information.

The Tag\_ID is stored in a 128-bit page of the control memory at page address 00h. It can also be addressed by a symbolic addressing mechanism (symbolic address 0h). The MSB of the Tag\_ID is located at the MSByte of block 2. In some cases, it contains the header information of the Tag ID.

The Tag\_ID, the AFI, and the DSFID values have to be set via the system provider or in cooperation with the label or IC manufacturer, and can be protected by a lock bit. The default structure of the ID page is shown in Table 3-2 on page 14:

|           | 2010101000000000 |         | ]=      |                   |

|-----------|------------------|---------|---------|-------------------|

| Block/Bit | 31:24            | 23:16   | 15:8    | 7:0               |

| 3         | Administration   | 7:0 RFU | 7:0 AFI | 7:0 DSFID         |

| 2         | Upper byte of ID |         |         |                   |

| 1         |                  |         |         |                   |

| 0         |                  |         |         | Lowest byte of ID |

Table 3-2.

Default Construction of the Tag\_ID Page

For private structures or for structures of closed data systems, the structure can be changed. It is also possible to use other sizes for the ID.

Notes: 1. When using Aloha commands, only this ID page is supported.

- 2. Deterministic-arbitration commands can point to any memory address. Also, it is possible to support an expanded size of the ID for arbitration

- 3. In the case of large ID values (for example, license plate applications), it is recommended to start the ID within the ID page. The other values are stored then in the user memory (page address 7, 6, 5, etc.), because the addressing mechanism during deterministic arbitration is based on an auto-increment function. Then, only the lock bit function of each page must be considered.

The administration byte is defined as:

| Table 3-3. | Recommended Construction of the Administration Byte of the Tag_ID Page |

|------------|------------------------------------------------------------------------|

|            |                                                                        |

| Bit 7           | Bit 6   | Bit 5     | Bit 4     | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-----------------|---------|-----------|-----------|-------|-------|-------|-------|

| Lock_ID<br>page | Private | DSFID_nAC | DSFID_ISO | AFI   | DSFID | LID   | CRC   |

- Lock\_ID page: Locks the whole page. No change of the page is possible after setting this bit to 1.

- Private: If set to "1", custom structure and flags will be used. If set to "0", the flags defined here will be used.

- DSFID\_nAC: If set to "1", DSFID information is stored at byte 0 of block 3. If set to "0", the Allocation Class information is stored at byte 0 of block 3.

- DSFID\_ISO: If set to "1", the DSFID coding structure is not in line with ISO15962 regulations (only 00 to 0B are currently defined by ISO)

- DSFID: Indicates if the DSFID information is stored in the Tag\_ID page. The contents are stored at byte 0 or byte 2, depending on DSFID\_nAC.

- AFI: Indicates that the AFI is stored in the Tag\_ID page. The construction of AFI corresponds with ISO 18000-6 FDIS

- LID: Indicates that a Tag\_ID has a size longer than 96 bits. The other bits are stored in page 7,6, etc. of the user memory, as required.

- CRC: Indicates that a CRC value is supported. The CRC value can be stored after the administration part (byte 2) if the location is not used for storing the DSFID value.

- Notes: 1. The anticollision and group-selection procedures of ATA5590 support AFI as well as the ID\_type (DSFID) information.

- 2. The tag manufacturer can program and lock the Tag\_ID page.

- 3. The lock bit function is hard-wired in ATA5590. All of the other bits are recommended.

#### 3.1.5 ID\_type Coding

The ID\_type is an 8-bit value defined according to the DSF information in ISO/IEC 15962. Therefore, the ID is defined by the lower 5 bits of the DSFID information. The codes for the different ID structures are defined as:

- 00 to 0B reserved by ISO/IEC 15961 (see section 7.1.2.5 of ISO/IEC 15961 and 7.2 of ISO/IEC 15962)

- 0C to 1F: RFU

Code 00 enables migration paths for private or closed-system numbering systems.

Note: As the anticollision commands support an auto decrement function of the memory address, the ID can have more then 96 bits. The other information may then be located at address 1F, 1E, etc.

#### 3.2 User System Information Block

The second page of the system memory is available for private system management indication. This page is in the system memory at page address 1. The symbolic address is 1h.

After sawing, the MSByte of the upper block can be programmed using an OTP mechanism. The MSB is the lock bit of the three lower blocks of the page. The MSBlock of this page will not be locked against programming (except the upper byte of this block, which is OTP). Therefore, the user can use the three lower bytes of the upper block for changeable data such as the packaging level information, a CRC, etc.

To protect the three lower blocks of the page against over programming, the lock bit must be set. The user system information can be read out by read32c or read128c commands, or by using the get\_system informational command.

#### 3.3 Manufacturer System Information

Information regarding the functionality of the chip and other reference data is stored in the manufacturer system information blocks.

This information is stored in the system memory area of the EEPROM, and can be read out directly by a get\_system command. Programming is possible during wafer test. After sawing, only the 8th byte can be reprogrammed by using a sequence of arbitration and prognbyte commands. The physical page address is 2h, as is the symbolic address.

The system information is split in 8 bytes (64 bits)

#### 3.3.1 Manufacturer System Information Byte 8

|            | Manufact   | ulei System  | mormation | , our byte |       |       |       |  |  |  |

|------------|------------|--------------|-----------|------------|-------|-------|-------|--|--|--|

| Bit 7      | Bit 6      | Bit 5        | Bit 4     | Bit 3      | Bit 2 | Bit 1 | Bit 0 |  |  |  |

| Trigger_en | Trigger(0) | igger(0) RFU |           | RFU        | RFU   | RFU   | RFU   |  |  |  |

| 0          | 0          | 0            | 0         | 0          | 0     | 0     | 0     |  |  |  |

Table 3-4.

Manufacturer System Information, 8th Byte

Trigger\_en = "1" indicates that the trigger function is selected

Trigger(0) defines the frequency of the sub-carrier:

The definition of the following bytes is reserved for further use, based on the described protocol mechanism.

# 3.4 Memory Organization Summary

#### Table 3-5.System Memory

ProgNbyte (tag must be selected)

Blocked after sawing

Can be locked (when locked it can't be reprogrammed) - OTP mechanism

1: List of Application Family Identifiers are defined in ISO/IEC 15961.

| Logical | Block   |                         |    | By | te3 |    |    |    |    | By | te2 |    |    |    |    | By | te1 |    |    |    |    |    |    |   |   | By | te0 |   |   |   |   |   |   |

|---------|---------|-------------------------|----|----|-----|----|----|----|----|----|-----|----|----|----|----|----|-----|----|----|----|----|----|----|---|---|----|-----|---|---|---|---|---|---|

| Address | Address | 31                      | 30 | 29 | 28  | 27 | 26 | 25 | 24 | 23 | 22  | 21 | 20 | 19 | 18 | 17 | 16  | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7  | 6   | 5 | 4 | 3 | 2 | 1 | 0 |

| 7       | 3       | Lock Bit <sup>(1)</sup> |    |    |     |    |    |    |    |    |     |    |    |    |    |    |     |    |    |    |    |    |    |   |   |    |     |   |   |   |   |   |   |

| '       | 2       |                         |    |    |     |    |    |    |    |    |     |    |    |    |    |    |     |    |    |    |    |    |    |   |   |    |     |   |   |   |   |   |   |

|         | 1       |                         |    |    |     |    |    |    |    |    |     |    |    |    |    |    |     |    |    |    |    |    |    |   |   |    |     |   |   |   |   |   |   |

|         | 0       |                         |    |    |     |    |    |    |    |    |     |    |    |    |    |    |     |    |    |    |    |    |    |   |   |    |     |   |   |   |   |   |   |

| :       | :       | :                       | :  | :  | :   | :  | •• | :  | :  | :  | :   | •• | :  | •• | :  |    | :   | :  | :  | :  | :  | :  | :  | : | : | :  | :   | : | : | : |   | • | : |

| :       | :       | :                       | :  | :  | :   | :  | :  | :  | :  | :  | :   | :  | :  | :  | :  | :  | :   | :  | :  | :  | :  | :  | :  | : | : | :  | :   | : | : | : | : | : | : |

| :       | :       | :                       | :  | :  | :   | :  | :  | :  | :  | :  | :   | :  | :  | :  | :  | :  | :   | :  | :  | :  | :  | :  | :  | : | : | :  | :   | : | : | : | : | : | : |

| 0       | 3       | Lock Bit <sup>(1)</sup> |    |    |     |    |    |    |    |    |     |    |    |    |    |    |     |    |    |    |    |    |    |   |   |    |     |   |   |   |   |   |   |

| 0       | 2       |                         |    |    |     |    |    |    |    |    |     |    |    |    |    |    |     |    |    |    |    |    |    |   |   |    |     |   |   |   |   |   |   |

|         | 1       |                         |    |    |     |    |    |    |    |    |     |    |    |    |    |    |     |    |    |    |    |    |    |   |   |    |     |   |   |   |   |   |   |

|         | 0       |                         | l  |    |     |    |    |    |    |    |     |    |    |    |    |    |     |    |    |    |    |    |    |   |   |    |     |   |   |   |   |   | 1 |

#### Table 3-6.User Memory

Notes: 1. Page can be locked (when locked it can't be reprogrammed) - OTP mechanism

2. Whole page usable for expanded ID

# 4. Communication

#### 4.1 Default Operation Basics

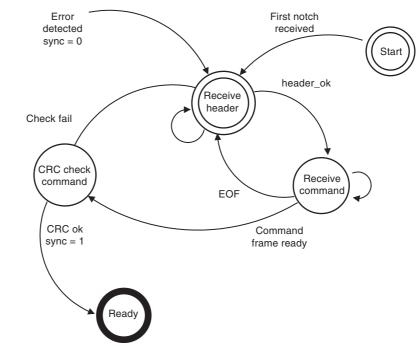

Communication between the reader and the tag is based on the reader talks first (RTF) principle. When a tag receives modulation ticks from the reader, the stream is checked by several mechanisms. If they all result in a valid status, the tag becomes synchronous to the stream and the tag is ready to communicate.

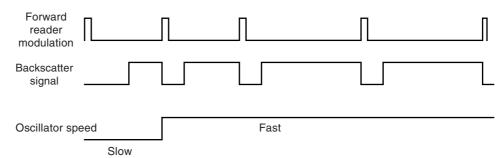

Communication always starts with a forward message (reader to tag). ATA5590 supports full duplex communication during the forward link after becoming synchronous to the reader. Therefore, the reader can check on-the-fly whether the tags have received the right values.

The tag answers by backscattering a message back to the reader (return link).

The messages are covered by a CRC.

The backscatter mechanism is based on 2PSK modulation, which means that the tag changes the imaginary part of the input impedance as a function of the data stream and the selected encoding. This modulation type offers maximum robustness against noise combined with minimum influence on supply voltage generation.

### 4.2 Status Registers

ATA5590 has two status registers.

- Status1, which represents the selection status and

- Status2, which represents the communication status

Status1 contains the result of the arbitration procedure (Aloha-based or anticollision and group-selection status), and status2 contains the communication results.

#### 4.2.1 Status1 Register

Status1 is a special register; the contents of the register are persistent for 8 seconds at 25°C after RF power is lost. The register will be refreshed by the POR mechanism.

- Note: The persistence time is a function of the temperature. A common attribute of CMOS technologies is that the leakage current changes by a factor of 2 for every 9°C. The leakage current is the main influence on the storage time.

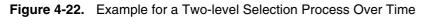

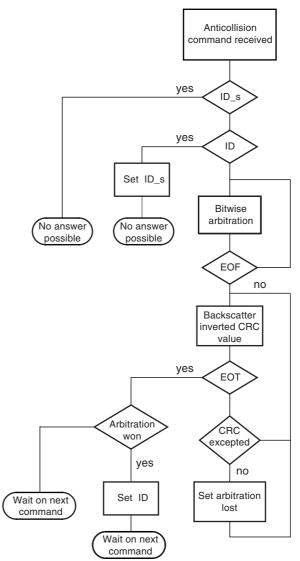

- Pre\_select: A "1" indicates that the tag was previously selected by a group-selection command. It can be set and reset by group-selection commands. A reset is also possible using the reset command.

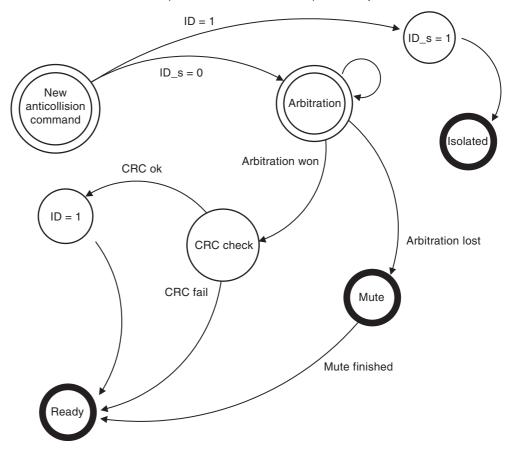

- ID: A "1" indicates that the tag has currently won a deterministic arbitration via deterministic anticollision commands. It can be reset by group-selection commands (group condition is no longer true) or by the reset command.

- ID\_s: A "1" indicates that the tag, which has won arbitration before, will now be silent because it was detected, or, in the case of a deterministic selection procedure, it has received a new anticollision command. The bit can be reset by the reset command.

| GENERALLY  | Indicates or stores the selection status of the IC (ALOHA, deterministic anticollision or group select)                                                                                                                                                                                  |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pre-select | "1b" indicates that the reader was detected before by a group select command                                                                                                                                                                                                             |

| ID         | "1b" indicates that the tag has won the arbitration (deterministic anticollision)                                                                                                                                                                                                        |

| ID_s       | "1b" indicates that the tag which has won the arbitration and detected before,<br>shall now be silent (during deterministic- and ALOHA arbitration the flag is set<br>after detecting and by following of a new arbitration command - ALOHA- or a<br>deterministic arbitration command). |

Table 4-1. Contents of Status 1 Register

| Table 4-2. | Typical Storage Time of a Logical "1" in Status1 Register at Different |

|------------|------------------------------------------------------------------------|

|            | Temperatures                                                           |

| Temperature      | –47°C | –29°C | –11°C | 7°C | 25°C | 43°C | 61°C |

|------------------|-------|-------|-------|-----|------|------|------|

| Storage time [s] | 2048  | 512   | 128   | 32  | 8    | 2    | 0.5  |

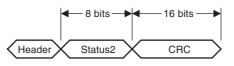

#### 4.2.2 Status2 Register

Register status2 gives an overview of the status of communication. It is part of a backscattered message during program commands and read commands.

|       | Contents of Statusz Tregister |                  |  |

|-------|-------------------------------|------------------|--|

| Index | Read Commands                 | Program Commands |  |

| 7     | Pre_select                    | Pre_select       |  |

| 6     | ID                            | ID               |  |

| 5     | Lock protected                | Lock protected   |  |

| 4     | 1                             | 1                |  |

| 3     | Bit length not ok             | Program_ok       |  |

| 2     | Aloha                         | Aloha            |  |

| 1     | CRC wrong                     | CRC wrong        |  |

| 0     | 0                             | 0                |  |

Table 4-3. Contents of Status2 Register

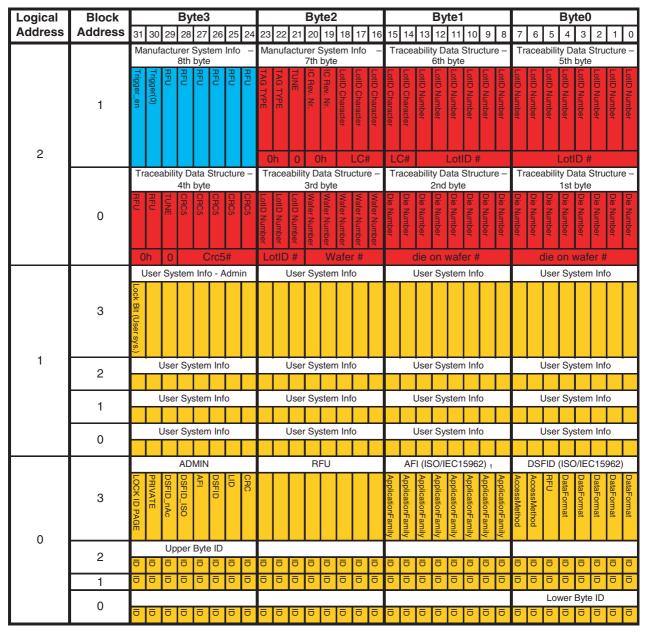

#### 4.3 Frame Concept

Communication is based on the following frames:

- A header frame for timing adjustments

- A data frame to transport the data (Forward: reader to tag, and Return: tag to reader)

- In the forward direction, the data frame contains the command, the parameters, the CRC value, and, if necessary, the address vectors and the data for programming. The length of the data frame depends on the command and the selected addressing mechanism.

- In the return link, the data frame contains the required data, if possible, and, as a function of the command, the status2 information. A CRC is also part of the data frame.

- An end of transmission (EOT) frame to mark the end of the forward or return link.

These three frames are elementary parts of the forward and return links.

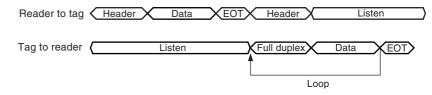

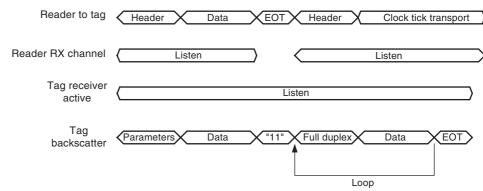

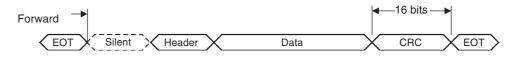

Figure 4-1. Frame Ordering During the Default Communication

During the header it is possible to work in full duplex mode to optimize the link. Under control of the reader, the return link can operate in a loop until the reader sends an EOT frame.

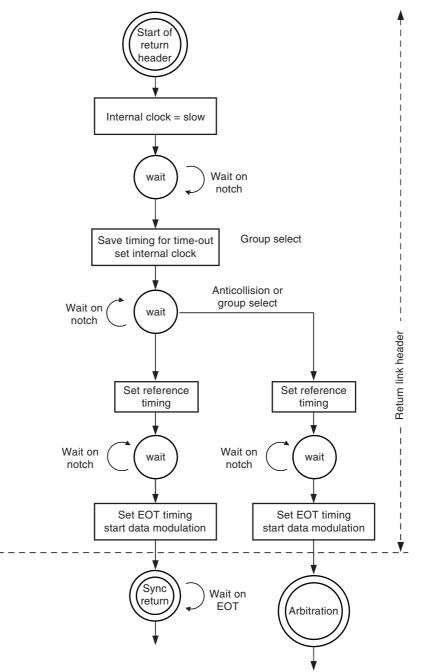

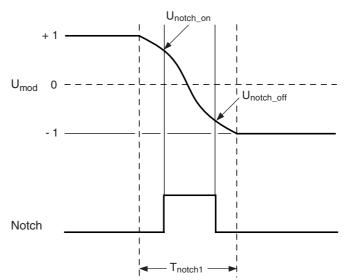

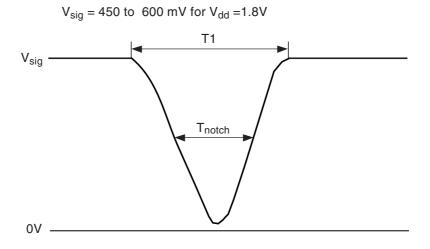

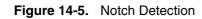

The return link is arranged as a synchronous link. The reader transmits the boundaries of the bit by sending notches to achieve higher SNR. The maximum time for this bit as well as the spectrum of the backscattered bit shall be adjusted by the reader by tuning the return link header.

### 4.4 OSI1 Layer Concept

To enable communication in even the worst environments, ATA5590 supports the following options:

- The reader transmits clock ticks to the tags in the RF field. The clock tick receiver circuit tolerates ticks generated by PR-ASK or ASK (m > 0.8) mechanisms. PR-ASK combines high SNR, a good power transport mechanism, and a lower frequency spectrum compared to ASK ticks. Therefore, PR-ASK guarantees robustness against noise and blocking from other RF sources, as well as reliability.

- The time for a notch is not part of any timing calculation, enabling power savings and guaranteeing flexibility with regards to different spectrum requirements.

- The forward coding is based on a Pulse Interval Encoding (PIE) style.

- The forward baud rate and the rules to distinguish between "0", "1", and EOF symbols are transmitted during a header section by the reader.

- The return link operates synchronously. As the reader can control the speed and the modulation ticks of the synchronous return link, this link type has a higher SNR than an asynchronous link.

- The return link is based on a 2PSK modulation, which means that the imaginary part of the input impedance changes mainly. This has a positive influence on supply voltage for the tag IC, and also on the tolerated noise floor of the system.

- The timings of the return link are based on a header section in the beginning of the return link. During this header section, the reader transports timing information, which is used in the return link.

- ATA5590 supports static and dynamic modulation coding techniques to backscatter data. The dynamic coding style is able to shift the modulation edges to get a better spectrum or to shift the edge away from the synchronization tick.

- Static modulation coding: NRZI coding

- Dynamic modulation coding:

- Soft NRZI coding

- FM0 coding

- 3phase1 coding

The baud rate is fully controlled by the reader by adjusting the timings in the header section of the forward and the return header. The baud rate can be adjusted between 5 Kbits/s and 60 Kbits/s.

ATA5590 operates in the following communication modes

- Half duplex communication

- During the forward link if the synchronous condition is not valid

- Full duplex communication

- During the forward link if the synchronous condition is valid

- During the deterministic-arbitration process

- During the return link

# ATA5590

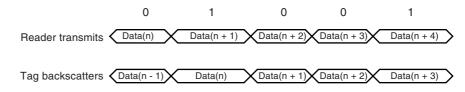

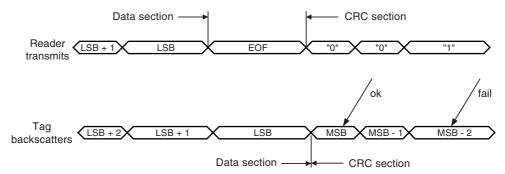

Figure 4-2. Default Full Duplex Communication Principle

During the data section of the forward stream, the tag backscatters the decoded value of the received data back to the reader.

This enables the reader to control the quality of the link. It also enables the reader to check if the tag has received the right message. If the reader detects an error, it stops the transmission directly by sending the stop code or by remaining silent for a specific time (programmable watchdog). Then the tag becomes asynchronous to the link, and the reader can tune the link by tuning the transport parameters via the header section of the forward link.

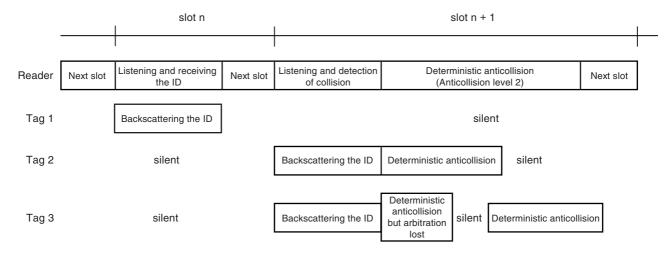

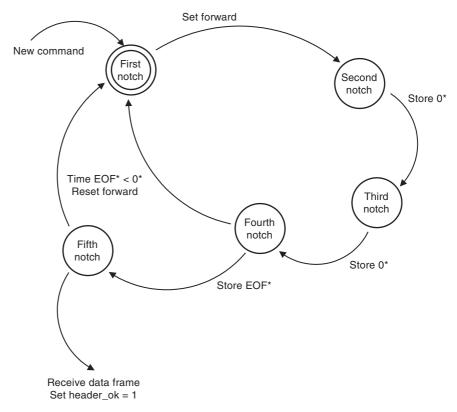

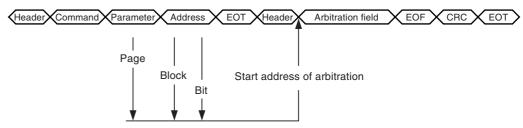

#### Figure 4-3. Communication During Deterministic Arbitration

| Reader to tag          | Header Data     | EOT L        | isten and arbitration | EOT        |

|------------------------|-----------------|--------------|-----------------------|------------|

| Reader RX<br>channel   | Listen          |              |                       |            |

| Tag receiver<br>active | (               | Listen       | Arbit                 | ration won |

| Tag<br>backscatter     | Parameters Data | a Y"11" Head | der Data              | ¥"11"      |

|                        |                 |              | Arbitration los       | \$t        |

| Tag<br>backscatter     | Parameters Data | Heade        | er Data               | Mute       |

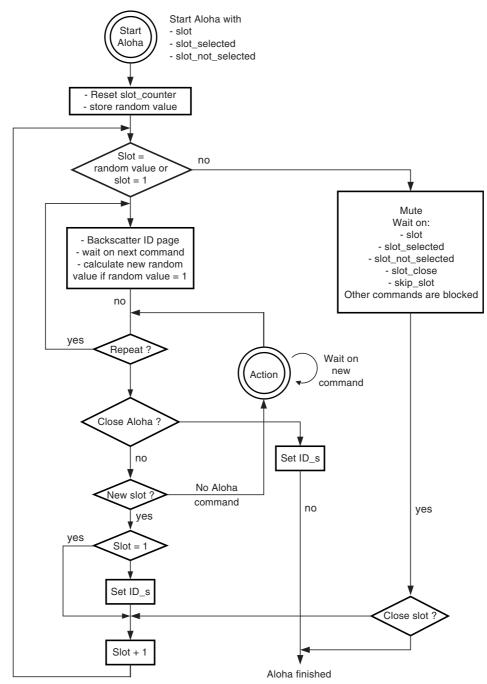

During the deterministic anticollision procedure, full duplex communication is used.

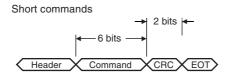

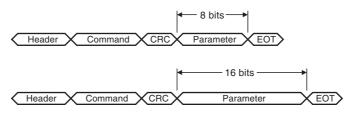

## 4.5 Default Frames of the Forward Link Stream

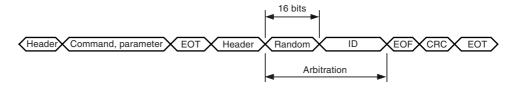

The basic protocol contains the following elements:

- A forward header to define the boundaries of the data encoding transmitted by the reader.

- A data frame containing the command and its CRC, data setting parameters, address information, and data for programming. The encoding of the data frame is based on the boundary setting made during the header.

- Short commands are based only on the 6-bit command code and its 2-bit CRC.

- Temporary commands are short commands which are not stored in an on-chip command register. They are only used to repeat the former command if possible.

- Long commands consist, at least, of the command frame, its CRC, and the parameter field.

- A 16-bit CRC frame if a long command was transmitted. In the case of deterministic anticollision commands, the 16-bit CRC field is not part of the forward link because the CRC result is the start value for the CRC of the return link.

- An EOT frame which is based on 2 EOF (end of file) symbols.

#### Figure 4-4. Default Forward Frames

Long commands (read and program)

Long commands (deterministic anticollision)

Note: The speed of the deterministic anticollision procedure can be increased by combining the long commands with the short repeat\_arb command.

# ATA5590

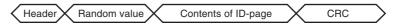

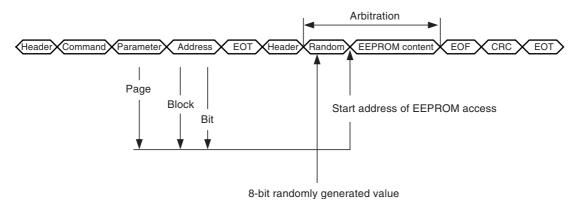

### 4.6 Use of the Random Number Generator

ATA5590 supports several commands where the execution or the return link contents is based on random effects. Therefore, a random number generator is implemented on the ATA5590 chip.

Random effects are used

- To calculate a 5-bit slot number and/or an 8-bit random value, which is backscattered during the Aloha-based arbitration

- To calculate a 4-bit slot number for the answering mechanism triggered by the wake-up commands

- To calculate an 8-bit random value for the deterministic arbitration, if required

Therefore, ATA5590 supports non-unique data structures for each arbitration procedure.

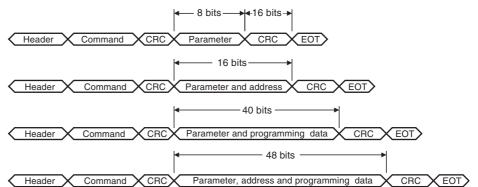

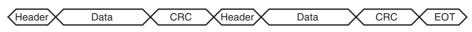

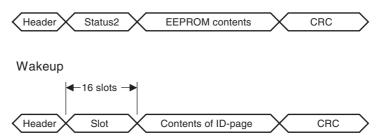

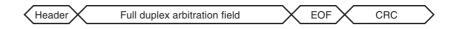

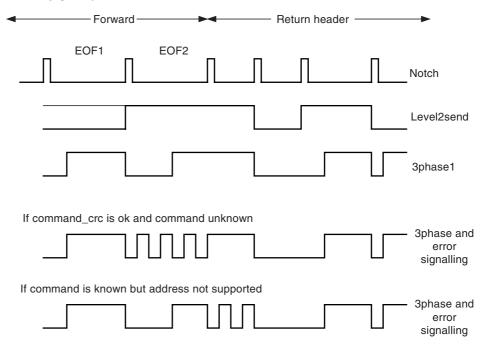

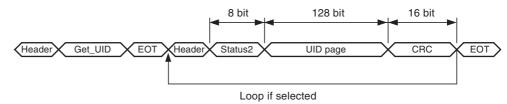

### 4.7 Default Frames of the Return Link Stream

The return link is built by

- A return link header to get reference symbols, adjust modulation timing, adjust timing windows for anticollision, and set the EOF timing

- A data frame which can be based (depending on the command) on

- The 8-bit status2 register

- The 8-bit random value (arbitration commands)

- The 16-bit slot information (wake-up commands)

- The contents of the EEPROM (n bits)

- A 16-bit CRC frame (the bit count can be adjusted by the reader, if required)

- An EOT frame

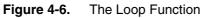

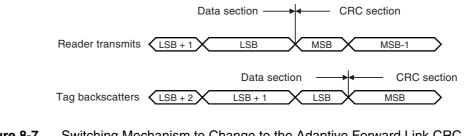

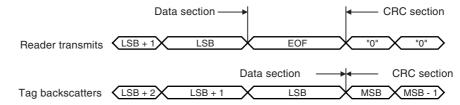

During the synchronous return link, it is possible to operate in a loop mode which increases the SNR for the whole communication. There is no need for new command sequences.

Synchronous operation mode enables some adaptive mechanisms such as quasi-continuous bit rates or adaptive CRC.

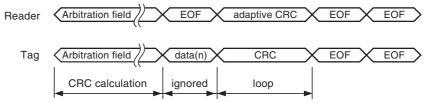

#### Figure 4-5. Return Link Frame

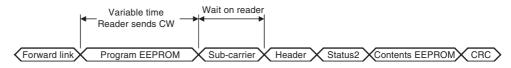

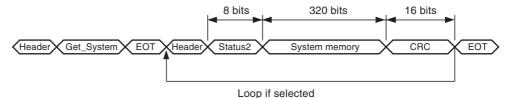

During programming the return link contains a silent time, during which the reader does not send any messages to the tag. During this time the reader sends a continuous wave (CW). The length of the silent time depends on the field strength of the received RF signal.

For all other commands, the silent time is zero.

The length of the data frame depends on the command and the reader. The reader is able to close the return link by transmitting an EOT frame.

If the reader wants to increase the robustness of the link, the reader may restart the message by sending a new header instead of the EOT frame.

The construction of the data frame itself depends on the command. It can contain

- A status (status2) message (read, program commands, error)

- An 8-bit random field (wake-up, and some arbitration commands)

- A data field which is the output of the EEPROM

- A 16-bit CRC field

#### Figure 4-7. Construction of the Default Return Link in Detail

Error message

#### Read/program

Deterministic arbitration

Aloha

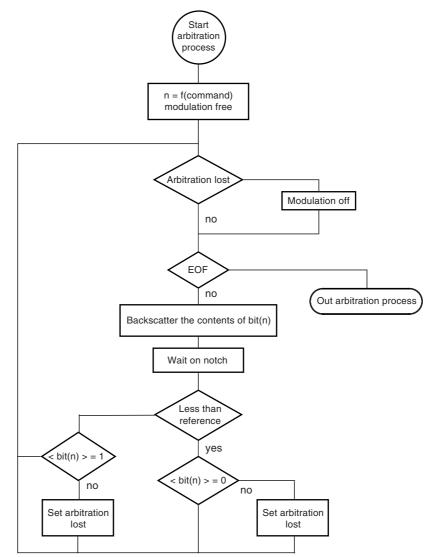

During deterministic arbitration (deterministic selection procedures), the data field works in full duplex mode. The tag backscatters the value of its EEPROM value bit by bit, and the reader transfers (as a reaction to this information) a bit by bit decision. This decision then controls the next bit operation of the tag. If the reader has transmitted a decision which corresponds with the content of the selected bit of the EEPROM, the tag backscatters the next bit. Otherwise it is silent until the next deterministic-arbitration command.

If the reader then marks the end of the arbitration by sending an EOT sequence,

- The reader knows the (item level linked) ID or a part of it for the selected tag, and

- The reader is free to send new commands to this selected tag. The tags which are not selected listen, but are not active

During programming, the tag is silent. When the programming is finished or if the tag has detected an error, the tag backscatters a sub-carrier, until the reader transmits a header to start the return link.

- Notes: 1. Due to 2PSK backscatter modulation, ATA5590 is able to detect a notch until it backscatters a message.

- 2. When the RF field strength is low, the programming time is longer. The programming time depends on the field strength of the received RF signal.

#### Figure 4-8. Frame Construction During Programming

The time required to program the EEPROM is a function of the RF field strength, and the status of the block to which the address pointer points. If the block is locked against over programming, the tag starts immediately to backscatter a sub-carrier back.

# 4.8 **Principal Communication Flow**

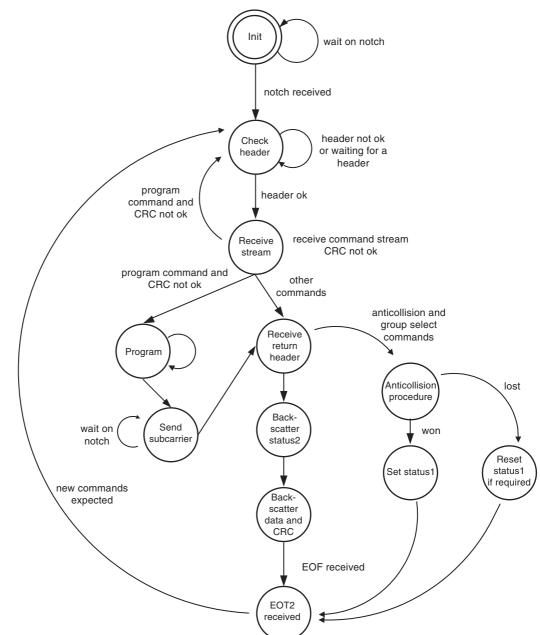

Figure 4-9.

Principal Flow of the Communication

Figure 4-9 shows the flows for read, program, and deterministic anticollision commands. ATA5590 also supports other types of commands; in which case the flow can be slightly different.

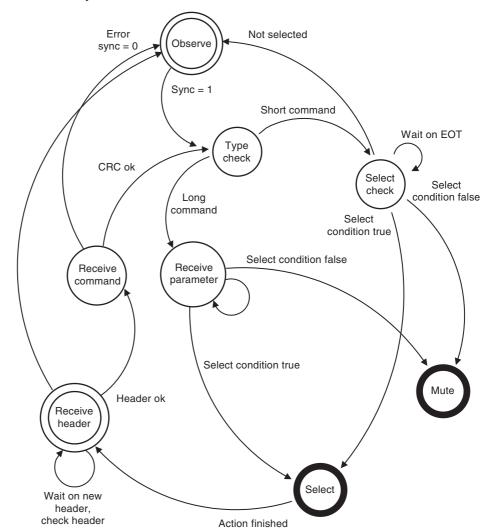

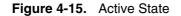

To be able to control such flows, ATA5590 implements several state machines, which work in parallel or sequentially.

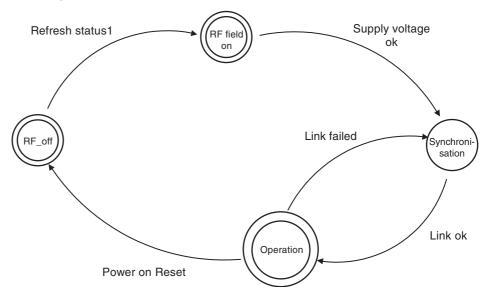

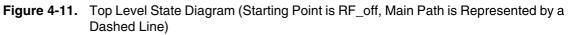

### 4.9 States of the Tag

To minimize communication problems, the tag has to first become synchronous to the RF stream transmitted by a reader; after this the tag is ready for communication.

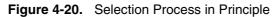

Additionally, most of the operations are controlled by select conditions which are fully controlled by the reader, and are based on the status1 register contents.

#### Figure 4-10. Operation Flow

To enable this operation flow, the tag must be in one of the following top view states:

- RF field off

- RF field on

- Start state

- Observe state

- Ready state

- Active state

- Mute state

- Isolated state

#### 4.9.1 Starting Point: RF Field Off

As long as the tag is not powered, the tag is not able to operate.

The tag stores the information of the status1 register (pre\_select, ID, ID\_s) for a defined time without any external power (8 seconds at 25°C). The storage time is a function of the temperature. The storage time increases as the temperature drops. As the time depends on temperature, the contents of the register after this time is no longer defined.

Note: Only a logical "1" can be stored over time. If the register was "0", the contents is still defined after this persistence time; it will still be "0".

#### 4.9.2 RF Field On

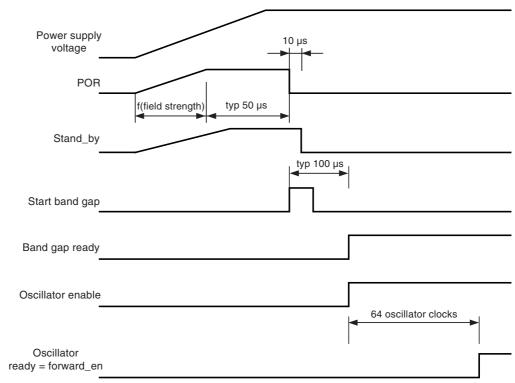

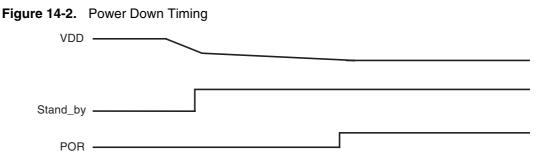

When a tag enters an RF field, and the RF field strength (in respect to the resonant frequency of the antenna and its bandwidth) is above a certain value, the reset circuit generates a power-on reset (POR). After POR the on-chip oscillator is switched on.

If the RF field has reached a minimum power level, and the power-on reset is finished, the tag IC changes to the start state.

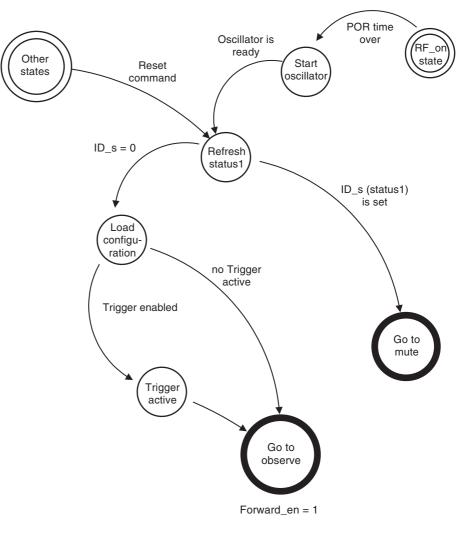

#### 4.9.3 Start State

After POR, the circuit generates a refresh procedure for the status1 register (pre\_select, ID, ID\_s). Then it reads the configuration of the chip out of memory. Based on the configuration, it enables or disables the trigger function. The detection of a first modulation tick (RSSI circuit) is enabled after configuration.

After enabling the RSSI circuit, the tag waits for a first modulation dip. The trigger function stops after receiving a first modulation dip.

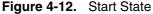

#### 4.9.4 Observe State

To enable further actions, such as programming, the chip must be synchronous to the reader. Therefore, some checks have to be made over the stream which is received by the tag (timing of the forward header must be valid, the command must be known, and the first command CRC must be valid).

If these checks pass, the tag is synchronous to the modulated stream transmitted by the reader.

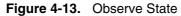

#### 4.9.5 Ready State

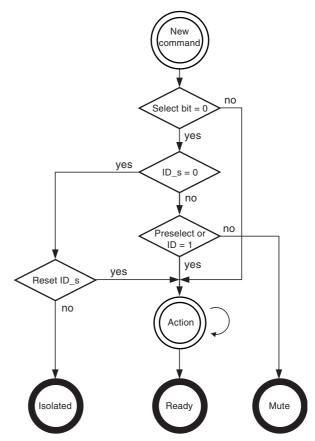

In this state, the enabling conditions are checked. If the conditions are true, the tag changes to the selected state, otherwise to the mute state.

Figure 4-14. Ready State

#### 4.9.6 Active State

If necessary, the rest of the forward frame (address, data, or both) must be received. Then the tag can carry out the required operation (program, arbitration, or starting the return link).

#### 4.9.7 Mute State

The mute state is quite similar to the select state. However, as the select condition was false, the tag remains silent, and no operation (such as programming, arbitration or backscattering data) is done.

#### 4.9.8 Isolate State

The isolate state is also quite similar to the select state. The tag is isolated and waits on a power-on reset or a reset command, which will reset the ID\_s flag of the status1 register.

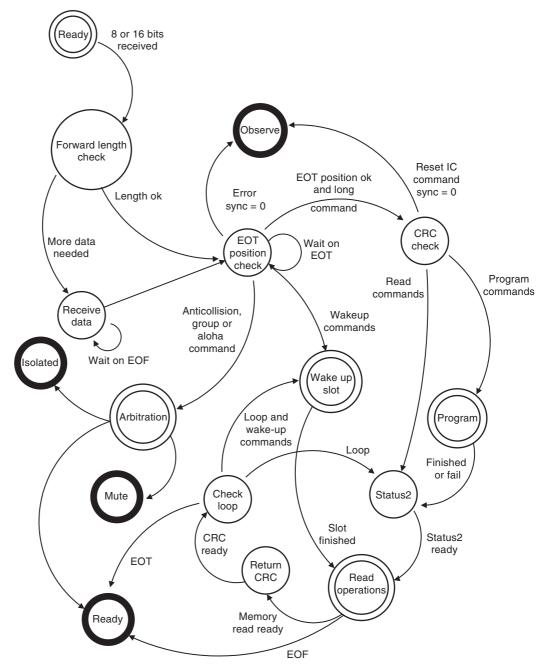

#### 4.10 Summary of the Supported Arbitration Possibilities

If more than one tag is in the RF field and ready to operate, the system must support an arbitration procedure to be able to select one or a group of tags for further operations (for example, program or read), or to identify them.

The system must also be able to isolate a tag after an operation to be sure that this tag does not disturb the following communications. The flag which indicates this silent mode is ID\_s, one of the status1 register bits.

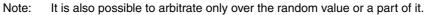

Furthermore, in some applications it is helpful to get a first impression of whether there are several tags in the field or not. Therefore, the ATA5590 supports wake-up commands. After the return link header, the protocol supports a slot zone containing 16 bits. A tag modulates one of the 16 slots (the select mechanism for the slot is based on a random value calculated on-chip).

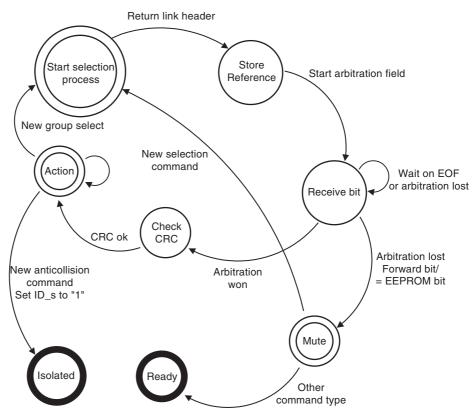

ATA5590 supports two kinds of principal arbitration mechanisms:

- A deterministic-arbitration procedure which is able to handle hierarchical processes, and

- An Aloha-based procedure which is time-slot-based. The size (time and bit count) of such a slot is under control of the reader

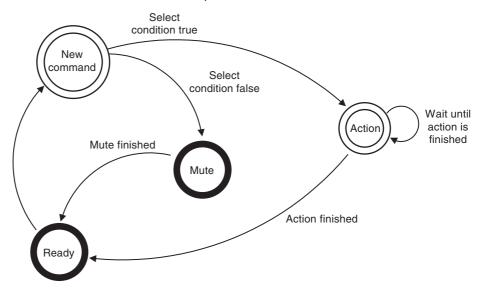

ATA5590 can mix these procedures, yielding a two-level arbitration mechanism.

The deterministic procedure can be combined with a random approach to be able to handle data structures in the arbitration process which are not unique. This random approach is not Aloha-based, and, therefore, strongly deterministic.

The result of each procedure is stored in the register status1.

Aloha-based procedures also influence the ID\_s flag, and are able to consider the flags pre\_select and ID.

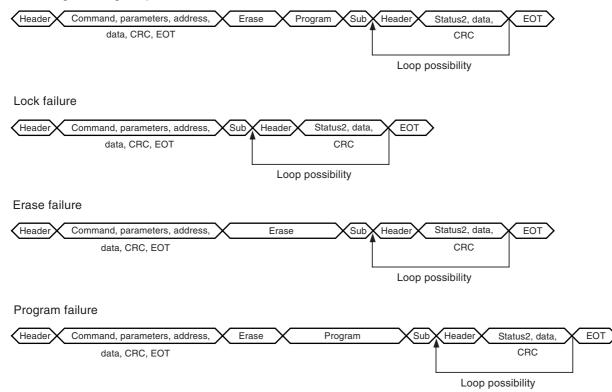

Aloha is controlled by slot commands. The close slot command finishes the Aloha arbitration.

After POR, the tag starts to calculate a random value. The calculation continues as long as the tag receives power.

After a tag has received a slot command

- It takes a random number from the random number generator, which points to a slot number between 0 and 31 on-chip.

- After receiving the start command, all tags backscatter their information back to the reader during the first slot, independently from the chosen random value. If the tag's calculated random value matches the first slot number, it calculates a new one during this slot. Therefore, the tags in Aloha are always able to backscatter their information two times.

- If this random slot value matches the slot number which is under control of the reader, the tag becomes active, enabling the reader to communicate with the tag. If the slot value doesn't match, the tag does not answer to any command (mute state). The other operations (changing status1 or programming) are also blocked.

If the tag receives a new slot command (without the slot repeat, skip slot or slot close command) the tag calculates if it is now to be active or not.

If the reader detects a collision, it can skip the slot directly by sending a skip slot command. Then the formerly selected tags calculate a new slot value, rather than set the ID\_s flag.

To increase the number of slots, the ATA5590 is able to change to a second arbitration level which is based on deterministic procedures. Therefore, the ATA5590 is able to operate with second level slots without changing the slot number.

The information which is backscattered by the tags is an 8-bit random number, and the contents of the ID page. Therefore, if the tags are virgin or if the ID is not unique, the reader is able to identify a collision between tags by observing the random number.

Most of the commands supported by the ATA5590 consider the status1 contents. Therefore, it is possible to communicate with a group, with a single tag, or with all tags in the RF field. Some commands (short commands) directly consider the status1 flags. Long commands support a selection condition inside their streams; if the select condition flag is set to "1", all tags with the pre\_select or the ID flag set, and the ID\_s flag not set, are addressed. For all commands except the reset command, if the selection flag is set to "0", all tags in the RF field with ID\_s flag set to "0" are selected.

- Note: If the pre\_select flag is set, and then the reader sends a deterministic anticollision command combined with the select condition

- The anticollision procedure is based only on the pre\_select flag

- The subsequent commands (read or program), combined with the select condition, are based only on the result of the arbitration procedure. The pre\_select status bit no longer influences the commands

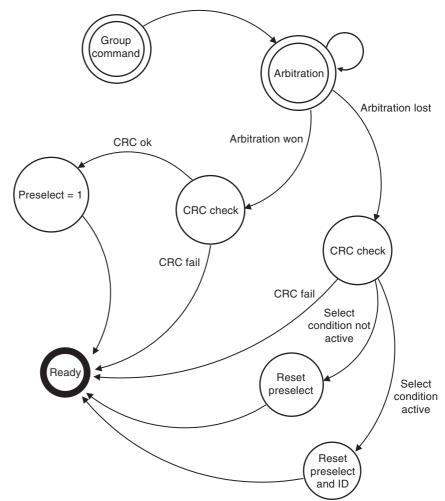

ATA5590 supports several commands to solve collision problems deterministically. ATA5590 distinguishes between deterministic anticollision and the group-selection mechanism. The deterministic anticollision procedure of ATA5590 is based on a flexible binary tree algorithm which is characterized by:

- A modified deterministic binary tree algorithm, and

- Full duplex communication

During arbitration, the procedure is based on full duplex communication to enable closed loop arbitration. Therefore, during arbitration the reader is able to control and to change priority bit-by-bit.

If the CRC condition is true, at the end of each arbitration procedure a group of tags or a single tag is automatically selected. The contents of the memory which was part of the arbitration is also known. There is no need for an additional acknowledgement to the tag. The reader can communicate immediately with the selected tags.

The deterministic anticollision procedure which is implemented in ATA5590 does not expect unique data structures, such as an ID, for arbitration, because ATA5590 also supports random frames during arbitration.

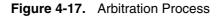

The arbitration process itself is also based on a PIE style. The reader transmits a reference time first (return link header section). Then, during arbitration, the tag compares the time between two bits with this reference. If the bit time is less than the reference time, a "0" was transmitted, otherwise a "1". This value will be compared against the internal bit value of the EEPROM. If the values are the same, the tag has won the arbitration for this bit, and is enabled for further steps. If not, the tag has lost the arbitration, and waits on a new arbitration command. Up to this time, the tag is silent, and not available for programming or reading.

The pre\_select flag of status1 can be set and reset by group-selection commands. Therefore, it is possible to select a group or a single tag with these command types. ATA5590 offers full duplex operation during group-selection commands.

The pre\_select flag can also be reset by the reset command.

ATA5590 supports several kinds of group-selection commands addressing the ID or the AFI and DSFID mechanism. Additionally, a pointer-based group-selection mechanism is supported. Decisions can be made based on =,  $\geq$ , and  $\leq$  comparisons.

After a group or a single tag is selected, the reader is immediately free to communicate with the tag(s).

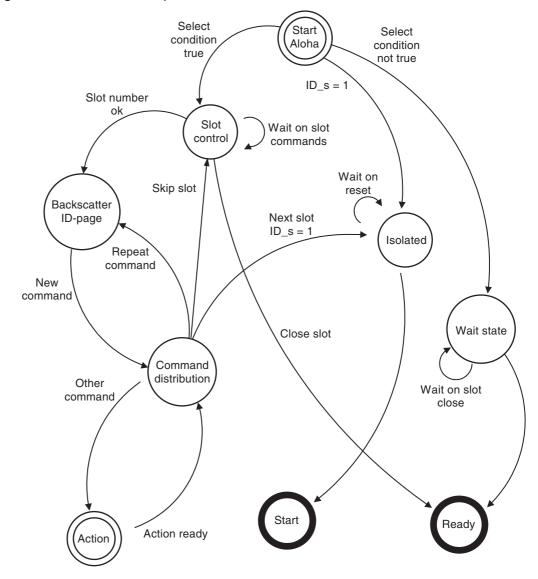

#### Figure 4-18. Pre\_select Flow

During the deterministic-arbitration procedure, ID and ID\_s flags can be set. The ID and ID\_s flags are based on full duplex communication results.

The ID flag is set to "1" if the tag wins an arbitration frame, and if the CRC is correct. The ID flag can be reset by a reset command, or, if the select flag is set, by a group-selection command (arbitration was lost)

**ATA5590**

Figure 4-19. ID and ID\_s Flow (Deterministic Arbitration) in Principle

Deterministic procedures are able to influence the pre\_select, the ID, and the ID\_s flags.

The default anticollision procedure is based principally on a Tag\_ID. The deterministic anticollision procedure itself is based on an adaptable binary search. The adaptation is fully controlled by the reader, and allows a priority change on the fly.

The deterministic anticollision is based principally on full duplex communication.

The IC stores the status of anticollision in 2 bits (ID and ID\_s) in the status1 register (8 seconds storage time without power at 25°C).

ATA5590 also supports variable pointer-based anticollision commands, and a command which considers a random value. These commands are able to address the whole system and user memory.

After a group or a single tag is selected, the reader is free to communicate with them immediately.

The length of the arbitration fields is under the control of the reader. After receiving an EOF symbol, the CRC section starts.

A combination of the long deterministic commands and the short repeat\_arb command is possible, which results in a faster arbitration.

### 4.11 Combination of Different Deterministic Selection Procedures

Anticollision and group-selection commands can be combined to achieve a hierarchical selection algorithm.

# 4.12 Combination of Aloha-based and Deterministic-based Selection Procedures

As ATA5590 supports Aloha and deterministic-based selection procedures, the user can mix them to implement a second selection level.

Figure 4-21. Flow to Implement a Second Selection Level in Aloha

# 4.13 Application-specific Selection Procedures

#### 4.13.1 Initialization of Virgin Tags Out of a Group of Tags

ATA5590 supports two possibilities for communication with virgin tags. During Aloha, the tags calculate a slot number which is independent from the memory contents. If only one tag back-scatters during a slot, this tag can be programmed.

In the case of deterministic procedures, the reader shall send a command which enables an arbitration over a random value. Based on this random value, the reader can isolate each tag.

After separation, the reader is able to program the tags with a unique number (Tag\_ID or item-linked information).

#### 4.13.2 One Tag is in the RF Field

Once the tag IC is ready for operation, the reader can send a first command to the tag to start communication.

#### 4.13.3 Several Tags are in the RF Field

If the situation is stable (the tags are not moving), the reader can send a wake-up command first to get an initial impression of how many tags are in the field.

Then the reader determines which kind of selection procedure it wants to use, or it can decide that there is a need first for a pre-selection.

Pre-selection can be based on an AFI mechanism or can be based on some portion of the memory contents. Each anticollision mechanism supports the feasibility of operating with or without pre-selection, as does each read or program command.

The reader is also free to chose to operate using anticollision commands, a combination of Aloha and deterministic procedures, or a combination of both.

- Notes: 1. The deterministic selection process supported by ATA5590 is able to address each bit position of the EEPROM during the arbitration process.

- 2. Deterministic arbitration is not limited by block or page borders of the EEPROM.

#### 4.13.4 Moving Tags in the Field

If there is a possibility of tags arriving in the field (because the tags are moving), then it is recommended to operate with pre-selection. At the end of the communication (with the selected tags), the reader can send a wake-up command to all tags not pre-selected to be sure that it has identified all tags in the RF field which can participate ( $ID_s = 0$ ).

# 5. Trigger Functionality

After each POR or global reset command, the start state becomes active. In this state, ATA5590 reads the trigger configuration out of the EEPROM. If the trigger function is enabled (trigger configuration(1)), the second bit is read out to configure the sub-carrier frequency.

Table 5-1.Trigger Configuration

| Trigger Configuration(1:0) | Function                         |

|----------------------------|----------------------------------|

| 00                         | Trigger not active               |

| 01                         | Trigger not active               |

| 10                         | Sub-carrier frequency is OSC / 4 |

| 11                         | Sub-carrier frequency is OSC / 8 |

The sub-carrier modulates the field as long as the tag does not receive a notch tick. After detection of the start of the forward stream, the trigger function is switched off.

The trigger function becomes active again after receiving a global reset command.

The trigger function can be controlled by a special programming sequence.

# 6. Commands

ATA5590 supports long and short commands.

# 6.1 Long Commands

| Command | Short Description | Comment                                                |

|---------|-------------------|--------------------------------------------------------|

| Reset   | •                 | Affects the whole circuit or just the status1 register |

#### Table 6-2. Group-selection Commands

| Command      | Short Description                                                 | Comment                          |

|--------------|-------------------------------------------------------------------|----------------------------------|

| Group_ID     | Group select targeting ID                                         | Affects only the pre_select flag |

| Group_AFI    | D_AFI Group select targeting AFI Affects only the pre_select flag |                                  |

| Group_p      | Group select supporting address and bit pointer                   | Affects only the pre_select flag |

| Group_p_leeq | Group select supporting address and bit pointer                   | Affects only the pre_select flag |

| Group_p_greq | Group select supporting address and bit pointer                   | Affects only the pre_select flag |

# Table 6-3. Full-duplex Anticollision Commands

| Command                    | Short Description                                                                      | Comment             |

|----------------------------|----------------------------------------------------------------------------------------|---------------------|

| Anticollision_ID           | Full-duplex anticollision command targeting ID                                         | Affects ID and ID_s |

| Anticollision_p            | Full duplex anticollision command, supporting address and bit pointer                  | Affects ID and ID_s |

| Anticollision_p<br>_random | Full duplex anticollision command, supporting address, bit pointer, and random methods | Affects ID and ID_s |

# Table 6-4.Read Commands

| Command  | Short Description     | Comment                    |

|----------|-----------------------|----------------------------|

| Read32   | Read 32 bits in loop  | Pointing to memory         |

| Read32c  | Read 32 bits in loop  | Pointing to control memory |

| Read128  | Read 128 bits in loop | Pointing to memory         |

| Read128c | Read 128 bits in loop | Pointing to control memory |

# Table 6-5.Program Commands

| Command       | Short Description                                                       | Comment                          |

|---------------|-------------------------------------------------------------------------|----------------------------------|

| Program4byte  | 32-bit programming at once                                              | Pointing to memory               |

| Program4bytec | 32-bit programming at once                                              | Pointing to control memory       |

| Programnbyte  | Up to 32-bit programming at once<br>A portion of 8 bits can be selected | 1 byte to 4 bytes are selectable |

# 6.2 Short Commands

| Table 6-6. | Short Read Commands |

|------------|---------------------|

|            |                     |

| Command     | Short Description                          | Comment                                 |

|-------------|--------------------------------------------|-----------------------------------------|

| Get_ID_page |                                            | Corresponds with read128c(0)            |

| GET_system  | Manufacturer system information to ID page | 8-bit status2 + 320-bit EEPROM contents |

| Command           | Short Description                                                                                                                                                              | Comment                                                                                                                                      |

|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|

| Wakeup_s          | Each selected tag answers in one of 16 slots,<br>and backscatters the ID plus 8-bit DSFID                                                                                      |                                                                                                                                              |