### **General Description**

The MAX9985 high-linearity, dual-channel downconversion mixer is designed to provide approximately 6dB gain, +28.5dBm of IIP3, and 10.5dB of noise figure (NF) ideal for diversity receiver applications. With a 700MHz to 1000MHz RF frequency range and a 570MHz to 865MHz LO frequency range, this mixer is ideal for lowside LO injection architectures. In addition, the broad frequency range makes the MAX9985 ideal for GSM 850/950, 2G/2.5G EDGE, WCDMA, cdma2000®, and iDEN® base-station applications.

The MAX9985 dual-channel downconverter achieves a high level of component integration. The MAX9985 integrates two double-balanced active mixer cores, two LO buffers, a dual-input LO selectable switch, and a pair of differential IF output amplifiers. In addition, integrated on-chip baluns at the RF and LO ports allow for singleended RF and single-ended LO inputs. The MAX9985 requires a typical OdBm LO drive. Supply current is adjustable up to 400mA.

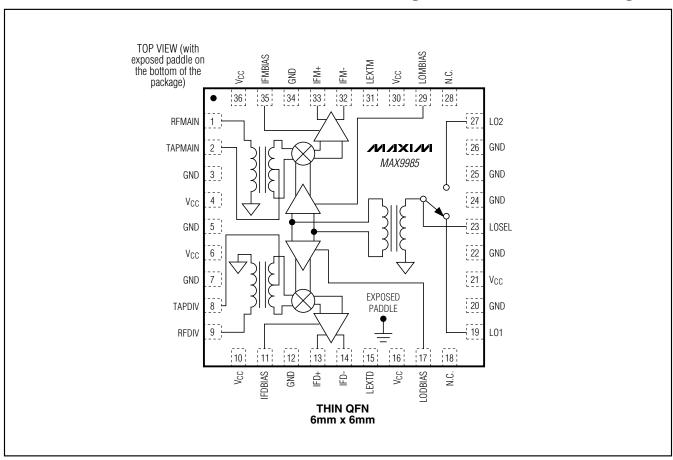

The MAX9985 is available in a 36-pin thin QFN package (6mm x 6mm) with an exposed paddle. Electrical performance is guaranteed over the extended temperature range, from  $T_C = -40^{\circ}C$  to  $+85^{\circ}C$ .

## **Applications**

850MHz WCDMA Base Stations

GSM 850/GSM 950, 2G/2.5G EDGE Base Stations

cdmaOne™ and cdma2000 Base Stations

iDEN Base Stations

Fixed Broadband Wireless Access

Wireless Local Loop

Private Mobile Radios

Military Systems

Digital and Spread-Spectrum Communication Systems

Microwave Links

cdma2000 is a registered trademark of Telecommunications Industry Association.

iDEN is a registered trademark of Motorola, Inc. cdmaOne is a trademark of CDMA Development Group.

#### **Features**

- ◆ 700MHz to 1000MHz RF Frequency Range

- ♦ 570MHz to 865MHz LO Frequency Range

- ♦ 50MHz to 250MHz IF Frequency Range

- ♦ 6dB Typical Conversion Gain

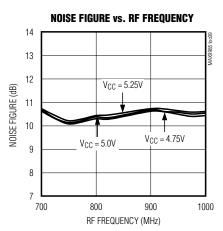

- ♦ 10.5dB Typical Noise Figure

- ♦ +28.5dBm Typical Input IP3

- ♦ +16.2dBm Typical Input 1dB Compression Point

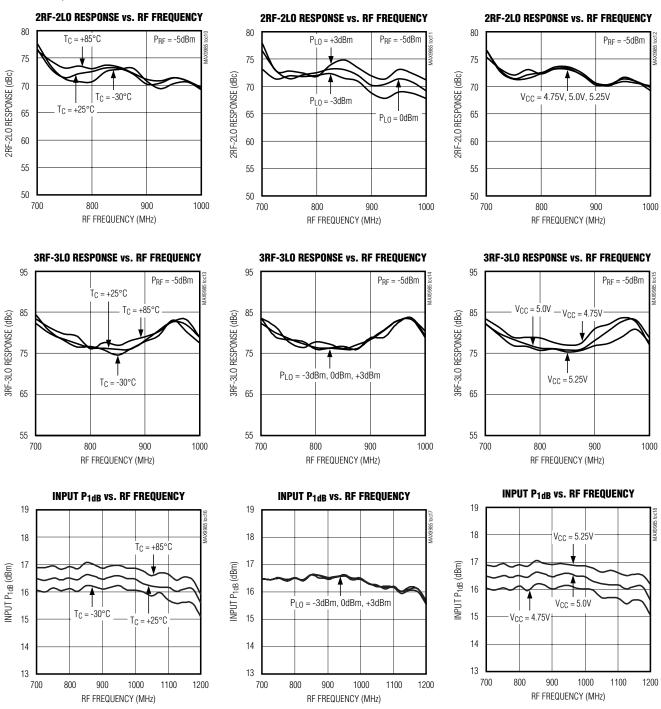

- ♦ 77dBc Typical 2RF-2LO Spurious Rejection at PRF = -10dBm

- **♦ Dual Channels Ideal for Diversity Receiver Applications**

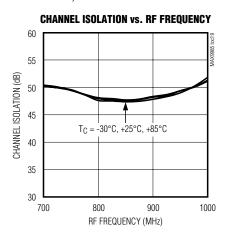

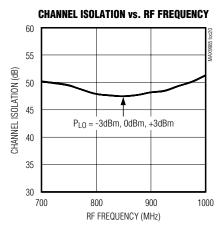

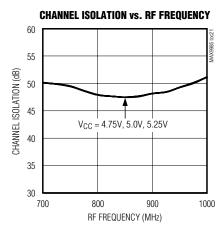

- **♦** 47dB Typical Channel-to-Channel Isolation

- ♦ -3dBm to +3dBm LO Drive

- ♦ Integrated LO Buffer

- ♦ Internal RF and LO Baluns for Single-Ended

- ♦ Built-In SPDT LO Switch with 43dB LO1-to-LO2 Isolation and 50ns Switching Time

- ♦ Pin-Compatible with MAX9995/MAX9995A 1700MHz to 2200MHz Mixers

- **♦ Lead-Free Package Available**

## **Ordering Information**

| PART         | TEMP RANGE     | PIN-PACKAGE                                        | PKG<br>CODE |

|--------------|----------------|----------------------------------------------------|-------------|

| MAX9985ETX   | -40°C to +85°C | 36 Thin QFN-EP*<br>(6mm x 6mm)                     | T3666-2     |

| MAX9985ETX-T | -40°C to +85°C | 36 Thin QFN-EP*<br>(6mm x 6mm),<br>T/R             | T3666-2     |

| MAX9985ETX+  | -40°C to +85°C | 36 Thin QFN-EP*<br>(6mm x 6mm),<br>lead free, bulk | T3666-2     |

| MAX9985ETX+T | -40°C to +85°C | 36 Thin QFN-EP*<br>(6mm x 6mm),<br>lead free, T/R  | T3666-2     |

<sup>\*</sup>EP = Exposed paddle.

T = Tape-and-reel package.

+Denotes lead-free and RoHS compliant.

Maxim Integrated Products 1

#### **ABSOLUTE MAXIMUM RATINGS**

| V <sub>CC</sub> to GND0.3V to +5.5V                            |

|----------------------------------------------------------------|

| LO1, LO2 to GND±0.3V                                           |

| Any Other Pins to GND0.3V to (V <sub>CC</sub> + 0.3V)          |

| RFMAIN, RFDIV, and LO_ Input Power+20dBm                       |

| RFMAIN, RFDIV Current (RF is DC shorted to GND through         |

| balun)50mA                                                     |

| Continuous Power Dissipation ( $T_C = +70^{\circ}C$ ) (Note A) |

| 36-Pin Thin QFN (derate 26mW/°C above +70°C)10.8W              |

| Operating Temperature Range40°C to +85°C                       |

| Maximum Junction Temperature Range | +150°C         |

|------------------------------------|----------------|

| θJA                                | +38°C/W        |

| θJC                                | 7.4°C/W        |

| Storage Temperature Range          | 65°C to +150°C |

| Lead Temperature (soldering, 10s)  | +300°C         |

**Note A:** T<sub>C</sub> is the temperature on the exposed paddle of the package.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### DC ELECTRICAL CHARACTERISTICS

(Using the *Typical Application Circuit*, no input RF or LO signals applied,  $V_{CC} = 4.75V$  to 5.25V,  $T_{C} = -40^{\circ}$ C to +85°C. Typical values are at  $V_{CC} = 5.0V$ ,  $T_{C} = +25^{\circ}$ C, unless otherwise noted.)

| PARAMETER                | SYMBOL                              | CONDITIONS                                                    | MIN  | TYP | MAX  | UNITS |

|--------------------------|-------------------------------------|---------------------------------------------------------------|------|-----|------|-------|

| Supply Voltage           | V <sub>CC</sub>                     |                                                               | 4.75 | 5   | 5.25 | V     |

| Supply Current           |                                     | Total supply current (see Table 1 for lower current settings) |      | 400 | 440  |       |

|                          | la-                                 | V <sub>CC</sub> (pin 16)                                      |      | 80  |      | A     |

|                          | Icc                                 | V <sub>CC</sub> (pin 30)                                      |      | 80  |      | mA    |

|                          |                                     | IFM+/IFM- (total of both)                                     |      | 105 |      |       |

|                          |                                     | IFD+/IFD- (total of both)                                     |      | 105 |      |       |

| LOSEL Input High Voltage | VIH                                 |                                                               | 2    |     |      | V     |

| LOSEL Input Low Voltage  | VIL                                 |                                                               |      |     | 0.8  | V     |

| LOSEL Input Current      | I <sub>IH</sub> and I <sub>IL</sub> |                                                               | -10  |     | +10  | μΑ    |

#### **AC ELECTRICAL CHARACTERISTICS**

(Using the Typical Application Circuit,  $V_{CC}=4.75V$  to 5.25V, RF and LO ports are driven from  $50\Omega$  sources,  $P_{LO}=-3dBm$  to +3dBm,  $P_{RF}=-5dBm$ ,  $f_{RF}=820MHz$  to 920MHz,  $f_{LO}=670MHz$  to 865MHz,  $f_{IF}=100MHz$ ,  $f_{RF}>f_{LO}$ ,  $T_{C}=-40^{\circ}C$  to  $+85^{\circ}C$ . Typical values are at  $V_{CC}=5.0V$ ,  $P_{RF}=-5dBm$ ,  $P_{LO}=0dBm$ ,  $f_{RF}=870MHz$ ,  $f_{LO}=770MHz$ ,  $f_{IF}=100MHz$ ,  $T_{C}=+25^{\circ}C$ , unless otherwise noted.) (Note 1)

| PARAMETER                       | SYMBOL | CONDITIONS                                                                                                                                                                             |     | TYP    | MAX  | UNITS |

|---------------------------------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|--------|------|-------|

| RF Frequency                    | fRF    | (Note 2)                                                                                                                                                                               | 700 |        | 1000 | MHz   |

| LO Frequency                    | fLO    | (Note 2)                                                                                                                                                                               | 570 |        | 865  | MHz   |

| IF Frequency                    | fıF    | IF matching components affect the IF frequency range (Note 2)                                                                                                                          | 50  |        | 250  | MHz   |

| LO Drive                        | PLO    | (Note 3)                                                                                                                                                                               | -3  |        | +3   | dBm   |

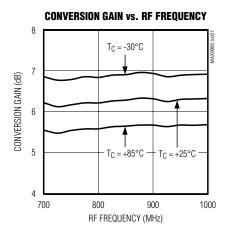

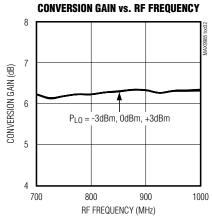

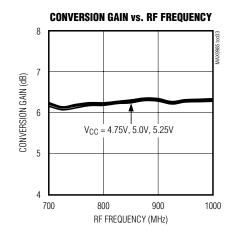

| Conversion Gain                 | GC     | (Note 6)                                                                                                                                                                               | 4.5 | 6      | 7.5  | dB    |

| Gain Variation over Temperature |        |                                                                                                                                                                                        |     | -0.012 |      | dB/°C |

| Conversion Gain Flatness        |        | Flatness over any one of three frequency bands: $f_{RF} = 824 \text{MHz to } 849 \text{MHz}$ $f_{RF} = 869 \text{MHz to } 894 \text{MHz}$ $f_{RF} = 880 \text{MHz to } 915 \text{MHz}$ |     | ±0.1   |      | dB    |

### **AC ELECTRICAL CHARACTERISTICS (continued)**

(Using the *Typical Application Circuit*,  $V_{CC}=4.75V$  to 5.25V, RF and LO ports are driven from  $50\Omega$  sources,  $P_{LO}=-3dBm$  to +3dBm,  $P_{RF}=-5dBm$ ,  $f_{RF}=820MHz$  to 920MHz,  $f_{LO}=670MHz$  to 865MHz,  $f_{IF}=100MHz$ ,  $f_{RF}>f_{LO}$ ,  $T_{C}=-40^{\circ}C$  to  $+85^{\circ}C$ . Typical values are at  $V_{CC}=5.0V$ ,  $P_{RF}=-5dBm$ ,  $P_{LO}=0dBm$ ,  $f_{RF}=870MHz$ ,  $f_{LO}=770MHz$ ,  $f_{IF}=100MHz$ ,  $T_{C}=+25^{\circ}C$ , unless otherwise noted.) (Note 1)

| PARAMETER                                                    | SYMBOL            | CONDITIONS                                                                                                                                                                        |                          | MIN  | TYP   | MAX | UNITS |

|--------------------------------------------------------------|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|------|-------|-----|-------|

| Noise Figure, Single Sideband                                | NF                | f <sub>IF</sub> = 190MHz, no blockers present (Note 3)                                                                                                                            |                          |      | 10.5  | 13  | dB    |

| Noise Figure under Blocking<br>Condition                     |                   | +11dBm blocker tone applied to RF port at 961MHz, f <sub>RF</sub> = 860MHz, f <sub>LO</sub> = 670MHz, f <sub>IFDESIRED</sub> = 190MHz, f <sub>BLOCKER</sub> = 291MHz (Notes 3, 4) |                          |      | 21    | 26  | dB    |

| Input Compression Point                                      | P <sub>1dB</sub>  |                                                                                                                                                                                   |                          |      | 16.2  |     | dBm   |

| Output Compression Point                                     | OP <sub>1dB</sub> |                                                                                                                                                                                   |                          | 18.5 | 21.2  |     | dBm   |

| Small-Signal Compression under                               |                   | P <sub>RF</sub> = -5dBm, f <sub>RF</sub> = 870MHz, f <sub>BLOCKER</sub>                                                                                                           | PBLOCKER = +8dBm         |      | 0.1   |     | dB    |

| Blocking Conditions                                          |                   | = 871MHz PBLOCKER = +11dBm                                                                                                                                                        |                          | 0.25 |       | ub. |       |

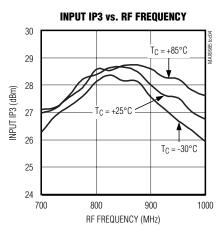

| Third-Order Input Intercept Point                            | IIP3              | $f_{RF1}$ - $f_{RF2}$ = 1MHz, $f_{II}$<br>$P_{RF}$ = -5dBm/tone                                                                                                                   | F = 100MHz,              |      | 28.5  |     | dBm   |

| Third-Order Input Intercept Point Variation over Temperature |                   |                                                                                                                                                                                   |                          |      | -0.01 |     | dB/°C |

| Third-Order Output Intercept<br>Point                        | OIP3              | P <sub>RF</sub> = -5dBm/tone, f <sub>IF</sub> = 100MHz,<br>f <sub>RF1</sub> -f <sub>RF2</sub> = 1MHz (Note 3)                                                                     |                          | 32.0 | 34.5  |     | dBm   |

| 2RF-2LO Spur                                                 | 2 x 2             | f <sub>RF</sub> = 870MHz, f <sub>LO</sub><br>= 770MHz, f <sub>SPUR</sub> =                                                                                                        | P <sub>RF</sub> = -10dBm | 63   | 77    |     | dBc   |

| 2111 -220 οραί                                               | 2 \ Z             | 820MHz (Note 3)                                                                                                                                                                   | P <sub>RF</sub> = -5dBm  | 58   | 72    |     | abc   |

| 3RF-3LO Spur                                                 | 3 x 3             | f <sub>RF</sub> = 870MHz, f <sub>LO</sub><br>= 770MHz, f <sub>SPUR</sub> =                                                                                                        | P <sub>RF</sub> = -10dBm | 70   | 85    |     | dBc   |

| onr-old opul                                                 | 3 X 3             | 803.3MHz (Note 3)                                                                                                                                                                 | P <sub>RF</sub> = -5dBm  | 60   | 75    |     | UDC   |

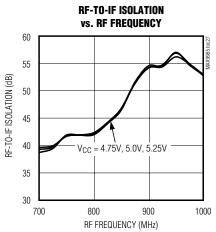

| LO1-to-LO2 Port Isolation                                    |                   | P <sub>LO1</sub> = +3dBm, P <sub>LO2</sub> = +3dBm,<br>f <sub>LO1</sub> -f <sub>LO2</sub> = 1MHz, P <sub>RF</sub> = -5dBm,<br>f <sub>IF</sub> = 100MHz (Notes 3, 5)               |                          | 39   | 43    |     | dB    |

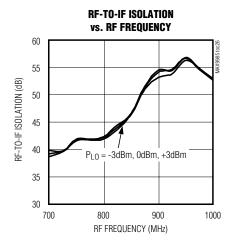

| Maximum LO Leakage at RF Port                                |                   |                                                                                                                                                                                   |                          |      | -40   | -30 | dBm   |

| Maximum 2LO Leakage at RF Port                               |                   |                                                                                                                                                                                   |                          |      | -45   | -20 | dBm   |

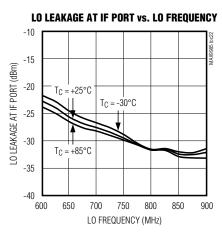

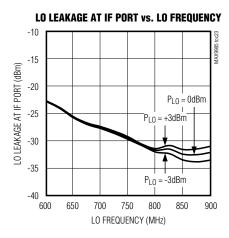

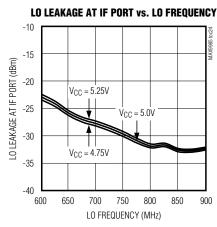

| Maximum LO Leakage at IF Port                                |                   |                                                                                                                                                                                   |                          |      | -30   | -20 | dBm   |

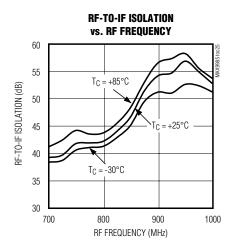

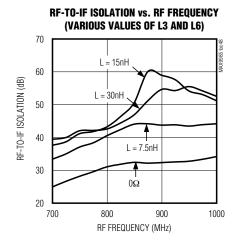

| Minimum RF-to-IF Isolation                                   |                   |                                                                                                                                                                                   |                          | 30   | 45    |     | dB    |

| Minimum Channel-to-Channel Isolation                         |                   | $P_{RF}$ = -10dBm, RFMAIN (RFDIV) power measured at IFDIV (IFMAIN), relative to IFMAIN (IFDIV), all unused ports terminated to $50\Omega$                                         |                          | 40   | 47    |     | dB    |

#### **AC ELECTRICAL CHARACTERISTICS (continued)**

(Using the *Typical Application Circuit*,  $V_{CC} = 4.75V$  to 5.25V, RF and LO ports are driven from  $50\Omega$  sources,  $P_{LO} = -3dBm$  to +3dBm,  $P_{RF} = -5dBm$ ,  $f_{RF} = 820MHz$  to 920MHz,  $f_{LO} = 670MHz$  to 865MHz,  $f_{IF} = 100MHz$ ,  $f_{RF} > f_{LO}$ ,  $T_{C} = -40^{\circ}C$  to  $+85^{\circ}C$ . Typical values are at  $V_{CC} = 5.0V$ ,  $P_{RF} = -5dBm$ ,  $P_{LO} = 0dBm$ ,  $f_{RF} = 870MHz$ ,  $f_{LO} = 770MHz$ ,  $f_{IF} = 100MHz$ ,  $f_{C} = +25^{\circ}C$ , unless otherwise noted.) (Note 1)

| PARAMETER            | SYMBOL | CONDITIONS                                           |  | TYP  | MAX | UNITS |

|----------------------|--------|------------------------------------------------------|--|------|-----|-------|

| LO Switching Time    |        | 50% of LOSEL to IF settled within 2 degrees (Note 3) |  | 0.05 | 1   | μs    |

| RF Input Impedance   |        |                                                      |  | 50   |     | Ω     |

| LO Input Impedance   |        |                                                      |  | 50   |     | Ω     |

| IF Output Impedance  |        | Differential                                         |  | 200  |     | Ω     |

| RF Input Return Loss |        | LO on and IF terminated                              |  | 24   |     | dB    |

| LO legat Deturn Lega |        | LO port selected                                     |  | 35   |     | dB    |

| LO Input Return Loss |        | LO port unselected                                   |  | 36   |     | uБ    |

| IF Return Loss       |        | RF terminated in $50\Omega$ 20                       |  | •    | dB  |       |

- Note 1: All limits reflect losses of external components. Output measurements taken at IF outputs of the Typical Application Circuit.

- **Note 2:** Performance is guaranteed for f<sub>RF</sub> = 820MHz to 920MHz, f<sub>LO</sub> = 670MHz to 865MHz, and f<sub>IF</sub> = 100MHz. Operation outside this range is possible, but with degraded performance of some parameters. See the *Typical Operating Characteristics*.

- Note 3: Guaranteed by design and characterization.

- **Note 4:** Measured with external LO source noise filtered so the noise floor is -174dBm/Hz. This specification reflects the effects of all SNR degradations in the mixer including the LO noise, as defined in Maxim Application Note 2021.

- Note 5: Measured at IF port at IF frequency. LOSEL may be in any logic state.

- **Note 6:** Performance at  $T_C = -40^{\circ}C$  is guaranteed by design.

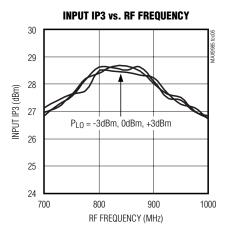

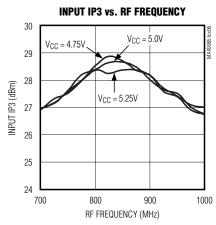

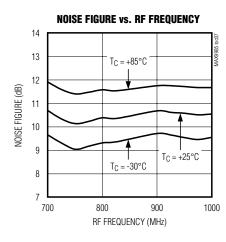

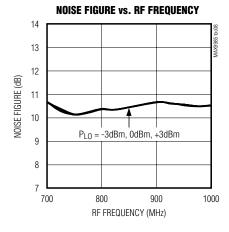

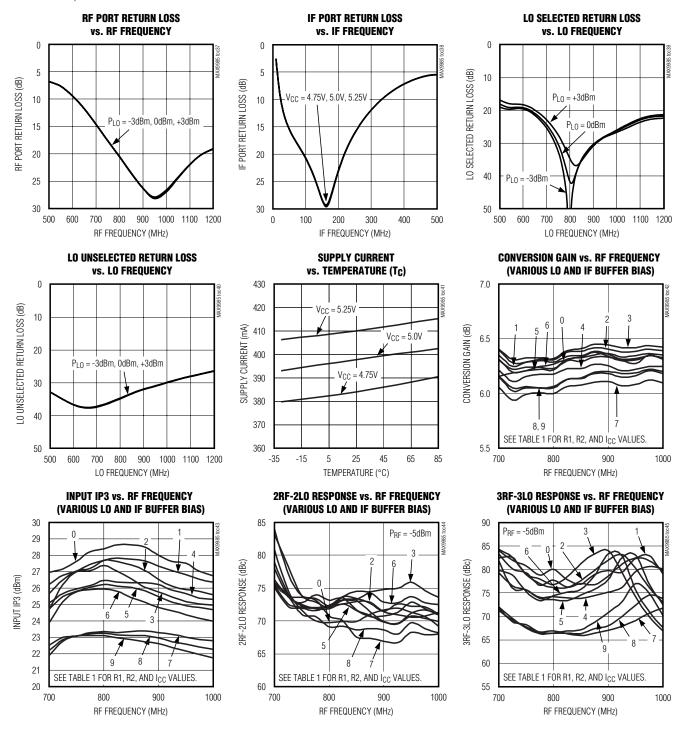

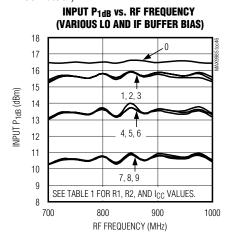

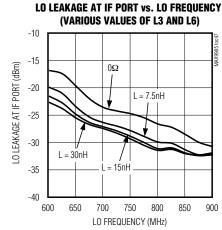

### **Typical Operating Characteristics**

(Using the *Typical Application Circuit*,  $V_{CC}$  = 5.0V,  $P_{LO}$  = 0dBm,  $P_{RF}$  = -5dBm,  $f_{RF}$  >  $f_{LO}$ ,  $f_{IF}$  = 100MHz,  $T_{C}$  = +25°C, unless otherwise noted.)

MIXIM

## Typical Operating Characteristics (continued)

(Using the *Typical Application Circuit*,  $V_{CC}$  = 5.0V,  $P_{LO}$  = 0dBm,  $P_{RF}$  = -5dBm,  $f_{RF}$  >  $f_{LO}$ ,  $f_{IF}$  = 100MHz,  $T_{C}$  = +25°C, unless otherwise noted.)

## Typical Operating Characteristics (continued)

(Using the *Typical Application Circuit*,  $V_{CC}$  = 5.0V,  $P_{LO}$  = 0dBm,  $P_{RF}$  = -5dBm,  $f_{RF}$  >  $f_{LO}$ ,  $f_{IF}$  = 100MHz,  $T_{C}$  = +25°C, unless otherwise noted.)

MIXIM

#### Typical Operating Characteristics (continued)

(Using the *Typical Application Circuit*,  $V_{CC}$  = 5.0V,  $P_{LO}$  = 0dBm,  $P_{RF}$  = -5dBm,  $f_{RF}$  >  $f_{LO}$ ,  $f_{IF}$  = 100MHz,  $T_{C}$  = +25°C, unless otherwise noted.)

### Typical Operating Characteristics (continued)

(Using the *Typical Application Circuit*,  $V_{CC}$  = 5.0V,  $P_{LO}$  = 0dBm,  $P_{RF}$  = -5dBm,  $f_{RF}$  >  $f_{LO}$ ,  $f_{IF}$  = 100MHz,  $T_{C}$  = +25°C, unless otherwise noted.)

#### Typical Operating Characteristics (continued)

(Using the *Typical Application Circuit*,  $V_{CC}$  = 5.0V,  $P_{LO}$  = 0dBm,  $P_{RF}$  = -5dBm,  $f_{RF}$  >  $f_{LO}$ ,  $f_{IF}$  = 100MHz,  $T_{C}$  = +25°C, unless otherwise noted.)

Table 1. DC Current vs. Bias Resistor Settings

| •              |                 |                         |                               |

|----------------|-----------------|-------------------------|-------------------------------|

| BIAS CONDITION | DC CURRENT (mA) | R1 AND R4<br>VALUES (Ω) | R2 AND R5 VALUES ( $\Omega$ ) |

| 0              | 397.8           | 1070                    | 1100                          |

| 1              | 345.0           | 1400                    | 1100                          |

| 2              | 316.5           | 1400                    | 1620                          |

| 3              | 297.5           | 1400                    | 2210                          |

| 4              | 301.2           | 1910                    | 1100                          |

| 5              | 271.7           | 1910                    | 1620                          |

| 6              | 252.2           | 1910                    | 2210                          |

| 7              | 260.1           | 2800                    | 1100                          |

| 8              | 230.5           | 2800                    | 1620                          |

| 9              | 211.5           | 2800                    | 2210                          |

## **Pin Description**

| PIN                                       | NAME       | FUNCTION                                                                                                                                                                                                                                               |

|-------------------------------------------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                                         | RFMAIN     | Main Channel RF input. Internally matched to 50Ω. Requires an input DC-blocking capacitor.                                                                                                                                                             |

| 2                                         | TAPMAIN    | Main Channel Balun Center Tap. Bypass to GND with capacitors close to the pin.                                                                                                                                                                         |

| 3, 5, 7, 12,<br>20, 22, 24,<br>25, 26, 34 | GND        | Ground                                                                                                                                                                                                                                                 |

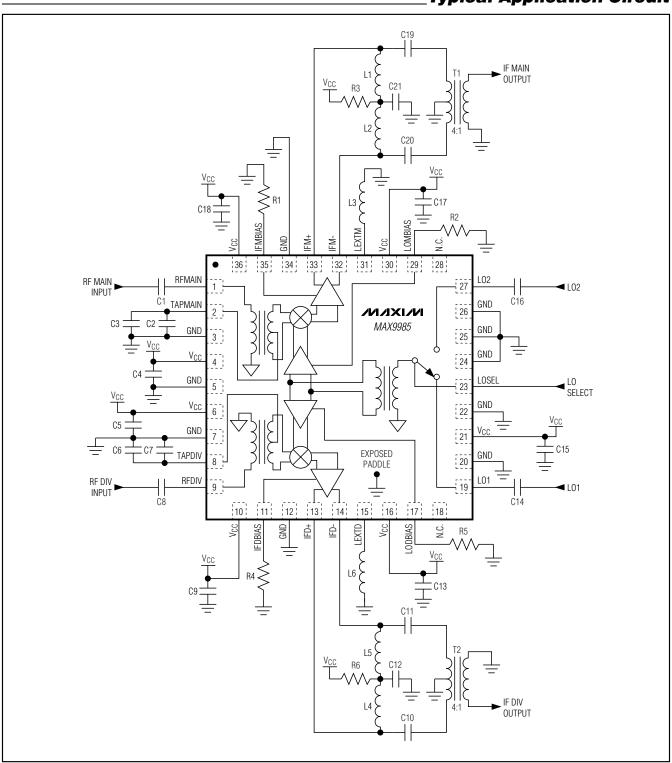

| 4, 6, 10, 16,<br>21, 30, 36               | VCC        | Power Supply. Connect bypass capacitors as close to the pin as possible (see the <i>Typical Application Circuit</i> ).                                                                                                                                 |

| 8                                         | TAPDIV     | Diversity Channel Balun Center Tap. Bypass to GND with capacitors close to the pin.                                                                                                                                                                    |

| 9                                         | RFDIV      | Diversity Channel RF Input. Internally matched to 50Ω. Requires an input DC-blocking capacitor.                                                                                                                                                        |

| 11                                        | IFDBIAS    | IF Diversity Amplifier Bias Control. Connect a $1.07k\Omega$ resistor from this pin to ground to set the bias current for the diversity IF amplifier (see the <i>Typical Operating Characteristics</i> for typical performance versus resistor value). |

| 13, 14                                    | IFD+, IFD- | Diversity Mixer Differential IF Output. Connect pullup inductors from each of these pins to V <sub>CC</sub> (see the <i>Typical Application Circuit</i> ).                                                                                             |

| 15                                        | LEXTD      | Connect a 30nH inductor from this pin to ground to increase the RF-to-IF and LO-to-IF isolation. Connect this pin to ground if isolations can be degraded (see the <i>Typical Operating Characteristics</i> for typical degradation).                  |

| 17                                        | LODBIAS    | LO Diversity Amplifier Bias Control. Connect a 1.1kΩ resistor from this pin to ground to set the bias current for the diversity LO amplifier (see the <i>Typical Operating Characteristics</i> for typical performance versus resistor value).         |

| 18, 28                                    | N.C.       | No Connection. Not internally connected.                                                                                                                                                                                                               |

| 19                                        | LO1        | Local Oscillator 1 Input. This input is internally matched to 50Ω. Requires an input DC-blocking capacitor.                                                                                                                                            |

| 23                                        | LOSEL      | Local Oscillator Select. Set this pin to high to select LO1. Set low to select LO2.                                                                                                                                                                    |

| 27                                        | LO2        | Local Oscillator 2 Input. This input is internally matched to 50Ω. Requires an input DC-blocking capacitor.                                                                                                                                            |

| 29                                        | LOMBIAS    | LO Main Amplifier Bias Control. Connect a $1.1k\Omega$ resistor from this pin to ground to set the bias current for the main LO amplifier (see the <i>Typical Operating Characteristics</i> for typical performance versus resistor value).            |

| 31                                        | LEXTM      | Connect a 30nH inductor from this pin to ground to increase the RF-IF and LO-IF isolation. Connect this pin to ground if isolations can be degraded (see the <i>Typical Operating Characteristics</i> for typical degradation).                        |

| 32, 33                                    | IFM-, IFM+ | Main Mixer Differential IF Output. Connect pullup inductors from each of these pins to V <sub>CC</sub> (see the <i>Typical Application Circuit</i> ).                                                                                                  |

| 35                                        | IFMBIAS    | IF Main Amplifier Bias Control. Connect a $1.07k\Omega$ resistor from this pin to ground to set the bias current for the main IF amplifier (see the <i>Typical Operating Characteristics</i> for typical performance vs. resistor value).              |

| _                                         | EP         | Exposed Paddle. Solder the exposed paddle to the ground plane using multiple vias. This paddle affects RF performance and provides heat dissipation.                                                                                                   |

### **Detailed Description**

The MAX9985 is a dual-channel downconverter designed to provide 6dB of conversion gain, +28.5dBm input IP3, and +16.2dBm 1dB input compression point, with a 10.5dB NF.

In addition to its high-linearity performance, the MAX9985 achieves a high level of component integration. The device integrates two double-balanced active mixers for two-channel downconversion. Both the main and diversity channels include a balun and matching circuitry to allow  $50\Omega$  single-ended interfaces to the RF ports and the two LO ports. An integrated single-pole, double-throw (SPDT) switch provides 50ns switching time between the two LO inputs with 43dB of LO-to-LO isolation and a -40dBm of LO leakage at the RF port. Furthermore, the integrated LO buffers provide a high drive level to each mixer core, reducing the LO drive required at the MAX9985's inputs to a -3dBm to +3dBm range. The IF ports for both channels incorporate differential outputs for downconversion, which is ideal for providing enhanced IIP2 performance.

Dual-channel downconversion makes the MAX9985 ideal for diversity receiver applications. In addition, specifications are guaranteed over broad frequency ranges to allow for use in GSM 850/950, 2G/2.5G EDGE, WCDMA, cdma2000, and iDEN base stations. The MAX9985 is specified to operate over a 700MHz to 1000MHz RF input range, a 570MHz to 865MHz LO range, and a 50MHz to 250MHz IF range. The external IF components set the lower frequency range (see the *Typical Operating Characteristics* for details).

#### **RF Port and Balun**

The RF input ports to both the main and diversity channels are internally matched to  $50\Omega$ , requiring no external matching components. A DC-blocking capacitor is required as the input is internally DC-shorted to ground through the on-chip balun. The RF port return loss is typically 15dB over the entire 700MHz to 1000MHz RF frequency range.

#### LO Inputs, Buffer, and Balun

The MAX9985 is optimized for a 570MHz to 865MHz LO frequency range. As an added feature, the MAX9985 includes an internal LO SPDT switch for use in frequency-hopping applications. The switch selects one of the two single-ended LO ports, allowing the external oscillator to settle on a particular frequency before it is switched in. LO switching time is typically less than 50ns, which is more than adequate for typical GSM applications. If frequency hopping is not employed, simply set the switch to either of the LO inputs. The switch is controlled by a digital input

(LOSEL), where logic-high selects LO1 and logic-low selects LO2. LO1 and LO2 inputs are internally matched to  $50\Omega$ , requiring only an 82pF DC-blocking capacitor. To avoid damage to the part, voltage **MUST** be applied to VCC before digital logic is applied to LOSEL. Alternatively, a  $1k\Omega$  resistor can be placed in series at the LOSEL to limit the input current in applications where LOSEL is applied before VCC.

The main and diversity channels incorporate a two-stage LO buffer that allows for a wide-input power range for the LO drive. All guaranteed specifications are for an LO signal power from -3dBm to +3dBm. The on-chip low-loss baluns, along with LO buffers, drive the double-balanced mixers. All interfacing and matching components from the LO inputs to the IF outputs are integrated on-chip.

#### **High-Linearity Mixer**

The core of the MAX9985 dual-channel downconverter consists of two double-balanced, high-performance passive mixers. Exceptional linearity is provided by the large LO swing from the on-chip LO buffers. When combined with the integrated IF amplifiers, the cascaded IIP3, 2RF-2LO rejection, and NF performance are typically +28.5dBm, 77dBc, and 10.5dB, respectively.

#### Differential IF

The MAX9985 has a 50MHz to 250MHz IF frequency range, where the low-end frequency depends on the frequency response of the external IF components. Note that these differential ports are ideal for providing enhanced IIP2 performance. Single-ended IF applications require a 4:1 (impedance ratio) balun to transform the  $200\Omega$  differential IF impedance to a  $50\Omega$  single-ended system. After the balun, the IF return loss is better than 20dB. The user can use a differential IF amplifier on the mixer IF ports, but a DC block is required on both IFD+/IFD- and IFM+/IFM- ports to keep external DC from entering the IF ports of the mixer.

## Applications Information

#### **Input and Output Matching**

The RF and LO inputs are internally matched to  $50\Omega$ . No matching components are required. Return loss at the RF port is typically 15dB over the entire input range and return loss at the LO ports are typically 25dB. RF and LO inputs require only DC-blocking capacitors for interfacing.

The IF output impedance is  $200\Omega$  (differential). For evaluation, an external low-loss 4:1 (impedance ratio) balun transforms this impedance to a  $50\Omega$  single-ended output (see the *Typical Application Circuit*).

#### **LO Buffer Bias Resistors**

Bias currents for the two on-chip LO buffers is optimized by fine-tuning the off-chip resistors on LODBIAS (pin 17) and LOMBIAS (pin 29). The current in the buffer amplifiers is reduced by increasing the value of these resistors, but performance may degrade. See the *Typical Operating Characteristics* for key performance parameters versus this resistor value. Doubling the value of these resistors reduces the total chip current by approximately 50mA (see Table 1).

#### **IF Amplifier Bias Resistors**

Bias currents for the two on-chip IF amplifiers are optimized by fine-tuning the off-chip resistors on IFDBIAS (pin 11) and IFMBIAS (pin 35). The current in the IF amplifiers is decreased by raising the value of these resistors, but performance may degrade. See the *Typical Operating Characteristics* for key performance parameters versus this resistor value. Doubling the value of this resistor reduces the current in each IF amplifier from 100mA to approximately 50mA (see Table 1).

#### **LEXT Inductor**

Short LEXT\_ to ground using a  $0\Omega$  resistor. For applications requiring improved RF-to-IF and LO-to-IF isolation, LEXT\_ can be used by connecting a low-ESR inductor from LEXT\_ to GND. See the *Typical Operating Characteristics* on RF-to-IF port isolation and LO-to-IF port leakage for various inductor values. The load impedance presented to the mixer must be such that any capacitance from both IF- and IF+ to ground do not exceed several picofarads to ensure stable operating conditions.

Approximately 100mA flows through LEXT\_, so it is important to use a low-DCR wire-wound inductor.

#### **Layout Considerations**

A properly designed PCB is an essential part of any RF/microwave circuit. Keep RF signal lines as short as possible to reduce losses, radiation, and inductance. For the best performance, route the ground pin traces directly to the exposed paddle under the package. The PCB exposed paddle **MUST** be connected to the ground plane of the PCB. It is suggested that multiple vias be used to connect this paddle to the lower-level ground planes. This method provides a good RF/thermal-conduction path for the device. Solder the exposed paddle on the bottom of the device package to the PCB. Refer to the *MAX9985 Evaluation Kit* as a reference for board layout. Gerber files are available upon request at www.maxim-ic.com.

#### **Power-Supply Bypassing**

Proper voltage-supply bypassing is essential for high-frequency circuit stability. Bypass each VCC pin and TAPMAIN/TAPDIV with the capacitors shown in the *Typical Application Circuit* (see Table 2 for component values). Place the TAPMAIN/TAPDIV bypass capacitor to ground within 100 mils of the pin.

**Table 2. Component Values**

| COMPONENT                       | VALUE   | DESCRIPTION                                      |

|---------------------------------|---------|--------------------------------------------------|

| C1, C2, C7, C8                  | 39pF    | Microwave capacitors (0402)                      |

| C3, C6                          | 0.033µF | Microwave capacitors (0603)                      |

| C4, C5                          | _       | Not used                                         |

| C9, C13, C15,<br>C17, C18       | 0.01µF  | Microwave capacitors (0402)                      |

| C10, C11, C12,<br>C19, C20, C21 | 150pF   | Microwave capacitors (0603)                      |

| C14, C16                        | 82pF    | Microwave capacitors (0402)                      |

| L1, L2, L4, L5                  | 560nH   | Wire-wound high-Q inductors (0805)               |

| L3, L6                          | 30nH    | Wire-wound high-Q inductors (0603)               |

| R1, R4                          | 1.07kΩ  | ±1% resistors (0402)                             |

| R2, R5                          | 1.1kΩ   | ±1% resistors (0402)                             |

| R3, R6                          | 0Ω      | Resistors (1206)                                 |

| T1, T2                          | 4:1     | Transformers (200:50)<br>Mini-Circuits TC4-1W-7A |

| U1                              | _       | MAX9985 IC                                       |

# Exposed Paddle RF/Thermal Considerations

The exposed paddle (EP) of the MAX9985's 36-pin thin QFN-EP package provides a low thermal-resistance path to the die. It is important that the PCB on which the MAX9985 is mounted be designed to conduct heat from the EP. In addition, provide the EP with a low-inductance path to electrical ground. The EP **MUST** be soldered to a ground plane on the PCB, either directly or through an array of plated via holes.

### **Typical Application Circuit**

### Pin Configuration/Functional Diagram

#### \_Chip Information

PROCESS: SiGe BiCMOS

## \_Package Information

For the latest package outline information, go to **www.maxim-ic.com/packages**.

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.

Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600

\_ 15

© 2007 Maxim Integrated Products

is a registered trademark of Maxim Integrated Products, Inc.