#### **General Description**

The MAX2837 direct-conversion zero-IF RF transceiver is designed specifically for 2.3GHz to 2.7GHz wireless broadband systems. The MAX2837 completely integrates all circuitry required to implement the RF transceiver function, providing RF-to-baseband receive path; and baseband-to-RF transmit path, VCO, frequency synthesizer, crystal oscillator, and baseband/control interface. The device includes a fast-settling sigmadelta RF synthesizer with smaller than 20Hz frequency steps and a crystal oscillator, which allows the use of a low-cost crystal in place of a TCXO. The transceiver IC also integrates circuits for on-chip DC offset cancellation, I/Q error, and carrier-leakage detection circuits. Only an RF bandpass filter (BPF), crystal, RF switch, PA, and a small number of passive components are needed to form a complete wireless broadband RF

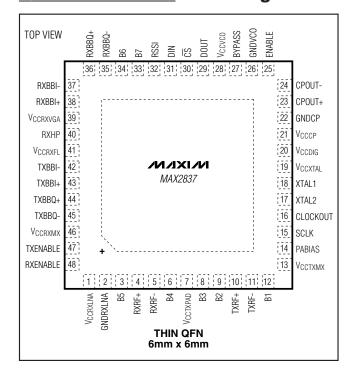

The MAX2837 completely eliminates the need for an external SAW filter by implementing on-chip monolithic filters for both the receiver and transmitter. The baseband filters along with the Rx and Tx signal paths are optimized to meet stringent noise figure and linearity specifications. The device supports up to 2048 FFT OFDM and implements programmable channel filters for 1.75MHz to 28MHz RF channel bandwidths. The transceiver requires only 2us Tx-Rx switching time, which includes frequency transient settling. The IC is available in a small, 48-pin thin QFN package measuring only 6mm x 6mm x 0.8mm.

#### **Applications**

802.16-2004 Fixed WiMAX Korea Wibro and 802.16e Mobile WiMAX Dual Mode<sup>TM</sup> WiMAX/802.11b/g Wi-Fi Proprietary Wireless Broadband Systems 4G/LTE Systems

Dual Mode is a trademark of Maxim Integrated Products, Inc. SPI is a trademark of Motorola, Inc.

#### **Features**

- ♦ 2.3GHz to 2.7GHz Wideband Operation

- ♦ Complete RF Transceiver, PA Driver, and **Crystal Oscillator**

**0dBm Linear OFDM Transmit Power**

-70dBr Tx Spectral Emission Mask

2.3dB Rx Noise Figure

Tx/Rx I/Q Error and LO Leakage Detection

Monolithic Low-Noise VCO with -39dBc **Integrated Phase Noise**

Programmable Tx I/Q Lowpass **Anti-Aliasing Filter**

Sigma-Delta Fractional-N PLL with 20Hz Step Size

45dB Tx Gain-Control Range

94dB Receive Gain-Control Range

60dB Analog RSSI Instantaneous **Dynamic Range**

4-Wire SPI™ Digital Interface

I/Q Analog Baseband Interface

**Digitally Tuned Crystal Oscillator**

**On-Chip Digital Temperature Sensor Read-Out**

- ♦ +2.7V to +3.6V Transceiver Supply

- ♦ Low-Power Shutdown Current

- ♦ Small 48-Pin Thin QFN Package (6mm x 6mm x 0.8mm)

### **Ordering Information**

| PART          | TEMP RANGE     | PIN-<br>PACKAGE |

|---------------|----------------|-----------------|

| MAX2837ETM+TD | -40°C to +85°C | 48 TQFN-EP*     |

<sup>\*</sup>EP = Exposed paddle.

Pin Configuration appears at end of data sheet.

<sup>+</sup>Denotes a lead-free package.

#### **ABSOLUTE MAXIMUM RATINGS**

| VCCLNA, VCCTXMX, VCCTXPAD, V(   |                                         |

|---------------------------------|-----------------------------------------|

| VCCVCO, VCCRXVGA, VCCRXFL       | and V <sub>CCRXMX</sub> to              |

| GND                             | 0.3V to +3.9V                           |

| B1-B7, TXRF_, CS, SCLK, DIN, DO | OUT, TXBBI_, TXBBQ_, RXHP,              |

| RXBBI_, RXBBQ_, RSSI, ENAE      | BLE, BYPASS, CPOUT_,                    |

| CLOCKOUT, XTAL1, XTAL2, R       | XRF_,RXENABLE, TXENABLE                 |

| to GND                          | $-0.3V$ to (Operating $V_{CC} + 0.3V$ ) |

| RXBBI_, RXBBQ_, RSSI, BYPASS,   | CPOUT_, DOUT, CLOCKOUT,                 |

| PABIAS Short-Circuit Duration.  | 10s                                     |

| RF Input Power                  | +10dBm                                  |

| Continuous Power Dissipation (T <sub>A</sub> = +70°C) |           |

|-------------------------------------------------------|-----------|

| 48-Pin Thin QFN (derates 37mW/°C above +70°C)         | 2.96W     |

| Operating Temperature Range40°C                       | to +85°C  |

| Junction Temperature                                  | +150°C    |

| Storage Temperature Range65°C t                       | io +160°C |

| Lead Temperature (soldering, 10s)                     | +260°C    |

|                                                       |           |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### DC ELECTRICAL CHARACTERISTICS

(MAX2837 evaluation kit:  $V_{CC}$  = 2.7V to 3.6V, Rx set to the maximum gain;  $\overline{CS}$  = high, RXHP = SCLK = DIN = low, RSSI and clock output buffer are off, no signal at RF inputs, all RF inputs and outputs terminated into 50Ω, receiver baseband outputs are open; 90mV<sub>RMS</sub> differential I and Q signals applied to I, Q baseband inputs of transmitter in transmit mode, f<sub>REF</sub> = 40MHz, registers set to recommended settings and corresponding test mode, T<sub>A</sub> = -40°C to +85°C, unless otherwise noted. Typical values are at V<sub>CC</sub> = 2.8V, f<sub>LO</sub> = 2.5GHz, and T<sub>A</sub> = +25°C, unless otherwise noted.) (Note 1)

| PARAMETER                                                 | CONDITIONS                                 | MIN                   | TYP  | МАХ  | UNITS |

|-----------------------------------------------------------|--------------------------------------------|-----------------------|------|------|-------|

| Supply Voltage                                            | Vcc_                                       | 2.7                   |      | 3.6  | V     |

|                                                           | Shutdown mode, $T_A = +25^{\circ}C$        |                       | 10   |      | μΑ    |

|                                                           | Standby mode                               |                       | 35   | 45   |       |

| Supply Current                                            | Rx mode                                    |                       | 91   | 110  |       |

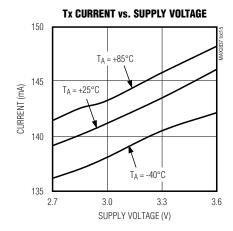

| Supply Current                                            | Tx mode, $T_A = +25$ °C                    |                       | 145  | 170  | mA    |

|                                                           | Rx calibration mode                        |                       | 135  | 160  |       |

|                                                           | Tx calibration mode                        |                       | 110  | 135  |       |

| Rx I/Q Output Common-Mode                                 | D9:D8 = 00 in A4:A0 = 00100                | 0.85                  | 1.0  | 1.20 |       |

|                                                           | D9:D8 = 01 in A4:A0 = 00100                |                       | 1.1  |      | V     |

| Voltage                                                   | D9:D8 = 10 in A4:A0 = 00100                |                       | 1.2  |      | V     |

|                                                           | D9:D8 = 11 in A4:A0 = 00100                |                       | 1.35 |      |       |

| Tx Baseband Input Common-<br>Mode Voltage Operating Range | DC-coupled                                 | 0.5                   |      | 1.2  | V     |

| Tx Baseband Input Bias Current                            | Source current                             |                       | 10   | 20   | μΑ    |

| LOGIC INPUTS: ENABLE, TXENA                               | ABLE, RXENABLE, SCLK, DIN, CS, B7:B1, RXHP |                       |      |      |       |

| Digital Input-Voltage High, VIH                           |                                            | V <sub>CC</sub> - 0.4 |      |      | V     |

| Digital Input-Voltage Low, VIL                            |                                            |                       |      | 0.4  | V     |

| Digital Input-Current High, I <sub>IH</sub>               |                                            | -1                    |      | +1   | μΑ    |

| Digital Input-Current Low, IIL                            |                                            | -1                    |      | +1   | μΑ    |

2 \_\_\_\_\_\_*NIXIN*

#### DC ELECTRICAL CHARACTERISTICS (continued)

(MAX2837 evaluation kit:  $V_{CC}$  = 2.7V to 3.6V, Rx set to the maximum gain;  $\overline{CS}$  = high, RXHP = SCLK = DIN = low, RSSI and clock output buffer are off, no signal at RF inputs, all RF inputs and outputs terminated into 50Ω, receiver baseband outputs are open; 90mV<sub>RMS</sub> differential I and Q signals applied to I, Q baseband inputs of transmitter in transmit mode, f<sub>REF</sub> = 40MHz, registers set to recommended settings and corresponding test mode, T<sub>A</sub> = -40°C to +85°C, unless otherwise noted. Typical values are at V<sub>CC</sub> = 2.8V, f<sub>LO</sub> = 2.5GHz, and T<sub>A</sub> = +25°C, unless otherwise noted.) (Note 1)

| PARAMETER                        | CONDITIONS     | MIN                   | TYP | MAX | UNITS |

|----------------------------------|----------------|-----------------------|-----|-----|-------|

| LOGIC OUTPUTS: DOUT              |                |                       |     |     |       |

| Digital Output-Voltage High, VOH | Sourcing 100µA | V <sub>CC</sub> - 0.4 |     |     | V     |

| Digital Output-Voltage Low, VOL  | Sinking 100µA  |                       |     | 0.4 | V     |

#### AC ELECTRICAL CHARACTERISTICS—Rx MODE

(MAX2837 evaluation kit:  $V_{CC}$  = 2.8V,  $f_{RF}$  = 2.502GHz,  $f_{LO}$  = 2.5GHz; receiver baseband I/Q outputs at 90mV<sub>RMS</sub> (-21dBV),  $f_{REF}$  = 40MHz, ENABLE = RXENABLE =  $\overline{CS}$  = high, TXENABLE = SCLK = DIN = low, with power matching for the differential RF pins using the typical applications and registers set to default settings and corresponding test mode,  $T_A$  = +25°C, unless otherwise noted. Lowpass filter is set to 10MHz RF channel BW. Unmodulated single-tone RF input signal is used, unless otherwise indicated.) (Note 1)

| PARAMETER                                                 | CONDITIONS                                                                                               |                                      | MIN | TYP | MAX | UNITS |

|-----------------------------------------------------------|----------------------------------------------------------------------------------------------------------|--------------------------------------|-----|-----|-----|-------|

| RECEIVER SECTION: LNA RF IN                               | PUT TO BASEBAND                                                                                          | I/Q OUTPUTS                          |     |     |     |       |

| RF Input Frequency Range                                  |                                                                                                          |                                      | 2.3 |     | 2.7 | GHz   |

| Peak-to-Peak Gain Variation over RF Input Frequency Range | Tested at band edge                                                                                      | Tested at band edges and band center |     |     |     | dB    |

| RF Input Return Loss                                      | All LNA gain settings                                                                                    |                                      |     | 13  |     | dB    |

| Total Voltage Gain                                        | $T_A = -40^{\circ}C \text{ to } +85^{\circ}C$                                                            | Maximum gain, B7:B1 = 0000000        | 90  | 99  |     | dB    |

| Total Voltage Gain                                        | 1A = -40 C to +05 C                                                                                      | Minimum gain, B7:B1 = 1111111        |     | 5   | 13  | QD.   |

|                                                           | From max RF gain to                                                                                      | max RF gain - 8dB                    |     | 8   |     |       |

| RF Gain Steps                                             | From max RF gain to                                                                                      | max RF gain - 16dB                   |     | 16  |     | dB    |

|                                                           | From max RF gain to                                                                                      | max RF gain - 32dB                   |     | 32  |     |       |

| Coin Change Settling Time                                 | Any RF or baseband gain change; gain settling to within ±1dB of steady state; RXHP = 1                   |                                      |     | 0.2 |     | 110   |

| Gain Change Settling Time                                 | Any RF or baseband gain change; gain settling to within $\pm 0.1$ dB of steady state; RXHP = 1           |                                      |     | 2   |     | μs    |

| Baseband Gain Range                                       | From maximum baseband gain (B5:B1 = 00000) to minimum baseband gain (B5:B1 = 11111), TA = -40°C to +85°C |                                      | 58  | 62  | 66  | dB    |

| Baseband Gain Minimum<br>Step Size                        |                                                                                                          |                                      |     | 2   |     | dB    |

|                                                           | Voltage gain ≥ 65dB                                                                                      | with max RF gain (B7:B6 = 00)        |     | 2.3 |     |       |

|                                                           | Voltage gain = 50dB<br>(B7:B6 = 01)                                                                      | with max RF gain - 8dB               |     | 5.5 |     |       |

| DSB Noise Figure                                          | Voltage gain = 45dB with max RF gain - 16dB (B7:B6 = 10)                                                 |                                      |     | 17  |     | dB    |

|                                                           | Voltage gain = 15dB<br>(B7:B6 = 11)                                                                      | with max RF gain - 32dB              |     | 27  |     |       |

### AC ELECTRICAL CHARACTERISTICS—Rx MODE (continued)

MAX2837 evaluation kit:  $V_{CC_-} = 2.8V$ ,  $f_{RF} = 2.502 GHz$ ,  $f_{LO} = 2.5 GHz$ ; receiver baseband I/Q outputs at  $90mV_{RMS}$  (-21dBV),  $f_{REF} = 40MHz$ , ENABLE = RXENABLE =  $\overline{CS}$  = high, TXENABLE = SCLK = DIN = low, with power matching for the differential RF pins using the typical applications and registers set to default settings and corresponding test mode,  $T_A = +25^{\circ}C$ , unless otherwise noted. Lowpass filter is set to 10MHz RF channel BW. Unmodulated single-tone RF input signal is used, unless otherwise indicated.) (Note 1)

| PARAMETER                                       | CON                                                                   | NDITIONS                                                                                                                                         | MIN        | TYP  | MAX  | UNITS            |  |

|-------------------------------------------------|-----------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|------------|------|------|------------------|--|

|                                                 | Max RF gain (B7:B6 = 00                                               | ))                                                                                                                                               |            | -37  |      |                  |  |

| la Dand law & D. 4 dD                           | Max RF gain - 8dB (B7:B6                                              | Max RF gain - 8dB (B7:B6 = 01)                                                                                                                   |            |      |      | j                |  |

| In-Band Input P-1dB                             | Max RF gain - 16dB (B7:E                                              | 36 = 10)                                                                                                                                         |            | -21  |      | dBm              |  |

|                                                 | Max RF gain - 32dB (B7:                                               | 36 = 11)                                                                                                                                         |            | -4   |      | 1                |  |

| Maximum Output Signal Level                     | Over passband frequency 1dB compression point                         | y range; at any gain setting;                                                                                                                    |            | 2.5  |      | V <sub>P-P</sub> |  |

|                                                 | Max RF gain (B7:B6 = 00 wanted signal                                 | )), AGC set for -65dBm                                                                                                                           |            | -11  |      |                  |  |

| Out of Decad leavet IDO (Nate O)                | Max RF gain - 8dB (B7:B0 wanted signal                                | 6 = 01), AGC set for -55dBm                                                                                                                      |            | -8   |      | -10              |  |

| Out-of-Band Input IP3 (Note 2)                  | Max RF gain - 16dB (B7:8 wanted signal                                | 36 = 10), AGC set for -40dBm                                                                                                                     |            | -6   |      | - dBm            |  |

|                                                 | Max RF gain - 32dB (B7:E) wanted signal                               | 36 = 11), AGC set for -30dBm                                                                                                                     | -30dBm +16 |      |      |                  |  |

| I/Q Phase Error                                 | 50kHz baseband output;                                                | $1\sigma$ variation                                                                                                                              |            | 0.15 |      | Degrees          |  |

| I/Q Gain Imbalance                              | 50kHz baseband output;                                                | 1σ variation                                                                                                                                     |            | 0.1  |      | dB               |  |

| Rx I/Q Output Load Impedance                    | Minimum differential resi                                             | stance                                                                                                                                           | 10         |      |      | kΩ               |  |

| (R II C)                                        | Maximum differential cap                                              | pacitance                                                                                                                                        |            | 5    |      | pF               |  |

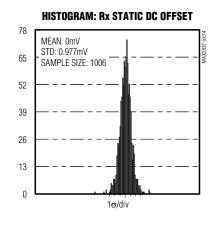

| I/Q Output DC Droop                             | gain change, or 2µs after                                             | After switching RXHP to 0; average over 1μs after any gain change, or 2μs after receive enabled with 100Hz ±1 interval AC-coupling, 1σ variation |            |      |      | mV/ms            |  |

| I/Q Static DC Offset                            | No RF input signal; meas<br>enable; RXHP = 1 for 0 to<br>1σ variation | sure at 3µs after receive<br>2µs and set to 0 after 2µs,                                                                                         |            | ±1   |      | mV               |  |

| Loopback Gain<br>(for Receiver I/Q Calibration) |                                                                       | ceiver I/Q output; transmitter<br>r B5:B1 = 10100 programmed                                                                                     | -4.5       | 0    | +4.5 | dB               |  |

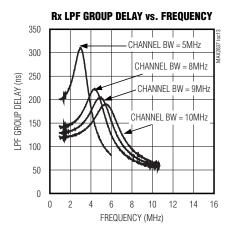

| RECEIVER BASEBAND FILTER                        | S                                                                     |                                                                                                                                                  |            |      |      |                  |  |

|                                                 | At 15MHz                                                              |                                                                                                                                                  |            | 57   |      |                  |  |

| Baseband Filter Rejection                       | At 20MHz                                                              |                                                                                                                                                  |            | 75   |      | dB               |  |

|                                                 | At > 40MHz                                                            |                                                                                                                                                  |            | 90   |      |                  |  |

|                                                 | RXHP = 1 (used before A                                               |                                                                                                                                                  | 650        |      |      |                  |  |

| Baseband Highpass Filter                        | DVIID O (wood off -                                                   | D5:D4 = 00                                                                                                                                       | 0.1        |      |      |                  |  |

| Corner Frequency                                | RXHP = 0 (used after AGC completion)                                  | D5:D4 = 01                                                                                                                                       |            | 1    |      | kHz              |  |

|                                                 | address A4:A0 = 01110 D5:D4 = 10                                      |                                                                                                                                                  | 30         |      | ]    |                  |  |

|                                                 |                                                                       | D5:D4 = 11                                                                                                                                       |            | 100  |      |                  |  |

### AC ELECTRICAL CHARACTERISTICS—Rx MODE (continued)

MAX2837 evaluation kit:  $V_{CC_-} = 2.8V$ ,  $f_{RF} = 2.502 GHz$ ,  $f_{LO} = 2.5 GHz$ ; receiver baseband I/Q outputs at  $90mV_{RMS}$  (-21dBV),  $f_{REF} = 40MHz$ , ENABLE = RXENABLE =  $\overline{CS}$  = high, TXENABLE = SCLK = DIN = low, with power matching for the differential RF pins using the typical applications and registers set to default settings and corresponding test mode,  $T_A = +25^{\circ}C$ , unless otherwise noted. Lowpass filter is set to 10MHz RF channel BW. Unmodulated single-tone RF input signal is used, unless otherwise indicated.) (Note 1)

| PARAMETER                         | COI                                    | NDITIONS                    | MIN                                  | TYP               | MAX | UNITS   |

|-----------------------------------|----------------------------------------|-----------------------------|--------------------------------------|-------------------|-----|---------|

|                                   | A4:A0 = 00010 serial bits              | D7:D4 = 0000                |                                      | 1.75              |     |         |

|                                   | A4:A0 = 00010 serial bits              |                             | 2.25                                 |                   |     |         |

|                                   | A4:A0 = 00010 serial bits              |                             | 3.5                                  |                   |     |         |

|                                   | A4:A0 = 00010 serial bits              | D7:D4 = 0011                |                                      | 5.0               |     | 1       |

|                                   | A4:A0 = 00010 serial bits              |                             | 5.5                                  |                   |     |         |

|                                   | A4:A0 = 00010 serial bits              | D7:D4 = 0101                |                                      | 6.0               |     |         |

|                                   | A4:A0 = 00010 serial bits              | D7:D4 = 0110                |                                      | 7.0               |     |         |

| RF Channel BW Supported by        | A4:A0 = 00010 serial bits              | D7:D4 = 0111                |                                      | 8.0               |     | N 41 1- |

| Baseband Filter                   | A4:A0 = 00010 serial bits              | D7:D4 = 1000                |                                      | 9.0               |     | MHz     |

|                                   | A4:A0 = 00010 serial bits              | D7:D4 = 1001                |                                      | 10.0              |     |         |

|                                   | A4:A0 = 00010 serial bits              | D7:D4 = 1010                |                                      | 12.0              |     |         |

|                                   | A4:A0 = 00010 serial bits D7:D4 = 1011 |                             |                                      | 14.0              |     |         |

|                                   | A4:A0 = 00010 serial bits              |                             | 15.0                                 |                   | 1   |         |

|                                   | A4:A0 = 00010 serial bits              |                             | 20.0                                 |                   |     |         |

|                                   | A4:A0 = 00010 serial bits              |                             | 24.0                                 |                   |     |         |

|                                   | A4:A0 = 00010 serial bits              |                             | 28.0                                 |                   |     |         |

| Deschand Cain Dinale              | 0 to 2.3MHz for BW = 5M                | to 2.3MHz for BW = 5MHz 1.3 |                                      |                   |     | dD      |

| Baseband Gain Ripple              | 0 to 4.6MHz for BW = 10N               | ИНz                         | 14.0<br>15.0<br>20.0<br>24.0<br>28.0 | dB <sub>P-P</sub> |     |         |

| December of Crouse Deley Discrete | 0 to 2.3MHz for BW = 5M                | Hz                          |                                      |                   |     |         |

| Baseband Group Delay Ripple       | 0 to $4.6$ MHz for BW = $10$ M         | ИНz                         |                                      | 50                |     | nsp-p   |

| Baseband Filter Rejection for     | At 3.3MHz                              |                             |                                      | 7                 |     | 4D      |

| 5MHz RF Channel BW                | At > 21MHz                             |                             |                                      | 85                |     | dB      |

| Baseband Filter Rejection for     | At 6.7MHz                              |                             |                                      | 7                 |     | dB      |

| 10MHz RF Channel BW               | At > 41.6MHz                           |                             |                                      | 85                |     | иь      |

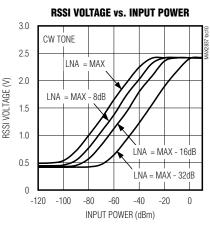

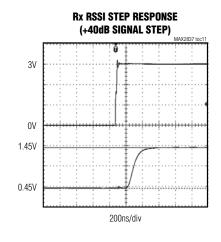

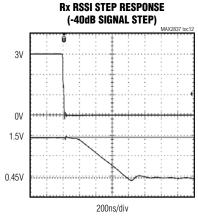

| RSSI                              |                                        |                             |                                      |                   |     |         |

| RSSI Minimum Output Voltage       | $R_{LOAD} \ge 10k\Omega$               |                             |                                      | 0.4               |     | V       |

| RSSI Maximum Output Voltage       | $R_{LOAD} \ge 10k\Omega$               | $R_{LOAD} \ge 10k\Omega$    |                                      | 2.2               |     | V       |

| RSSI Slope                        |                                        |                             |                                      | 30                |     | mV/dB   |

| RSSI Output Settling Time         | To within 3dB of steady                | +32dB signal step           |                                      | 200               |     | 200     |

| nooi Ouipui oeiliing Time         | state                                  | -32dB signal step           |                                      | 800 ns            | ns  |         |

|                                   | •                                      | •                           |                                      |                   |     | •       |

#### AC ELECTRICAL CHARACTERISTICS—Tx MODE

(MAX2837 evaluation kit:  $V_{CC}$  = 2.8V,  $T_A$  = +25°C,  $f_{RF}$  = 2.502GHz,  $f_{LO}$  = 2.5GHz;  $f_{REF}$  = 40MHz, ENABLE = TXENABLE =  $\overline{CS}$  = high, and RXENABLE = SCLK = DIN = low, with power matching for the differential RF pins using the *Typical Operating Circuit*. Lowpass fitler is set to 10MHz RF channel BW, 90mV<sub>RMS</sub> sine and cosine signal (or 90mV<sub>RMS</sub> 64QAM 1024-FFT OFDMA FUSC I/Q signals wherever OFDM is mentioned) applied to baseband I/Q inputs of transmitter (differential DC-coupled).) (Note 1)

| PARAMETER                                                           | CONDITIONS                                                                                                       | MIN          | TYP | MAX  | UNITS |  |

|---------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|--------------|-----|------|-------|--|

| TRANSMIT SECTION: Tx BASEB                                          | AND I/Q INPUTS TO RF OUTPUTS                                                                                     | •            |     |      |       |  |

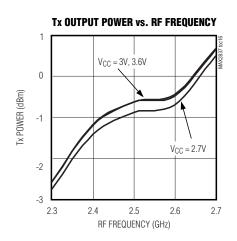

| RF Output Frequency Range                                           |                                                                                                                  | 2.3          |     | 2.7  | GHz   |  |

| Peak-to-Peak Gain Variation over RF Band                            | Output optimally matched over 200MHz RF BW                                                                       |              | 2.5 |      | dB    |  |

| Total Voltage Gain                                                  | Max gain; at unbalanced 50Ω balun output                                                                         |              | 12  |      | dB    |  |

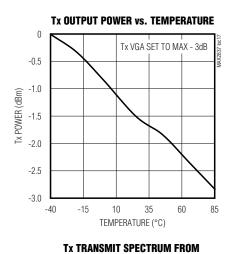

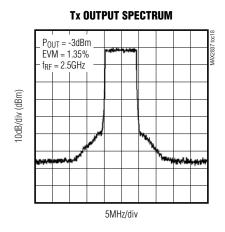

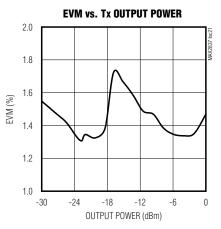

| Maximum Output Power over<br>Frequency for Any Given<br>200MHz Band | OFDM signal conforming to spectral emission mask and -36dB EVM after I/Q imbalance calibration by modem (Note 3) |              | 0   |      |       |  |

| RF Output Return Loss                                               | Given 200MHz band in the 2.3GHz to 2.7GHz range, for which the matching has been optimized                       |              | 8   |      |       |  |

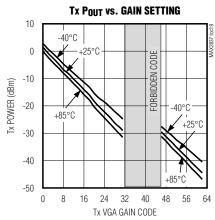

| RF Gain Control Range                                               |                                                                                                                  |              | 45  |      | dB    |  |

| Unwanted Sideband Suppression                                       | Without calibration by modem, and excludes modem I/Q imbalance; POUT = 0dBm                                      | 45           |     |      | dBc   |  |

|                                                                     | B1                                                                                                               |              | 1   |      |       |  |

|                                                                     | B2                                                                                                               |              | 2   |      | ]     |  |

| RF Gain-Control Binary Weights                                      | B3                                                                                                               | 4<br>8<br>16 |     |      | dB    |  |

| The Cami-Control Billary Weights                                    | B4                                                                                                               |              |     |      |       |  |

|                                                                     | B5                                                                                                               |              |     |      |       |  |

|                                                                     | B6                                                                                                               |              | 16  |      |       |  |

| Carrier Leakage                                                     | Relative to 0dBm output power; without calibration by modem                                                      |              | -35 |      | dBc   |  |

| Ty I/O logget logged and a (D.II.C)                                 | Minimum differential resistance                                                                                  |              | 100 |      | kΩ    |  |

| Tx I/Q Input Impedance (R II C)                                     | Maximum differential capacitance                                                                                 |              | 0.5 |      | pF    |  |

| Baseband Frequency Response                                         | 0 to 2.3MHz                                                                                                      |              | 0.2 |      | 40    |  |

| for 5MHz RF Channel BW                                              | At > 25MHz                                                                                                       | 80           |     |      | dB    |  |

| Baseband Frequency Response 0 to 4.6MHz                             |                                                                                                                  | 0.2          |     | dB   |       |  |

| for 10MHz RF Channel BW                                             | At > 17MHz                                                                                                       |              | 80  |      | l ub  |  |

| Baseband Group Delay Ripple                                         | 0 to 2.3MHz (BW = 5MHz)                                                                                          |              | 20  |      | ns    |  |

| baseband Group Delay Ripple                                         | 0 to 4.6MHz (BW = 10MHz)                                                                                         | 12           |     | 1115 |       |  |

\_\_\_\_\_\_*NIXI/*M

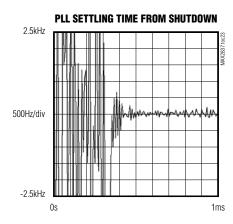

#### AC ELECTRICAL CHARACTERISTICS—FREQUENCY SYNTHESIS

(MAX2837 evaluation kit:  $V_{CC}$  = 2.8V,  $f_{LO}$  = 2.5GHz,  $f_{REF}$  = 40MHz, ENABLE =  $\overline{CS}$  = high, SCLK = DIN = low, PLL loop bandwidth = 120kHz,  $T_A$  = +25°C, unless otherwise noted.) (Note 1)

| PARAMETER                                                 | CONDITIONS                                                                                                                           | MIN | TYP                | MAX | UNITS             |

|-----------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|-----|--------------------|-----|-------------------|

| FREQUENCY SYNTHESIZER                                     |                                                                                                                                      |     |                    |     |                   |

| RF Channel Center Frequency                               |                                                                                                                                      | 2.3 |                    | 2.7 | GHz               |

| Channel Center Frequency<br>Programming Minimum Step Size |                                                                                                                                      |     | 20                 |     | Hz                |

| Charge-Pump Comparison Frequency                          |                                                                                                                                      | 11  | 40                 |     | MHz               |

| Reference Frequency Range                                 |                                                                                                                                      | 11  | 40                 | 80  | MHz               |

| Reference Frequency Input<br>Levels                       | AC-coupled to XTAL2 pin                                                                                                              | 800 |                    |     | mV <sub>P-P</sub> |

| Reference Frequency Input                                 | Resistance (XTAL2 pin)                                                                                                               |     | 10                 |     | kΩ                |

| Impedance (R II C)                                        | Capacitance (XTAL2 pin)                                                                                                              |     | 1                  |     | рF                |

| Programmable Reference Divider Values                     |                                                                                                                                      | 1   | 2                  | 4   |                   |

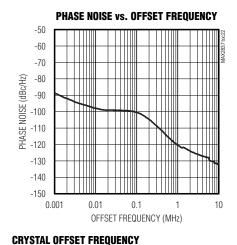

| Closed-Loop Integrated Phase Noise                        | Loop BW = 120kHz; integrate phase noise from 200Hz to 5MHz, charge-pump comparison frequency = 40MHz                                 |     | -39                |     | dBc               |

| Charge-Pump Output Current                                | On each differential side                                                                                                            |     | 1.6                |     | mA                |

|                                                           | foffset = 0 to 1.8MHz                                                                                                                |     | -40                |     |                   |

| Close-In Spur Level                                       | foffset = 1.8MHz to 7MHz                                                                                                             |     | -70                |     | dBc               |

|                                                           | foffset > 7MHz                                                                                                                       |     | -80                |     |                   |

| Reference Spur Level                                      |                                                                                                                                      |     | -85                |     | dBc               |

| Turnaround LO Frequency Error                             | Relative to steady state; measured 35µs after Tx-Rx or Rx-Tx switching instant, and 4µs after any receiver gain changes              |     | ±50                |     | Hz                |

| Temperature Range over Which VCO Maintains Lock           | Relative to the ambient temperature T <sub>A</sub> , as long as the VCO lock temperature range is within operating temperature range |     | T <sub>A</sub> ±40 |     | °C                |

| Reference Output Clock Divider Values                     |                                                                                                                                      | 1   |                    | 2   |                   |

| Output Clock Drive Level                                  | 20MHz output, 1x drive setting                                                                                                       |     | 1.5                |     | V <sub>P-P</sub>  |

| Output Clock Minimum Load                                 | Resistance                                                                                                                           |     | 10                 |     | kΩ                |

| Impedance (R II C)                                        | Capacitance                                                                                                                          |     | 2                  |     | pF                |

#### AC ELECTRICAL CHARACTERISTICS—MISCELLANEOUS BLOCKS

(MAX2837 evaluation kit:  $V_{CC}$  = 2.8V,  $f_{REF}$  = 40MHz, ENABLE =  $\overline{CS}$  = high, SCLK = DIN = low,  $T_A$  = +25°C, unless otherwise noted.) (Note 1)

| PARAMETER                               | CONDITIONS                                            |                                                                                                                                                                                                                                                                                                               | MIN | TYP                   | MAX | UNITS |

|-----------------------------------------|-------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----------------------|-----|-------|

| PA BIAS DAC: CURRENT MOD                | E                                                     |                                                                                                                                                                                                                                                                                                               | _   |                       |     |       |

| Numbers of Bits                         |                                                       |                                                                                                                                                                                                                                                                                                               |     | 6                     |     | Bits  |

| Minimum Output Sink Current             | D5:D0 = 000000 in A4:A0 = 11100                       | 5:D0 = 000000 in A4:A0 = 11100 5:D0 = 111111 in A4:A0 = 11100  ccludes programmable delay of 0 to 7μs in steps 0.5μs  0mA source current  ccludes programmable delay of 0 to 7μs in steps 0.5μs  0.5μs  aximum capacitance, A4:A0 = 11000, 6:D0 = 1111111  inimum capacitance, A4:A0 = 11000, 6:D0 = 00000000 |     | 0                     |     | μΑ    |

| Maximum Output Sink Current             | D5:D0 = 111111 in A4:A0 = 11100                       |                                                                                                                                                                                                                                                                                                               |     | 310                   |     | μΑ    |

| Compliance Voltage Range                |                                                       |                                                                                                                                                                                                                                                                                                               | 0.8 |                       | 2.0 | V     |

| Turn-On Time                            | Excludes programmable delay of 0 of 0.5µs             | Excludes programmable delay of 0 to 7µs in steps of 0.5µs                                                                                                                                                                                                                                                     |     |                       |     | ns    |

| DNL                                     |                                                       |                                                                                                                                                                                                                                                                                                               |     | 1                     |     | LSB   |

| PA BIAS DAC: VOLTAGE MODI               | <u> </u>                                              |                                                                                                                                                                                                                                                                                                               | •   |                       |     |       |

| Output High Level                       | 10mA source current                                   |                                                                                                                                                                                                                                                                                                               |     | V <sub>CC</sub> - 0.2 |     | V     |

| Output Low Level                        | 10mA sink current                                     |                                                                                                                                                                                                                                                                                                               | 0.1 |                       | V   |       |

| Turn-On Time                            | Excludes programmable delay of 0 of 0.5µs             |                                                                                                                                                                                                                                                                                                               | 200 |                       | ns  |       |

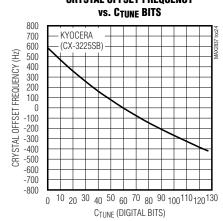

| CRYSTAL OSCILLATOR                      |                                                       |                                                                                                                                                                                                                                                                                                               | '   |                       |     |       |

| On-Chip Tuning Capacitance              | Maximum capacitance, A4:A0 = 11000, D6:D0 = 1111111   |                                                                                                                                                                                                                                                                                                               |     | 15.5                  |     | 25    |

| Range                                   | Minimum capacitance, A4:A0 = 11 D6:D0 =0000000        | Minimum capacitance, A4:A0 = 11000, D6:D0 = 0000000                                                                                                                                                                                                                                                           |     | 0.5                   |     | - pF  |

| On-Chip Tuning Capacitance<br>Step Size |                                                       |                                                                                                                                                                                                                                                                                                               |     | 0.12                  |     | pF    |

| ON-CHIP TEMPERATURE SEN                 | SOR                                                   |                                                                                                                                                                                                                                                                                                               |     |                       |     | •     |

|                                         | Dood out at DOLIT pin through CDI                     | T <sub>A</sub> = +25°C                                                                                                                                                                                                                                                                                        |     | 01111                 |     |       |

| Digital Output Code                     | Read-out at DOUT pin through SPI A4:A0 = 00111, D4:D0 | T <sub>A</sub> = +85°C                                                                                                                                                                                                                                                                                        |     | 11101                 |     |       |

|                                         |                                                       | T <sub>A</sub> = -40°C                                                                                                                                                                                                                                                                                        |     | 00001                 |     |       |

#### AC ELECTRICAL CHARACTERISTICS—TIMING

(MAX2837 evaluation kit:  $V_{CC}$  = 2.8V,  $f_{LO}$  = 2.5GHz,  $f_{REF}$  = 40MHz, ENABLE =  $\overline{CS}$  = high, SCLK = DIN = low, PLL loop bandwidth = 120kHz,  $T_A$  = +25°C, unless otherwise noted.) (Note 1)

| PARAMETER                              | SYMBOL                               | CONDITIONS                                                  |                                                                                      | MIN | TYP | MAX | UNITS |

|----------------------------------------|--------------------------------------|-------------------------------------------------------------|--------------------------------------------------------------------------------------|-----|-----|-----|-------|

| SYSTEM TIMING                          |                                      |                                                             |                                                                                      |     |     |     |       |

| Turnaround Time                        | Measured from Tx or Rx enable rising | Rx to Tx                                                    | 2                                                                                    |     |     |     |       |

|                                        |                                      | edge; signal settling<br>to within 0.5dB of<br>steady state | Tx to Rx, RXHP = 1                                                                   |     | 2   |     | - µs  |

| Tx Turn-On Time<br>(from Standby Mode) |                                      |                                                             | Measured from Tx enable rising edge; signal settling to within 0.5dB of steady state |     | 2   |     | μs    |

3 \_\_\_\_\_\_*NIXIM*

#### AC ELECTRICAL CHARACTERISTICS—TIMING (continued)

(MAX2837 evaluation kit:  $V_{CC_{-}}$  = 2.8V,  $f_{LO}$  = 2.5GHz,  $f_{REF}$  = 40MHz, ENABLE =  $\overline{CS}$  = high, SCLK = DIN = low, PLL loop bandwidth = 120kHz,  $T_A$  = +25°C, unless otherwise noted.) (Note 1)

| PARAMETER                                                                              | SYMBOL           | CONDITIONS                                                                           | MIN TYP               | MAX | UNITS |

|----------------------------------------------------------------------------------------|------------------|--------------------------------------------------------------------------------------|-----------------------|-----|-------|

| Tx Turn-Off Time<br>(to Standby Mode)                                                  |                  | From Tx enable falling edge                                                          | 0.1                   |     | μs    |

| Rx Turn-On Time<br>(from Standby Mode)                                                 |                  | Measured from Rx enable rising edge; signal settling to within 0.5dB of steady state | 2                     |     | μs    |

| Rx Turn-Off Time<br>(to Standby Mode)                                                  |                  | From Rx enable falling edge                                                          | 0.1                   |     | μs    |

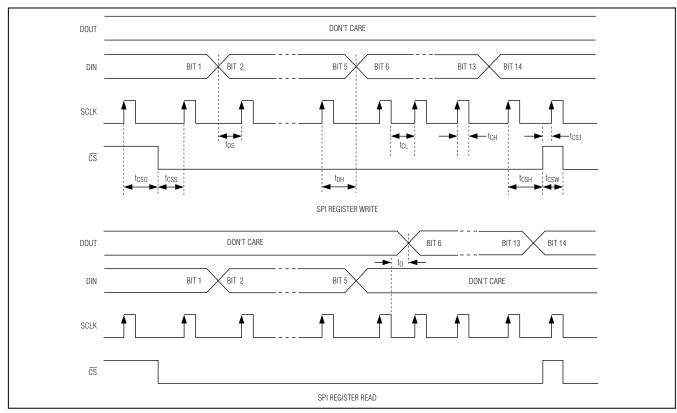

| 4-WIRE SERIAL-INTERFACE TIM                                                            | ING (See Fig     | ure 1)                                                                               |                       |     |       |

| SCLK Rising Edge to CS Falling Edge Wait Time                                          | tcso             |                                                                                      | 6                     |     | ns    |

| Falling Edge of CS to Rising Edge of First SCLK Time                                   | tcss             |                                                                                      | 6                     |     | ns    |

| DIN to SCLK Setup Time                                                                 | t <sub>DS</sub>  |                                                                                      | 6                     |     | ns    |

| DIN to SCLK Hold Time                                                                  | tDH              |                                                                                      | 6                     |     | ns    |

| SCLK Pulse-Width High                                                                  | tch              |                                                                                      | 6                     |     | ns    |

| SCLK Pulse-Width Low                                                                   | tcl              |                                                                                      | 6                     |     | ns    |

| Last Rising Edge of SCLK to<br>Rising Edge of CS or Clock to<br>Load Enable Setup Time | tCSH             |                                                                                      | 6                     |     | ns    |

| CS High Pulse Width                                                                    | t <sub>CSW</sub> |                                                                                      | 20                    |     | ns    |

| Time Between Rising Edge of CS and the Next Rising Edge of SCLK                        | tCS1             |                                                                                      | 6                     |     | ns    |

| Clock Frequency                                                                        | fCLK             |                                                                                      |                       | 45  | MHz   |

| Rise Time                                                                              | t <sub>R</sub>   |                                                                                      | f <sub>CLK</sub> / 10 |     | ns    |

| Fall Time                                                                              | tF               |                                                                                      | f <sub>CLK</sub> / 10 |     | ns    |

| SCLK Falling Edge to Valid DOUT                                                        | t <sub>D</sub>   |                                                                                      | 12.5                  |     | ns    |

Note 1: Min and max limits guaranteed by test above  $T_A = +25^{\circ}C$  and guaranteed by design and characterization at  $T_A = -40^{\circ}C$ . The power-on register settings are not production tested. Recommended register setting must be loaded after  $V_{CC}$  is supplied.

Note 2: Two tones at +25MHz and +39MHz offset with -35dBm/tone. Measure IM3 at 1MHz.

Note 3: Gain adjusted over max gain and max gain - 3dB. Optimally matched over given 200MHz band.

$f_{OFFSET} = 10MHz$

P<sub>JAMMER</sub> (dBm)

f<sub>OFFSET</sub> = 20MHz

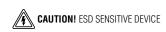

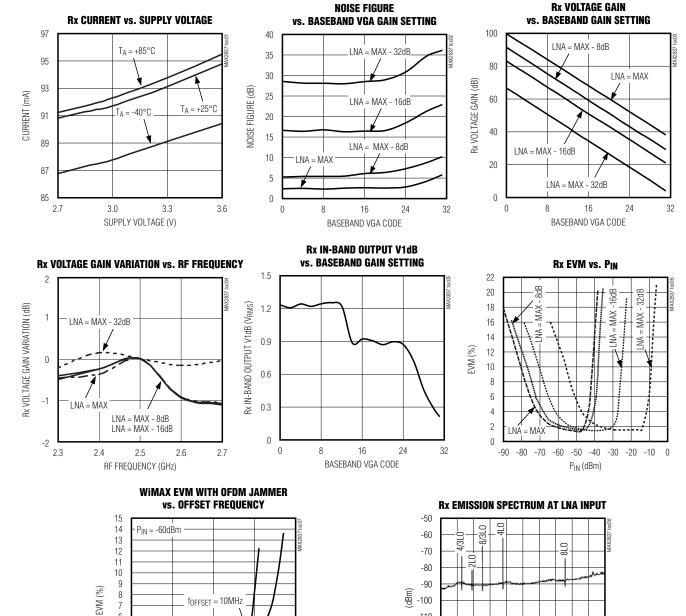

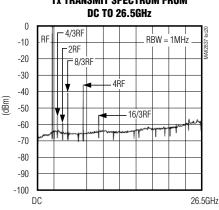

### Typical Operating Characteristics

(MAX2837 evaluation kit:  $V_{CC_{-}} = 2.8V$ ,  $f_{LO} = 2.5GHz$ , 10MHz channel 16E UL/DL WiMax signal,  $f_{REF} = 40MHz$ , ENABLE =  $\overline{\text{CS}}$  = high, RXHP = SCLK = DIN = low,  $T_A$  = +25°C, unless otherwise noted.)

MIXIM 10

-110

-120

-130

-140

-150 DC

MIN LNA GAIN

RBW = 300kHz

26.5GHz

6

5

### Typical Operating Characteristics (continued)

(MAX2837 evaluation kit:  $V_{CC}$  = 2.8V,  $f_{LO}$  = 2.5GHz, 10MHz channel 16E UL/DL WiMax signal,  $f_{REF}$  = 40MHz, ENABLE =  $\overline{CS}$  = high, RXHP = SCLK = DIN = low,  $T_A$  = +25°C, unless otherwise noted.)

MIXIM

### Typical Operating Characteristics (continued)

(MAX2837 evaluation kit:  $V_{CC}$  = 2.8V,  $f_{LO}$  = 2.5GHz, 10MHz channel 16E UL/DL WiMax signal,  $f_{REF}$  = 40MHz, ENABLE =  $\overline{CS}$  = high, RXHP = SCLK = DIN = low,  $T_A$  = +25°C, unless otherwise noted.)

12 \_\_\_\_\_\_ /I/XI/VI

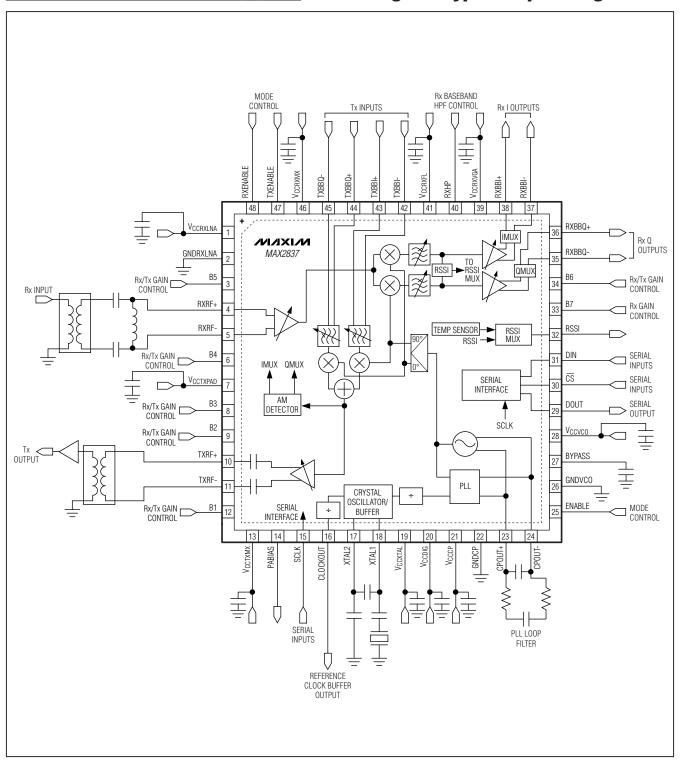

### **Block Diagram/Typical Operating Circuit**

MIXIM

### **Pin Description**

| PIN | NAME     | FUNCTION                                                                                                                      |

|-----|----------|-------------------------------------------------------------------------------------------------------------------------------|

| 1   | VCCRXLNA | LNA Supply Voltage. Bypass with a capacitor as close as possible to the pin.                                                  |

| 2   | GNDRXLNA | LNA Ground                                                                                                                    |

| 3   | B5       | Receiver and Transmitter Gain-Control Logic Input Bit 5                                                                       |

| 4   | RXRF+    | LNA Differential Inputs. Inputs are internally DC-coupled. An external shunt inductor and series                              |

| 5   | RXRF-    | capacitors match the inputs to $100\Omega$ differential.                                                                      |

| 6   | B4       | Receiver and Transmitter Gain-Control Logic Input Bit 4                                                                       |

| 7   | VCCTXPAD | Supply Voltage for Power-Amplifier Driver. Bypass with a capacitor as close as possible to the pin.                           |

| 8   | B3       | Receiver and Transmitter Gain-Control Logic Input Bit 3                                                                       |

| 9   | B2       | Receiver and Transmitter Gain-Control Logic Input Bit 2                                                                       |

| 10  | TXRF+    | Power-Amplifier Driver Differential Output. PA driver output is internally matched to a $100\Omega$                           |

| 11  | TXRF-    | differential. The pins have internal DC-blocking capacitors.                                                                  |

| 12  | B1       | Receiver and Transmitter Gain-Control Logic Input Bit 1                                                                       |

| 13  | VCCTXMX  | Transmitter Upconverter Supply Voltage. Bypass with a capacitor as close as possible to the pin.                              |

| 14  | PABIAS   | Transmit PA Bias DAC Output                                                                                                   |

| 15  | SCLK     | Serial-Clock Logic Input of 4-Wire Serial Interface (See Figure 1)                                                            |

| 16  | CLOCKOUT | Reference Clock Buffer Output                                                                                                 |

| 17  | XTAL2    | Crystal or Reference Clock Input. AC-couple a crystal or a reference clock to this analog input.                              |

| 18  | XTAL1    | Connection for Crystal-Oscillator Off-Chip Capacitors. When using an external reference clock input, leave XTAL1 unconnected. |

| 19  | VCCXTAL  | Crystal-Oscillator Supply Voltage. Bypass with a capacitor as close as possible to the pin.                                   |

| 20  | Vccdig   | Digital Circuit Supply Voltage. Bypass with a capacitor as close as possible to the pin.                                      |

| 21  | VCCCP    | PLL Charge-Pump Supply Voltage. Bypass with a capacitor as close as possible to the pin.                                      |

| 22  | GNDCP    | Charge-Pump Circuit Ground                                                                                                    |

| 23  | CPOUT+   | Differential Charge-Pump Output. Connect the frequency synthesizer's loop filter between CPOUT+                               |

| 24  | CPOUT-   | and CPOUT (See the Typical Operating Circuit.)                                                                                |

| 25  | ENABLE   | Operation Mode Logic Input. See Table 1 for operating modes.                                                                  |

| 26  | GNDVCO   | VCO Ground                                                                                                                    |

| 27  | BYPASS   | On-Chip VCO Regulator Output Bypass. Bypass with a 1µF capacitor to GND. Do not connect other circuitry to this point.        |

| 28  | Vccvco   | VCO Supply Voltage. Bypass with a capacitor as close as possible to the pin.                                                  |

| 29  | DOUT     | Data Logic Output of 4-Wire Serial Interface (See Figure 1)                                                                   |

| 30  | CS       | Chip-Select Logic Input of 4-Wire Serial Interface (See Figure 1)                                                             |

| 31  | DIN      | Data Logic Input of 4-Wire Serial Interface (See Figure 1)                                                                    |

| 32  | RSSI     | RSSI or Temperature Sensor Multiplexed Analog Output                                                                          |

| 33  | B7       | Receiver Gain-Control Logic Input Bit 7                                                                                       |

| 34  | B6       | Receiver and Transmitter Gain-Control Logic Input Bit 6                                                                       |

| 35  | RXBBQ-   | Receiver Baseband Q-Channel Differential Outputs. In Tx calibration mode, these pins are the                                  |

| 36  | RXBBQ+   | LO leakage and sideband detector outputs.                                                                                     |

| 37  | RXBBI-   | Receiver Baseband I-Channel Differential Outputs. In Tx calibration mode, these pins are the                                  |

| 38  | RXBBI+   | LO leakage and sideband detector outputs.                                                                                     |

| 39  | VCCRXVGA | Receiver VGA Supply Voltage                                                                                                   |

| 40  | RXHP     | Receiver Baseband AC-Coupling Highpass Corner Frequency Control Logic Input                                                   |

| 41  | VCCRXFL  | Receiver Baseband Filter Supply Voltage                                                                                       |

|     | *CORAFL  |                                                                                                                               |

### **Pin Description (continued)**

| PIN | NAME     | FUNCTION                                                                                                                                                                         |  |

|-----|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 42  | TXBBI-   | Transmitter Resolvend I Channel Differential Inputs                                                                                                                              |  |

| 43  | TXBBI+   | Transmitter Baseband I-Channel Differential Inputs                                                                                                                               |  |

| 44  | TXBBQ+   | Transmitter Baseband Q-Channel Differential Inputs                                                                                                                               |  |

| 45  | TXBBQ-   | Transmitter baseband Q-Orianner binerential inputs                                                                                                                               |  |

| 46  | VCCRXMX  | Receiver Downconverters Supply Voltage. Bypass with a capacitor as close as possible to the pin.                                                                                 |  |

| 47  | TXENABLE | Tx Mode Control Logic Input. See Table 1 for operating modes.                                                                                                                    |  |

| 48  | RXENABLE | Rx Mode Control Logic Input. See Table 1 for operating modes.                                                                                                                    |  |

| EP  | EP       | Exposed Paddle. Connect to the ground plane with multiple vias for proper operation and heat dissipation. Do not share with any other pin grounds and bypass capacitors' ground. |  |

#### **Table 1. Operating Mode Table**

|                   | LOGIC<br>PINS |          |          | REGISTER<br>SETTING |                | CIRCUIT<br>BLOCK STATES |                              |                     |                                |              |

|-------------------|---------------|----------|----------|---------------------|----------------|-------------------------|------------------------------|---------------------|--------------------------------|--------------|

| MODE              | ENABLE        | RXENABLE | TXENABLE | D1:<br>A4:A0 =      | :D0<br>= 10000 | Rx<br>PATH              | Tx<br>PATH                   | PLL, VCO,<br>LO GEN | CALIBRATION<br>SECTIONS<br>ON  | CLOCK<br>OUT |

| Clock-Out         | 1             | 0        | 0        | 0                   | 0              | Off                     | Off                          | Off                 | None                           | On           |

| Shutdown          | 0             | 0        | 0        | 0                   | Х              | Off                     | Off                          | Off                 | None                           | Off          |

| Standby           | 1             | 0        | 0        | 0                   | 1              | Off*                    | Off*                         | On                  | None                           | On           |

| Rx                | 1             | 1        | 0        | 0                   | 1              | On                      | Off                          | On                  | None                           | On           |

| Tx                | 1             | 0        | 1        | 0                   | 1              | Off                     | On                           | On                  | None                           | On           |

| Rx<br>Calibration | 1             | 1        | 0        | 1                   | 1              | On<br>(Except<br>LNA)   | Off (Except<br>Upconverters) | On                  | Tx Baseband<br>Buffer          | On           |

| Tx<br>Calibration | 1             | 0        | 1        | 1                   | 1              | Off                     | On<br>(Except PA<br>Driver)  | On                  | AM Detector,<br>Rx I/Q Buffers | On           |

<sup>\*</sup>Blocks of the transceiver can be selectively enabled through SPI.

### Detailed Description

#### **Modes of Operation**

The modes of operation for the MAX2837 are clock-out, shutdown, transmit, receive, transmitter calibration, and receiver calibration. See Table 1 for a summary of the modes of operation. The logic input pins—ENABLE (pin 25), TXENABLE (pin 47), and RXENABLE (pin 48)—control the various modes. When the parts are active, various blocks can be shut down individually through SPI.

#### Shutdown Mode

The MAX2837 features a low-power shutdown mode. Current drain is the minimum possible with the supply voltages applied. In shutdown mode, all circuit blocks are powered down, except the 4-wire serial bus and its internal programmable registers. If the supply voltage is applied, the registers are loaded and retained.

#### Standby Mode

The standby mode is used to enable the frequency synthesizer block while the rest of the device is powered down. In this mode, PLL, VCO, and LO generator are on, so that Tx or Rx modes can be quickly enabled from this mode. These and other blocks can be selectively enabled in this mode.

#### Receive (Rx) Mode

In receive mode, all Rx circuit blocks are powered on and active. Antenna signal is applied; RF is downconverted, filtered, and buffered at Rx BB I and Q outputs. The slow-charging Tx circuits are in a precharged "idle-off" state for fast Rx-to-Tx turnaround time.

#### Transmit (Tx) Mode

In transmit mode, all Tx circuit blocks are powered on. The external PA is powered on after a programmable

Figure 1. 4-Wire SPI Serial-Interface Timing Diagram

delay using the on-chip PA bias DAC. The slow-charging Rx circuits are in a precharged "idle-off" state for fast Tx-to-Rx turnaround time.

#### Clock-Out Only

In clock-out mode, the entire transceiver is off except the divided reference clock output on the CLKOUT pin and the clock divider, which remains on.

### **Programmable Registers** and 4-Wire SPI Interface

The MAX2837 includes 32 programmable 16-bit registers. The most significant bit (MSB) is the read/write selection bit. The next 5 bits are register address. The 10 least significant bits (LSBs) are register data. Register data is loaded through the 4-wire SPI/MICROWIRE™-compatible serial interface. Data at DIN is shifted in MSB first and is framed by  $\overline{\text{CS}}$ . When

CS is low, the clock is active, and input data is shifted at the rising edge of the clock. During the read mode, register data selected by address bits is shifted out to DOUT at the falling edges of the clock. At the CS rising edge, the 10-bit data bits are latched into the register selected by address bits. See Figure 1. The register values are preserved in shutdown mode as long as the power-supply voltage is maintained. However, every time the power-supply voltage is turned on, the registers are reset to the default values. Note that default register states are not guaranteed, and the user should always reprogram all registers after power-up.

MICROWIRE is a trademark of National Semiconductor Corp.

\_ /VIXI/VI

### **Pin Configuration**

\_\_\_Chip Information

PROCESS: SiGe BiCMOS

### \_Package Information

For the latest package outline information and land patterns, go to  ${\color{red} \underline{www.maxim-ic.com/packages}}.$

| PACKAGE TYPE | PACKAGE CODE | DOCUMENT NO. |  |  |

|--------------|--------------|--------------|--|--|

| 48 TQFN-EP   | T4866-2      | 21-0141      |  |  |

#### Revision History

| REVISION<br>NUMBER | REVISION<br>DATE | DESCRIPTION                                                                                 | PAGES<br>CHANGED |

|--------------------|------------------|---------------------------------------------------------------------------------------------|------------------|

| 0                  | 5/07             | Initial release                                                                             | _                |

| 1                  | 11/08            | Corrected SPI description in <i>Programmable Registers and 4-Wire SPI-Interface</i> section | 16               |

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.

18 \_\_\_\_\_\_Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600

© 2008 Maxim Integrated Products

is a registered trademark of Maxim Integrated Products, Inc.