## LM5045

# Full-Bridge PWM Controller with Integrated MOSFET Drivers

#### **General Description**

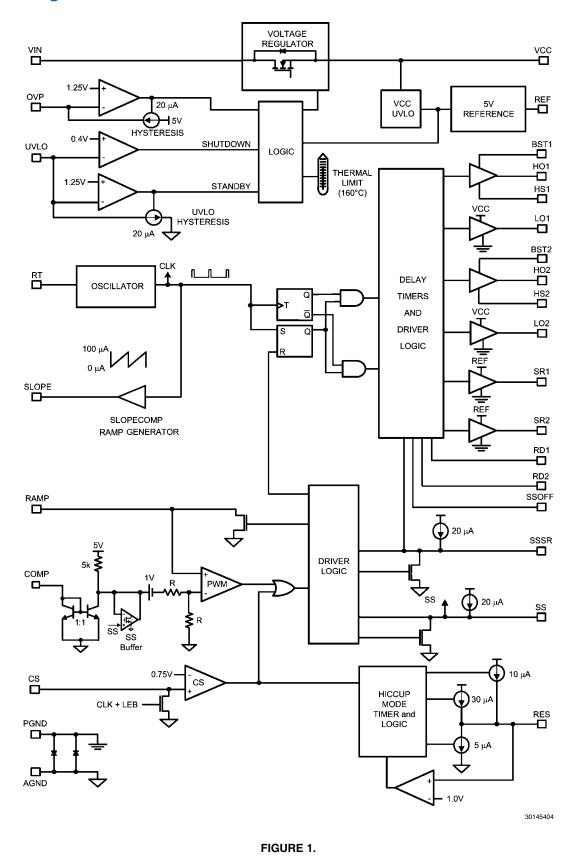

The LM5045 PWM controller contains all of the features necessary to implement Full-Bridge topology power converters using either current mode or voltage mode control. This device is intended to operate on the primary side of an isolated dc-dc converter with input voltage up to 100V. This highly integrated controller-driver provides dual 2A high and low side gate drivers for the four external brige MOSFETs plus control signals for the secondary side synchronous rectifier MOS-FETs. External resistors program the leading and trailing edge dead-time between the main and synchronous rectifier control signals. Intelligent startup of the synchronous rectifiers allows monotonic turn-on of the power converter even with pre-bias load conditions. Additional features include cycle-by-cycle current limiting, hiccup mode restart, programmable soft-start, synchronous rectifier soft-start and a 2 MHz capable oscillator with synchronization capability and thermal shutdown.

#### **Features**

- Highest Integration Controller for Small Form Factor, High Density Power Converters

- High Voltage Start-up Regulator

- Intelligent Sync Rectifier Start-up Allows Linear Turn-on into Pre-biased Loads

- Synchronous Rectifiers Disabled in UVLO mode and Hiccup Mode

- Two Independent, Programmable Synchronous Rectifier dead-time Adjustments

- Four High Current 2A Bridge Gate Drivers

- Wide-Bandwidth Opto-coupler Interface

- Configurable for either Current Mode or Voltage Mode Control

- Dual-mode Over-Current Protection

- Resistor Programmed 2MHz Oscillator

- Programmable Line UVLO and OVP

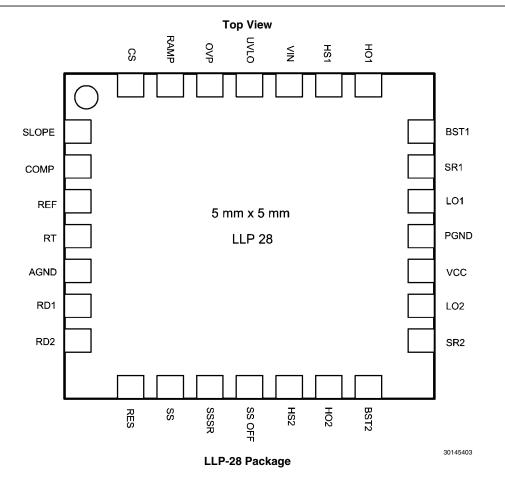

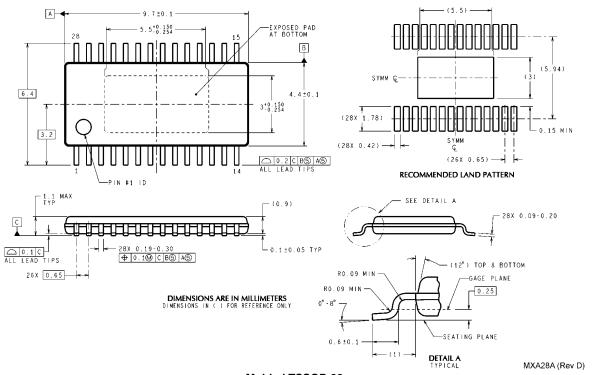

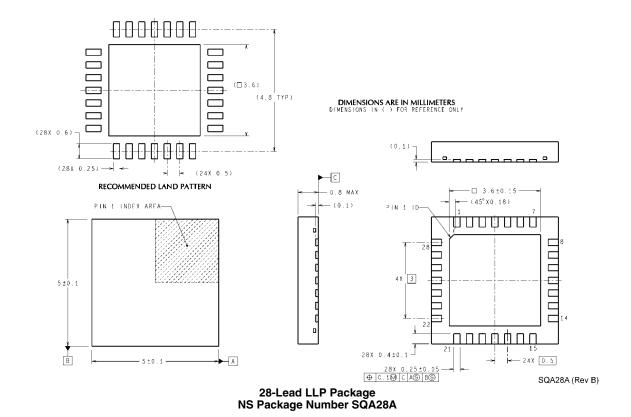

## **Packages**

- eTSSOP-28

- LLP-28 (5mm x 5mm)

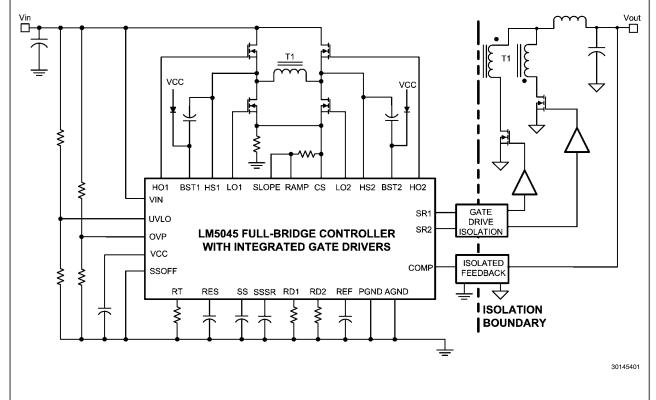

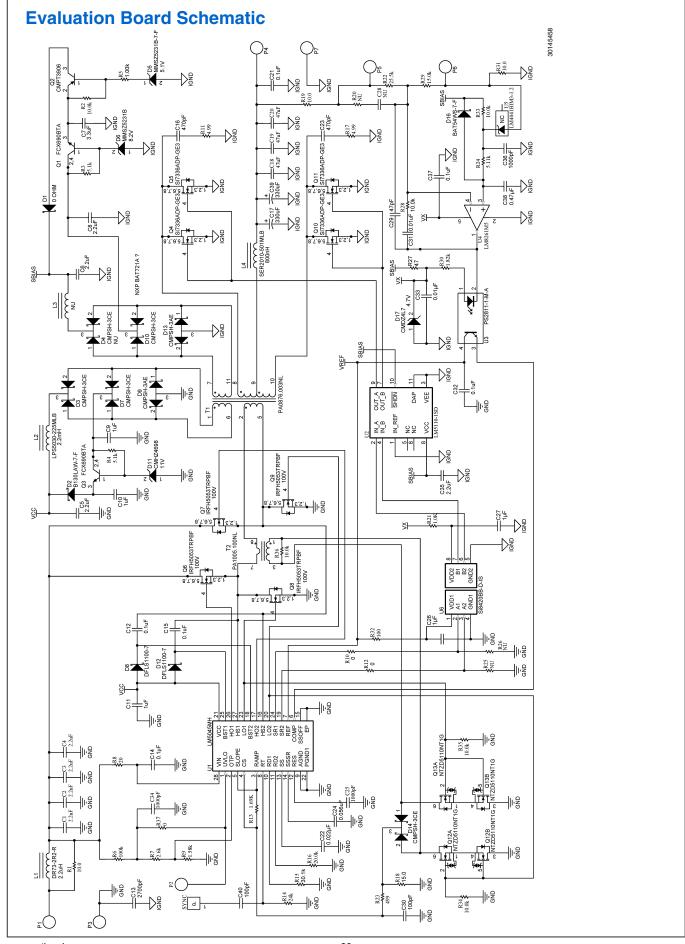

## Simplified Full-Bridge Power Converter

# **Connection Diagrams Top View** UVLO ( VIN OVP HS1 RAMP HO1 cs BST1 SR1 SLOPE COMP LO1 REF PGND TSSOP28 RT VCC AGND LO2 SR2 RD1 RD2 BST2 HO2 RES HS2 SS SSSR SS OFF 30145402 TSSOP28

# **Ordering Information**

| Order Number | Package Type | NSC Package Drawing | Supplied As                 |

|--------------|--------------|---------------------|-----------------------------|

| LM5045MH     | eTSSOP-28    | MXA28A              | Rail of 48 Units            |

| LM5045MHX    | eTSSOP-28    | MXA28A              | Tape and Reel of 2500 Units |

| LM5045SQ     | LLP-28       | SQA28A              | Available Soon              |

| LM5045SQX    | LLP-28       | SQA28A              | Available Soon              |

# **Pin Descriptions**

| TSSOP<br>Pin | LLP Pin | Name    | Description                | Application Information                                                                                                                                                                                                                                                                                                                                                     |

|--------------|---------|---------|----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

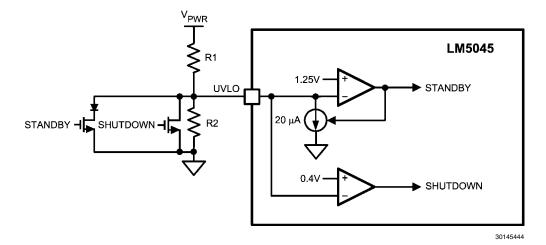

| 1            | 25      | UVLO    | Line Under-Voltage Lockout | An external voltage divider from the power source sets the shutdown and standby comparator levels. When UVLO reaches the 0.4V threshold the VCC and REF regulators are enabled. At the 1.25V threshold, the SS pin is released and the controller enters the active mode. Hysteresis is set by an internal current sink that pulls 20µA from the external resistor divider. |

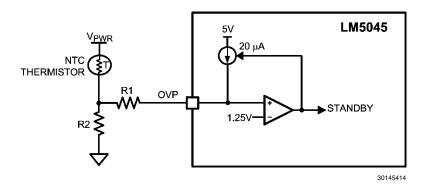

| 2            | 26      | OVP/OTP | Over Voltage Protection    | An external voltage divider from the input power supply sets the shutdown level during an over-voltage condition. Alternatively, an external NTC thermistor voltage divider can be used to set the shutdown temperature. The threshold is 1.25V. Hysteresis is set by an internal current that sources 20 µA of current into the external resistor divider.                 |

| TSSOP<br>Pin | LLP Pin | Name    | Description                                                | Application Information                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|--------------|---------|---------|------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3            | 27      | RAMP    | Input to PWM Comparator                                    | Modulation ramp for the PWM comparator. This ramp can be signal representative of the primary current (current mode) or proportional to the input voltage (feed-forward voltage mode) This pin is reset to GND at the end of every cycle.                                                                                                                                                                                                                                                                                            |

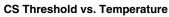

| 4            | 28      | CS      | Current Sense Input                                        | If CS exceeds 750mV the PWM output pulse will be terminat entering cycle-by-cycle current limit. An internal switch holds low for 40nS after either output switches high to blank leading edge transients.                                                                                                                                                                                                                                                                                                                           |

| 5            | 1       | SLOPE   | Slope Compensation Current                                 | A ramping current source from 0 to 100µA is provided for slo compensation in current mode control. This pin can be connect through an appropriate resistor to the CS pin to provide slope compensation. If slope compensation is not required, SLOPE must be tied to ground.                                                                                                                                                                                                                                                         |

| 6            | 2       | COMP    | Input to the Pulse Width Modulator                         | An external opto-coupler connected to the COMP pin source current into an internal NPN current mirror. The PWM duty countries at maximum with zero input current, while 1mA reduces the duty cycle to zero. The current mirror improves the frequency response by reducing the AC voltage across the opto-coupled                                                                                                                                                                                                                    |

| 7            | 3       | REF     | Output of a 5V reference                                   | Maximum output current is 15mA. Locally decouple with a 0. capacitor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

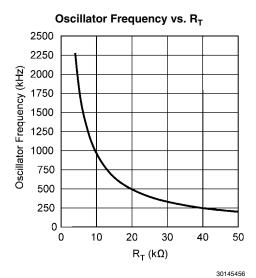

| 8            | 4       | RT/SYNC | Oscillator Frequency Control and Frequency Synchronization | The resistance connected between RT and AGND sets the oscillator frequency. Synchronization is achieved by AC coup a pulse to the RT/SYNC pin that raises the voltage at least 1 above the 2V nominal bias level.                                                                                                                                                                                                                                                                                                                    |

| 9            | 5       | AGND    | Analog Ground                                              | Connect directly to the Power Ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

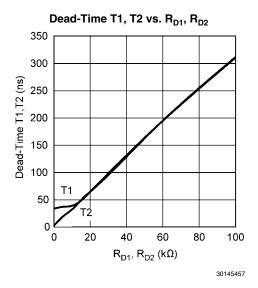

| 10           | 6       | RD1     | Synchronous Rectifier Leading<br>Edge Delay                | The resistance connected between RD1 and AGND sets the delay from the falling edge of SR1 or SR2 and the rising edg HO2/LO1 or HO1/LO2 respectively.                                                                                                                                                                                                                                                                                                                                                                                 |

| 11           | 7       | RD2     | Synchronous Rectifier Trailing<br>Edge Delay               | The resistance connected between RD2 and AGND sets the delay from the falling edge of HO1/LO2 or HO2/LO1 and the riedge of SR2 or SR1 respectively.                                                                                                                                                                                                                                                                                                                                                                                  |

| 12           | 8       | RES     | Restart Timer                                              | Whenever the CS pin exceeds the 750mV cycle-cycle currer limit threshold, 30µA current is sourced into the RES capacitor the remainder of the PWM cycle. If the RES capacitor voltage reaches 1.0V, the SS capacitor is discharged to disable the HO2, LO1, LO2 and SR1, SR2 outputs. The SS pin is held fountil the voltage on the RES capacitor has been ramped betw 2V and 4V eight times by 10µA charge and 5µA discharge currents. After the delay sequence, the SS capacitor is releat to initiate a normal start-up sequence. |

| 13           | 9       | SS      | Soft-Start Input                                           | An internal 20µA current source charges the SS pin during s up. The input to the PWM comparator gradually rises as the capacitor charges to steadily increase the PWM duty cycle. Pulling the SS pin to a voltage below 200mV stops PWM pu at HO1,2 and LO1,2 and turns off the synchronous rectifier F to a low state.                                                                                                                                                                                                              |

| 14           | 10      | SSSR    | Secondary Side Soft-Start                                  | An external capacitor and an internal 20μA current source set soft-start ramp for the synchronous rectifiers. The SSSR capacitor charge-up is enabled after the first output pulse an SS>2V and Icomp <800μA                                                                                                                                                                                                                                                                                                                         |

| 15           | 11      | SSOFF   | Soft-Stop Disable                                          | When SS OFF pin is connected to the AGND, the LM5045 s stops in the event of a VIN UVLO and Hiccup mode current condition. If the SSOFF pin is connected to REF pin, the control hard-stops on any fault condition. Refer Table 1 for more det                                                                                                                                                                                                                                                                                       |

| TSSOP<br>Pin | LLP Pin | Name     | Description                  | Application Information                                                                                                                                                                                                                                                                                                                               |

|--------------|---------|----------|------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 19           | 15      | SR2      | Synchronous Rectifier Driver | Control output for synchronous rectifier gate. Capable of peak sourcing 100mA and sinking 400mA.                                                                                                                                                                                                                                                      |

| 21           | 17      | VCC      | Output of Start-Up Regulator | The output voltage of the start-up regulator is initially regulated to 9.5V. Once the secondary side soft-start (SSSR pin) reaches 1V the VCC output is reduced to 7.7V. If an auxiliary winding raises the voltage on this pin above the regulation set-point, the interna start-up regulator will shutdown, thus reducing the IC power dissipation. |

| 22           | 18      | PGND     | Power Ground                 | Connect directly to Analog Ground                                                                                                                                                                                                                                                                                                                     |

| 23, 20       | 19, 16  | LO1, LO2 | Low Side Output Driver       | Alternating output of the PWM gate driver. Capable of 1.5A peak source and 2A peak sink current.                                                                                                                                                                                                                                                      |

| 24           | 20      | SR1      | Synchronous Rectifier Driver | Control output for synchronous rectifier gate. Capable of peak sourcing 100mA and sinking 400mA.                                                                                                                                                                                                                                                      |

| 25, 18       | 21, 14  | BST1,2   | Gate Drive Bootstrap         | Bootstrap capacitors connected between BST1,2 and SW1,2 provide bias supply for the high side HO1,2 gate drivers. Externa diodes are required between VCC and BST1,2 to charge the bootstrap capacitors when SW1,2 are low.                                                                                                                           |

| 26, 17       | 22, 13  | HO1,2    | High Side Output Driver      | High side PWM outputs capable of driving the upper MOSFET of the bridge with 1.5A peak source and 2A peak sink current.                                                                                                                                                                                                                               |

| 27, 16       | 23, 12  | HS1,2    | Switch Node                  | Common connection of the high side FET source, low side FET drain and transformer primary winding.                                                                                                                                                                                                                                                    |

| 28           | 24      | VIN      | Input Power Source           | Input to the Start-up Regulator. Operating input range is 14V to 100V. For power sources outside of this range, the LM5045 can be biased directly at VCC by an external regulator.                                                                                                                                                                    |

## **Absolute Maximum Ratings** (Note 1)

VIN to GND -0.3V to 105V HS to GND(*Note 4*) -5V to 105V BST1/BST2 to GND -0.3V to 116V

BST1/BST2 to HS1/HS2 -0.3V to 16V HO1/HO2 to HS1/HS2(*Note 2*) -0.3V to BST1/

BST2+0.3V

COMP -0.3V

COMP Input Current +10mA

All other inputs to GND(*Note 2*) -0.3 to REF+0.3V

ESD Rating HBM(*Note 3*) 2 kV

Storage Temperature Range -55°C to 150°C Junction Temperature 150°C

**Operating Ratings** (Note 1)

VIN Voltage 14V to 100V External Voltage Applied to VCC 10V to 14V Junction Temperature -40°C to +125°C

SLOPE -0.3V to 2V

**Electrical Characteristics** Limits in standard typeface are for  $T_J = 25^{\circ}$ C only; limits in **boldface** type apply the junction temperature range of **-40°C to +125°C.** Unless otherwise specified, the following conditions apply: VIN = 48V, RT =  $25k\Omega$ , RD1=RD2= $20k\Omega$ . No load on HO1, HO2, LO1, LO2, SR1, SR2, COMP=0V, UVLO=2.5V, OVP=0V, SSOFF=0V.

| Symbol                | Parameter                                   | Conditions                                                                | Min                       | Тур                       | Max  | Unit       |

|-----------------------|---------------------------------------------|---------------------------------------------------------------------------|---------------------------|---------------------------|------|------------|

| rtup Regu             | lator (VCC pin)                             |                                                                           |                           | -                         |      |            |

| V <sub>CC1</sub>      | VCC voltage                                 | I <sub>CC</sub> = 10mA (SSSR<1V)                                          | 9.3                       | 9.6                       | 9.9  | V          |

| V <sub>CC2</sub>      | VCC voltage                                 | I <sub>CC</sub> = 10mA (SSSR>1V)                                          | 7.5                       | 7.8                       | 8.1  | V          |

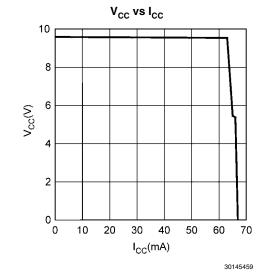

| I <sub>CC(Lim)</sub>  | VCC current limit                           | V <sub>CC</sub> = 6V                                                      | 52                        | 70                        |      | mA         |

| I <sub>CC(ext)</sub>  | VCC supply current                          | Supply current into VCC from an externally applied source. $V_{CC} = 10V$ |                           | 4.6                       |      | mA         |

|                       | VCC load regulation                         | I <sub>CC</sub> from 0 to 50 mA                                           |                           | 35                        |      | mV         |

| V <sub>CC(UV)</sub>   | VCC under-voltage threshold                 | Positive going VCC                                                        | V <sub>CC1</sub> -<br>0.2 | V <sub>CC1</sub> -<br>0.1 |      | V          |

|                       | VCC under-voltage threshold                 | Negative going VCC                                                        | 5.9                       | 6.3                       | 6.7  | V          |

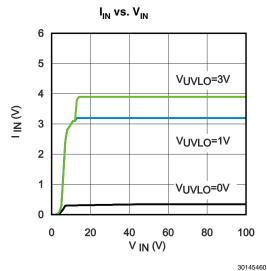

| I <sub>IN</sub>       | VIN operating current                       |                                                                           |                           | 4                         |      | mA         |

|                       | VIN shutdown current                        | V <sub>IN</sub> =20V, V <sub>UVLO</sub> =0V                               |                           | 300                       | 520  | μΑ         |

|                       |                                             | V <sub>VIN</sub> =100V, V <sub>UVLO</sub> =0V                             |                           | 350                       | 550  | μΑ         |

|                       | VIN start-up regulator leakage              | V <sub>CC</sub> =10V                                                      |                           | 160                       |      | μΑ         |

| Itage Refe            | rence Regulator (REF pin)                   |                                                                           |                           | •                         |      |            |

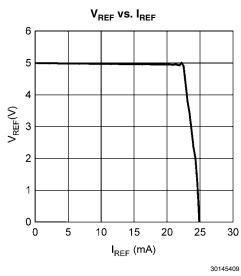

| V <sub>REF</sub>      | REF Voltage                                 | I <sub>REF</sub> = 0mA                                                    | 4.85                      | 5                         | 5.15 | V          |

|                       | REF voltage regulation                      | I <sub>REF</sub> = 0 to 10mA                                              |                           | 25                        | 50   | m۱         |

| I <sub>REF(Lim)</sub> | REF current limit                           | V <sub>REF</sub> = 4.5V                                                   | 15                        | 20                        |      | m <i>A</i> |

| V <sub>REFUV</sub>    | V <sub>REF</sub> under-voltage threshold    | Positive going V <sub>REF</sub>                                           | 4.3                       | 4.5                       | 4.7  | V          |

|                       | Hysteresis                                  |                                                                           |                           | 0.25                      |      | V          |

| der-Voltag            | e Lock Out and shutdown (UVLO p             | in)                                                                       |                           |                           |      |            |

| V <sub>UVLO</sub>     | Under-voltage threshold                     |                                                                           | 1.18                      | 1.25                      | 1.32 | V          |

| I <sub>UVLO</sub>     | Hysteresis current                          | UVLO pin sinking current when V <sub>UVLO</sub> <1.25V                    | 16                        | 20                        | 24   | μΑ         |

|                       | Under-voltage standby enable threshold      | UVLO voltage rising                                                       | 0.32                      | 0.4                       | 0.48 | V          |

|                       | Hysteresis                                  |                                                                           |                           | 0.05                      |      | V          |

| V <sub>OVP</sub>      | OVP shutdown threshold                      | OVP rising                                                                | 1.18                      | 1.25                      | 1.32 | V          |

|                       | OVP hysteresis current                      | OVP sources current when OVP>1.25V                                        | 16                        | 20                        | 24   | μΑ         |

| ft-Start (SS          | S Pin)                                      |                                                                           |                           |                           |      |            |

| I <sub>ss</sub>       | SS charge current                           | V <sub>SS</sub> = 0V                                                      | 16                        | 20                        | 24   | μΑ         |

|                       | SS threshold for SSSR charge current enable | I <sub>COMP</sub> <800μA                                                  | 1.93                      | 2.0                       | 2.20 | V          |

|                       | SS output low voltage                       | Sinking 100μA                                                             |                           | 40                        |      | m۷         |

|                       | SS threshold to disable switching           |                                                                           |                           | 200                       |      | m۷         |

| Symbol                 | Parameter                                           | Conditions                                    | Min   | Тур   | Max      | Units |

|------------------------|-----------------------------------------------------|-----------------------------------------------|-------|-------|----------|-------|

| I <sub>SSSR</sub>      | SSSR charge current                                 | V <sub>SS</sub> >2V, I <sub>COMP</sub> <800μA | 16    | 20    | 24       | μΑ    |

| I <sub>SSSR-DIS1</sub> | SSSR discharge current 1                            | V <sub>UVLO</sub> <1.25V                      | 54    | 65    | 75       | μA    |

| I <sub>SSSR-DIS2</sub> | SSSR discharge current 2                            | V <sub>RES</sub> >1V                          | 109   | 125   | 147      | μΑ    |

|                        | SSSR output low voltage                             | Sinking 100µA                                 |       | 50    |          | mV    |

|                        | SSSR threshold to enable SR1/SR2                    |                                               |       | 1.2   |          | V     |

| urrent Sens            | e Input (CS Pin)                                    |                                               | •     | •     |          |       |

| V <sub>CS</sub>        | Current limit threshold                             |                                               | 0.710 | 0.750 | 0.785    | ٧     |

|                        | CS delay to output                                  |                                               |       | 65    |          | ns    |

|                        | CS leading edge blanking                            |                                               |       | 50    |          | ns    |

| R <sub>CS</sub>        | CS sink impedance (clocked)                         | Internal FET sink impedance                   |       | 18    | 45       | Ω     |

|                        | able (SS OFF Pin)                                   |                                               | •     |       | Į        |       |

| V <sub>IH(min)</sub>   | SSOFF Input-threshold                               |                                               |       | 2.8   |          | ٧     |

| ()                     | SSOFF pull down resistance                          |                                               |       | 200   |          | kΩ    |

| urrent Limit           | Restart (RES Pin)                                   | I .                                           |       |       |          |       |

| R <sub>RES</sub>       | RES pull-down resistance                            | Termination of hiccup timer                   |       | 37    |          | Ω     |

| V <sub>RES</sub>       | RES hiccup threshold                                | ·                                             |       | 1     |          | V     |

| nEo                    | RES upper counter threshold                         |                                               |       | 4     |          | V     |

|                        | RES lower counter threshold                         |                                               |       | 2     |          | V     |

| I <sub>RES-SRC1</sub>  | Charge current source 1                             | V <sub>RES</sub> <1V,V <sub>CS</sub> >750mV   |       | 30    |          | μA    |

| I <sub>RES-SRC2</sub>  | Charge current source 2                             | 1V <v<sub>RES&lt;4V</v<sub>                   |       | 10    |          | μA    |

| I <sub>RES-DIS2</sub>  | Discharge current source 1                          | V <sub>CS</sub> <750mV                        |       | 5     |          | μA    |

|                        | Discharge current source 2                          | 2V <v<sub>RES&lt;4V</v<sub>                   |       | 5     |          | μA    |

| RES-DIS2               | Ratio of time in hiccup mode to time                |                                               |       | 147   |          | μ, ,  |

|                        | in current limit                                    | RES TV, Flictup Counter                       |       | 147   |          |       |

| oltage Feed            | -Forward (RAMP Pin)                                 |                                               |       |       | <u> </u> |       |

| <u> </u>               | RAMP sink impedance (Clocked)                       |                                               |       | 5.5   | 20       | Ω     |

| Scillator (R1          |                                                     |                                               |       |       | <u> </u> |       |

| F <sub>SW1</sub>       | Frequency (LO1, half oscillator frequency)          | $R_T = 25 \text{ k}\Omega$                    | 185   | 200   | 215      | kHz   |

| F <sub>SW2</sub>       | Frequency (LO1, half oscillator frequency)          | $R_T = 10 \text{ k}\Omega$                    | 420   | 480   | 540      | kHz   |

|                        | DC level                                            |                                               |       | 2.0   |          | V     |

|                        | RT sync threshold                                   |                                               | 2.8   | 3     | 3.3      | V     |

| Synchronous            | Rectifier Timing Control (RD1 & RD                  | 2 Pins)                                       |       |       |          |       |

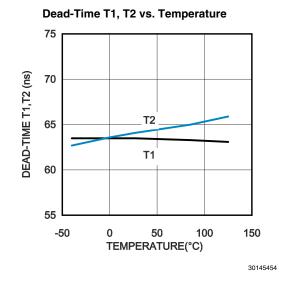

| T1                     | SR trailing edge delay SR turn-off to HO&LO both on | R <sub>D1</sub> =20 kΩ                        | 45    | 65    | 90       | ns    |

|                        |                                                     | R <sub>D1</sub> =100 kΩ                       | 232   | 300   | 388      | ns    |

| T2                     | SR leading edge HO or LO turn-off to SR turn-on     | $R_{D2}$ =20 k $\Omega$                       | 43    | 65    | 90       | ns    |

|                        |                                                     | R <sub>D2</sub> =100 kΩ                       | 227   | 300   | 384      | ns    |

| Symbol              | Parameter                                   | Conditions                                                  | Min  | Тур  | Max   | Units |

|---------------------|---------------------------------------------|-------------------------------------------------------------|------|------|-------|-------|

| Comp Pin            |                                             |                                                             |      |      | -     |       |

| V <sub>PWM-OS</sub> | COMP current to RAMP offset                 | V <sub>RAMP</sub> =0V                                       | 680  | 800  | 940   | μA    |

| V <sub>SS-OS</sub>  | SS to RAMP offset                           | V <sub>RAMP</sub> =0V                                       | 0.78 | 1.0  | 1.22  | V     |

|                     | COMP current to RAMP gain                   | ΔRAMP/ΔI <sub>COMP</sub>                                    |      | 2400 |       | Ω     |

|                     | SS to RAMP gain                             | ΔSS/ΔRAMP                                                   |      | 0.5  |       |       |

|                     | COMP current for SSSR charge current enable | V <sub>SS</sub> > 2V                                        | 690  | 800  | 915   | μA    |

|                     | COMP to output delay                        |                                                             |      | 120  |       | ns    |

|                     | Minimum duty cycle                          | I <sub>COMP</sub> = 1mA                                     |      |      | 0     | %     |

| Slope Compe         | ensation (SLOPE Pin)                        | Com                                                         |      |      |       | l     |

| I <sub>SLOPE</sub>  | Slope compensation current ramp             | Peak of RAMP current                                        |      | 100  | 1     | μA    |

| BOOST (BST          | Pin)                                        |                                                             |      |      |       |       |

| V <sub>Bst uv</sub> | BST under-voltage threshold                 | V <sub>BST</sub> -V <sub>HS</sub> rising                    | 3.8  | 4.7  | 5.6   | V     |

| Dot av              | Hysteresis                                  | 20                                                          |      | 0.5  |       | V     |

| HO1, HO2, LO        | O1, LO2 Gate Drivers                        |                                                             |      |      |       |       |

| V <sub>OL</sub>     | Low-state output voltage                    | I <sub>HO/LO</sub> = 100mA                                  |      | 0.16 | 0.32  | V     |

| V <sub>OH</sub>     | High-state output voltage                   | I <sub>HO/LO</sub> = 100mA                                  |      | 0.27 | 0.495 | V     |

| 311                 |                                             | $V_{OHL} = V_{CC} - V_{LO}$<br>$V_{OHH} = V_{BST} - V_{HO}$ |      |      |       |       |

|                     | Rise Time                                   | C-load = 1000pF                                             |      | 16   |       | ns    |

|                     | Fall Time                                   | C-load = 1000pF                                             |      | 11   |       | ns    |

| I <sub>OHL</sub>    | Peak Source Current                         | $V_{HO/LO} = 0V$                                            |      | 1.5  | -     | Α     |

| I <sub>OLL</sub>    | Peak Sink Current                           | $V_{HO/LO} = V_{CC}$                                        |      | 2    | -     | Α     |

| SR1, SR2 Ga         | te Drivers                                  | 1.0,20                                                      | !    |      |       |       |

| V <sub>OL</sub>     | Low-state output voltage                    | I <sub>SR1/SR2</sub> = 10mA                                 |      | 0.05 | 0.1   | V     |

| V <sub>OH</sub>     | High-state output voltage                   | $I_{SR1/SR2} = 10mA,$ $V_{OH} = V_{REF} - V_{SR}$           |      | 0.17 | 0.28  | V     |

|                     | Rise Time                                   | C-load = 1000pF                                             |      | 60   |       | ns    |

|                     | Fall Time                                   | C-load = 1000pF                                             |      | 20   |       | ns    |

| I <sub>OHL</sub>    | Peak Source Current                         | V <sub>SR</sub> = 0V                                        |      | 0.1  | -     | Α     |

| I <sub>OLL</sub>    | Peak Sink Current                           | V <sub>SR</sub> = V <sub>REF</sub>                          |      | 0.4  | -     | Α     |

| Thermal             | -                                           | -                                                           | 1    | 1    |       |       |

| TSD                 | Thermal Shutdown Temp                       |                                                             |      | 160  |       | °C    |

|                     | Thermal Shutdown Hysteresis                 |                                                             |      | 25   |       | °C    |

| RJA                 | Junction to Ambient(Note 5)                 | eTSSOP - 28/LLP-28                                          |      | 40   |       | °C/W  |

| RJC                 | Junction to Case                            |                                                             |      | 4    |       | °C/W  |

**Note 1:** Absolute Maximum Ratings are limits beyond which damage to the device may occur. Operating Ratings are conditions under which operation of the device is intended to be functional. For guaranteed specifications and test conditions, see the Electrical Characteristics.

**Note 2:** These pins are output pins and as such should not be connected to an external voltage source. The voltage range listed is the limits the internal circuitry is designed to reliably tolerate in the application circuit.

Note 3: The human body model is a 100pF capacitor discharged through a 1.5k $\Omega$  resistor into each pin.

Note 4: The negative HS voltage must never be more negative than VCC-16V. For example, if VCC=12V, the negative transients at HS must not exceed -4V.

Note 5: 4 layer standard thermal test board. Cu thickness of layers (2oz, 1oz, 1oz, 2oz).

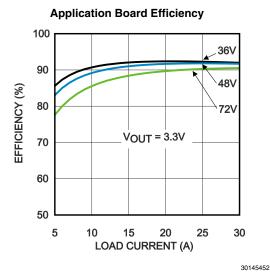

# **Typical Performance Characteristics**

www.national.com

10

## **Block Diagram**

### **Functional Description**

The LM5045 PWM controller contains all of the features necessary to implement a Full-Bridge topology power converter using either current mode or voltage mode control. This device is intended to operate on the primary side of an isolated dc-dc converter with input voltage up to 100V. This highly integrated controller-driver provides dual 2A high and low side gate drivers for the four external bridge MOSFETs plus control signals for secondary side synchronous rectifiers. External resistors program the leading and trailing edge dead-time between the main and synchronous rectifier control signals. Intelligent startup of synchronous rectifier allows turn-on of the power converter into the pre-bias loads. Cycle-by-cycle current limit protects the power components from load transients while hiccup mode protection limits average power dissipation during extended overload conditions. Additional features include programmable soft-start, soft-start of the synchronous rectifiers, and a 2 MHz capable oscillator with synchronization capability and thermal shutdown.

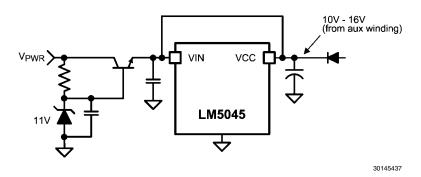

### **High-Voltage Start-Up Regulator**

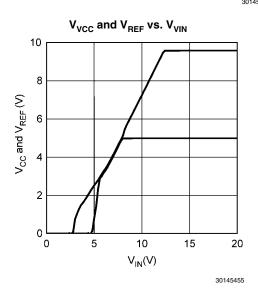

The LM5045 contains an internal high voltage start-up regulator that allows the input pin (VIN) to be connected directly to the supply voltage over a wide range from 14V to 100V. The input can withstand transients up to 105V. When the UV-LO pin potential is greater than 0.4V, the VCC regulator is enabled to charge an external capacitor connected to the VCC pin. The VCC regulator provides power to the voltage reference (REF) and the gate drivers (HO1/HO2 and LO1/ LO2). When the voltage on the VCC pin exceeds its Under Voltage (UV) threshold, the internal voltage reference (REF) reaches its regulation set point of 5V and the UVLO voltage is greater than 1.25V, the soft-start capacitor is released and normal operation begins. The regulator output at VCC is internally current limited. The value of the VCC capacitor depends on the total system design, and its start-up characteristics. The recommended range of values for the VCC capacitor is  $0.47\mu F$  to  $10\mu F$ .

The internal power dissipation of the LM5045 can be reduced by powering VCC from an external supply. The output voltage of the VCC regulator is initially regulated to 9.5V. After the synchronous rectifiers are engaged (which is approximately when the output voltage in within regulation), the VCC voltage is reduced to 7.7V. In typical applications, an auxiliary transformer winding is connected through a diode to the VCC pin. This winding must raise the VCC voltage above 8V to shut off the internal start-up regulator. Powering VCC from an auxiliary winding improves efficiency while reducing the controller's power dissipation. The VCC UV circuit will still function in this mode, requiring that VCC never falls below its UV threshold during the start-up sequence. The VCC regulator series pass transistor includes a diode between VCC and VIN that should not be forward biased in normal operation. Therefore, the auxiliary VCC voltage should never exceed the VIN voltage.

An external DC bias voltage can be used instead of the internal regulator by connecting the external bias voltage to both the VCC and the VIN pins. This implementation is shown in the Applications Information section. The external bias must be greater than 10V and less than the VCC maximum voltage rating of 14V.

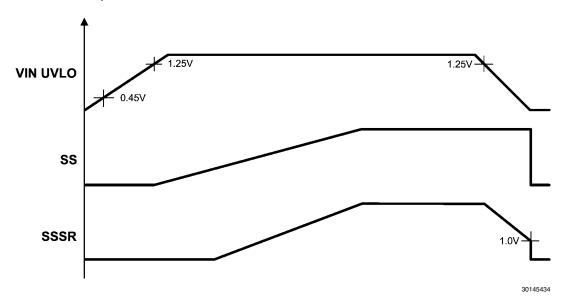

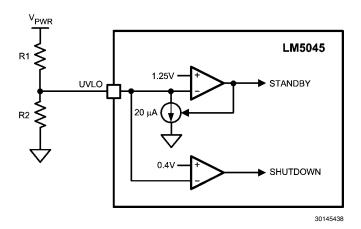

## **Line Under-Voltage Detector**

The LM5045 contains a dual level Under-Voltage Lockout (UVLO) circuit. When the UVLO pin voltage is below 0.4V, the

controller is in a low current shutdown mode. When the UVLO pin voltage is greater than 0.4V but less than 1.25V, the controller is in standby mode. In standby mode the VCC and REF bias regulators are active while the controller outputs are disabled. When the VCC and REF outputs exceed their respective under-voltage thresholds and the UVLO pin voltage is greater than 1.25V, the soft-start capacitor is released and the normal operation begins. An external set-point voltage divider from VIN to GND can be used to set the minimum operating voltage of the converter. The divider must be designed such that the voltage at the UVLO pin will be greater than 1.25V when VIN enters the desired operating range. UVLO hysteresis is accomplished with an internal 20µA current sink that is switched on or off into the impedance of the set-point divider. When the UVLO threshold is exceeded, the current sink is deactivated to guickly raise the voltage at the UVLO pin. When the UVLO pin voltage falls below the 1.25V threshold, the current sink is enabled causing the voltage at the UVLO pin to quickly fall. The hysteresis of the 0.4V shutdown comparator is internally fixed at 50mV.

The UVLO pin can also be used to implement various remote enable / disable functions. Turning off the converter by forcing the UVLO pin to standby condition (0.4V < UVLO < 1.25V) provides a controlled soft-stop. Refer to the Soft Stop section for more details.

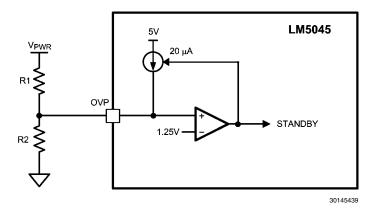

## **Over Voltage Protection**

An external voltage divider can be used to set either an over voltage or an over temperature protection. During an OVP condition, the SS and SSSR capacitors are discharged and all the outputs are disabled. The divider must be designed such that the voltage at the OVP pin is greater than 1.25V when over voltage/temperature condition exists. Hysteresis is accomplished with an internal 20µA current source. When the OVP pin voltage exceeds 1.25V, the 20µA current source is activated to quickly raise the voltage at the OVP pin. When the OVP pin voltage falls below the 1.25V threshold, the current source is deactivated causing the voltage at the OVP to quickly fall. Refer to the Applications Information section for more details.

#### Reference

The REF pin is the output of a 5V linear regulator that can be used to bias an opto-coupler transistor and external house-keeping circuits. The regulator output is internally current limited to 15mA. The REF pin needs to be locally decoupled with a ceramic capacitor, the recommended range of values are from  $0.1\mu\text{F}$  to  $10\mu\text{F}$

## **Oscillator, Sync Input**

The LM5045 oscillator frequency is set by a resistor connected between the RT pin and AGND. The RT resistor should be located very close to the device. To set a desired oscillator frequency (F<sub>OSC</sub>), the necessary value of RT resistor can be calculated from the following equation:

$$R_T = \frac{1}{F_{OSC} \times 1 \times 10^{10}}$$

For example, if the desired oscillator frequency is 400 kHz i.e. each phase (LO1 or LO2) at 200 kHz, the value of  $R_{T}$  will be  $25k\Omega.$  If the LM5045 is to be synchronized to an external clock, that signal must be coupled into the RT pin through a 100pF capacitor. The RT pin voltage is nominally regulated

at 2.0V and the external pulse amplitude should lift the pin to between 3.5V and 5.0V on the low-to-high transition. The synchronization pulse width should be between 15 and 200ns. The RT resistor is always required, whether the oscillator is free running or externally synchronized and the SYNC frequency must be equal to, or greater than the frequency set by the RT resistor. When syncing to an external clock, it is recommended to add slope compensation by connecting an appropriate resistor from the VCC pin to the CS pin. Also disable the SLOPE pin by grounding it.

### **Cycle-by-Cycle Current Limit**

The CS pin is to be driven by a signal representative of the transformer's primary current. If the voltage on the CS pin exceeds 0.75V, the current sense comparator immediately terminates the PWM cycle. A small RC filter connected to the CS pin and located near the controller is recommended to suppress noise. An internal  $18\Omega$  MOSFET discharges the external current sense filter capacitor at the conclusion of every cycle. The discharge MOSFET remains on for an additional 40ns after the start of a new PWM cycle to blank leading edge spikes. The current sense comparator is very fast and may respond to short duration noise pulses. Layout is critical for the current sense filter and the sense resistor. The capacitor associated with CS filter must be placed very close to the device and connected directly to the CS and AGND pins. If a current sense transformer is used, both the leads of the transformer secondary should be routed to the filter network, which should be located close to the IC. When designing with a current sense resistor, all of the noise sensitive low power ground connections should be connected together near the AGND pin, and a single connection should be made to the power ground (sense resistor ground point).

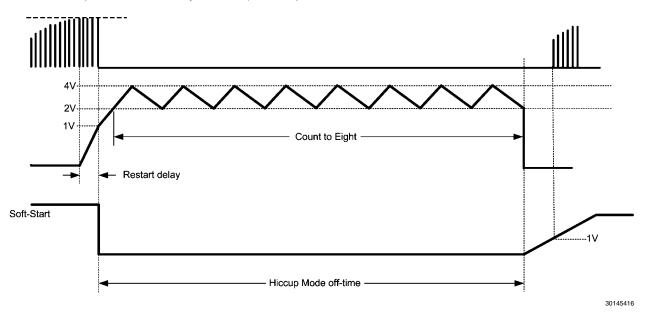

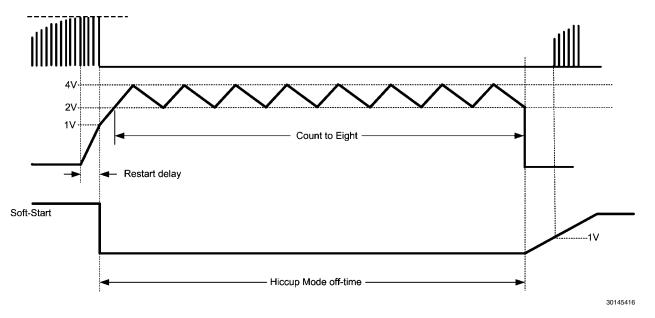

### **Hiccup Mode**

The LM5045 provides a current limit restart timer to disable the controller outputs and force a delayed restart (i.e. Hiccup mode) if a current limit condition is repeatedly sensed. The number of cycle-by-cycle current limit events required to trigger the restart is programmed by the external capacitor at the RES pin. During each PWM cycle, the LM5045 either sources or sinks current from the RES capacitor. If current limit is detected, the  $5\mu A$  current sink is disabled and a  $30\mu A$  current source is enabled. If the RES voltage reaches the 1.0V threshold, the following restart sequence occurs, as shown in Figure 2:

- The SS and SSSR capacitors are fully discharged

- The 30μA current source is turned-off and the 10μA current source is turned-on.

- Once the voltage at the RES pin reaches 4.0V the 10μA current source is turned-off and a 5μA current sink is turned-on, ramping the voltage on the RES capacitor down to 2.0V.

- Once RES capacitor reaches 2.0V, threshold, the 10μA current source is turned-on again. The RES capacitor voltage is ramped between 4.0V and 2.0V eight times.

- When the counter reaches eight, the RES pin voltage is pulled low and the soft-start capacitor is released to begin a soft-start sequence. The SS capacitor voltage slowly increases. When the SS voltage reaches 1.0V, the PWM comparator will produce the first narrow pulse.

- If the overload condition persists after restart, cycle-bycycle current limiting will begin to increase the voltage on the RES capacitor again, repeating the hiccup mode sequence.

- If the overload condition no longer exists after restart, the RES pin will be held at ground by the 5µA current sink and the normal operation resumes.

The hiccup mode function can be completely disabled by connecting the RES pin to the AGND pin. In this configuration the cycle-by-cycle protection will limit the maximum output current indefinitely, no hiccup restart sequences will occur.

FIGURE 2. Hiccup Mode Delay and Soft-Start Timing Diagram

#### **PWM Comparator**

The LM5045 pulse width modulator (PWM) comparator is a three input device, it compares the signal at the RAMP pin to the loop error signal or the soft-start, whichever is lower, to control the duty cycle. This comparator is optimized for speed in order to achieve minimum controllable duty cycles. The loop error signal is received from the external feedback and isolation circuit in the form of a control current into the COMP pin. The COMP pin current is internally mirrored by a matching pair of NPN transistors which sink current through a  $5k\Omega$  resistor connected to the 5V reference. The resulting control voltage passes through a 1V offset, followed by a 2:1 resistor divider before being applied to the PWM comparator.

An opto-coupler detector can be connected between the REF pin and the COMP pin. Because the COMP pin is controlled by a current input, the potential difference across the opto-coupler detector is nearly constant. The bandwidth limiting phase delay which is normally introduced by the significant capacitance of the opto-coupler is thereby greatly reduced. Higher loop bandwidths can be realized since the bandwidth limiting pole associated with the opto-coupler is now at a much higher frequency. The PWM comparator polarity is configured such that with no current flowing into the COMP pin, the controller produces maximum duty cycle.

#### **RAMP Pin**

The voltage at the RAMP pin provides the modulation ramp for the PWM comparator. The PWM comparator compares the modulation ramp signal at the RAMP pin to the loop error signal to control the duty cycle. The modulation ramp signal can be implemented either as a ramp proportional to the input voltage, known as feed-forward voltage mode control, or as a ramp proportional to the primary current, known as current mode control. The RAMP pin is reset by an internal MOSFET with an  $R_{\rm DS(ON)}$  of  $5.5\Omega$  at the conclusion of each PWM cycle. The ability to configure the RAMP pin for either voltage mode or current mode allows the controller to be implemented for the optimum control method depending upon the design con-

straints. Refer to the Applications Information section for more details on configuring the RAMP pin for feed-forward voltage mode control and peak current mode control.

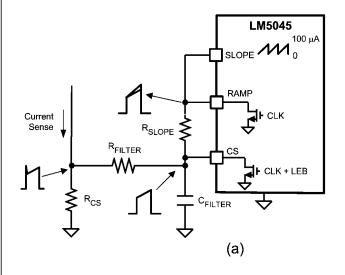

### **Slope Pin**

For duty cycles greater than 50% (25% for each phase), peak current mode control is subject to sub-harmonic oscillation. Sub-harmonic oscillation is normally characterized by observing alternating wide and narrow duty cycles. This can be eliminated by adding an artificial ramp, known as slope compensation, to the modulating signal at the RAMP pin. The SLOPE pin provides a current source ramping from 0 to  $100\mu\text{A}$ , at the frequency set by the RT resistor, for slope compensation. The ramping current source at the SLOPE pin can be utilized in a couple of different ways to add slope compensation to the RAMP signal:

- 1) As shown in Figure 3(a), the SLOPE and RAMP pins can be connected together through an appropriate resistor to the CS pin. This configuration will inject current sense signal plus slope compensation to the RAMP pin but CS pin will not see any slope compensation. Therefore, in this scheme slope compensation will not affect the current limit.

- 2) In a second configuration, as shown in Figure 3(b), the SLOPE, RAMP and CS pins can be tied together. In this configuration the ramping current source from the SLOPE pin will flow through the filter resistor and filter capacitor, therefore both the CS pin and the RAMP pin will see the current sense signal plus the slope compensation ramp. In this scheme, the current limit is compensated by the slope compensation and the current limit onset point will vary.

If the slope compensation is not required for e.g. in feed-forward voltage mode control, the SLOPE pin must be connected to the AGND pin. When the RT pin is synched to an external clock, it is recommended to disable the SLOPE pin and add slope compensation externally by connecting an appropriate resistor from the VCC pin to the CS pin. Please refer to the Applications Information section for more details.

30145451

FIGURE 3. Slope Compensation Configuration

a) Slope Compensation Configured for PWM Only (No Current Limit Slope)

b) Slope Compensation Configured for PWM and Current Limit

#### **Soft-Start**

The soft-start circuit allows the power converter to gradually reach a steady state operating point, thereby reducing the start-up stresses and current surges. When bias is supplied to the LM5045, the SS capacitor is discharged by an internal MOSFET. When the UVLO, VCC and REF pins reach their operating thresholds, the SS capacitor is released and is charged with a 20µA current source. Once the SS pin voltage crosses the 1V offset, SS controls the duty cycle. The PWM comparator is a three input device; it compares the RAMP signal against the lower of the signals between the soft-start and the loop error signal. In a typical isolated application, as the secondary bias is established, the error amplifier on the secondary side soft-starts and establishes closed-loop control, steering the control away from the SS pin.

One method to shutdown the regulator is to ground the SS pin. This forces the internal PWM control signal to ground, reducing the output duty cycle quickly to zero. Releasing the SS pin begins a soft-start cycle and normal operation resumes. A second shutdown method is presented in the UVLO section.

### **Gate Driver Outputs**

The LM5045 provides four gate drivers: two floating high side gate drivers HO1 and HO2 and two ground referenced low side gate drivers LO1 and LO2. Each internal driver is capable of source 1.5A peak and sinking 2A peak. Initially, the diagonal HO1 and LO2 are turned-on together, followed by an off-time when all the four gate driver outputs are off. In the subsequent phase the diagonal HO2 and LO1 are turned on together followed by an off-time. The low-side gate drivers are powered directly by the VCC regulator. The HO1 and HO2 gate drivers are powered from a bootstrap capacitor connect-

ed between BST1/BST2 and HS1/HS2 respectively. An external diode connected between VCC (anode pin) and BST (cathode pin) provides the high side gate driver power by charging the bootstrap capacitor from VCC when the corresponding switch node (HS1/HS2 pin) is low. When the high side MOSFET is turned on, BST1 rises to a peak voltage equal to VCC +  $V_{\rm HS1}$  where  $V_{\rm HS1}$  is the switch node voltage. The BST and VCC capacitors should be placed close to the pins of the LM5045 to minimize voltage transients due to parasitic inductances since the peak current sourced to the MOSFET gates can exceed 1.5A. The recommended value of the BST capacitor is  $0.1\mu F$  or greater. A low ESR / ESL capacitor, such as a surface mount ceramic, should be used to prevent voltage droop during the HO transitions.

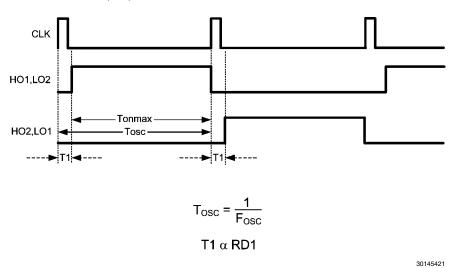

If the COMP pin is open circuit, the outputs will operate at maximum duty cycle. The maximum duty cycle for each phase is limited by the dead-time set by the RD1 resistor. If the RD1 resistor is set to zero then the maximum duty cycle is slightly less than 50% due to the internally fixed dead-time. The internally fixed dead-time is 30ns which does not vary with the operating frequency. The maximum duty cycle for each output can be calculated from the following equation:

$$D_{MAX} = \frac{\left(\frac{1}{F_{OSC}}\right) - (T1)}{\left(\frac{2}{F_{OSC}}\right)}$$

Where, T1 is the time set by the RD1 resistor and  $F_{OSC}$  is the frequency of the oscillator. For example, if the oscillator frequency is set at 400 kHz and the T1 time set by the RD1 resistor is 60ns, the resulting  $D_{MAX}$  will be equal to 0.488.

FIGURE 4. Timing Diagram Illustrating the Maximum Duty Cycle and Dead-Time Set by RD1

# Synchronous Rectifier Control Outputs (SR1 & SR2)

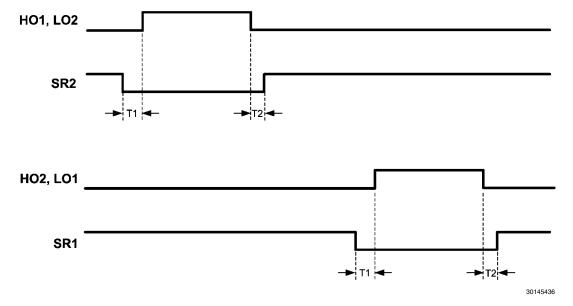

Synchronous rectification (SR) of the transformer secondary provides higher efficiency, especially for low output voltage converters, compared to the diode rectification. The reduction of rectifier forward voltage drop (0.5V - 1.5V) to 10mV -200mV VDS voltage for a MOSFET significantly reduces rectification losses. In a typical application, the transformer secondary winding is center tapped, with the output power inductor in series with the center tap. The SR MOSFETs provide the ground path for the energized secondary winding and the inductor current. From Figure 5 it can be seen that when the HO1/LO2 diagonal is turned ON, power transfer is enabled from the primary. During this period, the SR1 MOSFET is enabled and the SR2 MOSFET is turned-off. The secondary winding connected to the SR2 MOSFET drain is twice the voltage of the center tap at this time. At the conclusion of the HO1/LO2 pulse, the inductor current continues to flow through the SR2 MOSFET body diode. Since the body diode causes more loss than the SR MOSFET, efficiency can be improved by minimizing the T2 period while maintaining sufficient timing margin over all conditions (component tolerances, etc.) to prevent the shoot-through current. When HO2/ LO1 enables power transfer from the primary, the SR2 MOS-FET is enabled and the SR1 MOSFET is off.

During the freewheeling period, the inductor current is almost equally shared between both the SR1 and SR2 MOSFETs which effectively shorts the transformer secondary. The SR2

MOSFET is disabled before HO1/LO2 is turned-on. The SR2 MOSFET body diode continues to carry about the half inductor current until the primary power raises the SR2 MOSFET drain voltage and reverse biases the body diode. Ideally, dead-time T1 would be set to the minimum time that allows the SR MOSFET to turn off before the SR MOSFET body diode starts conducting.

The SR drivers are powered by the REF regulator and each SR output is capable of sourcing 0.1A and sinking 0.4A peak. The amplitude of the SR drivers is limited to 5V. The 5V SR signals enable the LM5045 to transfer SR control across the isolation barrier either through a solid-state isolator or a pulse transformer. The actual gate sourcing and sinking currents for the synchronous MOSFETs are provided by the secondary-side bias and gate drivers.

T1 and T2 can be programmed by connecting a resistor between RD1 and RD2 pins and AGND. It should be noted that while RD1 effects the maximum duty cycle, RD2 does not. The RD1 and RD2 resistors should be located very close to the device. The formula for RD1 and RD2 resistors are given below:

RD(1,2) =

$$\frac{T(1,2)}{3 \text{ pF}}$$

; For 20k < (1,2) < 100k

If the desired dead-time for T1 is 60ns, then the RD1 will be 20 kO.

FIGURE 5. Synchronous Rectifier Timing Diagram

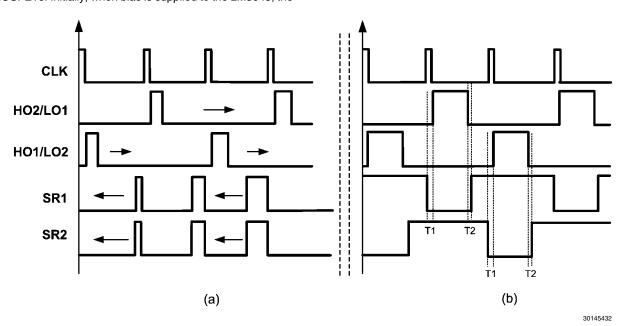

# Soft-Start of the Synchronous Rectifiers

In addition to the basic soft-start already described, the LM5045 contains a second soft-start function that gradually turns on the synchronous rectifiers to their steady-state duty cycle. This function keeps the synchronous rectifiers off during the basic soft-start allowing a linear start-up of the output voltage even into pre-biased loads. Then the SR output duty cycle is gradually increased to prevent output voltage disturbances due to the difference in the voltage drop between the body diode and the channel resistance of the synchronous MOSFETs. Initially, when bias is supplied to the LM5045, the

SSSR capacitor is discharged by an internal MOSFET. When the SS capacitor reaches a 2V threshold and once it is established that COMP is in control of the duty cycle i.e.  $I_{\text{COMP}} < 800 \mu \text{A}$ , the SSSR discharge is released and SSSR capacitor begins charging with a 20 $\mu \text{A}$  current source. During the soft-start of synchronous rectifiers, SR1 and SR2 are turned on simultaneously in pairs, as shown in Figure 6(a), to avoid any transformer imbalance. The duty cycle of the SR outputs gradually increase with increasing SSSR voltage until the duty cycle gets locked into the steady state value as shown in Figure 6(b). The synchronous rectifier outputs can be disabled by grounding the SSSR pin.

FIGURE 6. (a) Waveforms during Soft-Start (b) Waveforms after Soft-Start

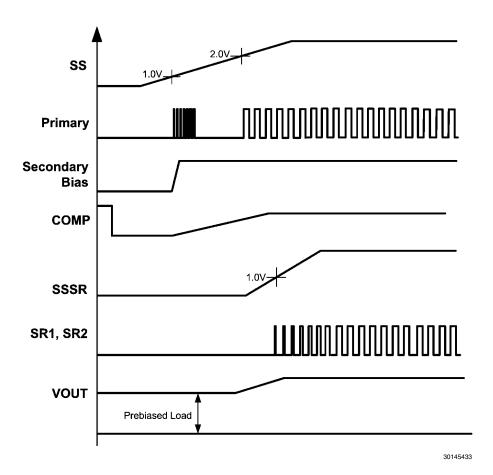

## **Pre-Bias Startup**

A common requirement for power converters is to have a monotonic output voltage start-up into a pre-biased load i.e. a pre-charged output capacitor. In a pre-biased load condition, if the synchronous rectifiers are engaged prematurely they will sink current from the pre-charged output capacitors resulting in an undesired output voltage dip. This condition is undesirable and could potentially damage the power converter. The LM5045 utilizes unique control circuitry to ensure intelligent turn-on of the synchronous rectifiers such that the output has a monotonic startup. Initially, the SSSR capacitor is held at ground to disable the synchronous MOSFETs allowing the body diode to conduct. The synchronous rectifier soft-start is initiated once it is established the duty cycle is controlled by the COMP instead of the soft-start capacitor i.e.  $I_{COMP}$  < 800 $\mu$ A and the voltage at the SS pin>2V. The SSSR capacitor is then released and is charged by a 20µA current source. Further, as shown in Figure 7, a 1V offset on the SSSR pin is used to provide additional delay. This delay ensures the output voltage is in regulation avoiding any reverse current when the synchronous MOSFETs are engaged.

## **Soft-Stop**

As shown in Figure 8, if the UVLO pin voltage falls below the 1.25V standby threshold, but above the 0.4V shutdown threshold, the SSSR capacitor is soft-stopped with a  $60\mu A$  current source (3 times the charging current). Once the SSSR pin reaches the 1.0V threshold, both the SS and SSSR pins are immediately discharged to GND. Soft-stopping the power converter gradually winds down the energy in the output capacitors and results in a monotonic decay of the output voltage. During the hiccup mode, the same sequence is executed except that the SSSR is discharged with a  $120\mu A$  current source (6 times the charging current). In case of an OVP, VCC UV, thermal limit or a VREF UV condition, the power converter hard-stops, whereby all of the control outputs are driven to a low state immediately.

FIGURE 7. Pre-Bias Voltage Startup Waveforms

## **Soft-Stop Off**

The Soft-Start Off (SSOFF) pin gives additional flexibility by allowing the power converter to be configured for hard-stop during line UVLO and hiccup mode condition. If the SS OFF

pin is pulled up to the 5V REF pin, the power converter hardstops in any fault condition. Hard-stop drives each control output to a low state immediately. Refer to Table 1 for more details

FIGURE 8. Stop-Stop Waveforms during a UVLO Event

Table 1: Soft-Stop in Fault Conditions

| Fault Condition        | SSSR                 |

|------------------------|----------------------|

| UVLO                   | Soft-Stop            |

| (UVLO<1.25V)           | 3x the charging rate |

| OVP                    | Hard-Stop            |

| (OVP>1.25V)            |                      |

| Hiccup                 | Soft-Stop            |

| (CS>0.75 and RES>1V)   | 6x the charging rate |

| VCC/VREF UV            | Hard-Stop            |

| Internal Thermal Limit | Hard-Stop            |

Note: All the above conditions are valid with SSOFF pin tied to GND. If SSOFF=5V, the LM5045 hard-stops in all the conditions. The SS pin remains high in all the conditions until the SSSR pin reaches 1V.

#### **Thermal Protection**

Internal thermal shutdown circuitry is provided to protect the integrated circuit in the event the maximum rated junction temperature is exceeded. When activated, typically at 160°C, the controller is forced into a shutdown state with the output drivers, the bias regulators (VCC and REF) disabled. This helps to prevent catastrophic failures from accidental device overheating. During thermal shutdown, the SS and SSSR capacitors are fully discharged and the controller follows a normal start-up sequence after the junction temperature falls to the operating level (140 °C).

## **Applications Information**

#### **CONTROL METHOD SELECTION**

The LM5045 is a versatile PWM control IC that can be configured for either current mode control or voltage mode control. The choice of the control method usually depends upon the designer preference. The following must be taken into consideration while selecting the control method. Current mode control can inherently balance flux in both phases of the full-bridge topology. The full-bridge topology, like other dou-

ble ended topologies, is susceptible to the transformer core saturation. Any asymmetry in the volt-second product applied between the two alternating phases results in flux imbalance that causes a dc buildup in the transformer. This continual dc buildup may eventually push the transformer into saturation. The volt-second asymmetry can be corrected by employing current mode control. In current mode control, a signal representative of the primary current is compared against an error signal to control the duty cycle. In steady-state, this results in each phase being terminated at the same peak current by adjusting the pulse-width and thus applying equal volt-seconds to both the phases.

Current mode control can be susceptible to noise and subharmonic oscillation, while voltage mode control employs a larger ramp for PWM and is usually less susceptible. Voltagemode control with input line feed-forward also has excellent line transient response. When configuring for voltage mode control, a dc blocking capacitor can be placed in series with the primary winding of the power transformer to avoid any flux imbalance that may cause transformer core saturation.

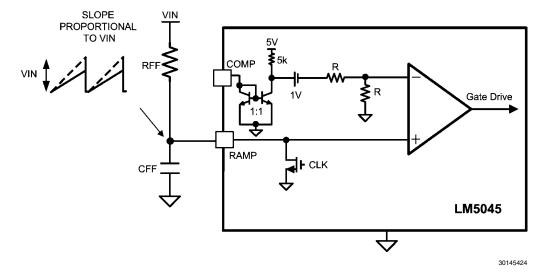

#### **VOLTAGE MODE CONTROL USING THE LM5045**

To configure the LM5045 for voltage mode control, an external resistor ( $R_{\rm FF}$ ) and capacitor ( $C_{\rm FF}$ ) connected to VIN, AG-ND, and the RAMP pins is required to create a saw-tooth modulation ramp signal shown in Figure 9. The slope of the signal at RAMP will vary in proportion to the input line voltage. The varying slope provides line feed-forward information necessary to improve line transient response with voltage mode control. With a constant error signal, the on-time (T<sub>ON</sub>) varies inversely with the input voltage (VIN) to stabilize the Volt-Second product of the transformer primary. Using a line feedforward ramp for PWM control requires very little change in the voltage regulation loop to compensate for changes in input voltage, as compared to a fixed slope oscillator ramp. Furthermore, voltage mode control is less susceptible to noise and does not require leading edge filtering. Therefore, it is a good choice for wide input range power converters. Voltage mode control requires a Type-III compensation network, due to the complex-conjugate poles of the L-C output filter.

FIGURE 9. Feed-Forward Voltage Mode Configuration

The recommended capacitor value range for  $C_{FF}$  is from 100pF to 1800pF. Referring to Figure 9, it can be seen that  $C_{FF}$  value must be small enough to be discharged with in the clock pulse-width which is typically within 50ns. The  $R_{DS(ON)}$  of the internal discharge FET is  $5.5\Omega$ .

The value of R<sub>FF</sub> required can be calculated from

$$R_{FF} = \frac{-1}{F_{OSC} \times C_{FF} \times In \left(1 - \frac{V_{RAMP}}{VIN_{MIN}}\right)}$$

For example, assuming a  $V_{RAMP}$  of 1.5V (a good compromise of signal range and noise immunity), at VIN<sub>MIN</sub> of 36V (oscillator frequency of 400 kHz and  $C_{FF}$  = 470pF results in a value for  $R_{FF}$  of 125 k $\Omega$ .

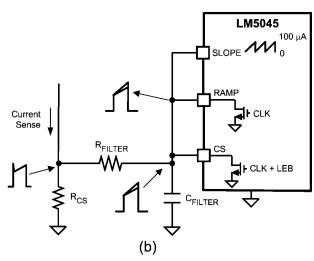

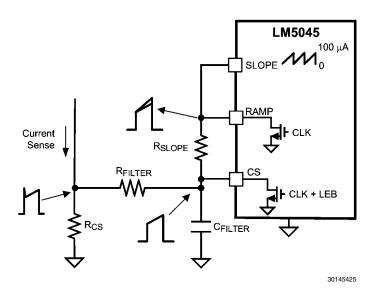

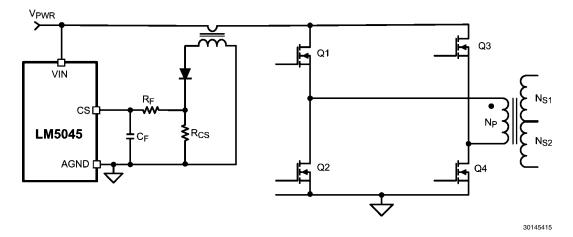

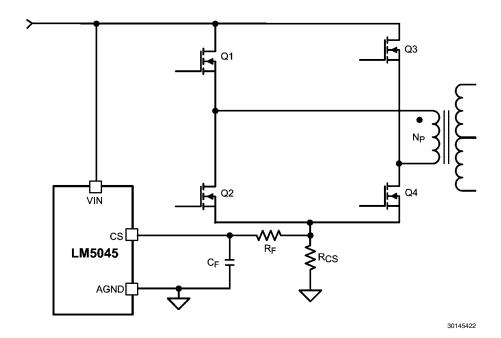

#### **CURRENT MODE CONTROL USING THE LM5045**

The LM5045 can be configured for current mode control by applying a signal proportional to the primary current to the RAMP pin. One way to achieve this is shown in Figure 10. The primary current can be sensed using a current transformer or sense resistor, the resulting signal is filtered and applied to the RAMP pin through a resistor used for slope compensation. It can be seen that the signal applied to the RAMP pin consists of the primary current information from the CS pin plus an additional ramp for slope compensation, added by the resistor  $R_{\rm SLOPE}$ .

The current sense resistor is selected such that during over current condition, the voltage across the current sense resistor is above the minimum CS threshold of 728mV.

In general, the amount of slope compensation required to avoid sub-harmonic oscillation is equal to at least one-half the down-slope of the output inductor current, transformed to the primary. To mitigate sub-harmonic oscillation after one switching period, the slope compensation has to be equal to one times the down slope of the filter inductor current transposed to primary. This is known as deadbeat control. The slope compensation resistor required to implement dead-beat control can be calculated as follows:

Where N<sub>TR</sub> is the turns-ratio with respect to the primary. For example, for a 3.3V output converter with a turns-ratio between primary and secondary of 9:1, an output filter inductance (L<sub>FILTER</sub>) of 800nH and a current sense resistor (R<sub>SENSE</sub>) of  $15m\Omega$ , R<sub>SLOPE</sub> of  $1.67k\Omega$  will suffice.

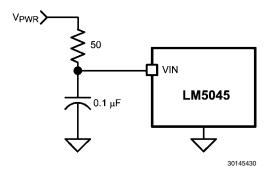

#### **VIN and VCC**

The voltage applied to the VIN pin, which may be the same as the system voltage applied to the power transformer's primary ( $V_{PWR}$ ), can vary in the range of the 14 to 100V. It is recommended that the filter shown in Figure 11 be used to suppress the transients that may occur at the input supply. This is particularly important when VIN is operated close to the maximum operating rating of the LM5045. The current into VIN depends primarily on the LM5045's operating current, the switching frequency, and any external loads on the VCC pin, that typically include the gate capacitances of the power MOSFETs. In typical applications, an auxiliary transformer winding is connected through a diode to the VCC pin. This pin must raise VCC voltage above 8V to shut off the internal startup regulator.

After the outputs are enabled and the external VCC supply voltage has begun supplying power to the IC, the current into the VIN pin drops below 1mA. VIN should remain at a voltage equal to or above the VCC voltage to avoid reverse current through the internal body diode of the internal VCC regulator.

#### FOR APPLICATIONS WITH > 100V INPUT

For applications where the system input voltage exceeds 100V, VIN can be powered from an external start-up regulator as shown in Figure 12. In this configuration, the VIN and VCC pins should be connected together. The voltage at the VCC and VIN pins must be greater than 10V (>Max VCC reference voltage) yet not exceed 16V. To enable operation the VCC voltage must be raised above 10V. The voltage at the VCC pin must not exceed 16V. The voltage source at the right side of Figure 12 is typically derived from the power stage, and becomes active once the LM5045's outputs are active.

$$R_{SLOPE} = \frac{N_{TR} x V_{OUT}}{L_{FILTER} x F_{OSC} x I_{SLOPE}}$$

FIGURE 10. Current Mode Configuration

**FIGURE 11. Input Transient Protection**

FIGURE 12. Start-up Regulator for VPWR>100V

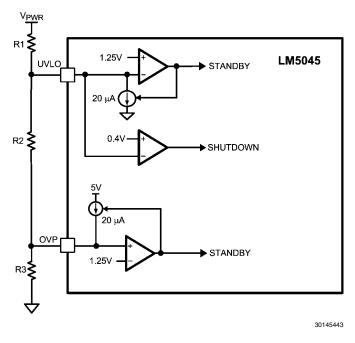

#### **UVLO AND OVP VOLTAGE DIVIDER SELECTION**

Two dedicated comparators connected to the UVLO and OVP pins are used to detect under voltage and over voltage conditions. The threshold values of both these comparators are set at 1.25V. The two functions can be programmed independently with two separate voltage dividers from VIN to AGND as shown in Figure 13 and 14, or with a three-resistor divider as shown in Figure 15. Independent UVLO and OVP pins provide greater flexibility for the user to select the operational voltage range of the system. When the UVLO pin voltage is below 0.4V, the controller is in a low current shutdown mode. For a UVLO pin voltage greater than 0.4V but less than 1.25V the controller is in standby mode. Once the UVLO pin voltage is greater than 1.25V, the controller is fully enabled. Two external resistors can be used to program the minimum operational voltage for the power converter as shown in Figure 13. When the UVLO pin voltage falls below the 1.25V threshold, an internal 20µA current sink is enabled to lower the voltage at the UVLO pin, thus providing threshold hysteresis. Resistance values for R1 and R2 can be determined from the following equations:

$$R_{1} = \frac{V_{HYS}}{20 \ \mu A}$$

$$R_{2} = \frac{1.25 V \ x \ R_{1}}{V_{PWR-OFF} - 1.25 V - (20 \ \mu A \ x \ R1)}$$

Where  $V_{PWR}$  is the desired turn-on voltage and  $V_{HYS}$  is the desired UVLO hysteresis at  $V_{PWR}.$

For example, if the LM5045 is to be enabled when VPWR reaches 33V, and disabled when  $V_{PWR}$  is decreased to 31V,  $R_1$  should be  $100k\Omega,$  and  $R_2$  should be  $4.2k\Omega.$  The voltage at the UVLO pin should not exceed 7V at any time.

Two external resistors can be used to program the maximum operational voltage for the power converter as shown in Figure 13. When the OVP pin voltage rises above the 1.25V threshold, an internal  $20\mu A$  current source is enabled to raise the voltage at the OVP pin, thus providing threshold hysteresis. Resistance values for  $R_1$  and  $R_2$  can be determined from the following equations:

$$R_{1} = \frac{V_{HYS}}{20 \ \mu A}$$

$$R_{2} = \frac{1.25 V \times R_{1}}{V_{PWR} - 1.25 V - (20 \ \mu A \times R1)}$$

If the LM5045 is to be disabled when V<sub>PWR-OFF</sub> reaches 80V and enabled when it is decreased to 78V.  $R_1$  should be  $100 k\Omega,$  and  $R_2$  should be  $1.5~k\Omega.$  The voltage at the OVP pin should not exceed 7V at any time.

FIGURE 13. Basic UVLO Configuration

FIGURE 14. Basic OVP Configuration

FIGURE 15. UVLO/OVP Divider

The UVLO and OVP can also be set together using a 3 resistor divider ladder as shown in Figure 15.  $R_1$  is calculated as explained in the basic UVLO divider selection. Using the same values, as in the above two examples, for the UVLO and OVP set points,  $R_1$  and  $R_3$  remain the same at  $100 k\Omega$  and  $1.5 k\Omega$ . The  $R_2$  is  $2.7 k\Omega$  obtained by subtracting  $R_3$  from  $4.2 k\Omega$ .

Remote configuration of the controller's operational modes can be accomplished with open drain device(s) connected to the UVLO pin as shown in Figure 16.

Figure 17 shows an application of the OVP comparator for Remote Thermal Protection using a thermistor (or multiple thermistors) which may be located near the main heat sources of the power converter. The negative temperature coefficient (NTC) thermistor is nearly logarithmic, and in this example a  $100 k\Omega$  thermistor with the  $\beta$  material constant of 4500 Kelvin changes to approximately  $2k\Omega$  at  $130^{\circ}C$ . Setting  $R_1$  to one-third of this resistance ( $665\Omega$ ) establishes  $130^{\circ}C$  as the desired trip point (for VREF = 5V). In a temperature band from  $20^{\circ}C$  below to  $20^{\circ}C$  above the OVP threshold, the voltage divider is nearly linear with 25 mV per  $^{\circ}C$  sensitivity.

$R_2$  provides temperature hysteresis by raising the OVP comparator input by  $R_2$  x 20µA. For example, if a  $22k\Omega$  resistor is selected for  $R_2$ , then the OVP pin voltage will increase by 22k x 20µA = 506mV. The NTC temperature must therefore fall by 506mV / 25mV per  $^{\circ}\text{C}$  = 20°C before the LM5045 switches from standby mode to the normal mode.

FIGURE 16. Remote Standby and Disable Control

**FIGURE 17. Remote Thermal Protection**

#### **CURRENT SENSE**

The CS pin receives an input signal representative of its transformer's primary current, either from a current sense transformer or from a resistor located at the junction of source pin of the primary switches, as shown in Figure 18 and Figure 19 respectively. In both the cases, the filter components  $\rm R_F$  and  $\rm C_F$  should be located as close to the IC as possible, and the ground connection from the current sense transformer, or  $\rm R_{SENSE}$  should be a dedicated trace to the appropriate GND pin. Please refer to the layout section for more layout tips.