ADQ114 is a high speed digitizer. The ADQ114 has outstanding dynamic performance from a combination of high bandwidth and high dynamic range, which enables demanding measurements such as RF/IF sampling. Excellent spectral purity in combination with low noise makes ADQ114 ideal for noise measurements.

## Features

- 800 MSPS sampling rate

- 720 MHz analog bandwidth

- 14 bits resolution

- Internal and external clock

- External trigger

- Multi record >1 MHz PRF

- 128 MSamples data memory

- Data interface USB 2.0 / cPCIe / PXIe

- FPGAs available for customized applications

- Support for C/C++ and MATLAB

## Applications

- RADAR

- LIDAR

- Wireless communication

- Optical transmission

- High-speed data recording

- Test and measurement

#### Software support

- MATLAB

- C/C++

## **Ordering information**

| ORDERING INFORMATION    |                |  |  |

|-------------------------|----------------|--|--|

| ADQ114 standard         | ADQ114         |  |  |

| OPTIONS                 |                |  |  |

| Low frequency AC AFE    | -LFAFE         |  |  |

| Buffered DC coupled AFE | -DCAFE         |  |  |

| cPCle / PXle            | -PXIE          |  |  |

| Decimation              | -DEC           |  |  |

| FPGA upgrade            | -SX50T         |  |  |

| RELATED PRODUCTS        |                |  |  |

| ADQ Development Kit     | ADQ114 Dev Kit |  |  |

#### Example: ADQ114–DCAFE–PXIE

## Introduction

The ADQ114 digitizer features single channel, 14 bits resolution, 800 MSPS capture rate with 720 MHz analog input bandwidth, and 128 MSamples memory buffer.

The ADQ114 is optimized for spectral purity over a large bandwidth, which makes it ideal for broadband applications such as IF/RF sampling and high-speed data recording. The ADQ114 offers an easy-to-use API that allows easy integration into any application. The card connects to the host via a high-speed USB 2.0 cable. cPCIe / PXIe x8 interface is available as an option. The ADQ114 is equipped with two advanced Xilinx V5 series FPGAs that are available for customized real time applications.

## **ADQ Development Kit**

SP Devices' ADQ Development Kit is an optional software tool that rapidly enhances the customization process of your next DSP application for the ADQ-series onboard FPGAs. More details about this product can be found in the product brief for the ADQ Development Kit.

Document Number 08-0111 Revision D Date 2009-12-21 Printed 2009-12-22 Contact

# 1 Technical data<sup>1</sup>

| KEY PARAMETERS         |                               |

|------------------------|-------------------------------|

| Number of channels     | 1                             |

| Digitizer Resolution   | 14 bits                       |

| Sampling rate          | 140 - 800 MSps                |

| Data memory            | 128 MSamples                  |

| Trigger                | Software / External / Edge    |

| Number of GPIOs        | 6                             |

| Front panel connectors | SMA / Micro-D Plug 9 way      |

| Clock                  | Internal / External / Ext ref |

| ANALOG INPUT        |           |                 |

|---------------------|-----------|-----------------|

| ENOB @ 70 MHz       | 11.2      | bits            |

| SFDR @ 70 MHz       | 82        | dB              |

| SNDR @ 70 MHz       | 69        | dB              |

| Impedance AC        | 50        | Ω               |

| Bandwidth (-3 dB)   | 10 – 720M | Hz              |

| Input voltage range | 2.2       | V <sub>PP</sub> |

| INTERNAL CLOCK          |                                  |        |

|-------------------------|----------------------------------|--------|

| Accuracy                | 400                              | fs RMS |

| Internal sampling rate  | 1600/n, n=211                    | MHz    |

| Clock references source | 10 MHz external<br>Internal TCXO |        |

| EXTERNAL CLOCK                     |          |                 |

|------------------------------------|----------|-----------------|

| Frequency (min – max) <sup>1</sup> | 70 - 400 | MHz             |

| Signal level (min – max)           | 0.25 – 2 | V <sub>PP</sub> |

| Impedance AC                       | 50       | Ω               |

| Duty cycle                         | 50% ± 5% |                 |

1. The sampling frequency is 2X clock frequency due to interleaving.

| MEMORY                  |                         |

|-------------------------|-------------------------|

| Data memory             | 128 MSamples            |

| Pre-trigger buffer      | Up to batch size        |

| Trigger hold off        | 2 <sup>34</sup> samples |

| Multi record batch size | 1 – memory size         |

| Multi record max PRF    | 1.7 MHz                 |

| EXTERNAL REFERENCE       |           |                 |

|--------------------------|-----------|-----------------|

| Frequency                | 10        | MHz             |

| Signal level (min – max) | 0.8 – 3.3 | V <sub>PP</sub> |

| Impedance AC             | 50        | Ω               |

1. All values are typical unless otherwise noted.

| Document Number |

|-----------------|

| 08-0111         |

| Revision        |

| D               |

Date 2009-12-21 Printed 2009-12-22

| EXTERNAL TRIGGER INPUT  |             |    |

|-------------------------|-------------|----|

| Input impedance DC      | 50          | Ω  |

| Input range (min – max) | -2.5 - +3.3 | V  |

| Threshold rising edge   | 0.5         | V  |

| Time resolution         | 625         | ps |

| TRIGGER USED AS GPIO |         |   |

|----------------------|---------|---|

| Output impedance     | 20      | Ω |

| Output (low – high)  | 0.1 – 2 | V |

| GPIO                       |           |    |

|----------------------------|-----------|----|

| Output imp. GPIO-pin       | 30        | Ω  |

| Out. imp. dedicated output | 100       | Ω  |

| Output (low – high)        | 0.1 – 3.2 | V  |

| Input impedance            | 10        | kΩ |

| Input (low – high)         | 1 – 2.3   | V  |

| HI-SPEED USB 2.0 INTERFACE     |  |  |  |  |

|--------------------------------|--|--|--|--|

| Sustained data rate 25 MByte/s |  |  |  |  |

| Connector Mini–B               |  |  |  |  |

| POWER SUPPLY      |    |   |

|-------------------|----|---|

| Supply voltage    | 12 | V |

| Power consumption | 20 | W |

| ENVIRONMENTAL / MECHANICAL        |                |                 |

|-----------------------------------|----------------|-----------------|

| Operating temperature             | 0 – 45         | °C              |

| Storage temperature               | -20 - 70       | °C              |

| Relative humidity, non-condensing | 5% – 95%       |                 |

| Board size                        | 100 x 163      | mm <sup>2</sup> |

| Case size                         | 103 x 166 x 31 | mm <sup>3</sup> |

| OPERATING SYSTEM |                 |

|------------------|-----------------|

| Windows XP       | SP 2 and higher |

| Windows Vista    | All versions    |

| APPLICATION SOFTWARE |                           |

|----------------------|---------------------------|

| ADCaptureLab         | Data capture and analysis |

| MATLAB               | Data capture interface    |

| C/C++                | Data capture interface    |

#### CERTIFICATION AND COMPLIANCE CE, FCC Part 15 B

Contact Signal Processing Devices Sweden AB Teknikringen 6, SE-583 33 Linköping, SWEDEN www.spdevices.com

ADQ114 Datasheet

## 2 Dynamic performance

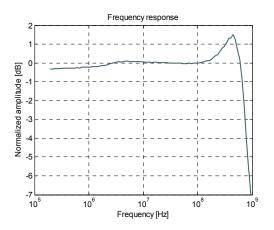

# 2.2 Frequency response

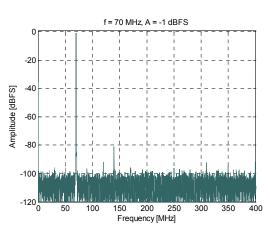

# 2.1 Noise and distortion

| SFDR | 82   | dB   |

|------|------|------|

| SNR  | 69   | dB   |

| ENOB | 11.2 | bits |

| Full scale        | 2.2 V <sub>PP</sub> |

|-------------------|---------------------|

| Bandwidth (-3 dB) | 720 MHz             |

| 1 dB flatness     | 340 MHz             |

Figure 3: Frequency response.

Figure 1: FFT of 70 MHz input signal.

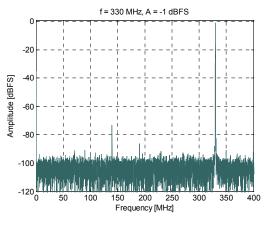

| SFDR | 73   | dB   |

|------|------|------|

| SNR  | 65   | dB   |

| ENOB | 10.5 | bits |

Figure 2: FFT of 330 MHz input signal.

Document Number 08-0111 Revision D Date 2009-12-21 Printed 2009-12-22

# 3 Absolute Maximum ratings

Exposure to conditions exceeding these rating may reduce life time or permanently damage the device.

| ABSOLUTE MAXIMUM RATINGS        |        |                     |

|---------------------------------|--------|---------------------|

|                                 | Min    | Max                 |

| Supply voltage (to GND)         | –0.4 V | 14 V                |

| Analog input (AC)               |        | 4.4 V <sub>PP</sub> |

| Trigger input (to GND)          | –3 V   | 3.7 V               |

| Clock input (AC)                |        | 3.3 V <sub>PP</sub> |

| Ambient temperature (operation) | 0°C    | 45 °C               |

The ADQ114 has a built in fan to cool the device. If the air flow is blocked or the fan malfunctions, the temperature surveillance unit will protect the ADQ114 from overheating by shutting down parts of the device.

The SMA connectors have an expected life time of 500 operations. For frequent connecting and disconnecting of cables, connector savers are recommended.

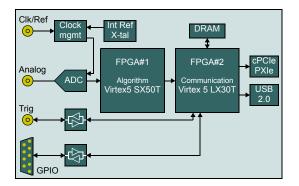

## 4 Architecture

#### 4.1 Overview

Figure 4: Block diagram

## 4.2 Analog Front End, AFE

The analog input is single ended AC coupled 50 ohm. The single ended signal is converted to a differential signal in a balun.

#### 4.3 ADC

The ADC configuration is two 14 bit 400 MSps ADCs which are time interleaved to reach 800 MSps effective sampling rate. The time interleaving is enabled by SP Devices' time interleaving algorithm ADX216.

### 4.4 Clock

The clock generator consists of a crystal oscillator as a clock reference and a PLL with built in VCO. The PLL has also built in dividers for generating necessary clock frequencies on the board. The sampling frequency is set by configuring these frequency dividers.

There is also an external SMA connector for either an external clock reference or an external clock source.

#### 4.5 FPGAs

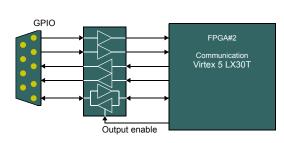

The data outputs of the ADCs are connected to a first Xilinx XC5VSX50T-1 FPGA which runs the time interleaving algorithm ADX216. The data is then transferred to a second FPGA, Xilinx XC5VLX30T-1, which handles the communication with the host and the batch data RAM. This FPGA is open for user applications through the ADQ Development Kit. 29 DSP elements and 30 % of the logic is available for user applications.

### 4.6 Memory

There is 128 MSamples data batch memory. The data batch length for each recording is set to any value within this range. For more information about memory handling, see **Section 4.8**.

## 4.7 Interface

The ADQ114 is connected to the host computer through a Hi-Speed USB interface which is used for control and uploading of data.

The USB connection can be configured in a streaming mode. The sustained data rate is then 25 MBytes/s<sup>1</sup>. This is typically used together with a data reduction algorithm, implemented through the ADQ Development Kit.

See Section 6.1 for Compact PCI Express (cPCIe) / PXI Express (PXIe) interface.

- 4.8 Trigger

- 4.8.1 Overview

The ADQ114 has several trigger options

- Software trigger

- Level trigger

1. This is highly dependent of other tasks performed by the operating system on the host computer.

| Contact                                     |                                                                                    |

|---------------------------------------------|------------------------------------------------------------------------------------|

| Signal Processing Devices Sweden AB         | 4(7)                                                                               |

| Teknikringen 6, SE-583 33 Linköping, SWEDEN |                                                                                    |

| www.spdevices.com                           |                                                                                    |

|                                             | Signal Processing Devices Sweden AB<br>Teknikringen 6, SE-583 33 Linköping, SWEDEN |

### • External trigger

When armed, the system is waiting for the selected trigger event. At the trigger event, a data batch of selected length is recorded in the batch memory. A pre-trigger buffer is available. The length of the pre-trigger buffer is fully controllable<sup>1</sup>. The pre-trigger buffer is a part of the total batch length.

The trigger hold-off is up to  $2^{34}$  samples and is set in steps of 4 samples.

#### 4.8.2 Software trigger

Data capture is triggered by a software command. This is suitable for measurements on continuous waves.

#### 4.8.3 Level trigger

Data capture is triggered by an event on the input data. This is useful for capturing pulses. The level trigger combined with the pre-trigger or trigger hold-off setting can capture any pulse shape.

#### 4.8.4 External trigger

Data capture is triggered by positive edge on the trigger input connector. This is intended for synchronizing the signal source with the ADQ114. It can also be used for synchronizing several ADQ114.

#### 4.8.5 Multi record

The ADQ114 can be set up in a multi record mode. At each trigger, a record of data is recorded in the memory. The length of each record and number of records is user defined. Multi record works together with pre-trigger buffer and trigger hold off.

**Figure 5** shows an example, where an external trigger is used for triggering each record. The analog channel samples a low frequency sine wave. The records has been reconstructed in time domain to illustrate the slow sine wave.

The pulse repeat frequency (PRF) can be set up to 1.7 MHz depending on the record length.

| PRF           | 550  | kHz     |

|---------------|------|---------|

| Record length | 1024 | samples |

| PULSE REPEAT FREQUENCY, MULTI RECORD |                 |

|--------------------------------------|-----------------|

| Record length                        | Maximum PRF kHz |

| 16                                   | 1700            |

| 64                                   | 1600            |

| 256                                  | 1100            |

| 1024                                 | 550             |

| 4096                                 | 175             |

| 16384                                | 47              |

| 65536                                | 12              |

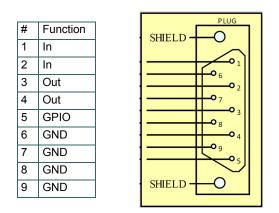

#### 4.9 GPIO

The ADQ114 is equipped with one bi-directional GPIO, two dedicated inputs and 2 dedicated outputs. The GPIOs are controlled from software, but can also be accessed from the ADQ Development Kit.

The connector is Micro D plug 9 way. A suitable socket with lead is for example MOLEX 83421-9044.

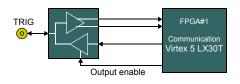

The trigger port can also be used as a bi-directional GPIO. The trigger can be configured as a trigger output, see **Figure 7**.

There is a fixed amount of delay between the trigger and data depending on the length of the wires and the internal signal paths. This delay will change for a custom application using the ADQ Development Kit

| Document Number | Date       | Contact                                     |

|-----------------|------------|---------------------------------------------|

| 08-0111         | 2009-12-21 | Signal Processing Devices Sweden AB         |

| Revision        | Printed    | Teknikringen 6, SE-583 33 Linköping, SWEDEN |

| D               | 2009-12-22 | www.spdevices.com                           |

Figure 6: GPIO block diagram.

Figure 7: Trigger as GPIO: block diagram.

## 5 Software tools

### 5.1 ADCaptureLab

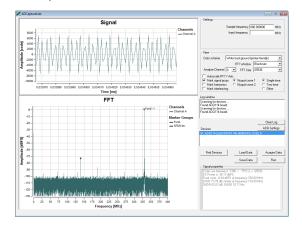

The ADQ114 is supplied with the ADCaptureLab software that provides quick and easy control of the digitizer. The tool also offers both time domain and frequency domain analysis, see **Figure 8**. Data can be saved in different file formats for off-line analysis. Comparison of results is easily done by importing data from file and analyze it in ADCaptureLab.

Figure 8: ADCaptureLab

## 5.2 Software development kit (SDK)

The ADQ114 data acquisition system is easily integrated into your own application by using the included Software development kit. The SDK includes programming examples and reference projects for C/C++ and MATLAB.

Date 2009-12-21 Printed 2009-12-22

## 6 Options

#### 6.1 cPCle / PXle interface

The ADQ114 is available with cPCIe / PXIe interface.

| cPCIe / PXIe INTERFACE       |               |         |

|------------------------------|---------------|---------|

| Bus width                    | 8             | lanes   |

| Bus peak capacity            | 16            | Gbit/s  |

| Sustained data rate, 4 lanes | 400           | MByte/s |

| PXIe card size               | 1 slot 3U 4TE |         |

Figure 9: cPCle / PXle interface

Order code: -PXIE

## 6.2 Low frequency AC AFE<sup>1</sup>

The AFE is available with a low frequency configuration. The AC coupling is tuned to get a lower cut off frequency (–3dB) at typically 0.4 Hz. This configuration maintains low noise performance of the standard AFE.

#### Order code: -LFAFE

### 6.3 Active DC coupled AFE<sup>2</sup>

The ADQ114 is available with an active buffered DC coupled AFE. The gain compared to the AC AFE options is 18 dB which means that full scale analog input is  $0.25 V_{PP}$ .

#### Order code: -DCAFE

### 6.4 Decimation IP

A Decimation IP is available for integration in FPGA#2. Decimation IP requires FPGA upgrade to SX50T. The Decimation IP can decimate up to  $2^{34}$  times. The Decimation IP together with the low frequency option is ideal for low frequency noise measurements.

The Decimation IP implements a close to ideal low pass filter, which suppresses the wide band quantization noise in digitizer. The theory of decimation gives that each factor of 4 in decimation yields one extra bit in resolution. The effect is an increased dynamic range.

The Decimation IP makes the ADQ114 very flexible and a large set of measurements specifications can be met with the same device.

| DECIMATION IP CONFIGURATIONS (EXAMPLES) |               |            |  |  |

|-----------------------------------------|---------------|------------|--|--|

| Decimation order                        | Sampling rate | Resolution |  |  |

| 2 <sup>0</sup> = 1                      | 800 MSps      | 14 bits    |  |  |

| 2 <sup>4</sup> = 16                     | 50 MSps       | 16 bits    |  |  |

| 2 <sup>12</sup> = 4096                  | 195 kSps      | 20 bits    |  |  |

Order code: –DEC

#### 6.5 FPGA upgrade

The ADQ Development Kit opens a user area in FPGA#2 for custom designs. The standard configuration for FPGA#2 is a Xilinx Virtex 5 LX30T-1 FPGA, which is enough for many applications. However, for demanding real time signal processing applications, an FPGA upgrade to Xilinx Virtex 5 SX50T-1 is available. This gives the user access to more than 285 DSP elements. 60% of the logic in this FPGA is also available.

#### Order code: -SX50T

1. It is not possible to switch between different AFEs.

2. It is not possible to switch between different AFEs.

7(7)

| Document Number | Date       | Contact                                     |   |

|-----------------|------------|---------------------------------------------|---|

| 08-0111         | 2009-12-21 | Signal Processing Devices Sweden AB         | 7 |

| Revision        | Printed    | Teknikringen 6, SE-583 33 Linköping, SWEDEN |   |

| D               | 2009-12-22 | www.spdevices.com                           |   |