Le7920 Subscriber Line Interface Circuit VE580 Series

The Le7920 Subscriber Line Interface Circuit implements the basic telephone line interface functions, and enables the

# DISTINCTIVE CHARACTERISTICS

- Control states: Active, Ringing, Standby, and Disconnect

- Low standby power (35 mW)

- –19 V to –58 V battery operation

- On-hook transmission

- Two-wire impedance set by single external impedance

- Programmable constant-current feed

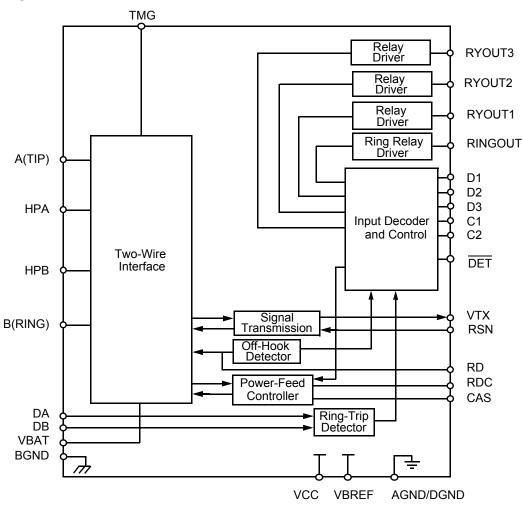

## **BLOCK DIAGRAM**

design of low cost, high performance, POTS line interface cards.

- Programmable loop-detect threshold

- Programmable ring-trip detect threshold

- No –5 V supply required

- Current Gain = 500

- On-chip Thermal Management (TMG) feature

- Four on-chip relay drivers and relay snubbers, 1 ringing and 3 general purpose (32 PLCC)

| Document ID#  | 080146   | Date:    | Sep 19, 2007 |

|---------------|----------|----------|--------------|

| Rev:          | J        | Version: | 2            |

| Distribution: | Public D | ocument  |              |

# TABLE OF CONTENTS

| Ordering Information                     |

|------------------------------------------|

| Standard Products                        |

| Connection Diagram                       |

| Top View                                 |

| Pin Descriptions                         |

| Absolute Maximum Ratings                 |

| Operating Ranges                         |

| Electrical Characteristics               |

| Electrical Characteristics (continued)9  |

| Electrical Characteristics (continued)10 |

| Relay Driver Schematics                  |

| DC Feed Characteristics                  |

| Test Circuits                            |

| Test Circuits (continued)                |

| Test Circuits (continued)16              |

| Physical Dimensions                      |

| 32-Pin PLCC                              |

| Revision Summary                         |

| Revision C to Revision D                 |

| Revision D to Revision E                 |

| Revision E to Revision F                 |

| Revision F to Revision G                 |

| Revision G to Revision H                 |

| Revision H to Revision I                 |

| Revision I1 to Revision J1               |

| Revision J1 to Revision J2               |

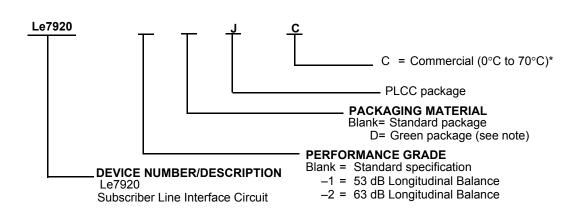

## **ORDERING INFORMATION**

### **Standard Products**

Zarlink standard products are available in several packages and operating ranges. The order number (Valid Combination) is formed by a combination of the elements below.

**Note:** Green package meets RoHS Directive 2002/95/EC of the European Council to minimize the environmental impact of electrical equipment.

| Valid Combinations |    |     |  |  |

|--------------------|----|-----|--|--|

| Le7920*            | –1 | JC  |  |  |

|                    | -2 | DJC |  |  |

#### Valid Combinations

Valid Combinations list configurations planned to be supported in volume for this device. Consult the local Zarlink sales office to confirm availability of specific valid combinations, to check on newly released combinations, and to obtain additional data on Zarlink's standard military–grade products.

\*Zarlink reserves the right to fulfill all orders for this device with parts marked with the "Am" part number prefix, until such time as all inventory bearing this mark has been depleted. It should be noted that parts marked with either the "Am" or the "Le" part number prefix are equivalent devices in terms of form, fit, and function. The only difference between the two is in the part number prefix appearing on the topside mark.

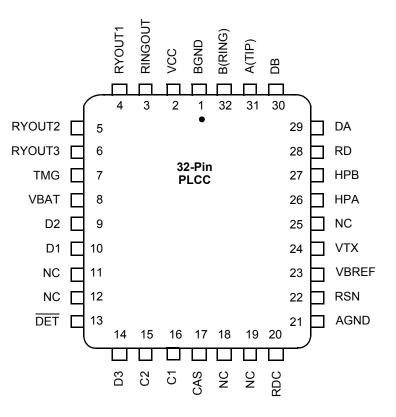

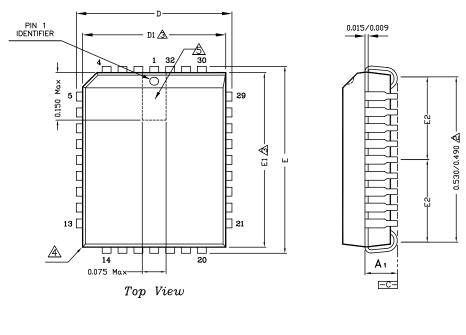

# **CONNECTION DIAGRAM**

## **Top View**

Notes:

- 1. Pin 1 is marked for orientation.

- 2. NC = No Connect

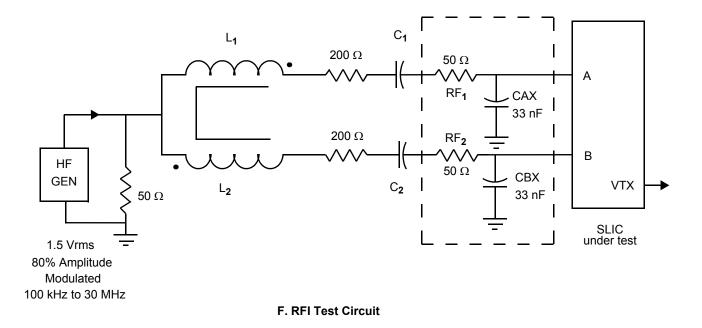

# **PIN DESCRIPTIONS**

| Pin Name  | Туре      | Description                                                                                                                                                                                                                                                         |  |

|-----------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| AGND/DGND | Ground    | Analog and Digital ground.                                                                                                                                                                                                                                          |  |

| A(TIP)    | Output    | Output of A(TIP) power amplifier.                                                                                                                                                                                                                                   |  |

| BGND      | Ground    | Battery (power) ground.                                                                                                                                                                                                                                             |  |

| B(RING)   | Output    | Output of B(RING) power amplifier.                                                                                                                                                                                                                                  |  |

| C2–C1     | Inputs    | Decoder. TTL compatible. C2 is MSB and C1 is LSB.                                                                                                                                                                                                                   |  |

| CAS       | Capacitor | Anti-Saturation pin for capacitor to filter reference voltage when operating in anti-<br>saturation region.                                                                                                                                                         |  |

| D3–D1     | Input     | Relay Driver Control. D3–D1 control the relay drivers RYOUT1, RYOUT2, and RYOUT3.<br>Logic Low on D1 activates the RYOUT1 relay driver. Logic Low on D2 activates the<br>RYOUT2 relay driver. Logic Low on D3 activates the RYOUT3 relay driver. TTL<br>compatible. |  |

| DA        | Input     | Ring-trip negative. Negative input to ring-trip comparator.                                                                                                                                                                                                         |  |

| DB        | Input     | Ring-trip positive. Positive input to ring-trip comparator.                                                                                                                                                                                                         |  |

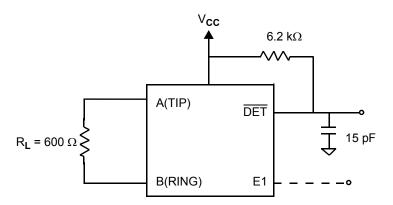

| DET       | Output    | Switchhook detector. Logic Low indicates that selected detector is tripped. Logic inputs C2–C1, E1, and E0 select the detector. Open-collector with a built-in 15 k $\Omega$ pull-up resistor.                                                                      |  |

| HPA       | Capacitor | High-Pass Filter Capacitor. A(TIP) side of high-pass filter capacitor.                                                                                                                                                                                              |  |

| HPB       | Capacitor | High-Pass Filter Capacitor. B(RING) side of high-pass filter capacitor.                                                                                                                                                                                             |  |

| NC        | —         | No Connect. Pin not internally connected.                                                                                                                                                                                                                           |  |

| RD        | Resistor  | Detect resistor. Detector threshold set and filter pin.                                                                                                                                                                                                             |  |

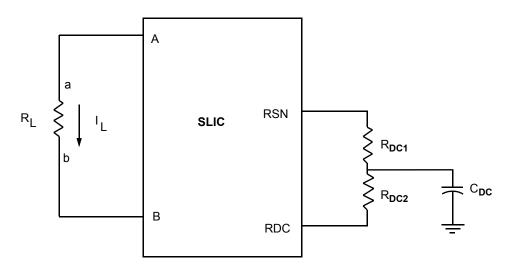

| RDC       | Resistor  | DC feed resistor. Connection point for the DC feed current programming network. The other end of the network connects to the receiver summing node (RSN).                                                                                                           |  |

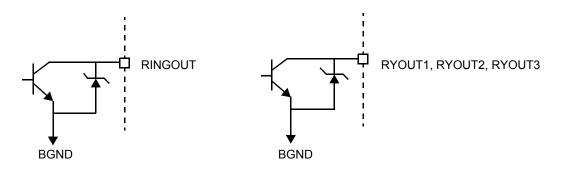

| RINGOUT   | Output    | Ring Relay Driver. Open-collector driver with emitter internally connected to BGND.                                                                                                                                                                                 |  |

| RSN       | Input     | Receive Summing Node. The metallic current (both AC and DC) between A(TIP) and B(RING) is equal to 500 times the current into this pin. The networks that program receive gain, two-wire impedance, and feed resistance all connect to this node.                   |  |

| RYOUT1    | Output    | Relay/Switch Driver. Open-collector driver with emitter internally connected to BGND.                                                                                                                                                                               |  |

| RYOUT2    | Output    | Relay/Switch Driver. Open-collector driver with emitter internally connected to BGND (PLCC only).                                                                                                                                                                   |  |

| RYOUT3    | Output    | Relay/Switch Driver. Open-collector driver with emitter internally connected to BGND (PLCC only).                                                                                                                                                                   |  |

| TMG       | _         | Thermal Management. External resistor connects between this pin and VBAT to offload power from SLIC.                                                                                                                                                                |  |

| VBAT      | Battery   | Battery supply and connection to substrate.                                                                                                                                                                                                                         |  |

| VBREF     | _         | This is an Zarlink reserved pin and must always be connected to the VBAT pin.                                                                                                                                                                                       |  |

| VCC       | Power     | +5 V power supply.                                                                                                                                                                                                                                                  |  |

| VTX       | Output    | Transmit Audio. This output is a 0.50 gain version of the A(TIP) and B(RING) metallic voltage. VTX also sources the two-wire input impedance programming network.                                                                                                   |  |

# **ABSOLUTE MAXIMUM RATINGS**

| Storage temperature55°C to +150°C                                                        |

|------------------------------------------------------------------------------------------|

| $V_{\mbox{\rm CC}}$ with respect to AGND/DGND –0.4 V to +7.0 V                           |

| V <sub>BAT</sub> with respect to AGND/DGND:<br>Continuous                                |

| 10 ms +0.4 V to –75 V                                                                    |

| BGND with respect to AGND/DGND +3 V to –3 V                                              |

| A(TIP) or B(RING) to BGND:                                                               |

| ContinuousV <sub>BAT</sub> to +1 V                                                       |

| 10 ms (f = 0.1 Hz)                                                                       |

| 1 µs (f = 0.1 Hz)80 V to +8 V<br>250 ns (f = 0.1 Hz)90 V to +12 V                        |

| Current from A(TIP) or B(RING)±150 mA                                                    |

| RINGOUT/RYOUT1,2,3 current                                                               |

| RINGOUT/RYOUT1,2,3 voltage BGND to +7 V                                                  |

| RINGOUT/RYOUT1,2,3 transient BGND to +10 V                                               |

| DA and DB inputs                                                                         |

| Voltage on ring-trip inputsV <sub>BAT</sub> to 0 V                                       |

| Current into ring-trip inputs±10 mA                                                      |

| C2–C1 and D3–D1<br>Input voltage–0.4 V to V <sub>cc</sub> + 0.4 V                        |

|                                                                                          |

| Maximum power dissipation, continuous,<br>T <sub>A</sub> = 70°C, No heat sink (See note) |

| In 32-pin PLCC package1.7 W                                                              |

| Thermal Data: $\theta_{JA}$                                                              |

| In 32-pin PLCC package43°C/W typ                                                         |

| ESD immunity/pin (HBM)1500 V                                                             |

**Note:** Thermal limiting circuitry on chip will shut down the circuit at a junction temperature of about 165°C. Continuous operation above 145°C junction temperature may degrade device reliability.

Stresses above those listed under "Absolute Maximum Ratings" can cause permanent device failure. Functionality at or above these limits is not implied. Exposure to absolute maximum ratings for extended periods may affect device reliability.

## **OPERATING RANGES**

The operating ranges define those limits between which the functionality of the device is guaranteed.

| Commercial (C) Devices            |                      |

|-----------------------------------|----------------------|

| Ambient temperature               | 0°C to +70°C*        |

| V <sub>CC</sub>                   | 4.75 V to 5.25 V     |

| V <sub>BAT</sub>                  | –19 V to –58 V       |

| AGND/DGND                         | 0 V                  |

| BGND with respect to<br>AGND/DGND | –100 mV to +100 mV   |

| Load resistance on VTX to grou    | ind20 k $\Omega$ min |

\* Zarlink guarantees the performance of this device over commercial (0 to 70° C) and industrial (-40 to 85°C) temperature ranges by conducting electrical characterization over each range and by conducting a production test with single insertion coupled to periodic sampling. These characterization and test procedures comply with section 4.6.2 of Bellcore GR-357-CORE Component Reliability Assurance Requirements for Telecommunications Equipment.

#### Package Assembly

The standard (non-green) package devices are assembled with industry-standard mold compounds, and the leads possess a tin/ lead (Sn/Pb) plating. These packages are compatible with conventional SnPb eutectic solder board assembly processes. The peak soldering temperature should not exceed 225°C during printed circuit board assembly.

The green package devices are assembled with enhanced environmental compatible lead (Pb), halogen, and antimony-free materials. The leads possess a matte-tin plating which is compatible with conventional board assembly processes or newer lead-free board assembly processes. The peak soldering temperature should not exceed 245°C during printed circuit board assembly.

Refer to IPC/JEDEC J-Std-020B Table 5-2 for the recommended solder reflow temperature profile

# **ELECTRICAL CHARACTERISTICS**

| Description                                     | Description Test Conditions (See Note 1)                                                                                                     |                            |            | Max            | Unit  | Note   |

|-------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|------------|----------------|-------|--------|

| Transmission Performance                        |                                                                                                                                              | •                          |            |                | •     |        |

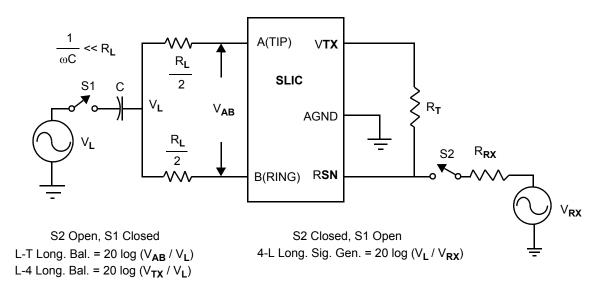

| 2-wire return loss                              | 200 Hz to 3.4 kHz                                                                                                                            | 26                         |            |                | dB    | 1, 4   |

| Analog output (VTX) impedance                   |                                                                                                                                              |                            | 3          | 20             | Ω     | 4      |

| Analog (VTX) output offset voltage              |                                                                                                                                              | -50                        |            | +50            | mV    |        |

| Overload level, 2-wire and 4-wire               | Active state                                                                                                                                 | 2.5                        |            |                | Vpk   | 2a     |

| Overload level                                  | On hook, $R_{LAC}$ = 600 $\Omega$                                                                                                            | 0.77                       |            |                | Vrms  | 2b     |

| THD, Total Harmonic Distortion                  | 0 dBm<br>+7 dBm                                                                                                                              |                            | -64<br>-55 | -50<br>-40     | dB    | 5      |

| THD, On hook                                    | 0 dBm, R <sub>LAC</sub> = 600 Ω                                                                                                              |                            |            | -36            |       |        |

| Longitudinal Capability (See Test Cir           | cuit D)                                                                                                                                      | 1                          |            |                |       |        |

| Longitudinal to<br>metallic L-T, L-4<br>balance | 200 Hz to 1 kHz         0°C to +70°C       -1*         0°C to +70°C       -2         -40°C to +85°C       -1         -40°C to +85°C       -2 | 52<br>63<br>50<br>58       |            |                |       | 4<br>4 |

| Longitudinal signal generation 4-L              | 1 kHz to 3.4 kHz<br>0°C to +70°C -1*<br>0°C to +70°C -2<br>-40°C to +85°C -1<br>-40°C to +85°C -2<br>200 Hz to 3.4 kHz                       | 52<br>58<br>50<br>53<br>40 |            |                | dB    | 4      |

| Longitudinal current per pin (A or B)           | Active state                                                                                                                                 | 20                         | 27         | 35             | mArms | 8      |

| Longitudinal impedance at A or B                | 0 to 100 Hz                                                                                                                                  |                            | 25         |                | Ω/pin |        |

| Idle Channel Noise                              |                                                                                                                                              | 1                          |            |                |       |        |

| C-message weighted noise                        | $R_L = 600 \Omega$ 0°C to +70°C $R_L = 600 \Omega$ -40°C to +85°C                                                                            |                            | 7          | +10<br>+12     | dBrnc | 4      |

| Psophometric weighted noise                     | $R_L = 600 \Omega$ 0°C to +70°C $R_L = 600 \Omega$ -40°C to +85°C                                                                            |                            | -83        | 80<br>78       | dBmp  | 4      |

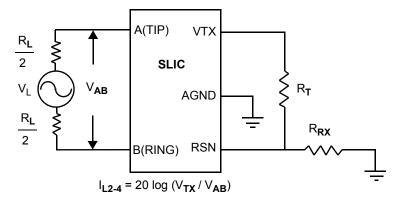

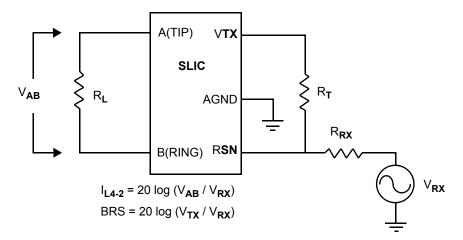

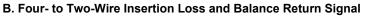

| Insertion Loss and Balance Return S             | Signal (See Test Circuits A and B)                                                                                                           |                            |            |                |       |        |

| Gain accuracy<br>4- to 2-wire                   | 0 dBm, 1 kHz                                                                                                                                 | -0.20                      | 0          | +0.20          |       |        |

| Gain accuracy<br>2- to 4-wire, 4- to 4-wire     | 0 dBm, 1 kHz                                                                                                                                 | -6.22                      | -6.02      | -5.82          |       |        |

| Gain accuracy, 4- to 2-wire                     | On hook                                                                                                                                      | -0.35                      |            | +0.35          |       | 4      |

| Gain accuracy, 2- to 4-wire, 4- to 4-wire       | On hook –6                                                                                                                                   |                            | -6.02      | -5.67          | dB    | 4      |

| Gain accuracy over frequency                    | 300 to 3.4 kHz         -0.15         +0.15           relative to 1 kHz         -0.15         +0.15                                           |                            |            |                |       |        |

| Gain tracking                                   | +3 dBm to –55 dBm<br>relative to 0 dBm                                                                                                       | -0.15                      |            | +0.15          |       |        |

| Gain tracking<br>On hook                        | 0 dBm to –37 dBm<br>+3 dBm to 0 dBm                                                                                                          | -0.15<br>-0.35             |            | +0.15<br>+0.35 |       |        |

| Group delay                                     | 0 dBm, 1 kHz                                                                                                                                 | 1                          | 4          |                | μs    | 4, 7   |

Note:

\* Performance Grade

# ELECTRICAL CHARACTERISTICS (continued)

| Description                                                   | Test Conditions (See Note 1)                                                           | Min               | Тур                 | Мах               | Unit  | Note |

|---------------------------------------------------------------|----------------------------------------------------------------------------------------|-------------------|---------------------|-------------------|-------|------|

| Line Characteristics                                          |                                                                                        |                   |                     |                   |       |      |

| I <sub>L</sub> , Short Loops, Active state                    | R <sub>LDC</sub> = 600 Ω                                                               | 20                | 23                  | 26                |       |      |

| I <sub>L</sub> , Long Loops, Active state                     | R <sub>LDC</sub> = 1930 Ω, BAT = –42.75 V,<br>T <sub>A</sub> = 25°C                    | 18                | 19                  |                   |       |      |

| I <sub>L</sub> , Accuracy, Standby state                      | $I_{L} = \frac{ BAT  - 3 V}{R_{L} + 400}$ $T_{A} = 25^{\circ}C$                        | 0.71 <sub>L</sub> | ١L                  | 1.3I <sub>L</sub> | mA    |      |

|                                                               | Constant-current region                                                                | 18                | 30                  |                   |       |      |

| I <sub>L</sub> , Loop current, Disconnect state               | R <sub>L</sub> = 0                                                                     |                   |                     | 100               | μA    |      |

| ILLIM                                                         | Active, A and B to ground                                                              |                   | 85                  | 120               | mA    |      |

| VAB, Open Circuit voltage                                     | V <sub>BAT</sub> = -52 V                                                               | -42.75            | -44                 |                   | V     |      |

| Power Supply Rejection Ratio (V <sub>R</sub>                  | <sub>IPPLE</sub> = 100 mVrms), Active Normal Stat                                      | te                |                     |                   |       |      |

| V <sub>cc</sub>                                               | 50 Hz to 3.4 kHz                                                                       | 30                | 40                  |                   |       | _    |

| V <sub>BAT</sub>                                              | 50 Hz to 3.4 kHz                                                                       | 28                | 50                  |                   | dB    | 5    |

| Effective internal resistance                                 | CAS pin to V <sub>BAT</sub>                                                            | 85                | 170                 | 255               | kΩ    | 4    |

| Power Dissipation                                             |                                                                                        |                   |                     |                   | 1     |      |

| On hook, Disconnect state                                     |                                                                                        |                   | 25                  | 70                |       |      |

| On hook, Standby state                                        |                                                                                        |                   | 35                  | 100               |       |      |

| On hook, Active state                                         |                                                                                        |                   | 125                 | 270               | mW    |      |

| Off hook, Standby state                                       | R <sub>L</sub> = 600 Ω                                                                 |                   | 860                 | 1200              |       |      |

| Off hook, Active state                                        | R <sub>L</sub> = 300 Ω, R <sub>TMG</sub> = 2350 Ω                                      |                   | 450                 | 800               | †     |      |

| Supply Currents, Battery = –48V                               |                                                                                        |                   |                     |                   |       |      |

| I <sub>cc</sub> ,<br>On-hook V <sub>cc</sub> supply current   | Disconnect state<br>Standby state<br>Active state, BAT = -48 V                         |                   | 1.7<br>2.2<br>6.3   | 4.0<br>4.0<br>8.5 |       |      |

| I <sub>BAT</sub> ,<br>On-hook V <sub>BAT</sub> supply current | Disconnect state<br>Standby state<br>Active state, BAT = -48 V                         |                   | 0.25<br>0.55<br>2.8 | 1.0<br>1.5<br>4.8 | mA    |      |

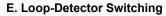

| RFI Rejection                                                 | ·                                                                                      |                   |                     |                   |       |      |

| RFI rejection                                                 | 100 kHz to 30 MHz, (See Figure F)                                                      |                   |                     | 1.0               | mVrms | 4    |

| Receive Summing Node (RSN)                                    |                                                                                        | -                 |                     |                   |       |      |

| RSN DC voltage                                                | I <sub>RSN</sub> = 0 mA                                                                |                   | 0                   |                   | V     | 4    |

| RSN impedance                                                 | 200 Hz to 3.4 kHz                                                                      |                   | 10                  | 20                | Ω     | 4    |

| Logic Inputs (C2–C1 and D3–D1)                                |                                                                                        | -                 |                     |                   |       |      |

| V <sub>IH</sub> , Input High voltage                          |                                                                                        | 2.0               |                     |                   |       |      |

| V <sub>IL</sub> , Input Low voltage                           |                                                                                        |                   |                     | 0.8               | - V - |      |

| I <sub>IH</sub> , Input High current                          |                                                                                        | -75               |                     | 40                |       |      |

| I <sub>IL</sub> , Input Low current                           |                                                                                        | -400              |                     |                   | μA    |      |

| Logic Output (DET)                                            |                                                                                        |                   |                     |                   |       |      |

| V <sub>OL</sub> , Output Low voltage                          | Dutput Low voltage $I_{OUT}$ = 0.3 mA, 15 kΩ to V <sub>CC</sub>                        |                   |                     | 0.40              | V     |      |

| V <sub>OH</sub> , Output High voltage                         | Output High voltage $I_{OUT} = -0.1 \text{ mA}, 15 \text{ k}\Omega \text{ to } V_{CC}$ |                   |                     |                   | V     |      |

| Ring-Trip Detector Input (DA, DB)                             |                                                                                        |                   |                     |                   |       |      |

| Bias current                                                  |                                                                                        | -500              | -50                 |                   | nA    |      |

| Offset voltage                                                | Source resistance = 2 M $\Omega$                                                       | -50               | 0                   | +50               | mV    | 6    |

# **ELECTRICAL CHARACTERISTICS (continued)**

| Description                                 | Min                        | Тур  | Max  | Unit | Note |   |

|---------------------------------------------|----------------------------|------|------|------|------|---|

| Loop Detector                               |                            |      |      |      |      |   |

| On threshold $R_{D} = 35.4 \text{ k}\Omega$ |                            | 11.5 |      | 17.3 |      |   |

| Off threshold                               | R <sub>D</sub> = 35.4 kΩ   | 9.4  |      | 14.1 | mA   |   |

| Hysteresis                                  | R <sub>D</sub> = 35.4 kΩ   | 0    |      | 4.4  |      |   |

| Relay Driver Output (RINGOU                 | T, RYOUT1, RYOUT2, RYOUT3) | •    | •    |      |      | • |

| On voltage                                  | I <sub>OL</sub> = 40 mA    |      | +0.3 | +0.7 | V    |   |

| Off leakage                                 | V <sub>OH</sub> = +5 V     |      |      | 100  | μA   |   |

| Zener breakover                             | I <sub>Z</sub> = 100 μA    | 6    | 7.2  |      | v    |   |

| Zener On voltage                            | I <sub>Z</sub> = 30 mA     |      | 10   |      |      |   |

## **RELAY DRIVER SCHEMATICS**

#### Notes:

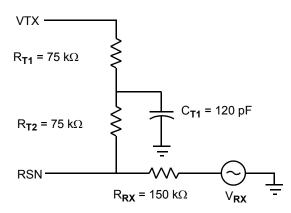

Unless otherwise noted, test conditions are BAT = -52 V, V<sub>CC</sub> = +5 V, R<sub>L</sub> = 600 Ω, R<sub>DC1</sub> = R<sub>DC2</sub> = 27.17 kΩ, R<sub>TMG</sub> = 2350 Ω, R<sub>D</sub> = 35.4 kΩ, no fuse resistors, C<sub>HP</sub> = 0.22 μF, C<sub>DC</sub> = 0.1 μF, C<sub>CAS</sub> = 0.33 μF, D1 = 1N400x, two-wire AC input impedance is a 600 Ω resistance synthesized by the programming network shown below.

- a. Overload level is defined when THD = 1%.

b. Overload level is defined when THD = 1.5%.

- 3. Balance return signal is the signal generated at V<sub>TX</sub> by V<sub>RX</sub>. This specification assumes that the two-wire, AC-load impedance matches the programmed impedance.

- 4. Not tested in production. This parameter is guaranteed by characterization or correlation to other tests.

- 5. This parameter is tested at 1 kHz in production. Performance at other frequencies is guaranteed by characterization.

- 6. Tested with 0  $\Omega$  source impedance. 2  $M\Omega$  is specified for system design only.

- 7. Group delay can be greatly reduced by using a Z<sub>T</sub> network such as that shown in Note 1. The network reduces the group delay to less than 2 µs and increases 2WRL. The effect of group delay on linecard performance also may be compensated for by synthesizing complex impedance with the QSLAC<sup>™</sup> or DSLAC<sup>™</sup> device.

- 8. Minimum current level guaranteed not to cause a false loop detect.

| State | C2 | C1 | Two-Wire Status | DET Output    |  |

|-------|----|----|-----------------|---------------|--|

| 0     | 0  | 0  | Disconnect      | Ring trip     |  |

| 1     | 0  | 1  | Ringing         | Ring trip     |  |

| 2     | 1  | 0  | Active          | Loop detector |  |

| 3     | 1  | 1  | Standby         | Loop detector |  |

## Table 2. User-Programmable Components

| $Z_{\rm T} = 250(Z_{\rm 2WIN} - 2R_{\rm F})$                                                                                                             | $Z_{\rm T}$ is connected between the VTX and RSN pins. The fuse resistors are R <sub>F</sub> , and $Z_{\rm 2WIN}$ is the desired 2-wire AC input impedance. When computing $Z_{\rm T}$ , the internal current amplifier pole and any external stray capacitance between VTX and RSN must be taken into account. |

|----------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $Z_{RX} = \frac{Z_L}{G_{42L}} \bullet \frac{500Z_T}{Z_T + 250(Z_L + 2R_F)}$                                                                              | $Z_{RX}$ is connected from VRX to RSN. $Z_T$ is defined above, and $G_{42L}$ is the desired receive gain.                                                                                                                                                                                                       |

| $R_{DC1} + R_{DC2} = \frac{1250}{I_{LOOP}}$ $C_{DC} = 1.5 \text{ ms} \bullet \frac{R_{DC1} + R_{DC2}}{R_{DC1} \bullet R_{DC2}}$                          | $R_{DC1}$ , $R_{DC2}$ , and $C_{DC}$ form the network connected to the $R_{DC}$ pin. $R_{DC1}$ and $R_{DC2}$ are approximately equal. $I_{LOOP}$ is the desired loop current in the constant-current region.                                                                                                    |

| $RD_{ON} = \frac{510}{I_T}$ , $RD_{OFF} = \frac{415}{I_T}$ , $C_D = \frac{0.5 \text{ ms}}{R_D}$                                                          | $R_D$ and $C_D$ form the network connected from $R_D$ to AGND/ DGND and $I_T$ is the threshold current between on hook and off hook.                                                                                                                                                                            |

| $C_{CAS} = \frac{1}{3.4 \bullet 10^5 \pi f_c}$                                                                                                           | $C_{\mbox{CAS}}$ is the regulator filter capacitor and $f_{\mbox{c}}$ is the desired filter cut-off frequency.                                                                                                                                                                                                  |

| $I_{\text{STANDBY}} = \frac{ V_{\text{BAT}}  - 3 V}{400 \Omega + R_{\text{L}}}$                                                                          | Standby loop current (resistive region).                                                                                                                                                                                                                                                                        |

| Thermal Management Equations (Normal Active and Tip C                                                                                                    | Open States)                                                                                                                                                                                                                                                                                                    |

| $R_{TMG} \ge \left(\frac{ V_{BAT}  - 6 V}{I_{LOOP}} - 70 \Omega\right)$                                                                                  | R <sub>TMG</sub> is connected from TMG to VBAT and saves power within the SLIC in Active and Disconnect state constant-currents only.                                                                                                                                                                           |

| $P_{RTMG} = \frac{\left(\left V_{BAT}\right  - 6 V - \left(I_{L} \bullet R_{L}\right)\right)^{2}}{\left(R_{TMG} + 70 \Omega\right)^{2}} \bullet R_{TMG}$ | Power dissipated in the TMG resistor, R <sub>TMG</sub> , during Active and Disconnect states.                                                                                                                                                                                                                   |

| $P_{SLIC} =  V_{BAT}  \bullet I_L - P_{RTMG} - R_L(I_L)^2 + 0.12 W$                                                                                      | Power dissipated in the SLIC while in Active and Disconnect states.                                                                                                                                                                                                                                             |

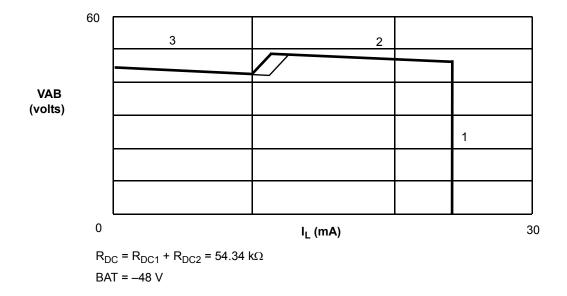

# **DC FEED CHARACTERISTICS**

Notes:

1.

$$V_{AB} = I_L R_L' = \frac{1250}{R_{DC}} R_L'$$

, where  $R_L' = R_L + 2R_F$

2.

$$V_{AB} = 0.857(|V_{BAT}| + 3.3) - I_L \frac{R_{DC}}{300}$$

**3.**

$$V_{AB} = 0.857(|V_{BAT}| + 1.2) - I_L \frac{R_{DC}}{300}$$

a. Load Line (Typical)

Feed current programmed by  $\mathsf{R}_{\mathsf{DC1}}$  and  $\mathsf{R}_{\mathsf{DC2}}$

b. Feed Programming

Figure 1. DC Feed Characteristics

# **TEST CIRCUITS**

A. Two- to Four-Wire Insertion Loss

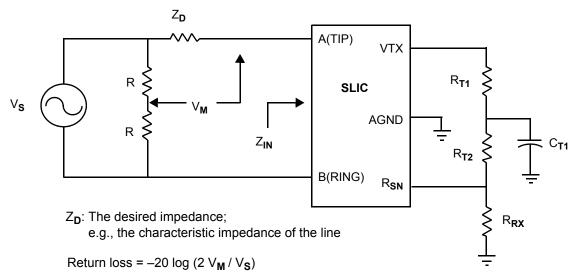

C. Longitudinal Balance

# **TEST CIRCUITS (continued)**

#### D. Two-Wire Return Loss Test Circuit

## **TEST CIRCUITS (continued)**

G. Le7920 Test Circuit

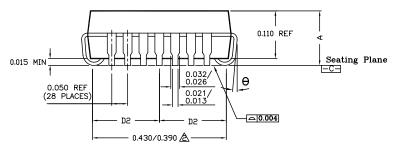

# PHYSICAL DIMENSIONS 32-Pin PLCC

| 32-Pin PLCC    |           |       |        | 1           |

|----------------|-----------|-------|--------|-------------|

| JEDEC # MS-016 |           |       |        |             |

| Symbol         | Min       | Nom   | Max    | <u>/2</u> \ |

| A              | 0.125     |       | 0.140  | $\wedge$    |

| A1             | 0.075     | 0.090 | 0.095  | <u>/</u> 3\ |

| D              | 0.485     | 0.490 | 0.495  |             |

| D1             | 0.447     | 0.450 | 0.453  |             |

| D2             | 0.205 REF |       |        |             |

| E              | 0.585     | 0.590 | 0.595  | ~           |

| E1             | 0.547     | 0.550 | 0.553  |             |

| E2             | 0.255 REF |       |        |             |

| θ              | 0 deg     |       | 10 deg |             |

NOTES:

- Dimensioning and tolerancing conform to ASME Y14,5M-1994.

- To be measured at seating plan C contact point.

- Dimensions "D1" and "E1" do not include mold protrusion. Allowable mold protrusion is 0.010 inch per side. Dimensions "D" and "E" include mold mismatch and determined at the parting line; that is "D1" and "E1" are measured at the extreme material condition at the upper or lower parting line.

- Exact shape of this feature is optional.

Details of pin 1 identifier are optional but must be located within the zone indicated.

- 6 Sum of DAM bar protrusions to be 0.007 max per lead.

- Controlling dimension : Inch. 7

- 8 Reference document : JEDEC MS-016

## 32-Pin PLCC

#### Note:

Packages may have mold tooling markings on the surface. These markings have no impact on the form, fit or function of the device. Markings will vary with the mold tool used in manufacturing.

#### 17

#### Zarlink Semiconductor Inc.

# **REVISION SUMMARY**

# **Revision C to Revision D**

• Minor changes were made to the datasheet style and format to conform to Zarlink standards.

# **Revision D to Revision E**

Absolute Maximum Ratings: Added ESD immunity specification.

## **Revision E to Revision F**

• Added the 28-pin SOIC connection diagram and the SC option to the ordering information.

# **Revision F to Revision G**

• The physical dimension (PL032) was added to the Physical Dimension section.

# **Revision G to Revision H**

- Deleted the plastic DIP package and references to it.

- Updated the Pin Description table to correct inconsistencies.

# **Revision H to Revision I**

- Updated device name from "Am7920" to "Le7920" throughout document.

- Absolute Maximum Ratings: Notes updated to standard.

- Operating Ranges: Temperature statement updated to standard.

- Updated "Sales Office Listing."

- Updated physical dimension drawings.

## Revision I1 to Revision J1

- Added green package OPN to <u>Ordering Information</u>, on page 3

- Added <u>Package Assembly</u> on page 7

- Updated 32-pin PLCC drawing in <u>Physical Dimensions</u>, on page 17

- Removed SOIC package information

# **Revision J1 to Revision J2**

- Enhanced format of package drawing in *Physical Dimensions*, on page 17

- Added new headers/footers due to Zarlink purchase of Legerity on August 3, 2007

# For more information about all Zarlink products visit our Web Site at

## www.zarlink.com

Information relating to products and services furnished herein by Zarlink Semiconductor Inc. or its subsidiaries (collectively "Zarlink") is believed to be reliable. However, Zarlink assumes no liability for errors that may appear in this publication, or for liability otherwise arising from the application or use of any such information, product or service or for any infringement of patents or other intellectual property rights owned by third parties which may result from such application or use. Neither the supply of such information or purchase of product or service conveys any license, either express or implied, under patents or other intellectual property rights owned by Zarlink or licensed from third parties by Zarlink, whatsoever. Purchasers of products are also hereby notified that the use of product in certain ways or in combination with Zarlink, or non-Zarlink furnished goods or services may infringe patents or other intellectual property rights owned by Zarlink.

This publication is issued to provide information only and (unless agreed by Zarlink in writing) may not be used, applied or reproduced for any purpose nor form part of any order or contract nor to be regarded as a representation relating to the products or services concerned. The products, their specifications, services and other information appearing in this publication are subject to change by Zarlink without notice. No warranty or guarantee express or implied is made regarding the capability, performance or suitability of any product or service. Information concerning possible methods of use is provided as a guide only and does not constitute any guarantee that such methods of use will be satisfactory in a specific piece of equipment. It is the user's responsibility to fully determine the performance and suitability of any equipment using such information and to ensure that any publication or data used is up to date and has not been superseded. Manufacturing does not necessarily include testing of all functions or parameters. These products are not suitable for use in any medical products whose failure to perform may result in significant injury or death to the user. All products and materials are sold and services provided subject to Zarlink's conditions of sale which are available on request.

Purchase of Zarlink's l2C components conveys a license under the Philips l2C Patent rights to use these components in an l2C System, provided that the system conforms to the l2C Standard Specification as defined by Philips.

Zarlink, ZL, the Zarlink Semiconductor logo and the Legerity logo and combinations thereof, VoiceEdge, VoicePort, SLAC, ISLIC, ISLAC and VoicePath are trademarks of Zarlink Semiconductor Inc.

TECHNICAL DOCUMENTATION - NOT FOR RESALE