# Multistandard TV digital video decoder with adaptive comb filter and RGB/YCrCb input

#### **Features**

- **■** Worldwide TV Standards Compatible

- Automatic NTSC/PAL/SECAM Digital Chroma Decoder

- NTSC/PAL Adaptive 4H/2D Comb Filter

- VBI Data Slicer for Teletext, Closed Caption, WSS and other systems

- Analog RGB/Fast Blanking Capture and Insertion in YCrCb Output Flow (SCART legacy)

- Analog YCrCb inputs with Tint Control

- 10-bit, 30-MSPS A/D Converter for Y/CVBS input

- 8-bit, 30-MSPS A/D Converter for C and RGB/ CrCb inputs

- Hue control and automatic flesh control for NTSC CVBS/YC signals

- Programmable Horizontal Scaling (x0.25 to x4 Scaling Factor) and Panorama Vision

- Copy-Protection System compatible

- H and V Synchronisation Processing that is robust to non-standard sources such as VCR, and to weak and noisy signals

- 8-bit Pixel Output Interface Line-Locked ITU-R BT\_656/601 or square pixel YCrCb outputs

- Single System Crock for all Video Input Formats

- Two-:v/re I-C Bus Interface up to 400 kHz

- ▼ 7 p cal Power Consumption: 550 mW

- Ower Supply: 1.8 V and 3.3 V

TQFP64 14x14x1.4 mm (Thin Quad Flat Package)

ORDER CODE: STV2310D/.)1

TQFP64 10x10x1.4 mm (Thin Quad Flat Package)

ORDER CODE: STV2310SD/SDT

The STV2310 is a high-quality front-end video circuit for processing all analog NTSC/PAL/SECAM standards into a 4:2:2 YCrCb digital video format ,as well as conventional analog RGB or YCrCb signals. The STV2310 is programmable through an I<sup>2</sup>C interface.

The STV2310 provides a cost-effective solution for digitized TV, LCD TV/monitors, digital TV, STB, video surveillance/security, video conferencing, video capturing devices and PC video card.

It can be used as a stand-alone chip working with third-party products, as a companion chip to the TV processor STV3500, STV3600 for digitized 100-Hz/ProScan CRT TVs, or as a companion chip to the TV processor STV3550 for LCD-TVs.

November 2008 Rev 4 1/113

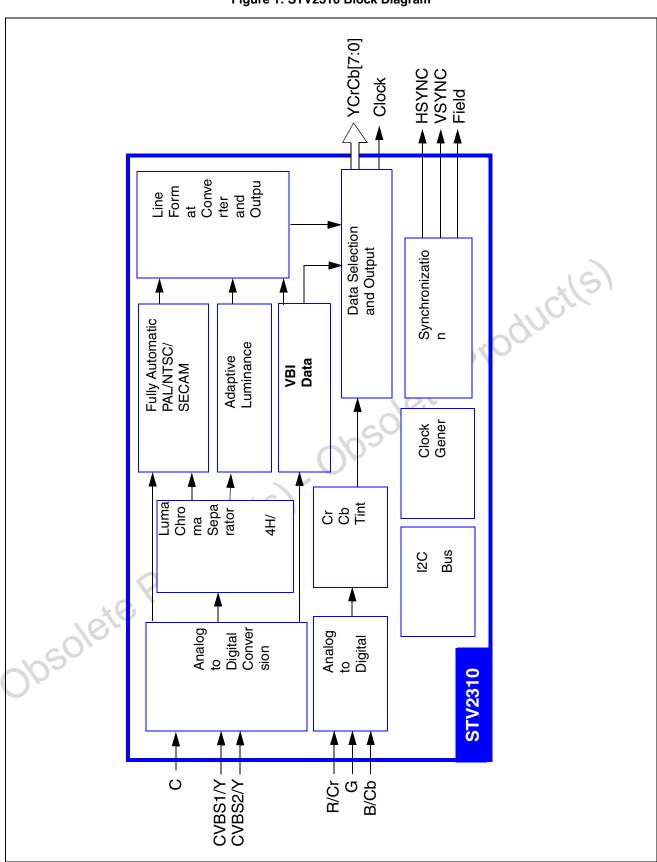

Figure 1: STV2310 Block Diagram

# **Table of Contents**

| Chapter 1 | General Description                                                               |          |

|-----------|-----------------------------------------------------------------------------------|----------|

| Chapter 2 | Pin Allocation and Description                                                    |          |

| 2.1       | Pinout Diagram                                                                    | 9        |

| 2.2       | Pin Descriptions                                                                  | 9        |

| Chapter 3 | Default Setup At Reset                                                            |          |

| 3.1       | System Clock Generation                                                           | 13       |

| Chapter 4 | Functional Description                                                            |          |

| 4.1       | Analog Input Stage                                                                | 14<br>16 |

| 4.2       | Synchronization and Monitoring Unit  4.2.1 General Description  4.2.2 Programming | 16<br>17 |

| 4.3       | Input Sample Rate Conversion                                                      | 18       |

| 4.4       | Luminance and Chrominance Separation                                              | 19       |

| 4.5       | Standard Research Sequence Programming                                            | 21       |

| 4.6       | Standard Identification                                                           | 23       |

| 4.7       | Chroma Demodulation  4.7.1 General Description  4.7.2 Programming                 | 23       |

| 4.8       | Soft Mixer                                                                        | 24       |

| 10GC      | 4.8.1 General Description                                                         |          |

| 4.9       | Output Scaler and Format Converter  4.9.1 General Description  4.9.2 Programming  | 25       |

| 4.10      | RGB Insertion                                                                     |          |

|           | 4.10.1 General Description                                                        |          |

| 4.11      | Analog YCrCb Mode                                                                 | 29       |

|            |       | 4.11.1 General Description                              |      |

|------------|-------|---------------------------------------------------------|------|

|            | 4.12  | Output FIFO and Line-locked Ouput Pixel Clock Generator | 29   |

|            |       | 4.12.1 General Description                              |      |

|            |       | 4.12.2 Output Data                                      |      |

|            |       | 4.12.3 Insertion of Ancillary Data                      |      |

|            |       | 4.12.5 Alternate Functions: Bus Extensions              |      |

|            |       | 4.12.6 Output Code Clipping                             |      |

|            |       | 4.12.7 Programming                                      | 41   |

|            | 4.13  | VBI Data Slicing and Insertion                          |      |

|            |       | 4.13.1 VBI Formatting Features                          |      |

|            | 4.14  | 4.13.2 Data Output Format (DOF)                         |      |

|            |       | ·                                                       |      |

| Chap       | ter 5 | Register List                                           | . 55 |

|            | 5.1   | Register Map                                            | 55   |

|            | 5.2   | Non-VBI Control Register Descriptions                   | 59   |

|            | 5.3   | VBI Control Register Descriptions                       | 87   |

|            | 5.4   | Acknowledge Registers                                   | 96   |

|            | 5.5   | Status Registers                                        | 97   |

| Chap       | tor 6 | Electrical Characteristics                              | 101  |

| Chap       |       | Absolute Maximum Ratings                                | 101  |

|            | 6.1   |                                                         |      |

|            | 6.2   | Thermal Data                                            |      |

|            | 6.3   | Operating Conditions                                    | 101  |

|            | 6.4   | CVBS/Y/C Analog Inputs                                  | 101  |

|            | 6.5   | R/G/B and Cr/Cb Inputs                                  | 102  |

|            | 6.6   | FB Input                                                | 103  |

|            | 6.7   | Analog-to-Digital Converter (ADC)                       | 103  |

| -10        | 6.8   | Analog Reference Levels                                 | 103  |

| $O_{\ell}$ | 6.9   | YCrCb, Hsync, Vsync, Field and PLL Lock Outputs         | 103  |

|            | 6.10  | Clock Data Output                                       | 104  |

|            | 6.11  | CLKSEL, TST_MODE, NRESET and I2CADD Inputs              | 104  |

|            | 6.12  | Main Clock Characteristics                              | 104  |

|            | 6.13  | Horizontal/Vertical Synchronization Block               | 106  |

|            | 6.14  | Chroma Block                                            | 106  |

|            |       |                                                         |      |

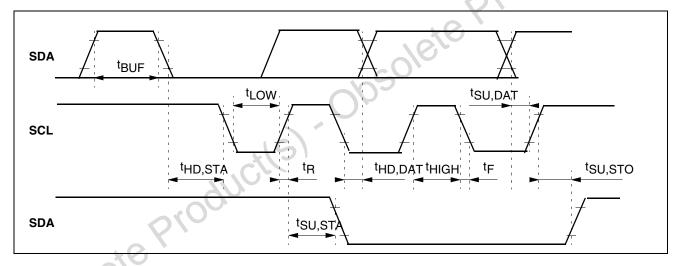

|            | 6.15  | I <sup>2</sup> C Bus Characteristics                    | .106 |

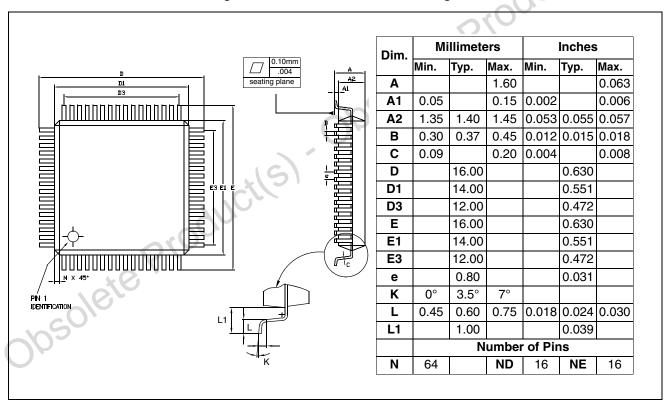

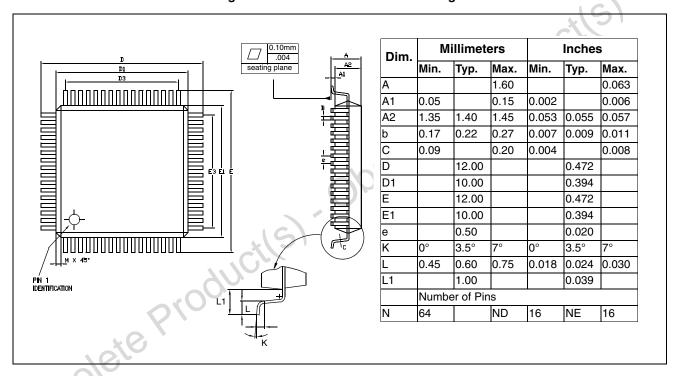

| Chapter 7 | Package Mechanical Data | 108 |

|-----------|-------------------------|-----|

| 7.1       | TQFP64 14x14 Package    | 108 |

| 7.2       | TQFP64 10x10 Package    | 109 |

| 7.3       | Lead-free Packaging     | 109 |

| Chapter 8 | Revision History        |     |

General Description STV2310

# 1 General Description

The STV2310 is a high-quality video front-end circuit for processing all analog standards into a digitalized 4:2:2 YCrCb video format. It processes NTSC/PAL/SECAM CVBS signals, as well as conventional analog RGB or YCrCb signals.

This circuit outputs demodulated chrominance, in-phased luminance and sliced Vertical Blanking Interval (VBI) data for the most common services such as Teletext, Closed Caption, WSS, VPS, Gemstar.

The STV2310 does not need an external synchronization system. It extracts all necessary synchronization signals from CVBS or Y signals, and delivers the horizontal, vertical and frame signals either on dedicated pins or embedded into the digital bit stream.

It features automatic standard recognition and automatic selection of the optimal Y/C separation algorithm according to the standard and has extensive output scaling capabilities. The STV2310 chip includes an analog RGB capture feature and programmable automatic mixing with the main picture digital output.

8-bit ITU-R BT.601/656 and Square Pixel output standards are supported.

The STV2310 provides a cost-effective solution for digitized TV, LCD TV/monitors, digital TV, STB, video surveillance/security, video conferencing, video capturing devices and PC video card.

It can be used as a stand-alone chip working with third-party products, as a companion chip to the TV processor STV3500, STV3600 for digitized 100-Hz/ProScan CRT TVs, or as a companion chip to the TV processor STV3550 for LCD-TVs.

All sub-level blocks operate at the frequency used as a sampling frequency (f<sub>S</sub>) for the five embedded A/D converters. This free-running clock is called the system clock (f<sub>S</sub>) and is provided

either by an embedded crystal oscillator or an external clock generator (27 MHz). The only exception is the output stage which operates at the line-locked output pixel clock frequency.

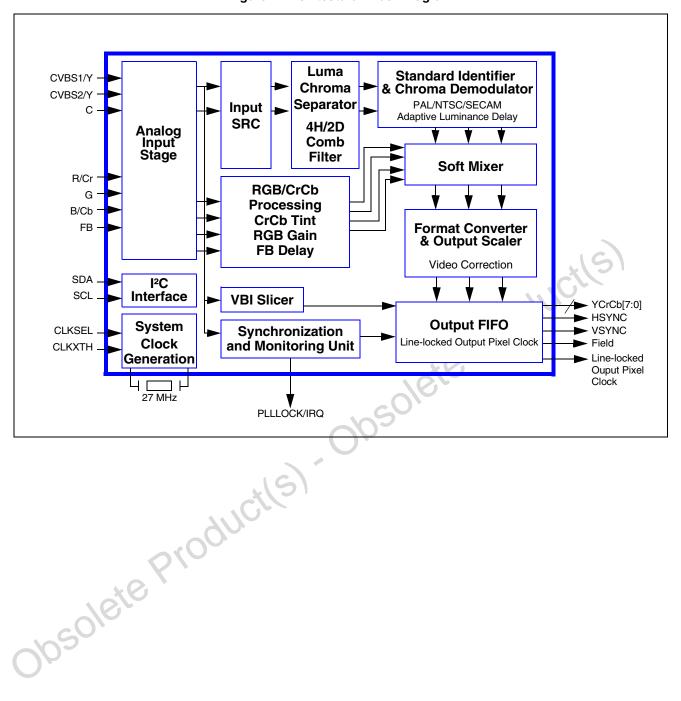

Figure 2: Architectural Block Diagram

General Description STV2310

1.8 V<sub>ANA</sub> 1.8 V<sub>ANA</sub> 150 Ω τ√√ 60 64 62 61 1.8 V<sub>ANA</sub> CVBS1/Y- $\mathbf{V}_{\mathsf{REF}}$ **ADC** CVBS2/Y-10 1.8 V<sub>ANA</sub> ADC  $3.3 \stackrel{\smile}{V}_{ANA}$ 15 SHIELD Chroma/Luma **VBI** 8 **Data Slicer Processing** ADC <sup>8</sup> 3.3 V<sub>OUT</sub> B\_CB Optional **Data Formatting** 1.8 V<sub>ANA</sub> 26 25 Y Cr Cb Output 20 19

**Digital Core**

CLKSEL

1.8 V<sub>ANA</sub>  $\stackrel{1}{\circlearrowleft}$

\* Possible alternate I<sup>2</sup>C address. See Section 5.1: Register Map on page 55.

**Synchronization and Monitoring**

Time Base

Figure 3: Application Block Diagram

CLKXTM TST\_MODE

**HSYNC**

**VSYNC**

**FIELD**

**PLLLOCK**

CLK\_DATA

1.8 V<sub>OUT</sub>

35

SCL

SDA

3.3 V<sub>ANA</sub> 9

NRESET

I2CADD\*

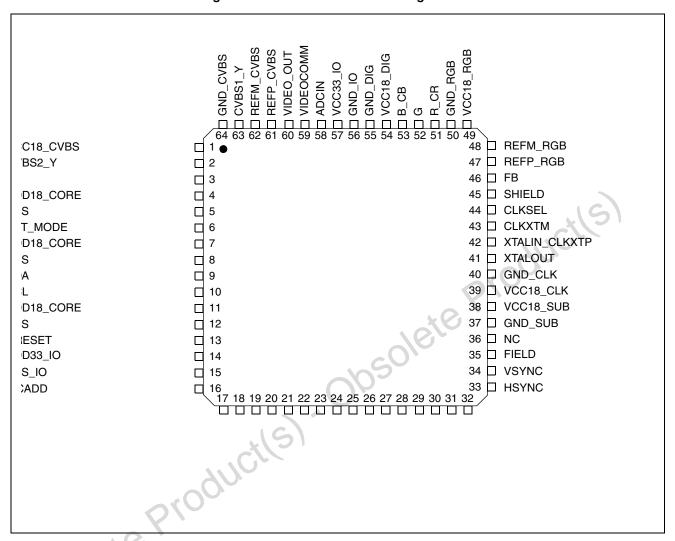

# 2 Pin Allocation and Description

## 2.1 Pinout Diagram

Figure 4: 64-Pin 14 x 14 TQFP Package Pinout

# 2.2 Pin Descriptions

Table 1: Power Supply Pins (page 1 of 2)

| Pin    | Pin Name   | Pin Description                                              |  |  |

|--------|------------|--------------------------------------------------------------|--|--|

| Analog | I          |                                                              |  |  |

| 1      | VCC18_CVBS | 1.8 V Analog Voltage Supply for Analog Input Stage           |  |  |

| 36     | NC         | Not connected                                                |  |  |

| 37     | GND_SUB    | Analog Ground Supply (Substrate Polarization)                |  |  |

| 38     | VCC18_SUB  | 1.8 V Analog Voltage Supply (Output and Pin Isolation layer) |  |  |

| 39     | VCC18_CLK  | 1.8 V Analog Voltage Supply for Clock Generator              |  |  |

Table 1: Power Supply Pins (page 2 of 2)

| Pin     | Pin Name   | Pin Description                                                         |  |  |

|---------|------------|-------------------------------------------------------------------------|--|--|

| 40      | GND_CLK    | Analog Ground Supply for Clock Generator                                |  |  |

| 45      | SHIELD     | Guard Ring (Analog Input Stage) To be connected to Analog Ground Supply |  |  |

| 49      | VCC18_RGB  | 1.8 V Analog Voltage Supply (RGB)                                       |  |  |

| 50      | GND_RGB    | Analog Ground Supply (RGB)                                              |  |  |

| 54      | VCC18_DIG  | 1.8 V Analog Voltage Supply (Analog Input Stage)                        |  |  |

| 55      | GND_DIG    | Analog Ground Supply (Analog Input Stage)                               |  |  |

| 56      | GND_IO     | Analog Ground Supply (Analog Input Stage)                               |  |  |

| 57      | VCC33_IO   | 3.3 V Analog Voltage Supply (Analog Input Stage)                        |  |  |

| 64      | GND_CVBS   | Analog Ground Supply (Analog Input Stage)                               |  |  |

| Digital |            |                                                                         |  |  |

| 4       | VDD18_CORE | 1.8 V Digital Voltage Supply (Digital Core)                             |  |  |

| 5       | VSS        | Digital Ground Supply (Digital Core)                                    |  |  |

| 7       | VDD18_CORE | 1.8 V Digital Voltage Supply (Digital Core)                             |  |  |

| 8       | VSS        | Digital Ground Supply (Digital Core)                                    |  |  |

| 11      | VDD18_CORE | 1.8 V Digital Voltage Supply (Digital Core)                             |  |  |

| 12      | VSS        | Digital Ground Supply (Digital Core)                                    |  |  |

| 14      | VDD33_IO   | 3.3 V I/O Voltage Supply (Digital Core)                                 |  |  |

| 15      | VSS_IO     | I/O Ground Supply                                                       |  |  |

| 17      | VDD18_CORE | 1.8 V Digital Voltage Supply (Digital Core)                             |  |  |

| 18      | VSS        | Digital Ground Supply (Digital Core)                                    |  |  |

| 23      | VSS_IOOUT  | Output Ground Supply (Output Stage)                                     |  |  |

| 24      | VDD33_OUT  | 3.3 V Output Voltage Supply (Output Stage)                              |  |  |

| 29      | VDD18_OUT  | 1.8 V Digital Voltage Supply (Output Stage)                             |  |  |

| 30      | VSS_OUT    | Digital Ground Supply (Output Stage)                                    |  |  |

Table 2: Analog Pins (page 1 of 2)

| Pin | Pin Name | Pin Description                                                                   |  |  |

|-----|----------|-----------------------------------------------------------------------------------|--|--|

| 2   | CVBS2_Y  | CVBS or Y Input 2 (Selected by programming)                                       |  |  |

| 3   | С        | Chroma Input (Y/C inputs used for S-Video) (Selected by programming)              |  |  |

| 46  | FB       | Fast Blanking Input (To be used only when R_CR, G, and B_CB inputs are connected) |  |  |

| 47  | REFP_RGB | Positive Reference Voltage for RGB ADCs                                           |  |  |

| 48  | REFM_RGB | Negative Reference Voltage for RGB ADCs                                           |  |  |

| 51  | R_CR     | R Input for RGB Insertion. Cr Input for Analog YCrCb mode.                        |  |  |

| 52  | G        | G Input for RGB Insertion.                                                        |  |  |

| 53  | B_CB     | B Input for RGB Insertion. Cb Input for Analog YCrCb mode.                        |  |  |

47/

Table 2: Analog Pins (page 2 of 2)

| Pin | Pin Name  | Pin Description                                                  |  |  |

|-----|-----------|------------------------------------------------------------------|--|--|

| 58  | ADCIN     | CVBS ADC Input (To be connected to Anti-Aliasing Filter output)  |  |  |

| 59  | VIDEOCOMM | VBS Anti-Aliasing Filter Reference Voltage                       |  |  |

| 60  | VIDEO_OUT | Video Analog Front-end Multiplexer Output for external filtering |  |  |

| 61  | REFP_CVBS | Positive Reference Voltage for CVBS and Chroma ADCs              |  |  |

| 62  | REFM_CVBS | Ground CVBS and Chroma ADCs                                      |  |  |

| 63  | CVBS1_Y   | CVBS or Y Input 1 (Selected by programming)                      |  |  |

**Table 3: Output Pins**

| Pin | Pin Name    | Туре | Pin Description                                                                                                     |  |  |

|-----|-------------|------|---------------------------------------------------------------------------------------------------------------------|--|--|

| 19  | YCRCB7      | 0    | Digital Video Output 7                                                                                              |  |  |

| 20  | YCRCB6      | 0    | Digital Video Output 6                                                                                              |  |  |

| 21  | YCRCB5      | 0    | Digital Video Output 5                                                                                              |  |  |

| 22  | YCRCB4      | 0    | Digital Video Output 4                                                                                              |  |  |

| 25  | YCRCB3      | 0    | Digital Video Output 3                                                                                              |  |  |

| 26  | YCRCB2      | 0    | Digital Video Output 2                                                                                              |  |  |

| 27  | YCRCB1      | 0    | Digital Video Output 1                                                                                              |  |  |

| 28  | YCRCB0      | 0    | Digital Video Output 0                                                                                              |  |  |

| 31  | CLK_DATA    | 0    | Output Pixel Clock, active edge is programmable                                                                     |  |  |

| 32  | PLLLOCK/IRQ | 0    | Output PLL Lock Signal Alternate Function 1: OUTBUS[0] Bus extension Alternate Function 2: Interrrupt Request (IRQ) |  |  |

| 33  | HSYNC       | 0    | Horizontal Synchronization Pulse Output Alternate Function: OUTBUS[1] Bus extension                                 |  |  |

| 34  | VSYNC       | 0    | Vertical Synchronization Pulse Output<br>Alternate Function: OUTBUS[2] Bus extension                                |  |  |

| 35  | FIELD       | 0    | Field (Parity) Output Signal Alternate Function: OUTBUS[3] Bus extension                                            |  |  |

**Table 4: Clock Signal Pins**

| Pin | Pin Name      | Pin Description                                                                                           |  |  |

|-----|---------------|-----------------------------------------------------------------------------------------------------------|--|--|

| 41  | XTALOUT       | Crystal Pad Oscillator Output                                                                             |  |  |

| 42  | XTALIN_CLKXTP | Crystal Pad Oscillator Input Alternate Function: Differential Clock input                                 |  |  |

| 43  | CLKXTM        | Differential Clock input (To be used in conjunction with CLKXTP)                                          |  |  |

| 44  | CLKSEL        | OV: Differential Clock input active (CLKXTM, CLKXTP 3.3V: Crystal Pad Oscillator active (XTALOUT, XTALIN) |  |  |

**Table 5: Configuration Pins**

| Pin | Pin Name | Туре | Pin Description                                                                                       |  |  |

|-----|----------|------|-------------------------------------------------------------------------------------------------------|--|--|

| 6   | TST_MODE | I    | To be Connected to Ground                                                                             |  |  |

| 9   | SDA      | I/O  | I <sup>2</sup> C Bus Data                                                                             |  |  |

| 10  | SCL      | I/O  | I <sup>2</sup> C Bus Clock                                                                            |  |  |

| 13  | NRESET   | 1    | Active Low Reset                                                                                      |  |  |

| 16  | I2CADD   | I    | 0V: 86h/87h and output pad active at Reset 3.3V: 8Eh/8Fh and output pad high impedance state at Reset |  |  |

# 3 Default Setup At Reset

The default configuration at reset is:

- CVBS1\_ input active

- Fast Blanking input for RGB insertion enable

- Automatic Standard Recognition of NTSC/PAL/SECAM

- Comb filter enable

- Data slicer enable

- Output ITU\_R BT. 656/601

- Output clock CLK\_DATA rising edge active

- PLL lock, HSYNC, VSYNC, FIELD primary functions enable

- Output pads active when Pin 16 connected to ground

- Output pads high impedance state when pin 16 connected to 3.3V

- Automatic HPLL time constant selection

For more detailed reset configuration descriptions, refer to Chapter 5: Register List.

## 3.1 System Clock Generation

The STV2310 clock is either provided by an internal 27-MHz crystal oscillator connected to pins XTALIN\_CLKXTP and XTALOUT, or imported in Differential mode from an external device such as the STV3500 and connected to the XTALIN\_CLKXTP and CLKXTM pins.

# 4 Functional Description

## 4.1 Analog Input Stage

#### 4.1.1 General Description

The Analog Input Stage provides the interface between the incoming video signals and the Analog-to-Digital Converters (ADC) using Clamp and Automatic Gain Control (AGC) stages to fit the analog signals to the ADC range.

Several video sources are processed in this stage:

- CVBS signals from a broadcast signal or the SCART connector.

- S-Video (Y/C) signals coming from an external video source (VCR, DVD, STB).

- RGB signals with Fast Blanking (FB) input coming from the SCART connector.

- Analog YCrCb signals coming from a DVD player (1H interlaced).

Anti-Aliasing Filter ADC Bias 1 CVBS Clamp CVBS1/Y Analog Control 10-bit Switch CVBS2/Y **PGA** ADC ±6 dB Composite and Luminance Input Channels Chroma Bias 8-bit ADC **Chrominance Input Channel** ADC Bias 2 Controller-R\_CR Clamp Control 8-bit R\_CR **ADC** Controller-G Clamp Control 8-bit G **ADC** 8-bit Controller-B\_CB Clamp Control **ADC** B CB 6-bit FΒ Interpolator **RGB and Fast Blanking Input Channels**

Figure 5: Analog Input Stage Functional Block Diagram

The CVBS/Y signal from the selected input channel goes through an automatic clamp and a Programmable Gain Amplifier (PGA) circuit. The clamping circuit automatically adjusts the black level to a programmable A/D output digital code. The clamp voltage is stored on the input coupling capacitor (22 nF, external to the STV2310). The PGA automatically adjusts the input signal

magnitude by  $\pm 6$  dB in 63 logarithmic steps to the optimal range of the A/D Converter. The video signal then goes through an external anti-aliasing filter before reaching the A/D Converter. The A/D Converter dedicated to the CVBS/Y channel has a 10-bit resolution. The A/D Converters dedicated to the C, R\_Cr, G and B\_Cb channels have an 8-bit resolution.

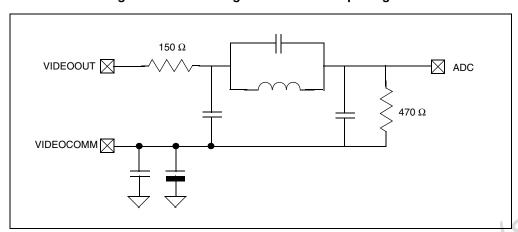

Figure 6: Anti-Aliasing Filter for CVBS Input Signals

Two independent CVBS sources can be connected to the STV2310. To process S-Video signals, the luma signal is connected to one of the CVBS inputs and the chroma signal is connected to the C input. RGB signals are directly connected to the three separate inputs (R\_Cr, G and B\_Cb). For Analog YCrCb signals, the luma signal is connected to one of the CVBS inputs, the Cr signal is connected to the R\_CR input and the Cb signal is connected to the B\_CB input.

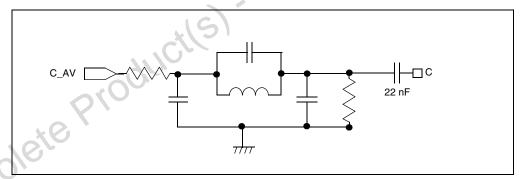

For S-Video signals, the Y (luminance) signal is connected to the selected CVBS input. The analog C (chrominance) input includes a bias and fixed gain circuit. The C signal is digitized by an 8-bit A/D Converter. It is recommended that an external anti-aliasing filter be added before the C input.

Figure 7: Anti-Aliasing Filter for Chroma Input Signals

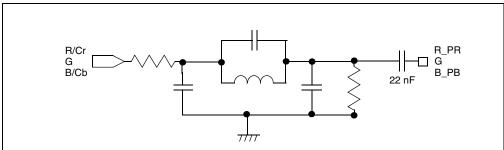

Analog R\_PR, G and B\_PB signals are clamped to the black level during the back porch period. These signals are digitized by a triple 8-bit A/D converter. It is recommended that an external antialiasing filter be added before each channel input.

Figure 8: Anti-Aliasing Filter for R PR, G and B PB Input Signals

The analog insertion (Fast Blanking) signal is sliced and sent to a shaper, controlling the soft switching between the analog R, G and B signals and the decoded main picture CVBS stream.

All reference voltages required by the A/D Converter are internally generated. Only two pairs of reference levels, REFP and REFM must be decoupled externally (REFP\_CVBS and REFM\_CVBS, REFP RGB and REFM RGB).

#### 4.1.2 **Programming**

The channel for the desired CVBS signal source is selected by the CVBSMUX bit in the DDECCONT0 register. The AGC and clamp mechanisms are described in Section 4.2.

#### **Synchronization and Monitoring Unit** 4.2

#### 4.2.1 **General Description**

The STV2310 system clock sampling frequency is provided by a free-running embedded crystal oscillator or an external clock generator. The nominal value of this sampling frequency is 27 MHz and is independent of any input TV standard.

Synchronization data (horizontal and vertical sync signals) is extracted from the video signal. After a low pass stage removing all high frequency information and noise, the video signal is sent to a synchronization slicer. Then the horizontal and vertical pulses are separated to generate the Hsync and Vsync pulses. The extracted Hsync pulses are sent to the horizontal PLL (HPLL) in order to filter the litter. The HPLL has an adaptive time constant with noise level and other operating conditions. It provides an easy lock even in difficult conditions and performs the skew extraction. Using this data, skew correction on the data stream is performed by the output scaler. This PLL can hold a frequency range of ±8% of the H frequency. A second PLL, associated with the output FIFO, is used to perform the line-locked clock generation from which the output HSYNC and VSYNC pulses are obtained by synchronous division.

A vertical sync processor is used to generate the output Vsync pulse, synchronous to the incoming CVBS signal. This processor is able to automatically detect 50 Hz/60 Hz standards. In the event of missing pulses, the Vsync processor replaces the missing pulse by inserting a V-pulse at the end of the 50 Hz or 60 Hz windows.

If an input video signal (CVBS or S-Video) is not detected, the sync processor operates in Freerunning mode.

The Output Sync Pulse (H, V and F) can be embedded in the digital output stream, according to the ITU\_R BT\_656/601 format, using the EAV and SAV codes. The Output Sync Pulse can also be delivered on dedicated external pins (33, 34, 35). These pins can be used specifically if the output sync pulses are no longer compliant with the ITU\_R BT\_656/601 format, as non-interlaced pictures or signals from a non-standard source (VCR). See Section 4.12.2.1 and Section for more information.

#### 4.2.2 Programming

The circuit can function in Automatic mode or use a programmable HPLL time constant. Automatic mode is selected by default. In this case the STV2310 automatically adapts the time constant to the reception conditions. In the case of unstable sources (such as VCRs) the circuit uses a special user-programmable VCR time constant. This HPLL time constant's proportional gain is selected in the HSYN\_GP[7:0] bits in the DDECCONT26 register. The value for the integral gain is selected in the HSYN\_GI[7:0] bits in the DDECCONT27 register. These bits also define the programmable time constant when the HTIMECSTSEL bit is reset in the DDECCONT22 register (Automatic mode disabled).

To be automatically selected, the VCR time constant requires that the noise level be below the noise threshold selected by the NOISE\_THRESHOLD[2:0] bits in the DDECCONT25 register.

The Vsync search and initial Free-running modes are selected by the 5060MODE[1:0] bits in the DDECCONT0 register.

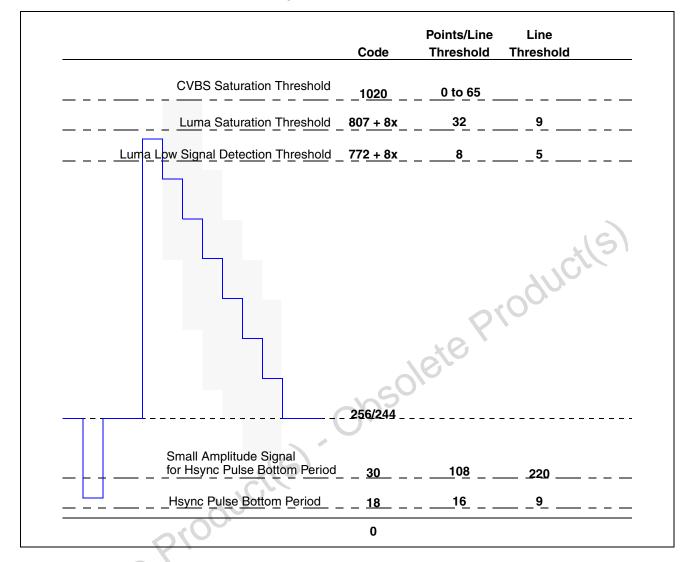

The (fluctuating) average sync bottom and blanking level values, based on the Hsync Pulse Bottom Period and Composite Video Burst Period identification data, are necessary in turn to perform the clamp correction on the CVBS signal in the analog domain. (See Figure 9.) The clamp level is programmed by the BLANKMODE[1:0] bits in the DDECCONT1 register.

The Active Input Video Period and small amplitude signals for the Active Input Video Period levels which control the gain level of the AGC are programmed in the ACTITH[1:0] and SMHITH[1:0] bits (respectively) in the DDECCONT16 register.

The CVBS saturation threshold is programmed in the SATLMTPT[1:0] and SATLMTLN[1:0] bits of the DDECCONT16 register in the event of a high level of chroma demodulation. It is expressed as a number of samples per field (when, according to the algorithm, the number of samples is reached, the gain is decreased).

Output mode can be forced to 50 Hz or 60 Hz by 5060MODE[1:0] bits in the the DDECCONT00 register.

To output a non-interlaced image, the chip must be set in direct parity mode by the DIRECTPARITY bit in the DDECCONT1F register.

The external HSync pulse can be synchronised to the End of Active Video (EAV) and the Start of Active Video (SAV) pulses, or initialized according to the usual analog H/V pulse using the HSYNC\_SAV bit in the DDECCONT25 register.

Figure 9: AGC Flowchart

## 4.3 Input Sample Rate Conversion

#### 4.3.1 General Description

An Input Sample Rate Converter (ISRC) converts the acquisition pixel rate to a clock domain virtually locked to the color subcarrier. This ISRC is controlled by a subcarrier phased-locked loop (Chroma PLL). This enables comb filtering and chroma demodulation to be carried out on various subcarrier frequencies using the same system clock sampling frequency.

The Input SRC uses the data provided by the front-end ADCs to process both the CVBS and C flows (in the event of separated Y/C inputs, the CVBS flow = Y flow). The same processing is applied to the CVBS and C data.

When the input video standard has been identified, its subcarrier frequency ( $f_{SC}$ ) is known and the Chroma PLL is locked. The Input SRC transforms the input data captured at the 27-MHz system clock sampling frequency ( $f_{SC}$ ) to the subcarrier clock domain frequency (4 x  $f_{SC}$ ).

The practical value of the 4 x f<sub>SC</sub> frequency depends on the actual input TV standard.

### 4.4 Luminance and Chrominance Separation

#### 4.4.1 General Description

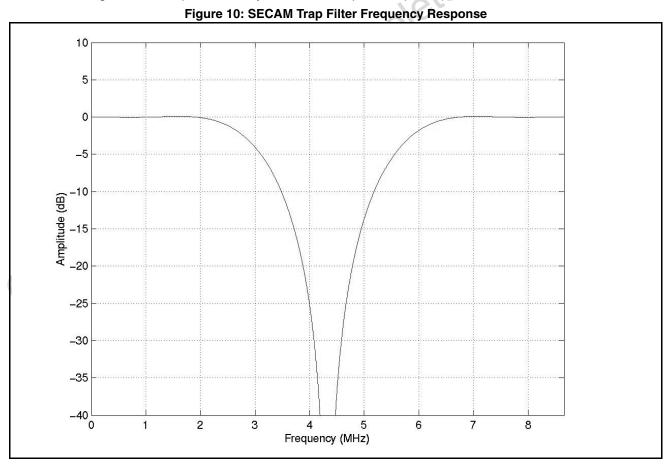

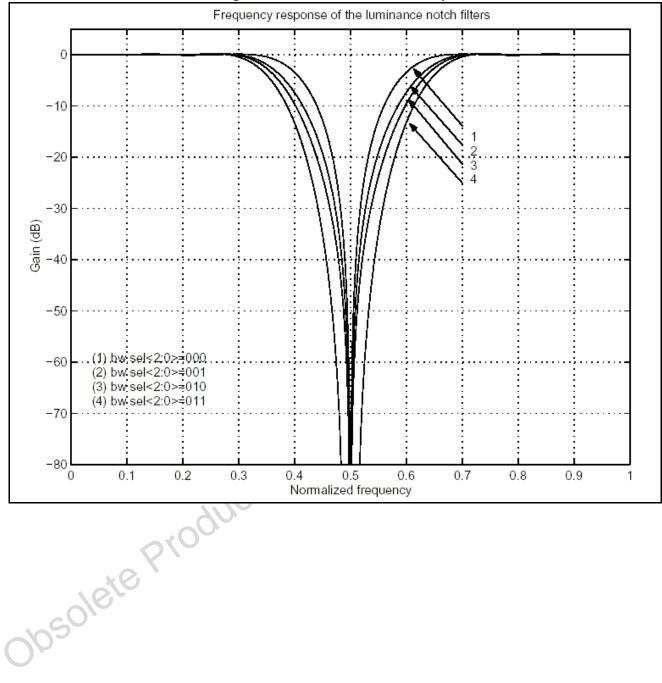

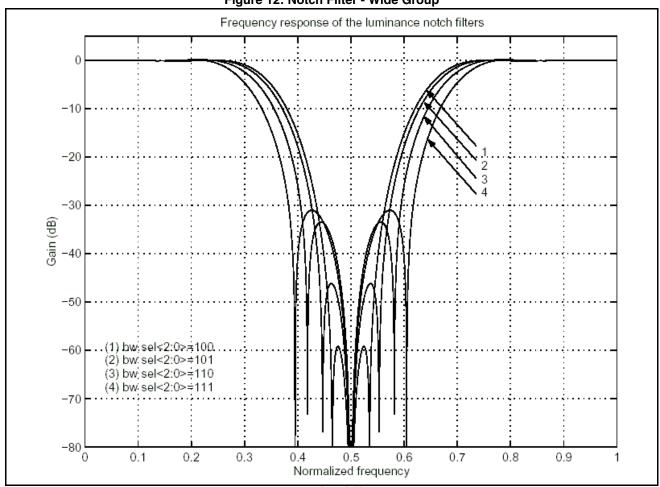

The Y/C Separator separates the chrominance (C) component from the composite signal which also includes the luminance (Y), synchronization and color burst (subcarrier) components. In normal operation (NTSC and PAL standards), this is done through comb or notch filtering which relies on the correlation of consecutive lines. For SECAM inputs, a Chroma Bandpass/Trap filter system is required. If an S-Video input is selected, Y/C separation is not required and the Y/C Separator operates in Bypass mode. Y/C delay adjustment can be done with both pixel and subpixel accuracy.

#### 4.4.2 Programming

Once the samples processed by the input SRC have been stored in RAM, the type of input signal (Y/C or CVBS) must be specified before the chroma component can be separated from the CVBS input signal. This is done by setting the SVIDEOSEL bit in the DDECCONTO register.

The Y/C separator block can either operate in auto-adaptive mode (Default mode) or Forced Separation mode (notch). This operating mode is selected by the COMB\_MODE bit in the DDECCONT18 register:

- Chroma Bandpass/Trap filtering is forced

- Adaptative Comb Filtering mode is forced. (This applies to PAL/NTSC signals only. SECAM signals remain processed by Chroma Bandpass/Trap filter)

The notch filter width used in the Y/C separation can be adjusted from narrow to wide by the BW\_SEL[2:0] bits in the DDECCONT18 register. Luma Chroma delay can be adjusted by the DEM\_YC\_DELAY[3:0] bits in the DDECCONT15 register and DDECCONT1A register, bit [5:0].

Figure 11: Notch Filter - Narrow Group

Figure 12: Notch Filter - Wide Group

# 4.5 Standard Research Sequence Programming

The chroma signal is sent to the Standard Identifier and Chroma Demodulator. The Standard Identifier performs an automatic recognition sequence for one of the following standards.

**Chroma Standard Standard Code Subcarrier Frequency** PAL B,D,G,H,I 4.4336 MHz 000 **SECAM** 4.406 MHz (foR) 001 4.250 MHz (foB) NTSC M 3.5795 MHz 010 PAL M 011 3.5756 MHz PAL N 100 3.5820 MHz NTSC 4.43 4.4336 MHz 101 n/a 110 No Standard<sup>1</sup> n/a 111 No Standard<sup>1</sup>

**Table 6: TV Standards**

Note 1: Codes 110 and 111 are associated with "No Standard".

From this list of possible standards, the user must complete the Automatic Standard Recognition table required for the automatic search. Identification will be restricted to the table entries and the first entry will be tried first. Entering code 110 or 111 in the Automatic Standard Recognition table terminates the standard sequence search. It is possible to enter several times the same code. The Automatic Standard Recognition table and its default values are presented in Table 7.

Standard Code Register **Entries** (Default values) Standard 1 000 DDECCONT4[5:0] Standard 2 001 Standard 3 010 DDECCONT3[5:0] Standard 4 111 Standard 5 001 DDECCONT2[5:0] Standard 6 001 Standard 7 111 DDECCONT1[5:0] Standard 8 111

**Table 7: Automatic Standard Recognition Table**

If the default values are used, code 111 (no standard) is the fourth entry and the standard identification will be restricted to the first three standards (in order PAL BGDHI, SECAM and NTSC M).

Each standard recognition trial period lasts 2 fields. All trials corresponding to table entries are performed. The identification decision is based on the results of the trials and a single table entry should be identified. If two entries are identified by error, the standard recognition sequence will restart from the beginning of the table and no standard will be identified.

The DDECCONT4[5:0], DDECCONT3[5:0], DDECCONT2[5:0], and DDECCONT1[5:0] registers are used to program the Automatic Standard Recognition table.

After the sequence search, a second step (also called a confirmation step) is performed by the algorithm. It is performed on the single identified Automatic Standard Recognition table entry. It is possible to program the number of fields where the standard identification must be confirmed before the status flags are modified. The confirmation code is described in Table 8.

Confirmation Code

Number of Successive Fields with Correct Identification

000

1

001

3 (Default)

010

7

011

10

**Table 8: Confirmation Codes**

The confirmation code is programmed in the STI\_NB\_FIELDS\_CONFIRM[2:0] bits of the DDECCONT17 register.

After the confirmation step has been successful, the standard is considered as identified. The TVSTID flag is set in the DDECSTAT2 register and the code of the identified standard is set in the TVSTD[2:0] bits of the DDECSTAT2 register.

#### 4.6 Standard Identification

The input signal standard is automatically recognized using a proprietary ST patented algorithm. It avoids false identification and ensures a good recognition of the color standard, even in bad signal conditions.

### 4.7 Chroma Demodulation

#### 4.7.1 General Description

The Chroma PLL and the Input SRC are the main hardware blocks involved in chroma demodulation. The Chroma PLL is locked to the input video burst signal in frequency and phase. Demodulation is performed on the chroma samples positioned in the virtual 4 x f<sub>SC</sub> clock domain.

Dedicated demodulation hardware is used for SECAM demodulation (frequency modulated signals). Demodulated chroma components are low pass filtered and matrixed into Cr and Cb components.

The Chroma Demodulator also includes an Automatic Chroma Control (ACC) which rescales the chroma components from -20 dB to +6 dB. The color is killed (output Cr Cb components to 80h value) until the standard is identified. ACC is disabled (fixed gain) in SECAM standard.

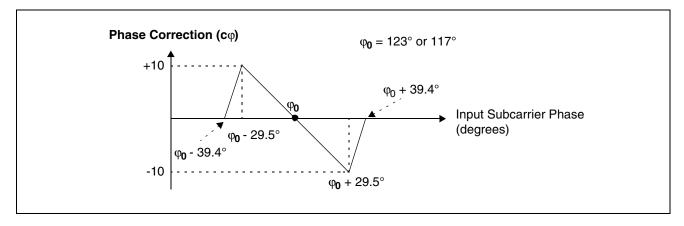

If NTSC M or NTSC 4.43 standards are identified, the Chroma Demodulator also incorporates a Hue Control mechanism and a Flesh Tone Correction mechanism. The Hue Control is a programmable fixed offset in the demodulation angle and is only operational in the active line.

The Flesh Tone Correction mechanism operates with a programmable reference axis. It performs an on-the-fly change of demodulation axis for any color with a phase of approximately  $\pm$  39.4° around the reference axis. It is only operational in the active video line.

Flesh Tone Correction (c $\varphi$ ) is up to a maximum of  $\pm 10^{\circ}$ .

Cr and Cb amplitudes can be adjusted separately. (See Section 4.12.1.)

#### 4.7.2 Programming

For NTSC standards, there are several ways to improve the video input. The hue value is controlled by the HUECTRL[5:0] bits in the DDECCONT2 register. The hue control value is defined in 63 steps of approximately 1.4 degrees each, which provide an offset between -45.0° and +43.6°. When 00000, the hue angle is 0, otherwise the value of the hue angle is coded in 2's complement.

An Automatic Flesh Control is also available with the STV2310. This mode is enabled by setting the FLESH\_EN bit in the DDECCONT10 register. For the Automatic Flesh Control Phase Shift selection, the Flesh Tone Reference Angle in the [B-Y, R-Y] axis system is either 123° or 117°. This value is selected in the FLESHPH\_SEL bit of the DDECCONT10 register.

The Color Kil control mode can be automatic, depending on the standard identification, or forced On or Off by the DEM\_CKILL\_CTRL[1:0] bits in the DDECCONTD register. In PAL/NTSC mode, it can also depend on burst amplitude by setting the in the DDECCONTF register.

A pedestal can be removed from the luminance input signal by the video standard using the PEDESTAL\_REMOVE bit in the DDECCONT2 register.

Figure 13: Phase Correction when Automatic Flesh Control Enabled

#### 4.8 Soft Mixer

#### 4.8.1 General Description

The Soft Mixer is used to mix the Y, Cr and Cb data flows (respectively) from the CVBS source and the RGB Insertion block. The mixing of the data flows is controlled by Fast Blanking mode. A forced CVBS or RGB flow mode can also be programmed. In this case, the mixer acts as a multiplexer. A static mixing (also called alpha blending) mode is also programmable.

When the normal mixing mode is programmed, the CVBS and RGB flows are blending according to the Fast Blanking (FB) signal. The FB signal is sampled with subpixel accuracy to ensure correct mixing. The mixing slope between flows is programmable.

#### 4.8.2 Programming

Fast Blanking mode is selected by the FBLANKMODE[2:0] bits in the DDECCONT5 register.

**Bit Value Mixing Mode** Description 00x Normal Mixing mode FB active during active line. Soft Mixing between 0 and 1. (Default mode) FB active and Soft Mixing from 0 to MIXSLOPE[7:0] 01x Dynamic Mixer mode 100 Static Mixer or Alpha FB inactive. Y<sub>OUT</sub> = alpha x Y<sub>CVBS</sub> + (1-alpha) x Y<sub>BGB</sub> Blending 1 mode with alpha = MIXSLOPE[7:0] (same for Cr and Cb signals) Static Mixer or Alpha FB inactive. Y<sub>OUT</sub> = alpha x Y<sub>RGB</sub> + (1- alpha) x Y<sub>CVBS</sub> Blending 2 mode with alpha = MIXSLOPE[7:0] (same for Cr and Cb signals) Forced CVBS mode FB inactive. Y<sub>OUT</sub> = Y<sub>CVBS</sub> (same for Cr and Cb signals) 110 111 Forced RGB mode FB inactive. Y<sub>OUT</sub> = Y<sub>RGB</sub> (same for Cr and Cb signals)

Table 9: Fast Blanking Modes

Note: The FBLANKMODE value is only applied when the STV2310 is not in Analog YCrCb mode

The soft mixing slope or the Alpha Blending value, depending on the Fast Blanking mode, is set in the MIX\_SLOPE[7:0] bits in the DDECCONT6 register. When the blanking mode is in Forced RGB or Forced CVBS mode, this value is ignored.

When one of the Alpha Blending modes is used for mixing, the alpha value is set in the MIX\_SLOPE[7:0] bits.

When the STV2310 is in normal RGB and CVBS mixing mode, the MIX\_SLOPE[3:0] bits indicate the mixing slope (duration of mixing). The MIX\_SLOPE[7:4] bits must be set to 0000. The MIX\_SLOPE[3:0] bits code the soft mixing slope from 0000 to 1111, with 0000 corresponding to a slope of 1 clock cycle (virtual 4 x f<sub>SC</sub> clock domain) and 1111 corresponding to a transition from one signal to the other spanned on 16 clock cycles.

### 4.9 Output Scaler and Format Converter

#### 4.9.1 General Description

An Output Sample Rate Converter (OSRC) is used to transpose the subcarrier locked virtual clock domain to the output sample rate domain. This converter is used to provide a fixed number of pixels per active line (i.e. 720 for ITU-R BT.601 format) independently of the input video standard and line length.

- Upsampling is required for zoom-in functions.

- Downsampling is required for zoom-out functions.

The Output Sample Rate Converter compensates for line length variations. At this level, a skew correction is applied on each pixel in order to compensate for the shift of the asynchronous acquisition with respect to the current line horizontal sync pulse. New sample rate and skew correction factors are computed at every line, taking into account the line length variation.

The Output Sample Rate Converter is also used to perform an horizontal format conversion to support zoom in/out functions. For linear scaling, the scaling factor can be programmed in linear steps from 0.25 to 4. Non-linear scaling is also available for Panorama mode. Region borders are fully programmable as well as the associated scaling factors (in the 0.25 to 4 range).

At the sample rate converter output, an active line is transposed into a fixed number of skew corrected pixels, according to the selected output format (ITU-R BT.601 or square pixel). This is used for the orthogonal display or field storage for the field-rate up-conversion, using an external up-converter.

#### 4.9.1.1 Square Pixel Mode

)bsolei

When a standard TV screen is used to display computer-generated images, Square Pixel mode is required to ensure the correct aspect ratio in relation to the required sampling frequency of the TV display format.

Luma Sampling FrequencyFormatPixels/Line13.5 MHzITU-R BT.601 (NTSC/PAL)72012.27 MHzNTSC Square Pixel64014.75 MHzPAL Square Pixel768

**Table 10: TV Display Formats**

The output formatting can be performed with Normal or Square Pixel modes. For Square Pixel mode, the number of required samples per line depends on the input standard.

Samples per Line

Y Signal

Cr Signal

Cb Signal

625 Lines/50 Hz

768

384

384

320

320

Table 11: Required Samples per Line for Square Pixel Mode

#### 4.9.1.2 Zoom-In Mode

525 Lines/60 Hz

640

In Zoom-In mode, a portion of the TV scan line is expanded to take all the available output samples for that line. The zoom-in factor ranges from 1 (no zoom) to 4 (large zoom). The Zoom-In mode start position is programmable.

Output Line after zoom

720 Samples (Y Normal Pixel Mode)

2 Examples for Zoom In Action

Figure 14: Zoom-In Mode

#### 4.9.1.3 Zoom-Out Mode

In Zoom-Out mode, the entire input TV scan line is compressed to take only a part of the output line. The active samples are positionned in the center of the output line and the rest of the line is blacked out. The zoom-out factor ranges from 0.25 (large zoom) to 1 (no zoom).

Output Line after zoom

Black Level

720 Samples (Y Normal Pixel Mode)

Figure 15: Zoom-Out Mode

#### 4.9.1.4 Panorama Mode (Non-Linear Scaling)

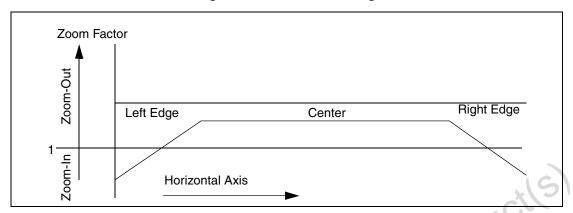

To better display wider TV screen aspect ratios, Panorama mode applies a different zoom factor to the center of the image in relation to the edges; i.e. a Non-Linear Scaling mode must be implemented. This implies that the compression/expansion factor will vary on the edges and remain stable at the center. Note in Figure 16 that the resulting TV image is symetrical (right and left edges are equal).

Figure 16: Non-Linear Scaling

#### 4.9.2 Programming

#### 4.9.2.1 Square Pixel Mode

Square Pixel mode is enabled by setting the PIXMODE bit in the DDECCONT0 register.

#### 4.9.2.2 Zoom-In Mode

To enable Zoom-In mode, the ZOOMIN\_EN bit in the DDECCONTB register must be set.

The zoom-in value must be between 256 and 1023. A value of 512 will zoom-in the picture by a factor of 2.0; i.e. pixels are twice as large. The zoom-in factor is programmed in the ZOOMIN\_FACT[9:0] bits in the DDECCONT6 and DDECCONTB registers. The default value is 256 (No Zoom).

The position where the zoom-in operation starts is programmed in the ZOOMIN\_OFFSET[9:0] bits in the DDECCONTA and DDECCONTB registers. If the value is 0, the zoom-in starts at the beginning of the TV scan line (first left pixel). The number of pixels per line is based on the vertical frequency and the pixel mode. For more information, refer to Table 10. The default value is 0; i.e. the first left pixel of the active line is the first pixel of zoom.

#### 4.9.2.3 Zoom-Out Mode

To enable Zoom-Out mode, the ZOOMOUT\_EN bit in the DDECCONTB register must be set.

The zoom-out value must be between 256 and 1023. A value of 512 will zoom-out the picture by a factor of 0.5; i.e. pixels are twice as small. The zoom-out factor is programmed in the ZOOMOUT FACT[9:0] bits in the DDECCONT9 and DDECCONTB registers.

#### 4.9.2.4 Panorama Mode

Panorama mode is enabled when both the ZOOMIN\_EN bit in the DDECCONTB register and the ZOOMOUT EN bit in the DDECCONTB register are set to 1.

In Panorama mode, the ZOOMIN\_FACT, the ZOOMOUT\_FACT and the ZOOMIN\_OFFSET values are used (see Figure 16).

- The ZOOMIN\_FACT bits determine the zoom-in factor at the left and right edges of the picture

- The ZOOMOUT FACT bits determine the zoom-out factor at the center of the picture

- The ZOOMIN\_OFFSET bits determine the border width where the zoom factor increases from the zoom-in factor to the zoom-out factor, starting from the left edge (resp. the border width finishing on the right edge where the zoom factor decreases from the zoom-out factor to the zoom-in factor)

For correct programming the following formula must be checked:

Zt x (Zout - Zin) = N x (Zout -1)

where Zin = ZOOMIN\_FACT; Zout = ZOOMOUT\_FACT; Zt = ZOOMIN\_OFFSET; N number of Y pixels per line (720 in Normal Pixel mode, 640 or 768 in Square Pixel mode).

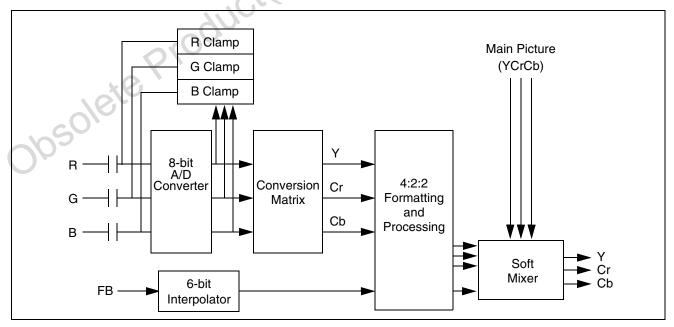

#### 4.10 RGB Insertion

#### 4.10.1 General Description

The RGB signals are captured by three 8-bit A/D converters and should be synchronous to the selected CVBS or Y/C sources. The RGB signals are also adjusted in the analog domain by clamp circuits used for sourcing and sinking charges on the front end capacitor.

A digital adjustable gain can be applied to the RGB data flow, in order to adapt to the CVBS dynamic range.

The RGB signals are YCrCb formatted and mixed with the YCrCb signals from the main picture. Soft mixing is driven by the FB signal. The rising and falling edges of the FB signal are measured with subpixel accuracy to perform correct insertion. (For more information, refer to Section 4.8: Soft Mixer on page 24).

The RGB insertion block also provides a Cr Cb overload mechanism. This mechanism is used to avoid clipping YCrCb signals (i.e when the input RGB signals are too large). The Cr Cb overload mechanism measures the chroma signal during the video line in order to compute the correcting scale factor.

Figure 17: RGB Capture and Mixing with Main Picture

#### 4.10.2 Programming

To enable the CrCb overload mechanism, set the CRCBOVER\_EN bit in the DDECCONTB register. The automatic gain for the RGB is set in the DDECCONT35 register.

#### 4.11 Analog YCrCb Mode

#### 4.11.1 General Description

The STV2310 can be programmed in Analog YCrCb mode. This mode has specific input connections:

- the Y analog input signal must be connected to the CVBS1\_Y (or CVBS2\_Y) pin

- the Cr and Cb analog input signals must be connected to the R\_CR and B\_CB input pins (respectively).

A ±20 degree Tint Control mechanism is available to compensate for incorrect hue levels on the input signals. When the Analog YCrCb mode is programmed, the various clamp circuits are modified accordingly.

Note: The Fast Blanking (FB) signal is not relevant in Analog YCrCb mode. This mode is a full-page display mode.

#### 4.11.2 Programming

The YCrCb Tint Angle Correction values are programmed in the TINTANGLE[4:0] bits in the DDECCONT12 register. The tint angle is coded from -20° to +20° in steps of 1.33°. These bits are coded in 2's complement. The default value is 0 (no correction).

## 4.12 Output FIFO and Line-locked Ouput Pixel Clock Generator

#### 4.12.1 General Description

The Output FIFO and Line-Locked Output Pixel Clock Generator block has two functions:

- 1 Handle the active line data received from the Output Scaler and Format Converter and the ancillary data from the VBI slicer.

- The active video line data is provided on 3 buses: Y, Cr and Cb. The output flow is on 8 bit and multiplexes the Y, Cr and Cb flows. Before being multiplexed, a programmable attenuation can be applied to the Cr, Cb data. For every output line, digital preambles for synchronization and ancillary data (when available) are inserted in the output flow in compliance with standard ITU-R BT 656.

- Generate the Output Pixel Clock and associated signals.

- A line-locked output pixel clock is generated. This output clock is a multiple of the input line frequency. There are 4 possible multiples:

- 1716 or 1728 in Normal Pixel mode.

- 1560 or 1888 in Square Pixel mode.

When there is no input signal, the output data can be blanked in option.

When required the STV2310 is able to enlarge the vertical blanking area. On the other hand it is possible to disable the blanking mode during the VBI, using the "pass through" mode. (The "pass through" mode must not be selected when the TXT VBI slice is used).

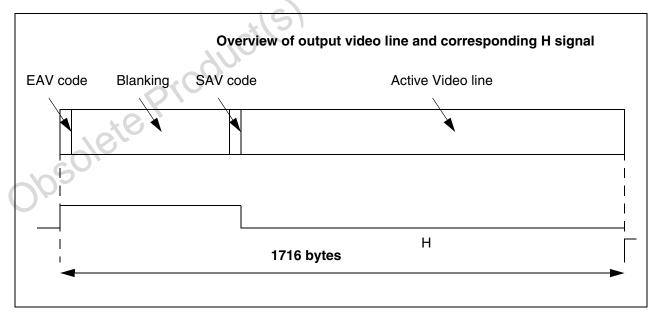

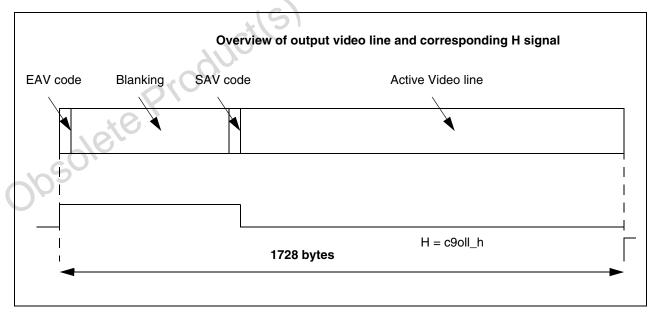

#### 4.12.2 Output Data

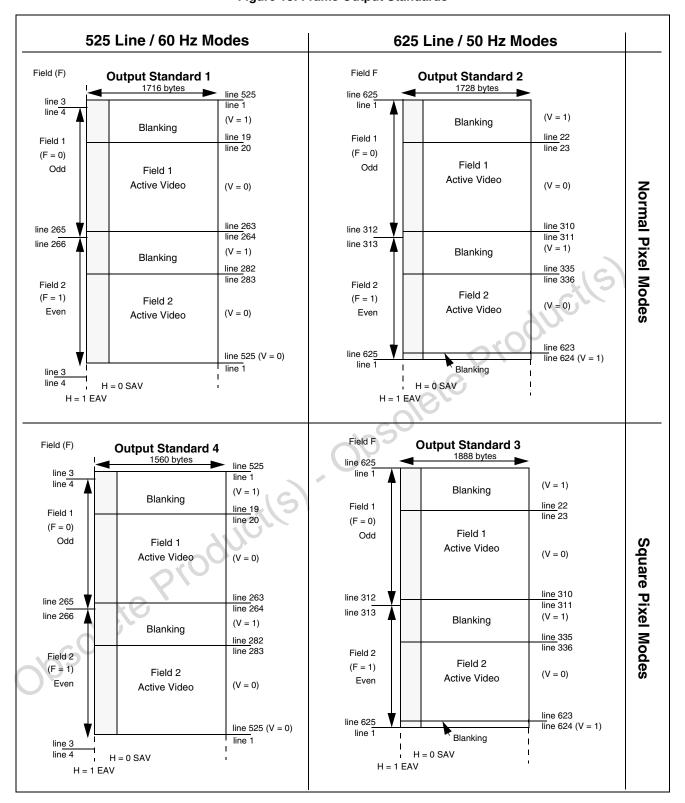

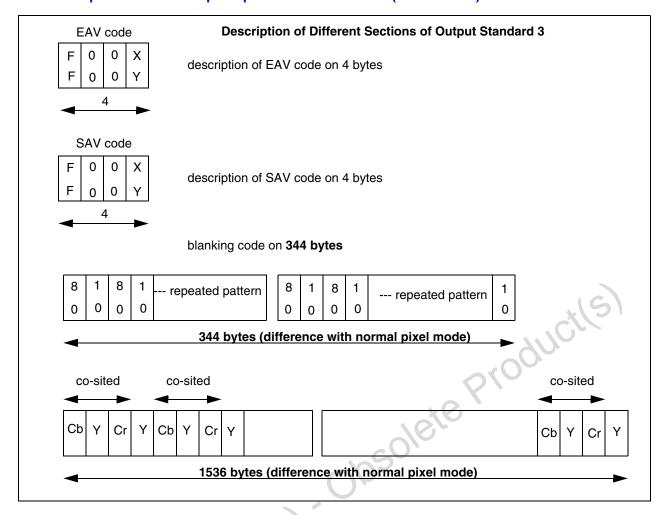

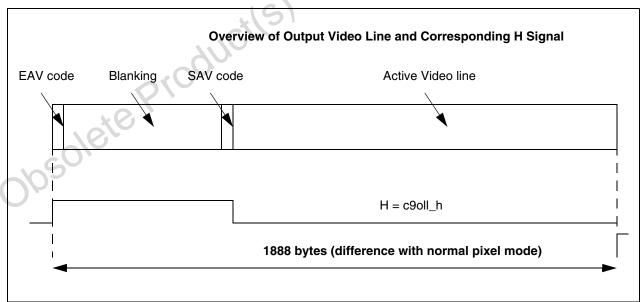

There are 4 data output standards which are a combination of 525/625 input standards and Normal/Square pixel format. There are four possible multiples:

- 1716 or 1728 in Normal Pixel mode,

- 1560 or 1888 in Square Pixel mode.

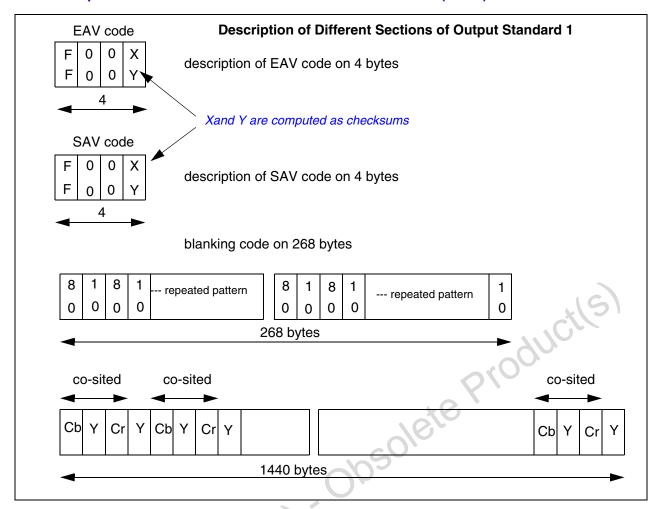

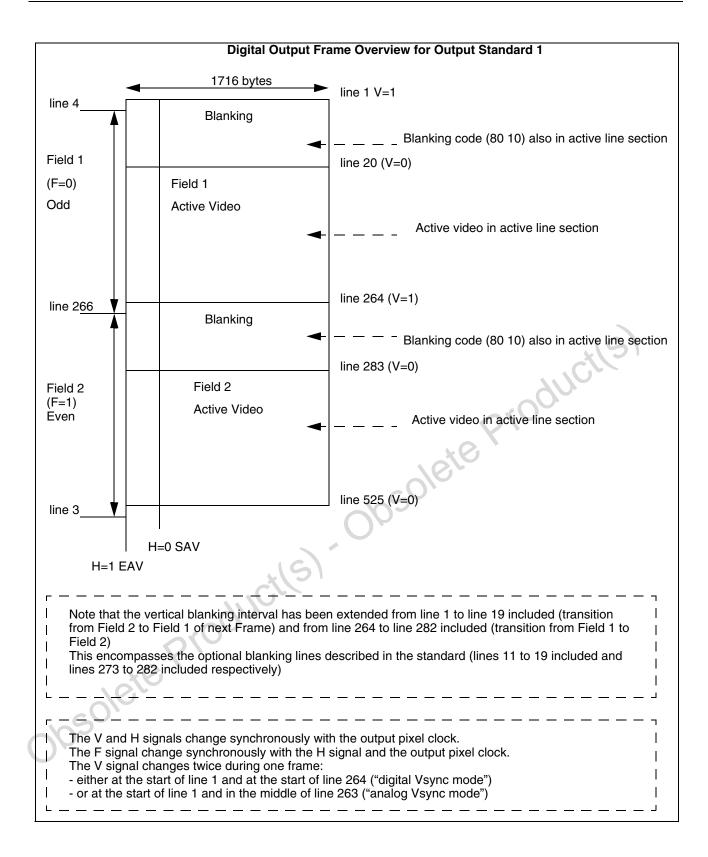

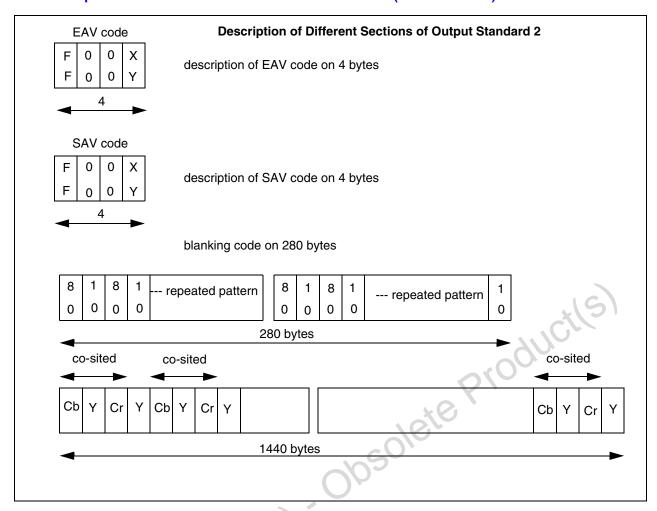

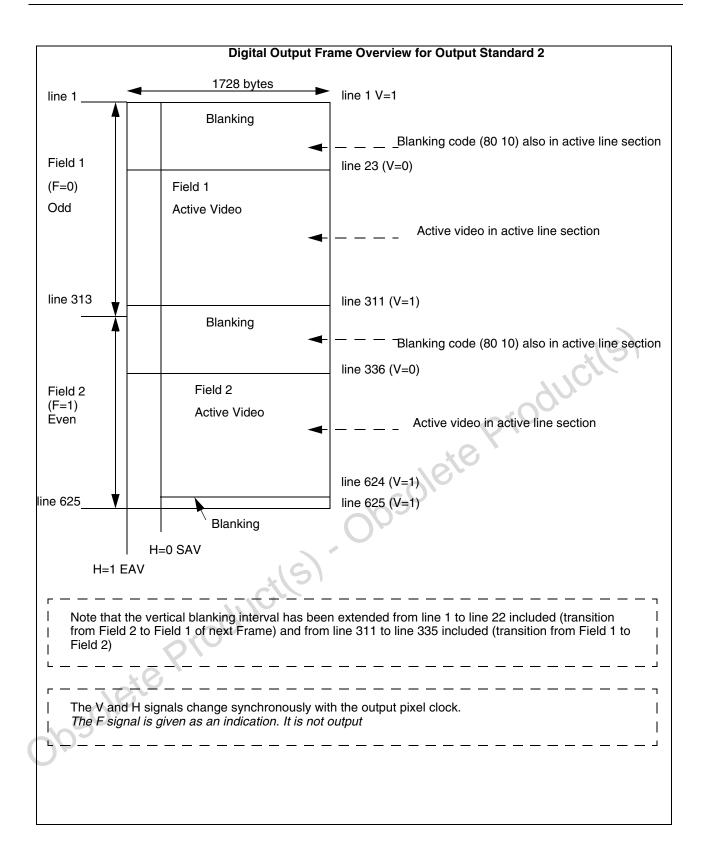

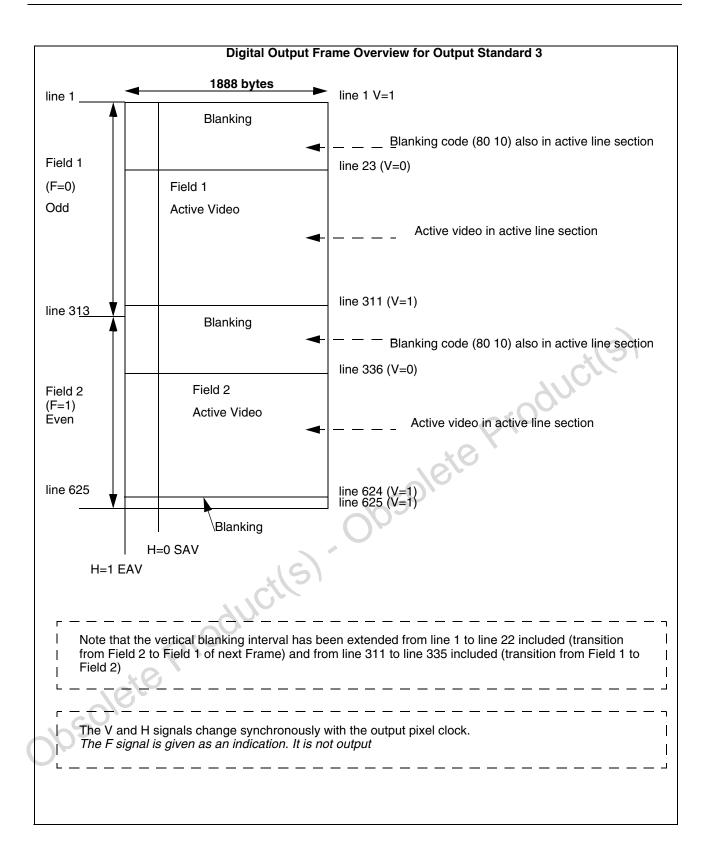

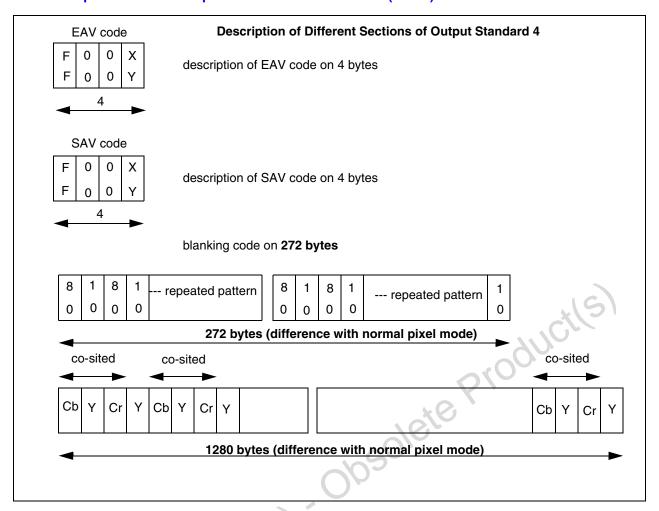

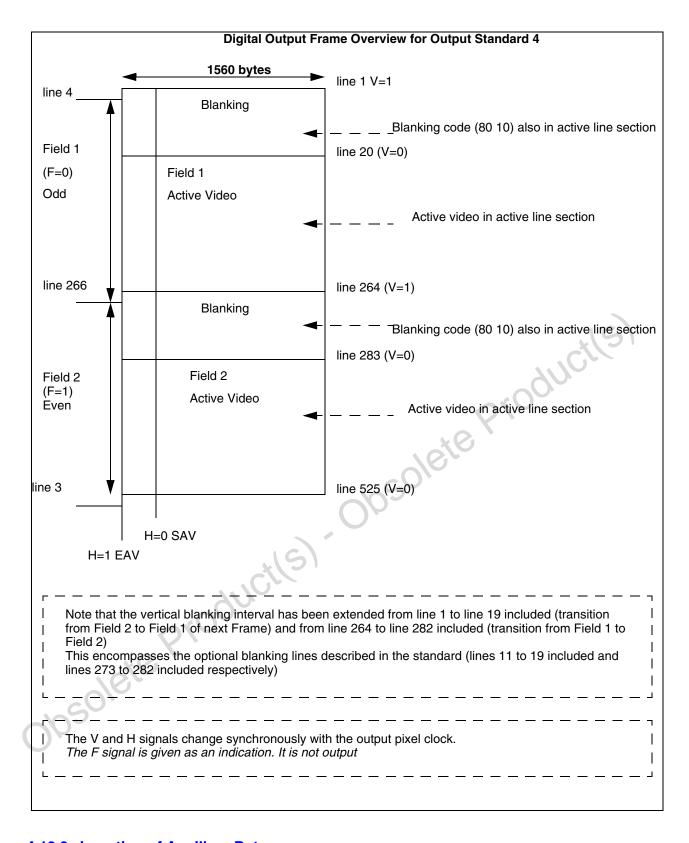

For each output standard, the blanking code (Cb = 80h, Y = 10h, Cr = 80h, Y = 10h...) is used in the active line section during the Vertical Blanking Interval (VBI). (See Figure 18.)

**Table 12: Frame Output Standards**

|                                            | Output Standard<br>1                                         | Output Standard<br>2                                   | Output Standard<br>3                                   | Output Standard<br>4              |

|--------------------------------------------|--------------------------------------------------------------|--------------------------------------------------------|--------------------------------------------------------|-----------------------------------|

| Input Standard                             | 525/60 Hz                                                    | 625/50 Hz                                              | 625/50 Hz                                              | 525/60 Hz                         |

| Pixel Format                               | Normal                                                       | Normal                                                 | Square                                                 | Square                            |

| Blanking (bytes)                           | 268 + 8                                                      | 280 + 8                                                | 344 + 8                                                | 272 + 8                           |

| Active Video (bytes)                       | 1440                                                         | 1440                                                   | 1536                                                   | 1280                              |

| Vertical Blanking<br>Interval <sup>1</sup> | Lines 1 to 19<br>Lines 264 to 282                            | Lines 1 to 22<br>Lines 311 to 335<br>Lines 624 and 625 | Lines 1 to 22<br>Lines 311 to 335<br>Lines 624 and 625 | Lines 1 to 19<br>Lines 264 to 282 |

| Vsync Signal                               | Synchronized with the output pixel clock. See below.         |                                                        |                                                        |                                   |

| Hsync Signal                               | Synchronized with the output pixel clock.                    |                                                        |                                                        |                                   |

| Field Signal                               | ignal Synchronized with the Hsync signal output pixel clock. |                                                        |                                                        |                                   |

<sup>1.</sup> Lines are numbered in compliance with specification ITU-R BT470.

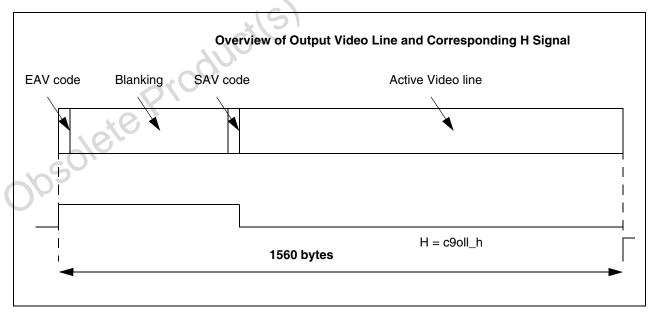

#### 4.12.2.1 Vsync Output Pin Modes

Figure 18: Frame Output Standards

For all output standards, the Vsync output signal changes twice per frame. The Vsync signal (pin 34) can be generated at the output in one of two modes:

- 1 <u>"Digital" Vsync mode</u>: The VSYNC signal always changes at the beginning of the line, depending on the output standard.

- 2 <u>"Analog" Vsync mode</u>: The VSYNC signal changes either at the beginning or the middle of the line, depending on the analog input signal.

- > for Output Standard 1: Start of line 4 and middle of line 266

- > for Output Standard 2: Start of line 1 and middle of line 313

- for Output Standard 3: Start of line 1 and middle of line 313 (same as standard 2)

- for Output Standard 4: Start of line 4 and middle of line 266

Note that the output standard depends on the input TV standard and the programmable Normal Pixel or Square Pixel mode.

The VSYNC output mode is selected by the VSYNCTYPE bit in the DDECCONT0 register.

The V bit of the output flow always changes at the beginning of the line (in compliance with standard ITU-R BT 656).

Non-Interlaced mode: When required, the STV2310 is able to interlace the output, even if the source is non-interlaced (by default, the output Vsync follows the input Vsync).

#### 4.12.2.2 Hsync Output Pin Mode

The Hsync output pulse can shifted, this is in comparision with the embedded Hsync pulse.

#### 4.12.2.3 FIELD Output Pin Mode

Obsolete Product(s)

The FIELD output pulse represents the parity of the field and toggles either with the embedded FIELD pulse, or is synchronous with the Vsync pin, when set in analog interlaced mode. To toggle in analog interlaced mode, the direct parity mode must be selected.

#### 4.12.2.4 Output Standard 1 : Normal Pixel mode / 525 lines / 60 Hz (NTSC)

#### 4.12.2.5 Output Standard 2: Normal Pixel / 625 lines / 50 Hz (PAL & SECAM)

# 4.12.2.6 Output Standard 3: square pixel / 625 lines / 50Hz (PAL SECAM)

47/

# 4.12.2.7 Output Standard 4: Square Pixel / 525 lines / 60Hz (NTSC)

47/

# 4.12.3 Insertion of Ancillary Data

Ancillary data is inserted in the output flow as it is received from the VBI slicer. No operation/modification is performed on this data. No fixed prefix or suffix is added.

The ancillary data is always inserted between the EAV and SAV codes of each line.

The line number is provided by the VBI slicer.VBI data is inserted on the next possible output line. The only lines where insertion cannot take place are the forbidden lines. The list of forbidden lines depend on the standard:

- for the 525 lines (60 Hz): 9,10,11,272,273,274

- for the 625 lines (50 Hz): 5,6,7,318,319,320

Ancillary data is inserted starting just after the EAV code. Ancillary data will replace the blanking data codes. Ancillary data is inserted in the same order as it is received from the VBI slicer.

VBI data belonging to the same line at reception is inserted in a single line. The maximum number of ancillary data bytes to be inserted is 84.

# 4.12.4 Line-Locked Output Pixel Clock Generation

A phase-locked loop (PLL) generates a clock signal (CLK\_DATA) that is used to read the output FIFO and to output the YCrCb data in synchronization. This output pixel clock frequency is a multiple of the input line frequency. Its value (1716, 1728, 1560 or 1888) depends on the input TV standard and the programmable Normal Pixel or Square Pixel mode.

Note that phase jumps detected in the input video are replicated in the output PLL. This is equivalent to a temporary change of the number of samples per line, but no change in the output clock frequency. This feature can be disabled. In this case, the output PLL then corrects the input phase step by frequency modulation.

### 4.12.5 Alternate Functions: Bus Extensions

Output data is issued synchronously to the CLK\_DATA clock active edge. Either the rising or falling edge of the CLK\_DATA signal can be programmed as the active edge.

The following pins can be used for bus extension purposes as programmable output pins: PLLLOCK, HSYNC, VSYNC and FIELD.

PLLLOCK has a second alternate function IRQ (Interrrupt Request). Interrupt can be generated by several functions described in registers DDECCONT36 and DDECCONT3C.

# 4.12.6 Output Code Clipping

To allow compatibility with other devices, output codes can be clipped to remain inside 0 to 100% of luminance (16 to 235) and chrominance (16 to 240) components.

# 4.12.7 Programming

The Vsync Insertion mode for the output flow is selected in the VSYNCTYPE bit in the DDECCONTO register.

The PHSHFT\_DIS bit in the DDECCONT5 register is used to disable the phase jump mechanism in the output PLL. By default, phase jumps are allowed when a phase shift in the video input is transmitted in the data flow to the output PLL.

The active edge for the CLK\_DATA signal is selected by the ACTEDGE bit in the DDECCONTO register.

Data is output from the STV2310 on the FIELD, VSYNC, HSYNC, PLLLOCK and YCRCB[7:0] pins which are synchronous to the CLK\_DATA output clock on either the rising or falling edge (depending on the selected option).

To force the Interlaced output mode, use the NONINTERLACED\_EN bit in the DDECCONT18 register.

To force the pass through mode, use the PASSTHROUGH\_EN bit in the DDECCONT38 register.

To shift the external Hsync pulse, use the HSYNCSHIFT\_DEL[1:0] and HSYNCSHIFT\_EN bits in the DDECCONT22 register.

Cr Cb attenuation are controlled by the DDECCONT37 and the DDECCONT38 registers. The output blanking modes are controlled by the OUTBEHAV\_BLANK2 and OUTBEHAV\_BLANK1 bits in the DDECCONT38 register.

Output clipping is controlled by the DDECCONT18 register bit [2].

The PLLLOCK, HSYNC, VSYNC and FIELD pins may have bus extension functions. This is done by programming the OUTBUS [7:0] bits in the DDECCONT7 register.

| Bitfield  | Descrip                                         | tion  |

|-----------|-------------------------------------------------|-------|

| OUTBUS[0] | 0: Standard function.<br>1: PLLLOCK = OUTBUS[1] |       |

| OUTBUS[6] | 0: Standard function.<br>1: FIELD = OUTBUS[7]   | . (   |

| OUTBUS[4] | 0: Standard function.<br>1: VSYNC = OUTBUS[5]   | 11100 |

| OUTBUS[2] | 0: Standard function.<br>1: HSYNC = OUTBUS[3]   | 01000 |

**Table 13: Output PLL Alternate Functions**

The PLLLOCK pin has a second alternate IRQ (Interrupt Request) function, selected by the PLLLOCKIT\_EN bit in the DDECCONT35 register.

Note: By default, the PLLLOCK, HSYNC, VSYNC, and FIELD pins are used for their primary functions.

# 4.13 VBI Data Slicing and Insertion

The following standards are supported by the VBI Data Slicer (see Table 14). After slicing, VBI data is embedded in the output stream, using the intervals between the End of Active Video (EAV) and the Start of Active Video (SAV) codes of each line and formatted according to the ancillary sequences in compliance with specification ITU-R BT.656. VBI data is inserted in the Output FIFO.

| VBI Standards               | TV Systems<br>(lines/freq.) | TV Lines <sup>1</sup> | Bit Rate<br>(Mbit/s) | Modulation | Bytes per<br>Line |

|-----------------------------|-----------------------------|-----------------------|----------------------|------------|-------------------|

| Teletext B WST              | 625/50                      | 6 to 22               | 6.9375               | NRZ        | 45                |

| VPS                         | 625/50                      | 16                    | 2.5000               | Bi-phase   | 15                |

| wss                         | 625/50                      | 23                    | 0.8333               | Bi-phase   | 14 bits of data   |

| Closed Caption              | 625/50                      | 21/22                 | 0.5035               | NRZ        | 3                 |

| Teletext B-WST <sup>1</sup> | 525/60                      | 10 to 21              | 5.727272             | NRZ        | 37                |

| Closed Caption              | 525/60                      | 21                    | 0.5035               | NRZ        | 3                 |

| Gemstar                     | 525/60                      | 21                    | 1.007                | NRZ        | 5                 |

**Table 14: VBI Slicing Standards**

<sup>1.</sup> Lines are numbered in compliance with specification ITU-R BT.470.

Note: The WST - Teletext C and D (525 lines /60 Hz) formats (NATBS - MOJI) may be covered by the WST - Teletext B (525 lines -60 Hz) format.

# 4.13.1 VBI Formatting Features

### **4.13.1.1 VPS Features**

Video Programming System (VPS) data complies with ETSI specifications.

- Search of VPS data on TV line 16 of each field

- Optional Extended VPS data on three TV lines (15,16 and 17) of each field

- Search of VPS data regardless of the field information

- · Recognition of Start code

- Sampling and decoding of bytes 5 and 11 to 14

- Bi-phase code check

- Generation of bi-phase correctness flags

### **4.13.1.2 WSS Features**

Wide Screen Signaling (WSS) data complies with ETSI specifications.

- Search of WSS data on TV line 23 of each field

- Optional Extended WSS data on four TV lines (21, 22, 23 and 24) of each field

- Search of WSS data regardless of the field information solete P

- Recognition of Start code

- Sampling and decoding of relevant 14 bits

- Bi-phase code check

- Generation of bi-phase correctness flags

### 4.13.1.3 WST Features

World System Teletext (WST) data complies with ETSI specifications. The searched WST format is unique at a given time and is programmed by software through register-based control bits (50 Hz or 60 Hz, etc.).

- Search of WST data starting at TV line 6 for 525-line broadcasts, or TV line 318 for 625-line broadcasts.

- Optional Extended WST data search starting at 2nd TV line (register-based control bit).

- Recognition and check of usual WST frame code (27h).

- Optional recognition and check of programmable extended frame code (register-based value but the three LSBs must be kept at '1').

- Recognition of all packets or recognition of only Service Packets X/30 and X/31 (register-based) control bit).

- Hamming decode & check of Magazine and Page bytes for usual frame code.

- Split of Magazine & Page data in two separate bytes (1st byte is for Magazine, 2nd for Page).

# 4.13.1.4 Closed Caption Features

- Search of CC data during line 21 (NTSC) or line 22 (PAL), regardless of the field information.

- Optional Extended slicing during all the VBI (line 5 to 25 /NTSC or 2 to 25 /PAL), regardless of the field information.

- Recognition and check of usual CC Frame code (11000b).

- Recognition and check of tighter CC Frame code (C2h).

Producils

Generation of Per-byte Parity check flags.

### 4.13.1.5 Gemstar Features

- Search of Gemstar data during the line 21 (NTSC) or line 22 (PAL), regardless of the field information.

- Optional Extended slicing during all the VBI (line 5 to 25 /NTSC or 2 to 25 /PAL), regardless of the field information.

- Recognition and check of usual Gemstar Frame code (x011x1x1b)

- Recognition and check of tighter Gemstar Frame code (10110111b)

# 4.13.2 Data Output Format (DOF)

The Data Output Format stage will add the following data items to those received from the VBI Formatting unit:

- An ancillary preamble

- A User Data Word Count

- Filler Words

- A User Data Word checksum

It will then perform the following operations:

- Byte-to-nibble Data conversion operations

- Calculation of word-wise parity control bits

- User Data Word checksum calculation

The data output flow issued by the Data Output Format is inserted into an ITU-R BT.656-type digitized stream which complies with specifications ITU-R BT.656, ITU-R BT.1364 and SMPTE 291M.

In particular, the data flow follows the 8-bit data coding convention. Ancillary data is coded as "Type 2" 8-bit data items (as defined in both ITU.1364 and SMPTE 291M specifications).

| EAV Blanking Interval | SAV Video Digitalized Stream |  |

|-----------------------|------------------------------|--|

|-----------------------|------------------------------|--|

A maximum of 100 bytes are used in the Blanking Interval for ancillary data. For more information, refer to Table 12: Frame Output Standards.

The Data Output Format unit provides the following data on a TV line base:

- The Transport layer which consists of the Ancillary Data Flag (ADF), Data ID (DID), Secondary Data ID (SDID), Data Count (DC) and Checksum Word (CS).

- The entire data flow generated by the Hardware Filtering, after having split each byte into nibble format.

- The current TV Line value, from which the data was extracted.

### **Ancillary Data Flow**

For each TV line, the following sequence is generated immediately after the EAV code:

| ADF             | DID    | SDID      | DC        | UDWi                  | cs       |

|-----------------|--------|-----------|-----------|-----------------------|----------|

| 3 Bytes         | 1 Byte | 1 Byte    | 1 Byte    | User Data<br>Words    | 1 Byte   |

| 00h - FFh - FFh | 41h    | Format ID | UDW Count | Sliced Data in nibble | Checksum |

# **DID & SDID Coding Convention**

All VBI data formats recognized by the Slicer use the same Data ID value. This Data ID value is programmed in the SLDID[5:0] bits in the VBICONT1 register. The default value of the DID register is "000001" respecting an 8-bit format and coding for 8-bit applications, in compliance with SMPTE 291M specifications (the full default code is 41h when parity control bits are added). Bits 6 and 7 of the DID value are hardware calculated (bit 6 is the even parity of bits 5 to 0, bit 7 is the binary complement of bit 6).

Note: All possible DID values are coded using a Type 2 ancillary data coding format.

The Secondary Data ID codes (SDID) identify the recognized data formats as follows:

SDID1 **SDID Byte** Comments 01 41h WSS (No field link) 02 42h (Not used) 03 83h VPS (No field link) 04 44h Closed Caption - Field 2 05 85h Closed Caption - Field 1 06 86h Gemstar - Field 2 07 47h Gemstar - Field 1 08 48h Teletext B - 625 lines/50 Hz - Field 2 Frame Code: 27h - F = 6.9375 MHz 09 89h Teletext B - 625 lines/50 Hz - Field 1 Frame Code: 27h - F = 6.9375 MHzTeletext B - 625 lines/50 Hz - Field 2 Frame Code:  $XXh^2 - F = 6.9375 MHz$ 0A 8Ah 0B 4Bh Teletext B - 625 lines/50 Hz - Field 1 Frame Codecode: XXh<sup>2</sup> - F = 6.9375 MHz Frame Code: 27h - F = 5.727272 MHz 10 50h Teletext B - 525 lines/60 Hz - Field 2 11 91h Teletext B - 525 lines/60 Hz - Field 1 Frame Code: 27h - F = 5.727272 MHz 12 92h Teletext B - 525 lines/60 Hz - Field 2 Frame Code:  $XXh^2 - F = 5.727272 MHz$ 53h Teletext B - 525 lines/60 Hz - Field 1 13 Frame Code:  $XXh^2 - F = 5.727272 MHz$

**Table 15: Secondary ID Codes**

<sup>1. 8-</sup>bit Format

<sup>2.</sup> A different Frame Code (from the usual one) has been validated for this data. The field information can be recovered from the Data ID value.

## **Data Count (DC) Coding**

The Data Count (DC) byte is coded according to the parity protection scheme defined in SMPTE 291M or ITU-R BT.1364 specifications, as applied to 8-bit coded data (i.e. bit 6 is the even parity check of bits 0 to 5, bit 7 is bit 6 complement to 1). In 8-bit applications, the DC byte gives a value as a 4-byte group.

The number of the group of 4 User Data Words (UDW) transferred for the corresponding TV line is given in the DC byte using 6 bits.

### Checksum (CS) Coding

The Checksum (CS) byte is coded according to the parity protection scheme defined in SMPTE 291M or ITU-R BT.1364 specifications, as applied to 8-bit coded data.

Bits 6 to 0 are the LSB bits of the result of the sum of the seven LSB bits of DID, SDID, DC and all UDW bytes (any carry is dropped). Bit 7 is the complement of Bit 6.

# **User Data Word (UDW) Coding**

As 00h and FFh codes are prohibited in ITU-R BT.656 specifications, each data byte is substituted by a pair of bytes; these two bytes are respectively built with:

- The lower data nibble for the lower nibble of the 1st byte.

- The upper data nibble for the lower nibble of the 2<sup>nd</sup> byte.

Data is transmitted in the same temporal order as for the Hardware Filtering.

The TV line value is also provided to the DOF block to prevent scrambling errors when the ancillary data flow is re-mixed with the video flow.

### **User Data Word Filler**

As data is coded according to the 8-bit application protocol described in SMPTE 291M and ITU-R BT.1364 specifications, some extra bytes may be inserted into the User Data Word sequence. These bytes code the value 80h which is meaningless and is used only to maintain a 4-byte UDW modularity (in compliance with the above specifications). These meaningless bytes are also used to maintain the most adequate 4-byte wise data storing format handled by the microcontroller.

When an application is running, it is important that these filler bytes are not processed as valid data items.

### **UDW Coding for WST - Teletext B**

For World System Teletext (WST) standards, the UDW coding scheme depends on the searched frame code.

When the searched frame code is the usual code (27h), the two first UDW words code the Magazine (3 bits) and the Page (5 bits) values. In this case, there is no need to perform a nibble split on these two words. When the searched frame code is validated with a programmable value, a split of the two first words is applied (as they may not be necessarily Hamming 8/4 coded).

The above bytes are followed by 80 bytes (respectively 64 bytes in 525/60Hz) resulting of the nibble split of the 40 bytes (respectively 32 bytes in 525/60Hz) decoded from the current TV ancillary data.

Table 16: Magazine and Page Coding

| Bit                        | 7                       | 6                                | 5        | 4 | 3 | 2          | 1    | 0 |

|----------------------------|-------------------------|----------------------------------|----------|---|---|------------|------|---|

| Magazine<br>Byte<br>Coding | Bit 6<br>1's complement | Even parity check for bits [5:0] | Always 0 |   |   | Magazine v | alue |   |

**Table 16: Magazine and Page Coding**

| Bit                 | 7                       | 6                                      | 5        | 4          | 3 | 2 | 1 | 0 |

|---------------------|-------------------------|----------------------------------------|----------|------------|---|---|---|---|

| Page Byte<br>Coding | Bit 6<br>1's complement | Even parity<br>check for bits<br>[5:0] | Always 0 | Page value |   |   |   |   |

In both cases, two filler bytes are added immediately after the last meaningful User Data Word in order to maintain a Data Count value that is a multiple of 4 bytes.

All UDW bytes are coded according to the parity protection scheme defined in SMPTE 291M or ITU-R BT.1364 specifications, as applied to 8-bit coded data (i.e. bit 6 is the even parity check of bits 0 to 5 and bit 7 is bit 6 complement to1).

**Table 17: UDW Coding for WST**

| Frame Code            |     |            | ADF | DID | SDID | DC | MAG | PAGE | Other<br>UDW<br>Bytes | FIL1 | FIL2 | cs |

|-----------------------|-----|------------|-----|-----|------|----|-----|------|-----------------------|------|------|----|

| WST - 625 lines/50 Hz | 27h | Byte.count | 3   | 1   | 1    | 1  | 1   | 1    | 80                    | 1    | 101  | 1  |

| WST - 625 lines/50 Hz | xxh | Byte.count | 3   | 1   | 1    | 1  | 0   | 0    | 84                    | 0    | 0    | 1  |

| WST - 525 lines/60 Hz | 27h | Byte.count | 3   | 1   | 1    | 1  | 1   | 1    | 64                    | 7    | 1    | 1  |

| WST - 525 lines/60 Hz | xxh | Byte.count | 3   | 1   | 1    | 1  | 0   | 0    | 68                    | 0    | 0    | 1  |

Note: "FIL1" and "FIL2" stand for Filler Bytes 1 and 2.

**Table 18: UDW Byte Contents**

| Byt<br>e | 625 lines / 50 Hz<br>Content<br>(Framing = 27h) | 625 lines / 50 Hz<br>Content<br>(Custom Framing) | Byt<br>e | 525 lines / 60 Hz<br>Content<br>(Framing = 27h) | 525 lines / 60 Hz<br>Content<br>(Custom Framing) |

|----------|-------------------------------------------------|--------------------------------------------------|----------|-------------------------------------------------|--------------------------------------------------|

| 1        | Decoded Magazine value                          | LSB of Raw sliced 1 <sup>st</sup> byte           | 1        | Decoded Magazine value                          | LSB of Raw sliced 1 <sup>st</sup> byte           |

| 2        | Decoded Page value                              | MSB of Raw sliced 1 <sup>st</sup><br>byte        | 2        | Decoded Page value                              | MSB of Raw sliced 1 <sup>st</sup> byte           |

| 3        | LSB of 1 <sup>st</sup> data byte                | LSB of Raw sliced 2 <sup>nd</sup> byte           | 3        | LSB of 1 <sup>st</sup> data byte                | LSB of Raw sliced 2 <sup>nd</sup> byte           |

| 4        | MSB of 1 <sup>st</sup> data byte                | MSB of Raw sliced 2 <sup>nd</sup> byte           | 4        | MSB of 1 <sup>st</sup> data byte                | MSB of Raw sliced 2 <sup>nd</sup> byte           |

| 5        | LSB of 2 <sup>nd</sup> data byte                | LSB of Next raw byte                             | 5        | LSB of 2 <sup>nd</sup> data byte                | LSB of Next raw byte                             |

| 6        | MSB of 2 <sup>nd</sup> data byte                | MSB of Next raw byte                             | 6        | MSB of 2 <sup>nd</sup> data byte                | MSB of Next raw byte                             |

|          |                                                 |                                                  |          |                                                 |                                                  |

|          |                                                 |                                                  | 67       | LSB of 32 <sup>nd</sup> data byte               | LSB of Last raw byte                             |

| 83       | LSB of 40 <sup>th</sup> data byte               | LSB of Last raw byte                             | 68       | MSB of 32 <sup>nd</sup> data byte               | MSB of Last raw byte                             |

| 84       | MSB of 40 <sup>th</sup> data byte               | MSB of Last raw byte                             |          |                                                 |                                                  |

# **UDW Coding for VPS**

In Video Programming Systems (VPS), a nibble split algorithm is applied. In all bytes, bit 6 is the even parity check of bits 5 to 0. Bit 7 is the complement of bit 6.

# Table 19: UDW Coding for VPS

| ADF | DID | SDID | DC | VPUD | CS |

|-----|-----|------|----|------|------|------|------|------|------|------|------|------|------|------|------|----|

|     |     |      |    | 00   | 01   | 10   | 11   | 20   | 21   | 30   | 31   | 40   | 41   | S0   | S1   |    |

The result of the VPS sliced information is providing 12 bytes of data, which are generated in the following order:

• **VPUD00:** This byte provides the LSB contents of VPS byte 5.

| bit | 7 | 6 | 5 | 4 | 3   | 2   | 1   | 0   |