# Integrated Transceiver Modules for WLAN 802.11 b/g/n, Bluetooth.

### **FEATURES**

- IEEE 802.11 b,g,n,d,e,i, compliant.

- Typical WLAN Transmit Power:

- o 20.0 dBm, 11 Mbps, CCK (b).

- o 14.5 dBm, 54 Mbps, OFDM (g).

- o 12.5 dBm, 65 Mbps, OFDM (n).

- Bluetooth 2.1+EDR, Power Class 1.5.

- Typical WLAN Sensitivity:

- o 89 dBm, 8% PER,11 Mbps.

- o -76 dBm, 10% PER, 54 Mbps.

- - 73 dBm, 10% PER, 65 Mbps.

- Miniature footprint: 18 mm x 13 mm

- Low height profile: 1.9 mm.

- U.FL connector for external antenna.

- Terminal for PCB/Chip antenna feeds.

- Integrated band-pass filter

- Worldwide acceptance: FCC (USA), IC (Canada), and ETSI (Europe)

- Compact design based on Texas Instruments WL1271WSP Transceiver.

- Seamless integration with TI OMAP™ application processor.

- SDIO Host data path interfaces.

- Bluetooth Advanced Audio Interfaces

- Low power operation mode.

- RoHS compliant

- Streamlined development with LSR design services.

# **APPLICATIONS**

- Security

- HVAC Control , Smart Energy

- Sensor Networks

- Medical

#### DESCRIPTION

The TiWi module is a high performance 2.4 GHz IEEE 802.11 b/g/n Bluetooth 2.1+EDR radio in a cost effective, pre-certified footprint.

The module realizes the necessary PHY/MAC layers to support WLAN applications in conjunction with a host processor over a SDIO interface.

The module also provides a Bluetooth platform through the HCI transport layer. Both WLAN and Bluetooth share the same antenna port.

Need to get to market quickly? Not an expert in 802.11. or Bluetooth? Need a custom antenna? Would you like to own the design? Would you like a custom design? Not quite what you need? Do you need help with your host board? LS Research Design Services will be happy to develop custom hardware or software, integrate the design, or license the design so you can manufacture yourself. Contact us at sales@lsr.com or call us at 262-375-4400.

# **ORDERING INFORMATION**

| Order Number    | Description                                             |

|-----------------|---------------------------------------------------------|

| LS240-WI-01-A20 | This order number has been replaced with 450-0009       |

| 450-0009        | TiWi-R1 Module with U.FL connector for external antenna |

|                 | TiWi-R1 Module with U.FL connector for external antenna |

Table 1: Orderable TiWi-R1 Model Numbers

### **MODULE ACCESSORIES**

| Order Number | Description                                                   |

|--------------|---------------------------------------------------------------|

| 001-0001     | 2.4 GHz Dipole Antenna with Reverse<br>Polarity SMA Connector |

| <br>080-0001 | u.fl to Reverse Polarity SMA Bulkhead<br>Cable 105mm          |

# **END OF LIFE NOTIFICATION**

The footprint of the TiWi-R1 is changing and the new model will be called TiWi-R2. Please see Footprint Migration Document (LSR # 330-0043) on the TiWi page at <u>www.lsr.com/tiwi</u> for more information.

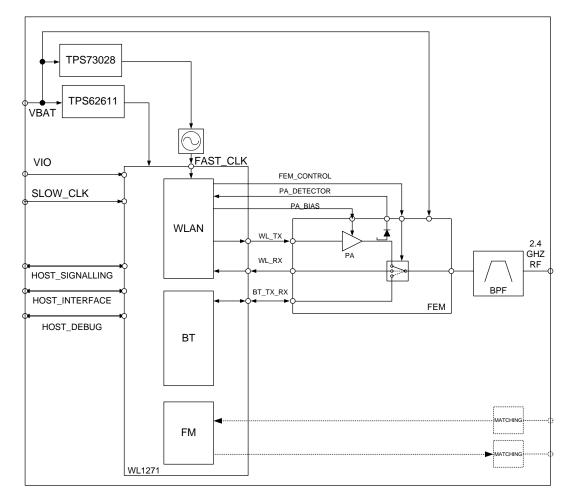

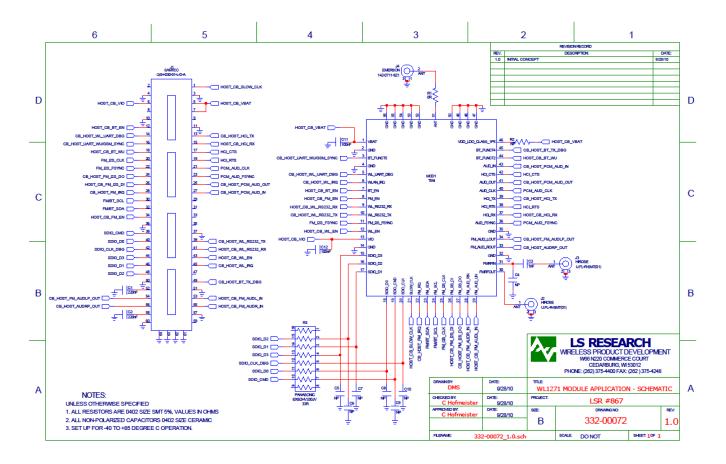

# **BLOCK DIAGRAM**

Figure 1: TiWi Module Block Diagram – Top-Level

The information in this document is subject to change without notice. Confirm the data is current by downloading the latest revision from www.lsr.com.

# TABLE OF CONTENTS

| FEATURES1                                                                                                                   |

|-----------------------------------------------------------------------------------------------------------------------------|

| APPLICATIONS                                                                                                                |

| DESCRIPTION1                                                                                                                |

| ORDERING INFORMATION                                                                                                        |

| MODULE ACCESSORIES2                                                                                                         |

| END OF LIFE NOTIFICATION                                                                                                    |

| BLOCK DIAGRAM                                                                                                               |

| TIWI™ MODULE FOOTPRINT AND PIN DEFINITIONS6                                                                                 |

| PIN DESCRIPTIONS                                                                                                            |

| ELECTRICAL SPECIFICATIONS       9         Absolute Maximum Ratings       9         Recommended Operating Conditions       9 |

| General Characteristics                                                                                                     |

| BLUETOOTH RF Characteristics                                                                                                |

| WLAN POWER-UP SEQUENCE                                                                                                      |

| WLAN POWER-DOWN SEQUENCE                                                                                                    |

| BLUETOOTH POWER-UP SEQUENCE                                                                                                 |

| BLUETOOTH POWER-DOWN SEQUENCE                                                                                               |

| ENABLE SCHEME                                                                                                               |

| IRQ OPERATION                                                                                                               |

| SLOW (32 KHZ) CLOCK SOURCE REQUIREMENTS                                                                                     |

| BT HCI UART                                                                                                                 |

| SDIO INTERFACE TIMING                                                                                                       |

| SDIO CLOCK TIMING                                                                                                           |

The information in this document is subject to change without notice. Confirm the data is current by downloading the latest revision from www.lsr.com.

Downloaded from Elcodis.com electronic components distributor

| APPLICATION SCHEMATIC            |  |

|----------------------------------|--|

| SOLDERING RECOMMENDATIONS        |  |

| Recommended Reflow Profile       |  |

| Lead (Pb) Free Soldering Paste   |  |

| Cleaning                         |  |

| Optical Inspection               |  |

| Repeating Reflow Soldering       |  |

| Wave Soldering                   |  |

| Hand Soldering                   |  |

| Rework                           |  |

| Additional Grounding             |  |

| SHIPPING, HANDLING, AND STORAGE  |  |

| Shipping                         |  |

| Handling                         |  |

| Moisture Sensitivity Level (MSL) |  |

| Storage                          |  |

| AGENCY CERTIFICATIONS            |  |

| MECHANICAL DATA                  |  |

| MODULE REVISION HISTORY          |  |

| Rev A                            |  |

| CONTACTING LS RESEARCH           |  |

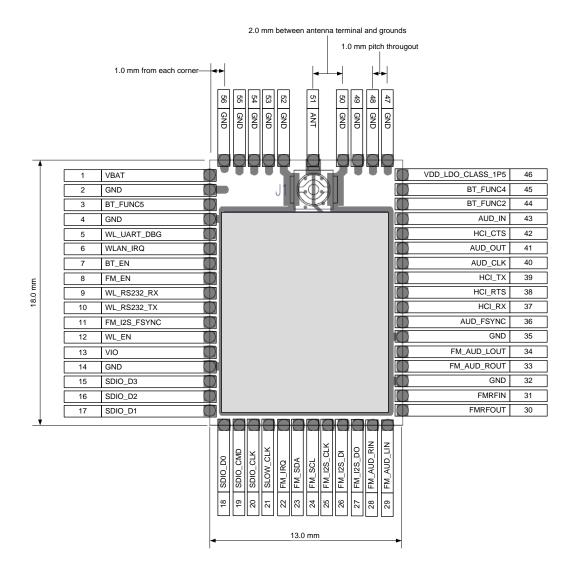

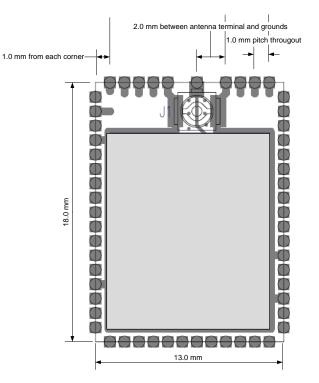

### TIWI™ MODULE FOOTPRINT AND PIN DEFINITIONS

To apply the TiWi<sup>™</sup> module, it is important to use the module pins in your application as they are designated in below and in the corresponding pin definition table found on pages 7 and 8. Not all the pins on the TiWi module may be used, as some are reserved for future functionality.

Figure 2: TiWi™ PIN DEFINITIONS and Generic Module Footprint

# **PIN DESCRIPTIONS**

| Module<br>Pin | Name         | l/O<br>Type | Buffer<br>Type | Description [termination if FM not used]      |

|---------------|--------------|-------------|----------------|-----------------------------------------------|

| 1             | VBAT         | PI          | -              | Battery Voltage 3.6 VDC Nominal (3.0-4.8 VDC) |

| 2             | GND          | GND         | -              | Ground                                        |

| 3             | BT_FUNC5     | DO          | 4 mA           | HOST_WU (*)                                   |

| 4             | GND          | GND         | -              | Ground                                        |

| 5             | WL_UART_DBG  | DIO         | 4 mA           | WL_UART_DBG                                   |

| 6             | WLAN_IRQ     | DO          | 4 mA           | WLAN Interrupt Request                        |

| 7             | BT_EN        | DI          | -              | BT_RST                                        |

| 8             | FM_EN        | DI          | -              | FM_RST [GND]                                  |

| 9             | WL_RS232_RX  | DI          | -              | WLAN TEST UART RX (*)                         |

| 10            | WL_RW_232_TX | DO          | 4 mA           | WLAN TEST UART TX (*)                         |

| 11            | FM_I2S_FSYNC | DO          | 4 mA           | FM_I2S_IF [NC, OPEN] (*)                      |

| 12            | WL_EN        | DI          | -              | WL_RST                                        |

| 13            | VIO          | PI          | -              | POWER SUPPLY FOR 1.8 VDC DIGITAL DOMAIN       |

| 14            | GND          | GND         | -              | Ground                                        |

| 15            | SDIO_D3      | DIO         | 8 mA           | SDIO INTERFACE, HOST PULL UP                  |

| 16            | SDIO_D2      | DIO         | 8 mA           | SDIO INTERFACE, HOST PULL UP                  |

| 17            | SDIO_D1      | DIO         | 8 mA           | SDIO INTERFACE, HOST PULL UP                  |

| 18            | SDIO_D0      | DIO         | 8 mA           | SDIO INTERFACE, HOST PULL UP                  |

| 19            | SDIO_CMD     | DIO         | 8 mA           | HOST PULL UP                                  |

| 20            | SDIO_CLK     | DI          | -              | HOST PULL UP                                  |

| 21            | SLOW_CLK     | DI          | -              | SLEEP CLOCK (32 kHz), 1.8 VDC DIGITAL DOMAIN  |

| 22            | FM_IRQ       | DO          | 4 mA           | FM_I2C_IF [NC, OPEN] (*)                      |

| 23            | FM_SDA       | DO          | 4 mA           | FM_I2C_IF [NC, OPEN] (*)                      |

| 24            | FM_SCL       | DO          | 4 mA           | FM_I2C_IF [NC, OPEN] (*)                      |

| 25            | FM_I2S_CLK   | DO          | 4 mA           | FM_I2C_IF [NC, OPEN] (*)                      |

| 26            | FM_I2S_DI    | DI          | 4 mA           | FM_I2C_IF [GND]                               |

| 27            | FM_I2S_DO    | DO          | 4 mA           | FM_I2C_IF [NC, OPEN] (*)                      |

| 28            | FM_AUD_RIN   | AI          | -              | FM_AUD_RIN [GND]                              |

| 29            | FM_AUD_LIN   | AI          | -              | FM_AUD_LIN[GND]                               |

| 30            | FMRFOUT      | AO          | -              | FMRFOUT [NC, OPEN]                            |

| 31            | FMRFIN       | AI          | -              | FMRFIN [GND]                                  |

The information in this document is subject to change without notice. Confirm the data is current by downloading the latest revision from www.lsr.com.

Downloaded from Elcodis.com electronic components distributor

| Module<br>Pin | Name              | l/O<br>Type | Buffer<br>Type | Description [termination if FM not used]           |

|---------------|-------------------|-------------|----------------|----------------------------------------------------|

| 32            | GND               | GND         | -              | Ground                                             |

| 33            | FM_AUD_ROUT       | AO          | -              | FM_AUD_ROUT [NC, OPEN]                             |

| 34            | FM_AUD_LOUT       | AO          | -              | FM_AUD_LOUT [NC,OPEN]                              |

| 35            | GND               | GND         | -              | Ground                                             |

| 36            | AUD_FSYNC         | DIO         | 4 mA           | PCM I/F or FM_I2S_FSYNC                            |

| 37            | HCI_RX            | DI          | 8 mA           | BT UART I/F or btSPI_DIN (*)                       |

| 38            | HCI_RTS           | DO          | 4 mA           | BT UART I/F or btSPI_IRQ (*)                       |

| 39            | HCI_TX            | DIO         | 8 mA           | BT UART I/F or btSPI_DOUT                          |

| 40            | AUD_CLK           | DO          | 4 mA           | PCM I/F or FM_I2S_CLK (*)                          |

| 41            | AUD_OUT           | DO          | 4 mA           | PCM I/F or FM_I2S_DO (*)                           |

| 42            | HCI_CTS           | DI          | 4 mA           | BT UART I/F or btSPI_CS (*)                        |

| 43            | AUD_IN            | DI          | 4 mA           | PCM I/F or FM_I2S_DI (*)                           |

| 44            | BT_FUNC2          | DI          | 4 mA           | BT WU/ DC2DC mode (*)                              |

| 45            | BT_FUNC4          | DO          | 4 mA           | BT_UARTD (DEBUG) (*)                               |

| 46            | VDD_LDO_CLASS_1P5 | NC          | -              | VBAT VOLTAGE PRESENT, NO CONNECT                   |

| 47            | GND               | GND         | -              | Ground                                             |

| 48            | GND               | GND         | -              | Ground                                             |

| 49            | GND               | GND         | -              | Ground                                             |

| 50            | GND               | GND         | -              | Ground                                             |

| 51            | ANT               | RF          |                | Antenna terminal for WLAN and Bluetooth (note [1]) |

| 52            | GND               | GND         | -              | Ground                                             |

| 53            | GND               | GND         | -              | Ground                                             |

| 54            | GND               | GND         | -              | Ground                                             |

| 55            | GND               | GND         | -              | Ground                                             |

| 56            | GND               | GND         | -              | Ground                                             |

PI = Power Input PO = Power Output DI = Digital Input DI = Digital Mput DO = Digital Output AI = Analog Input AO=Analog Output AIO = Bi-directional Analog Port RF = Bi-directional RF Port

GND=Ground

Note[1]: Antenna terminal presents d.c. short circuit to ground.

(\*) indicates that pin is capable of bidirectional operation, but is used as the type shown.

**Table 2: TIWi Module Pin Descriptions**

The information in this document is subject to change without notice. Confirm the data is current by downloading the latest revision from www.lsr.com.

Downloaded from Elcodis.com electronic components distributor

# **ELECTRICAL SPECIFICATIONS**

The majority of these characteristics are based on controlling and conditioning the tests using the evaluation kit and TiWi control software application. Other control conditions may require these values to be re-characterized by the customer.

### **Absolute Maximum Ratings**

| Parameter                    | Min  | Мах       | Unit |

|------------------------------|------|-----------|------|

| Power supply voltage (VBAT)  | -0.5 | +5.5      | V    |

| Digital supply voltage (VIO) | -0.5 | 2.1       | V    |

| Voltage on any GPIO          | -0.5 | VIO + 0.5 | V    |

| Voltage on any Analog Pins   | -0.5 | 2.1       | V    |

| RF input power, antenna port |      | +10       | dBm  |

| Operating temperature        | -40  | +85       | ٥C   |

| Storage temperature          | -    | +105      | ٥C   |

Table 3: Absolute Maximum Ratings<sup>1</sup>

# **Recommended Operating Conditions**

| Parameter                 | Min        | Тур | Мах        | Unit |

|---------------------------|------------|-----|------------|------|

| V <sub>BAT</sub>          | 3.0        | 3.6 | 4.8        | V    |

| VIO                       | 1.62       | 1.8 | 1.92       | V    |

| V <sub>IH</sub>           | 0.65 X VIO | -   | VIO        | V    |

| V <sub>IL</sub>           | 0          | -   | 0.35 X VIO | V    |

| V <sub>OH</sub> @ 4, 8 mA | VIO-0.45   | -   | VIO        | V    |

| V <sub>OL</sub> @ 4, 8 mA | 0          | -   | 0.45       | V    |

| Ambient temperature range | -40        | 25  | 85         | °C   |

**Table 4: Recommended Operating Conditions**

<sup>1</sup> Under no circumstances should exceeding the ratings specified in the Absolute Maximum Ratings section be allowed. Stressing the module beyond these limits may result permanent damage to the module that is not covered by the warranty.

The information in this document is subject to change without notice. Confirm the data is current by downloading the latest revision from www.lsr.com.

# **General Characteristics**

| Parameter               | Min  | Тур                                | Мах  | Unit |

|-------------------------|------|------------------------------------|------|------|

| WLAN RF frequency range | 2412 |                                    | 2472 | MHz  |

| WLAN RF data rate       | 1    | 802.11 b/g/n<br>rates<br>supported | 65   | Mbps |

| BT RF frequency Range   | 2402 |                                    | 2480 | MHz  |

**Table 5 General Characteristics**

### Power Consumption - WLAN

| Parameter           | Test Conditions                                           | Min | Тур  | Мах | Unit |

|---------------------|-----------------------------------------------------------|-----|------|-----|------|

|                     | 2437 MHz, V <sub>BAT</sub> =3.6V, T <sub>amb</sub> =+25°C |     |      |     |      |

| CCK (b) TX Current  | Po=20 dBm, 11 Mbps CCK                                    | -   | 280  | -   | mA   |

|                     | L=1200 bytes, $t_{delay}$ (idle)=4 $\mu$ S.               |     |      |     |      |

|                     | 2437 MHz, V <sub>BAT</sub> =3.6V, T <sub>amb</sub> =+25°C |     |      |     |      |

| OFDM (g) TX Current | Po=14.5 dBm, 54 Mbps OFDM                                 | -   | 185  | -   | mA   |

| GFDM (g) TX Current | L=1200 bytes, $t_{delay}$ (idle)=4 $\mu$ S.               |     |      |     |      |

|                     | 2437 MHz, V <sub>BAT</sub> =3.6V, T <sub>amb</sub> =+25°C |     |      |     |      |

| OFDM (n) TX Current | Po=12.5 dBm, 65 Mbps OFDM                                 | -   | 165  | -   | mA   |

|                     | L=1200 bytes, $t_{delay}$ (idle)=4 $\mu$ S.               |     |      |     |      |

| CCK (b) RX Current  |                                                           | -   | 100  | -   | mA   |

| OFDM (g) RX Current |                                                           | -   | 100  | -   | mA   |

| OFDM (n) RX Current |                                                           | -   | 100  | -   | mA   |

| Dynamic Mode [1]    |                                                           | -   | <1.2 | -   | mA   |

### Table 6: WLAN Power Consumption

[1] Total Current from  $V_{BAT}$  for reception of Beacons with DTIM=1 TBTT=100 mS, Beacon duration 1.6ms, 1 Mbps beacon reception in Listen Mode.

#### **Power Consumption - Bluetooth**

| Parameter          | Test Conditions                        | Min | Тур | Мах | Unit |

|--------------------|----------------------------------------|-----|-----|-----|------|

| GFSK TX Current    | Constant Transmit, DH5, PRBS9          | -   | 45  | -   | mA   |

| EDR TX Current     | Constant Transmit, 2DH5,3DH5,<br>PRBS9 | -   | 43  | -   | mA   |

| GFSK RX Current    | Constant Receive, DH1                  | -   | 35  | -   | mA   |

| EDR RX Current     | Constant Receive, 2DH5, 3DH5           | -   | 41  | -   | mA   |

| Deep Sleep Current | Deep Sleep Mode                        | -   | 70  | -   | μA   |

#### Table 7: Bluetooth Power Consumption

#### DC Characteristics – General Purpose I/O

| Parameter                                            | Test Conditions | Min        | Тур | Мах        | Unit |

|------------------------------------------------------|-----------------|------------|-----|------------|------|

| Logic input low, V <sub>IL</sub>                     |                 | 0          | -   | 0.35 X VIO | V    |

| Logic input high, V <sub>IH</sub>                    |                 | 0.65 X VIO | -   | VIO        | V    |

| Logic output low, V <sub>OL</sub>                    | lout = 8 mA     | 0          | -   | 0.45       | V    |

| (Full Drive)                                         | lout = 4 mA     | 0          | -   | 0.45       | V    |

| Logic output low, V <sub>OL</sub><br>(Reduced Drive) | lout = 1 mA     | 0          | -   | 0.112      | V    |

|                                                      | lout = 0.09 mA  | 0          | -   | 0.01       | V    |

| Logic output high, V <sub>OH</sub>                   | lout = -8 mA    | VIO-0.45   | -   | VCC        | V    |

| (Full Drive)                                         | lout = -4 mA    | VIO-0.45   | -   | VCC        | V    |

| Logic output high, V <sub>OH</sub>                   | lout = -1 mA    | VIO-0.112  | -   | VCC        | V    |

| (Reduced Drive)                                      | lout = -0.3 mA  | VIO-0.033  | -   | VCC        | V    |

#### Table 8: DC Characteristics General Purpose I/O

# **WLAN RF Characteristics**

#### WLAN Transmitter Characteristics (TA =25°C, VBAT=3.6 V)

| Parameter                            | Test Conditions                                                                    | Min | Тур  | Max | Unit |

|--------------------------------------|------------------------------------------------------------------------------------|-----|------|-----|------|

| 11 Mbps CCK (b) TX<br>Output Power   | 11 Mbps CCK , 802.11(b) Mask<br>Compliance, 35% EVM<br>RMS power over TX packet    | -   | 20   | -   | dBm  |

| 9 Mbps OFDM (g) TX<br>Output Power   | 9 Mbps OFDM , 802.11(g) Mask<br>Compliance, -8 dB EVM<br>RMS power over TX packet  | -   | 19   | -   | dBm  |

| 54 Mbps OFDM (g) TX<br>Output Power  | 54 Mbps OFDM, 802.11(g) Mask<br>Compliance, -25 dB EVM<br>RMS power over TX packet | -   | 14.5 | -   | dBm  |

| 6.5 Mbps OFDM (n) TX<br>Output Power | 6.5 Mbps OFDM, 802.11(n) Mask<br>Compliance, -5 dB EVM<br>RMS power over TX packet | -   | 19   | -   | dBm  |

| 65 Mbps OFDM (n) TX<br>Output Power  | 65 Mbps OFDM, 802.11(n) Mask<br>Compliance, -28 dB EVM<br>RMS power over TX packet | -   | 12.5 | -   | dBm  |

**Table 9: WLAN Transmitter RF Characteristics**

### WLAN Receiver Characteristics (TA =25°C, VBAT=3.6 V) [1]

| Parameter                             | Test Conditions | Min | Тур | Max | Unit |

|---------------------------------------|-----------------|-----|-----|-----|------|

| 1 Mbps CCK (b) RX<br>Sensitivity      | 8% PER          | -   | -97 | -   | dBm  |

| 11 Mbps CCK (b) RX<br>Sensitivity     | 8% PER          | -   | -89 | -   | dBm  |

| 9 Mbps OFDM (g) RX<br>Sensitivity     | 10% PER         | -   | -90 | -   | dBm  |

| 54 Mbps OFDM (g) RX<br>Sensitivity    | 10% PER         | -   | -76 | -   | dBm  |

| 6.5 Mbps OFDM (n) RX<br>Sensitivity   | 10% PER         | -   | -91 | -   | dBm  |

| 65 Mbps OFDM (n) RX<br>Sensitivity    | 10% PER         | -   | -73 |     | dBm  |

| 11 Mbps CCK (b) RX<br>Overload Level. | 8% PER          | -10 | -   | -   | dBm  |

| 6 Mbps OFDM(g) RX<br>Overload Level.  | 10% PER         | -20 | -   | -   | dBm  |

| 54 Mbps OFDM(g) RX<br>Overload Level. | 10% PER         | -20 | -   | -   | dBm  |

| 65 Mbps OFDM(n) RX<br>Overload Level. | 10% PER         | -20 | -   | -   | dBm  |

[1] Up to 2 dB degradation at Channel 13 for 11g/n modes and up to 2 dB degradation at Channel 14 for 11b/g/n modes.

**Table 10: WLAN Receiver RF Characteristics**

# **BLUETOOTH RF Characteristics**

# Bluetooth Transmitter GFSK and EDR Characteristics, Class 1.5 (TA =25°C, VBAT=3.6 V)

| Parameter               | Test<br>Conditions | Min | Тур | Мах | BT Spec | Unit |

|-------------------------|--------------------|-----|-----|-----|---------|------|

| GFSK RF Output Power    |                    | -   | 9.5 | -   | -       | dBm  |

| EDR RF Output Power     |                    | -   | 7   | -   |         |      |

| Power Control Step Size |                    | 2   | 4   | 8   | 2-8     | dB   |

| EDR Relative Power      |                    | -2  |     | 1   | -4/+1   | dB   |

#### Table 11: Bluetooth Transmitter RF Characteristics

#### Bluetooth Receiver Characteristics (TA =25°C, VBAT=3.6 V)

| Parameter                 | Test<br>Conditions | Min | Тур | Max | BT Spec | Unit |

|---------------------------|--------------------|-----|-----|-----|---------|------|

| GFSK Sensitivity          | BER=0.1%           | -   | -92 | -   | -70     | dBm  |

| EDR 2 Mbps Sensitivity    | BER=0.01%          | -   | -91 | -   | -70     | dBm  |

| EDR 3 Mbps Sensitivity    | BER=0.01%          | -   | -82 | -   | -70     | dBm  |

| GFSK Maximum Input Level  | BER=0.1%           | -   | -5  | -   | -20     | dBm  |

| EDR 2 Maximum Input Level | BER=0.1%           | -   | -10 | -   | -       | dBm  |

| EDR 3 Maximum Input Level | BER=0.1%           | -   | -10 | -   | -       | -    |

#### Table 12: Bluetooth Receiver RF Characteristics

The information in this document is subject to change without notice. Confirm the data is current by downloading the latest revision from www.lsr.com.

Downloaded from Elcodis.com electronic components distributor

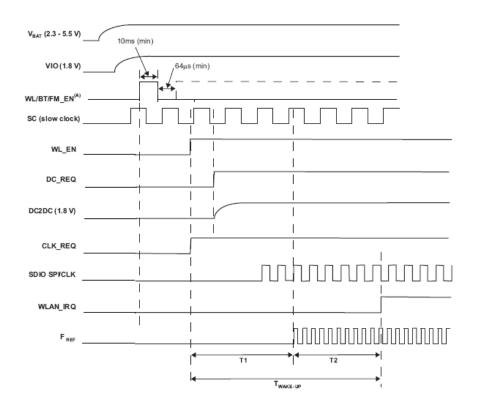

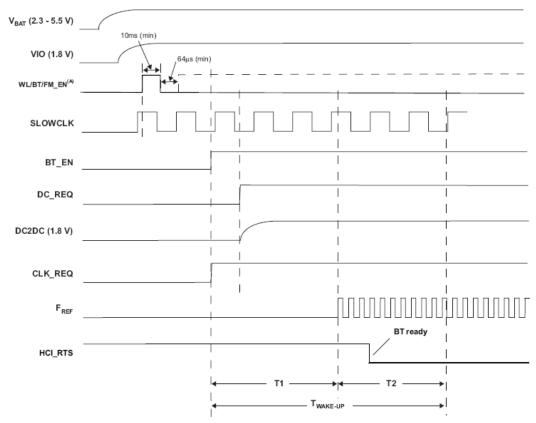

# WLAN POWER-UP SEQUENCE

A. After this sequence is completed, the device is in the low VIO-leakage state while in shutdown.

#### Figure 4-1: TiWi Power-up Sequence Requirements

The following sequence describes device power-up from shutdown. Only the WLAN Core is enabled; the BT and FM cores are disabled.

1. No signals are allowed on the IO pins if no IO power supplied, because the IOs are not 'fail safe'. Exceptions are CLK\_REQ\_OUT, SLOWCLK, XTALP and AUD\_xxx, which are failsafe and can tolerate external voltages with no VDDS and DC2DC".

2. VBAT, VIO and SLOWCLK must be available before WL\_EN.

3. Twakeup = T1 + T2

The duration of T1 is defined as the time from WL\_EN=high until Fref is valid for the SoC, T1 ~55ms

The duration of T2 depends on:

- Operating system

- Host enumeration for the SDIO/WSPI

- PLL configuration

- Firmware download

- Releasing the core from reset

- Firmware initialization

The information in this document is subject to change without notice. Confirm the data is current by downloading the latest revision from www.lsr.com.

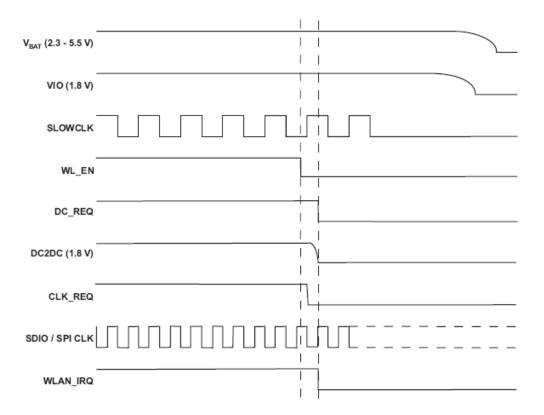

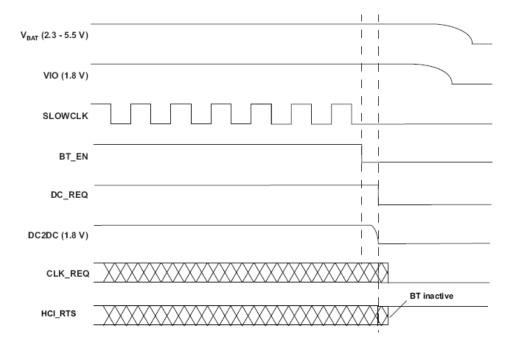

# WLAN POWER-DOWN SEQUENCE

Figure 4-2: TiWi Module Power-down Sequence Requirements

1. DC\_REQ will go low only if WLAN is the only core working. Otherwise if another core is working (e.g BT) it will stay high.

2. CLK\_REQ will go low only if WLAN is the only core working. Otherwise if another core is working and using the Fref (e.g BT) it will stay high.

3. If WLAN is the only core that is operating, WL\_EN must remain de-asserted for at least  $64\mu$ sec before it is re-asserted.

# **BLUETOOTH POWER-UP SEQUENCE**

The following sequence describes device power up from shutdown. Only the BT core is enabled; the WLAN core is disabled.

Power up requirements:

1. No signals are allowed on the IO pins if no IO power supplied, because the IOs are not 'failsafe'. Exceptions are CLK\_REQ\_OUT, SLOWCLK, XTALP and AUD\_xxx, which are failsafe and can tolerate external voltages with no VDDS and DC2DC.

2. VDDS and SLOWCLK must be stable before releasing BT\_EN.

3. Fast clock must be stable maximum 55 ms after BT\_EN goes HIGH.

A. After this sequence is completed, the device is in the low VIO-leakage state while in shutdown.

Figure 4-3. BT Power-up Sequence

The information in this document is subject to change without notice. Confirm the data is current by downloading the latest revision from www.lsr.com.

# **BLUETOOTH POWER-DOWN SEQUENCE**

Figure 4-4. BT Power-down Sequence

The TiWi module indicates completion of BT power up sequence by asserting RTS low. This occurs up to 100 ms after BT\_EN goes high.

### ENABLE SCHEME

The module has 3 enable pins, one for each core: WL\_EN, and BT\_EN and FM\_EN. Presently, there are 2 modes of active operation now supported: WLAN and BT. It is recommended that the FM\_EN pin be grounded to disable the FM section. It is also recommended that the FM section be disabled by Bluetooth HCI commands.

1. Each core is operated independently by asserting each EN to Logic '1'. in this mode it is possible to control each core asynchronously and independently.

2. BT mode operation. WLAN will be operated through WL\_EN asynchronously independently of BT

# **IRQ OPERATION**

- 1. The default state of the WLAN\_IRQ prior to firmware initialization is 0.

- 2. During firmware initialization, the WLAN\_IRQ is configured by the SDIO module; a WLAN\_IRQ changes its state to 1.

- 3. A WLAN firmware interrupt is handled as follows:

- a. The WLAN firmware creates an Interrupt-to-Host, indicated by a 1-to-0 transition on the WLAN\_IRQ line (host must be configured as active-low or falling-edge detect).

- b. After the host is available, depending on the interrupt priority and other host tasks, it masks the firmware interrupt. The WLAN\_IRQ line returns to 1 (0-to-1 transition on the WLAN\_IRQ line).

- c. The host reads the internal register status to determine the interrupt sources the register is cleared after the read.

- d. The host processes in sequence all the interrupts read from this register

- e. The host unmasks the firmware interrupts.

- 4. The host is ready to receive another interrupt from the WLAN device.

# SLOW (32 KHZ) CLOCK SOURCE REQUIREMENTS

| Characteristics (1)                     | Condition               | Sym   | Min         | Тур   | Max  | Unit   |

|-----------------------------------------|-------------------------|-------|-------------|-------|------|--------|

| Input slow clock frequency              |                         |       |             | 32768 |      | Hz     |

| Input slow clock accuracy               | WLAN, BT                |       |             |       | ±150 | ppm    |

| Input transition time Tr/Tf -10% to 90% |                         | Tr/Tf |             |       | 100  | ns     |

| Frequency input duty cycle              |                         |       | 30          | 50    | 70   | %      |

| Input voltage limits                    | Square wave, DC-coupled | VIH   | 0.65 X VDDS |       | VDDS | Vpeak  |

| VIL                                     | 0                       |       | 0.35X VDDS  |       |      |        |

| Input impedence                         |                         |       | 1           |       |      | MW     |

| Input capacitance                       |                         |       |             |       | 5    | рF     |

| Rise and fall time                      |                         |       |             |       | 100  | ns     |

| Phase noise                             | 1 kHz                   |       |             | -125  |      | dBc/Hz |

| 1) Slow clock is a fail safe input      |                         |       |             |       |      |        |

The information in this document is subject to change without notice. Confirm the data is current by downloading the latest revision from www.lsr.com.

Downloaded from Elcodis.com electronic components distributor

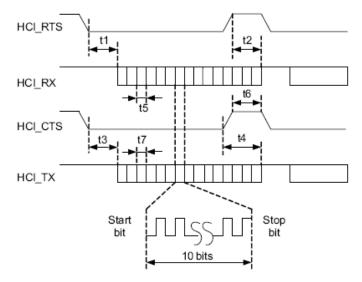

# **BT HCI UART**

#### Figure 7-1. UART TIming

| Symbol | Characteristics         | Condition                 | Min   | Тур         | Max                 | Unit                                   |

|--------|-------------------------|---------------------------|-------|-------------|---------------------|----------------------------------------|

|        | Baud rate               | Most rates <sup>(1)</sup> | 37.5  |             | 4000                | kbps                                   |

| t5, t7 | Baud rate accuracy      | Receive/Transmit          |       |             | -2.5 to<br>1.5      | %                                      |

| t3     | CTS low to TX_DATA on   |                           | 0     | 2           |                     | μs                                     |

| t4     | CTS high to TX_DATA off | Hardware flow control     |       |             | 1                   | byte                                   |

| t6     | CTS-high pulse width    |                           | 1     |             |                     | bit                                    |

| t1     | RTS low to RX_DATA on   |                           | 0     | 2           |                     | μs                                     |

| t2     | RTS high to RX_DATA off | Interrupt set to 1/4 FIFO |       |             | 16                  | byte                                   |

| tb     | Bit width (Jitter)      |                           | See a | application | note <sup>(1)</sup> | %<br>relative<br>to ideal<br>bit width |

(1) Some exceptions: e.g. for 19.2-MHz max baud rate = 3.84 kbps.

ΤХ

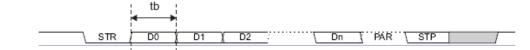

#### Figure 7-2. Data Frame

| Symbol | Description           |

|--------|-----------------------|

| STR    | Start bit             |

| D0Dn   | Data bits (LSB first) |

| PAR    | Parity bit (optional) |

| STP    | Stop bit              |

The information in this document is subject to change without notice. Confirm the data is current by downloading the latest revision from www.lsr.com.

Downloaded from Elcodis.com electronic components distributor

# **SDIO INTERFACE TIMING**

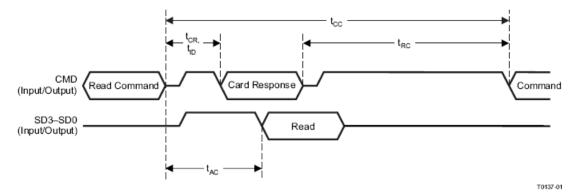

#### Table 7-9. SDIO-Interface Read (see Figure 7-3)

|                 | PARAMETER                                                                 |                                                      | MIN | MAX | UNIT         |

|-----------------|---------------------------------------------------------------------------|------------------------------------------------------|-----|-----|--------------|

| t <sub>CR</sub> | Delay time, assign relative address or data transfer<br>mode              | Read-command CMD valid to card-response<br>CMD valid | 2   | 64  | Clock cycles |

| t <sub>cc</sub> | t <sub>CC</sub> Delay time, CMD command valid to CMD command valid        |                                                      |     |     | Clock cycles |

| t <sub>RC</sub> | t <sub>RC</sub> Delay time, CMD response valid to CMD command valid       |                                                      | 8   |     | Clock cycles |

| t <sub>AC</sub> | t <sub>AC</sub> Access time, CMD command valid to SD3–SD0 read data valid |                                                      |     |     | Clock cycles |

Figure 7-3. SDIO Single Block Read

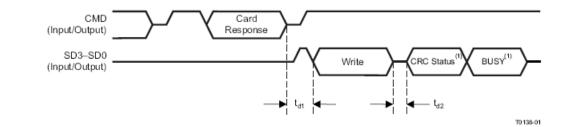

#### Table 7-10. SDIO SD Interface Write (see Figure 7-4)

|                 | PARAMETER                                                         | MIN | MAX | UNIT         |

|-----------------|-------------------------------------------------------------------|-----|-----|--------------|

| t <sub>d1</sub> | Delay time, CMD card response invalid to SD3-SD0 write data valid | 2   |     | Clock cycles |

| t <sub>d2</sub> | Delay time, SD3-SD0 write data invalid end to CRC status valid    | 2   | 2   | Clock cycles |

NOTE: CRC status and busy waveforms are only for data line 0. Data lines 1–3 are N/A. The busy waveform is optional, and may not be present.

#### Figure 7-4. SDIO Single Block Write

The information in this document is subject to change without notice. Confirm the data is current by downloading the latest revision from www.lsr.com.

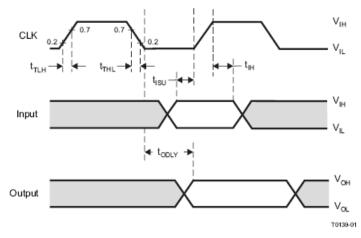

# SDIO CLOCK TIMING

#### Over Recommended Operating Conditions

Note: all timing parameters are indicated for the maximum Host-interface clock frequency.

|                    | PARAMETER                            |                         | MIN | MAX | UNIT |

|--------------------|--------------------------------------|-------------------------|-----|-----|------|

| f <sub>clock</sub> | Clock frequency, CLK                 | $C_L \le 30 \text{ pF}$ | 0   | 26  | MHz  |

| DC                 | Low/high duty cycle                  | $C_L \le 30 \text{ pF}$ | 40  | 60  | %    |

| t <sub>TLH</sub>   | Rise time, CLK                       | $C_L \le 30 \text{ pF}$ |     | 4.3 | ns   |

| t <sub>THL</sub>   | Fall time, CLK                       | $C_L \le 30 \text{ pF}$ |     | 3.5 | ns   |

| t <sub>ISU</sub>   | Setup time, input valid before CLK 1 | $C_L \le 30 \text{ pF}$ | 4   |     | ns   |

| t <sub>IH</sub>    | Hold time, input valid after CLK ↑   | $C_L \le 30 \text{ pF}$ | 5   |     | ns   |

| t <sub>ODLY</sub>  | Delay time, CLK↓ to output valid     | $C_L \le 30 \text{ pF}$ | 2   | 12  | ns   |

The information in this document is subject to change without notice. Confirm the data is current by downloading the latest revision from www.lsr.com.

# **APPLICATION SCHEMATIC**

The information in this document is subject to change without notice. Confirm the data is current by downloading the latest revision from www.lsr.com.

Downloaded from Elcodis.com electronic components distributor

# SOLDERING RECOMMENDATIONS

### **Recommended Reflow Profile**

- Ramp up rate (from Tsoakmax to Tpeak) 3º/sec max

- Minimum Soak Temperature 150°C

- Maximum Soak Temperature 200°C

- Soak Time 60-120 sec

- TLiquidus 217°C

- Time above TL 60-150 sec

- Tpeak 260°C

- Time within 5° of Tpeak 20-30 sec

- Time from 25° to Tpeak 8 min max

- Ramp down rate 6°C/sec max

- Achieve the brightest possible solder fillets with a good shape and low contact angle.

# Lead (Pb) Free Soldering Paste

Use of a "No Clean" Lead (Pb) free Tin/Silver/Copper solder paste is strongly recommended. Melting temperature 216-221°C.

Note: The quality of solder joints on the castellations ('half vias') where they contact the host board should meet the appropriate IPC Specification. See IPC-A-610-D Acceptability of Electronic Assemblies, section 8.2.4 Castellated Terminations."

The soldering temperatures and profile chosen depends on additional factors such as choice of soldering paste, size, thickness and other properties of the host board.

# Cleaning

In general, cleaning the populated modules is strongly discouraged. Residuals under the module cannot be easily removed with any cleaning process.

- Cleaning with water can lead to capillary effects where water is absorbed into the gap between the host board and the module. The combination of soldering flux residuals and encapsulated water could lead to short circuits between neighboring pads. Water could also damage any stickers or labels.

- Cleaning with alcohol or a similar organic solvent will likely flood soldering flux residuals into the RF shield, which is not accessible for post-washing inspection. The solvent could also damage any stickers or labels.

- Ultrasonic cleaning could damage the module permanently.

Consider using a "no clean" soldering paste and thus eliminate the post-soldering cleaning step completely.

# **Optical Inspection**

After soldering the Module to the host board, consider optical inspection to check the following:

- Proper alignment and centering of the module over the pads.

- Proper solder joints on all pads.

- Excessive solder or contacts to neighboring pads, or vias.

# **Repeating Reflow Soldering**

Only a single reflow soldering process is encouraged for host boards.

# **Wave Soldering**

If wave soldering is required on the host boards due to the presence of leaded components, only a single wave soldering process on the side opposite the module is encouraged.

# Hand Soldering

Hand soldering is possible. Use a soldering iron temperature setting equivalent to 350°C, follow IPC recommendations/reference document IPC-7711.

### Rework

The TiWi module can be unsoldered from the host board. Use of a hot air rework tool and hot plate for pre-heating from underneath is recommended. Avoid overheating.

Never attempt a rework on the module itself, e.g. replacing individual components. Such actions will terminate warranty coverage.

# **Additional Grounding**

Attempts to improve module or system grounding by soldering braids, wires, or cables onto the module RF shield cover is done at the customers own risk. The numerous ground pins at the module perimeter should be sufficient for optimum immunity to external RF interference.

# SHIPPING, HANDLING, AND STORAGE

# Shipping

Bulk orders of the TiWi modules are delivered in trays of TBD.

### Handling

The TiWi modules are designed and packaged to be processed in an automated assembly line.

Warning! The TiWi modules contain a highly sensitive electronic circuitry. Handling without proper ESD protection may destroy or damage the module permanently.

Warning! According to JEDEC ISP, the TiWi modules are moisture sensitive devices. Appropriate handling instructions and precautions are summarized in Section 2.1. Read carefully to prevent permanent damage due to moisture intake.

### Moisture Sensitivity Level (MSL)

MSL 3, per J-STD-033

### Storage

Storage/shelf life in sealed bags is 12 months at <40°C and <90% relative humidity.

# AGENCY CERTIFICATIONS

FCC ID: TBD, 15.247.

IC ID: TBD, RSS 210

ETSI: The European Telecommunications Standards Institute. It produces the radio and communication standards for Europe. Our testing is to the ETSI standard EN 300 328, which is the portion of the relevant directives needed for a radio to obtain a CE mark.

See the User's Guide for detailed information regarding agency approvals.

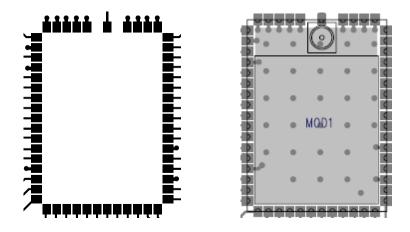

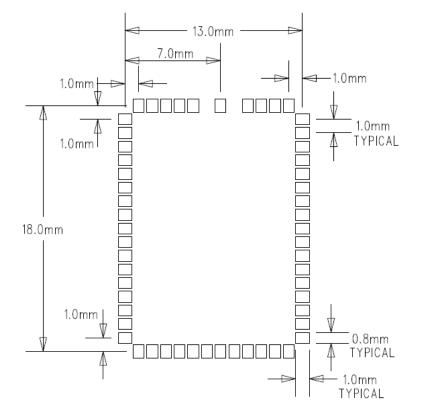

# **MECHANICAL DATA**

This footprint may not be suitable for new designs. Please see Footprint Migration Document (LSR # 330-0043) on the TiWi page at <u>www.lsr.com/tiwi</u> for more information.

Figure 4: Module Mechanical Dimensions (Maximum Module Height = 1.9 mm)

Figure 5: Soldering Footprint for Host Board and Module Placement

The information in this document is subject to change without notice. Confirm the data is current by downloading the latest revision from www.lsr.com.

Downloaded from Elcodis.com electronic components distributor

Figure 6: Host Board Pad Array Placement Dimensioning.

The information in this document is subject to change without notice. Confirm the data is current by downloading the latest revision from www.lsr.com.

# **DEVICE MARKINGS**

# **Rev 0 Devices**

| WL1271 Silicon Rev | Front End |

|--------------------|-----------|

| 2.1                | TQM679002 |

Where rr = revision

XXXXXX = incremental serial number

# **MODULE REVISION HISTORY**

**Rev A**

• Initial production release.

The information in this document is subject to change without notice. Confirm the data is current by downloading the latest revision from www.lsr.com.

### **CONTACTING LS RESEARCH**

| Headquarters      | LS Research, LLC<br>W66 N220 Commerce Court<br>Cedarburg, WI 53012-2636<br>USA<br>Tel: 1(262) 375-4400<br>Fax: 1(262) 375-4248 |

|-------------------|--------------------------------------------------------------------------------------------------------------------------------|

| Website           | www.lsr.com                                                                                                                    |

| Technical Support | support@lsr.com                                                                                                                |

| Sales Contact     | sales@lsr.com                                                                                                                  |

The information in this document is provided in connection with LS Research (hereafter referred to as "LSR") products. No license, express or implied, by estoppel or otherwise, to any intellectual property right is granted by this document or in connection with the sale of LSR products. EXCEPT AS SET FORTH IN LSR'S TERMS AND CONDITIONS OF SALE LOCATED ON LSR'S WEB SITE, LSR ASSUMES NO LIABILITY WHATSOEVER AND DISCLAIMS ANY EXPRESS, IMPLIED OR STATUTORY WARRANTY RELATING TO ITS PRODUCTS INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTY OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT. IN NO EVENT SHALL LSR BE LIABLE FOR ANY DIRECT, INDIRECT, CONSEQUENTIAL, PUNITIVE, SPECIAL OR INCIDENTAL DAMAGES (INCLUDING, WITHOUT LIMITATION, DAMAGES FOR LOSS OF PROFITS, BUSINESS INTERRUPTION, OR LOSS OF INFORMATION) ARISING OUT OF THE USE OR INABILITY TO USE THIS DOCUMENT, EVEN IF LSR HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES. LSR makes no representations or warranties with respect to the accuracy or completeness of the contents of this document and reserves the right to make changes to specifications and product descriptions at any time without notice. LSR does not make any commitment to update the information contained herein. Unless specifically provided otherwise, LSR products are not suitable for, and shall not be used in, automotive applications. LSR's products are not intended, authorized, or warranted for use as components in applications intended to support or sustain life.

The information in this document is subject to change without notice. Confirm the data is current by downloading the latest revision from www.lsr.com.

Downloaded from Elcodis.com electronic components distributor