# High Voltage Ring Generator IC

#### **Features**

- 220V maximum operating voltage

- Integrated high voltage transistors

- ▶ Up to 70V<sub>RMS</sub> ring signal

- Pulse by pulse output over current protection

- ▶ 5 REN output capability

- External MOSFETs enhance output rating to 20 REN

#### Applications

- Microcontroller or microprocessor controlled high voltage ring generator

- Set-top/street box ring generator

- Pair gain ring generator

- Wireless local loops

- Fibre in the loop/to the curb

- Coax cable loop

#### **General Description**

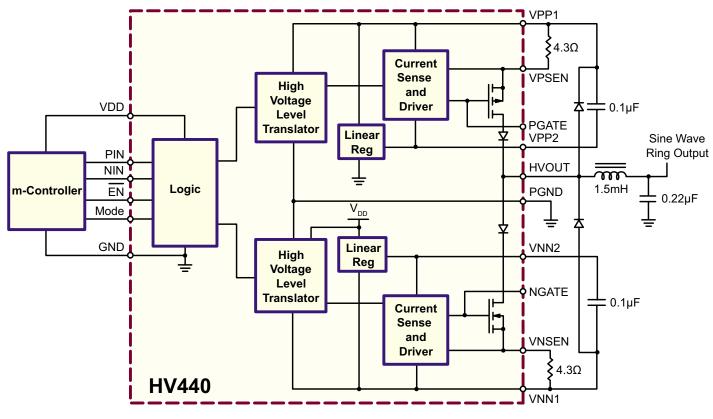

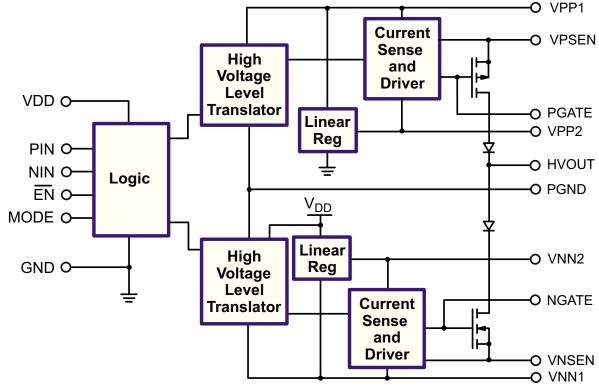

The Supertex HV440 is a monolithic integrated circuit capable of generating up to 70V RMS sine wave output at frequencies of 15 to 60Hz with a load of 5 North American RENs. Its out putrating can be enhanced to 20 North American RENs with the addition of two Supertex MOSFETs: one N-Channel MOSFET, the TN2524N8, and one P-Channel MOSFET, the TP2522N8.

The high voltage output P- and N-Channel transistors are controlled independently by the logic inputs PIN and NIN. Connecting the mode pin to ground will enable the device to be controlled with a single input, NIN. This adds a 200ns deadband on the control logic to avoid cross conduction on the high voltage output. A logic high on NIN will turn the high voltage P-Channel on and the N-Channel off. The high voltage outputs have pulse by pulse overcurrent protection set by two external sense resistors. Nominal PWM logic input frequency is 100KHz.

#### **Typical Application Circuit**

#### **Ordering Information**

| Device                       | 16-Lead SOW<br>10.30x7.50mm body<br>2.65mm height (max)<br>1.27mm pitch |

|------------------------------|-------------------------------------------------------------------------|

| HV440                        | HV440WG-G                                                               |

| -G indicates package is RoHS | compliant ('Green')                                                     |

-G indicates package is RoHS compliant ('Green')

## Absolute Maximum Ratings

| Parameter                                    | Value           |

|----------------------------------------------|-----------------|

| $V_{PP1}$ - $V_{NN1}$ , power supply voltage | +240V           |

| $V_{PP1}$ , positive high supply voltage     | +120V           |

| $V_{PP2}$ , positive gate supply voltage     | +120V           |

| $V_{_{NN1}}$ , negative high voltage         | -170V           |

| $V_{_{NN2}}$ , negative gate voltage         | -170V           |

| $V_{\text{DD}}$ , logic supply voltage       | +7.5V           |

| Storage temperature                          | -65°C to +150°C |

| Power dissipation                            | 800mW           |

Absolute Maximum Ratings are those values beyond which damage to the device may occur. Functional operation under these conditions is not implied. Continuous operation of the device at the absolute rating level may affect device reliability. All voltages are referenced to device ground.

## **Pin Configuration**

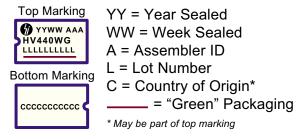

#### **Product Marking**

Package may or may not include the following marks: Si or (1) 16-Lead SOW (WG)

### **Electrical Characteristics** (over operating supply voltage unless otherwise specified. $T_A = 25^{\circ}C$ )

| Sym               | Parameter                          | Min                   | Тур | Max                    | Units | Conditions                                                                                   |  |  |

|-------------------|------------------------------------|-----------------------|-----|------------------------|-------|----------------------------------------------------------------------------------------------|--|--|

| V <sub>PP1</sub>  | High voltage positive supply       | 15                    | -   | 110                    |       |                                                                                              |  |  |

| V <sub>PP2</sub>  | Positive linear regulator output   | V <sub>PP1</sub> -9.9 | -   | V <sub>PP1</sub> -19.1 |       | $T_A = -40^{\circ}C$ to +85°C                                                                |  |  |

| V <sub>NN1</sub>  | High voltage negative supply       | V <sub>PP1</sub> -220 | -   | -110                   | V     |                                                                                              |  |  |

| V <sub>NN2</sub>  | Negative linear regulator output   | V <sub>PP1</sub> +5.6 | -   | V <sub>NN1</sub> +10.5 |       |                                                                                              |  |  |

| V <sub>DD</sub>   | Logic supply                       | 4.5                   | -   | 5.5                    |       |                                                                                              |  |  |

| I <sub>PP1Q</sub> | V <sub>PP1</sub> quiescent current | -                     | 250 | 400                    |       | $P_{1N} = N_{1N} = 0V,$                                                                      |  |  |

| I <sub>NN1Q</sub> | V <sub>NN1</sub> quiescent current | -                     | 250 | 550                    | μA    | $P_{IN} = N_{IN} = 0V,$<br>$T_{A} = -40^{\circ}C \text{ to } +85^{\circ}C$                   |  |  |

|                   | V guiescent current                | -                     | -   | 150                    |       | $P_{IN} = N_{IN} = 0V$ , MODE = 0                                                            |  |  |

| I DDQ             | $V_{_{DD1}}$ quiescent current     | -                     | -   | 60                     | μA    | $P_{IN} = N_{IN} = 0V$ , MODE = 1                                                            |  |  |

| I <sub>PP1</sub>  | V <sub>PP1</sub> operating current | -                     | -   | 1.7                    | mA    | No load, $V_{OUTP}$ and $V_{OUTN}$<br>switching at 100KHz,<br>$T_A = -40^{\circ}$ C to +85°C |  |  |

Supertex inc. • 1235 Bordeaux Drive, Sunnyvale, CA 94089 • Tel: 408-222-8888 • www.supertex.com

#### **Electrical Characteristics** (cont.) (over operating supply voltage unless otherwise specified. $T_A = 25^{\circ}C$ )

| Sym              | Parameter                         | Min | Тур | Мах | Units | Conditions                                                                                   |

|------------------|-----------------------------------|-----|-----|-----|-------|----------------------------------------------------------------------------------------------|

| I <sub>NN1</sub> | $V_{_{NN1}}$ operating current    | -   | -   | 1.9 | mA    | No load, $V_{OUTP}$ and $V_{OUTN}$<br>switching at 100KHz,<br>$T_A = -40^{\circ}$ C to +85°C |

| I <sub>DD</sub>  | V <sub>DD</sub> operating current | -   | -   | 1.0 | mA    |                                                                                              |

| I <sub>IL</sub>  | Mode logic input low current      | -   | 25  | -   | μA    | MODE = 0V                                                                                    |

| V <sub>IL</sub>  | Logic input low voltage           | 0   | -   | 1.0 | V     | V <sub>DD</sub> = 5.0V                                                                       |

| V <sub>IH</sub>  | Logic input high voltage          | 4.0 | -   | 5.0 | V     | V <sub>DD</sub> = 5.0V                                                                       |

#### High Voltage Output

| R <sub>SOURCE</sub> | $V_{out}P$ source resistance                                               | -                      | 60                     | 80                     | Ω    | I <sub>OUT</sub> = 100mA                      |  |

|---------------------|----------------------------------------------------------------------------|------------------------|------------------------|------------------------|------|-----------------------------------------------|--|

| R <sub>SINK</sub>   | $V_{out}P$ sink resistance                                                 | -                      | 60                     | 80                     | Ω    | I <sub>out</sub> = -100mA                     |  |

| ΔR/ΔT               | Change in source/sink resistance over temperature                          | -                      | 0.33                   | -                      | Ω/°C | $T_A = -40^{\circ}C \text{ to } +85^{\circ}C$ |  |

| t <sub>D(ON)</sub>  | HV <sub>out</sub> delay time                                               | -                      | 150                    | -                      | ns   | P <sub>IN</sub> = high to low,<br>Mode = high |  |

| t <sub>RISE</sub>   | $HV_{OUT}$ rise time                                                       | -                      | -                      | 50                     | ns   | $P_{IN}$ = high to low                        |  |

| t <sub>D(OFF)</sub> | HV <sub>out</sub> delay time                                               | -                      | 200                    | -                      | ns   | N <sub>IN</sub> = low to high,<br>Mode = high |  |

| t <sub>FALL</sub>   | HV <sub>ουτ</sub> fall time                                                | -                      | -                      | 50                     | ns   | $N_{IN}$ = low to high                        |  |

| t <sub>DB</sub>     | Logic deadband time                                                        | -                      | -                      | 200                    | ns   | Mode = low                                    |  |

| V                   | HV <sub>out</sub> current source sense                                     | V <sub>PP1</sub> -0.75 | V <sub>PP1</sub> -1.00 | V <sub>PP1</sub> -1.25 | V    | $T_A = -40^{\circ}C$ to +85°C                 |  |

| V <sub>PSEN</sub>   | voltage                                                                    | V <sub>PP1</sub> -0.67 | -                      | V <sub>PP1</sub> -1.31 | v    |                                               |  |

| V                   | HV <sub>out</sub> current sink sense voltage                               | V <sub>NN1</sub> +0.75 | V <sub>NN1</sub> +1.00 | V <sub>NN1</sub> +1.25 | V    | $T_A = -40^{\circ}C \text{ to } +85^{\circ}C$ |  |

| V <sub>NSEN</sub>   |                                                                            | V <sub>NN1</sub> +0.65 | -                      | V <sub>NN1</sub> +1.33 | v    |                                               |  |

| t <sub>shortp</sub> | HV <sub>out</sub> off time when current source sense is activated          | -                      | -                      | 100                    | ns   |                                               |  |

| t <sub>shortn</sub> | $\mathrm{HV}_{\mathrm{OUT}}$ off time when current sink sense is activated | -                      | -                      | 100                    | ns   |                                               |  |

| t <sub>whout</sub>  | Minimum pulse width for $HV_{OUT}$ at $V_{PP1}$                            | -                      | -                      | 500                    | ns   | $T_A = -40^{\circ}C$ to $+85^{\circ}C$        |  |

| t <sub>wLOUT</sub>  | Minimum pulse width for $HV_{OUT}$ at $V_{NN1}$                            | -                      | -                      | 500                    | ns   | $T_A = -40^{\circ}C$ to $+85^{\circ}C$        |  |

|                     |                                                                            |                        |                        |                        |      |                                               |  |

#### **Truth Table**

| N <sub>IN</sub> | P <sub>IN</sub> | Mode | EN | HV <sub>out</sub> |

|-----------------|-----------------|------|----|-------------------|

| L               | L               | Н    | L  | VPP1              |

| L               | Н               | Н    | L  | High Z            |

| Н               | L*              | Н    | L  | _                 |

| Н               | Н               | Н    | L  | VNN1              |

| L               | Х               | L    | L  | VNN1              |

| Н               | Х               | L    | L  | VPP1              |

| X               | Х               | Х    | Н  | High Z            |

\* This state will short V  $_{_{PP1}}$  to V  $_{_{NN1}}$  and should therefore be avoided.

### **Block Diagram**

## **Pin Description**

| Pin | Name  | Description                                                                                                                                                                                  |

|-----|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | VPP1  | Positive high voltage supply.                                                                                                                                                                |

| 2   | PGND  | High voltage power ground.                                                                                                                                                                   |

| 3   | GND   | Low voltage ground.                                                                                                                                                                          |

| 4   | MODE  | Logic mode input. Logic low activates 200nsec deadband. When mode is low, NIN turns on and off the high voltage N- and P-Channels. Pin is not used and should be connected to VDD or ground. |

| 5   | PIN   | Logic control input. When mode is high, logic input high turns off output high voltage P-Channel.                                                                                            |

| 6   | NIN   | Logic control input. When mode is high, logic input high turns on output high voltage N-Channel.                                                                                             |

| 7   | EN    | Active low enable input.                                                                                                                                                                     |

| 8   | VDD   | Logic supply voltage.                                                                                                                                                                        |

| 9   | VNN1  | Negative high voltage supply.                                                                                                                                                                |

| 10  | VNN2  | Negative gate voltage supply. Generated by an internal linear regulator. A $0.1\mu F$ capacitor should be connected between VNN2 and VNN1.                                                   |

| 11  | NGATE | Gate drive for external N-channel MOSFET.                                                                                                                                                    |

| 12  | VNSEN | Pulse by pulse over current sensing for internal N-Channel MOSFET.                                                                                                                           |

| 13  | HVOUT | High voltage output. Voltage swings from VPP1 to VNN1.                                                                                                                                       |

| 14  | VPSEN | Pulse by pulse over current sensing for internal P-Channel MOSFET.                                                                                                                           |

| 15  | PGATE | Gate drive for external P-channel MOSFET.                                                                                                                                                    |

| 16  | VPP2  | Positive gate voltage supply. Generated by an internal linear regulator. A $0.1\mu$ F capacitor should be connected between VPP2 and VPP1.                                                   |

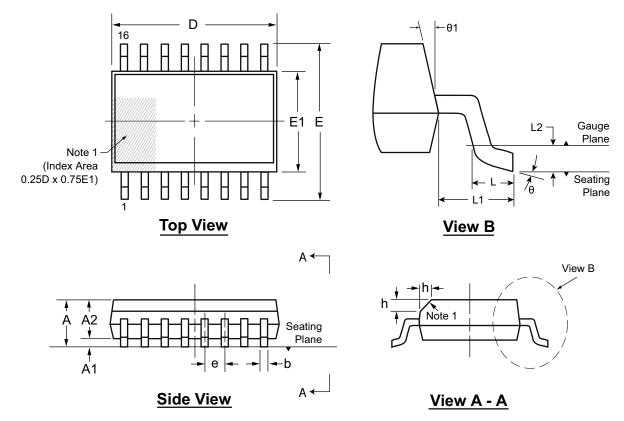

### 16-Lead SOW (Wide Body) Package Outline (WG) 10.30x7.50mm body, 2.65mm height (max), 1.27mm pitch

Note:

1. A Pin 1 identifier must be located in the index area indicated. The Pin 1 identifier can be: a molded mark/identifier; an embedded metal marker; or a printed indicator.

| Symbo             | bl  | Α     | A1   | A2    | b    | D      | E      | E1    | е    | h    | L    | L1                   | L2  | θ          | θ1              |    |

|-------------------|-----|-------|------|-------|------|--------|--------|-------|------|------|------|----------------------|-----|------------|-----------------|----|

| Dimension<br>(mm) | MIN | 2.15* | 0.10 | 2.05  | 0.31 | 10.10* | 9.97*  | 7.40* | 1.27 |      | 0.25 | 0.40                 |     |            | <b>0</b> 0      | 5° |

|                   | NOM | -     | -    | -     | -    | 10.30  | 10.30  | 7.50  |      | -    | -    | 1.40 0.25<br>REF BSC | -   | -          |                 |    |

| ()                | MAX | 2.65  | 0.30 | 2.55* | 0.51 | 10.50* | 10.63* | 7.60* |      | 0.75 | 1.27 |                      | 200 | <b>8</b> 0 | 15 <sup>0</sup> |    |

JEDEC Registration MS-013, Variation AA, Issue E, Sep. 2005.

\* This dimension is not specified in the JEDEC drawing.

Drawings are not to scale.

Supertex Doc. #: DSPD-16SOWWG, Version E041309.

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information go to <u>http://www.supertex.com/packaging.html</u>.)

**Supertex inc.** does not recommend the use of its products in life support applications, and will not knowingly sell them for use in such applications unless it receives an adequate "product liability indemnification insurance agreement." **Supertex inc.** does not assume responsibility for use of devices described, and limits its liability to the replacement of the devices determined defective due to workmanship. No responsibility is assumed for possible omissions and inaccuracies. Circuitry and specifications are subject to change without notice. For the latest product specifications refer to the **Supertex inc.** (website: http://www.supertex.com)

©2010 Supertex inc. All rights reserved. Unauthorized use or reproduction is prohibited.