# CY4625

# MoBL-USB<sup>™</sup> Bridge Firmware Guide

Document # 001-15686 Version \*A

Cypress Semiconductor 198 Champion Court San Jose, CA 95134-1709 Phone (USA): 800.858.1810 Phone (Intnl): 408.943.2600 http://www.cypress.com

#### Copyrights

© Cypress Semiconductor Corporation, 2007. The information contained herein is subject to change without notice. Cypress Semiconductor Corporation assumes no responsibility for the use of any circuitry other than circuitry embodied in a Cypress product. Nor does it convey or imply any license under patent or other rights. Cypress products are not warranted nor intended to be used for medical, life support, life saving, critical control or safety applications, unless pursuant to an express written agreement with Cypress. Furthermore, Cypress does not authorize its products for use as critical components in life-support systems where a malfunction or failure may reasonably be expected to result in significant injury to the user. The inclusion of Cypress products in life-support systems application implies that the manufacturer assumes all risk of such use and in doing so indemnifies Cypress against all charges.

Cypress, the Cypress Logo, MoBL-USB<sup>™</sup> and EZ-USB FX2LP<sup>™</sup> are trademarks or registered trademarks of Cypress Semiconductor. I<sup>2</sup>C is a registered trademark of Philips. Windows is a registered trademark of Microsoft Corporation. All product and company names mentioned in this document are the trademarks of their respective holders.

Any Source Code (software and/or firmware) is owned by Cypress Semiconductor Corporation (Cypress) and is protected by and subject to worldwide patent protection (United States and foreign), United States copyright laws and international treaty provisions. Cypress hereby grants to licensee a personal, non-exclusive, non-transferable license to copy, use, modify, create derivative works of, and compile the Cypress Source Code and derivative works for the sole purpose of creating custom software and or firmware in support of licensee product to be used only in conjunction with a Cypress integrated circuit as specified in the applicable agreement. Any reproduction, modification, translation, compilation, or representation of this Source Code except as specified above is prohibited without the express written permission of Cypress.

#### Disclaimer

CYPRESS MAKES NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARD TO THIS MATERIAL, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PAR-TICULAR PURPOSE. Cypress reserves the right to make changes without further notice to the materials described herein. Cypress does not assume any liability arising out of the application or use of any product or circuit described herein. Cypress does not authorize its products for use as critical components in life-support systems where a malfunction or failure may reasonably be expected to result in significant injury to the user. The inclusion of Cypress' product in a life-support systems application implies that the manufacturer assumes all risk of such use and in doing so indemnifies Cypress against all charges.

Use may be limited by and subject to the applicable Cypress software license agreement.

# Contents

| 1. Overvi | ew                                                             | 7  |

|-----------|----------------------------------------------------------------|----|

| 1.1       | Purpose                                                        | 7  |

| 1.2       | Chapter Overviews                                              | 7  |

| 1.3       | Support                                                        | 7  |

|           | 1.3.1 Acronyms                                                 | 8  |

| 1.4       | Document History                                               | 8  |

| 1.5       | Document Conventions                                           | 8  |

| 2. Introd | uction                                                         | 9  |

| 2.1       | Introducing the MoBL-USB™ Bridge Firmware                      | 9  |

|           | 2.1.1 Features                                                 |    |

| 2.2       | Applications                                                   |    |

|           | 2.2.1 System Diagram                                           |    |

| 2.3       | Ordering Information                                           |    |

| 3. Functi | onal Overview                                                  | 15 |

| 3.1       | USB Signaling Speed                                            |    |

| 3.2       | Boot Method                                                    |    |

| 3.3       | Resets and Wakeup                                              |    |

| 0.0       | 3.3.1 Reset                                                    |    |

|           | 3.3.2 USB Reset                                                |    |

|           | 3.3.3 Wakeup                                                   |    |

| 3.4       | Endpoint RAM Organization                                      |    |

| 3.5       | External Interface                                             |    |

| 0.0       | 3.5.1 Control Signals                                          |    |

|           | 3.5.1.1 FIFOADDR Lines                                         |    |

|           | 3.5.1.2 Read: SLOE and SLRD                                    |    |

|           | 3.5.1.3 Write: SLWR                                            |    |

|           | 3.5.1.4 PKTEND                                                 |    |

|           | 3.5.2 IFCLK                                                    |    |

|           | 3.5.3 FIFO Access                                              |    |

|           | 3.5.4 FIFO Flag Pins Configuration                             |    |

|           | 3.5.5 Default FIFO Programmable Flag Setup                     |    |

|           | 3.5.6 FIFO Programmable Flag Setup                             |    |

|           | 3.5.7 Command Protocol                                         |    |

|           | 3.5.7.1 Write Register Example                                 |    |

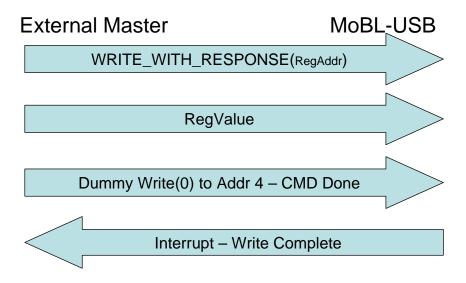

|           | 3.5.7.2 Write Register with Response Example                   |    |

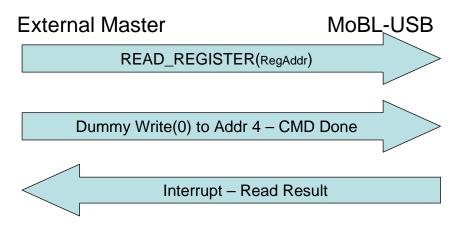

|           | 3.5.7.3 Read Register Example                                  |    |

|           | 3.5.8 Enabling OUT Transfers on EP2 and EP6                    |    |

|           | <ul> <li>3.5.6 Enabling OUT Transfers on EP2 and EP6</li></ul> |    |

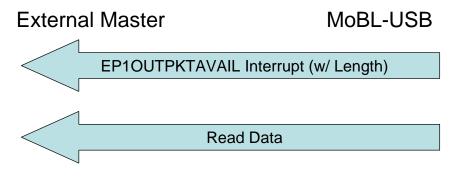

|           | 3.5.10 Getting EP1OUT Data                                     | 22 |

|          |                                                                                                                      | 3.5.11 Getting EP2OUT Data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                |

|----------|----------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          |                                                                                                                      | 3.5.12 Getting EP4OUT Data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                |

|          |                                                                                                                      | 3.5.13 Putting EP1IN Data<br>3.5.13.1 EP1IN and EP8IN Data Commit Bit Settings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                |

|          |                                                                                                                      | 3.5.14 Putting EP8 IN Data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                |

|          |                                                                                                                      | 3.5.15 Putting EP6IN Data - Full Packet                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                |

|          |                                                                                                                      | 3.5.16 Putting EP6IN Data - Full Packet                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                |

|          |                                                                                                                      | 3.5.17 Bridge Firmware Images and Standby Sequences                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                |

|          |                                                                                                                      | 3.5.17 Bloger Innware images and Standby Sequences                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                |

|          |                                                                                                                      | 3.5.17.2 Host Initiated Suspend                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                |

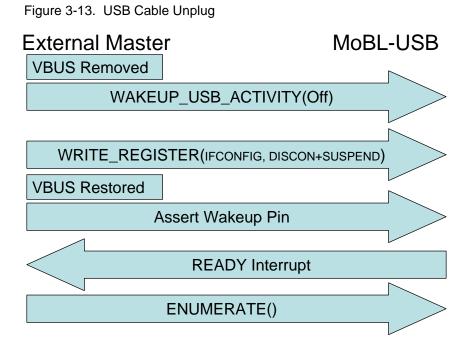

|          |                                                                                                                      | 3.5.17.3 Cable Unplug Initiated Suspend                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                |

|          |                                                                                                                      | 3.5.18 Command List                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                |

|          |                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                |

| 4.       | Enume                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 31                                                                                                                                                             |

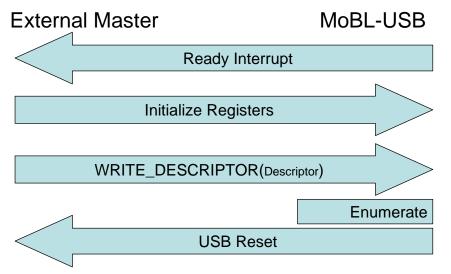

|          | 4.1                                                                                                                  | Manual Enumeration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                |

|          | 4.2                                                                                                                  | Default Enumeration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                |

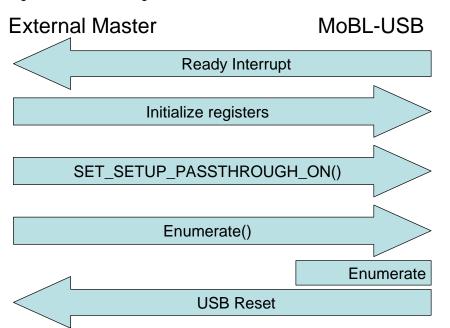

|          | 4.3                                                                                                                  | External Master Passthrough Enumeration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                |

|          | 4.4                                                                                                                  | Interrupt System                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                |

|          |                                                                                                                      | 4.4.1 Architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 34                                                                                                                                                             |

|          |                                                                                                                      | 4.4.2 INTENABLE Register Bit Definition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                |

|          |                                                                                                                      | 4.4.3 Standard Interrupt Bit Positions and Extended Interrupts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 35                                                                                                                                                             |

|          |                                                                                                                      | 4.4.3.1 INTMODE - Interrupt Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                |

|          |                                                                                                                      | 4.4.3.2 RDREGRSP - Read Register Response                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 35                                                                                                                                                             |

|          |                                                                                                                      | 4.4.3.3 INTCODE[3:0] - Interrupt Code                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                |

|          |                                                                                                                      | 4.4.3.4 PL[9:0] - Packet Length for OUT Packets                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                |

|          |                                                                                                                      | 4.4.3.5 EP[3:0] - Endpoint Number for INNF, OUTNE, and INSH                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ORTPK-                                                                                                                                                         |

|          |                                                                                                                      | TACK36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                |

| 5.       | Endpoi                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 37                                                                                                                                                             |

| 5.       | Endpoi<br>5.1                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                |

|          | 5.1                                                                                                                  | nt 0<br>SETUP Commands                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 37                                                                                                                                                             |

| 5.<br>6. | 5.1                                                                                                                  | nt 0<br>SETUP Commands                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 37<br><b>39</b>                                                                                                                                                |

|          | 5.1<br><b>Registe</b><br>6.1                                                                                         | nt 0<br>SETUP Commands<br>er Summary<br>Register Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 37<br><b>39</b><br>39                                                                                                                                          |

|          | 5.1<br><b>Registe</b><br>6.1<br>6.2                                                                                  | nt 0<br>SETUP Commands<br>er Summary<br>Register Summary<br>IFCONFIG Register 0x01                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 37<br><b>39</b><br>39<br>40                                                                                                                                    |

|          | 5.1<br><b>Registe</b><br>6.1<br>6.2<br>6.3                                                                           | nt 0<br>SETUP Commands<br>er Summary<br>Register Summary<br>IFCONFIG Register 0x01<br>FLAGSAB/FLAGSCD Registers 0x02/0x03                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 37<br><b>39</b><br>39<br>40<br>41                                                                                                                              |

|          | 5.1<br><b>Registe</b><br>6.1<br>6.2<br>6.3<br>6.4                                                                    | nt 0<br>SETUP Commands<br>er Summary<br>Register Summary<br>IFCONFIG Register 0x01<br>FLAGSAB/FLAGSCD Registers 0x02/0x03<br>POLAR Register 0x04                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 37<br><b>39</b><br>40<br>41<br>43                                                                                                                              |

|          | 5.1<br><b>Registe</b><br>6.1<br>6.2<br>6.3<br>6.4<br>6.5                                                             | nt 0<br>SETUP Commands<br>er Summary<br>Register Summary<br>IFCONFIG Register 0x01<br>FLAGSAB/FLAGSCD Registers 0x02/0x03<br>POLAR Register 0x04<br>REVID Register 0x05                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 37<br>39<br>39<br>40<br>41<br>43<br>44                                                                                                                         |

|          | 5.1<br><b>Registe</b><br>6.1<br>6.2<br>6.3<br>6.4<br>6.5<br>6.6                                                      | nt 0<br>SETUP Commands<br>er Summary<br>Register Summary<br>IFCONFIG Register 0x01<br>FLAGSAB/FLAGSCD Registers 0x02/0x03<br>POLAR Register 0x04<br>REVID Register 0x05<br>EPxCFG Register 0x06–0x09                                                                                                                                                                                                                                                                                                                                                                                                                        | 37<br>39<br>39<br>40<br>41<br>43<br>43<br>44<br>44                                                                                                             |

|          | 5.1<br><b>Registe</b><br>6.1<br>6.2<br>6.3<br>6.4<br>6.5<br>6.6<br>6.7                                               | nt 0<br>SETUP Commands<br>er Summary<br>Register Summary<br>IFCONFIG Register 0x01<br>FLAGSAB/FLAGSCD Registers 0x02/0x03<br>POLAR Register 0x04<br>REVID Register 0x04<br>EPxCFG Register 0x06–0x09<br>EPxPKTLENH/L Registers 0x0A–0x0F                                                                                                                                                                                                                                                                                                                                                                                    | 37<br>39<br>39<br>40<br>41<br>43<br>43<br>44<br>44<br>44                                                                                                       |

|          | 5.1<br><b>Registe</b><br>6.1<br>6.2<br>6.3<br>6.4<br>6.5<br>6.6                                                      | nt 0<br>SETUP Commands<br>er Summary<br>Register Summary<br>IFCONFIG Register 0x01<br>FLAGSAB/FLAGSCD Registers 0x02/0x03<br>POLAR Register 0x04<br>REVID Register 0x04<br>REVID Register 0x05<br>EPxCFG Register 0x06–0x09<br>EPxPKTLENH/L Registers 0x0A–0x0F<br>EPxPFH/L Registers 0x12–0x17                                                                                                                                                                                                                                                                                                                             | 37<br>39<br>40<br>41<br>43<br>44<br>44<br>44<br>45<br>46                                                                                                       |

|          | 5.1<br><b>Registe</b><br>6.1<br>6.2<br>6.3<br>6.4<br>6.5<br>6.6<br>6.7                                               | nt 0<br>SETUP Commands<br>er Summary<br>Register Summary<br>IFCONFIG Register 0x01<br>FLAGSAB/FLAGSCD Registers 0x02/0x03<br>POLAR Register 0x04<br>REVID Register 0x04<br>EPxCFG Register 0x05<br>EPxCFG Register 0x06–0x09<br>EPxPKTLENH/L Registers 0x0A–0x0F<br>EPxPFH/L Registers 0x12–0x17<br>6.8.1 DECIS: EPxPFH.7                                                                                                                                                                                                                                                                                                   | 37<br>39<br>39<br>40<br>41<br>43<br>43<br>44<br>44<br>44<br>44<br>44<br>45<br>46<br>47                                                                         |

|          | 5.1<br><b>Registe</b><br>6.1<br>6.2<br>6.3<br>6.4<br>6.5<br>6.6<br>6.7                                               | nt 0<br>SETUP Commands<br>er Summary<br>Register Summary<br>IFCONFIG Register 0x01<br>FLAGSAB/FLAGSCD Registers 0x02/0x03<br>POLAR Register 0x04<br>REVID Register 0x04<br>EPxCFG Register 0x05<br>EPxCFG Register 0x06–0x09<br>EPxPKTLENH/L Registers 0x0A–0x0F<br>EPxPFH/L Registers 0x12–0x17<br>6.8.1 DECIS: EPxPFH.7<br>6.8.2 PKSTAT: EPxPFH.6                                                                                                                                                                                                                                                                         | 37<br>39<br>39<br>40<br>41<br>43<br>43<br>44<br>44<br>44<br>45<br>46<br>47<br>47                                                                               |

|          | 5.1<br><b>Registe</b><br>6.1<br>6.2<br>6.3<br>6.4<br>6.5<br>6.6<br>6.7                                               | nt 0<br>SETUP Commands<br>er Summary<br>Register Summary<br>IFCONFIG Register 0x01<br>FLAGSAB/FLAGSCD Registers 0x02/0x03<br>POLAR Register 0x04<br>REVID Register 0x04<br>REVID Register 0x05<br>EPxCFG Register 0x06–0x09<br>EPxPKTLENH/L Registers 0x0A–0x0F<br>EPxPFH/L Registers 0x12–0x17<br>6.8.1 DECIS: EPxPFH.7<br>6.8.2 PKSTAT: EPxPFH.6<br>6.8.3 IN: PKTS(2:0)/OUT: PFC[12:10]: EPxPFH[5:3]                                                                                                                                                                                                                      | 37<br>39<br>39<br>40<br>41<br>41<br>43<br>44<br>44<br>44<br>45<br>46<br>47<br>47<br>47                                                                         |

|          | 5.1<br><b>Registe</b><br>6.1<br>6.2<br>6.3<br>6.4<br>6.5<br>6.6<br>6.7                                               | nt 0<br>SETUP Commands<br>Register Summary<br>IFCONFIG Register 0x01<br>FLAGSAB/FLAGSCD Registers 0x02/0x03<br>POLAR Register 0x04<br>REVID Register 0x04<br>REVID Register 0x05<br>EPxCFG Register 0x06–0x09<br>EPxPKTLENH/L Registers 0x0A–0x0F<br>EPxPFH/L Registers 0x12–0x17<br>6.8.1 DECIS: EPxPFH.7<br>6.8.2 PKSTAT: EPxPFH.6<br>6.8.3 IN: PKTS(2:0)/OUT: PFC[12:10]: EPxPFH[5:3]<br>6.8.3.1 IN Endpoints                                                                                                                                                                                                            | 37<br>39<br>40<br>40<br>41<br>43<br>43<br>44<br>44<br>45<br>46<br>47<br>47<br>47<br>47                                                                         |

|          | 5.1<br><b>Registe</b><br>6.1<br>6.2<br>6.3<br>6.4<br>6.5<br>6.6<br>6.7<br>6.8                                        | nt 0<br>SETUP Commands<br>Fr Summary<br>IFCONFIG Register 0x01<br>FLAGSAB/FLAGSCD Registers 0x02/0x03<br>POLAR Register 0x04<br>REVID Register 0x05<br>EPxCFG Register 0x06–0x09<br>EPxPKTLENH/L Registers 0x0A–0x0F<br>EPxPFH/L Registers 0x12–0x17<br>6.8.1 DECIS: EPxPFH.7<br>6.8.2 PKSTAT: EPxPFH.6<br>6.8.3 IN: PKTS(2:0)/OUT: PFC[12:10]: EPxPFH[5:3]<br>6.8.3.1 IN Endpoints<br>6.8.3.2 OUT Endpoints                                                                                                                                                                                                                | 37<br>39<br>40<br>41<br>43<br>43<br>44<br>44<br>45<br>46<br>47<br>47<br>47<br>47<br>47<br>47                                                                   |

|          | 5.1<br><b>Registe</b><br>6.1<br>6.2<br>6.3<br>6.4<br>6.5<br>6.6<br>6.7<br>6.8                                        | nt 0<br>SETUP Commands<br>Fr Summary<br>Register Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 37<br>39<br>40<br>41<br>43<br>43<br>44<br>44<br>44<br>45<br>46<br>47<br>47<br>47<br>47<br>47<br>47<br>48<br>48                                                 |

|          | 5.1<br><b>Registe</b><br>6.1<br>6.2<br>6.3<br>6.4<br>6.5<br>6.6<br>6.7<br>6.8<br>6.9<br>6.10                         | nt 0<br>SETUP Commands<br>Pr Summary<br>Register Summary<br>IFCONFIG Register 0x01<br>FLAGSAB/FLAGSCD Registers 0x02/0x03<br>POLAR Register 0x04<br>REVID Register 0x05<br>EPxCFG Register 0x06–0x09<br>EPxPKTLENH/L Registers 0x0A–0x0F<br>EPxPFH/L Registers 0x12–0x17<br>6.8.1 DECIS: EPxPFH.7<br>6.8.2 PKSTAT: EPxPFH.6<br>6.8.3 IN: PKTS(2:0)/OUT: PFC[12:10]: EPxPFH[5:3]<br>6.8.3.1 IN Endpoints<br>6.8.3.2 OUT Endpoints<br>EPxFLAGS Registers 0x1E–0x1F<br>INPKTEND/FLUSH Register 0x20                                                                                                                            | 37<br>39<br>40<br>41<br>43<br>43<br>44<br>44<br>44<br>45<br>46<br>47<br>47<br>47<br>47<br>47<br>47<br>47<br>48<br>48<br>48                                     |

|          | 5.1<br><b>Registe</b><br>6.1<br>6.2<br>6.3<br>6.4<br>6.5<br>6.6<br>6.7<br>6.8<br>6.9<br>6.10<br>6.11                 | nt 0<br>SETUP Commands<br>er Summary<br>Register Summary<br>IFCONFIG Register 0x01<br>FLAGSAB/FLAGSCD Registers 0x02/0x03<br>POLAR Register 0x04<br>REVID Register 0x05<br>EPxCFG Register 0x06–0x09<br>EPxPKTLENH/L Registers 0x0A–0x0F<br>EPxPFH/L Registers 0x12–0x17<br>6.8.1 DECIS: EPxPFH.7<br>6.8.2 PKSTAT: EPxPFH.6<br>6.8.3 IN: PKTS(2:0)/OUT: PFC[12:10]: EPxPFH[5:3]<br>6.8.3.2 OUT Endpoints<br>6.8.3.2 OUT Endpoints<br>EPxFLAGS Registers 0x1E–0x1F<br>INPKTEND/FLUSH Register 0x20<br>USBFRAMEH/L Registers 0x2A, 0x2B                                                                                       | 37<br>39<br>39<br>40<br>41<br>43<br>43<br>44<br>44<br>45<br>46<br>47<br>47<br>47<br>47<br>47<br>47<br>47<br>47<br>48<br>48<br>48<br>48<br>48<br>49             |

|          | 5.1<br><b>Registe</b><br>6.1<br>6.2<br>6.3<br>6.4<br>6.5<br>6.6<br>6.7<br>6.8<br>6.9<br>6.10<br>6.11<br>6.12         | nt 0<br>SETUP Commands<br>er Summary<br>IFCONFIG Register 0x01<br>FLAGSAB/FLAGSCD Registers 0x02/0x03<br>POLAR Register 0x04<br>REVID Register 0x05<br>EPxCFG Register 0x06–0x09<br>EPxPKTLENH/L Registers 0x0A–0x0F<br>EPxPFH/L Registers 0x12–0x17<br>6.8.1 DECIS: EPxPFH.7<br>6.8.2 PKSTAT: EPxPFH.6<br>6.8.3 IN: PKTS(2:0)/OUT: PFC[12:10]: EPxPFH[5:3]<br>6.8.3.1 IN Endpoints<br>6.8.3.2 OUT Endpoints<br>6.8.3.2 OUT Endpoints<br>EPxFLAGS Registers 0x1E–0x1F<br>INPKTEND/FLUSH Register 0x20<br>USBFRAMEH/L Registers 0x2A, 0x2B<br>MICROFRAME Registers 0x2C                                                      | 37<br>39<br>39<br>40<br>41<br>43<br>43<br>44<br>44<br>45<br>45<br>46<br>47<br>47<br>47<br>47<br>47<br>47<br>47<br>47<br>47<br>47<br>49<br>49                   |

|          | 5.1<br><b>Registe</b><br>6.1<br>6.2<br>6.3<br>6.4<br>6.5<br>6.6<br>6.7<br>6.8<br>6.9<br>6.10<br>6.11<br>6.12<br>6.13 | nt 0<br>SETUP Commands<br>er Summary<br>IFCONFIG Register 0x01<br>FLAGSAB/FLAGSCD Registers 0x02/0x03<br>POLAR Register 0x04<br>REVID Register 0x05<br>EPxCFG Register 0x06–0x09<br>EPxPKTLENH/L Registers 0x0A–0x0F<br>EPxPFH/L Registers 0x12–0x17<br>6.8.1 DECIS: EPxPFH.7<br>6.8.2 PKSTAT: EPxPFH.6<br>6.8.3 IN: PKTS(2:0)/OUT: PFC[12:10]: EPxPFH[5:3]<br>6.8.3.1 IN Endpoints<br>6.8.3.2 OUT Endpoints<br>6.8.3.2 OUT Endpoints<br>EPxFLAGS Registers 0x1E–0x1F<br>INPKTEND/FLUSH Register 0x20<br>USBFRAMEH/L Register 0x20<br>USBFRAMEH/L Registers 0x2A, 0x2B<br>MICROFRAME Registers 0x2C<br>FNADDR Register 0x2D | 37<br>39<br>40<br>41<br>43<br>44<br>43<br>44<br>44<br>45<br>46<br>47<br>47<br>47<br>47<br>47<br>47<br>47<br>47<br>47<br>48<br>48<br>48<br>48<br>49<br>49<br>49 |

|          | 5.1<br><b>Registe</b><br>6.1<br>6.2<br>6.3<br>6.4<br>6.5<br>6.6<br>6.7<br>6.8<br>6.9<br>6.10<br>6.11<br>6.12         | nt 0<br>SETUP Commands<br>Register Summary<br>IFCONFIG Register 0x01<br>FLAGSAB/FLAGSCD Registers 0x02/0x03<br>POLAR Register 0x04<br>REVID Register 0x05<br>EPxCFG Register 0x06–0x09<br>EPxPKTLENH/L Registers 0x0A–0x0F<br>EPxPFH/L Registers 0x12–0x17<br>6.8.1 DECIS: EPxPFH.7<br>6.8.2 PKSTAT: EPxPFH.6<br>6.8.3 IN: PKTS(2:0)/OUT: PFC[12:10]: EPxPFH[5:3]<br>6.8.3.1 IN Endpoints<br>6.8.3.2 OUT Endpoints<br>EPxFLAGS Registers 0x1E–0x1F<br>INPKTEND/FLUSH Register 0x20<br>USBFRAMEH/L Registers 0x2A, 0x2B<br>MICROFRAME Registers 0x2C<br>FNADDR Register 0x2D<br>INTENABLE Register 0x2E                      | 37<br>39<br>39<br>40<br>41<br>43<br>44<br>43<br>44<br>44<br>45<br>46<br>47<br>47<br>47<br>47<br>47<br>47<br>47<br>47<br>47<br>47                               |

|     |          | EP0STALL Register 0x32                                      |    |

|-----|----------|-------------------------------------------------------------|----|

|     | 6.17     | CPUCS Unindexed Register 0xE600                             |    |

|     |          | 6.17.1 Example Unindexed Register Read                      |    |

|     |          | 6.17.2 Example Un-indexed Register Write                    | 53 |

| 7.  | Default  | Descriptor                                                  | 55 |

|     | 7.1      | Introduction to the Default Descriptor                      | 55 |

| 8.  | Pin Ass  | signments                                                   | 59 |

|     | 8.1      | 56-Pin SSOP                                                 | 59 |

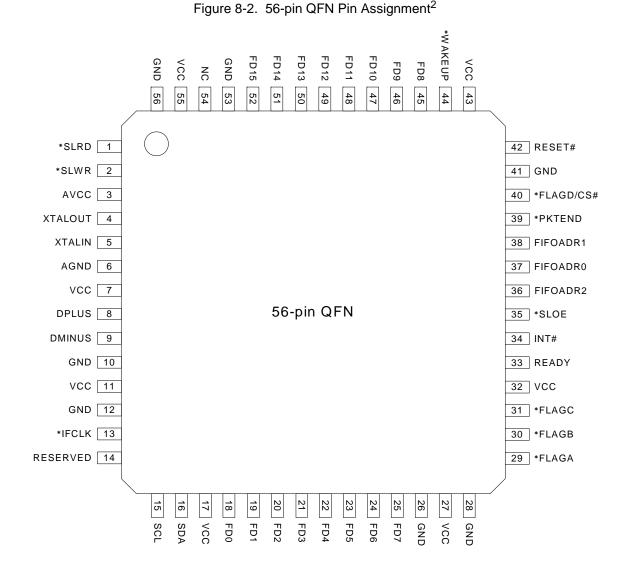

|     | 8.2      | 56-Pin QFN                                                  | 60 |

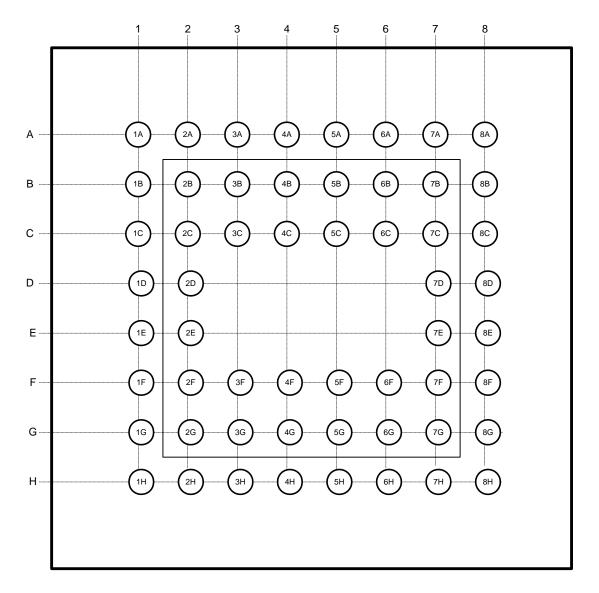

|     | 8.3      | 56-Pin VFBGA                                                | 61 |

|     | 8.4      | MoBL-USB <sup>™</sup> FX2LP18 Device Pin Descriptions       | 62 |

| 9.  | Externa  | al Interface Description                                    | 65 |

|     | 9.1      | External Interface Pin Description                          | 65 |

| 10  | . DMA Ir | nterface                                                    | 67 |

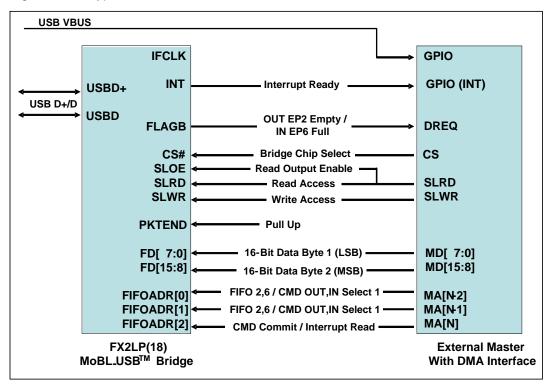

|     | 10.1     | Fast Slave Interface to DMA Interface on External Processor | 67 |

|     | 10.2     |                                                             |    |

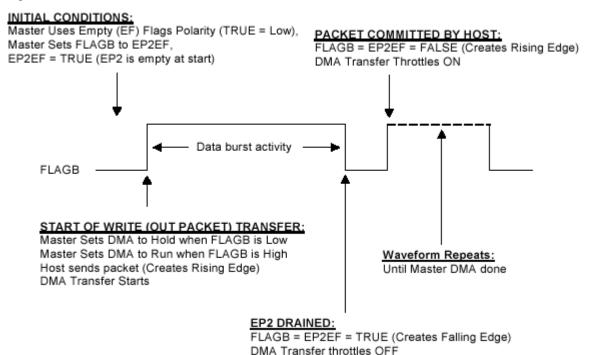

|     |          | 10.2.1 OUT Packet Read Bursts                               | 68 |

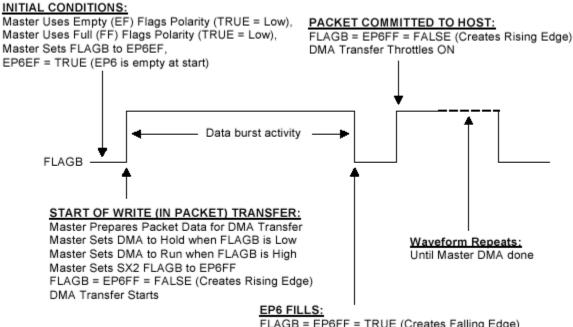

|     |          | 10.2.2 IN Packet Write Bursts                               | 69 |

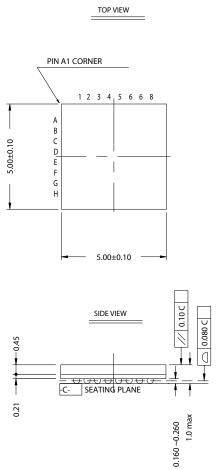

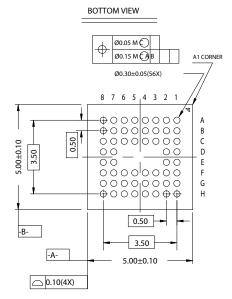

| 11  | . Packag | ge Diagrams                                                 | 71 |

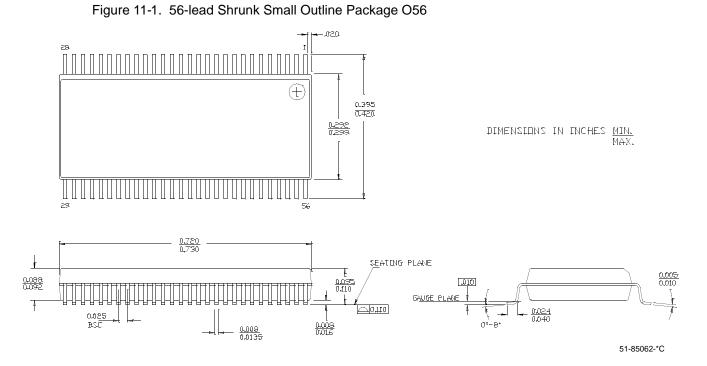

|     | 11.1     | 56-pin SSOP Package                                         | 71 |

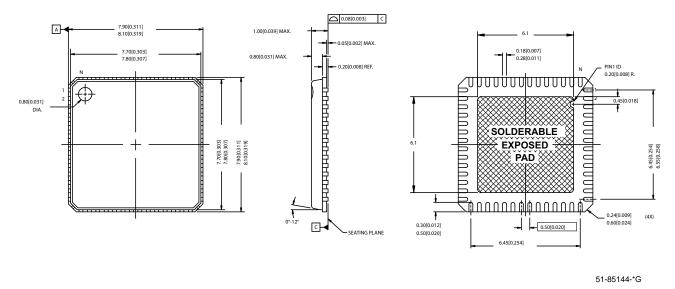

|     | 11.2     |                                                             |    |

|     | 11.3     |                                                             |    |

| Inc | lex      |                                                             | 75 |

Contents

# 1.1 Purpose

The purpose of this manual is to help developers understand how the MoBL-USB Bridge Firmware works.

# 1.2 Chapter Overviews

| Chapter                                     | Description                                                                                                                                                                                               |

|---------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Overview<br>(on page 7)                     | Describes the purpose of this guide, overviews each chapter, supplies product support and upgrade information, and acronyms. This chapter lists the document history and the document conventions.        |

| Introduction<br>(on page 9)                 | Introduces the firmware features, applications, and ordering information.                                                                                                                                 |

| Functional Overview<br>(on page 15)         | Lists USB signaling speed, boot method, resets and wakeup, endpoint RAM organization, external interface, and command lists.                                                                              |

| Enumeration<br>(on page 31)                 | Discusses manual enumeration, default enumeration, external master passthrough enumeration, and the interrupt system.                                                                                     |

| Endpoint 0<br>(on page 37)                  | Presents the setup commands.                                                                                                                                                                              |

| Register Summary<br>(on page 39)            | Presents a table that summarizes all the commands.                                                                                                                                                        |

| Default Descriptor<br>(on page 55)          | Lists example code.                                                                                                                                                                                       |

| Pin Assignments<br>(on page 59)             | Includes figures of the 56-Pin SSOP, 56-Pin QFN, and 56-Pin VFBGA. A table lists the MoBL-USB FX2LP18 device pin descriptions.                                                                            |

| External Interface Description (on page 65) | Presents a table that lists the FX2LP pin names and the cross reference pins to the Bridge Slave FIFO.                                                                                                    |

| DMA Interface<br>(on page 67)               | Describes the fast slave interface to DMA interface on an external pro-<br>cessor, and the DREQ waveform generation with FLAGB which includes<br>the OUT packet read burst and the In packet write burst. |

| Package Diagrams<br>(on page 71)            | Presents the packages for the 56-pin SSOP, 56-pin QFN, and the 56-pin VFBGA.                                                                                                                              |

Table 1-1. Overview of the MoBL-USB Bridge Firmware Guide Chapters

# 1.3 Support

Technical Support can be reached at http://www.cypress.com/support or can be contacted by phone at: 1-800-541-4736.

The following related documentation can be found on the Cypress web site.

| Document Number | Document Type | Document Name                                     |

|-----------------|---------------|---------------------------------------------------|

| 38-08032        | Data Sheet    | EZ-USB FX2LP™ USB Microcontroller                 |

| 001-06120       | Data Sheet    | MoBL-USB <sup>™</sup> FX2LP18 USB Microcontroller |

| 001-11981       | TRM           | MoBL-USB™ FX2LP18 Technical Reference Manual      |

| 001-13670       | TRM           | EZ-USB® Technical Reference Manual                |

#### 1.3.1 Acronyms

The following are acronyms used throughout this user guide.

#### Table 1-2. Acronyms

| Acronym | Description                                       |

|---------|---------------------------------------------------|

| ADC     | analog-to-digital converter                       |

| API     | application programming interface                 |

| С       | (refers to C programming language)                |

| DAC     | digital-to-analog converter                       |

| EE      | empty flag                                        |

| EEPROM  | electrical erasable programmable read only memory |

| FF      | full flag                                         |

| 10      | input/output                                      |

| ISR     | interrupt service routine                         |

| MCU     | microcontroller unit                              |

| MHz     | megahertz                                         |

| MSC     | mass storage class                                |

| MTP     | media transfer protocol                           |

| PF      | programmable flag                                 |

| PLL     | phase lock loop                                   |

| PWM     | pulse width modulator                             |

| RAM     | random access memory                              |

| ROM     | read only memory                                  |

| USB     | universal serial bus                              |

# 1.4 Document History

This section serves as a chronicle of the CY4626 MoBL-USB<sup>™</sup> Bridge Firmware Guide.

| Release<br>Date | Firmware<br>Revision | Manual<br>Version | Originator | Description of Change                                                                                                                                      |

|-----------------|----------------------|-------------------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 05/24/07        | 5.3                  | **                | ARI        | This manual is a new document to the Cypress Document Con-<br>trol (Revision **) system; this manual has gone through several<br>versions as a data sheet. |

| 09/11/07        | 5.4                  | *A                | ARI        | Added Extended Short Packet information in the Putting EP6IN Data–Short Packet section and in the Command List section.                                    |

CY4626 MoBL-USB™ Bridge Firmware Guide History

# **1.5 Document Conventions**

This manual uses the Courier New font to distinguish code examples from regular text. File names are presented in *italics* text.

# 2.1 Introducing the MoBL-USB<sup>™</sup> Bridge Firmware

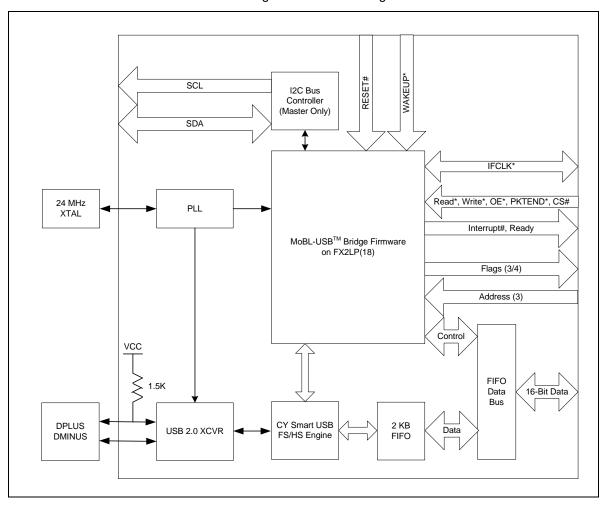

The MoBL-USB Bridge firmware is designed to work with any external master, such as standard microprocessors, DSPs, ASICs, and FPGAs to enable USB 2.0 support for any peripheral design. The Bridge firmware operates on both the EZ-USB FX2LP™ and MoBL-USB™ FX2LP18 chips, which have a built-in USB transceiver and Serial Interface Engine (SIE), along with a command decoder for sending and receiving USB data. The controller has two double buffered high-speed capable endpoints that share a 2 KB FIFO space for maximum flexibility and throughput, as well as Control Endpoint 0. The Bridge firmware exposes three FIFO address pins and a 16 bit data bus for both command and data input or output.

## 2.1.1 Features

- USB 2.0 compliant

- Operates at high (480 Mbps) or full (12 Mbps) speed

- Supports Control Endpoint 0

- Used for handling USB device requests

- Supports two double buffered high-speed endpoints that share a 2 KB FIFO space

Endpoints 2 and 6 for application specific control and data

- Supports two additional single buffered high-speed endpoints that share buffer space with the command interface

- □ Endpoints 4 and 8 for application specific control and data

- Bidirectional Endpoint 1 to support interrupt transfers

- Standard 16 bit Command and Data FIFO interface

- □ Glueless interface to most standard microprocessors DSPs, ASICs, and FPGAs

- Synchronous or Asynchronous interface

- Targeted to CY7C68013/14/53A FX2LP in 56 pin SSOP, QFN, and VFBGA packages

- Complies with most device class specifications

- Supports Microsoft's PMP (Portable Media Player) specification

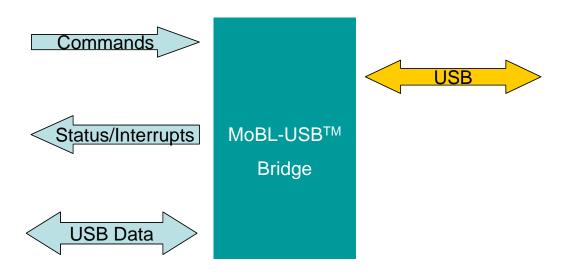

Figure 2-1. Block Diagram

# 2.2 Applications

- Cell phones

- DSL modems

- ATA interface

- Memory card readers

- Legacy conversion devices

- Cameras

- Scanners

- Home PNA

- Wireless LAN

- MP3 players

- Portable media players

- Networking

- Printers

The Reference Designs section of the Cypress web site provides additional tools for typical USB applications. Each reference design kit comes complete with firmware source code and object code, schematics, and documentation. See the Cypress web site at http://www.cypress.com.

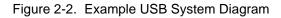

### 2.2.1 System Diagram

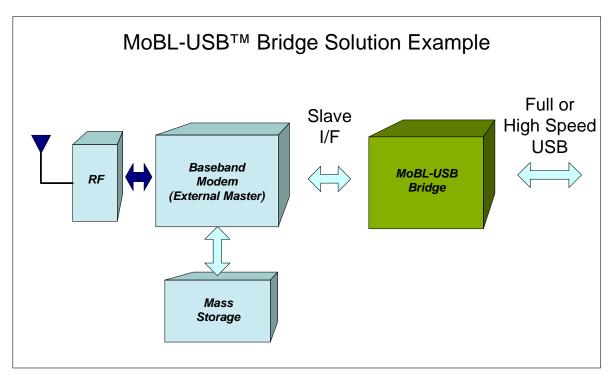

Figure 2-3. Bridge System States

# 2.3 Ordering Information

Use the following table to select the appropriate FX2LP part for the application. Refer to the data sheet for the selected part for pinout information.

| Ordering Code Package Type                 |                                             | RAM<br>Size | # Prog<br>I/Os |  |  |

|--------------------------------------------|---------------------------------------------|-------------|----------------|--|--|

| Ideal for battery powered applications     |                                             |             |                |  |  |

| CY7C68014A-56PVXC                          | CY7C68014A-56PVXC FX2LP 56 SSOP – Lead-free |             | 24             |  |  |

| CY7C68014A-56LFXC                          | FX2LP 56 QFN – Lead-free                    | 16K         | 24             |  |  |

| CY7C68014A-56BAXC                          | FX2LP 56 VFBGA – Lead-free                  | 16K         | 24             |  |  |

| CY7C68053-56BAXI                           | FX2LP18 56 VFBGA – Lead-free                | 16K         | 24             |  |  |

|                                            |                                             |             |                |  |  |

| Ideal for non-battery powered applications | 3                                           |             |                |  |  |

| CY7C68013A-56PVXC                          | FX2LP 56 SSOP – Lead-free                   | 16K         | 24             |  |  |

| CY7C68013A-56PVXI                          | FX2LP 56 SSOP – Lead-free (Industrial)      | 16K         | 24             |  |  |

| CY7C68013A-56LFXC                          | FX2LP 56 QFN – Lead-free                    | 16K         | 24             |  |  |

| CY7C68013A-56LFXI                          | FX2LP 56 QFN – Lead-free (Industrial)       | 16K         | 24             |  |  |

| CY7C68013A-56BAXC                          | FX2LP 56 VFBGA – Lead-free                  | 16K         | 24             |  |  |

|                                            |                                             |             |                |  |  |

| Development Tool Kit                       |                                             |             |                |  |  |

| CY3684                                     | EZ-USB FX2LP Development Kit                |             |                |  |  |

| CY3687                                     | MoBL-USB FX2LP18 Development Kit            |             |                |  |  |

| Reference Design Kit                       |                                             |             |                |  |  |

| CY4624                                     | Media Transfer Protocol for Microsoft Porta | able Media  | a Center       |  |  |

Introduction

# 3. Functional Overview

The intended use of this Bridge firmware is with class drivers such as Mass Storage Class (MSC) or Media Transfer Protocol (MTP). Therefore, for OUT transfers with data bus equal to 16 bits (wordwide), the master processor must ignore the extra byte for an odd packet size. For IN transfers with an odd number of bytes, the last odd byte is sent in the IN Short Packet command (see Command List on page 30).

# 3.1 USB Signaling Speed

The Bridge firmware operates at two of the three rates defined in the Universal Serial Bus Specification Revision 2.0, dated April 27, 2000.

- Full-speed, with a signaling bit rate of 12M bits per second

- High-speed, with a signaling bit rate of 480M bits per second

- The Bridge firmware does not support the low-speed signaling rate of 1.5M bits per second.

# **3.2 Boot Method**

Upon reset, MoBL-USB chips automatically look for and load from an EEPROM attached to the SDA and SCL signals. If an image is found and the first byte matches the proper signature value (0xC2), then the chip loader loads the image contained in the EEPROM. The eighth byte (byte 7) is the configuration byte and is set to 0x40 for the supplied Bridge images. This value sets the device in disconnect and sets the  $I^2C^{TM}$  interface speed to approximately 100 KHz or the default speed. If this value is modified in the image to 0x41, then the loader changes the EEPROM access speed to approximately 400 KHz.

Either an EEPROM can be used with one of the images identified in Bridge Firmware Images and Standby Sequences on page 27 loaded on the EEPROM, or the external master can be connected to the MoBL-USB SDA and SCL lines and emulate a slave EEPROM device, providing one of the images to the loader. The MoBL-USB chip is an I2C master-only device therefore, if the external master does not have a slave-only I2C interface, then bit-banging general purpose IO pins may be used to provide the slave I2C interface.

# 3.3 Resets and Wakeup

The Bridge firmware replies to a reset, USB reset, and wakeup call.

#### 3.3.1 Reset

Downloaded from Elcodis.com electronic components distributor

An input pin (RESET#) resets the chip. The internal PLL stabilizes after V<sub>CC</sub> has reached 3.3V. Typically, an external RC network (R = 100K ohms, C = 0.1  $\mu$ f) is used to provide the RESET# signal. The clock must be in a stable state for at least 200  $\mu$ s before the RESET is released.

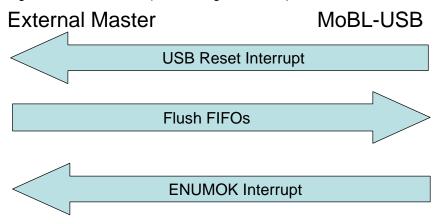

## 3.3.2 USB Reset

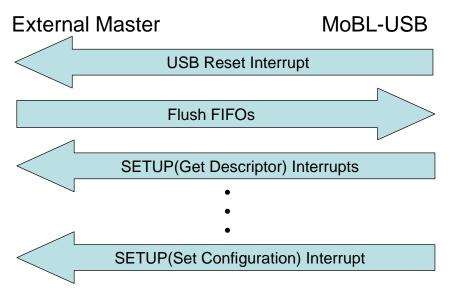

When the Bridge firmware detects a USB reset condition on the USB bus, Bridge firmware clears the data toggle bits for all endpoints, flushes all FIFOs, asserts the USB reset interrupt, then handles it the same as any other enumeration sequence. This means that the Bridge firmware enumerates again and asserts the ENUMOK interrupt to let the external master know that it has enumerated. The external master is then responsible for configuring the Bridge firmware for the application. The external master must also check whether the Bridge enumerated at High or Full speed in order to adjust the EPxPKTLENH/L register values accordingly. The last initialization task is for the external master to flush all of the Bridge firmware FIFOs.

## 3.3.3 Wakeup

The Bridge firmware exits its low power state when one of the following events occur:

- USB bus signals a resume. The Bridge firmware asserts a HOST\_RESUME extended interrupt.

- The external master asserts the WAKEUP pin. The Bridge firmware asserts a READY interrupt.

# 3.4 Endpoint RAM Organization

- EP0-Bidirectional Endpoint 0, 64-byte buffer.

- EP2 and EP6 Four 512-byte buffers, bulk or interrupt. EP2 and EP6 are high-speed doublebuffered endpoints. Applications configure EP2 for OUT and EP6 for IN packets.

- EP4OUT and EP8IN are available through shifted mode of the command interface. They are high-speed endpoints that are bulk or interrupt and single buffered.

- EP1IN is a 64-byte endpoint. It is intended for use as an interrupt endpoint and is single-buffered. It is accessed via the command interface.

- EP1OUT is a 64-byte endpoint. It is single-buffered. It is accessed via the command interface.

# 3.5 External Interface

The Bridge firmware presents two interfaces to the external master.

- 1. A double-buffered FIFO interface through which EP2 and EP6 data flows. This interface buffers up to two packets at the current transfer speed. At high-speed, each FIFO holds two 512-byte packets. At full-speed, each FIFO holds two 64-byte packets.

- 2. A single-buffered command interface, which is used to set up the Bridge firmware, read the status, load the descriptors, and access Endpoints 0 and 1. The extended endpoints 4 and 8 are also accessed through the command interface.

#### Figure 3-1. Bridge Interfaces

## 3.5.1 Control Signals

Bridge firmware has FIFOADDR control lines, the read controls: SLOE and SLRD, the write control: SLWR, and the PKTEND control line.

#### 3.5.1.1 FIFOADDR Lines

The Bridge firmware has three address pins that are used to select either the FIFOs or the command interface. How the address lines correspond are listed in the following table.

| Address/Selection                        | FIFOADR2 | FIFOADR1 | FIFOADR0 |

|------------------------------------------|----------|----------|----------|

| FIFO2                                    | 0        | 0        | 0        |

| Command OUT                              | 0        | 0        | 1        |

| FIFO6                                    | 0        | 1        | 0        |

| Command IN                               | 0        | 1        | 1        |

| Interrupt (read)<br>Command done (write) | 1        | 0        | 0        |

| RESERVED                                 | 1        | 0        | 1        |

| RESERVED                                 | 1        | 1        | 0        |

| RESERVED                                 | 1        | 1        | 1        |

| Table 3-1. | FIFO | Address | Lines | Setting |

|------------|------|---------|-------|---------|

|------------|------|---------|-------|---------|

The Bridge firmware accepts either an internally derived clock (30 or 48 MHz) or externally supplied clock (IFCLK, 5 – 48 MHz), and SLRD, SLWR, SLOE, CS#, FIFOADR[2:0] signals from an external master. The interface is 16 bits wide; an Output Enable signal, SLOE, enables the data bus driver for read operations. The external master must ensure that the output enable signal is inactive when writing data to the Bridge firmware. The interface can operate either asynchronously where the SLRD and SLWR signals act directly as strobes, or synchronously where the SLRD and SLWR act as clock qualifiers. The optional CS# signal tri-states the data bus and ignores SLRD and SLWR. Since the Bridge only supports 16 bit wide data, the PKTEND is typically not used since it does not allow odd

byte size transfers. The Bridge firmware provides a command for committing short packets that also includes handling odd packet size transfers.

The external master reads from OUT endpoints and writes to IN endpoints, and it reads from or writes to the command interface.

#### 3.5.1.2 Read: SLOE and SLRD

In synchronous mode, the FIFO pointer is incremented on each rising edge of IFCLK while SLRD is asserted. In asynchronous mode, the FIFO pointer is incremented on each asserted-to-deasserted transition of SLRD.

SLOE is a data bus driver enable. When SLOE is asserted, the data bus is driven by the Bridge firmware.

#### 3.5.1.3 Write: SLWR

In synchronous mode, data on the FD bus is written to the FIFO (and the FIFO pointer is incremented) on each rising edge of IFCLK while SLWR is asserted. In asynchronous mode, data on the FD bus is written to the FIFO (and the FIFO pointer is incremented) on each asserted-to-deasserted transition of SLWR.

#### 3.5.1.4 PKTEND

PKTEND commits the current buffer to USB. To send a short IN packet (one that has not been filled to max packet size determined by the value of PL[X:0] in EPxPKTLENH/L), the external master strobes the PKTEND pin.

Packet end can also be signaled using the IN Short Packet command shown in Command List on page 30. This is the preferred method in order to be able to write the last byte in the command for an odd packet length. If the PKTEND pin is not used, then it must be pulled high assuming that the default active low polarity is used.

The default configuration for this interface is active low. In order to change the polarity of the PKTEND pin, the master may write to the POLAR register at any time. In order to switch the polarity of the SLWR/SLRD/SLOE, the master must set bits 2, 3, and 4 respectively in the FIFOPINPOLAR register located at XDATA space 0xE609. Note that the Bridge powers up with the polarities set to low. POLAR Register 0x04 on page 43 provides further information on how to access this register located at XDATA space.

## 3.5.2 IFCLK

The IFCLK pin can be configured to be either an input (default) or an output interface clock. Bits IFCONFIG[7:4] define the behavior of the interface clock. To use the internally derived 30- or 48-MHz clock, set IFCONFIG.7 to '1' and set IFCONFIG.6 to '0' (30 MHz) or to '1' (48 MHz). To use an externally supplied clock, set IFCONFIG.7=0 and drive the IFCLK pin (5 MHz – 48 MHz). The input or output IFCLK signal can be inverted by setting IFCONFIG.4=1.

## 3.5.3 FIFO Access

An external master can access the slave FIFOs either asynchronously or synchronously:

- Asynchronous SLRD, SLWR, and PKTEND pins are strobes.

- Synchronous SLRD, SLWR, and PKTEND pins are enables for the IFCLK clock pin.

An external master accesses the FIFOs through the data bus, FD [15:0]. This bus must be set for 16 bits wide; the width is selected via the WORDWIDE bit in the EPxPKTLENH/L registers. The data

bus is bidirectional, with its output drivers controlled by the SLOE pin. The FIFOADR[2:0] pins select which of the two FIFOs is connected to the FD [15:0] bus, or if the command interface is selected.

## 3.5.4 FIFO Flag Pins Configuration

The FIFO flags are FLAGA, FLAGB, FLAGC, and FLAGD. These FLAGx pins report the status of the FIFO selected by the FIFOADR[2:0] pins. At reset, these pins are configured to report the status of the following:

- FLAGA reports the status of the programmable flag.

- FLAGB reports the status of the full flag.

- FLAGC reports the status of the empty flag.

- FLAGD defaults to the CS# function.

The FIFO flags can either be indexed or fixed. Fixed flags report the status of a particular FIFO regardless of the value on the FIFOADR [2:0] pins. Indexed flags report the status of the FIFO selected by the FIFOADR [2:0] pins.<sup>1</sup> Applications configure EP2 as an OUT endpoint and typically set FLAGA to fixed signalling of EP2 empty/not-empty status; they configure EP6 as an IN endpoint and typically set FLAGB to fixed signalling of EP6 full/not full status. For reduced pin interfacing, a single FLAG pin can be used by setting it for the current direction of data flow and using the INNF and OUTNE interrupts to signal when the direction should be reversed.

## 3.5.5 Default FIFO Programmable Flag Setup

By default, FLAGA is the Programmable Flag (PF) for the endpoint being pointed to by the FIFOADR[2:0] pins. For EP2, the default endpoint configuration is BULK, OUT, 512, 2x, and the PF pin asserts when the entire FIFO has greater than/equal to 512 bytes. For EP6, the default endpoint configuration is BULK, IN, 512, 2x, and the PF pin asserts when the entire FIFO is less than or equal to 512 bytes. In other words, EP6 reports a half-empty state, and EP2 reports a half-full state. The polarity of the programmable flags are set in the EEPROM configuration bytes.

## 3.5.6 FIFO Programmable Flag Setup

Each FIFO's programmable-level flag asserts when the FIFO reaches a user-defined fullness threshold. That threshold is configured as follows:

- For OUT packets: The threshold is stored in PFC12:0. The PF is asserted when the number of bytes in the entire FIFO is less than or equal to (DECIS = 0) or greater than/equal to (DECIS = 1) the threshold.

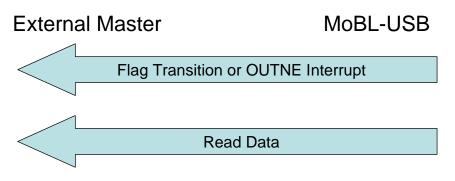

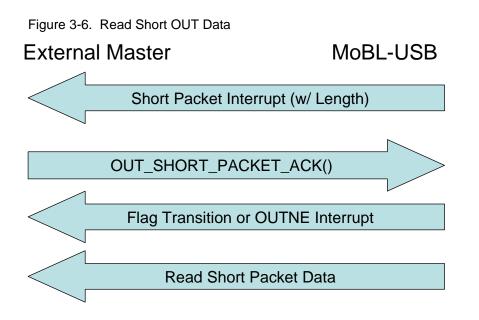

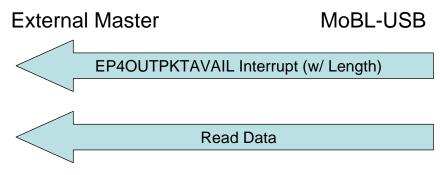

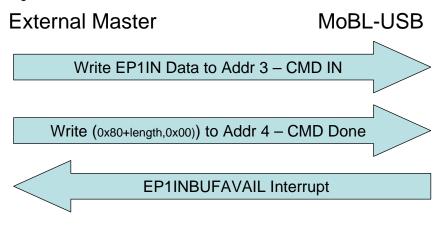

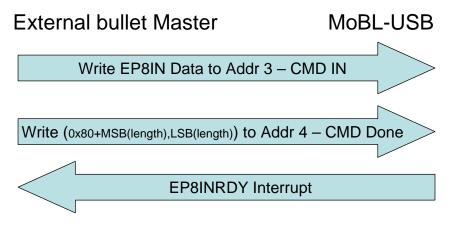

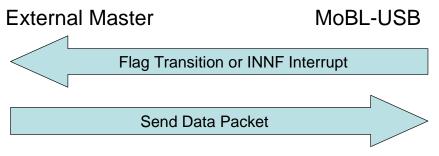

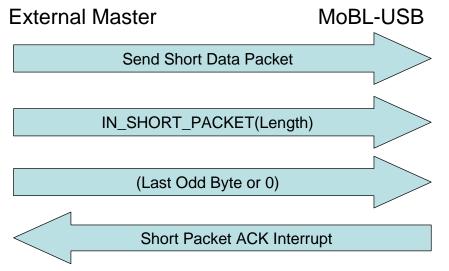

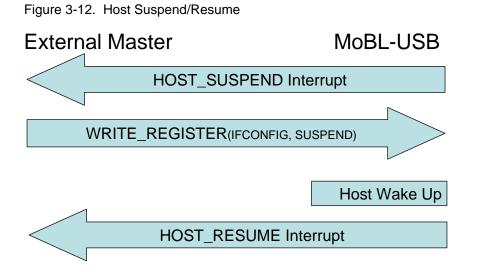

- For IN packets, with PKTSTAT = 1: The threshold is stored in PFC9:0. The PF is asserted when the number of bytes written into the current packet in the FIFO is less than or equal to (DECIS = 0) or greater than/equal to (DECIS = 1) the threshold.