User's Manual

Version 1.0 June 1, 2003

MPC852TADSRM/D

## Freescale Semiconductor, Inc.

MOTOROLA

intelligence everywhere™

# MPC852TADS

**User's Manual**

### **Important Notice to Users**

While every effort has been made to ensure the accuracy of all information in this document, Motorola assumes no liability to any party for any loss or damage caused by errors or omissions or by statements of any kind in this document, its updates, supplements, or special editions, whether such errors are omissions or statements resulting from negligence, accident, or any other cause. Motorola further assumes no liability arising out of the application or use of any information, product, or system described herein: nor any liability for incidental or consequential damages arising from the use of this document. Motorola disclaims all warranties regarding the information contained herein, whether expressed, implied, or statutory, *including implied warranties of merchantability or fitness for a particular purpose*. Motorola makes no representation that the interconnection of products in the manner described herein will not infringe on existing or future patent rights, nor do the descriptions contained herein imply the granting or license to make, use or sell equipment constructed in accordance with this description.

#### **Trademarks**

This document includes these trademarks:

Motorola and the Motorola logo are registered trademarks of Motorola, Inc.

Windows is a registered trademark of Microsoft Corporation in the U.S. and other countries.

Intel is a registered trademark of Intel Corporation.

Motorola, Inc., is an Equal Opportunity / Affirmative Action Employer.

For an electronic copy of this book, visit Motorola's web site at http://e-www.motorola.com/ © Motorola, Inc., 2002; All Rights Reserved

MPC852TADS - Version 1.0

User's Manual

MOTOROLA

## 1 - Hardware Preparation

## 1•1 Jumpers and Dip-Switches

Ensure the following jumpers are in place:

TABLE 1-1. Default Jumpers and dip switches settings

| Reference Name | Description                                                                                                | Default                                 |

|----------------|------------------------------------------------------------------------------------------------------------|-----------------------------------------|

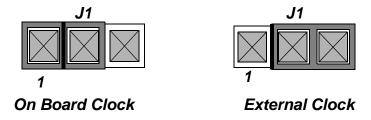

| J1             | Clock Oscillator source:<br>1-2: 10MHz on board<br>clock oscillator.<br>2-3: External clock<br>oscillator. | 1-2: 10MHz on board clock oscillator.   |

| SW1            | Power Switch ON/OFF                                                                                        | Power Switch OFF                        |

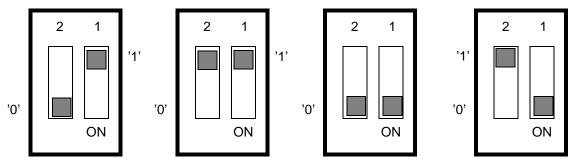

| SW4            | Modin Selector:<br>Modin[12] = 'OFF,ON'                                                                    | Modin[12] :<br>'OFF,ON' = '1,0'         |

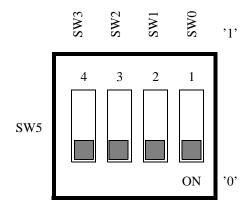

| SW5            | S/W Options[41]:<br>'ON,ON,ON,ON'                                                                          | S/W Option[41]:<br>'ON,ON,ON,ON'='0000' |

#### 1•2 Connections

Connect the following connectors:

- P16 Power Supply 5.0V DC.

- P13 Power Supply 12.0V DC for PCMCIA channel or for Flash Programming.

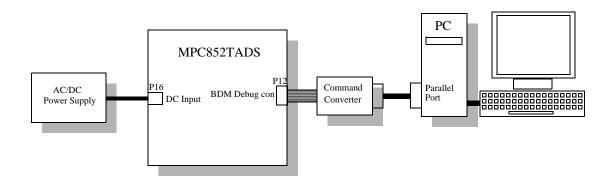

- P12 BDM Connector via External Command Converter to Host Computer Parallel Port.

- P17A (Down) RS232-1 Connector to Host Computer COM1 Port.

#### 1•3 Run

• Turn on the 5V power supply and verify LD8, LD14, LD15, LD17, LD18 Leds on board lit up.

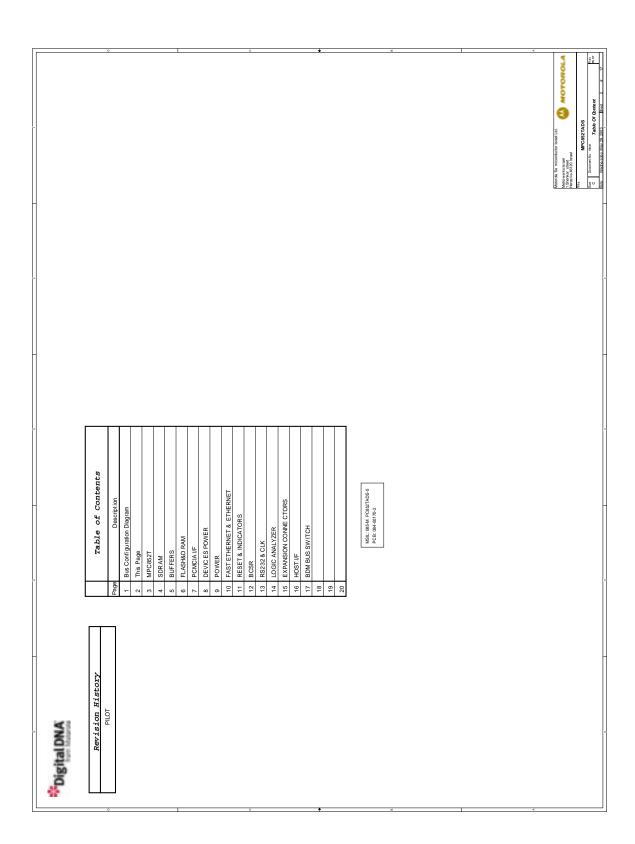

## **Table Of Contents**

| General Information                               | 1  |

|---------------------------------------------------|----|

| MPC852TADS Introduction and Goals                 | 1  |

| List of Abbreviations                             | 1  |

| Related Documentation                             | 1  |

| SPECIFICATIONS                                    | 1  |

| MPC852TADS Features                               | 3  |

| Hardware Preparation and Installation             | 5  |

| INTRODUCTION                                      | 5  |

| UNPACKING INSTRUCTIONS                            | 5  |

| HARDWARE PREPARATION                              | 5  |

| MPC Replacement of U1                             | 8  |

| Clock Source Selection - J1                       | 8  |

| Modin Selection - SW4                             | 8  |

| Software Option - SW5                             | 9  |

| INSTALLATION INSTRUCTIONS                         | 10 |

| Host Controlled Operation                         | 10 |

| Standalone Operation                              | 11 |

| 10/100-Base-T Ethernet Ports Connection - P9, P10 | 12 |

| BDM Debug Port Connector - P12                    | 12 |

| +12V Power Supply Connection - P13                | 12 |

| +5V Power Supply Connection - P16                 | 13 |

| Terminal to MPC852TADS RS-232 Connection - P17    | 13 |

| Parallel Host Connector in EPP I/F - P20          | 14 |

| Memory Installation                               | 15 |

| OPERATING INSTRUCTIONS                            | 17 |

| INTRODUCTION                                      | 17 |

| CONTROLS AND INDICATORS                           | 17 |

| ABORT Switch, SW2                                 | 17 |

| SOFT RESET Switch, SW3                            | 17 |

| HARD RESET Switches, SW2 & SW3                    | 17 |

| Modin Selection, SW4                              | 17 |

| Software Options Switch, SW5                      | 17 |

| Power-On RESET Switch, SW6                        | 17 |

| GND Bridges                                       | 18 |

| Ethernet 10Base-T. ETH TX/RX, LD1                 | 18 |

| Ethernet Full Duplex Indicator, LD2               | 18 |

| Ethernet LINK Indicator, LD3                      | 18 |

| Fast Ethernet 100Mbps Indicator, LD4              | 18 |

| Fast Ethernet 10/100Base-T. TX/RX, LD5            | 18 |

| Fast Ethernet Full Duplex Indicator, LD6          | 18 |

| Fast Ethernet LINK Indicator, LD7                 | 18 |

| Ethernet 10Base-T. ETH ON, LD8                    | 19 |

| RS232 Port 2 ON, LD9                              | 19 |

I

| Fast Ethernet 10/100Base-T. ON, LD10               | 19 |

|----------------------------------------------------|----|

| RS232 Port 1 ON, LD12                              | 19 |

| PCMCIA ON, LD13                                    | 19 |

| FLASH ON, LD14                                     | 19 |

| DRAM ON, LD15                                      | 19 |

| SGLAMP ON, LD16                                    | 19 |

| SDRAM ON, LD17                                     | 20 |

| 5V Indicator, LD18                                 | 20 |

| RUN Indicator, LD19                                | 20 |

| EPP Indicator, LD20                                | 20 |

| SPP Indicator, LD21                                | 20 |

| MEMORY MAP                                         | 20 |

| MPC Register Programming                           | 22 |

| Memory Controller Registers Programming            | 23 |

| Functional Description                             | 34 |

| Reset & Reset - Configuration                      | 34 |

| Regular Power - On Reset                           | 34 |

| Manual Soft Reset                                  | 34 |

| Manual Hard Reset                                  | 34 |

| Host Hard Reset through on board command converter | 34 |

| MPC Internal Sources                               | 35 |

| Reset Configuration                                | 35 |

| Power On Reset Configuration                       | 35 |

| Hard Reset Configuration                           | 35 |

| Soft Reset Configuration                           | 36 |

| Local Interrupter                                  | 36 |

| Clock Generator                                    | 36 |

| Buffering                                          | 36 |

| Chip - Select Generator                            | 37 |

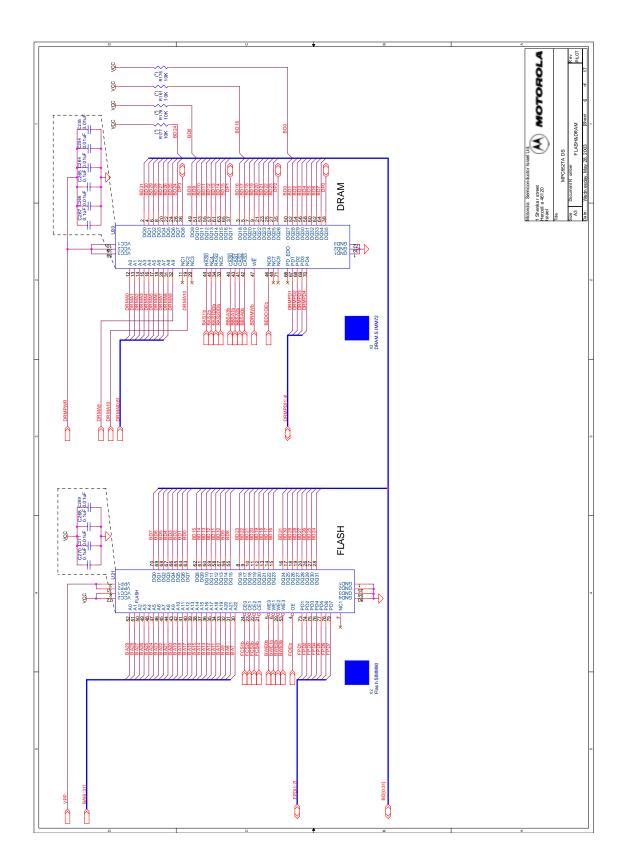

| DRAM                                               | 37 |

| DRAM 16-Bit Operation                              | 38 |

| DRAM Performance Figures                           | 38 |

| Refresh Control                                    | 39 |

| Variable Bus-Width Control                         | 40 |

| Flash Memory SIMM                                  | 42 |

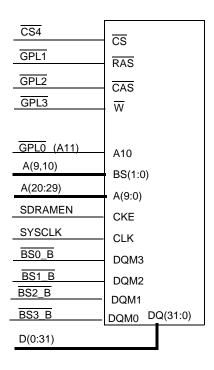

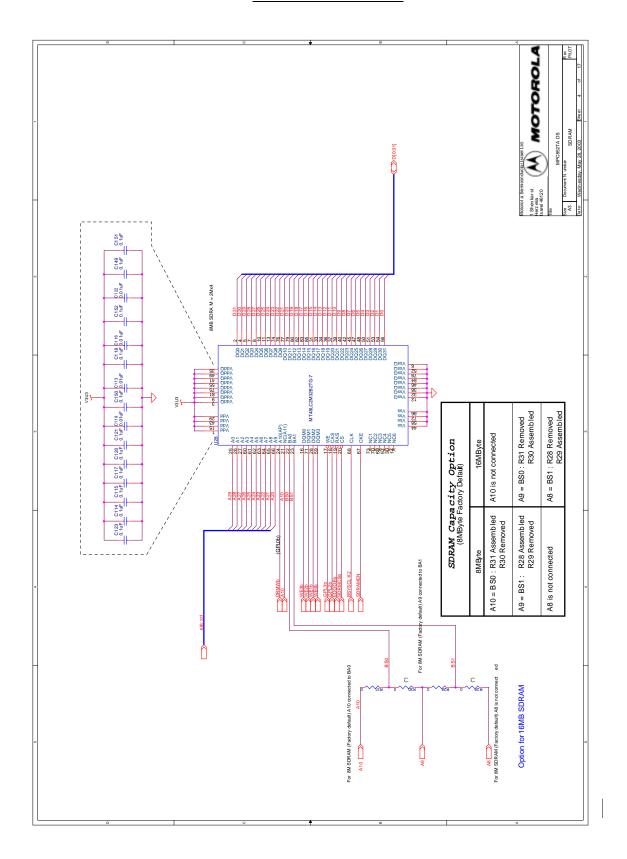

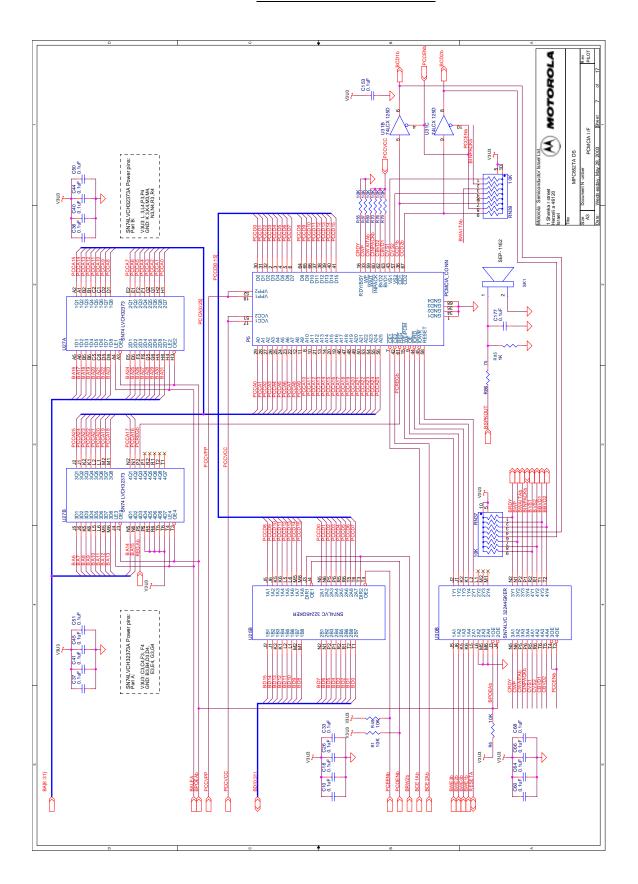

| Synchronous DRAM                                   | 43 |

| SDRAM Programming                                  | 46 |

| SDRAM Initializing Procedure                       | 47 |

| SDRAM Refresh                                      | 47 |

| Communication Ports                                | 48 |

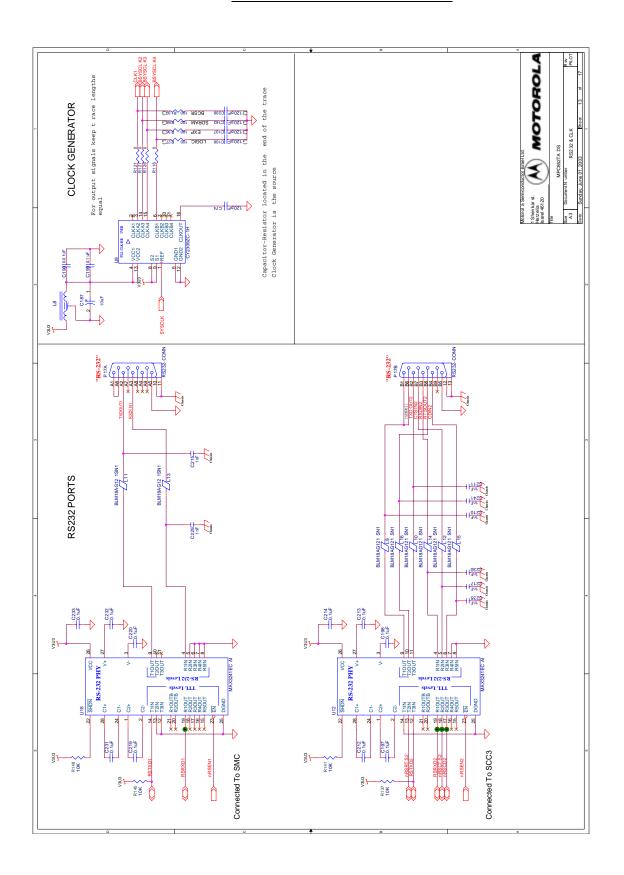

| RS232 Ports                                        | 48 |

| RS232 Port Signal Descriptions                     | 48 |

| Ethernet Port                                      | 48 |

| FETHC - Fast Ethernet Controller on Port - D       | 48 |

| DM9161E Control                                    | 49 |

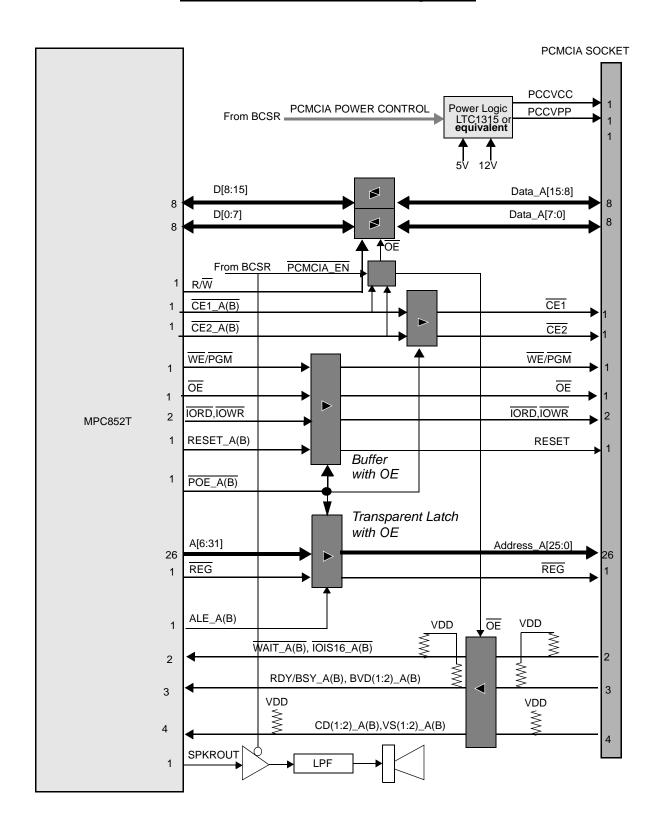

| PCMCIA Port                                        | 49 |

| PCMCIA Power Control                                              | 51 |

|-------------------------------------------------------------------|----|

| Board Control & Status Register: BCSR                             | 51 |

| BCSR0: Hard Reset Configuration Register                          | 52 |

| BCSR1: Board Control Register 1                                   | 53 |

| BCSR2: Board Control / Status Register 2                          | 55 |

| BCSR3: Board Control / Status Register 3                          | 57 |

| BCSR4 - Board Control / Status Register 4                         | 58 |

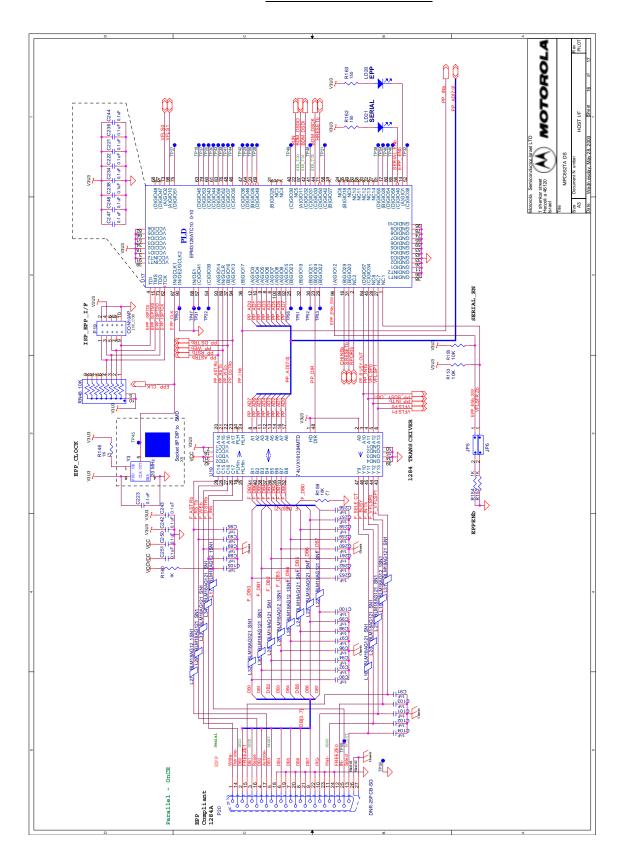

| On board EPP/SPP Command Converter                                | 59 |

| EPP Register Definitions                                          | 61 |

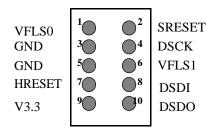

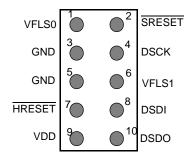

| BDM Debug Port                                                    | 62 |

| Standard MPC852T Debug Port Connector Pin Description             | 62 |

| VFLS(0:1)                                                         | 62 |

| HRESET*                                                           | 62 |

| SRESET*                                                           | 62 |

| DSDI: Debug Port Serial Data In                                   | 62 |

| DSCK: Debug Port Serial Clock                                     | 63 |

| DSDO: Debug Port Serial Data Out                                  | 63 |

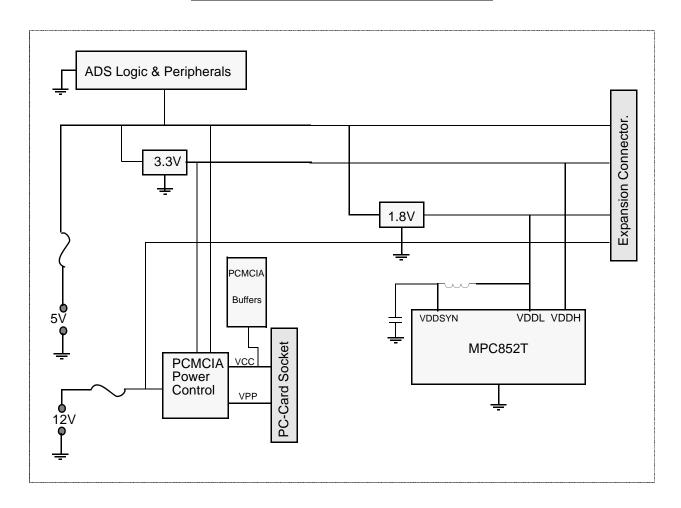

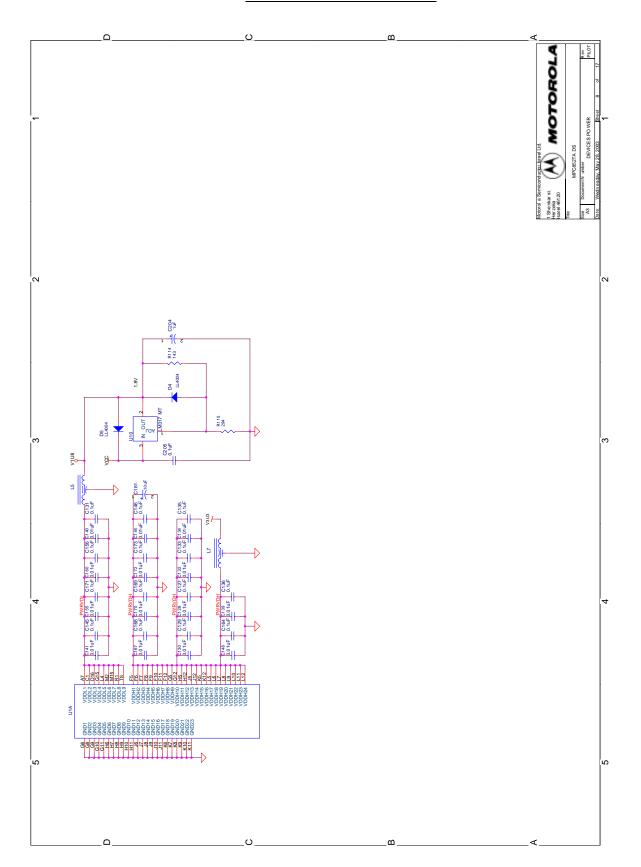

| Power                                                             | 63 |

| 5V Bus                                                            | 65 |

| 3.3V Bus                                                          | 65 |

| 12V Bus                                                           | 65 |

| Support Information                                               | 66 |

| Interconnect Signals                                              | 66 |

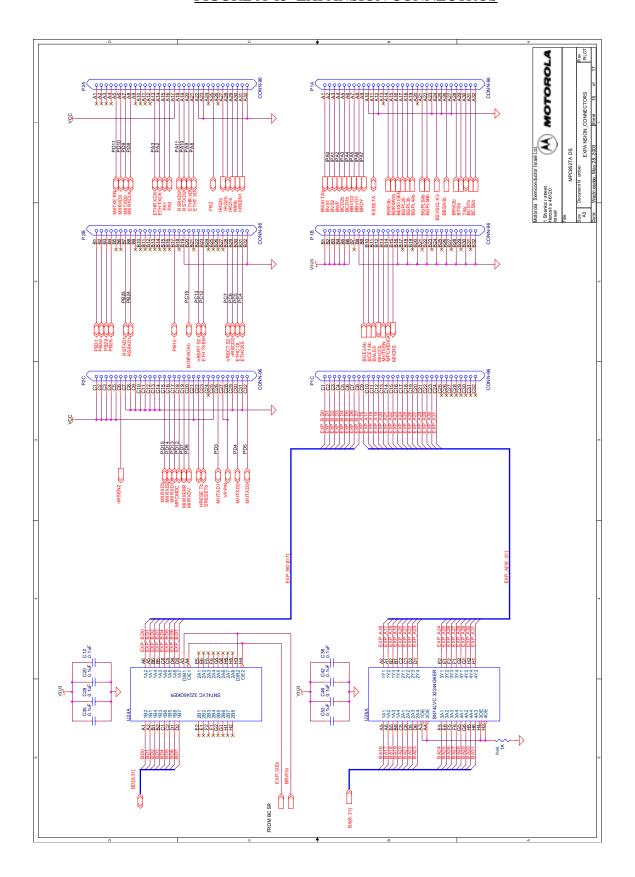

| P1, P2: Expansion Connectors                                      | 66 |

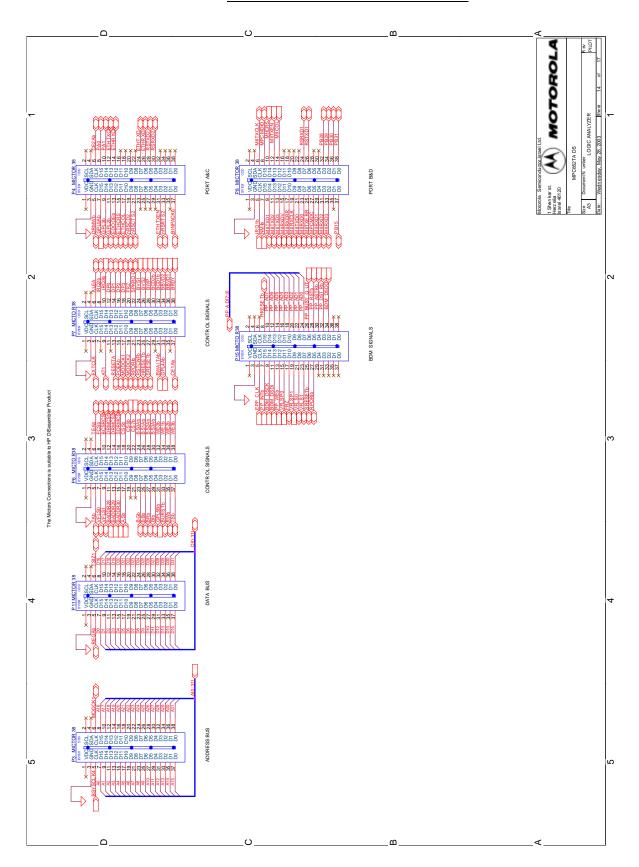

| P3, P4, P6, P7, P8, P11 and P15 MICTOR: Logic Analyzer connectors | 74 |

| P5: PCMCIA Port Connector                                         | 80 |

| P9, P10: 100/10BaseT Ethernet Port Connector                      | 82 |

| P12: External Debug Port Controller Input Interconnect            | 83 |

| P13: 12V Power-In Connector                                       | 84 |

| P14: BNC Connector                                                | 85 |

| P16: 2.1 mm Power Jack 5V Connector                               | 85 |

| P17: RS232 Dual Port Connector                                    | 85 |

| P18, P19: Altera programming ISP Connectors                       | 85 |

| P20: Parallel Host Port Connector                                 | 86 |

| MPC852TADS Parts Listing                                          | 87 |

| Schematics                                                        | 91 |

## **List Of Tables**

| MPC852TADS Specifications                                                           | 1  |

|-------------------------------------------------------------------------------------|----|

| Power ON Reset DPLL Configuration                                                   | 9  |

| Memory Map in MP852TADS New Mode                                                    | 21 |

| Memory Map in MPC852TADS Compatible Mode                                            | 21 |

| SIU REGISTER PROGRAMMING                                                            | 23 |

| Memory Controller Initialization For 66Mhz with DRAM-EDO                            | 24 |

| Memory Controller Initialization For 66Mhz with No DRAM-EDO                         | 26 |

| UPMA Initializations for 60nsec DRAMs @ 66MHz                                       | 28 |

| Memory Controller Initializations For 20Mhz                                         | 29 |

| UPMA Initializations for 60nsec EDO DRAMs @ 20MHz                                   | 31 |

| UPMB Initialization for KS643232C-TC60 upto 32MHz                                   | 32 |

| UPMB Initialization for KS643232C-TC60, 32+MHz - 50MHz                              | 33 |

| MPC852TADS Chip-Select Assignment                                                   | 37 |

| Regular DRAM Performance Figures                                                    | 39 |

| EDO DRAM Performance Figures                                                        | 39 |

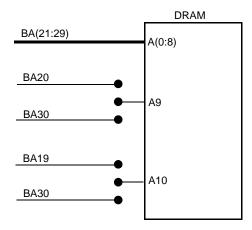

| DRAM ADDRESS CONNECTIONS                                                            | 41 |

| Flash Memory Performance Figures                                                    | 43 |

| SDRAM ADD and MPC852T Pin Correlations                                              | 44 |

| SDRAM - MPC Connections                                                             | 45 |

| Estimated SDRAM Performance Figures                                                 | 45 |

| SDRAM Mode Register Programming                                                     | 47 |

| BCSR0 Description                                                                   | 52 |

| BCSR1 Description                                                                   | 54 |

| PCCVCC(0:1) Encoding                                                                | 55 |

| PCCVPP(0:1) Encoding                                                                | 55 |

| BCSR2 Description                                                                   | 56 |

| Flash Presence Detect (4:1) Encoding                                                | 56 |

| DRAM Presence Detect (2:1) Encoding                                                 | 56 |

| DRAM Presence Detect (4:3) Encoding                                                 | 57 |

| BCSR3 Description                                                                   | 58 |

| FLASH Presence Detect (7:5) Encoding                                                | 58 |

| BCSR4 Description                                                                   | 58 |

| Parallel Host Port Connector's Signal Description with EPP I/F                      | 60 |

| Parallel Host Port Connector's Signal Description with Serial Command Converter I/F | 60 |

| EPP Register Interface                                                              | 61 |

| Off-board Application Maximum Current Consumption                                   | 64 |

| P1: ADD, Data and PCMCIA Expansion Connector Interconnect Signals                   | 67 |

| P2: I/O Port Expansion Interconnect Signals                                         | 71 |

| P3: Logic Analyzer Interconnect Signals                                             | 74 |

| P4: Logic Analyzer Interconnect Signals                                             | 75 |

| P6: Logic Analyzer Interconnect Signals                                             | 76 |

| P7: Logic Analyzer Interconnect Signals                                             | 76 |

| P8: Logic Analyzer Interconnect Signals                                             | 77 |

| P11: Logic Analyzer Interconnect Signals                       | 78 |

|----------------------------------------------------------------|----|

| P15: Logic Analyzer Interconnect Signals                       | 79 |

| P5: PCMCIA Connector Interconnect Signals                      | 80 |

| P9, P10: 100/10Base-T Ethernet Port Interconnect Signals       | 83 |

| P12: External Debug Port Controller Input Interconnect Signals | 84 |

| P13: 12V Power-In Interconnect Signals                         | 84 |

| P17B: RS232 Interconnect Signals                               | 85 |

| P18, P19 - JTAG connector for Altera programing.               | 86 |

| MPC852TADS Part List                                           | 87 |

## **List Of Figures**

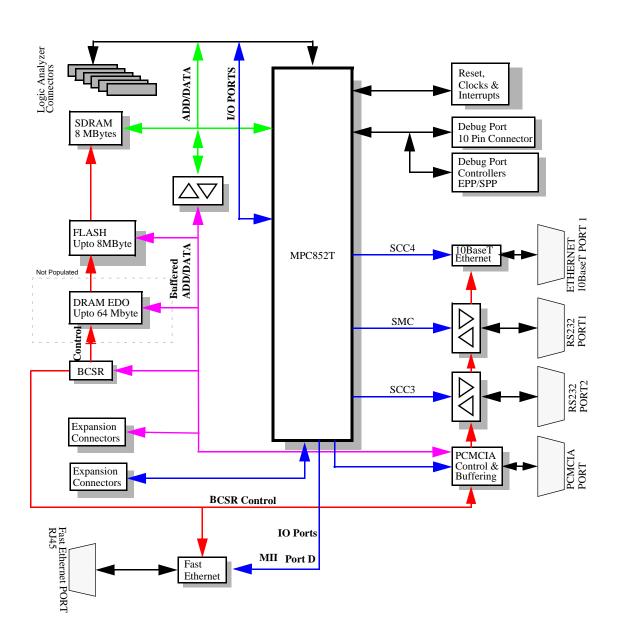

| MPC852TADS Block Diagram                                         | 4   |

|------------------------------------------------------------------|-----|

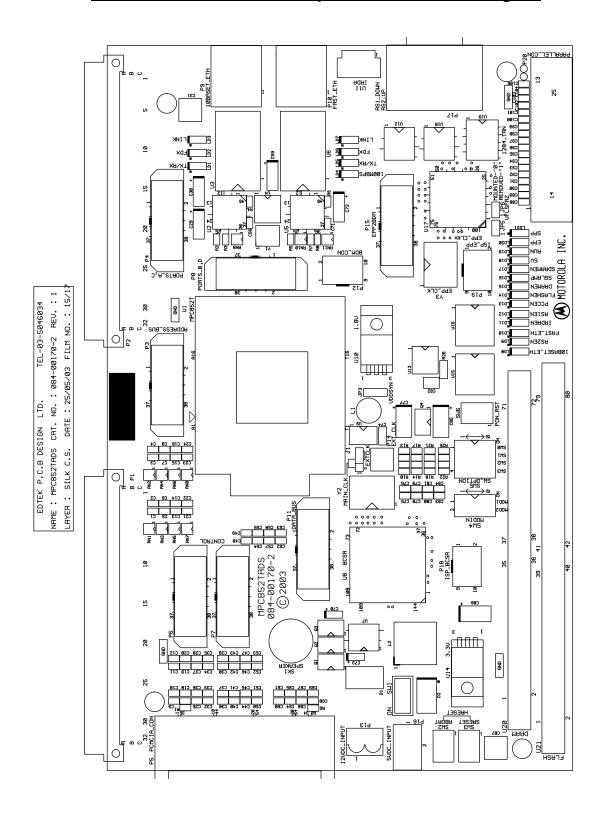

| MPC852TADS Top-Side Part Location Diagram                        | 6   |

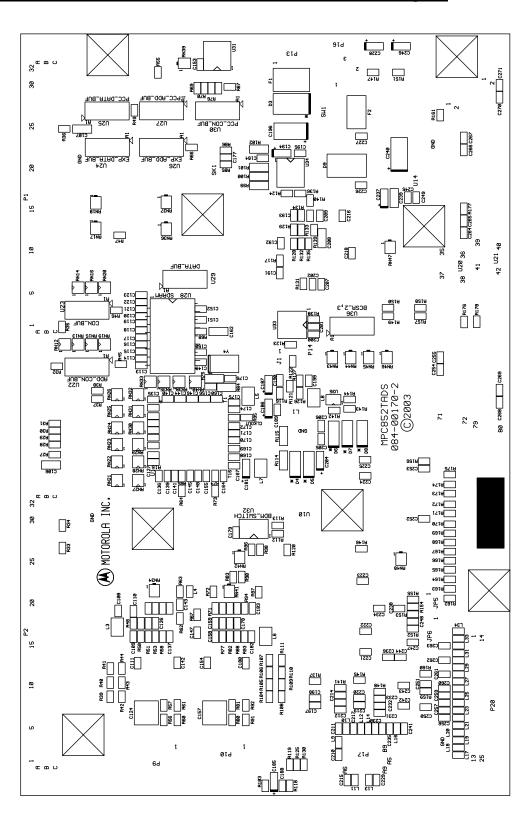

| MPC852TADS Bottom-Side Part Location Diagram                     | 7   |

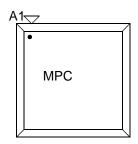

| MPC TOP-VIEW                                                     | 8   |

| Clock Source Selection - J1                                      | 8   |

| Modin Selection - SW4                                            | 9   |

| S/W Option - SW5                                                 | 10  |

| Host-Controlled Operation Scheme with External Command Converter | 11  |

| Host-Controlled Operation on board Command Converter schem       | 11  |

| Standalone operation schem                                       | 12  |

| BDM Debug Connector - P12                                        | 12  |

| +12V Power Connector - P13                                       | 13  |

| P16: +5V Power Connector                                         | 13  |

| RS-232 Serial Port Connectors: P17A & P17B                       | 14  |

| Parallel host connector with EPP I/F - P20                       | 14  |

| Parallel host connector in serial mode - P20                     | 15  |

| Memory SIMM Installation                                         | 16  |

| Refresh Scheme                                                   | 40  |

| DRAM Address Line Switching Scheme                               | 41  |

| Flash Memory SIMM Architecture                                   | 42  |

| SDRAM Connection Scheme                                          | 46  |

| PCMCIA Port Configuration                                        | 50  |

| Standard BDM Debug Port Connector                                | 62  |

| MPC852TADS Power Scheme                                          | 64  |

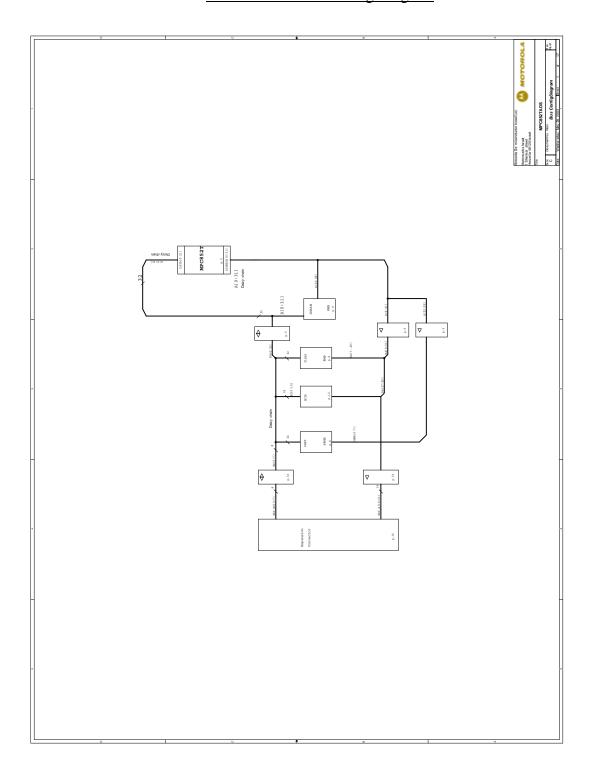

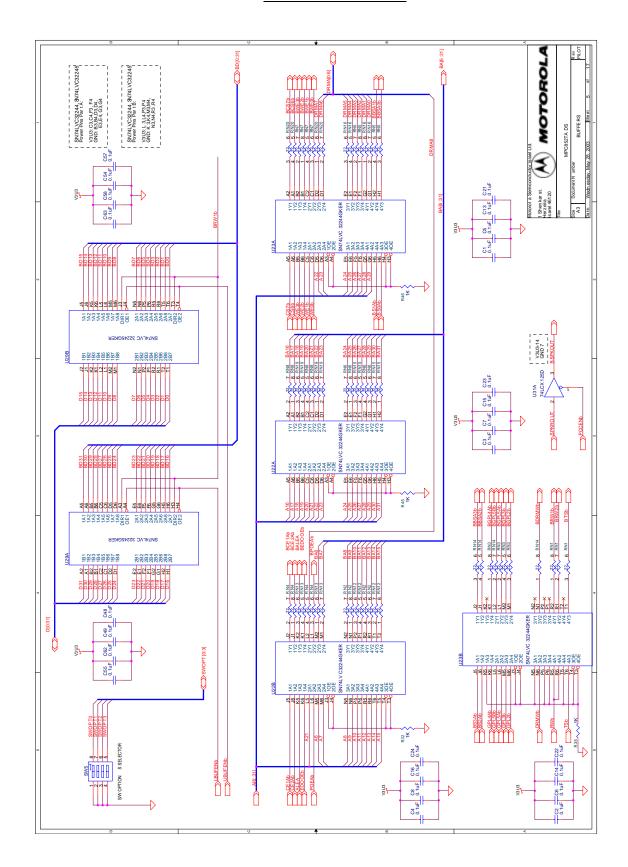

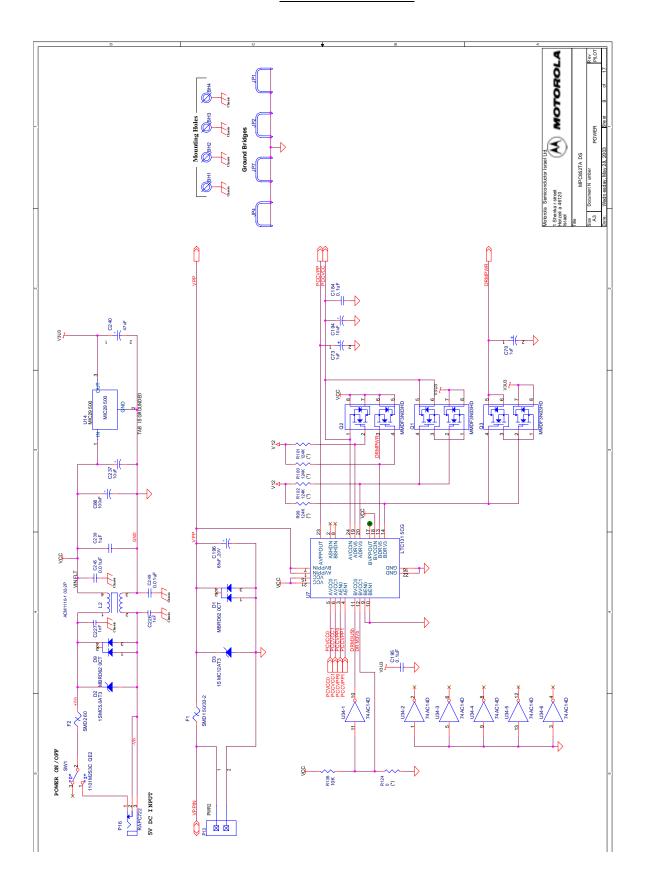

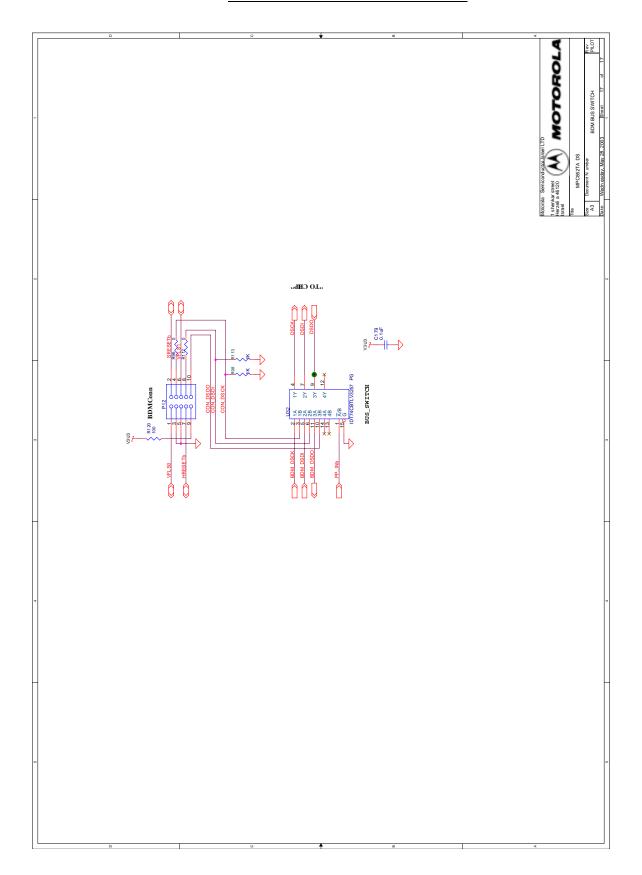

| Bus Config Diagram                                               | 92  |

| Table of Contents                                                | 93  |

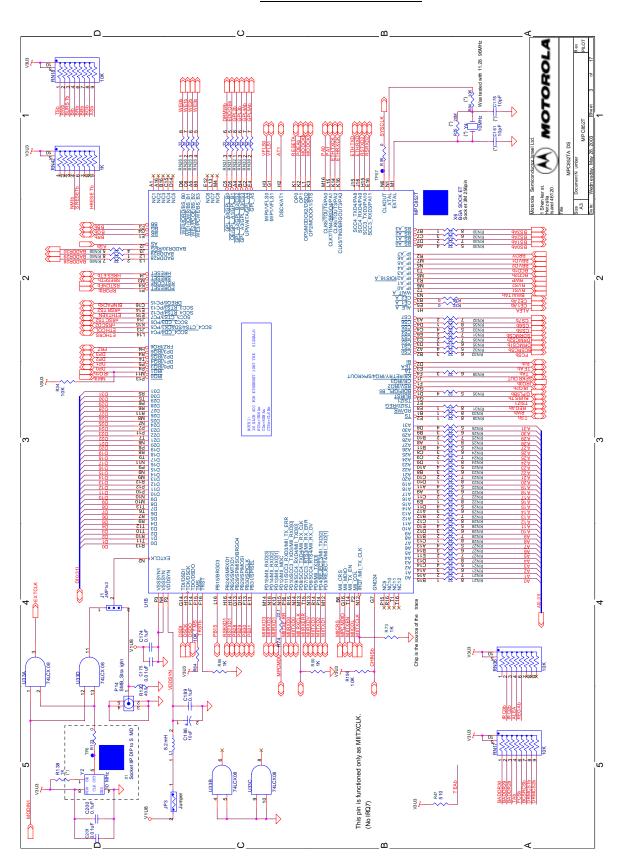

| MPC852T                                                          | 94  |

| SDRAM                                                            | 95  |

| Buffers                                                          | 96  |

| Flash & DRAM                                                     | 97  |

| PCMCIA I/F                                                       | 98  |

| Devices Power                                                    | 99  |

| Power                                                            | 100 |

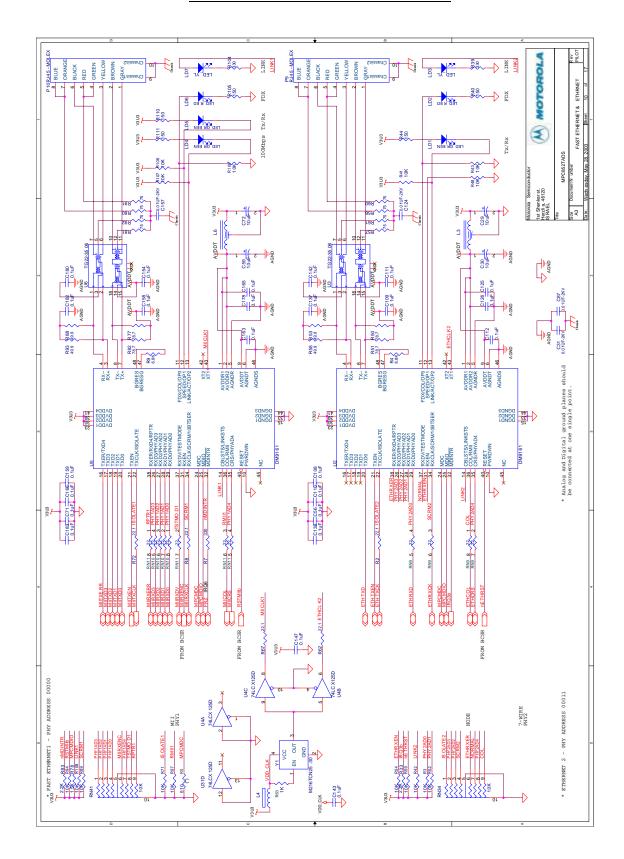

| Fast Ethernet & Ethernet                                         | 101 |

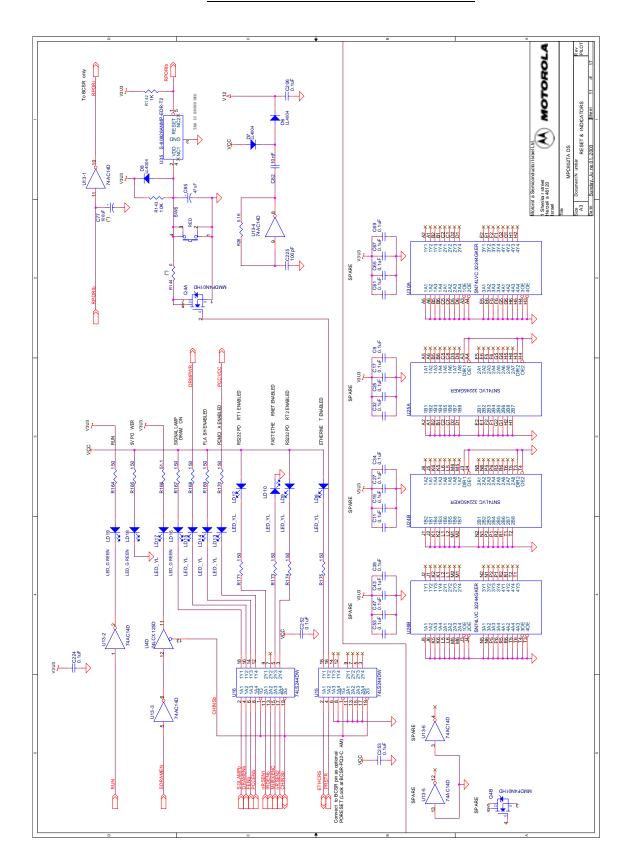

| RESET & INDICATORS                                               | 102 |

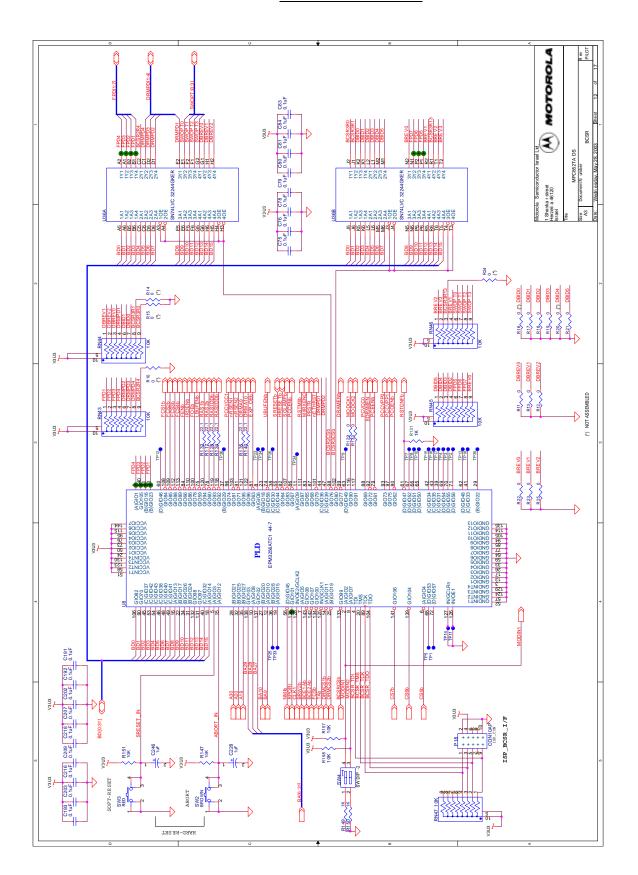

| BCSR                                                             | 103 |

| RS232 & CLOCK                                                    | 104 |

| LOGIC ANALYZER                                                   | 105 |

| EXPANSION CONNECTROS                                             | 106 |

| HOST I/F                                                         | 107 |

| RDM RUS SWITCH                                                   | 108 |

#### **General Information**

## 1 - General Information

#### 1•1 MPC852TADS Introduction and Goals

This operation guide for the MPC852TADS board contains operational, functional and general information. The MPC852T is a Power PC architecture based derivative of Motorola MPC860 Quad Integrated Communication Controller (PowerQuicc<sup>TM</sup>). As such the MPC852TADS board is a derivative of the MPC866ADS. It is designed to serve as a platform for both software and hardware development using the MPC852T processor.

On-board resources and the associated debugger enable developers to perform a variety of tasks: download and run code; set breakpoints; display memory and registers; and, connect proprietary h/w via the expansion connectors. All these features may be incorporated into a selected system using the MPC852T processor.

The MPC852TADS board may be used as a demonstration tool. For example, the application software may be burned<sup>A</sup> into its flash memory and run in exhibitions.

### 1•2 List of Abbreviations

- ADS MPC852TADS, the document subject

- BCSR Board Control & Status Register

- BGA Ball Grid Array

- GPCM General Purpose Chip-Select Machine

- GPL General Purpose Line (associated with UPM)

- SIMM Single In-line Memory Module

- UPM User Programmable Machine

#### 1•3 Related Documentation

- MPC866 Family User Manual

- Davicom 10/100Mbps Fast Ethernet DM9161E Transceiver

- IEEE Std. 1284-1994 Standard

#### 1•4 SPECIFICATIONS

The MPC852TADS specifications are given in TABLE 1-1.

TABLE 1-1. MPC852TADS Specifications

| CHARACTERISTICS                               | SPECIFICATIONS                                         |

|-----------------------------------------------|--------------------------------------------------------|

| Power requirements (no other boards attached) | +5V DC @ 1.4 A (typical), 3 A (maximum)<br>+12V DC@1A. |

| Microprocessor                                | MPC852T running @ 66 MHz bus speed                     |

A. Either on-board or off-board.

1

#### **General Information**

## TABLE 1-1. MPC852TADS Specifications

| CHARACTERISTICS                                                                         | SPECIFICATIONS                                                                                                                      |  |  |

|-----------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Addressing                                                                              |                                                                                                                                     |  |  |

| Total Address Range: Flash Memory Dynamic RAM optional not populated.  Synchronous DRAM | 4 GB 2 MB, 32-bit wide expandable to 8 MB 4 MB, 32-bit wide EDO SIMM, optional support for up to 32 MB, EDO or FPM SIMM 8 MB, SDRAM |  |  |

| Operating temperature                                                                   | 0°C - 30°C                                                                                                                          |  |  |

| Storage temperature                                                                     | -25°C to 85°C                                                                                                                       |  |  |

| Relative humidity                                                                       | 5% to 90% (non-condensing)                                                                                                          |  |  |

| Dimensions:  Length  Width  Thickness                                                   | 9.173" (233 mm)<br>5.9" (150 mm)<br>0.063" (1.6 mm)                                                                                 |  |  |

#### **General Information**

#### 1.5 MPC852TADS Features

- o The MPC852TADS is compatible with the old MPC86xADS board.

- o The MPC852T, when mounted on a BGA socket, runs at 66 MHz bus frequency.

- o 8 MB, unbuffered, synchronous DRAM.

- o 4 MB EDO 60nsec delay DRAM SIMM. Support for 4 32 MB FPM or EDO DRAM SIMM with Automatic DRAM SIMM identification. 16-bit data - bus width support. The optional EDO DRAM will not be populated on-board.

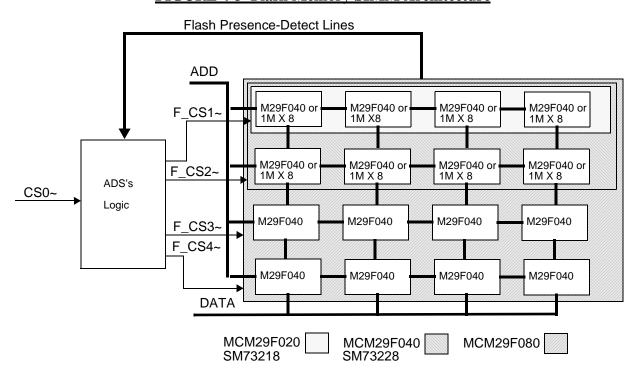

- o 2 MB Flash SIMM. Support for up to 8 MB. 5V or 12V Programmable with Automatic Flash SIMM identification. Can be changed up to 8MB.

- Optional Hard-Reset Configuration Burned in Flash<sup>A</sup>.

- o Dual RS232 port.

- o Fast Ethernet connection to Port-D using Davicom DM9161E.

- o 10-Base-T Port On-board using Davicom DM9161E.

- Memory Disable Option for every local memory map slave.

- o Board Control & Status Register 5 BCSR controlling board operation.

- o External Tool Identification Capability via BCSR.

- o Programmable Hard-Reset Configuration via BCSR.

- 5V only PCMCIA Socket with full buffering, power control and port disable options. Complies with PCMCIA 2.1+ Standard.

- Module Enable Indications in order to control external peripherals, expansion connectors include all the CPM ports & bus signals.

- o On-board Debug Port Controller & EPP/SPP Interface.

- o Push button for Soft- / Hard-B Reset.

- o ABORT button.

- o Single<sup>C</sup> 5V supply.

- o Reverse / Over Voltage Protection for Power Inputs.

- o 3.3V VDDH and 1.8V VDDL are supplied for MPC852T.

3

A. Flash burning available only if also supported on the MPC852T.

B. To activate hard-reset, press BOTH the soft-reset & ABORT buttons.

C. Use 5V single supply unless a 12V supply is required for a PCMCIA card or a 12V programmable Flash SIMM.

#### **General Information**

#### FIGURE 1-1 MPC852TADS Block Diagram

#### **Hardware Preparation and Installation**

## 2 - Hardware Preparation and Installation

#### 2•1 INTRODUCTION

This chapter describes unpacking instructions, hardware preparation and installation instructions for the MPC852TADS.

#### 2•2 UNPACKING INSTRUCTIONS

#### **NOTE**

If the shipping carton arrives damaged request that the carrier agent be present at the time of equipment unpacking and inspection.

Remove equipment from the shipping carton. Consult the packing list and verify that all listed items are present. Save the packing material in the instance that either storage or reshipment of the equipment should become necessary.

#### **CAUTION**

AVOID TOUCHING AREAS OF INTEGRATED CIRCUITRY AS STATIC DISCHARGE CAN DAMAGE CIRCUITS.

#### 2•3 HARDWARE PREPARATION

Prior to installation it may be necessary to change the DIP switch settings or jumpers in order to achieve both the desired configuration and ensure proper operation of the MPC852TADS board. FIGURE 2-1 "MPC852TADS Top-Side Part Location Diagram" illustrates the location of the switches, LEDs, DIP switches, jumpers and connectors. The factory tested boards are delivered with default DIP switch settings. The default settings are described in the paragraphs below.

Parameters relating to the below listed features may be changed:

- MPC Clock Source

- Host Controlled Operation

- PCMCIA Enable

- MPC I/O port connected to Expansion Connector

5

### **Hardware Preparation and Installation**

#### FIGURE 2-1 MPC852TADS Top-Side Part Location Diagram

### **Hardware Preparation and Installation**

#### FIGURE 2-2 MPC852TADS Bottom-Side Part Location Diagram

EDTEK P.C.B DESIGN LTD. TEL-03-5046034

NAME : MPC852TADS CAT. NO. : 084-00170-2 REU. : 1

LAYER : SILK P.S. DATE : 25/05/03 FILM NO. : 16/17

#### **Hardware Preparation and Installation**

#### 2•3•1 MPC Replacement of U1

Turn off the power prior to replacing the MPC. Note the location of the original MPC A1 pin when replacing a U1 with another MPC. Set the new MPC in the same direction as the previous one.

#### FIGURE 2-3 MPC TOP-VIEW

#### 2•3•2 Clock Source Selection - J1

The clock source for the MPC is selected by J1. When a jumper is placed between position 1-2, On board Clock is selected either 10MHz Clock generator or 10MHz Crystal resonator depending on SW4 position.

When a jumper is placed between position 2-3, External Clock is selected.

#### FIGURE 2-4 Clock Source Selection - J1

#### 2•3•3 Modin Selection - SW4

The on board clock source for the MPC is selected by SW4. The on-board 10MHz crystal resonator connected between EXTAL and XTAL MPC pins, becomes the clock source when SW4[1-2] = ['ON','ON'] or ['ON','OFF'] and the ADS is powered-up. However, when SW4[1-2] = ['OFF','ON'] or ['OFF','OFF'] but the ADS is powered-up, then the on-board 10MHz clock generator connected to EXTCLK MPC pin, becomes the clock source. Clkout is calculated by CLK\_IN, 10MHz, multiplied by the PLL multiplication factor. See TABLE 2-1. "Power ON Reset DPLL Configuration" on page 9.

#### **NOTE**

Crystal resonator circuit is not assembled on board.

#### **Hardware Preparation and Installation**

FIGURE 2-5 Modin Selection - SW4

10MHz Clock generator 10MHz Clock generator 10MHz Crystal Oscillator 10MHz Crystal Oscillator

TABLE 2-1. Power ON Reset DPLL Configuration

| MODCK[1-2] | Default at Power On<br>Reset |      | DPLL and<br>Interface Input | System Frequency                       |

|------------|------------------------------|------|-----------------------------|----------------------------------------|

|            | MFI[12-15] PDF[27-30]        |      |                             |                                        |

| 00         | 8 0000                       |      | OSCM Freq <sup>a</sup>      | 40MHz for 10MHz input Crystal          |

| 01         | 15 0000                      |      | OSCM Freq                   | 75MHz for 10MHz input Crystal          |

| 10         | 8                            | 0011 | EXTCLK Freq                 | 1:1 Mode <sup>b</sup>                  |

| 11         | 15                           | 0000 | EXTCLK Freq                 | 75MHz for 10MHz input Clock Oscillator |

a. OSCM Freq means the Frequency between EXTAL and XTAL MPC pins.

#### 2•3•4 Software Option - SW5

SW5 is a 4-Dip Switch. This switch is connected over SWOPT[0-3] lines which are available at BCSR2. S/W Options may be manually selected, according to SW5 state. SW5 is factory set to all'ON'.

9

b. If Clock in is 10MHz Clock Oscillator, the System Frequency is 10MHz.

# Hardware Preparation and Installation FIGURE 2-6 S/W Option - SW5

#### 2•4 INSTALLATION INSTRUCTIONS

Boards are shipped without DRAM EDO. Since all the SW is based on the DRAM it is necessary that the user change BR2, BR3, BR4 and OR4. In BR2, BR3 the valid bit should be 0 (bit 31), BR4 = 0x000000C1 and OR4 should be 0xFC800A00. This configuration will map the SDRAM to ADD 0 & 0x3000000 for 8MB. Once configured, the MPC852TADS may be installed as per the required working environment:

- Host Controlled Operation

- Standalone

### 2•4•1 Host Controlled Operation

For host-controlled operation, a host computer controls the board via the BDM Debug Port, which is a subset of the JTAG port. This configuration serves for extensive debugging using an on-host debugger. Host computer connects with the board as follows:

- or through External Command Converter provided by a third party -

Macraigor System.

- or through On-Board Serial Command Converter<sup>A</sup> -

No needs an external part.

- or through On-Board Enhanced Parallel Port (EPP) Converter<sup>A</sup> -

No needs an external part.

A. For FUTURE USE

#### **Hardware Preparation and Installation**

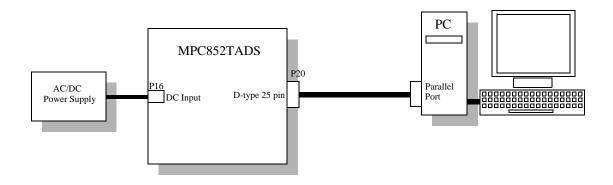

## FIGURE 2-7 Host-Controlled Operation Scheme with External Command Converter

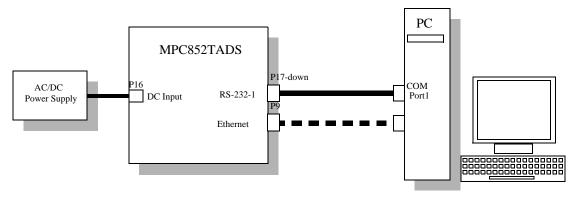

FIGURE 2-8 Host-Controlled Operation on board Command Converter schem

#### 2•4•2 Standalone Operation

In this mode the ADS is not controlled by the host via the debug port. Rather, connection to the host may be made via another port, e.g., RS232 port, Ethernet port, etc. Operations in this mode require that an application be programmed into the board's Flash memory. No memory is required with host-controlled operations.

### **Hardware Preparation and Installation**

#### FIGURE 2-9 Standalone operation schem

#### 2•4•3 10/100-Base-T Ethernet Ports Connection - P9, P10

The 10/100-Base-T port connectors - P9 and P10, are an 8-pin, 90°, receptacle RJ45 connectors. The connection between the 10/100-Base-T ports to the network is done by a standard cable. The pinout of P9 and P10 is described in TABLE 5-11. "P9, P10: 100/10Base-T Ethernet Port Interconnect Signals" on page 83.

#### 2•4•4 BDM Debug Port Connector - P12

Users may also control the board via the Bdm debug port connector. Currently, the majority of control SW use this connector via a command converter box connected to the PC parallel port.

#### FIGURE 2-10 BDM Debug Connector - P12

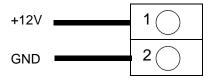

#### 2•4•5 +12V Power Supply Connection - P13

The MPC852TADS requires a +12 Vdc @ 1 A max power supply for either the PCMCIA channel Flash programming capability or the 12V programmable Flash SIMM. As long as there is no need to program either a 12V programmable PCMCIA flash card or a 12V programmable Flash SIMM then the MPC852TADS works properly without a +12V power supply.

Connect the +12V power supply to connector P13 as shown below:

#### **Hardware Preparation and Installation**

#### FIGURE 2-11 +12V Power Connector - P13

P13 is a 2-terminal block power connector with power plug. The plug is designed to accept 14 to 22 AWG wires though the use of between 14 to 18 AWG wires is recommended.

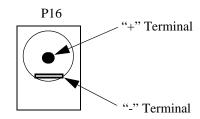

#### 2•4•6 +5V Power Supply Connection - P16

The MPC852TADS requires a +5 VDC @ 3A max power supply for operation. Connect the +5V power supply to connector P16 as shown below:

#### FIGURE 2-12 P16: +5V Power Connector

P16 is a power jack connector.

#### **NOTE**

Hardware applications may be connected to the MPC852TADS via expansion connectors P1 & P2. Power consumption should be considered when a power supply is connected to the MPC852TADS. Thus when adding HW to the expansion connectors note that the new addition will not consume more power than 1A.

#### 2•4•7 Terminal to MPC852TADS RS-232 Connection - P17

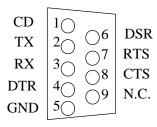

RS232 equipment and serial RS232 terminals may be connected to P17A and P17B RS-232 connectors. The RS-232, shown in FIGURE 2-13 "RS-232 Serial Port Connectors: P17A & P17B", is a female, 9-pin, stacked D-type connector.

The connectors are arranged in a manner that allows for a 1:1 connection via a flat cable to the serial port of an a personal computer.

#### **Hardware Preparation and Installation**

#### FIGURE 2-13 RS-232 Serial Port Connectors: P17A & P17B

Note: On the MPC852TADS, the RTS line (pin #7) is not connected.

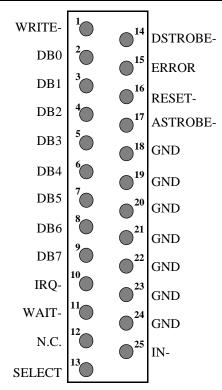

#### 2•4•8 Parallel Host Connector in EPP I/F - P20

The MPC852TADS' P20-EPP interface connector is a male, 25-pin, D-type connector. The connection between the MPC852TADS and the host computer is by 25-line flat cable. This connector enables connection to host computer when using On board serial command converter or EPP converter. When connection to host is made via P20, the capability of working with an external BDM Debug connector is disabled. FIGURE 2-14 "Parallel host connector with EPP I/F - P20" below shows the pin configuration of the connector when choosing EPP Mode transfer.

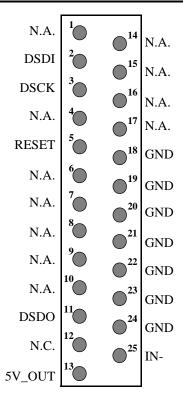

FIGURE 2-15 "Parallel host connector in serial mode - P20" below shows the pin configuration of the same connector when choosing Serial Mode transfer.

FIGURE 2-14 Parallel host connector with EPP I/F - P20

#### **Hardware Preparation and Installation**

#### FIGURE 2-15 Parallel host connector in serial mode - P20

#### 2•4•9 Memory Installation

The MPC852TADS has two types of memory SIMM:

- Dynamic Memory SIMM: will not be populated, only the socket will be soldered.

- Flash Memory SIMM.

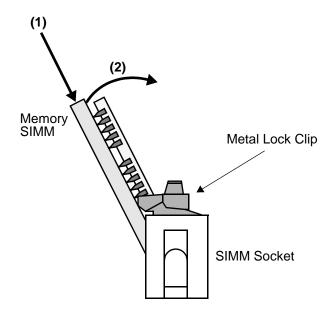

Installation of a memory SIMM: remove from packaging; place diagonally in its socket - difficult to err as the Flash socket has 80 contacts, while the DRAM socket only has 72; twist to a vertical position until the metal lock clips are locked. See FIGURE 2-16 "Memory SIMM Installation".

#### **Hardware Preparation and Installation**

#### **CAUTION**

Near the #1 pin the memory SIMMs have an alignment nibble. It is essential to correctly align the memory before twisting as damage may result to both the memory SIMM and its socket.

## **FIGURE 2-16 Memory SIMM Installation**

#### **OPERATING INSTRUCTIONS**

## 3 - OPERATING INSTRUCTIONS

#### 3•1 INTRODUCTION

Information necessary for using the MPC852TADS in both host-controlled and standalone configurations is detailed in this chapter. The information includes controls and indicators, memory map details and board software initialization.

#### 3•2 CONTROLS AND INDICATORS

The MPC852TADS features the switches and indicators noted in the following sub-sections.

#### 3•2•1 ABORT Switch, SW2

The SW2 ABORT switch is used for aborting program execution. This is done by issuing a level 0 interrupt to the MPC. There is no resident debugger with the MPC852TADS. As such, if the ADS is in standalone mode, it is the users responsibility to provide a means of handling the interrupt. The Abort switch signal is debouncing and cannot be disabled by software.

#### 3•2•2 SOFT RESET Switch, SW3

The SW3 SOFT RESET switch performs Soft Reset on the MPC internal modules while maintaining MPC configuration (clock & chip-select) Dram and SDram contents. The switch signal is debouncing and cannot be disabled by software. Upon completion of the Soft Reset sequence, the Soft Reset configuration is sampled prior to becoming valid.

#### 3•2•3 HARD RESET Switches, SW2 & SW3

When both the SW2 and SW3 switches are depressed simultaneously then HARD RESET is generated on the MPC. When the MPC undergoes Hard Reset it must be re initialized as its configuration is lost - including data stored in the DRAM or SDRAM. Upon completion of the Hard Reset sequence, the Hard Reset configuration stored in BCSR0 becomes valid.

#### 3•2•4 Modin Selection, SW4

The on board clock source for the MPC is selected by SW4. The on-board 10MHz crystal resonator<sup>A</sup> connected between EXTAL and XTAL MPC pins, becomes the clock source when SW4[1-2] = ['ON','ON'] or ['ON','OFF'] and the ADS is powered-up. However, when SW4[1-2] = ['OFF','ON'] or ['OFF','OFF'] but the ADS is powered-up, then the on-board 10MHz clock generator connected to EXTCLK MPC pin, becomes the clock source. Clkout is calculated by CLK\_IN, 10MHz, multiplied by the PLL multiplication factor. See TABLE 2-1. "Power ON Reset DPLL Configuration" on page 9.

#### 3•2•5 Software Options Switch, SW5

The SW5 SOFTWARE OPTIONS switch is a 4-switch DIP switch. The SW5 is connected over SWOPT(0:3) lines available at BCSR. Software options may be manually selected according to the state of the SW5.

#### 3•2•6 Power-On RESET Switch, SW6

The Power-On RESET switch SW6 performs Power-On reset to the MPC852T, as if the power was re-applied to the

A. Crystal resonator is not assembled on board.

#### **OPERATING INSTRUCTIONS**

ADS. When the MPC is reset that way, all configuration and all data residing in volatile memories are lost. After PORST signal is negated, the MPC re-acquires the power-on reset and hard-reset configuration data from the hard-reset configuration source. (Flash / BCSR).

#### 3•2•7 GND Bridges

The 4 GND bridges on the MPC852TADS are intended to assist in general measurements and logic-analyzer connections.

#### **WARNING**

Use only INSULATED GND clips when connecting to a GND bridge. Failure to do so may result in permanent damage to the MPC852TADS.

#### 3•2•8 Ethernet 10Base-T. ETH TX/RX, LD1

The green ETH TX/RX LED indicates that the Ethernet port, Davicom DM9161E on SCC4, is transmitting or receiving data via the 10 Base-T port.

#### 3•2•9 Ethernet Full Duplex Indicator, LD2

The red ETH FDX LED indicates that the Ethernet port, Davicom DM9161E on SCC4, is in Full Duplex operation mode.

#### 3•2•10 Ethernet LINK Indicator, LD3

The yellow ETH Twisted Pair LINK LED indicates, that there is a good link integrity on the 10-Base-T port. LD3 is off when the link integrity fails.

#### 3•2•11 Fast Ethernet 100Mbps Indicator, LD4

The green FAST ETH 100Mpbs LED indicates that the Fast Ethernet port, Davicom DM9161E on Port D is in 100 Mbps operation mode.

#### **3•2•12** Fast Ethernet 10/100Base-T. TX/RX, LD5

The green FAST ETH TX/RX LED indicates that the Fast Ethernet port, Davicom DM9161E on Port D, is transmitting or receiving data via the 10/100 Base-T port.

#### 3•2•13 Fast Ethernet Full Duplex Indicator, LD6

The red FAST ETH FDX LED indicates that the Fast Ethernet port, Davicom DM9161E on Port D, is in Full Duplex operation mode.

#### 3•2•14 Fast Ethernet LINK Indicator, LD7

The yellow FAST ETH Twisted Pair LINK LED indicates, that there is a good link integrity on the 10/100-Base-T port. LD7 is off when the link integrity fails.

#### OPERATING INSTRUCTIONS

#### 3•2•15 Ethernet 10Base-T. ETH ON, LD8

The yellow ETH ON LED indicates that the Ethernet port transceiver, Davicom DM9161E, is active.

#### 3•2•16 RS232 Port 2 ON, LD9

The yellow RS232 Port 1 ON LED signifies that the RS232 transceiver, connected to SCC3, is active and that communication via that medium is allowed. The RS232 transceiver is in shutdown mode when unlit - an indication that the associated MPC pins may be used off-board via the expansion connectors.

#### 3•2•17 Fast Ethernet 10/100Base-T. ON, LD10

The yellow FAST ETH ON LED indicates that the Fast Ethernet port transceiver, Davicom DM9161E, is active. The Davicom outputs pins are in tri-states when unlit - an indication that the associated Port D pins may be used off-board via the expansion connectors.

#### 3•2•18 RS232 Port 1 ON, LD12

The yellow RS232 Port 1 ON LED signifies that the RS232 transceiver, connected to SMC1, is active and that communication via that medium is allowed. The RS232 transceiver is in shutdown mode when unlit - an indication that the associated MPC pins may be used off-board via the expansion connectors.

#### 3•2•19 PCMCIA ON, LD13

The yellow PCMCIA ON LED indicates the following:

- 1) Address & strobe buffers are driven towards the PCMCIA card.

- 2) Data buffers are driven to / from the PCMCIA card whenever CE1A~ or CE2A~ signals are asserted.

- 3) Card status lines are driven towards the MPC from the PCMCIA card.

When unlit it indicates that the above noted buffers are tri-stated and that the pins associated with the PCMCIA channel A may be used off-board via the expansion connectors.

#### 3•2•20 FLASH ON, LD14

The yellow FLASH ON LED indicates that the FLASH SIMM has been enabled in the BCSR1 register. For example, accessing the CS0~ address space will hit the Flash memory. When unlit the Flash has been disabled.

#### 3•2•21 DRAM ON, LD15

The yellow DRAM ON LED indicates that the DRAM SIMM has been enabled in BCSR1 and that accessing CS2~ (or CS3~) will hit on the DRAM. When unlit the DRAM has been disabled in BCSR1.

#### 3•2•22 SGLAMP ON, LD16

The green SGLAMP LED indicates that this signal is active (low). When inactive there is no LED light. The LED is used for software signalling. Controlling the led is done via BCSR4[3].

#### OPERATING INSTRUCTIONS

#### 3•2•23 SDRAM ON, LD17

The yellow SDRAM ON LED indicates that the SDRAM has been enabled in BCSR1 and that accessing CS4~ will hit on the SDRAM. When unlit the SDRAM has been disabled in BCSR1.

####

The green 5V LED indicates the presence of a +5V supply at P16.

#### 3•2•25 RUN Indicator, LD19

The green RUN LED indicates that the MPC <u>isn't</u> in debug mode.

### 3•2•26 EPP Indicator, LD20<sup>A</sup>

The yellow Enhanced Parallel Port connection LED indicates that the board is connected directly to the Pc's parallel port using EPP transfer mode and the BDM Debug connector (P12) is irrelevant.

### 3•2•27 SPP Indicator, LD21<sup>A</sup>

The yellow SPP connection LED indicates that the board is connected directly to the Pc's parallel port using SPP transfer mode and the BDM Debug connector (P12) is irrelevant.

#### 3•3 MEMORY MAP

All access to MPC852TADS memory slaves is controlled by the MPC's memory controller. As a consequence, the user may reprogram the memory map. The debug station performs Hard Reset. Then the debugger checks for the existence, size, delay and type of EDO DRAM and FLASH memory SIMMs that are mounted on board. Accordingly the debugger initializes chip-selects. The SDRAM, DRAM and FLASH memory respond to all types of memory access. For example: user / supervisory; program / data; and DMA.

Following is a memory map description for 2 options: Compatible Mode and MPC852TADS New Mode.

The Compatible Mode uses an EDO DRAM and 8MB SDRAM. Further, all the programmable registers remain the same - the memory map is the same as that of the MPC8xxFADS board with the *exception* of OR4 Mask Register bits. The latter are changed according to SDRAM size to 0xFF80.

In the MPC852TADS New Mode the EDO DRAM is not used and consequently the SDRAM is mapped differently. See TABLE 3-1. "Memory Map in MP852TADS New Mode," and TABLE 3-2. "Memory Map in MPC852TADS Compatible Mode". The following programmable changes are necessary in order to work on the board in the MPC852TADS New Mode:

- Programming BR2, BR3 Base Address bits for EDO DRAM aren't valid. The L-bit should be cleared.

- Programming OR4 Mask Register bits for SDRAM should be changed according to SDRAM size. This where the 2 MS bits are not masked. 8MB SDRAM, OR4 Mask bits = 0xFC80. In this case users may view address 0 and also add 30000000 they are the same word in the memory. Users must also change the BIH to 0.

A. For FUTURE Use

#### **OPERATING INSTRUCTIONS**

TABLE 3-1. Memory Map in MP852TADS New Mode,

| ADDESS RANGE                    | Memory Type                      | Device Type |             |            | Port<br>Size |                 |

|---------------------------------|----------------------------------|-------------|-------------|------------|--------------|-----------------|

| 00000000 - 007FFFF <sup>a</sup> | SDRAM                            | 8MByte      |             |            |              | 32              |

| 02000000 - 020FFFF              | Empty Space                      |             |             |            |              |                 |

| 02000300 - 020003FF             | Control<br>Register              |             |             |            |              |                 |

| 02100000 - 02107FFF             | BCSR(0:4)b                       |             |             |            |              | 32 <sup>c</sup> |

| 02100000 - 02107FE3             | BCSR0                            |             |             |            |              |                 |

| 2100004 - 02107FE7              | BCSR1                            |             |             |            |              |                 |

| 2100008 - 02107FEB              | BCSR2                            |             |             |            |              |                 |

| 210000C - 02107FEF              | BCSR3                            |             |             |            |              |                 |

| 2100010 - 02107FF3              | BCSR4                            |             |             |            |              |                 |

| 02108000 - 021FFFFF             | Empty Space                      |             |             |            |              |                 |

| 02200000 - 02207FFF             | MPC Internal<br>MAP <sup>d</sup> |             |             |            |              | 32              |

| 02208000 - 027FFFF              | Empty Space                      |             |             |            |              |                 |

| 02800000 - 029FFFFF             | Flash SIMM                       | MCM29F020   | MCM29F040   | MCM29F080  |              | 32              |

| 02A00000 - 02BFFFFF             |                                  |             | SM732A1000A | SM732A2000 |              | 32              |

| 02C00000 - 02FFFFF              |                                  |             |             |            |              | 32              |

| 03000000 - 037FFFF              | SDRAM <sup>a</sup>               | (for 8MB)   |             |            |              | 32              |

| 03400000 - FFFFFFF              | Empty Space                      |             |             |            |              |                 |

- a. 0 0x007F\_FFFF, 0x0300\_0000 0x037F\_FFFF are both mapped to SDRAM (8MB).

- b. The device appears repeatedly in multiples of its size, e.g., BCSR0 appears at memory locations 2100000, 2100020, 2100040..., while BCSR1 appears at 2100004, 2100024, 2100044... and so on.

- c. Only upper 16-bit (D0-D15) are used.

- d. Refer to the relevant MPC User Manual for a complete description of the MPC internal memory map.

#### TABLE 3-2. Memory Map in MPC852TADS Compatible Mode

| ADDESS RANGE       | Memory Type | Device Type             |                         |                         | Port<br>Size            |    |

|--------------------|-------------|-------------------------|-------------------------|-------------------------|-------------------------|----|

| 00000000 - 003FFFF | DRAM SIMM   | MB321Bx <sup>a</sup> 08 | MB322Bx <sup>a</sup> 08 | MC324Cx <sup>a</sup> 00 | MB328Cx <sup>a</sup> 00 | 32 |

| 00400000 - 007FFFF |             |                         |                         |                         |                         | 32 |

| 00800000 - 00FFFFF |             |                         |                         |                         |                         | 32 |

| 01000000 - 01FFFFF |             |                         |                         |                         |                         | 32 |

#### **OPERATING INSTRUCTIONS**

### TABLE 3-2. Memory Map in MPC852TADS Compatible Mode

| ADDESS RANGE        | Memory Type                      | Device Type |                        |           | Port<br>Size    |

|---------------------|----------------------------------|-------------|------------------------|-----------|-----------------|

| 02000000 - 020FFFF  | Empty Space                      |             |                        |           |                 |

| 02000300 - 020003FF | Control<br>Register              |             |                        |           |                 |

| 02100000 - 02107FFF | BCSR(0:4) <sup>b</sup>           |             |                        | <u> </u>  | 32 <sup>c</sup> |

| 02100000 - 02107FE3 | BCSR0                            |             |                        |           |                 |

| 2100004 - 02107FE7  | BCSR1                            |             |                        |           |                 |

| 2100008 - 02107FEB  | BCSR2                            |             |                        |           |                 |

| 210000C - 02107FEF  | BCSR3                            |             |                        |           |                 |

| 2100010 - 02107FF3  | BCSR4                            |             |                        |           |                 |

| 02108000 - 021FFFFF | Empty Space                      |             |                        |           |                 |

| 02200000 - 02207FFF | MPC Internal<br>MAP <sup>d</sup> |             |                        |           | 32              |

| 02208000 - 027FFFF  | Empty Space                      |             |                        |           |                 |

| 02800000 - 029FFFFF | Flash SIMM                       | MCM29F020   | MCM29F040              | MCM29F080 | 32              |

| 02A00000 - 02BFFFFF |                                  |             | SM732A1000A SM732A2000 |           | 32              |

| 02C00000 - 02FFFFF  |                                  |             |                        |           | 32              |

| 03000000 - 037FFFFF | SDRAM (for 8MB)                  |             |                        |           | 32              |

| 03400000 - FFFFFFF  | Empty Space                      |             |                        |           |                 |

a. x Œ [B,T]

## 3•4 MPC Register Programming

The MPC offers the following functions on the MPC852TADS:

- 1) DRAM Controller

- 2) SDRAM Controller

- 3) Chip Select Generator

- 4) UART for terminal or host computer connection

- 5) Ethernet Controller

- 6) Fast Ethernet Controller

- 7) General Purpose I/O signals

b. The device appears repeatedly in multiples of its size, e.g., BCSR0 appears at memory locations 2100000, 2100020, 2100040..., while BCSR1 appears at 2100004, 2100024, 2100044... and so on.

c. Only upper 16-bit (D0-D15) are used.

d. Refer to the relevant MPC User Manual for a complete description of the MPC internal memory map.

#### **OPERATING INSTRUCTIONS**

The MPC internal registers must be programmed after Hard Reset. See the following paragraphs for descriptions. The addresses and programming values are in hexadecimal base. For more information and a better understanding of the below noted initialization, refer to the MPC866 User Manual.

#### TABLE 3-3. SIU REGISTER PROGRAMMING

| Register | Init Value[hex] | Description                                                                                                                                                                                                                                                                                                                                                                                                                                |

|----------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SIUMCR   | 01012440        | Internal arbitration. External master arbitration priority - 0. External arbitration priority - 0. PCMCIA channel II pins - PCMCIA. Debug Port on JTAG port pins. FRZ/IRQ6~ - FRZ. Debug register - locked. No parity for non-CS regions. DP(0:3)/ IRQ(3:6)~ pins - DP(0:3). Reservation disabled. SPKROUT - Tri-stated. BS_A(0:3)~ and WE(0:3)~ are only driven on their dedicated pins. GPL_B5~ enabled. GPL_A/B(2:3)~ function as GPLs. |

| SYPCR    | FFFFF88         | Software watchdog timer count - FFFF. Bus-monitor timing FF. Bus-monitor - Enabled. S/W watch-dog - Freeze. S/W watch-dog - disabled. S/W watch-dog (if enabled) causes NMI. S/W (if enabled) not prescaled.                                                                                                                                                                                                                               |

| TBSCR    | 00C2            | No interrupt level. Reference match indications cleared. Interrupts disabled. No freeze. Time-base disabled.                                                                                                                                                                                                                                                                                                                               |

| PISCR    | 0082            | No level for interrupt request. Periodic interrupt disabled. Clear status. Interrupt disabled. FREEZE. Periodic timer disabled.                                                                                                                                                                                                                                                                                                            |

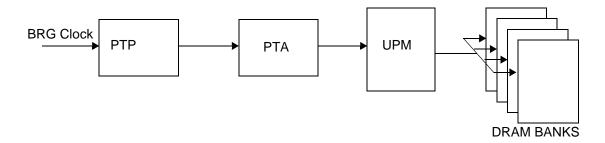

#### 3•4•1 Memory Controller Registers Programming

The MPC852TADS memory controller is initialized for 66 MHz operation. For example, register programming is based on a 66 MHZ timing calculation; an exception being the refresh timer that is initialized for 16.67Mhz. The latter is the lowest frequency at which the ADS may begin to operate. The ADS may be made to *wake-up* at 25MHz<sup>A</sup> but with inefficient initialization for there are too many wait-states inserted. As a consequence, an additional set of initialization is provided in order to support an effective 25MHz operation.

The ADS is initialized at 66Mhz in order to allow for a proper, though not efficient, ADS operation via all available ADS clock frequencies.

A. The refresh rate parameter is the only one initialized to the start-up frequency. Initialization to 66Mhz would have been inadequate for a board is running at a lower frequency. Thus, for the best bus bandwidth availability, the refresh rate should be adapted to the current system clock frequency.

#### **OPERATING INSTRUCTIONS**

#### **Warning**

Due to availability problems with several of the supported memory components, the initialization noted below were not tested with all the parts. Consequently, these initialization may CHANGE during the course of the testing period.

TABLE 3-4. Memory Controller Initialization For 66Mhz with DRAM-EDO

| Register | Device Type                               | Init Value [hex] | Description                                                                       |  |

|----------|-------------------------------------------|------------------|-----------------------------------------------------------------------------------|--|

| BR0      | All Flash SIMMs supported.                | 02800001         | Base at 2800000, 32-bit port size, no parity, GPCM                                |  |

| OR0      | MCM29F020-90                              | FFE00D34         | 2MB block size, all types access, CS early negate, 6 w.s., timing relax           |  |

|          | MCM29F040-90<br>SM732A1000A-9             | FFC00D34         | 4MB block size, all types access, CS early negate, 6 w.s., timing relax           |  |

|          | MCM29F080-90<br>SM732A2000-9              | FF800D34         | 8MB block size, all types access, CS early negate, 6 w.s., timing relax           |  |

|          | MCM29F020-12                              | FFE00D44         | 2MB block size, all types access, CS early negate, 8 w.s., timing relax           |  |

|          | MCM29F040-12<br>SM732A1000A-12            | FFC00D44         | 4MB block size, all types access, CS early negate, 8 w.s., timing relax           |  |

|          | MCM29F080-12<br>SM732A2000-12             | FF800D44         | 8MB block size, all types access, CS early negate, 8 w.s., timing relax           |  |

| BR1      | BCSR                                      | 02100001         | Base at 2100000, 32-bit port size, no parity, GPCM                                |  |

| OR1      |                                           | FFFF8110         | 32 KB block size, all types access, CS early negate, 1 w.s.                       |  |

| BR2      | All DRAM SIMMs supported                  | 00000081         | Base at 0, 32-bit port size, no parity, UPMA                                      |  |

| OR2      | MCM36100/200-60/70                        | FFC00800         | 4MB block size, all types access, initial address multiplexing according to AMA.  |  |

|          | MCM36400/800-60/70<br>MT8/16D432/832X-6/7 | FF000800         | 16MB block size, all types access, initial address multiplexing according to AMA. |  |

| BR3      | MCM36200-60/70                            | 00400081         | Base at 400000, 32-bit port size, no parity, UPMA                                 |  |

|          | MCM36800-60/70<br>MT16D832X-6/7           | 01000081         | Base at 1000000, 32-bit port size, no parity, UPMA                                |  |

| OR3      | MCM36200-60/70                            | FFC00800         | 4MB block size, all types access, initial address multiplexing according to AMA   |  |

|          | MCM36800-60/70<br>MT16D832X-6/7           | FF000800         | 16MB block size, all types access, initial address multiplexing according to AMA. |  |

#### **OPERATING INSTRUCTIONS**

### TABLE 3-4. Memory Controller Initialization For 66Mhz with DRAM-EDO

| Register                  | Device Type                                                                            | Init Value [hex]                                                        | Description                                                                                                                                                                                                                                                             |

|---------------------------|----------------------------------------------------------------------------------------|-------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BR4<br>Compatible<br>Mode | K4S643232-TC60                                                                         | 030000C1                                                                | Base at 3000000, on UPMB                                                                                                                                                                                                                                                |

| OR4<br>Compatible<br>Mode |                                                                                        | FFC00800                                                                | 4 MB block size, all types access, initial address multiplexing according to AMB.                                                                                                                                                                                       |

| MPTPR                     | All Dram SIMMs supported                                                               | 0400                                                                    | Divide by 16 (decimal)                                                                                                                                                                                                                                                  |

| MAMR                      | MAMR MB321BT08TASN60 40A21114 <sup>a</sup> 60A21114 <sup>b</sup> C0A21114 <sup>c</sup> |                                                                         | Refresh clock divided by 40 <sup>a</sup> or 60 <sup>b</sup> or C0 <sup>c</sup> . Periodic timer enabled. Type 2 address multiplexing scheme. 2 cycle disable timer. GPL4 disabled for data sampling edge flexibility. 1 loop read. 1 loop write. 4 beats refresh burst. |

|                           | MB322BT08TASN60                                                                        | 20A21114 <sup>a</sup><br>30A21114 <sup>b</sup><br>60A21114 <sup>c</sup> | Refresh clock divided by 20 <sup>a</sup> or 30 <sup>b</sup> or 60 <sup>c</sup> . Periodic timer enabled. Type 2 address multiplexing scheme. 2 cycle disable timer. GPL4 disabled for data sampling edge flexibility. 1 loop read. 1 loop write. 4 beats refresh burst. |

|                           | MB324CT00TBSN60                                                                        | 40B21114 <sup>a</sup><br>60B21114 <sup>b</sup><br>C0B21114 <sup>c</sup> | Refresh clock divided by 40 <sup>a</sup> or 60 <sup>b</sup> or C0 <sup>c</sup> . Periodic timer enabled. Type 3 address multiplexing scheme. 2 cycle disable timer. GPL4 disabled for data sampling edge flexibility. 1 loop read. 1 loop write. 4 beats refresh burst. |

|                           | MB328CT00TBSN60                                                                        | 20B21114 <sup>a</sup><br>30B21114 <sup>b</sup><br>60B21114 <sup>c</sup> | Refresh clock divided by 20 <sup>a</sup> or 30 <sup>b</sup> or 60 <sup>c</sup> . Periodic timer enabled. Type 3 address multiplexing scheme. 2 cycle disable timer. GPL4 disabled for data sampling edge flexibility. 1 loop read. 1 loop write. 4 beats refresh burst. |

| MBMR                      | KS643232C-TC60                                                                         | D0802114 <sup>c</sup><br>80802114 <sup>d</sup>                          | Refresh clock divided by D0 or 80. Periodic timer enabled. Type 0 address multiplexing scheme. 2 cycle disable timer. GPL4enabled. 1 loop read. 1 loop write. 4 beats refresh burst.                                                                                    |

- a. Assuming 16.67 MHz BRGCLK.

- b. Assuming 25MHz BRGCLK

- c. For 66MHz BRGCLK

- d. Assuming 32MHz BRGCLK.

#### **OPERATING INSTRUCTIONS**

TABLE 3-5. Memory Controller Initialization For 66Mhz with No DRAM-EDO

| Register                  | Device Type                               | Init Value [hex] | Description                                                                       |

|---------------------------|-------------------------------------------|------------------|-----------------------------------------------------------------------------------|

| BR0                       | All Flash SIMMs supported.                | 02800001         | Base at 2800000, 32-bit port size, no parity, GPCM                                |

| OR0                       |                                           |                  | 2MB block size, all types access, CS early negate, 6 w.s., timing relax           |

|                           | MCM29F040-90<br>SM732A1000A-9             | FFC00D34         | 4MB block size, all types access, CS early negate, 6 w.s., timing relax           |

|                           | MCM29F080-90<br>SM732A2000-9              | FF800D34         | 8MB block size, all types access, CS early negate, 6 w.s., timing relax           |

|                           | MCM29F020-12                              | FFE00D44         | 2MB block size, all types access, CS early negate, 8 w.s., timing relax           |

|                           | MCM29F040-12<br>SM732A1000A-12            | FFC00D44         | 4MB block size, all types access, CS early negate, 8 w.s., timing relax           |

|                           | MCM29F080-12<br>SM732A2000-12             | FF800D44         | 8MB block size, all types access, CS early negate, 8 w.s., timing relax           |

| BR1                       | BCSR                                      | 02100001         | Base at 2100000, 32-bit port size, no parity, GPCM                                |

| OR1                       |                                           | FFFF8110         | 32 KB block size, all types access, CS early negate, 1 w.s.                       |

| BR2                       | All Dram SIMMs supported                  | 00000080         | Invalid bank                                                                      |

| OR2                       | MCM36100/200-60/70                        | FFC00800         | Invalid bank                                                                      |

|                           | MCM36400/800-60/70<br>MT8/16D432/832X-6/7 | FF000800         |                                                                                   |

| BR3                       | MCM36200-60/70                            | 00400080         | Invalid bank                                                                      |

|                           | MCM36800-60/70<br>MT16D832X-6/7           | 01000080         | Invalid bank                                                                      |

| OR3                       | MCM36200-60/70                            | FFC00800         | Invalid bank                                                                      |

|                           | MCM36800-60/70<br>MT16D832X-6/7           | FF000800         | Invalid bank                                                                      |

| BR4<br>MPC86x<br>New Mode | K4S643232-TC60                            | 0x000000C1       | Base at 0x0, on UPMB                                                              |

| OR4<br>MPC86x<br>New Mode |                                           | 0xFC800A00       | 4 MB block size, all types access, initial address multiplexing according to AMB. |

| MPTPR                     | All Dram SIMMs supported                  | 0400             | Divide by 16 (decimal)                                                            |

#### **OPERATING INSTRUCTIONS**

### TABLE 3-5. Memory Controller Initialization For 66Mhz with No DRAM-EDO

| Register | Device Type     | Init Value [hex]                                                        | Description                                                                                                                                                                                                                                                             |

|----------|-----------------|-------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MAMR     | MB321BT08TASN60 | 40A21114 <sup>a</sup><br>60A21114 <sup>b</sup><br>C0A21114 <sup>c</sup> | Refresh clock divided by 40 <sup>a</sup> or 60 <sup>b</sup> or C0 <sup>c</sup> . Periodic timer enabled. Type 2 address multiplexing scheme. 2 cycle disable timer. GPL4 disabled for data sampling edge flexibility. 1 loop read. 1 loop write. 4 beats refresh burst. |

|          | MB322BT08TASN60 | 20A21114 <sup>a</sup><br>30A21114 <sup>b</sup><br>60A21114 <sup>c</sup> | Refresh clock divided by 20 <sup>a</sup> or 30 <sup>b</sup> or 60 <sup>c</sup> . Periodic timer enabled. Type 2 address multiplexing scheme. 2 cycle disable timer. GPL4 disabled for data sampling edge flexibility. 1 loop read. 1 loop write. 4 beats refresh burst. |

|          | MB324CT00TBSN60 | 40B21114 <sup>a</sup><br>60B21114 <sup>b</sup><br>C0B21114 <sup>c</sup> | Refresh clock divided by 40 <sup>a</sup> or 60 <sup>b</sup> or C0 <sup>c</sup> . Periodic timer enabled. Type 3 address multiplexing scheme. 2 cycle disable timer. GPL4 disabled for data sampling edge flexibility. 1 loop read. 1 loop write. 4 beats refresh burst. |

|          | MB328CT00TBSN60 | 20B21114 <sup>a</sup><br>30B21114 <sup>b</sup><br>60B21114 <sup>c</sup> | Refresh clock divided by 20 <sup>a</sup> or 30 <sup>b</sup> or 60 <sup>c</sup> . Periodic timer enabled. Type 3 address multiplexing scheme. 2 cycle disable timer. GPL4 disabled for data sampling edge flexibility. 1 loop read. 1 loop write. 4 beats refresh burst. |

| MBMR     | KS643232C-TC60  | D0802114 <sup>c</sup><br>80802114 <sup>d</sup>                          | Refresh clock divided by D0 or 80. Periodic timer enabled. Type 0 address multiplexing scheme. 2 cycle disable timer. GPL4 enabled. 1 loop read. 1 loop write. 4 beats refresh burst.                                                                                   |

- a. Assuming 16.67 MHz BRGCLK.

- b. Assuming 25MHz BRGCLK

- c. For 66MHz BRGCLK

- d. Assuming 32MHz BRGCLK.

#### **OPERATING INSTRUCTIONS**

### TABLE 3-6. UPMA Initialization for 60nsec DRAMs @ 66MHz

| Cycle Type    |   | Single Read | Burst Read | Single Write | Burst Write | Refresh  | Exceptions |

|---------------|---|-------------|------------|--------------|-------------|----------|------------|

| Offset in UPM |   | 0           | 8          | 18           | 20          | 30       | 3C         |

| Contents      | 0 | FFFFCC24    | FFFCC24    | FFFCC24      | FFFFCC24    | E0FFCC84 | 33FFCC07   |

| @ Offset +    | 1 | 0FFFCC24    | 0FFFCC24   | 0FAFCC24     | 0FAFCC24    | 00FFCC04 | FFFFFFF    |

|               | 2 | 0FFFCC04    | 0FFFCC04   | 0FAFCC04     | 0FAFCC04    | 00FFCC04 | FFFFFFF    |

|               | 3 | 0CFFCC04    | 08FFCC04   | 08AFCC04     | 08AFCC00    | 0FFFCC04 | FFFFFFF    |

|               | 4 | 00FFCC04    | 00FFCC04   | 00AFCC00     | 07AFCC4C    | 7FFFCC04 |            |

|               | 5 | 00FFCC00    | 00FFCC08   | 37FFCC47     | 08AFCC00    | FFFFCC86 |            |

|               | 6 | 37FFCC47    | 0CFFCC44   | FFFFFFF      | 07AFCC4C    | FFFFCC05 |            |

|               | 7 | FFFFFFF     | 00FFEC0C   | FFFFFFF      | 08AFCC00    | FFFFFFF  |            |

|               | 8 |             | 03FFEC00   |              | 07AFCC4C    | FFFFFFF  |            |

|               | 9 |             | 00FFEC44   |              | 08AFCC00    | FFFFFFF  |            |

|               | Α |             | 00FFCC08   |              | 37AFCC47    | FFFFFFF  |            |

|               | В |             | 0CFFCC44   |              | FFFFFFF     | FFFFFFF  |            |

|               | С |             | 00FFEC04   |              | FFFFFFF     |          |            |

|               | D |             | 00FFEC00   |              | FFFFFFF     |          |            |

|               | Е |             | 3FFFEC47   |              | FFFFFFF     |          |            |

|               | F |             | FFFFFFF    |              | FFFFFFF     |          |            |

#### **OPERATING INSTRUCTIONS**

**TABLE 3-7. Memory Controller Initialization For 20Mhz**

| Register                   | Device Type                    | Init Value [hex] | Description                                                                       |

|----------------------------|--------------------------------|------------------|-----------------------------------------------------------------------------------|

| BR0                        | All Flash SIMMs supported.     | 02800001         | Base at 2800000, 32-bit port size, no parity, GPCM                                |

| OR0                        | MCM29F020-90                   | FFE00D20         | 2MB block size, all types access, CS early negate, 2 w.s.                         |

|                            | MCM29F040-90<br>SM732A1000A-9  | FFC00D20         | 4MB block size, all types access, CS early negate, 2 w.s.                         |

|                            | MCM29F080-90<br>SM732A2000-9   | FF800920         | 8MB block size, all types access, CS early negate, 2 w.s., timing relax           |

|                            | MCM29F020-12                   | FFE00D30         | 2MB block size, all types access, CS early negate, 3 w.s.                         |

|                            | MCM29F040-12<br>SM732A1000A-12 | FFC00D30         | 4MB block size, all types access, CS early negate, 3 w.s.                         |

|                            | MCM29F080-12<br>SM732A2000-12  | FF800930         | 8MB block size, all types access, CS early negate, 3 w.s.                         |

| BR1                        | BCSR                           | 02100001         | Base at 2100000, 32-bit port size, no parity, GPCM                                |

| OR1                        |                                | FFFF8110         | 32 KB block size, all types access, CS early negate, 1 w.s.                       |

| BR2                        | All Dram SIMMs supported       | 00000081         | Base at 0, 32-bit port size, no parity, UPMA                                      |

| OR2                        | MB321/2BT08TASN60              | FFC00800         | 4MB block size, all types access, initial address multiplexing according to AMA.  |

|                            | MB324/8CT00TBSN60              | FF000800         | 16MB block size, all types access, initial address multiplexing according to AMA. |