# **Low Inductance Capacitors**

## Introduction

The signal integrity characteristics of a Power Delivery Network (PDN) are becoming critical aspects of board level and semiconductor package designs due to higher operating frequencies, larger power demands, and the ever shrinking lower and upper voltage limits around low operating voltages. These power system challenges are coming from mainstream designs with operating frequencies of 300MHz or greater, modest ICs with power demand of 15 watts or more, and operating voltages below 3 volts.

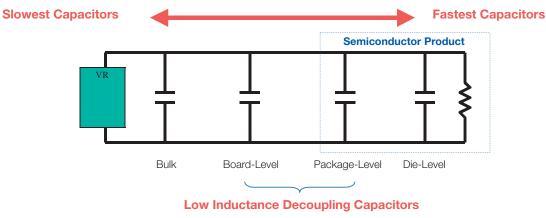

The classic PDN topology is comprised of a series of capacitor stages. Figure 1 is an example of this architecture with multiple capacitor stages.

An ideal capacitor can transfer all its stored energy to a load instantly. A real capacitor has parasitics that prevent instantaneous transfer of a capacitor's stored energy. The true nature of a capacitor can be modeled as an RLC equivalent circuit. For most simulation purposes, it is possible to model the characteristics of a real capacitor with one capacitor, one resistor, and one inductor. The RLC values in this model are commonly referred to as equivalent series capacitance (ESC), equivalent series resistance (ESR), and equivalent series inductance (ESL).

The ESL of a capacitor determines the speed of energy transfer to a load. The lower the ESL of a capacitor, the faster that energy can be transferred to a load. Historically, there has been a tradeoff between energy storage (capacitance) and inductance (speed of energy delivery). Low ESL devices typically have low capacitance. Likewise, higher capacitance devices typically have higher ESLs. This tradeoff between ESL (speed of energy delivery) and capacitance (energy storage) drives the PDN design topology that places the fastest low ESL capacitors as close to the load as possible. Low Inductance MLCCs are found on semiconductor packages and on boards as close as possible to the load.

Figure 1 Classic Power Delivery Network (PDN) Architecture

#### LOW INDUCTANCE CHIP CAPACITORS

The key physical characteristic determining equivalent series inductance (ESL) of a capacitor is the size of the current loop it creates. The smaller the current loop, the lower the ESL. A standard surface mount MLCC is rectangular in shape with electrical terminations on its shorter sides. A Low Inductance Chip Capacitor (LICC) sometimes referred to as Reverse Geometry Capacitor (RGC) has its terminations on the longer side of its rectangular shape.

When the distance between terminations is reduced, the size of the current loop is reduced. Since the size of the current loop is the primary driver of inductance, an 0306 with a smaller current loop has significantly lower ESL then an 0603. The reduction in ESL varies by EIA size, however, ESL is typically reduced 60% or more with an LICC versus a standard MLCC.

#### **INTERDIGITATED CAPACITORS**

The size of a current loop has the greatest impact on the ESL characteristics of a surface mount capacitor. There is a secondary method for decreasing the ESL of a capacitor. This secondary method uses adjacent opposing current loops to reduce ESL. The InterDigitated Capacitor (IDC) utilizes both primary and secondary methods of reducing inductance. The IDC architecture shrinks the distance between terminations to minimize the current loop size, then further reduces inductance by creating adjacent opposing current loops.

An IDC is one single capacitor with an internal structure that has been optimized for low ESL. Similar to standard MLCC versus LICCs, the reduction in ESL varies by EIA case size. Typically, for the same EIA size, an IDC delivers an ESL that is at least 80% lower than an MLCC.

# **Low Inductance Capacitors**

### Introduction

#### LAND GRID ARRAY (LGA) CAPACITORS

Land Grid Array (LGA) capacitors are based on the first Low ESL MLCC technology created to specifically address the design needs of current day Power Delivery Networks (PDNs). This is the 3rd low inductance capacitor technology developed by AVX. LGA technology provides engineers with new options. The LGA internal structure and manufacturing technology eliminates the historic need for a device to be physically small to create small current loops to minimize inductance.

The first family of LGA products are 2 terminal devices. A 2 terminal 0306 LGA delivers ESL performance that is equal to or better than an 0306 8 terminal IDC. The 2 terminal 0805 LGA delivers ESL performance that approaches the 0508 8 terminal IDC. New designs that would have used 8 terminal IDCs are moving to 2 terminal LGAs because the layout is easier for a 2 terminal device and manufacturing yield is better for a 2 terminal LGA versus an 8 terminal IDC.

LGA technology is also used in a 4 terminal family of products that AVX is sampling and will formerly introduce in 2008. Beyond 2008, there are new multi-terminal LGA product families that will provide even more attractive options for PDN designers.

#### LOW INDUCTANCE CHIP ARRAYS (LICA®)

The LICA® product family is the result of a joint development effort between AVX and IBM to develop a high performance MLCC family of decoupling capacitors. LICA was introduced in the 1980s and remains the leading choice of designers in high performance semiconductor packages and high reliability board level decoupling applications.

LICA® products are used in 99.999% uptime semiconductor package applications on both ceramic and organic substrates. The C4 solder ball termination option is the perfect compliment to flip-chip packaging technology. Mainframe class CPUs, ultimate performance multi-chip modules, and communications systems that must have the reliability of 5 9's use LICA®.

LICA® products with either Sn/Pb or Pb-free solder balls are used for decoupling in high reliability military and aerospace applications. These LICA® devices are used for decoupling of large pin count FPGAs, ASICs, CPUs, and other high power ICs with low operating voltages.

When high reliability decoupling applications require the very lowest ESL capacitors, LICA® products are the best option.

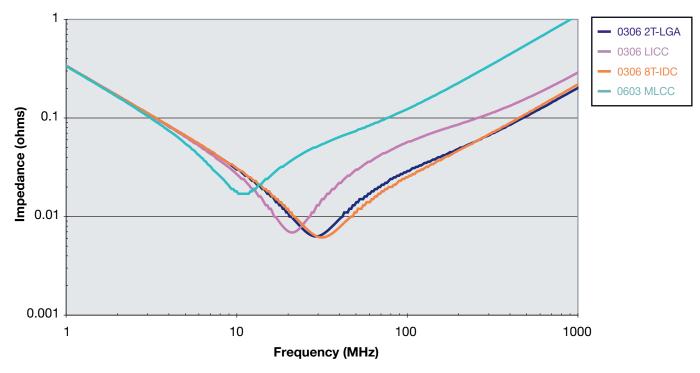

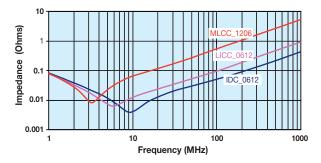

#### 470 nF 0306 Impedance Comparison

Figure 2 MLCC, LICC, IDC, and LGA technologies deliver different levels of equivalent series inductance (ESL).

# IDC Low Inductance Capacitors (RoHS)

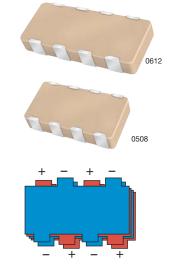

## 0612/0508 IDC (InterDigitated Capacitors)

#### **GENERAL DESCRIPTION**

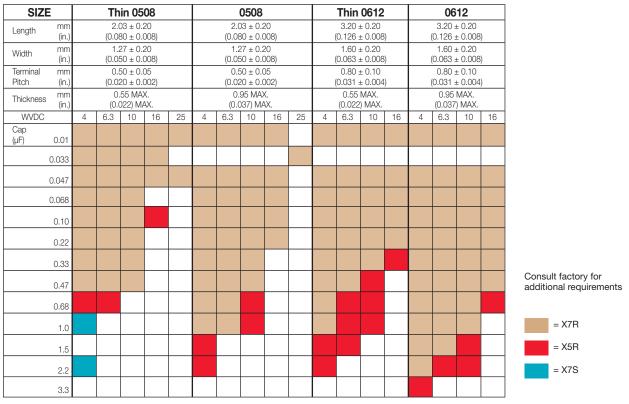

Inter-Digitated Capacitors (IDCs) are used for both semiconductor package and board level decoupling. The equivalent series inductance (ESL) of a single capacitor or an array of capacitors in parallel determines the response time of a Power Delivery Network (PDN). The lower the ESL of a PDN, the faster the response time. A designer can use many standard MLCCs in parallel to reduce ESL or a low ESL Inter-Digitated Capacitor (IDC) device. These IDC devices are available in versions with a maximum height of 0.95mm or 0.55mm.

IDCs are typically used on packages of semiconductor products with power levels of 15 watts or greater. Inter-Digitated Capacitors are used on CPU, GPU, ASIC, and ASSP devices produced on 0.13µ, 90nm, 65nm, and 45nm processes. IDC devices are used on both ceramic and organic package substrates. These low ESL surface mount capacitors can be placed on the bottom side or the top side of a package substrate. The low profile 0.55mm maximum height IDCs can easily be used on the bottom side of BGA packages or on the die side of packages under a heat spreader.

IDCs are used for board level decoupling of systems with speeds of 300MHz or greater. Low ESL IDCs free up valuable board space by reducing the number of capacitors required versus standard MLCCs. There are additional benefits to reducing the number of capacitors beyond saving board space including higher reliability from a reduction in the number of components and lower placement costs based on the need for fewer capacitors.

The Inter-Digitated Capacitor (IDC) technology was developed by AVX. This is the second family of Low Inductance MLCC products created by AVX. IDCs are a cost effective alternative to AVX's first generation low ESL family for high-reliability applications known as LICA (Low Inductance Chip Array).

AVX IDC products are available with a lead-free finish of plated Nickel/Tin.

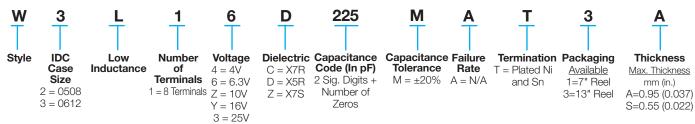

#### **HOW TO ORDER**

NOTE: Contact factory for availability of Termination and Tolerance Options for Specific Part Numbers.

#### **PERFORMANCE CHARACTERISTICS**

| Capacitance Tolerance   | ±20% Preferred                                 |  |  |

|-------------------------|------------------------------------------------|--|--|

| Operation               | X7R = -55°C to +125°C                          |  |  |

| Temperature Range       | $X5R = -55^{\circ}C$ to $+85^{\circ}C$         |  |  |

|                         | $X7S = -55^{\circ}C \text{ to } +125^{\circ}C$ |  |  |

| Temperature Coefficient | ±15% (0VDC)                                    |  |  |

| Voltage Ratings         | 4, 6.3, 10, 16 VDC                             |  |  |

| Dissipation Factor      | 4V, 6.3V = 6.5% max;                           |  |  |

| -                       | 10V = 5.0% max;                                |  |  |

|                         | 16V = 3.5% max                                 |  |  |

| Insulation Resistance   | 100,000M $\Omega$ min, or 1,000M $\Omega$ per  |  |  |

| (@+25°C, RVDC)          | μF min.,whichever is less                      |  |  |

| Dielectric Strength       | No problems observed after 2.5 x RVDC for 5 seconds at 50mA max current |  |

|---------------------------|-------------------------------------------------------------------------|--|

| CTE (ppm/C)               | 12.0                                                                    |  |

| Thermal Conductivity      | 4-5W/M K                                                                |  |

| Terminations<br>Available | Plated Nickel and Solder                                                |  |

| Max. Thickness            | 0.037" (0.95mm)                                                         |  |

|                           |                                                                         |  |

#### **TYPICAL IMPEDANCE**

# IDC Low Inductance Capacitors (RoHS)

0612/0508 IDC (InterDigitated Capacitors)

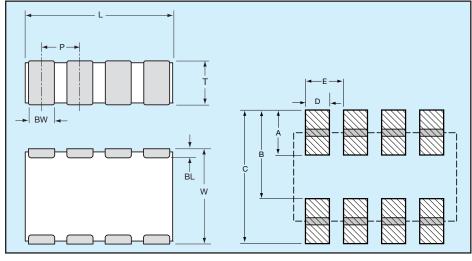

### PHYSICAL DIMENSIONS AND PAD LAYOUT

#### PHYSICAL CHIP DIMENSIONS millimeters (inches)

#### 0612

| L                              | W                              | BW                             | BL                                              | Р                              |  |

|--------------------------------|--------------------------------|--------------------------------|-------------------------------------------------|--------------------------------|--|

| 3.20 ± 0.20<br>(0.126 ± 0.008) | 1.60 ± 0.20<br>(0.063 ± 0.008) | 0.41 ± 0.10<br>(0.016 ± 0.004) | 0.18 +0.25<br>-0.08<br>(0.007 +0.010<br>-0.003) | 0.80 ± 0.10<br>(0.031 ± 0.004) |  |

#### 0508

| L                          | W                          | BW                                                                   | BL                                                                        | Р                                                                 |

|----------------------------|----------------------------|----------------------------------------------------------------------|---------------------------------------------------------------------------|-------------------------------------------------------------------|

| 2.03±0.20<br>(0.080±0.008) | 1.27±0.20<br>(0.050±0.008) | $\substack{0.25 \ +0.15 \\ -0.10 \\ (0.010 \ +0.006 \\ -0.004 \\ )}$ | $\substack{0.18 \ \ +0.25 \\ -0.08 \\ (0.007 \ \ +0.010 \\ -0.003 \ \ )}$ | $\begin{array}{c} 0.50 \pm 0.05 \\ (0.020 \pm 0.002) \end{array}$ |

PAD LAYOUT DIMENSIONS 0612

| А       | В       | С       | D       | E       |

|---------|---------|---------|---------|---------|

| 0.89    | 1.65    | 2.54    | 0.46    | 0.80    |

| (0.035) | (0.065) | (0.100) | (0.018) | (0.031) |

#### 0508

| А       | В       | С       | D       | E       |

|---------|---------|---------|---------|---------|

| 0.64    | 1.27    | 1.91    | 0.28    | 0.50    |

| (0.025) | (0.050) | (0.075) | (0.011) | (0.020) |