#### Freescale Semiconductor

**Data Sheet: Product Preview**

Document Number: SC33690DS

Rev. 5, 02/2007

### MC33690

# MC33690 Standalone Tag Reader Circuit

The standalone tag reader circuit (STARC) is an integrated circuit dedicated to the automotive immobilizer applications. It combines the antenna drivers and demodulator necessary to interface with a transponder.

A low dropout voltage regulator and a physical interface fully compatible with the ISO 9141 norm are also available.

The STARC is fabricated with the SMARTMOSTM3.5 technology. This process is a double layer metal 1.4µm 45V technology, combining CMOS and bipolar devices.

- Contactless 125 kHz tag reader module:

- Self synchronous sample and hold demodulator

- Amplitude or phase modulation detection

- High sensitivity

- Fast read after write demodulator settling time

- Low resistance and high current antenna drivers, 2W @ 150mA (typ.)

- Bidirectionnal data transmission

- Multi-tag, multi-scheme operation

- Low dropout voltage regulator:

- Wide input supply voltage range from 5.5V up to 40V

- Output current capability up to 150mA DC with an external power transistor

- 5V output voltage with a ±5% accuracy

- Low voltage reset function

- Low current consumption in standby mode:

- $-300\mu A$  (typ.)

- ISO 9141 transmitter and receiver module:

- Input voltage thresholds ratiometric to the supply voltage

- Current limitation

- Output slew rate control

- No external protection device required

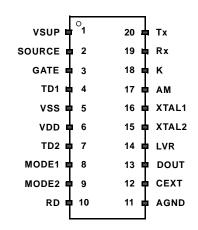

#### **Pin Connections**

#### ORDERING INFORMATION

| Device     | Operating<br>Junction<br>Temperature<br>Range | Package           |

|------------|-----------------------------------------------|-------------------|

| MC33690DW  | $T_J = -40^{\circ}\text{C} \text{ to}$        | SOIC 20           |

| MC33690DWE | TJ = -40°C to<br>125°C                        | SOIC 20<br>(ROHS) |

This document contains information on a product under development. Freescale reserves the right to change or discontinue this product without notice.

© Freescale Semiconductor, Inc., 2007. All rights reserved.

### **Table of Contents**

| 1 Description                                          | 5 Figure 8. Modes Access Description in                    |

|--------------------------------------------------------|------------------------------------------------------------|

| 1.1 Tag Reader Module                                  | 5 Two-wire Bus Configuration                               |

| 2 Read Function                                        | 6 Figure 9. Configuration B State Diagram                  |

| 3 Write Function                                       |                                                            |

| 4 Voltage Regulator                                    |                                                            |

| 5 ISO 9141 Physical Interface                          | 8 Figure 12.Demodulator Parameters Definition              |

| 6 Communication Modes Description                      |                                                            |

| 7 Standalone Configuration with One-Wire Bus           | 0 Figure 14.GATE Internal Circuits                         |

| 7.1 Timing Definitions for a 8 MHz Crystal             | 1 Figure 15.TD1, TD2, DOUT, and RX Internal Circuits 19    |

| 8 Standalone Configuration with Two-Wire Bus1          |                                                            |

| 9 Direct Connection to a Microcontroller Configuration |                                                            |

| 10 Electrical Characteristics                          |                                                            |

| 11 Supply Current                                      | Figure 19.MODE1, MODE2, and TX Internal Circuits           |

| 12 Voltage Regulator1                                  |                                                            |

| 13 Low-Voltage Reset                                   | 4 Figure 21.XTAL2 and XTAL1 Internal Circuits              |

| 14 Oscillator1                                         |                                                            |

| 15 Tag Reader1                                         |                                                            |

| 16 ISO 9141 Interface                                  |                                                            |

| 17 Digital I/O                                         | 8 Figure 25.Standalone Configuration with Two-Wires Bus 24 |

| 18 Pin Definition and Function1                        | 9 Figure 26.Direct Connection to a Microcontroller 25      |

| 19 Application Schemes                                 | 3                                                          |

| List of Flavors                                        | List of Tables                                             |

| List of Figures                                        | Table 1. Maximum Ratings                                   |

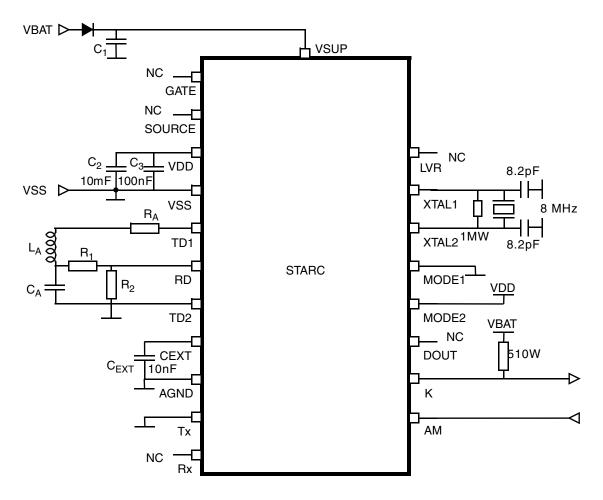

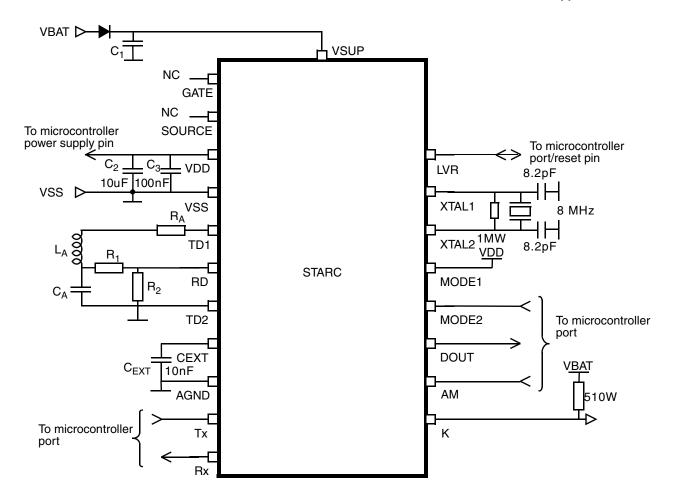

| Figure 1. Standalone Tag Reader Circuit                |                                                            |

| Figure 2. Tag Reader Block Diagram                     | ·                                                          |

| Figure 3. Current Flow When Buffers are Switched Off   | ·                                                          |

| Figure 4. Voltage Regulator Block Diagram              | 11.2                                                       |

| Figure 5.ISO 9141 Interface                            |                                                            |

| Figure 6. Mode Access Description in                   | Table 7. Low-Voltage Reset Specifications                  |

| One-Wire Bus Configuration                             |                                                            |

| Figure 7. Configuration A State Diagram                |                                                            |

|                                                        | Table 10.ISO 9141 Interface Specifications                 |

|                                                        | Table 11 Digital I/O Specifications                        |

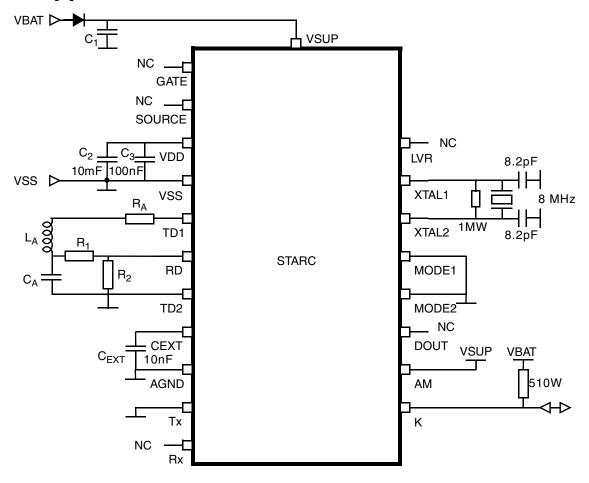

VBAT → **VSUP** SOURCE Voltage Regulator LVR VDD VDD 10mF VSS 8 MHz TD1 XTAL2 RD MODE1  $R_2$  $\mathsf{C}_\mathsf{A}$ MODE2 Tag Reader **DOUT** TD2 AM C<sub>EXT</sub> CEXT 10nF **VBAT** AGND 510W Тx ISO 9141 Interface Κ Rx

Optional: External N channel MOS required for sourced current > 50mA. A recommended reference is MMFT 3055VL from Freescale.

Figure 1. Standalone Tag Reader Circuit

**Table 1. Maximum Ratings**

| Rating                                                                  | Symbol           | Value                          | Unit |

|-------------------------------------------------------------------------|------------------|--------------------------------|------|

| Supply voltage                                                          | V <sub>SUP</sub> | V <sub>SS</sub> -0.3 to +40    | V    |

| Supply voltage without using the voltage regulator $(V_{SUP} = V_{DD})$ | V <sub>DD</sub>  | V <sub>SS</sub> -0.3 to +7     | ٧    |

| Voltage on SOURCE                                                       | _                | V <sub>SS</sub> -0.3 to +40    | V    |

| Current into/from GATE                                                  | _                | 0                              | mA   |

| Voltage on GATE                                                         | _                | V <sub>SS</sub> -0.3           | V    |

| Voltage on pins:<br>MODE1/2, CEXT, DOUT, LVR, XTAL1/2, Rx, Tx           | _                | $V_{SS}$ =0.3 to $V_{DD}$ +0.3 | V    |

| Voltage on RD                                                           | _                | ±10                            | V    |

| Voltage on K and AM                                                     | _                | V <sub>SS</sub> –3 to 40       | V    |

| Current on TD1 and TD2<br>(Drivers on and off)                          | _                | ±300                           | mA   |

| Voltage on AGND                                                         | _                | V <sub>SS</sub> ±0.3           | V    |

| ESD voltage capability <sup>1</sup>                                     | _                | ±2000                          | V    |

| ESD voltage capability <sup>1</sup>                                     | _                | ±200                           | V    |

| Solder heat resistance test (10s)                                       | _                | 260                            | °C   |

| Junction temperature                                                    | TJ               | 170                            | °C   |

| Storage temperature                                                     | T <sub>s</sub>   | -65 to +150                    | °C   |

<sup>1</sup> Human Body Model, AEC-Q100-002 Rev. C; Machine Model, AEC-Q100-003 Rev. E.

**Table 2. Thermal Characteristics**

| Characteristic                                  | Symbol          | Value | Unit |

|-------------------------------------------------|-----------------|-------|------|

| Junction to ambient thermal resistance (SOIC20) | R <sub>th</sub> | 80    | °C/W |

**Table 3. Pin Function Descriptions**

| Pin | Function | Description                          |

|-----|----------|--------------------------------------|

| 1   | VSUP     | Power supply                         |

| 2   | SOURCE   | External N channel transistor source |

| 3   | GATE     | External N channel transistor gate   |

| 4   | TD1      | Antenna driver 1 output              |

| 5   | VSS      | Power and digital ground             |

| 6   | VDD      | Voltage regulator output             |

| 7   | TD2      | Antenna driver 2 output              |

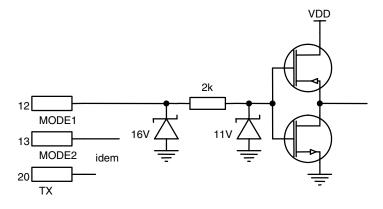

| 8   | MODE1    | Mode selection input 1               |

| 9   | MODE2    | Mode selection input 2               |

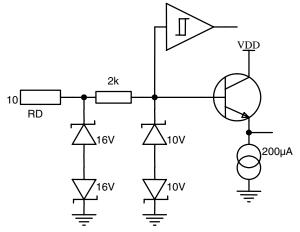

| 10  | RD       | Demodulator input                    |

**Table 3. Pin Function Descriptions (continued)**

| 11 | AGND  | Demodulator ground                             |

|----|-------|------------------------------------------------|

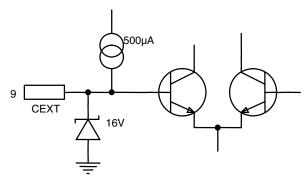

| 12 | CEXT  | Comparator reference input                     |

| 13 | DOUT  | Demodulator output (5V)                        |

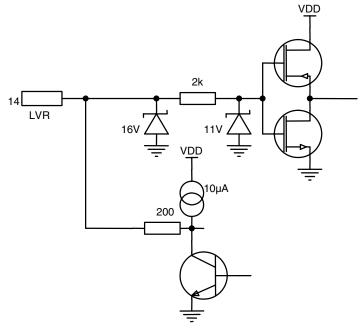

| 14 | LVR   | Low Voltage Reset input/output                 |

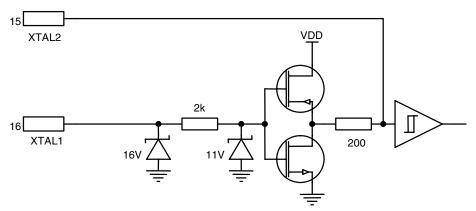

| 15 | XTAL2 | Oscillator output                              |

| 16 | XTAL1 | Oscillator input                               |

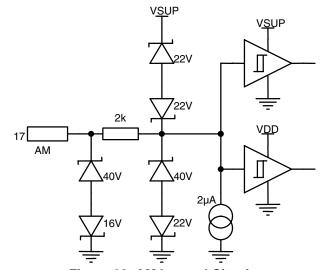

| 17 | AM    | Amplitude modulation input                     |

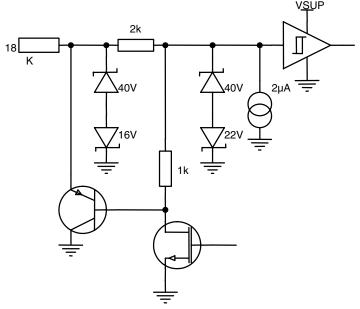

| 18 | K     | ISO 9141 transmitter output and receiver input |

| 19 | Rx    | ISO 9141 receiver monitor output               |

| 20 | Tx    | ISO 9141 transmitter input                     |

### 1 Description

#### 1.1 Tag Reader Module

The tag reader module is dedicated for automotive or industrial applications where information has to be transmitted contactless. The tag reader module is a write/read (challenge/response) controller for applications that a demand high security level.

The tag reader module is connected to a serial-tuned LC circuit that generates a magnetic field power supplying the tag. The use of a synchronous sample and hold technique allows communication with all available tags using admittance switching producing absorption of the RF field.

Load amplitude or phase shift modulation can be detected at high bit rates up to 8 kHz. The typical operational carrier frequency of the tag reader module with an 8 MHz clock is 125 kHz.

MC33690 Standalone Tag Reader Circuit, Rev. 5

#### **Read Function**

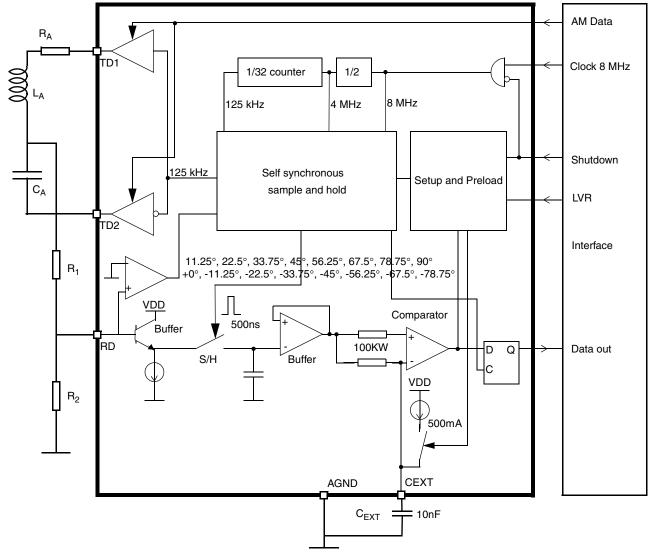

Figure 2. Tag Reader Block Diagram

#### 2 Read Function

When answering to the base station, a transponder generates an absorption modulation of the magnetic field. It results in an amplitude/phase modulation of the current across the antenna. This information is picked up at the antenna tap point between the coil and the capacitor. An external resistive ladder down scales this voltage to a level compatible with the demodulator input voltage range (see Section 15, "Tag Reader").

The demodulator (see Figure 2) consists of:

- an input stage (emitter follower)

- a sample and hold circuit

- a voltage follower

- a low offset voltage comparator

The sampling time is automatically set to take into account a phase shift due to the tolerances of the antenna components (L and C) and of the oscillator. The allowed phase shift measured at the input RD ranges from  $-45^{\circ}$  to  $+45^{\circ}$ . Assuming that the phase

MC33690 Standalone Tag Reader Circuit, Rev. 5

reference is the falling edge of the driving signal TD1, this leads to a sampling time phase ranging from  $-78.75^{\circ}$  to  $90^{\circ}$  with discrete steps of  $11.25^{\circ}$ . After reset condition, the sampling time phase is  $+11.25^{\circ}$ .

The antenna phase shift evaluation is only done after each wake-up command or after reset. This is necessary to obtain the best demodulator performances.

To ensure a fast demodulator settling time after wake-up, reset, or a write sequence, the external capacitor CEXT is preloaded at its working voltage. This preset occurs 256µs after switching the antenna drivers on and its duration is 128µs. After wake-up or reset, the preset has the same duration, but begins 518µs after clock settling. After power on reset, VSUP must meet the minimum specified value, enabling the nominal operation of VDD, before the start of the preset. Otherwise, the preset must be done through a standby/wake-up sequence.

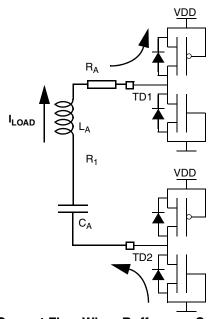

### 3 Write Function

Whatever the selected configuration (see Section 6, "Communication Modes Description"), the write function is achieved by switching on/off the output drivers TD1/2. After the drivers have been set in high impedance, the load current flows alternatively through the internal diodes to VSS and to VDD (see Figure 3).

Figure 3. Current Flow When Buffers are Switched Off

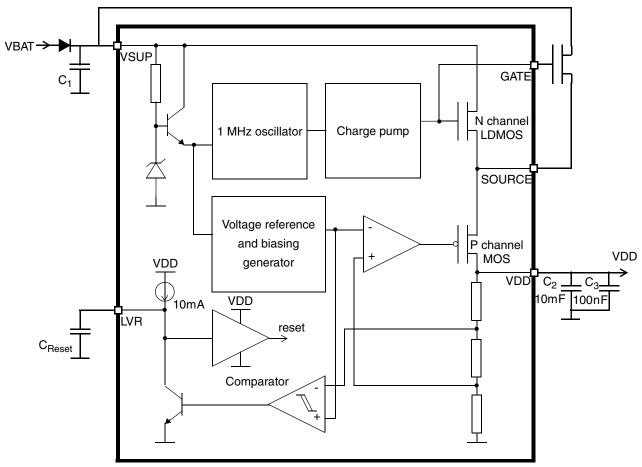

### 4 Voltage Regulator

The low dropout voltage regulator provides a regulated 5V supply for the internal circuitry. It can also supply external peripherals or sensors. The input supply voltage ranges from 5.5V to over 40V.

This voltage regulator uses a series combination of high voltage LDMOS and low voltage PMOS transistors to provide regulation. An external low ESR capacitor is required for the regulator stability.

The maximum average current is limited by the power dissipation capability of the SO 20 package. This limitation can be overcome by connecting an external N channel MOS parallel with the internal LDMOS. The threshold voltage of this transistor must be lower than the one of the internal LDMOS (1.95V typ.) to prevent the current from flowing into the LDMOS. Its breakdown voltage must be higher than the maximum supply voltage.

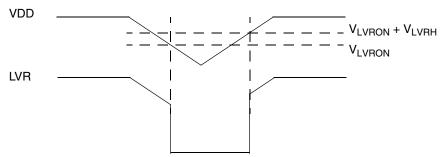

A low-voltage reset function monitors the VDD output. An internal  $10\mu A$  pull-up current source allows, when an external capacitor is connected between LVR and GND, to generate delays at power up (5ms typ. with  $C_{Reset}$ =22nF). The LVR pin is

MC33690 Standalone Tag Reader Circuit, Rev. 5

#### ISO 9141 Physical Interface

also the input generating the internal reset signal. Applying a logic low level on this pin resets the circuit, all the internal flip flops are reset, and drivers TD1/2 are switched on.

Figure 4. Voltage Regulator Block Diagram

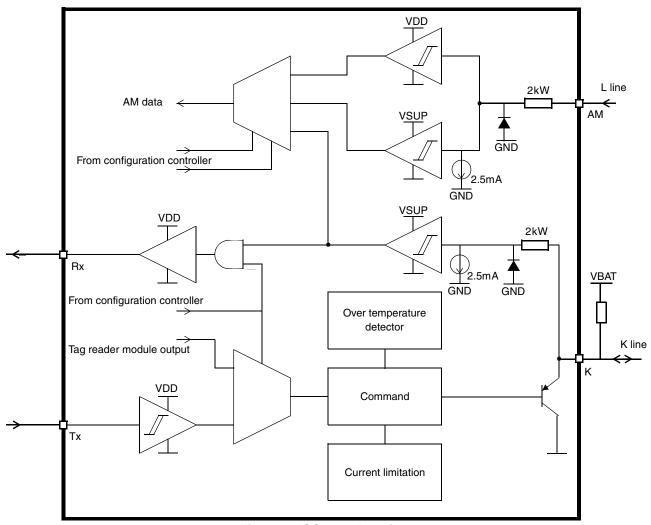

# 5 ISO 9141 Physical Interface

This interface module is fully compatible with the ISO 9141 norm describing the diagnosis line. It includes one transmitter (pin K) and two receivers (pins K and AM).

The input stages consist of high-voltage CMOS triggers. The thresholds are ratiometric to VSUP. A ground referenced current source  $(2.5\mu A\ typ.)$  pulls down the input when unconnected.

When a negative voltage is applied on the K or AM lines, the input current is internally limited by a  $2k\Omega$  resistor (typ.) in series with a diode.

A current limitation allows the transmitter to drive any capacitive load and protects against short circuit to the battery voltage. An overtemperature protection shuts the driver down when the junction temperature exceeds 150°C (typ). After shutdown by the overtemperature protection, the driver can be switched on again if the junction temperature has decreased below the threshold and by applying an off/on command, coming from the demodulator in configurations A and B, or directly applied on the input Tx in configuration C (see Table 4).

The electromagnetic emission is reduced because of the voltage slew rate control ( $5V/\mu s$  typ.).

MC33690 Standalone Tag Reader Circuit, Rev. 5

Figure 5. ISO 9141 Interface

# **6** Communication Modes Description

The STARC offers three different communication modes. Therefore, it can be used as a standalone circuit connected to an electronic control unit (ECU) through a bus line or it can be directly connected to a microcontroller in case of a single board architecture.

**Table 4. Communication Modes Description**

| С                                | onfiguration   |      | Configur | ation Pins |                                                                                                                                              |

|----------------------------------|----------------|------|----------|------------|----------------------------------------------------------------------------------------------------------------------------------------------|

| Туре                             | Bus Type       | Name | Mode1    | Mode2      | Pin Status Function Description                                                                                                              |

| Standalone                       | 1 wire (VBAT)  | A    | 0        | 0          | K output/input:  • demodulator output  • amplitude modulation input  • shutdown/wake-up AM must be connected to VSUP DOUT forces a low level |

|                                  | 2 wires (VBAT) | В    | 0        | 1          | K output:  • demodulator output  AM input:  • amplitude modulation input  • shutdown/wake-up  DOUT forces a low level                        |

| Direct<br>Connection to<br>a MCU | 2 wires (VDD)  | С    | 1        | х          | DOUT output:  • demodulator output AM input:  • amplitude modulation input MODE2 input:  • shutdown/wake-up                                  |

|                                  |                |      |          | 1          | K output/input (standalone ISO 9141 interface):  • driven by Tx and monitored by Rx                                                          |

|                                  |                |      |          | 0          | K input (standalone ISO 9141 interface):  • monitored by Rx  • Tx disabled                                                                   |

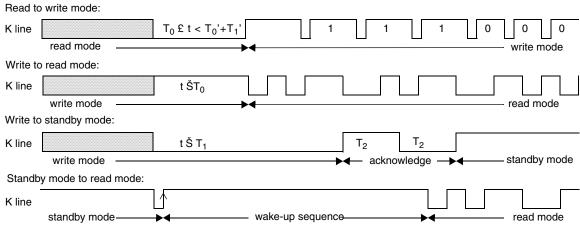

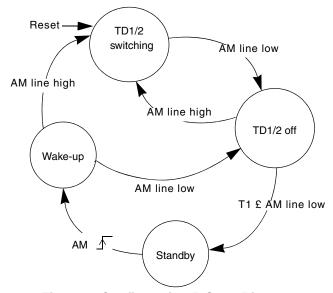

### 7 Standalone Configuration with One-Wire Bus

When a low level is applied on pins MODE1 and MODE2, the circuit is in configuration A (see Figure 24). After power on, the circuit is set into read mode. The demodulator output is directly routed to the ISO 9141 interface output K.

The circuit can be set into write mode at anytime by violation of all possible patterns on the single wire bus during more than 1ms. Then, the K line achieves the amplitude modulation by switching on/off both antenna drivers.

After 1ms of inactivity at the end of the challenge phase (bus in idle recessive one state), the circuit is set back into read mode.

The circuit can be put into standby mode by forcing the K line at zero during more than 2 ms after entering the write mode. After the K line is released, the circuit sends an acknowledge pulse before entering into standby mode. In standby mode, the oscillator and most of the internal biasing currents are switched off. Therefore, the functions (tag reader, ISO 9141 driver) are inactive except the voltage regulator and the ISO 9141 receiver on pin K. The driver output TD1 forces a low level and TD2 forces a high level. A rising edge on K wakes up the circuit. After completion of the wake-up sequence, the circuit is automatically set in read mode.

In configuration A, DOUT and Rx outputs always force a low level and Tx is disabled.

Figure 6. Mode Access Description in One-Wire Bus Configuration

Figure 7. Configuration A State Diagram

#### 7.1 Timing Definitions for a 8 MHz Crystal

The timing definitions for a 8 MHz crystal are:

- T<sub>ref</sub> is crystal oscillator period (125 ns typ.)

- $T_0 = 8064.T_{ref} = 1.008ms$  typ.

- $T_0$ '=7932. $T_{ref}$  = 0.992ms typ.

- $T_1=16256.T_{ref}=2.032ms$  typ.

- $T_1$ '=16128. $T_{ref}$  = 2.016ms typ.

- $T_2=4096.T_{ref}$ , = 512 $\mu$ s typ.

$T_0$  is the minimum time required to guarantee the device toggles from read to write (or from write to read). However, the STARC may toggle from read to write (or from write to read) between  $T_0$  and  $T_0$ .

$T_1$  is the minimum time required to guarantee the device toggles from write to standby. However, the STARC may toggle in standby between  $T_1$  and  $T_1$ .

MC33690 Standalone Tag Reader Circuit, Rev. 5

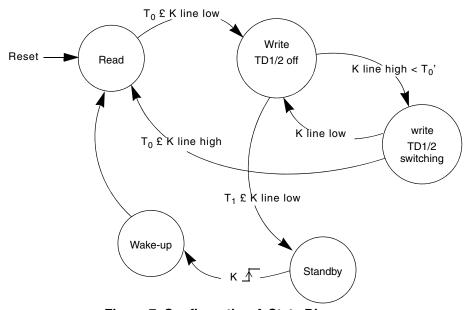

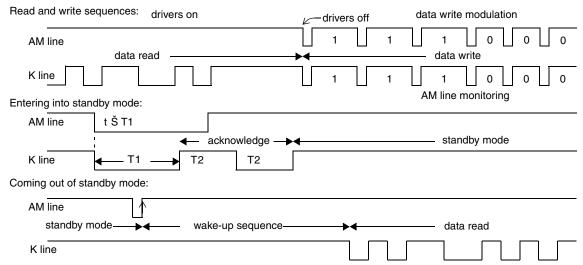

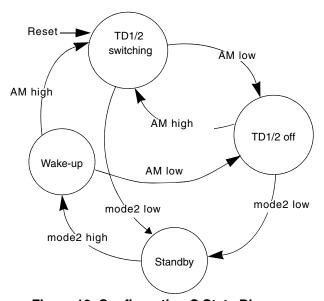

### 8 Standalone Configuration with Two-Wire Bus

When a low level is applied on MODE1 and a high level on MODE2, the circuit is in configuration B (see Figure 25). The K pin is set as an output sending the demodulated data.

The AM pin is set as a VSUP referenced input pin receiving the amplitude modulation and the shutdown/wake-up commands. Forcing high and low levels on AM achieves the amplitude modulation by switching on/off both antenna drivers. This amplitude modulation can be monitored on the K output and allows antenna short and open circuit diagnosis. The circuit can be put into standby mode by forcing the AM line at zero during more than 2 ms. The circuit sends an acknowledge pulse before entering into standby mode.

In standby mode, the oscillator and most of the internal biasing currents are switched off. Therefore, the functions (tag reader and ISO 9141 driver) are inactive except for the voltage regulator and the ISO 9141 receiver on pin AM. The driver output TD1 forces a low level and TD2 a high level. A rising edge on AM wakes up the circuit. After completion of the wake-up sequence, the circuit is automatically set in read mode.

In configuration B, DOUT and Rx outputs always force a low level and Tx is disabled.

Figure 8. Modes Access Description in Two-wire Bus Configuration

Figure 9. Configuration B State Diagram

MC33690 Standalone Tag Reader Circuit, Rev. 5

### 9 Direct Connection to a Microcontroller Configuration

When a high level is applied on MODE1, the circuit is in configuration C (see Figure 26). The demodulated data are sent through DOUT.

The AM pin is set as a VDD referenced input pin receiving the AM command. Forcing high and low levels on AM achieves the amplitude modulation by switching on/off both antenna drivers. Meanwhile, this amplitude modulation can be monitored on DOUT. This allows antenna short and open circuit diagnosis.

The circuit can be put into standby mode by applying a low level on the MODE2 pin. In standby mode, the oscillator and most of the internal biasing currents are switched off. Therefore, the functions (tag reader and ISO 9141 interface) are inactive except for the voltage regulator. The driver outputs TD1 and TD2 are frozen in their state (high or low level) before entering into standby mode. DOUT forces a low level.

The ISO 9141 interface K is standalone and can be directly controlled by the input pin Tx and monitored by the output Rx. Applying a logic high level on Tx switches the output driver K on (dominant zero state when an external pull-up resistor is connected between K and VBAT). Applying a logic low level turns the driver off (one recessive state).

Rx monitors the voltage at the K pin. When the voltage is below the low threshold voltage, Rx forces a logic low level. When the voltage is above the high threshold voltage, Rx forces a logic high level.

In standby mode, Tx is disabled and Rx output monitors the voltage at the K pin.

Figure 10. Configuration C State Diagram

### 10 Electrical Characteristics

Typical values reflect average measurements at V<sub>SUP</sub>=12V and T<sub>I</sub>=25°C.

### 11 Supply Current

Typical values reflect average measurements at  $6V \le V_{SUP} \le 16V$ ,  $V_{SS} = 0V$ ,  $T_J = -40^{\circ}C$  to  $+125^{\circ}C$ , unless otherwise noted.

MC33690 Standalone Tag Reader Circuit, Rev. 5

**Table 5. Supply Current Specifications**

| Parameter |                        | Symbol            | Test Conditions and Comments                                                                             | Min | Тур | Max | Unit | Туре |

|-----------|------------------------|-------------------|----------------------------------------------------------------------------------------------------------|-----|-----|-----|------|------|

|           | Pin VSUP               |                   |                                                                                                          |     |     |     |      |      |

| 9.1       | Standby mode current   | I <sub>SUP1</sub> | _                                                                                                        | _   | 300 | 500 | μА   | _    |

| 9.2       | Operating mode current | I <sub>SUP2</sub> | Circuit in configuration C<br>No current sunk from VDD<br>Drivers TD1/2 switched off<br>Tx forced to low | _   | 1.5 | 2.5 | mA   | _    |

## 12 Voltage Regulator

Typical values reflect average measurements at  $6V \le V_{SUP} \le 16V$ ,  $V_{SS} = 0V$ ,  $T_J = -40^{\circ}C$  to  $+125^{\circ}C$ , unless otherwise noted

**Table 6. Voltage Regulator Specifications**

|      | Parameter                                                | Symbol                | Test Conditions and Comments                                                                                                                                                                                                                                                                                                                          | Min  | Тур | Max  | Unit | Туре |

|------|----------------------------------------------------------|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----|------|------|------|

|      |                                                          | Pi                    | ns VSUP and VDD                                                                                                                                                                                                                                                                                                                                       |      |     |      |      |      |

| 1.1  | Output Voltage (5.5V $\leq$ V <sub>SUP</sub> $\leq$ 40V) | V <sub>VDD1</sub>     | Without external MOS                                                                                                                                                                                                                                                                                                                                  | 4.75 | 5.0 | 5.25 | V    | _    |

| 1.3  | Total Output Current                                     | I <sub>VDD1</sub>     | transistor, I <sub>OUT</sub> ≤ 50mA                                                                                                                                                                                                                                                                                                                   | _    | _   | 50   | mA   | _    |

| 1.5  | Load Regulation                                          | V <sub>LoadReg1</sub> | Without external MOS<br>transistor, 1 to 50mA I <sub>OUT</sub><br>change                                                                                                                                                                                                                                                                              | _    | 20  | 60   | mV   | _    |

| 1.9  | Output Voltage $(5.5V \le V_{SUP} \le 40V)$              | V <sub>VDD2</sub>     | With external MOS transistor,                                                                                                                                                                                                                                                                                                                         | 4.7  | 5.0 | 5.3  | V    | _    |

| 1.11 | Total Output Current                                     | I <sub>VDD2</sub>     | $I_{OUT} \le 150$ mA  The stability is ensured with a decoupling capacitor between VDD and VSS: $C_{OUT} \ge 10 \mu F$ with ESR $\le 3\Omega$ .  The current capability can be increased up to 150mA by using an external N channel MOS transistor (see Figure 1). The main characteristics for choosing this component are VT < 1.8V and BVDSS > 40V | _    |     | 150  | mA   |      |

| 1.6  | Load Regulation                                          | V <sub>LoadReg2</sub> | With external MOS transistor,1 to 150mA I <sub>OUT</sub> change                                                                                                                                                                                                                                                                                       | _    | 65  | 150  | mV   | _    |

| 1.4  | Line Regulation (6V $\leq$ V <sub>SUP</sub> $\leq$ 16V)  | V <sub>LineReg</sub>  | I <sub>OUT</sub> = 1mA                                                                                                                                                                                                                                                                                                                                | _    | _   | _    | mV   | _    |

# 13 Low-Voltage Reset

Typical values reflect average measurements at  $6V \le V_{SUP} \le 16V$ ,  $V_{SS} = 0V$ ,  $T_J = -40^{\circ}C$  to  $+125^{\circ}C$ , unless otherwise noted

MC33690 Standalone Tag Reader Circuit, Rev. 5

| Parameter |                                      | Symbol             | Test Conditions and Comments  | Min                      | Тур  | Max                      | Unit | Туре |  |  |  |

|-----------|--------------------------------------|--------------------|-------------------------------|--------------------------|------|--------------------------|------|------|--|--|--|

|           | Pin LVR                              |                    |                               |                          |      |                          |      |      |  |  |  |

| 1.6       | Low Voltage Reset Low Threshold      | V <sub>LVRON</sub> | and the low-voltage reset are | 4.1                      | 4.35 | 4.6                      | V    | _    |  |  |  |

| 1.7       | Low Voltage Reset Hysteresis         | V <sub>LVRH</sub>  |                               | 50                       | 100  | 150                      | mV   | _    |  |  |  |

| 1.12      | Pull-up Current                      | I <sub>LVRUP</sub> | V <sub>LVR</sub> = 2.5V       | 5                        | 10   | 15                       | μА   | _    |  |  |  |

| 1.13      | Output Resistance in reset condition | R <sub>LVR</sub>   | V <sub>LVR</sub> = 2.5V       | 200                      | 370  | 500                      | Ω    | _    |  |  |  |

| 1.14      | Input Low Voltage                    | V <sub>ILLVR</sub> | _                             | 0                        | _    | 0.3 x<br>V <sub>DD</sub> | V    | _    |  |  |  |

| 1.15      | Input High Voltage                   | V <sub>IHLVR</sub> | _                             | 0.7 x<br>V <sub>DD</sub> | ı    | $V_{DD}$                 | V    | _    |  |  |  |

Figure 11. Low Voltage Reset Waveform

### 14 Oscillator

Typical values reflect average measurements at  $6V \le V_{SUP} \le 16V$ ,  $V_{SS} = 0V$ ,  $T_J = -40^{\circ}C$  to  $+125^{\circ}C$ , unless otherwise noted

**Table 8. Oscillator Specifications**

|     | Characteristic                                       | Symbol             | Test Condition and Comments                                                                                                                                                                     | Min | Тур | Max             | Unit | Туре |  |  |

|-----|------------------------------------------------------|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----------------|------|------|--|--|

|     | Pins XTAL1, XTAL2                                    |                    |                                                                                                                                                                                                 |     |     |                 |      |      |  |  |

| 8.0 | Input Capacitance                                    | C <sub>XTAL1</sub> | V <sub>XTAL1</sub> = 2.5V                                                                                                                                                                       | _   | 5   | _               | pF   | _    |  |  |

| 8.1 | Voltage gain V <sub>XTAL2</sub> / V <sub>XTAL1</sub> | A <sub>OSC</sub>   | V <sub>XTAL1</sub> = 2.5V                                                                                                                                                                       | _   | 25  | _               | _    | _    |  |  |

| 8.3 | Clock input level                                    | V <sub>XTAL1</sub> | This level ensures the circuit operation with an 8 MHz clock. It is applied through a capacitive coupling. A $1M\Omega$ resistor connected between XTAL1 and XTAL2 biases the oscillator input. | 1.5 | _   | V <sub>DD</sub> | Vpp  |      |  |  |

MC33690 Standalone Tag Reader Circuit, Rev. 5

# 15 Tag Reader

Typical values reflect average measurements at  $6V \le V_{SUP} \le 16V$ ,  $V_{SS} = 0V$ ,  $T_J = -40^{\circ}C$  to  $+125^{\circ}C$ , unless otherwise noted

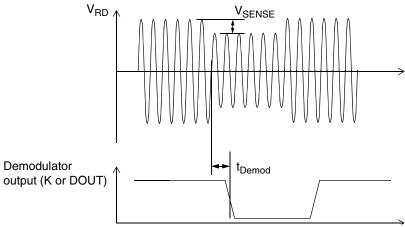

**Table 9. Tag Reader Specifications**

|                      | Parameter                                                                          | Symbol                 | Test Conditions and Comments                                                                                                                                                                                                                                               | Min | Тур | Max | Unit | Туре |  |  |

|----------------------|------------------------------------------------------------------------------------|------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|------|------|--|--|

| Demodulator (pin RD) |                                                                                    |                        |                                                                                                                                                                                                                                                                            |     |     |     |      |      |  |  |

| 2.0                  | Input Voltage Range                                                                | V <sub>INRD</sub>      | _                                                                                                                                                                                                                                                                          | 3   | 4   | 5   | V    | _    |  |  |

| 2.2                  | Input Modulation Frequency                                                         | F <sub>MOD</sub>       | _                                                                                                                                                                                                                                                                          | 0.5 | 4   | 8   | kHz  | _    |  |  |

| 2.3                  | Demodulator Sensitivity                                                            | V <sub>SENSE1</sub>    | $6.5V \le V_{SUP} \le 16V$<br>Sensitivity is measured in the following application conditions: $I_{ANTENNA} = 50$ mA peak, $V_{RD} = 4V$ peak, $C_{EXT} = 10$ nF, and square wave modulation $F_{MOD} = F_{TD1}/32$ . See Figure 12                                        | _   | 5   | 15  | mV   |      |  |  |

| 2.31                 | Demodulator Sensitivity                                                            | V <sub>SENSE2</sub>    | $6V \leq V_{SUP} < 6.5V$ The sensitivity is measured in the following application conditions: $I_{ANTENNA} = 50 \text{mA peak}, \\ V_{RD} = 4V \text{ peak}, C_{EXT} = 10 \text{nF}, \\ \text{and square wave modulation} \\ F_{MOD} = F_{TD1}/32 \\ \text{See Figure 12}$ | _   | 7   | 30  | mV   |      |  |  |

| 2.4                  | Demodulation Delay                                                                 | t <sub>Demod</sub>     | Configuration C Not including the delay due to the slew rate of the K output for configurations A and B See figure 12                                                                                                                                                      | _   | 7.5 | 10  | μS   | _    |  |  |

| 2.5                  | After Write Pulse Settling Time                                                    | t <sub>Settling1</sub> | _                                                                                                                                                                                                                                                                          | _   | 394 | 400 | μS   | _    |  |  |

| 2.6                  | Recovery Time after wake-up or reset from clock stable to demodulator valid output | t <sub>Settling2</sub> | Clock stable condition implies V <sub>XTAL1</sub> meets the specification (see page 15).                                                                                                                                                                                   | _   | 646 | 700 | μS   | _    |  |  |

|                      |                                                                                    | Dri                    | vers (pins TD1, TD2)                                                                                                                                                                                                                                                       |     | •   | •   |      | •    |  |  |

| 3.5                  | Output Carrier Frequency to Crystal Frequency Ratio                                | R <sub>FTD/FXT</sub>   | _                                                                                                                                                                                                                                                                          | _   | 64  | _   | _    | _    |  |  |

| 3.0                  | Turn on/off Delay                                                                  | t <sub>on/off</sub>    | _                                                                                                                                                                                                                                                                          | _   |     | 250 | ns   |      |  |  |

| 3.1                  | Driver1/2 Low Side Out. Resistance                                                 | R <sub>TDL</sub>       | I <sub>LOAD</sub> = 150mA DC                                                                                                                                                                                                                                               | _   | 2.4 | 4   | Ω    | _    |  |  |

| 3.2                  | Driver1/2 High Side Out. Resistance                                                | R <sub>TDH</sub>       | I <sub>LOAD</sub> = -150mA DC                                                                                                                                                                                                                                              |     | 2.1 | 4   | Ω    | _    |  |  |

MC33690 Standalone Tag Reader Circuit, Rev. 5

Figure 12. Demodulator Parameters Definition

# 16 ISO 9141 Interface

Typical values reflect average measurements at  $6V \le V_{SUP} \le 16V$ ,  $V_{SS} = 0V$ ,  $T_J = -40^{\circ}C$  to  $+125^{\circ}C$ , unless otherwise noted

Table 10. ISO 9141 Interface Specifications

|                          | Parameter                                 | Symbol              | Test Conditions and Comments                                               | Min                        | Тур  | Max                       | Unit | Туре |  |  |

|--------------------------|-------------------------------------------|---------------------|----------------------------------------------------------------------------|----------------------------|------|---------------------------|------|------|--|--|

| Receiver (pins K and AM) |                                           |                     |                                                                            |                            |      |                           |      |      |  |  |

| 4.0                      | Input Low Voltage                         | V <sub>IL</sub>     | _                                                                          | _                          | _    | 0.3 x<br>V <sub>SUP</sub> | V    | _    |  |  |

| 4.1                      | Input High Voltage                        | V <sub>IH</sub>     | _                                                                          | 0.65 x<br>V <sub>SUP</sub> | _    | 40                        | ٧    | _    |  |  |

| 4.2                      | Input Hysteresis Voltage                  | V <sub>HY1</sub>    | _                                                                          | 0.4                        | 0.65 | 1.3                       | V    | _    |  |  |

| 4.3                      | Biasing Current                           | I <sub>B</sub>      | $0V \le V_{IN} \le 16V$                                                    | 1                          | 3    | 5                         | μА   | _    |  |  |

| 4.31                     | Input Current                             | I <sub>BM</sub>     | -3 ≤ V <sub>IN</sub> < 0                                                   | -2                         | -1   | _                         | mA   | _    |  |  |

| 4.4                      | K to Rx delay                             | tdkrx               | _                                                                          |                            | 2    | 10                        | μS   | _    |  |  |

|                          |                                           | •                   | Driver (pin K)                                                             |                            |      |                           |      |      |  |  |

| 5.0                      | Output Falling Edge Slew Rate             | SR <sub>F</sub>     | $R_{Pull-up} = 510\Omega,$ Calculated from 20% to 80% of the output swing. | 3.5                        | 5    | 6.5                       | V/μs | _    |  |  |

| 5.1                      | Output Rising Edge Slew Rate              | SR <sub>R</sub>     |                                                                            | 3.5                        | 5    | 6.5                       | V/μs | _    |  |  |

| 5.2                      | Rise Fall Slew Rates Symmetry             | SR <sub>SYMET</sub> |                                                                            | -1                         | 0    | 1                         | V/μs | _    |  |  |

| 5.3                      | Output Low Voltage                        | V <sub>OLK</sub>    | I <sub>LOAD</sub> = 25mA                                                   | _                          | 1.1  | 1.4                       | V    | _    |  |  |

| 5.4                      | Input Current (driver switched on or off) | I <sub>IK</sub>     | $-3V \le V_{IN} \le 0V$                                                    | -2                         | _    | 0                         | mA   | _    |  |  |

| 5.5                      | Current Limitation Threshold              | ΙL                  | $0V \le V_{IN} \le 40V$                                                    | 35                         | 50   | 65                        | mA   | _    |  |  |

| 5.6                      | Thermal Shutdown Threshold                | TH <sub>SDWN</sub>  | _                                                                          | 130                        | 150  | 170                       | °C   | _    |  |  |

MC33690 Standalone Tag Reader Circuit, Rev. 5

# 17 Digital I/O

Typical values reflect average measurements at  $6V \le V_{SUP} \le 16V$ ,  $V_{SS} = 0V$ ,  $T_J = -40^{\circ}C$  to  $+125^{\circ}C$ , unless otherwise noted

Table 11. Digital I/O Specifications

|                       | Characteristic                    | Symbol           | Test Condition and Comments                                                   | Min                      | Тур | Max                      | Unit | Туре |  |  |  |

|-----------------------|-----------------------------------|------------------|-------------------------------------------------------------------------------|--------------------------|-----|--------------------------|------|------|--|--|--|

|                       | Input (pins MODE1, MODE2, AM, TX) |                  |                                                                               |                          |     |                          |      |      |  |  |  |

| 6.0                   | Input Low Voltage                 | V <sub>ILD</sub> | _                                                                             | 0                        | _   | 0.3 x<br>V <sub>DD</sub> | V    | _    |  |  |  |

| 6.1                   | Input High Voltage                | V <sub>IHD</sub> | _                                                                             | 0.7 x<br>V <sub>DD</sub> | _   | V <sub>DD</sub>          | V    | _    |  |  |  |

| 6.2                   | Input Hysteresis Voltage          | V <sub>HD</sub>  | _                                                                             | .24                      | .7  | 1                        | V    | _    |  |  |  |

| Output (pins DOUT,RX) |                                   |                  |                                                                               |                          |     |                          |      |      |  |  |  |

| 7.0                   | Output Low Voltage                | V <sub>OL</sub>  | I <sub>LOAD</sub> = 500uA                                                     | 0                        | 0.5 | 0.2 x<br>V <sub>DD</sub> | V    | _    |  |  |  |

| 7.1                   | Output High Voltage               | V <sub>OH</sub>  | I <sub>LOAD</sub> = -500uA                                                    | 0.8 x<br>V <sub>DD</sub> | 4.6 | V <sub>DD</sub>          | V    | _    |  |  |  |

| 7.2                   | Fall/Rise Time                    | t <sub>F/R</sub> | C <sub>LOAD</sub> =10pF,<br>Calculated from 10% to 90% of<br>the output swing | _                        | _   | 150                      | ns   | _    |  |  |  |

MC33690 Standalone Tag Reader Circuit, Rev. 5

### 18 Pin Definition and Function

The internal circuits connected to the pins of the device are shown in Figures 13 - 23, including the diodes used for ESD protection.

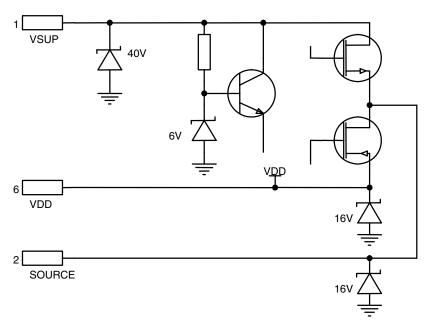

Figure 13. VSUP, VDD, and Source Internal Circuits

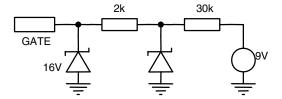

Figure 14. GATE Internal Circuits

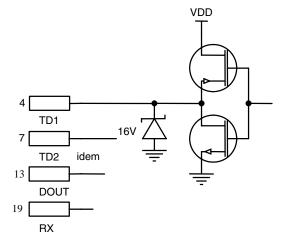

Figure 15. TD1, TD2, DOUT, and RX Internal Circuits

MC33690 Standalone Tag Reader Circuit, Rev. 5

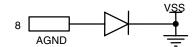

Figure 16. AGND Internal Circuits

Figure 17. CEXT Internal Circuits

Figure 18. RD Internal Circuits

Figure 19. MODE1, MODE2, and TX Internal Circuits

Figure 20. LVR Internal Circuits

Figure 21. XTAL2 and XTAL1 Internal Circuits

Figure 22. AM Internal Circuits

Figure 23. K Internal Circuits

# 19 Application Schemes

**Note:** If no external MOS transistor is necessary to increase the voltage regulator current capability, the pins GATE and SOURCE must be left unconnected. In this configuration, the outputs Rx and DOUT force a low level. C1 is not required for the STARC functionality and only acts as a reservoir of energy. To preserve the demodulator sensitivity, CEXT and R2 should be connected to AGND and VSS connected to AGND using a low resistance path.

Figure 24. Standalone Configuration with One-Wire Bus

#### **Application Schemes**

Note: If no external MOS transistor is necessary to increase the voltage regulator current capability, the pins GATE and SOURCE must be left unconnected. C<sub>1</sub> is not required for the STARC functionality and only acts as a reservoir of energy. To preserve the demodulator sensitivity, C<sub>EXT</sub> and R<sub>2</sub> should be connected to AGND and VSS connected to AGND using a low resistance path.

Figure 25. Standalone Configuration with Two-Wires Bus

MC33690 Standalone Tag Reader Circuit, Rev. 5

Freescale Semiconductor

24

Note: If no external MOS transistor is necessary to increase the voltage regulator current capability, the pins GATE and SOURCE must be left unconnected. C<sub>1</sub> is not required for the STARC functionality and only acts as a reservoir of energy. To preserve the demodulator sensitivity, C<sub>EXT</sub> and R<sub>2</sub> should be connected to AGND and VSS connected to AGND using a low resistance path.

Figure 26. Direct Connection to a Microcontroller

#### How to Reach Us:

**Home Page:**

www.freescale.com

Web Support:

http://www.freescale.com/support

**USA/Europe or Locations Not Listed:**

Freescale Semiconductor, Inc.

Technical Information Center, EL516

2100 East Elliot Road

Tempe, Arizona 85284

+1-800-521-6274 or +1-480-768-2130

www.freescale.com/support

Europe, Middle East, and Africa:

Freescale Halbleiter Deutschland GmbH Technical Information Center Schatzbogen 7 81829 Muenchen, Germany +44 1296 380 456 (English) +46 8 52200080 (English) +49 89 92103 559 (German) +33 1 69 35 48 48 (French) www.freescale.com/support

#### Japan:

Freescale Semiconductor Japan Ltd. Headquarters ARCO Tower 15F 1-8-1, Shimo-Meguro, Meguro-ku, Tokyo 153-0064 Japan 0120 191014 or +81 3 5437 9125 support.japan@freescale.com

#### Asia/Pacific:

Freescale Semiconductor Hong Kong Ltd. Technical Information Center 2 Dai King Street

Tai Po Industrial Estate

Tai Po, N.T., Hong Kong

+800 2666 8080

support.asia@freescale.com

For Literature Requests Only:

Freescale Semiconductor Literature Distribution Center

P.O. Box 5405

Denver, Colorado 80217

1-800-441-2447 or 303-675-2140

Fax: 303-675-2150

LDCForFreescaleSemiconductor@hibbertgroup.com

Document Number: SC33690DS

Rev. 5 02/2007 Information in this document is provided solely to enable system and software implementers to use Freescale Semiconductor products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits or integrated circuits based on the information in this document.

Freescale Semiconductor reserves the right to make changes without further notice to any products herein. Freescale Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in Freescale Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals", must be validated for each customer application by customer's technical experts. Freescale Semiconductor does not convey any license under its patent rights nor the rights of others. Freescale Semiconductor products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Freescale Semiconductor product could create a situation where personal injury or death may occur. Should Buyer purchase or use Freescale Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold Freescale Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Freescale Semiconductor was negligent regarding the design or manufacture of the part.

RoHS-compliant and/or Pb-free versions of Freescale products have the functionality and electrical characteristics as their non-RoHS-compliant and/or non-Pb-free counterparts. For further information, see <a href="http://www.freescale.com">http://www.freescale.com</a> or contact your Freescale sales representative.

For information on Freescale's Environmental Products program, go to http://www.freescale.com/epp.

Freescale<sup>™</sup> and the Freescale logo are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners. The Power Architecture and Power.org word marks and the Power and Power.org logos and related marks are trademarks and service marks licensed by Power.org © Freescale Semiconductor, Inc. 2007. All rights reserved.