### Freescale Semiconductor

### **Application Note**

Document Number: AN3266 Rev. 1, 5/2006

# **Getting Started with RS08**

by: Vincent Ko Systems Engineering Microcontroller Division

This application note is an introduction to the RS08 platform, an ultra low-cost 8-bit MCU core, from Freescale Semiconductor.

Section 1 provides information for the user to get started with RS08 and section 2 includes application discussions to demonstrate techniques and concepts, together with working examples.

### 1 Introduction to RS08

This section covers the RS08 architecture, programming model, and instruction set to help the user to gain a good understanding on the platform. Where necessary, cross references are provided to the popular Freescale HC08 and S08 platforms. In most cases, the MC9RS08KA2 device is used in examples to illustrate concepts.

#### **Contents**

| 1   | Intro  | duction to HS08               |

|-----|--------|-------------------------------|

|     | 1.1    | RS08 Architecture             |

|     | 1.2    | RS08 Instruction Set 6        |

|     | 1.3    | Paging Memory Scheme          |

|     | 1.4    | MCU Reset                     |

|     | 1.5    | Wait Mode                     |

|     | 1.6    | Stop Mode                     |

|     | 1.7    | Subroutine Call               |

|     | 1.8    | Interrupt                     |

| 2   | Emu    | lated ADC Application Example |

|     | 2.1    | Implementation                |

|     | 2.2    | Calibration                   |

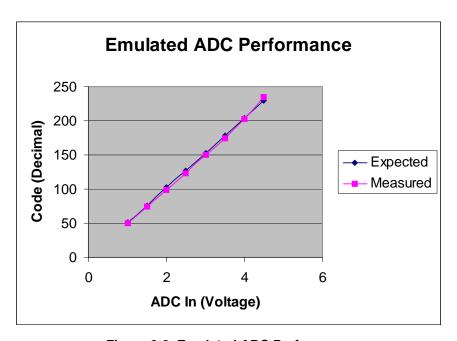

|     | 2.3    | Measurement Result            |

| Αрј | pendix | A                             |

|     | Proc   | ıram Listing                  |

This document contains information on a new product under development. Freescale reserves the right to change or discontinue this product without notice.

© Freescale Semiconductor, Inc., 2006. All rights reserved.

### 1.1 RS08 Architecture

The RS08 platform is developed for extremely low cost applications. Its hardware size is optimized and the overall system cost is reduced. The smaller hardware size allows the silicon to fit into a smaller package, such as the 6-pin dual flat no lead package (DFN). The RS08 platform retains a similar programming model as in the popular HC08/S08 platforms to allow easy source code migration between the platforms.

The main features of the RS08 platform are:

- Subset of S08 instruction set

- New instructions for shadow program counter (SPC) SHA and SLA

- New tiny and short addressing modes for code size optimization

- Maximum 16K-byte accessible memory space

- Eliminated vector fetch mechanism for interrupt and reset service

- Eliminated RAM stacking mechanism for subroutine call

- Single level hardware stacking for subroutine call

- Low power mode supported through the execution of STOP and WAIT instructions

- Stop wakeup through internal or external interrupt trigger

- Illegal address and opcode detection with reset

- Hardware security feature to protect unauthorized access to the non-volatile memory (NVM) area

- Debug and NVM program/erase support using single pin interface

### 1.1.1 CPU Registers

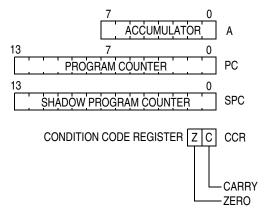

The RS08 CPU registers include an 8-bit general purpose accumulator (A), 14-bit program counter (PC), 14-bit shadow program counter (SPC), and a 2-bit conditional code register (CCR). The CCR contains two status flags and are tested for conditional branch instructions such as BCS and BEQ. Figure 1-1 shows the RS08 CPU registers.

Figure 1-1. RS08 CPU Registers

Getting Started with RS08, Rev. 1

The 8-bit general purpose accumulator A provides a primary data register for the RS08 CPU. Data can be read from memory into A with the LDA instruction. The data in A can be written into memory with the STA instruction. The new added exchange instructions, SHA and SLA, allow values to be exchanged between accumulator A and shadow program counter (SPC) high byte and low byte respectively.

The program counter (PC) contains the address of the next instruction or operand to be fetched as in the HC08/S08 platform. However, the PC in RS08 platform is 14-bit long, which means the maximum addressable space is 16K bytes.

In HC08/S08 platform, the return PC value is stacked into RAM during subroutine calls using JSR and BSR instructions. In RS08 platform, RAM stacking mechanism is eliminated, return address is saved into the SPC register. Upon completion of the subroutine, RTS instruction will restore the content of the PC from SPC. SPC only provides a single level of address saving, nested subroutine calls can be performed through software stacking. User firmware can utilize SHA and SLA instructions to swap the high byte and the low byte content of SPC to A, then stack them to RAM.

The status bits (Z and C) in condition code register (CCR) indicates the results of previous arithmetic and other operations. The bit definition is identical as in HC08/S08 platform. Please refer to RS08 Core Reference Manual for their detail definition.

### 1.1.2 Special Registers

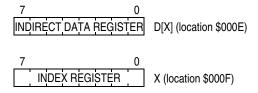

In additional to the CPU registers, there are two memory mapped registers that are tightly coupled with the core address generation. They are the indirect data register (D[X]) and the index register (X). These registers are located at \$000E and \$000F respectively.

Figure 1-2. RS08 Special Registers

Registers D[X] and X together perform indirect data access. The register X contains the address which is used when register D[X] is accessed. Figure 1-3 shows the index addressing scheme. The X and D[X] registers are not part of the CPU internal registers, but they are integrated seamlessly with the RS08 generic instruction set to form a pseudo instruction set.

Getting Started with RS08, Rev. 1

Figure 1-3. Index Addressing Scheme

### 1.1.3 Generic Addressing Mode

Whenever the MCU reads data from memory or writes data to memory, an addressing mode is used to determine the exact address whether data is read from or write to. Table 1-1 summarizes the generic addressing mode supported by the RS08 platform.

Table 1-1. RS08 Addressing Modes

| Addressing Mode      | Example              |

|----------------------|----------------------|

| Inherent Addressing  | CLRA, INCA, SHA, RTS |

| Direct Addressing    | LDA \$20, AND \$20   |

| Relative Addressing  | BRA, BCS, BEQ        |

| Immediate Addressing | LDA #9               |

| Tiny Addressing      | INC <\$0D            |

| Short Addressing     | CLR <\$1D            |

| Extended Addressing  | JMP, JSR             |

Getting Started with RS08, Rev. 1

### 1.1.3.1 Addressing Modes Common to HC08/S08 Platforms

The inherent addressing, direct addressing, relative addressing, immediate addressing, and extended addressing modes in RS08 have identical operation as in the HC08/S08 platform. Inherent addressing is used when the CPU inherently knows all the information needed to complete the instruction and no addressing information is supplied in the source code. Relative addressing is used to specify the offset address for branch instructions relative to the program counter. Immediate addressing is used when an explicit value to be used by the instruction is located immediately after the opcode in the instruction stream. Direct addressing is used to access operands located in direct address space (\$0000 through \$00FF). Extended addressing is used to specify 2-byte operand to the instructions. This addressing mode is only used in JMP and JSR instructions where the 14-bit target address is specified in the operand.

### 1.1.3.2 Tiny and Short Addressing Modes

Tiny and short addressing modes are introduced in the RS08 platform. These addressing modes have similar operations to direct addressing mode but the addressable space is limited. Only portion of direct address space within \$0000–\$00FF can be accessed by these addressing modes. However, all instructions associated with these addressing modes are single byte instructions. Maximizing the utilization of these instructions can reduce the overall code size.

Tiny addressing mode is capable of addressing only the first 16 bytes in the address map, from \$0000 to \$000F. This addressing mode is available for increment (INC), decrement (DEC), add (ADD), and subtract (SUB) instructions. Equivalent instructions are also available in direct addressing mode, 2-byte instructions, where the addressable space is from \$0000–\$00FF. User should add the less than symbol (<) before the operand in the source code as shown below, this forces the assembler to use tiny addressing instructions instead.

INC <\$0D DEC <\$0D ADD <\$0D SUB <\$0D

Short addressing mode is capable of addressing only the first 32 bytes in the address map, from \$0000 to \$001F. This addressing mode is available for clear (CLR), load accumulator A (LDA), and store accumulator A (STA) instructions. Similar to tiny addressing instructions equivalent instructions are also available in direct address mode. User should add the less than symbol (<) before the operand as shown below to force the assembler to use short addressing instructions.

CLR <\$1F LDA <\$1F STA <\$1F

### 1.1.3.3 Pseudo Addressing Modes

Using the special registers, D[X] and X, the RS08 generic instruction set can be used to emulate some of the accumulator X operations in the HC08/S08 architecture. This emulation is supported by the assembler/compiler and it is done during the time of compilation. When zero offset indexing instructions or register X related operations are involved, user can use the same HC08/S08 coding syntax for RS08 programming. During compilation the assembler will convert the pseudo RS08 instructions to equivalent generic RS08 instructions. This operation is transparent to the user.

Getting Started with RS08, Rev. 1

#### Introduction to RS08

Below summarizes the pseudo addressing modes supported by the RS08 architecture.

- Pseudo inherent addressing for example, TSTX, DBNZX is emulated by equivalent direct addressing operation where the operand is always loaded from register X location (\$000F). In some of these operations, such as DECX and INCX, the tiny and short addressing instructions are available. The pseudo instructions become single byte.

- Pseudo direct addressing for example, LDX \$20, STX \$20 is emulated by move (MOV) direct-direct operation. LDX operation is equivalent to moving operand to register X (\$000F). STX operation is equivalent to move the content of register X to operand targeted address.

- Pseudo immediate addressing for example, LDX #\$09 is emulated by move (MOV) immediate-direct operation. Register X is loaded by explicit data.

- Pseudo zero offset index addressing for example, ADD ,X is emulated by equivalent direct addressing operation where the operand is always loaded from register D[X] location (\$000E). Register D[X] itself holds the indirect data that its address is indicated by register X. Performing operation on register D[X] has equivalent operation as HC08/S08 style zero offset index addressing. RS08 platform preserves the same HC08/S08 style coding syntax which helps user to migrate source code among these platform. Below shows some coding examples.

```

LDA ,X

ADD ,X

DBNZ,X, rel

```

#### NOTE

Pseudo instructions are based on emulation, they have equivalent HC08/S08 operations. However in term of CPU cycle count and instruction byte count, they are not the same. Special care is needed for timing critical software before migrating source code from HC08/S08 platform to RS08 platform.

### 1.2 RS08 Instruction Set

The RS08 CPU core can be considered as a reduced version of S08 core. Most arithmetic operations are retained in the RS08 platform such that source code compatibility is maintained as much as possible. However, the RS08 platform is not intended for intensive mathematical calculations, therefore, nibble swap (NSA), multiple (MUL), and divide (DIV) operations were removed from the instruction set.

Since the stacking mechanism is removed, instructions involving the stack pointer (SP) that were in HC08/S08 core were removed from the RS08 core. Code condition register (CCR) contains two status flags, Z-bit and C-bit, only conditional branch instructions involving these bits were included.

Table 1-2 summarizes the difference between RS08 instruction set and S08 instruction set.

Getting Started with RS08, Rev. 1

Table 1-2. RS08 and S08 Instruction Set Comparison

| Description                                          | RS08                                                                              | S08                                                                                                       | Operation                                                                           |

|------------------------------------------------------|-----------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|

| Arithmetic Operations:                               |                                                                                   |                                                                                                           |                                                                                     |

| Add with Carry                                       | ADC #opr8<br>ADC opr8<br>ADC ,X 1<br>ADC X 1, 2                                   | ADC #opr8<br>ADC opr8<br>ADC opr16<br>ADC opr16,X<br>ADC opr16,X<br>ADC ,X<br>ADC opr8,SP<br>ADC opr16,SP | $A \leftarrow (A) + (M) + (C)$<br>$A \leftarrow (A) + (X) + (C)^{2}$                |

| Add without Carry                                    | ADD #opr8<br>ADD opr8<br>ADD opr4<br>ADD ,X <sup>1</sup><br>ADD X <sup>1, 2</sup> | ADD #opr8<br>ADD opr8<br>ADD opr16<br>ADD opr8,X<br>ADD opr16,X<br>ADD ,X<br>ADD opr8,SP<br>ADD opr16,SP  | $A \leftarrow (A) + (M)$ $A \leftarrow (A) + (X)^{2}$                               |

| Add Immediate Value (Signed) to Stack Pointer        |                                                                                   | AIS #opr8                                                                                                 | SP ← (SP) + (16 « M)                                                                |

| Add Immediate Value (Signed) to Index Register (H:X) |                                                                                   | AIX #opr8                                                                                                 | H:X ← (H:X) + (16 « M)                                                              |

| Arithmetic Shift Left<br>(Same as LSL)               | ASLA                                                                              | ASL opr8 ASLA ASLX ASL opr8,X ASL ,X ASL opr8,SP                                                          | C - 0 b7 b0                                                                         |

| Arithmetic Shift Right                               |                                                                                   | ASR opr8<br>ASRA<br>ASRX<br>ASR opr8,X<br>ASR ,X<br>ASR opr8,SP                                           | b7 b0                                                                               |

| Clear                                                | CLR opr8<br>CLR opr5<br>CLRA<br>CLRX 1<br>CLR ,X 1                                | CLR opr8 CLRA CLRX CLRH CLR opr8,X CLR ,X CLR opr8,SP                                                     | M ← \$00<br>A ← \$00<br>X ← \$00                                                    |

| Decimal Adjust<br>Accumulator                        |                                                                                   | DAA                                                                                                       | (A) <sub>10</sub>                                                                   |

| Decrement                                            | DEC opr8<br>DEC opr4<br>DECA<br>DECX 1<br>DEC ,X 1                                | DEC opr8 DECA DECX DEC opr8,X DEC ,X DEC opr8,SP                                                          | $M \leftarrow (M) - \$01$<br>$A \leftarrow (A) - \$01$<br>$X \leftarrow (X) - \$01$ |

| Divide                                               |                                                                                   | DIV                                                                                                       | A ← (H:A)/(X)<br>H ← Remainder                                                      |

| Increment                                            | INC opr8<br>INC opr4<br>INCA<br>INCX 1<br>INC ,X 1                                | INC opr8<br>INCA<br>INCX<br>INC opr8,X<br>INC ,X<br>INC opr8,SP                                           | $M \leftarrow (M) + \$01$<br>$A \leftarrow (A) + \$01$<br>$X \leftarrow (X) + \$01$ |

### **Introduction to RS08**

Table 1-2. RS08 and S08 Instruction Set Comparison (continued)

| Description                                | RS08                                                      | S08                                                                                                           | Operation                                                                                                                                            |

|--------------------------------------------|-----------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| Negate<br>(Two's Complement)               |                                                           | NEG opr8<br>NEGA<br>NEGX<br>NEG opr8,X<br>NEG ,X<br>NEG opr8,SP                                               | $M \leftarrow -(M) = \$00 - (M)$<br>$A \leftarrow -(A) = \$00 - (A)$<br>$X \leftarrow -(X) = \$00 - (X)$                                             |

| Subtract with Carry                        | SBC #opr8<br>SBC opr8<br>SBC ,X 1<br>SBC X 1, 2           | SBC #opr8<br>SBC opr8<br>SBC opr16<br>SBC opr8,X<br>SBC opr16,X<br>SBC ,X<br>SBC opr8,SP<br>SBC opr16,SP      | $A \leftarrow (A) - (M) - (C)$ $A \leftarrow (A) - (X) - (C)^{2}$                                                                                    |

| Subtract                                   | SUB #opr8<br>SUB opr8<br>SUB opr4<br>SUB,X 1<br>SUB X 1,2 | SUB #opr8<br>SUB opr8<br>SUB opr16<br>SUB opr16,X<br>SUB opr16,X<br>SUB ,X<br>SUB opr8,SP<br>SUB opr16,SP     | $\begin{array}{c} A \leftarrow (A) - (M) \\ A \leftarrow (A) - (X)^2 \end{array}$                                                                    |

| Logical Operations:                        |                                                           |                                                                                                               |                                                                                                                                                      |

| Logical AND                                | AND #opr8<br>AND opr8<br>AND X <sup>1</sup> , 2           | AND #opr8<br>AND opr8<br>AND opr16<br>AND opr8,X<br>AND opr16,X<br>AND opx8,SP<br>AND opr8,SP<br>AND opr16,SP | A ← (A) & (M)<br>A ← (A) & (X) <sup>2</sup>                                                                                                          |

| Clear Bit n in Memory                      | BCLR n,opr8<br>BCLR n,X 1, 2<br>BCLR n,D[X] 1, 2          | BCLR n, opr8                                                                                                  | Mn ← 0<br>Xn ← 0 <sup>2</sup>                                                                                                                        |

| Set Bit n in Memory                        | BSET n,opr8<br>BSET n,X 1, 2<br>BSET n,D[X] 1, 2          | BSET n, opr8                                                                                                  | Mn ← 1<br>Xn ← 1 <sup>2</sup>                                                                                                                        |

| Complement<br>(One's Complement)           | СОМА                                                      | COM opr8<br>COMA<br>COMX<br>COM opr8,X<br>COM ,X<br>COM opr8,SP                                               | $\begin{array}{l} M \leftarrow (\overline{M}) = \$FF - (M) \\ A \leftarrow (\overline{A}) = \$FF - (M) \\ X \leftarrow (X) = \$FF - (M) \end{array}$ |

| Exclusive OR<br>Memory with<br>Accumulator | EOR #opr8<br>EOR opr8<br>EOR ,X 1<br>EOR X 1, 2           | EOR #opr8<br>EOR opr16<br>EOR opr16,X<br>EOR opr16,X<br>EOR,X<br>EOR opr8,SP<br>EOR opr16,SP                  | $ \begin{array}{l} A \leftarrow (A \oplus M) \\ A \leftarrow (A \oplus X)^2 \end{array} $                                                            |

| Logical Shift Left<br>(Same as ASL)        | LSLA                                                      | LSL opr8<br>LSLA<br>LSLX<br>LSL opr8,X<br>LSL ,X<br>LSL opr8,SP                                               | C ←                                                                                                                                                  |

Getting Started with RS08, Rev. 1

Table 1-2. RS08 and S08 Instruction Set Comparison (continued)

| Description                                             | RS08                                                                  | S08                                                                                                      | Operation                                                         |

|---------------------------------------------------------|-----------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|

| Logical Shift Right                                     | LSRA                                                                  | LSR opr8<br>LSRA<br>LSRX<br>LSR opr8,X<br>LSR ,X<br>LSR opr8,SP                                          | 0 -> C b7 b0                                                      |

| Nibble Swap<br>Accumulator                              |                                                                       | NSA                                                                                                      | A ← (A[3:0]:A[7:4])                                               |

| Inclusive OR Accumulator and Memory                     | ORA #opr8<br>ORA opr8<br>ORA ,X <sup>1</sup><br>ORA X <sup>1, 2</sup> | ORA #opr8<br>ORA opr8<br>ORA opr16<br>ORA opr8,X<br>ORA opr16,X<br>ORA ,X<br>ORA opr8,SP<br>ORA opr16,SP | A ← (A)   (M)<br>A ← (A)   (X) <sup>2</sup>                       |

| Rotate Left through Carry                               | ROLA                                                                  | ROL opr<br>ROLA<br>ROLX<br>ROL opr,X<br>ROL ,X<br>ROL opr,SP                                             | b7 b0                                                             |

| Rotate Right through Carry                              | RORA                                                                  | ROR opr<br>RORA<br>RORX<br>ROR opr,X<br>ROR ,X<br>ROR opr,SP                                             | b7 b0                                                             |

| Branch Operations:                                      |                                                                       |                                                                                                          |                                                                   |

| Branch if Carry Bit Clear                               | BCC rel                                                               | BCC rel                                                                                                  | PC ← (PC) + \$0002 + rel ? (C) = 0                                |

| Branch if Carry Bit Set (Same as BLO)                   | BCS rel                                                               | BCS rel                                                                                                  | PC ← (PC) + \$0002 + rel ? (C) = 1                                |

| Branch if Equal                                         | BEQ rel                                                               | BEQ rel                                                                                                  | PC ← (PC) + \$0002 + rel ? (Z) = 1                                |

| Branch if Greater Than or Equal To (Signed Operands)    |                                                                       | BGE opr                                                                                                  | $PC \leftarrow (PC) + \$0002 + rel ? (N \oplus V) = 0$            |

| Branch if Greater Than (Signed Operands)                |                                                                       | BGT opr                                                                                                  | $PC \leftarrow (PC) + \$0002 + rel ? (Z)$<br>  $(N \oplus V) = 0$ |

| Branch if Half Carry Bit Clear                          |                                                                       | BHCC rel                                                                                                 | PC ← (PC) + \$0002 + rel ? (H) = 0                                |

| Branch if Half Carry Bit Set                            |                                                                       | BHCS rel                                                                                                 | PC ← (PC) + \$0002 + rel ? (H) = 1                                |

| Branch if Higher                                        |                                                                       | BHI rel                                                                                                  | PC ← (PC) + \$0002 + rel? (C)   (Z) = 0                           |

| Branch if Higher or Same (Same as BCC)                  | BHS rel                                                               | BHS rel                                                                                                  | PC ← (PC) + \$0002 + rel ? (C) = 0                                |

| Branch if IRQ Pin High                                  |                                                                       | BIH rel                                                                                                  | PC ← (PC) + \$0002 + rel ? <del>IRQ</del> = 1                     |

| Branch if IRQ Pin Low                                   |                                                                       | BIL rel                                                                                                  | PC ← (PC) + \$0002 + rel ? <del>IRQ</del> = 0                     |

| Branch if Less Than<br>or Equal To (Signed<br>Operands) |                                                                       | BLE opr                                                                                                  | PC ← (PC) + \$0002 + rel ? (Z)<br>  (N ⊕ V) = 1                   |

| Branch if Lower<br>(Same as BCS)                        | BLO rel                                                               | BLO rel                                                                                                  | PC ← (PC) + \$0002 + rel ? (C) = 1                                |

| Branch if Lower or Same                                 |                                                                       | BLS rel                                                                                                  | PC ← (PC) + \$0002 + rel? (C)   (Z) = 1                           |

### Getting Started with RS08, Rev. 1

### **Introduction to RS08**

Table 1-2. RS08 and S08 Instruction Set Comparison (continued)

| Description                           | RS08                                                                                | S08                                                                                                         | Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|---------------------------------------|-------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Branch if Less Than (Signed Operands) |                                                                                     | BLT opr                                                                                                     | PC ← (PC) + \$0002 + rel ? (N ⊕ V) =1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Branch if Interrupt Mask Clear        |                                                                                     | BMC rel                                                                                                     | PC ← (PC) + \$0002 + rel ? (I) = 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Branch if Minus                       |                                                                                     | BMI rel                                                                                                     | PC ← (PC) + \$0002 + rel ? (N) = 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Branch if Interrupt Mask Set          |                                                                                     | BMS rel                                                                                                     | PC ← (PC) + \$0002 + rel ? (I) = 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Branch if Not Equal                   | BNE rel                                                                             | BNE rel                                                                                                     | PC ← (PC) + \$0002 + rel ? (Z) = 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Branch if Plus                        |                                                                                     | BPL rel                                                                                                     | PC ← (PC) + \$0002 + rel ? (N) = 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Branch Always                         | BRA rel                                                                             | BRA rel                                                                                                     | PC ← (PC) + \$0002 + <i>rel</i>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Branch if Bit n in Memory Clear       | BRCLR n,opr8,rel<br>BRCLR n,X,rel 1, 2<br>BRCLR n,D[X],rel 1, 2                     | BRCLR n, opr8, rel                                                                                          | $PC \leftarrow (PC) + \$0003 + rel ? (Mn) = 0$<br>$PC \leftarrow (PC) + \$0003 + rel ? (Xn) = 0^{2}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Branch Never                          |                                                                                     | BRN rel                                                                                                     | PC ← (PC) + \$0002                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Branch if Bit <i>n</i> in Memory Set  | BRSET n,opr8,rel<br>BRSET n,X,rel 1, 2<br>BRSET n,D[X],rel 1, 2                     | BRSET n, opr8, rel                                                                                          | $PC \leftarrow (PC) + \$0003 + rel ? (Mn) = 1$<br>$PC \leftarrow (PC) + \$0003 + rel ? (Xn) = 1^{2}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Branch to Subroutine                  | BSR rel                                                                             | BSR rel                                                                                                     | For S08: $ \begin{array}{c} \text{PC} \leftarrow (\text{PC}) + \$0002; \; \text{push (PCL)} \\ \text{SP} \leftarrow (\text{SP}) - \$0001; \; \text{push (PCH)} \\ \text{SP} \leftarrow (\text{SP}) - \$0001 \\ \text{PC} \leftarrow (\text{PC}) + rel \\ \end{array} $ For RS08: $ \begin{array}{c} \text{PC} \leftarrow (\text{PC}) + 2 \\ \text{Push PC to shadow PC} \\ \text{PC} \leftarrow (\text{PC}) + rel \\ \end{array} $                                                                                                                                                                                                                                                                                                                              |

| Compare and Branch if Equal           | CBEQ opr8,rel<br>CBEQA #opr8,rel<br>CBEQ X rel 1, 2<br>CBEQ ,X,rel 1, 2             | CBEQ opr8,rel<br>CBEQA #opr8,rel<br>CBEQX #opr8,rel<br>CBEQ opr8, X+,rel<br>CBEQ X+,rel<br>CBEQ opr8,SP,rel | For S08: $ \begin{array}{c} For \ S08 \text{:} \\ PC \leftarrow (PC) + \$0003 + \mathit{rel} ? \ (A) - (M) = \$00 \\ PC \leftarrow (PC) + \$0003 + \mathit{rel} ? \ (A) - (M) = \$00 \\ PC \leftarrow (PC) + \$0003 + \mathit{rel} ? \ (X) - (M) = \$00 \\ PC \leftarrow (PC) + \$0003 + \mathit{rel} ? \ (A) - (M) = \$00 \\ PC \leftarrow (PC) + \$0002 + \mathit{rel} ? \ (A) - (M) = \$00 \\ PC \leftarrow (PC) + \$0004 + \mathit{rel} ? \ (A) - (M) = \$00 \\ PC \leftarrow (PC) + \$0003 + \mathit{rel} ? \ (A) - (M) = \$00 \\ PC \leftarrow (PC) + \$0003 + \mathit{rel} ? \ (A) - (M) = \$00 \\ PC \leftarrow (PC) + \$0003 + \mathit{rel} ? \ (A) - (M) = \$00 \\ PC \leftarrow (PC) + \$0003 + \mathit{rel} ? \ (A) - (X) = \$00^2 \\ \end{array} $ |

| Decrement and Branch if Not Zero      | DBNZ opr8,rel<br>DBNZA rel<br>DBNZX rel <sup>1</sup><br>DBNZ ,X,rel <sup>1, 2</sup> | DBNZ opr8,rel<br>DBNZA rel<br>DBNZX rel<br>DBNZ opr8, X,rel<br>DBNZ X,rel<br>DBNZ opr8, SP,rel              | $\begin{array}{c} A \leftarrow (A) - \$0001 \text{ or } M \leftarrow (M) - \$01 \text{ or } \\ X \leftarrow (X) - \$0001 \end{array}$ For \$08: PC \leftarrow (PC) + \\$0003 + rel \text{ if } (result) \neq 0 \text{ for DBNZ direct, } \text{ IX1} \\ PC \leftarrow (PC) + \\$0002 + rel \text{ if } (result) \neq 0 \text{ for DBNZA, DB-NZX, or IX} \\ PC \leftarrow (PC) + \\$0004 + rel \text{ if } (result) \neq 0 \text{ for DBNZ SP1} \\ For RS08: \text{PC} \leftarrow (PC) + \\$0003 + rel \text{ if } (result) \neq 0 \text{ for DBNZ direct, } \text{DBNZX, DBNZ, X} \\ PC \leftarrow (PC) + \\$0002 + rel \text{ if } (result) \neq 0 \text{ for DBNZA} \\ \end{arrow}                                                                            |

| Jump                                  | JMP opr16                                                                           | JMP opr8<br>JMP opr16<br>JMP opr8,X<br>JMP opr16,X<br>JMP ,X                                                | PC ← Jump Address                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

Getting Started with RS08, Rev. 1

Table 1-2. RS08 and S08 Instruction Set Comparison (continued)

| Description                              | RS08                                                                  | S08                                                                                                          | Operation                                                                                                                                                                                                                                                                                                                                                                              |  |  |

|------------------------------------------|-----------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Jump to Subroutine                       | JSR opr16                                                             | JSR opr8<br>JSR opr16<br>JSR opr16,X<br>JSR opr8,X<br>JSR ,X                                                 | For S08: $ \begin{array}{c} PC \leftarrow (PC) + n \ (n = 1, 2, \mathrm{or}\ 3) \\ Push\ (PCL); \ SP \leftarrow (SP) - \$0001 \\ Push\ (PCH); \ SP \leftarrow (SP) - \$0001 \\ PC \leftarrow Unconditional\ Address \\ \\ \mathbf{For}\ \mathbf{RS08:} \\ \begin{array}{c} PC \leftarrow (PC) + 3 \\ Push\ PC\ to\ shadow\ PC \\ PC \leftarrow Unconditional\ Address \\ \end{array} $ |  |  |

| Return from Subroutine                   | RTS                                                                   | RTS                                                                                                          | For S08:                                                                                                                                                                                                                                                                                                                                                                               |  |  |

| Data Verification Operations             | :                                                                     |                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

| Bit Test                                 |                                                                       | BIT #opr8 BIT opr8 BIT opr116 BIT opr8,X BIT opr16,X BIT, X BIT opr8,SP BIT opr16,SP                         | (A) & (M)                                                                                                                                                                                                                                                                                                                                                                              |  |  |

| Compare Accumulator with Memory          | CMP #opr8<br>CMP opr8<br>CMP ,X <sup>1</sup><br>CMP X <sup>1, 2</sup> | CMP #opr8<br>CMP opr8<br>CMP opr16<br>CMP opr8,X<br>CMP opr6,X<br>CMP opr8,SP<br>CMP opr8,SP<br>CMP opr16,SP | (A) – (M)<br>(A) – (X) <sup>2</sup>                                                                                                                                                                                                                                                                                                                                                    |  |  |

| Complement<br>(One's Complement)         |                                                                       | CPHX #opr8<br>CPHX opr8<br>CPHX opr16<br>CPHX opr8,SP                                                        | (H:X) - (M:M + \$0001)                                                                                                                                                                                                                                                                                                                                                                 |  |  |

| Compare Index Register (H:X) with Memory |                                                                       | CPX #opr8<br>CPX opr8<br>CPX opr16<br>CPX ,X<br>CPX opr8,X<br>CPX opr16,X<br>CPX opr16,X<br>CPX opr16,SP     | (X) – (M)                                                                                                                                                                                                                                                                                                                                                                              |  |  |

| Test for Negative or Zero                | TST opr8 <sup>1</sup><br>TSTA <sup>1</sup><br>TSTX <sup>1</sup>       | TST opr8 TSTA TSTX TST opr8,X TST ,X TST opr8,SP                                                             | (A) - \$00<br>(X) - \$00<br>(M) - \$00                                                                                                                                                                                                                                                                                                                                                 |  |  |

| Data Movement Operations:                | Data Movement Operations:                                             |                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

| Load Accumulator from Memory             | LDA #opr8<br>LDA opr8<br>LDA opr5<br>LDA ,X <sup>1</sup>              | LDA #opr8<br>LDA opr8<br>LDA opr16<br>LDA opr16,X<br>LDA ,X<br>LDA opr8,SP<br>LDA opr16,SP                   | A ← (M)                                                                                                                                                                                                                                                                                                                                                                                |  |  |

Getting Started with RS08, Rev. 1

### **Introduction to RS08**

Table 1-2. RS08 and S08 Instruction Set Comparison (continued)

| Description                                    | RS08                                                                                      | S08                                                                                                        | Operation                                                                                                                   |

|------------------------------------------------|-------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|

| Load Index Register (H:X) from Memory          |                                                                                           | LDHX #opr16<br>LDHX opr8<br>LDHX opr16<br>LDHX<br>LDHX opr8,X<br>LDHX opr16,X<br>LDHX opr8,SP              | H:X ← (M:M + \$0001)                                                                                                        |

| Load X (Index Register Low) from Memory        | LDX #opr8 <sup>1</sup><br>LDX opr8 <sup>1</sup>                                           | LDX #opr8<br>LDX opr8<br>LDX opr16<br>LDX opr16,X<br>LDX opr16,X<br>LDX ,X<br>LDX opr16,SP<br>LDX opr16,SP | X ← (M)                                                                                                                     |

| Move                                           | MOV opr8,opr8<br>MOV #opr8,opr8<br>MOV D[X],opr8 1<br>MOV opr8,D[X] 1<br>MOV #opr8,D[X] 1 | MOV opr8,opr8<br>MOV opr8,X+<br>MOV #opr8,opr8<br>MOV X+,opr8                                              | For S08/RS08:  (M) <sub>destination</sub> ← (M) <sub>source</sub> For S08 only:  H:X ← (H:X) + \$001 in IX+D and DIX+ Modes |

| Store Accumulator in Memory                    | STA <i>opr8</i><br>STA <i>opr5</i><br>STA ,X <sup>1</sup>                                 | STA opr8<br>STA opr16<br>STA opr8,X<br>STA opr16,X<br>STA ,X<br>STA opr8,SP<br>STA opr16,SP                | $M \leftarrow (A)$                                                                                                          |

| Store H:X (Index Reg.)                         |                                                                                           | STHX opr<br>STHX opr<br>STHX opr,SP                                                                        | (M:M + \$0001) ← (H:X)                                                                                                      |

| Store X (Index Register Low) in Memory         | STX opr8 <sup>1</sup>                                                                     | STX opr8<br>STX opr16<br>STX opr8,X<br>STX opr16,X<br>STX ,X<br>STX opr8,SP<br>STX opr16,SP                | M ← (X)                                                                                                                     |

| Transfer Accumulator to CCR                    |                                                                                           | TAP                                                                                                        | CCR ← (A)                                                                                                                   |

| Transfer Accumulator to X (Index Register Low) | TAX <sup>1</sup>                                                                          | TAX                                                                                                        | X ← (A)                                                                                                                     |

| Transfer CCR to Accumulator                    |                                                                                           | TPA                                                                                                        | A ← (CCR)                                                                                                                   |

| Transfer SP to Index Reg.                      |                                                                                           | TSX                                                                                                        | H:X ← (SP) + \$0001                                                                                                         |

| Transfer X (Index Reg. Low) to Accumulator     | TXA <sup>1</sup>                                                                          | TXA                                                                                                        | $A \leftarrow (X)$                                                                                                          |

| Transfer Index Reg. to SP                      |                                                                                           | TXS                                                                                                        | (SP) ← (H:X) – \$0001                                                                                                       |

| Other Operations:                              |                                                                                           | 1                                                                                                          |                                                                                                                             |

| Background                                     | BGND                                                                                      | BGND                                                                                                       | Enter Background Debug Mode                                                                                                 |

| Clear Carry Bit                                | CLC                                                                                       | CLC                                                                                                        | C ← 0                                                                                                                       |

| Clear Interrupt Mask Bit                       |                                                                                           | CLI                                                                                                        | I ← 0                                                                                                                       |

| No Operation                                   | NOP                                                                                       | NOP                                                                                                        | None                                                                                                                        |

| Push Accumulator onto Stack                    |                                                                                           | PSHA                                                                                                       | Push (A); SP ← (SP) – \$0001                                                                                                |

| Push H (Index Register High) onto<br>Stack     |                                                                                           | PSHH                                                                                                       | Push (H); SP ← (SP) – \$0001                                                                                                |

Getting Started with RS08, Rev. 1

Table 1-2. RS08 and S08 Instruction Set Comparison (continued)

| Description                             | RS08 | S08  | Operation                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-----------------------------------------|------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Push X (Index Register Low) onto Stack  |      | PSHX | Push (X); SP ← (SP) – \$0001                                                                                                                                                                                                                                                                                                                                                                                                |

| Pull Accumulator from Stack             |      | PULA | SP ← (SP + \$0001); Pull (A)                                                                                                                                                                                                                                                                                                                                                                                                |

| Pull H (Index Register High) from Stack |      | PULH | SP ← (SP + \$0001); Pull (H)                                                                                                                                                                                                                                                                                                                                                                                                |

| Pull X (Index Register Low) from Stack  |      | PULX | SP ← (SP + \$0001); Pull (X)                                                                                                                                                                                                                                                                                                                                                                                                |

| Reset Stack Pointer                     |      | RSP  | SP ← \$FF                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Return from Interrupt                   |      | RTI  | $\begin{array}{l} SP \leftarrow (SP) + \$0001; \; Pull \; (CCR) \\ SP \leftarrow (SP) + \$0001; \; Pull \; (A) \\ SP \leftarrow (SP) + \$0001; \; Pull \; (X) \\ SP \leftarrow (SP) + \$0001; \; Pull \; (PCH) \\ SP \leftarrow (SP) + \$0001; \; Pull \; (PCL) \end{array}$                                                                                                                                                |

| Swap Shadow PC High with A              | SHA  |      | A ⇔ SPCH                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Swap Shadow PC Low with A               | SLA  |      | A ⇔ SPCL                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Set Carry Bit                           | SEC  | SEC  | C ← 1                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Set Interrupt Mask Bit                  |      | SEI  | I ← 1                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Enable IRQ pin; Stop Osc.               | STOP | STOP | Stop Oscillator<br>I bit ← 0 for S08 only;                                                                                                                                                                                                                                                                                                                                                                                  |

| Software Interrupt                      |      | SWI  | $\begin{array}{l} PC \leftarrow (PC) + \$0001; \ Push \ (PCL) \\ SP \leftarrow (SP) - \$0001; \ Push \ (PCH) \\ SP \leftarrow (SP) - \$0001; \ Push \ (X) \\ SP \leftarrow (SP) - \$0001; \ Push \ (A) \\ SP \leftarrow (SP) - \$0001; \ Push \ (CCR) \\ SP \leftarrow (SP) - \$0001; \ I \leftarrow 1 \\ PCH \leftarrow Interrupt \ Vector \ High \ Byte \\ PCL \leftarrow Interrupt \ Vector \ Low \ Byte \\ \end{array}$ |

| Enable Interrupts; Stop Processor       | WAIT | WAIT | I bit ← 0 for S08 only;                                                                                                                                                                                                                                                                                                                                                                                                     |

#### NOTES:

### 1.2.1 Tiny and Short Addressing Mode Instructions

Tiny and short addressing mode instructions are single byte instructions. Maximizing the use of these instructions can efficiently improve the overall code density. Given the limited addressable space for these instructions, careful planning to allocate the most frequently used variables to be located within the tiny and short addressable area is recommended. Table 1-3 summarizes the tiny and short instructions support for the RS08 platform.

This is pseudo-instruction, the CPU cycle count and the instruction byte count may not be the same as the S08 equivalent instruction.

<sup>&</sup>lt;sup>2</sup> This emulated operation do not have an equivalent operation in S08 instruction set.

Table 1-3. RS08 Tiny and Short Addressing Mode Instructions

| Description                  | Tiny/Short Instruction | Addressable Space | Coding Example                              |

|------------------------------|------------------------|-------------------|---------------------------------------------|

| Load Accumulator from Memory | LDA opr5               | \$0000 to \$001F  | LDA < <i>\$1F</i><br>LDA <\$00              |

| Store Accumulator in Memory  | STA opr5               | \$0000 to \$001F  | STA <i>&lt;\$1F</i><br>STA <i>&lt;</i> \$00 |

| Clear                        | CLR opr5               | \$0000 to \$001F  | CLR <i>&lt;\$1F</i><br>CLR <i>&lt;</i> \$00 |

| Add without Carry            | ADD opr4               | \$0000 to \$000F  | ADD <i>&lt;\$0F</i><br>ADD <i>&lt;</i> \$00 |

| Subtract                     | SUB opr4               | \$0000 to \$000F  | SUB <i>&lt;\$0F</i><br>SUB <i>&lt;</i> \$00 |

| Increment                    | INC opr4               | \$0000 to \$000F  | INC <i>&lt;\$0F</i><br>INC <i>&lt;</i> \$00 |

| Decrement                    | DEC opr4               | \$0000 to \$000F  | DEC <i>&lt;\$0F</i><br>DEC <i>&lt;</i> \$00 |

### 1.2.2 Pseudo Instructions

Using register X located in \$000F and register D[X] located in \$000E, most HC08/S08 zero offset index addressing instructions and accumulator instructions can be emulated. This index addressing can be performed on virtually all direct addressing mode instructions. Table 1-4 summarizes all of the pseudo instructions supported in RS08 platform and their operations.

### **NOTE**

Instruction translation is done during time of compilation by the assembler, and is transparent to the user.

Table 1-4. Pseudo Instructions in RS08 Platform

| Operation                              | Pseudo<br>Instruction | Emulation              | Description                                                                                 | Bytes  | Cycles |

|----------------------------------------|-----------------------|------------------------|---------------------------------------------------------------------------------------------|--------|--------|

| Add with Carry                         | ADC ,X<br>ADC X       | ADC \$0E<br>ADC \$0F   | $\begin{array}{l} A \leftarrow (A) + (M) + (C) \\ A \leftarrow (A) + (X) + (C) \end{array}$ | 2<br>2 | 3<br>3 |

| Add without Carry                      | ADD ,X<br>ADD X       | ADD <\$0E<br>ADD <\$0F | $\begin{array}{c} A \leftarrow (A) + (M) \\ A \leftarrow (A) + (X) \end{array}$             | 1<br>1 | 3<br>3 |

| Logical AND                            | AND ,X                | AND \$0E               | A ← (A) & (M)                                                                               | 2      | 3      |

|                                        | AND X                 | AND \$0F               | A ← (A) & (X)                                                                               | 2      | 3      |

| Clear Bit n in Memory                  | BCLR n,D[X]           | BCLR n, \$0E           | Mn ← 0                                                                                      | 2      | 5      |

|                                        | BCLR n,X              | BCLR n, \$0F           | Xn ← 0                                                                                      | 2      | 5      |

| Branch if Bit <i>n</i> in Memory Clear | BRCLR n,D[X],rel      | BRCLR n, \$0E, rel     | PC ← (PC) + \$0003 + rel ? (Mn) = 0                                                         | 3      | 5      |

|                                        | BRCLR n,X,rel         | BRCLR n, \$0F, rel     | PC ← (PC) + \$0003 + rel ? (Xn) = 0                                                         | 3      | 5      |

| Branch if Bit <i>n</i> in Memory Set   | BRSET n,D[X],rel      | BRSET n, \$0E, rel     | PC ← (PC) + \$0003 + rel ? (Mn) = 1                                                         | 3      | 5      |

|                                        | BRSET n,X,rel         | BRSET n, \$0F, rel     | PC ← (PC) + \$0003 + rel ? (Xn) = 1                                                         | 3      | 5      |

| Set Bit <i>n</i> in Memory             | BSET n,D[X]           | BSET n, \$0E           | Mn ← 1                                                                                      | 2      | 5      |

|                                        | BSET n,X              | BSET n, \$0F           | Xn ← 1                                                                                      | 2      | 5      |

| Compare and Branch if Equal            | CBEQ ,X,rel           | CBEQ \$0E, rel         | PC ← (PC) + \$0003 + rel ? (A) − (M) = \$00                                                 | 3      | 5      |

|                                        | CBEQ X rel            | CBEQ \$0F, rel         | PC ← (PC) + \$0003 + rel ? (A) − (X) = \$00                                                 | 3      | 5      |

Getting Started with RS08, Rev. 1

Table 1-4. Pseudo Instructions in RS08 Platform (continued)

| Operation                                      | Pseudo<br>Instruction    | Emulation                               | Description                                                                                                                                       | Bytes       | Cycles      |

|------------------------------------------------|--------------------------|-----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-------------|

| Clear                                          | CLR ,X<br>CLRX           | CLR <\$0E<br>CLR <\$0F                  | M ← \$00<br>X ← \$00                                                                                                                              | 1           | 2<br>2      |

| Compare Accumulator with Memory                | CMP ,X<br>CMP X          | CMP \$0E<br>CMP \$0F                    | (A) – (M)<br>(A) – (X)                                                                                                                            | 2<br>2      | 3<br>3      |

| Decrement and Branch if Not<br>Zero            | DBNZ ,X,rel<br>DBNZX rel | DBNZ \$0E, rel<br>DBNZ \$0F, rel        | $\begin{array}{c} M \leftarrow (M) - \$01 \\ X \leftarrow (X) - \$01 \\ PC \leftarrow (PC) + \$0003 + rel \text{ if (result)} \neq 0 \end{array}$ | 3<br>3      | 6<br>6      |

| Decrement                                      | DEC ,X<br>DECX           | DEC <\$0E<br>DEC <\$0F                  | $ \begin{array}{c} M \leftarrow (M) - \$01 \\ X \leftarrow (X) - \$01 \end{array} $                                                               | 1           | 4<br>4      |

| Exclusive OR<br>Memory with<br>Accumulator     | EOR ,X<br>EOR X          | EOR \$0E<br>EOR \$0F                    | $\begin{array}{c} A \leftarrow (A \oplus M) \\ A \leftarrow (A \oplus X) \end{array}$                                                             | 2<br>2      | 3<br>3      |

| Increment                                      | INC ,X<br>INCX           | INC <\$0E<br>INC <\$0F                  | $M \leftarrow (M) + \$01 \\ X \leftarrow (X) + \$01$                                                                                              | 1           | 4<br>4      |

| Load Accumulator from Memory                   | LDA ,X                   | LDA <\$0E                               | A ← (M)                                                                                                                                           | 1           | 3           |

| Load X (Index Register Low) from Memory        | LDX #opr8<br>LDX opr8    | MOV #opr8, \$0F<br>MOV opr8, \$0F       | X ← (M)                                                                                                                                           | 3<br>3      | 4<br>5      |

| Inclusive OR Accumulator and Memory            | ORA ,X<br>ORA X          | ORA \$0E<br>ORA \$0F                    | $\begin{array}{c} A \leftarrow (A) \mid (M) \\ A \leftarrow (A) \mid (X) \end{array}$                                                             | 2<br>2      | 3<br>3      |

| Subtract with Carry                            | SBC ,X<br>SBC X          | SBC \$0E<br>SBC \$0F                    | $\begin{array}{c} A \leftarrow (A) - (M) - (C) \\ A \leftarrow (A) - (X) - (C) \end{array}$                                                       | 2<br>2      | 3<br>3      |

| Store Accumulator in Memory                    | STA ,X                   | STA <\$0E                               | M ← (A)                                                                                                                                           | 1           | 2           |

| Store X (Index Register Low) in Memory         | STX opr8                 | MOV \$0F, opr8                          | $M \leftarrow (X)$                                                                                                                                | 3           | 5           |

| Subtract                                       | SUB ,X<br>SUB X          | SUB <\$0E<br>SUB <\$0F                  | $\begin{array}{c} A \leftarrow (A) - (M) \\ A \leftarrow (A) - (X) \end{array}$                                                                   | 1           | 3           |

| Transfer Accumulator to X (Index Register Low) | TAX                      | STA <\$0F                               | X ← (A)                                                                                                                                           | 1           | 2           |

| Test for Negative or Zero                      | TST opr8<br>TSTA<br>TSTX | MOV opr8, opr8<br>ORA #\$00<br>MOV X, X | (M) - \$00<br>(A) - \$00<br>(X) - \$00                                                                                                            | 3<br>2<br>3 | 5<br>2<br>5 |

| Transfer X (Index Reg. Low) to Accumulator     | TXA                      | LDA <\$0F                               | A ← (X)                                                                                                                                           | 1           | 3           |

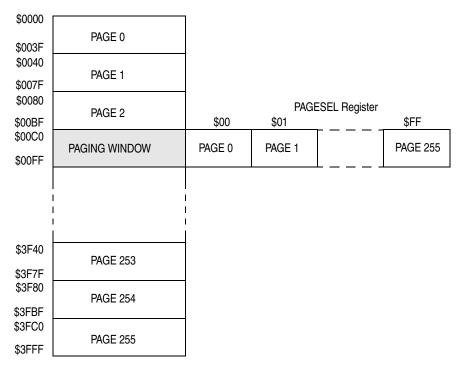

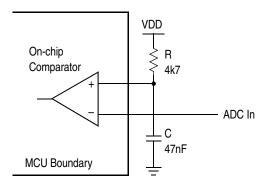

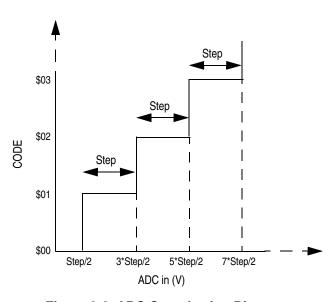

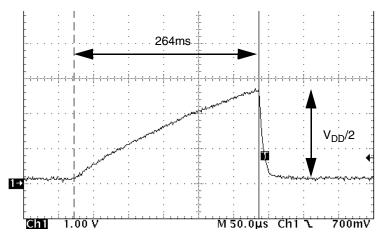

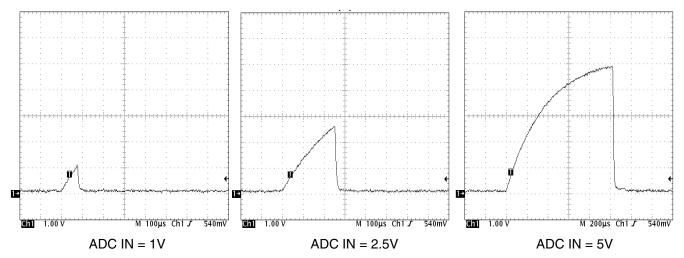

### 1.3 Paging Memory Scheme