# **External Memory Interface Handbook Volume 3**

# Section III. QDR II and QDR II+ SRAM Controller with UniPHY User Guide

101 Innovation Drive San Jose, CA 95134 www.altera.com

EMI\_QDRII\_UG-2.1

Document last updated for Altera Complete Design Suite version:

Document publication date:

10.1 December 2010

© 2010 Altera Corporation. All rights reserved. ALTERA, ARRIA, CYCLONE, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS and STRATIX are Reg. U.S. Pat. & Tm. Off. and/or trademarks of Altera Corporation in the U.S. and other countries. All other trademarks and service marks are the property of their respective holders as described at www.altera.com/common/legal.html. Altera warrants performance of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Altera. Altera customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

## **Contents**

| Chapter 1. About This IP                                           |             |

|--------------------------------------------------------------------|-------------|

| Release Information                                                | 1–1         |

| Device Family Support                                              |             |

| Features                                                           |             |

| Unsupported Features                                               |             |

| MegaCore Verification                                              |             |

| Resource Utilization                                               |             |

| System Requirements                                                | 1–4         |

| Chapter 2. Getting Started                                         |             |

| Installation and Licensing                                         | <b>2</b> –1 |

| Design Flows                                                       |             |

| MegaWizard Plug-In Manager Flow                                    |             |

| Specifying Parameters                                              |             |

| Simulate the IP Core                                               |             |

| SOPC Builder Design Flow                                           | 2-5         |

| Specify Parameters                                                 | 2-5         |

| Complete the SOPC Builder System                                   |             |

| Simulate the System                                                | 2–7         |

| Qsys System Integration Tool Design Flow                           |             |

| Specify Parameters                                                 | 2–8         |

| Complete the Qsys System                                           |             |

| Simulate the System                                                |             |

| HardCopy Migration Design Guidelines                               |             |

| Differences in UniPHY IP Generated with HardCopy Migration Support |             |

| ROM Loader for Designs Using Nios II Sequencer                     |             |

| PLL/DLL Run-time Reconfiguration                                   |             |

| Generated Files                                                    |             |

| MegaWizard Plug-in Manager Flow                                    |             |

| Synthesis                                                          |             |

| Simulation                                                         |             |

| Example Design                                                     |             |

| SOPC Builder Flow                                                  |             |

| Qsys Flow                                                          |             |

| Synthesis                                                          |             |

| Verilog Simulation                                                 |             |

| VHDL Simulation                                                    | 2–18        |

| Chapter 3. Parameter Settings                                      |             |

| General Settings                                                   | 3–1         |

| Clocks                                                             | 3–1         |

| Advanced PHY Settings                                              |             |

| Topology                                                           |             |

| Controller Settings                                                |             |

| Memory Parameters                                                  |             |

| Memory Timing                                                      |             |

| Board Settings                                                     |             |

| Intersymbol Interference                                           | 3-4         |

iv Contents

| Board Skews                                                 | 3–4             |

|-------------------------------------------------------------|-----------------|

| Chapter 4. Constraining and Compiling                       |                 |

| Add Pin and DQ Group Assignments                            | 4–1             |

| Board Settings                                              |                 |

| Compile the Design                                          |                 |

| Chapter 5. Functional Description—Controller                |                 |

| Block Description                                           | 5–1             |

| Avalon-MM Slave Read and Write Interfaces                   | 5–1             |

| Command Issuing FSM                                         |                 |

| AFI                                                         |                 |

| Avalon-MM and Memory Data Width                             |                 |

| Signal Description                                          |                 |

| Avalon-MM Slave Read Interface                              |                 |

| Avalon-MM Slave Write Interface                             |                 |

| Chapter 6. Functional Description—UniPHY                    |                 |

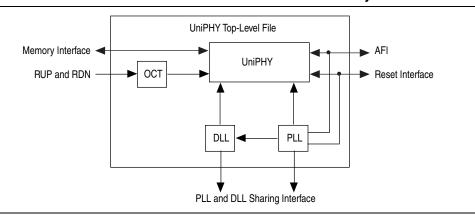

| Block Description                                           | 6 1             |

| I/O Pads                                                    |                 |

| Reset and Clock Generation                                  |                 |

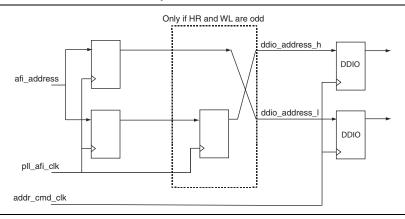

| Address and Command Datapath                                |                 |

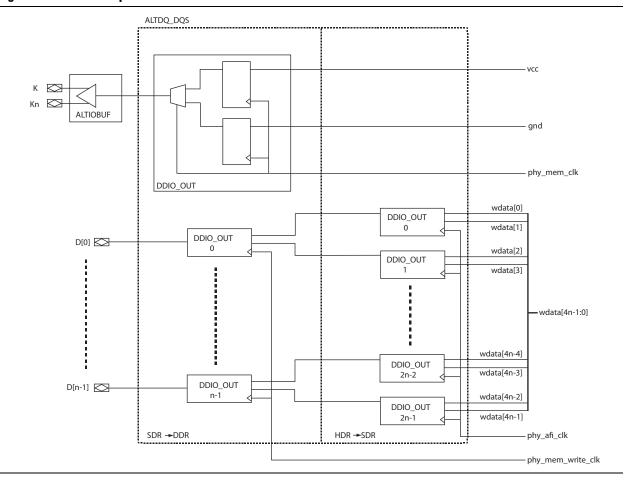

| Write Datapath                                              |                 |

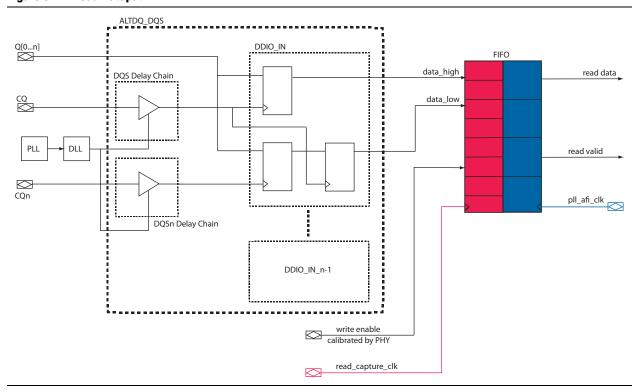

| Read Datapath                                               |                 |

| Sequencer                                                   |                 |

| Interfaces                                                  |                 |

| The Memory Interface                                        |                 |

| The DLL and PLL Sharing Interface                           |                 |

| The OCT Sharing Interface                                   |                 |

| UniPHY Signals                                              |                 |

| AFI Signal Names                                            |                 |

| PHY-to-Controller Interfaces                                |                 |

| Using a Custom Controller                                   |                 |

| Using a Vendor-Specific Memory Model                        |                 |

| Chapter 7. Functional Description—Example Top-Level Project |                 |

| Example Driver                                              | 7 2             |

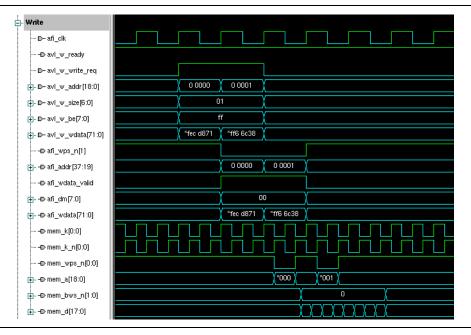

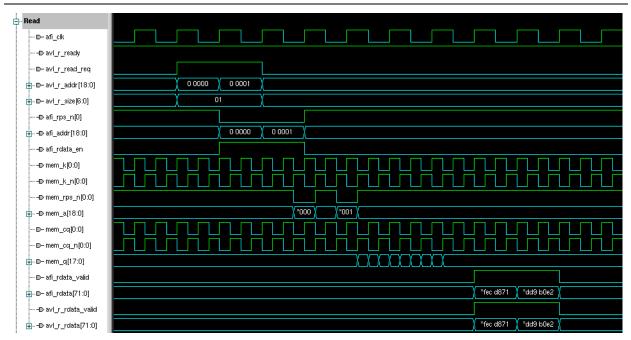

| Read and Write Generation                                   |                 |

| Individual Read and Write Generation                        |                 |

| Block Read and Write Generation                             |                 |

| Address and Burst Length Generation                         |                 |

| Sequential Addressing                                       |                 |

| Random Addressing                                           |                 |

| Sequential and Random Interleaved Addressing                |                 |

| Example Driver Signals                                      |                 |

| Example Driver Add-Ons                                      |                 |

| User Refresh Generator                                      |                 |

| Refresh Monitor                                             |                 |

| Data Corrupter                                              |                 |

| Data Corrupter                                              | , <del>-1</del> |

| Chapter 8. Latency Variable Controller Latency              | 8–1             |

Contents

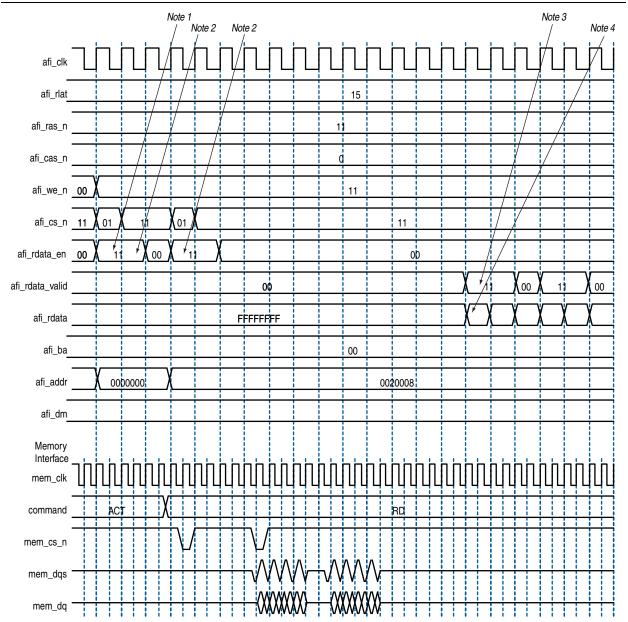

## **Chapter 9. Timing Diagrams**

#### **Additional Information**

| Document Revision History | Info-1 |

|---------------------------|--------|

| How to Contact Altera     | Info-1 |

| Typographic Conventions   | Info-2 |

vi Contents

The Altera QDR II and QDR II+ SRAM controllers with UniPHY provide simplified interfaces to industry-standard QDR II and QDR II+ SRAM.

The QDR II and QDR II+ SRAM controllers with UniPHY offer full-rate or half-rate QDR II and QDR II+ SRAM interfaces. The UniPHY IP is an interface between a memory controller and memory devices and performs read and write operations to the memory. The UniPHY IP creates the datapath between the memory device and the memory controller and user logic in various Altera devices.

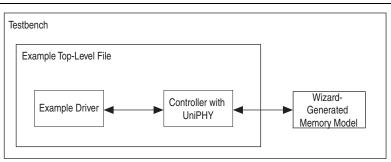

The Quartus II software generates an example top-level project, consisting of an example driver, and your QDR II or QDR II+ SRAM controller custom variation. The controller instantiates an instance of the UniPHY.

The example top-level project is a fully-functional design that you can simulate, synthesize, and use in hardware. The example driver is a self-test module that issues read and write commands to the controller and checks the read data to produce the pass or fail and test-complete signals.

For device families not supported by the UniPHY IP, use the Altera legacy integrated static datapath and controller MegaCore functions.

You can, alternatively, create your own memory interface datapath using the ALTDLL and ALTDQ\_DQS megafunctions, available in the Quartus II software, but you then must consider all of the aspects of the design including timing analysis and design constraints.

The UniPHY IP offers the Altera PHY interface (AFI). The AFI results in a simple connection between the PHY and controller.

## **Release Information**

Table 1–1 provides information about this release of the QDR II and QDR II+ SRAM controllers with UniPHY.

Table 1-1. Release Information

| Item           | Description   |  |

|----------------|---------------|--|

| Version        | 10.1          |  |

| Release Date   | December 2010 |  |

| Ordering Codes | IP-QDRII/UNI  |  |

| Vendor ID      | 6AF7          |  |

## **Device Family Support**

IP cores provide the following levels of support for target Altera device families:

- For FPGA device support:

- Preliminary—verified with preliminary timing models for this device

- Final—verified with final timing models for this device

- For ASIC devices (HardCopy families)

- HardCopy companion—verified with preliminary timing models for HardCopy companion device

- HardCopy compilation—verifed with final timing models for HardCopy device

Table 1–2 shows the level of support offered by the QDR II and QDR II+ SRAM controllers to each of the Altera device families.

For information about supported clock rates for external memory interfaces, refer to the *External Memory Interface System Specifications* section in volume 1 of the *External Memory Interface Handbook*.

Table 1-2. Device Family Support

| Device Family             | Support            |

|---------------------------|--------------------|

| Arria <sup>®</sup> II GX  | Final              |

| Arria II GZ               | Preliminary        |

| HardCopy <sup>®</sup> III | HardCopy companion |

| HardCopy IV               | HardCopy companion |

| Stratix <sup>®</sup> III  | Final              |

| Stratix IV                | Final              |

| Stratix V                 | Preliminary        |

| Other device families     | No support         |

## **Features**

Table 1–3 summarizes key feature support for the QDR II and QDR II+ SRAM Controllers with UniPHY.

Table 1–3. Key Feature Support for QDR II and QDR II+ SRAM Controllers with UniPHY (Part 1 of 2)

| Key Feature                             | QDR II SDRAM UniPHY | QDR II+ SDRAM UniPHY |

|-----------------------------------------|---------------------|----------------------|

| High-performance controller (HPC)       | _                   | _                    |

| High-performance controller II (HPC II) | ✓                   | ✓                    |

| Half-rate core logic and user interface | ✓                   | ✓                    |

| Full-rate core logic and user interface | ✓                   | ✓                    |

| Burst length (half-rate)                | 4                   | 4                    |

| Burst length (full-rate)                | 2 or 4              | 2 or 4               |

Table 1–3. Key Feature Support for QDR II and QDR II+ SRAM Controllers with UniPHY (Part 2 of 2)

| Key Feature                                              | QDR II SDRAM UniPHY | QDR II+ SDRAM UniPHY |

|----------------------------------------------------------|---------------------|----------------------|

| Reduced controller latency <sup>(1)</sup> <sup>(2)</sup> | ✓                   | ✓                    |

| Read latency                                             | 1.5                 | 2 or 2.5             |

| Maximum data width                                       | 72 bits             | 72 bits              |

| ODT (in memory device)                                   | _                   | ✓                    |

| x36 emulation mode <sup>(3)</sup>                        | ✓                   | ✓                    |

#### Notes for Table 1-3:

- (1) The maximum achievable clock rate when reduced controller latency is selected must be attained through Quatrus II software timing analysis of your complete design.

- (2) Not available in Arria II GX devices.

- (3) Emulation mode allows emulation of a larger memory-width interface using multiple smaller memory-width interfaces. For example, an x36 QDR II or QDR II+ interface can be emulated using two x18 interfaces.

## **Unsupported Features**

Table 1–4 summarizes unsupported features for the QDR II and QDR II+ SRAM Controllers with UniPHY.

Table 1-4. Unsupported Features for the QDR II and QDR II+ SRAM Controllers with UniPHY

| Memory Protocol | Unsupported Feature                                                                       |  |  |

|-----------------|-------------------------------------------------------------------------------------------|--|--|

|                 | Cyclone III devices                                                                       |  |  |

|                 | Cyclone IV devices                                                                        |  |  |

|                 | Deterministic latency                                                                     |  |  |

|                 | ECC                                                                                       |  |  |

| QDR II SRAM     | Memory device ODT                                                                         |  |  |

|                 | Multiple chip select                                                                      |  |  |

|                 | VHDL support for Arria II GX, Arria II GZ, Stratix III, Stratix IV, and Stratix V devices |  |  |

|                 | x36 emulation mode for Stratix V devices                                                  |  |  |

|                 | Cyclone III devices                                                                       |  |  |

|                 | Cyclone IV devices                                                                        |  |  |

|                 | Deterministic latency                                                                     |  |  |

| QDR II+ SRAM    | ECC                                                                                       |  |  |

| abit iii oiwiwi | Multiple chip select                                                                      |  |  |

|                 | VHDL support for Arria II GX, Arria II GZ, Stratix III, Stratix IV, and Stratix V devices |  |  |

|                 | x36 emulation mode for Stratix V devices                                                  |  |  |

## **MegaCore Verification**

Altera has carried out extensive random, directed tests with functional test coverage using industry-standard models to ensure the functionality of the QDR II and QDR II+ SRAM controllers with UniPHY.

Altera verifies that the current version of the Quartus II software compiles the previous version of each MegaCore function. The *MegaCore IP Library Release Notes and Errata* report any exceptions to this verification. Altera does not verify compilation with MegaCore function versions older than one release.

#### **Resource Utilization**

This section lists resource utilization for the QDR II and QDR II+ SRAM controllers with UniPHY for supported device families. Resource utilizations are derived with all parameters at their default values.

Table 1–5 shows the typical resource usage of the QDR II and QDR II+ SRAM controllers with UniPHY in the current version of Quartus II software for Arria II GX devices.

Table 1-5. Resource Utilization in Arria II GX Devices

| PHY<br>Rate | Memory<br>Width<br>(Bits) | Combinational<br>ALUTS | Logic Registers | Memory<br>(Bits) | M9K<br>Blocks |

|-------------|---------------------------|------------------------|-----------------|------------------|---------------|

|             | 9                         | 620                    | 701             | 0                | 0             |

| Half        | 18                        | 921                    | 1122            | 0                | 0             |

|             | 36                        | 1534                   | 1964            | 0                | 0             |

|             | 9                         | 584                    | 708             | 0                | 0             |

| Full        | 18                        | 850                    | 1126            | 0                | 0             |

|             | 36                        | 1387                   | 1962            | 0                | 0             |

Table 1–6 shows the typical resource usage of the QDR II and QDR II+ SRAM controllers with UniPHY in the current version of Quartus II software for Arria II GZ, Stratix III, Stratix IV, and Stratix V devices.

Table 1–6. Resource Utilization in Arria II GZ, Stratix III, Stratix IV, and Stratix V Devices

| PHY<br>Rate | Memory<br>Width<br>(Bits) | Combinational<br>ALUTS | Logic Registers | Memory<br>(Bits) | M9K<br>Blocks |

|-------------|---------------------------|------------------------|-----------------|------------------|---------------|

|             | 9                         | 602                    | 641             | 0                | 0             |

| Half        | 18                        | 883                    | 1002            | 0                | 0             |

|             | 36                        | 1457                   | 1724            | 0                | 0             |

|             | 9                         | 586                    | 708             | 0                | 0             |

| Full        | 18                        | 851                    | 1126            | 0                | 0             |

|             | 36                        | 1392                   | 1962            | 0                | 0             |

## **System Requirements**

The QDR II and QDR II+ SRAM controllers with UniPHY are part of the MegaCore IP Library, which is distributed with the Quartus II software.

For system requirements and installation instructions, refer to *Altera Software Installation & Licensing*.

This chapter provides a general overview of the Altera IP core design flow to help you quickly get started with any Altera IP core. The Altera IP Library is installed as part of the Quartus II installation process. You can select and parameterize any Altera IP core from the library. Altera provides an integrated parameter editor that allows you to customize IP cores to support a wide variety of applications. The parameter editor guides you through the setting of parameter values and selection of optional ports. The following sections describe the general design flow and use of Altera IP cores.

## **Installation and Licensing**

The Altera IP Library is distributed with the Quartus II software and downloadable from the Altera website (www.altera.com).

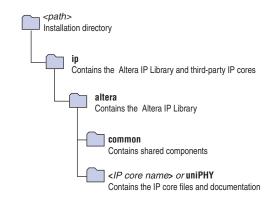

Figure 2–1 shows the directory structure after you install an Altera IP core, where *<path>* is the installation directory. The default installation directory on Windows is **C:\altera\**<*version number>*; on Linux it is */opt/altera*<*version number>*.

Figure 2-1. IP core Directory Structure

You can evaluate an IP core in simulation and in hardware until you are satisfied with its functionality and performance. Some IP cores require that you purchase a license for the IP core when you want to take your design to production. After you purchase a license for an Altera IP core, you can request a license file from the Altera Licensing page of the Altera website and install the license on your computer. For additional information, refer to *Altera Software Installation and Licensing*.

## **Design Flows**

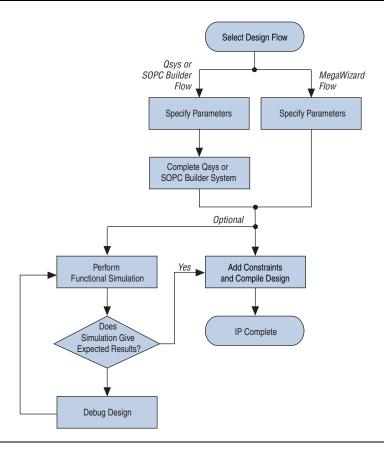

You can use the following flow(s) to parameterize Altera IP cores:

- MegaWizard Plug-In Manager Flow

- SOPC Builder Flow

- Qsys Flow

Altera's Qsys system integration tool is now available as beta for evaluation in the Quartus II software subscription edition version 10.1. Altera does not recommend using the beta release of Qsys in the Quartus II software version 10.1 for designs that are close to completion and are meeting design requirements. Before using Qsys, review the *Quartus II Software Version 10.1 Release Notes* and *AN 632: SOPC Builder to Qsys Migration Guidelines* for known issues and limitations. To submit general feedback or technical support on the beta release of Qsys, submit a service request through **mysupport.altera.com**. Alternatively, to submit general feedback, click **Feedback** on the Quartus II software Help menu.

Figure 2-2. Design Flows

The MegaWizard Plug-In Manager flow offers the following advantages:

- Allows you to parameterize an IP core variant and instantiate into an existing design

- For some IP cores, this flow generates a complete example design and testbench.

The SOPC Builder flow offer the following advantages:

- Generates simulation environment

- Allows you to integrate Altera-provided custom components

- Uses Avalon<sup>®</sup>memory-mapped (Avalon-MM) interfaces

The Qsys flow offers the following additional advantages over SOPC Builder:

- Provides visualization of hierarchical designs

- Allows greater performance through interconnect elements and pipelining

- Provides closer integration with the Quartus II software

# MegaWizard Plug-In Manager Flow

The MegaWizard Plug-In Manager flow allows you to customize your IP core and manually integrate the function into your design.

#### **Specifying Parameters**

To specify IP core parameters with the MegaWizard Plug-In Manager, follow these steps:

- 1. Create a Quartus II project using the **New Project Wizard** available from the File menu.

- 2. In the Quartus II software, launch the **MegaWizard Plug-in Manager** from the Tools menu, and follow the prompts in the MegaWizard Plug-In Manager interface to create or edit a custom IP core variation.

- 3. To select a specific Altera IP core, click the IP core in the **Installed Plug-Ins** list in the MegaWizard Plug-In Manager.

- 4. Specify the parameters on the **Parameter Settings** pages. For detailed explanations of these parameters, refer to the "Parameter Settings" chapter in this document.

- Some IP cores provide preset parameters for specific applications. If you wish to use preset parameters, click the arrow to expand the **Presets** list, select the desired preset, and then click **Apply**. To modify preset settings, in a text editor edit the *<installation directory>*\ip\altera\uniphy\lib\<*IP core>*.qprs file.

- 5. If the IP core provides a simulation model, specify appropriate options in the wizard to generate a simulation model.

- Altera IP supports a variety of simulation models, including simulation-specific IP functional simulation models and encrypted RTL models, and plain text RTL models. These are all cycle-accurate models. The models allow for fast functional simulation of your IP core instance using industry-standard VHDL or Verilog HDL simulators. For some cores, only the plain text RTL model is generated, and you can simulate that model.

- For more information about functional simulation models for Altera IP cores, refer to *Simulating Altera Designs* in volume 3 of the *Quartus II Handbook*.

Use the simulation models only for simulation and not for synthesis or any other purposes. Using these models for synthesis creates a nonfunctional design.

- 6. If the parameter editor includes **EDA** and **Summary** tabs, follow these steps:

- a. Some third-party synthesis tools can use a netlist that contains the structure of an IP core but no detailed logic to optimize timing and performance of the design containing it. To use this feature if your synthesis tool and IP core support it, turn on **Generate netlist**.

- b. On the **Summary** tab, if available, select the files you want to generate. A gray checkmark indicates a file that is automatically generated. All other files are optional.

If file selection is supported for your IP core, after you generate the core, a generation report (*<variation name*>.html) appears in your project directory. This file contains information about the generated files.

- 7. Click the **Finish** button, the parameter editor generates the top-level HDL code for your IP core, and a simulation directory which includes files for simulation.

- The **Finish** button may be unavailable until all parameterization errors listed in the messages window are corrected.

- 8. Click **Yes** if you are prompted to add the Quartus II IP File (.qip) to the current Quartus II project. You can also turn on **Automatically add Quartus II IP Files to all projects**.

You can now integrate your custom IP core instance in your design, simulate, and compile. While integrating your IP core instance into your design, you must make appropriate pin assignments. You can create virtual pin to avoid making specific pin assignments for top-level signals while you are simulating and not ready to map the design to hardware.

For some IP cores, the generation process also creates a complete example design in the *<variation\_name>\_*example\_design\_fileset/example\_project/ directory. This example demonstrates how to instantiate and connect the IP core.

For information about the Quartus II software, including virtual pins and the MegaWizard Plug-In Manager, refer to Quartus II Help.

#### Simulate the IP Core

You can simulate your IP core variation with the functional simulation model and the testbench or example design generated with your IP core. The functional simulation model and testbench files are generated in a project subdirectory. This directory may also include scripts to compile and run the testbench.

For a complete list of models or libraries required to simulate your IP core, refer to the scripts provided with the testbench.

For more information about simulating Altera IP cores, refer to *Simulating Altera Designs* in volume 3 of the *Quartus II Handbook*.

## **SOPC Builder Design Flow**

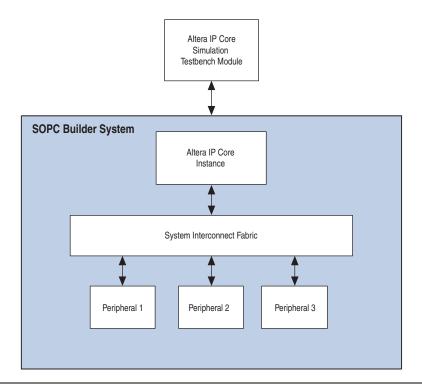

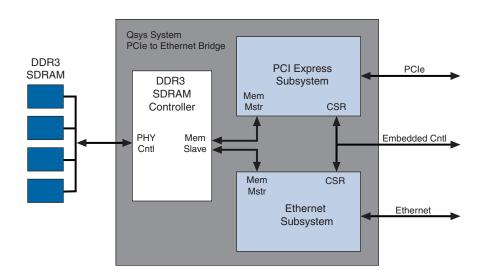

You can use SOPC Builder to build a system that includes your customized IP core. You easily can add other components and quickly create an SOPC Builder system. SOPC Builder automatically generates HDL files that include all of the specified components and interconnections. SOPC Builder defines default connections, which you can modify. The HDL files are ready to be compiled by the Quartus II software to produce output files for programming an Altera device. SOPC Builder generates a simulation testbench module for supported cores that includes basic transactions to validate the HDL files. Figure 2–3 shows a block diagram of an example SOPC Builder system.

Figure 2-3. SOPC Builder System

- For more information about system interconnect fabric, refer to the *System Interconnect Fabric for Memory-Mapped Interfaces* and *System Interconnect Fabric for Streaming Interfaces* chapters in the *SOPC Builder User Guide* and to the *Avalon Interface Specifications*.

- For more information about SOPC Builder and the Quartus II software, refer to the SOPC Builder Features and Building Systems with SOPC Builder sections in the SOPC Builder User Guide and to Quartus II Help.

## **Specify Parameters**

To specify IP core parameters in the SOPC Builder flow, follow these steps:

- 1. Create a new Quartus II project using the **New Project Wizard** available from the File menu.

- 2. On the Tools menu, click **SOPC Builder**.

- 3. For a new system, specify the system name and language.

- 4. On the **System Contents** tab, double-click the name of your IP core to add it to your system. The relevant parameter editor appears.

- 5. Specify the required parameters in the parameter editor. For detailed explanations of these parameters, refer to the "Parameter Settings" chapter in this document.

core>.qprs file.

- If your design includes external memory interface IP cores, you must turn on **Generate power of two bus widths** on the **PHY Settings** tab when parameterizing those cores.

- 6. Click **Finish** to complete the IP core instance and add it to the system.

- The **Finish** button may be unavailable until all parameterization errors listed in the messages window are corrected.

## **Complete the SOPC Builder System**

To complete the SOPC Builder system, follow these steps:

- 1. Add and parameterize any additional components. Some IP cores include a complete SOPC Builder system design example.

- 2. Use the Connection panel on the **System Contents** tab to connect the components.

- 3. By default, clock names are not displayed. To display clock names in the **Module** Name column and the clocks in the **Clock** column in the **System Contents** tab, click **Filters** to display the **Filters** dialog box. In the **Filter** list, click **All**.

- 4. If you intend to simulate your SOPC builder system, on the **System Generation** tab, turn on **Simulation** to generate simulation files for your system.

- 5. Click **Generate** to generate the system. SOPC Builder generates the system and produces the *<system name>*.qip file that contains the assignments and information required to process the IP core or system in the Quartus II Compiler.

- 6. In the Quartus II software, click **Add/Remove Files in Project** and add the **.qip** file to the project.

- 7. Compile your design in the Quartus II software.

#### Simulate the System

During system generation, you can specify whether SOPC Builder generates a simulation model and testbench for the entire system, which you can use to easily simulate your system in any of Altera's supported simulation tools. SOPC Builder also generates a set of ModelSim<sup>®</sup> Tcl scripts and macros that you can use to compile the testbench and plain-text RTL design files that describe your system in the ModelSim simulation software.

- For information about the latest Altera-supported simulation tools, refer to the *Quartus II Software Release Notes*.

- For information about simulating SOPC Builder systems, refer to the SOPC Builder User Guide and AN 351: Simulating Nios II Embedded Processor Designs.

- For general information about simulating Altera IP cores, refer to *Simulating Altera Designs* in volume 3 of the *Quartus II Handbook*.

## **Qsys System Integration Tool Design Flow**

You can use the Qsys system integration tool to build a system that includes your customized IP core. You easily can add other components and quickly create a Qsys system. Qsys automatically generates HDL files that include all of the specified components and interconnections. In Qsys, you specify the connections you want. The HDL files are ready to be compiled by the Quartus II software to produce output files for programming an Altera device. Qsys generates Verilog HDL simulation models for the IP cores that comprise your system. Figure 2–4 shows a high level block diagram of an example Qsys system.

Figure 2-4. Example Qsys System

- For more information about the Qsys system interconnect, refer to the Qsys Interconnect chapter in volume 1 of the Quartus II Handbook and to the Avalon Interface Specifications.

- For more information about the Qsys tool and the Quartus II software, refer to the *System Design with Qsys* section in volume 1 of the *Quartus II Handbook* and to Quartus II Help.

#### **Specify Parameters**

To specify parameters for your IP core using the Qsys flow, follow these steps:

- 1. Create a new Quartus II project using the **New Project Wizard** available from the File menu.

- 2. On the Tools menu, click **Qsys** (Beta).

- 3. On the **System Contents** tab, double-click the name of your IP core to add it to your system. The relevant parameter editor appears.

- 4. Specify the required parameters in all tabs in the Qsys tool. For detailed explanations of these parameters, refer to the "Parameter Settings" chapter in this document.

- If your design includes external memory interface IP cores, you must turn on **Generate power of two bus widths** on the **PHY Settings** tab when parameterizing those cores.

- Some IP cores provide preset parameters for specific applications. If you wish to use preset parameters, click the arrow to expand the **Presets** list, select the desired preset, and then click **Apply**. To modify preset settings, in a text editor edit the *<installation directory>\ip\altera\uniphy\lib\<IP core>.qprs* file.

- 5. Click **Finish** to complete the IP core instance and add it to the system.

- The **Finish** button may be unavailable until all parameterization errors listed in the messages window are corrected.

## **Complete the Qsys System**

To complete the Qsys system, follow these steps:

- 1. Add and parameterize any additional components.

- 2. Connect the components using the Connection panel on the **System Contents** tab.

- 3. In the **Export As** column, enter the name of any connections that should be a top-level Qsys system port. If the **Export As** column is not present, click the **Project Settings** tab and turn off **Use SOPC Builder port naming**.

- 4. If you intend to simulate your Qsys system, on the **Generation** tab, turn on one or more options under **Simulation** to generate desired simulation files.

- 5. If your system is not part of a Quartus II project and you want to generate synthesis RTL files, turn on **Create synthesis RTL files**.

- 6. Click **Generate** to generate the system. Qsys generates the system and produces the *<system name>*.qip file that contains the assignments and information required to process the IP core or system in the Quartus II Compiler.

- 7. In the Quartus II software, click **Add/Remove Files in Project** and add the **.qip** file to the project.

- 8. Compile your project in the Quartus II software.

#### Simulate the System

During system generation, Qsys generates a functional simulation model—or example design that includes a testbench—which you can use to simulate your system in any Altera-supported simulation tool.

- For information about the latest Altera-supported simulation tools, refer to the *Quartus II Software Release Notes*.

- For general information about simulating Altera IP cores, refer to *Simulating Altera Designs* in volume 3 of the *Quartus II Handbook*.

- For information about simulating Qsys systems, refer to the *System Design with Qsys* section in volume 1 of the *Quartus II Handbook*.

## **HardCopy Migration Design Guidelines**

If you intend to target your design to a HardCopy<sup>®</sup> device, ensure you use the following design guidelines:

On the General Settings page of the DDR2 SDRAM Controller with UniPHY or DDR3 SDRAM Controller with UniPHY MegaWizard, turn on HardCopy Compatibility Mode, and then specify whether the Reconfigurable PLL Location is Top\_Bottom or Left\_Right.

Altera recommends that you set the **Reconfigurable PLL Location** to the same side as your memory interface.

When turned on, the **HardCopy Compatibility Mode** option enables run-time reconfiguration for all phase-locked loops (PLLs) and delay-locked loops (DLLs) instantiated in memory interfaces that are configured in PLL and DLL masters, and brings the necessary reconfiguration signals to the top level of the design.

- "Top-Level HardCopy Migration Signals" on page 6–12 lists the top-level signals generated for HardCopy migration.

- Enable run-time reconfiguration mode for all PLLs and DLLs instantiated in interfaces that are configured in PLL and DLL slaves.

For information about PLL megafunctions, refer to the *Phase-Locked Loop* (ALTPLL) Megafunction User Guide and the Phase-Locked Loops Reconfiguration (ALTPLL\_RECONFIG) Megafunctions User Guide. For information about DLL megafunctions, refer to the ALTDLL and ALTDQ\_DQS Megafunctions User Guide.

Ensure that you place all memory interface pins close together. If, for example, address pins are located far away from data pins, closing timing might be difficult.

You can use the example top-level project that is generated when you turn on HardCopy Migration as a guide to help you connect the necessary signals in your design.

## Differences in UniPHY IP Generated with HardCopy Migration Support

When you generate a UniPHY memory interface for HardCopy device support, certain features in the IP are enabled that do not exist when you generate the IP core for only the FPGA. This section discusses those additional enabled features.

#### **ROM Loader for Designs Using Nios II Sequencer**

An additional ROM loader is intantiated in the design for UniPHY designs that use the Nios II sequencer. The Nios II sequencer instruction code resides in RAM on either the HardCopy or FPGA device.

When you target only an FPGA device, the RAM is initialized when the device is programmed; however, HardCopy devices are not programmed and therefore the RAM cannot be initialized in this fashion. Instead, the Nios II sequencer instruction code must be stored in an external, non-volatile, ROM that loads the Nios II sequencer RAM through a ROM loader. You must attach the ROM loader to the appropriate pins connected to the external non-volatile ROM.

Table 2–1 summarizes the ports exposed at the top level of the PHY+Controller wrapper to expose the ROM loader utilized by the Nios II-based sequencer within the DDR2 or DDR3 PHY.

Table 2–1. Top-level Ports that Connect to External ROM for Loading Nios II Code Memory (Part 1 of 2)

| Port Name                        | Direction | Description                                                                                                                                                              |

|----------------------------------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| hc_rom_config_clock              | Input     | Write clock for the ROM loader. This clock is the write clock for the Nios II code memory.                                                                               |

| hc_rom_config_datain             | Input     | Data input from external ROM.                                                                                                                                            |

| hc_rom_config_rom_data_<br>ready | Input     | Asserts to the code memory loader that the word of memory is ready to be loaded.                                                                                         |

| hc_rom_config_init               | Input     | Signals that the Nios II code memory is being loaded from the external ROM.                                                                                              |

| hc_rom_config_init_busy          | Output    | Remains asserted throughout initialization and becomes inactive when initialization is complete. soft_reset_n can be issued after hc_rom_config_init_busy is deasserted. |

Table 2–1. Top-level Ports that Connect to External ROM for Loading Nios II Code Memory (Part 2 of 2)

| Port Name                 | Direction | Description                                           |

|---------------------------|-----------|-------------------------------------------------------|

| hc_rom_config_rom_rden    | Output    | Read-enable signal that connects to the external ROM. |

| hc_rom_config_rom_address | Output    | ROM address that connects to the external ROM.        |

#### PLL/DLL Run-time Reconfiguration

The PLLs and DLLs in the HardCopy design have run-time reconfiguration enabled—provided that they are not in PLL/DLL slave mode.

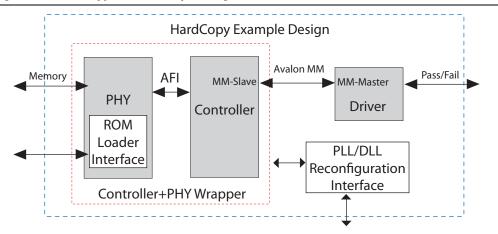

When the PLLs and DLLs are generated with reconfiguration enabled, there are extra signals that must be connected and driven by user logic. In the example design generated during IP core generation, the PLL/DLL reconfiguration signals are brought to the top level and connected to constants, as shown in Figure 2–5.

For information about PLL megafunctions and reconfiguration, refer to the *Phase-Locked Loop (ALTPLL) Megafunction User Guide* and the *Phase-Locked Loops Reconfiguration (ALTPLL\_RECONFIG) Megafunctions User Guide*.

Figure 2-5. HardCopy UnIPHY Example Design

Table 2–2 summarizes the DLL reconfiguration ports exposed at the top level of the Controller+PHY.

Table 2–2. DLL Reconfiguration Ports Exposed at Top-Level of Controller+PHY Wrapper (Part 1 of

| Port Name                             | Direction | Description                                                                                                                                                   |

|---------------------------------------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| hc_dll_config_dll_offset_ctrl_addnsub | Input     | Addition/subtraction control port for the DLL. This port controls if the delay-offset setting on hc_dll_config_dll_offset_ctrl_offset is added or subtracted. |

Table 2-2. DLL Reconfiguration Ports Exposed at Top-Level of Controller+PHY Wrapper (Part 2 of

| Port Name                                       | Direction | Description                                                                                                                                |

|-------------------------------------------------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------|

| hc_dll_config_dll_offset_ctrl_<br>offset        |           | Offset input setting for the PLL. This is a Gray-coded offset that is added or subtracted from the current value of the DLL's delay chain. |

| hc_dll_config_dll_offset_ctrl_<br>offsetctrlout | Output    | The registered and Gray-coded value of the current delay-offset setting.                                                                   |

Table 2–3 summarizes the ports exposed at the top level of the Controller and PHY wrapper to allow PLL reconfiguration.

Table 2-3. PLL Reconfiguration Ports Exposed at the Top-Level of Controller+PHY Wrapper

| Port Name                         | Direction | Description                                                                                                                                                   |

|-----------------------------------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| hc_pll_config_configupdate        | Input     | Control signal to enable PLL reconfiguration. (Applies to RLDRAMII and QDRII only, the phase reconfiguration feature for DDR2/3 is included in the CSR port.) |

| hc_pll_config_phasecounter select | Input     | Specifies the counter select for dynamic phase adjustment. (Applies to RLDRAMII and QDR II only.)                                                             |

| hc_pll_config_phasestep           | Input     | Specifies the phase step for dynamic phase shifting. (Applies to RLDRAMII and QDR II only.)                                                                   |

| hc_pll_config_phaseupdown         | Input     | Specifies if the phase adjustment should be up or down. (Applies to RLDRAMII and QDR II only.)                                                                |

| hc_pll_config_scanclk             | Input     | PLL reconfiguration scan chain clock.                                                                                                                         |

| hc_pll_config_scanclkena          | Input     | Clock enable port of the hc_pll_config_scanclk clock.                                                                                                         |

| hc_pll_config_scandata            | Input     | Serial input data for the PLL reconfiguration scan chain.                                                                                                     |

| hc_pll_config_phasedone           | Output    | When asserted, this signal indicates to core logic that phase adjustment is completed and that the PLL is ready to act on a possible second adjustment pulse. |

| hc_pll_config_scandataout         | Output    | The data output of the serial scan chain.                                                                                                                     |

| hc_pll_config_scandone            | Output    | Asserted when the scan chain write operation is in progress and is deasserted when the write operation is complete.                                           |

To facilitate placement and timing closure and help compensate for PLLs adjacent to I/Os and vertical I/O overhang issues that can occur when targeting HardCopy III and HardCopy IV devices, an additional pipeline stage is added to the write path in the RTL when you turn on **HardCopy Compatibility**. The additional pipeline stage is added in all cases, except when CAS write latency equals 2 (for DDR3) or CAS latency equals 3 (for DDR2), where the additional pipeline stage is not required to meet timing requirements. The additional pipeline stage does not affect the overall latency of the controller.

For information about HardCopy issues such as vertical I/O overhang, PLLs adjacent to I/Os, and timing closure, refer to HardCopy III Device I/O Features in the HardCopy III Device Handbook, Volume 1, and HardCopy IV Device I/O Features in the *HardCopy IV Device Handbook, Volume 1.*

#### **Generated Files**

When you complete the IP generation flow, there are generated files created in your project directory. The directory structure created varies somewhat, depending on the tool used to parameterize and generate the IP.

The PLL parameters are statically defined in the *<variation\_name>\_*parameters.tcl at generation time. To ensure timing constraints and timing reports are correct, when you use the GUI to make changes to the PLL component, apply those changes to the PLL parameters in this file.

## **MegaWizard Plug-in Manager Flow**

The tables in this section list the generated directory structure and key files of interest to users, resulting from the MegaWizard Plug-in Manager flow.

#### **Synthesis**

Table 2-4 lists the generated directory structure and key files created by the synthesis flow with the MegaWizard Plug-in Manager.

Table 2–4. Generated Directory Structure and Key Files—MegaWizard Plug-In Manager Synthesis Flow

| Directory                                                      | File Name                                                                                                         | Description                                                            |

|----------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|

| <working_dir>/</working_dir>                                   | < <i>variation_name</i> >.qip                                                                                     | QIP file which refers to all generated files in the synthesis fileset. |

| <working_dir>/</working_dir>                                   | <pre><variation_name>.v (for Verilog), or <variation_name>.vhd (for VHDL)</variation_name></variation_name></pre> | Top-level wrapper for synthesis files.                                 |

| <working_dir>/<variation_name>/</variation_name></working_dir> | <variation_name>_<stamp>.v (1)</stamp></variation_name>                                                           | UniPHY top-level wrapper.                                              |

| <working_dir>/<variation_name>/</variation_name></working_dir> | <variation_name>_<stamp>_*.v (1)</stamp></variation_name>                                                         | UniPHY Verilog RTL files.                                              |

| <working_dir>/<variation_name>/</variation_name></working_dir> | <variation_name>_<stamp>_*.sv (1)</stamp></variation_name>                                                        | UniPHY SystemVerilog RTL files.                                        |

| <working_dir>/<variation_name>/</variation_name></working_dir> | <variation_name>_<stamp>.sdc (1)</stamp></variation_name>                                                         | Synopsys constraints file.                                             |

| <working_dir>/<variation_name>/</variation_name></working_dir> | <variation_name>_<stamp>.ppf (1)</stamp></variation_name>                                                         | Pin Planner file.                                                      |

| <working_dir>/<variation_name>/</variation_name></working_dir> | <pre><variation_name>_<stamp>_pin_assignments.tcl (1)</stamp></variation_name></pre>                              | Pin constraints script to be run after synthesis.                      |

| <working_dir>/<variation_name>/</variation_name></working_dir> | <variation_name>_<stamp>_*.tcl (1)</stamp></variation_name>                                                       | Other Tcl scripts.                                                     |

| <working_dir>/<variation_name>/</variation_name></working_dir> | <variation_name>_<stamp>_readme.txt (1)</stamp></variation_name>                                                  | Readme text file.                                                      |

| Note to Table 2-4:                                             |                                                                                                                   |                                                                        |

| (1) < ctamp is a unique identifier detern                      | nined by the MagaWizard Plug-in Manager at generation time                                                        |                                                                        |

(1) <stamp> is a unique identifier determined by the MegaWizard Plug-in Manager at generation time.

#### **Simulation**

Table 2–5 lists the generated directory structure and key files created by the Verilog simulation flow with the MegaWizard Plug-in Manager.

Table 2–5. Generated Directory Structure and Key Files—MegaWizard Plug-In Manager Simulation Flow (Verilog)

| Directory                                                                      | File Name                                                                                                             | Description                     |

|--------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|---------------------------------|

| <pre><working_dir>/<variation_name> _sim/</variation_name></working_dir></pre> | <pre><variation_name>.v (for Verilog), or<br/><variation_name>.vho (for VHDL)</variation_name></variation_name></pre> | UniPHY top-level wrapper.       |

| <pre><working_dir>/<variation_name> _sim/</variation_name></working_dir></pre> | <variation_name>_*.v</variation_name>                                                                                 | UniPHY Verilog RTL files.       |

| <pre><working_dir>/<variation_name> _sim/</variation_name></working_dir></pre> | <variation_name>_*.sv</variation_name>                                                                                | UniPHY SystemVerilog RTL files. |

| <pre><working_dir>/<variation_name> _sim/</variation_name></working_dir></pre> | <variation_name>_readme.txt</variation_name>                                                                          | Readme text file.               |

Table 2–6 lists the generated directory structure and key files created by the VHDL simulation flow with the MegaWizard Plug-in Manager.

Table 2–6. Generated Directory Structure and Key Files—MegaWizard Plug-In Manager Simulation Flow (VHDL)

| Directory                                                                      | File Name                                                                                  | Description                   |

|--------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|-------------------------------|

| <pre><working_dir>/<variation_name> _sim/</variation_name></working_dir></pre> | <variation_name>.vho</variation_name>                                                      | UniPHY VHDL top-level module. |

| <working_dir>/<variation_name><br/>_sim/</variation_name></working_dir>        | <pre><variation_name>_*.vhd <variation_name>_*.vho</variation_name></variation_name></pre> | UniPHY simulation VHDL files. |

| <pre><working_dir>/<variation_name> _sim/</variation_name></working_dir></pre> | vhdl_files.txt                                                                             | File list text file.          |

#### **Example Design**

Table 2–7 lists the generated directory structure and key files created for the example design with the MegaWizard Plug-in Manager

Table 2–7. Generated Directory Structure and Key Files—MegaWizard Plug-In Manager Example Design (Part 1 of 2)

| Directory                                                                                          | File Name'                             | Description                                                                                                                                                               |

|----------------------------------------------------------------------------------------------------|----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <pre><working_dir>/<variation_name> _example_design_fileset/</variation_name></working_dir></pre>  | <variation_name>.qip</variation_name>  | QIP which refers to UniPHY RTL in this fileset. This is distinct from/ <variation_name>.qip. This file is included automatically in the example project.</variation_name> |

| <pre><working_dir>/<variation_name> _example_design_fileset/</variation_name></working_dir></pre>  | <variation_name>.v</variation_name>    | UniPHY top-level wrapper.                                                                                                                                                 |

| <pre><working_dir>/<variation_name>   _example_design_fileset</variation_name></working_dir></pre> | <variation_name>_*.v</variation_name>  | UniPHY Verilog RTL files.                                                                                                                                                 |

| <pre><working_dir>/<variation_name>   _example_design_fileset</variation_name></working_dir></pre> | <variation_name>_*.sv</variation_name> | UniPHY SystemVerilog RTL fies.                                                                                                                                            |

| <pre><working_dir>/<variation_name> _example_design_fileset/</variation_name></working_dir></pre>  | <variation_name>.sdc</variation_name>  | Synopsys constraints file.                                                                                                                                                |

Table 2-7. Generated Directory Structure and Key Files—MegaWizard Plug-In Manager Example Design (Part 2 of 2)

| Directory                                                                                                                | File Name'                                                   | Description                                                                    |

|--------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|--------------------------------------------------------------------------------|

| <pre><working_dir>/<variation_name> _example_design_fileset/</variation_name></working_dir></pre>                        | <variation_name>.ppf</variation_name>                        | Pin Planner file.                                                              |

| <pre><working_dir>/<variation_name> _example_design_fileset/</variation_name></working_dir></pre>                        | <variation_name>_pin_assignments.tcl</variation_name>        | Pin constraints script to be run after synthesis.                              |

| <pre><working_dir>/<variation_name> _example_design_fileset/</variation_name></working_dir></pre>                        | <variation_name>_*.tcl</variation_name>                      | Other Tcl scripts.                                                             |

| <pre><working_dir>/<variation_name> _example_design_fileset/</variation_name></working_dir></pre>                        | <pre><variation_name>_readme.txt</variation_name></pre>      | Readme text file.                                                              |

| <pre><working_dir>/<variation_name> _example_design_fileset/example _project/</variation_name></working_dir></pre>       | <variation_name>_example_top.qpf</variation_name>            | Example design project file.                                                   |

| <pre><working_dir>/<variation_name>    _example_design_fileset/example    _project/</variation_name></working_dir></pre> | <pre><variation_name>_example_top.qsf</variation_name></pre> | Example design project settings file.                                          |

| <pre><working_dir>/<variation_name> _example_design_fileset/example _project/</variation_name></working_dir></pre>       | <pre><variation_name>_example_top.v</variation_name></pre>   | Top-level wrapper including<br>UniPHY, traffic generator, and<br>memory model. |

| <pre><working_dir>/<variation_name> _example_design_fileset/example _project/</variation_name></working_dir></pre>       | <variation_name>_*.v</variation_name>                        | Other example design Verilog RTL files.                                        |

| <pre><working_dir>/<variation_name>    _example_design_fileset/example    _project/</variation_name></working_dir></pre> | <variation_name>_*.sv</variation_name>                       | Other example design<br>SystemVerilog RTL files.                               |

| <pre><working_dir>/<variation_name> _example_design_fileset/example _project/</variation_name></working_dir></pre>       | <pre><prefix>_mem_model.sv (1)</prefix></pre>                | Generic memory model.                                                          |

| <pre><working_dir>/<variation_name> _example_design_fileset/rtl_sim/</variation_name></working_dir></pre>                | <variation_name>_example_top_tb.v</variation_name>           | Top-level test bench.                                                          |

| Note to Table 2–7:                                                                                                       |                                                              |                                                                                |

| (1) <prefix> varies depending on protoc</prefix>                                                                         | ol and type of memory model.                                 |                                                                                |

## **SOPC Builder Flow**

Table 2–8 lists the generated directory structure and key files created by the SOPC Builder flow.

Table 2–8. Generated Directory Structure and Key Files—SOPC Builder Flow (Part 1 of 2)

| Directory                    | File Name'                                                 | Description                                                          |

|------------------------------|------------------------------------------------------------|----------------------------------------------------------------------|

| <working_dir>/</working_dir> | <system_name>.qip</system_name>                            | QIP which refers to all generated files in the SOPC Builder project. |

| <working_dir>/</working_dir> | <system_name>.v</system_name>                              | SOPC Builder system top-level wrapper.                               |

| <working_dir>/</working_dir> | <core_name>_<stamp>.v (1)</stamp></core_name>              | UniPHY top-level wrapper.                                            |

| <working_dir>/</working_dir> | <core_name>_<stamp>_*.v (1)</stamp></core_name>            | UniPHY Verilog RTL files.                                            |

| <working_dir>/</working_dir> | <core_name>_<stamp>_*.sv (1)</stamp></core_name>           | UniPHY SystemVerilog RTL files.                                      |

| <working_dir>/</working_dir> | <pre><core_name>_<stamp>.sdc (1)</stamp></core_name></pre> | Synopsys constraints file.                                           |

Table 2–8. Generated Directory Structure and Key Files—SOPC Builder Flow (Part 2 of 2)

| Directory                           | File Name'                                                        | Description                                       |

|-------------------------------------|-------------------------------------------------------------------|---------------------------------------------------|

| <working_dir>/</working_dir>        | <core_name>_<stamp>.ppf (1)</stamp></core_name>                   | Pin Planner file.                                 |

| <working_dir>/</working_dir>        | <core_name>_<stamp>_pin_assignments.tcl (1)</stamp></core_name>   | Pin constraints script to be run after synthesis. |

| <working_dir>/</working_dir>        | <core_name>_<stamp>_*.tcl (1)</stamp></core_name>                 | Other Tcl scripts.                                |

| <working_dir>/</working_dir>        | <pre><core_name>_<stamp>_readme.txt (1)</stamp></core_name></pre> | Readme text file.                                 |

| <working_dir>/</working_dir>        | Other IP core files.                                              | Other IP cores.                                   |

| Note to Table 2–8:                  |                                                                   |                                                   |

| (1) < stamp> is a unique identifier | determined by SOPC Builder at generation time.                    |                                                   |

## **Qsys Flow**

The tables in this section list the generated directory structure and key files of interest to users, resulting from the Qsys flow

#### **Synthesis**

Table 2–9 lists the generated directory structure and key files created by the synthesis flow with Qsys.

Table 2-9. Generated Directory Structure and Key Files—Qsys Synthesis Flow (Part 1 of 2)

| Directory                                                                                 | File Name                                                                  | Description                                                                   |

|-------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|-------------------------------------------------------------------------------|

| <pre><working_dir>/<system_name>/ synthesis/</system_name></working_dir></pre>            | <system_name>.qip</system_name>                                            | QIP which refers to all generated files in the Qsys system synthesis fileset. |

| <pre><working_dir>/<system_name>/ synthesis/</system_name></working_dir></pre>            | <system_name>.v</system_name>                                              | Qsys system top-level wrapper.                                                |

| <pre><working_dir>/<system_name>/ synthesis/submodules/</system_name></working_dir></pre> | <core_name>_<stamp>.v (1)</stamp></core_name>                              | UniPHY top-level wrapper.                                                     |

| <pre><working_dir>/<system_name>/ synthesis/submodules/</system_name></working_dir></pre> | <core_name>_<stamp>_*.v (1)</stamp></core_name>                            | UniPHY Verilog RTL files.                                                     |

| <pre><working_dir>/<system_name>/ synthesis/submodules/</system_name></working_dir></pre> | <core_name>_<stamp>_*.sv (1)</stamp></core_name>                           | UniPHY SystemVerilog RTL files.                                               |

| <pre><working_dir>/<system_name>/ synthesis/submodules/</system_name></working_dir></pre> | <core_name>_<stamp>.sdc (1)</stamp></core_name>                            | Synopsys constraints file.                                                    |

| <pre><working_dir>/<system_name>/ synthesis/submodules/</system_name></working_dir></pre> | <core_name>_<stamp>.ppf (1)</stamp></core_name>                            | Pin Planner file.                                                             |

| <pre><working_dir>/<system_name>/ synthesis/submodules/</system_name></working_dir></pre> | <pre><core_name>_<stamp>_pin_assignments.tcl (1)</stamp></core_name></pre> | Pin constraints script to be run after synthesis.                             |

| <pre><working_dir>/<system_name>/ synthesis/submodules/</system_name></working_dir></pre> | <core_name>_<stamp>_*.tcl (1)</stamp></core_name>                          | Other Tcl scripts.                                                            |

| <pre><working_dir>/<system_name>/ synthesis/submodules/</system_name></working_dir></pre> | <core_name>_<stamp>_readme.txt (1)</stamp></core_name>                     | Readme text file.                                                             |

Table 2-9. Generated Directory Structure and Key Files—Qsys Synthesis Flow (Part 2 of 2)

| Directory                                                                                 | File Name           | Description          |

|-------------------------------------------------------------------------------------------|---------------------|----------------------|

| <pre><working_dir>/<system_name>/ synthesis/submodules/</system_name></working_dir></pre> | Other IP core files | Other IP core files. |

| Note to Table 2–9                                                                         |                     |                      |

| (1) < stamp> is a unique identifier created by Qsys during generation.                    |                     |                      |

#### **Verilog Simulation**

Table 2–10 lists the generated directory structure and key files created by the Verilog HDL simulation flow with Qsys.

Table 2-10. Generated Directory Structure and Key Files—Qsys Verilog Simulation

| Directory                                                                                   | File Name                                              | Description                     |

|---------------------------------------------------------------------------------------------|--------------------------------------------------------|---------------------------------|

| <pre><working_dir>/<system_name>/ sim_verilog/</system_name></working_dir></pre>            | <system_name>.v</system_name>                          | Qsys system top-level wrapper.  |

| <pre><working_dir>/<system_name>/ sim_verilog/submodules/</system_name></working_dir></pre> | <core_name>_<stamp>.v</stamp></core_name>              | UniPHY top-level wrapper.       |

| <pre><working_dir>/<system_name>/ sim_verilog/submodules/</system_name></working_dir></pre> | <core_name>_<stamp>_*.v</stamp></core_name>            | UniPHY Verilog RTL files.       |

| <pre><working_dir>/<system_name>/ sim_verilog/submodules/</system_name></working_dir></pre> | <core_name>_<stamp>_*.sv</stamp></core_name>           | UniPHY SystemVerilog RTL files. |

| <pre><working_dir>/<system_name>/ sim_verilog/submodules/</system_name></working_dir></pre> | <core_name>_<stamp>_readme.txt (1)</stamp></core_name> | Readme text file.               |

| <pre><working_dir>/<system_name>/ sim_verilog/submodules/</system_name></working_dir></pre> | Other IP core files                                    | Other IP core files.            |

| Note for Table 2–10:                                                                        |                                                        |                                 |

| (1) <stamp> is a unique identifier created by Qsys during generation.</stamp>               |                                                        |                                 |

#### **VHDL Simulation**

Table 2–11 lists the generated directory structure and key files created by the VHDL simulation flow with Qsys.

Table 2–11. Generated Directory Structure and Key Files—Qsys VHDL Simulation

| Directory                                                                                | File Name                                                                                                  | Description                    |

|------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|--------------------------------|

| <pre><working_dir>/<system_name>/ sim_vhdl/</system_name></working_dir></pre>            | <system_name>.vhd</system_name>                                                                            | Qsys system top-level wrapper. |

| <pre><working_dir>/<system_name>/ sim_vhdl/submodules/</system_name></working_dir></pre> | <core_name>_<stamp>.vho (1)</stamp></core_name>                                                            | UniPHY VHDL top-level module.  |

| <pre><working_dir>/<system_name>/ sim_vhdl/submodules/</system_name></working_dir></pre> | <pre><core_name>_<stamp>_*.vhd <core_name>_<stamp>_*.vho (1)</stamp></core_name></stamp></core_name></pre> | UniPHY VHDL simulation files.  |

| <pre><working_dir>/<system_name>/ sim_vhdl/submodules/</system_name></working_dir></pre> | vhdl_files.txt                                                                                             | File list text file.           |

| Note to Table 2–11:                                                                      |                                                                                                            |                                |

| (1) < stamp> is a unique identifier created by Qsys during generation.                   |                                                                                                            |                                |

2–18 Chapter 2: Getting Started

Generated Files

# 3. Parameter Settings

This chapter describes the QDR II and QDR II+ SRAM Controller with UniPHY IP core parameters that you can set in the GUI.

## **General Settings**

The **General Settings** tab allows you to configure the following parameter settings.

#### Clocks

Table 3–1 describes the clock settings.

Table 3-1. Clock Settings

| Parameter                                | Description                                                                                                                                                                                                                                       |

|------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Memory clock frequency                   | The frequency of the clock that drives the memory device.                                                                                                                                                                                         |

| PLL reference clock frequency            | The frequency of the clock that feeds the PLL.                                                                                                                                                                                                    |

| Full or half rate on Avalon-MM interface | Defines the width of the data bus on the Avalon-MM interface. A setting of <b>Full</b> results in a width twice the memory data width. A setting of <b>Half</b> results in a width of four times the memory data width.                           |

| Additional address/command clock phase   | Increases or decreases the phase shift of the address/command clock. The base phase shift centeraligns the address/command clock at the memory device. In some circumstances, you can improve timing by increasing or decreasing the phase shift. |

## **Advanced PHY Settings**

Table 3–2 describes the advanced PHY settings.

Table 3-2. Advanced PHY Settings

| Parameter                      | Description                                                                                                                                                                                 |

|--------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Generate power-of-2 bus widths | Rounds down the Avalon-MM side data bus to the nearest power of 2.                                                                                                                          |

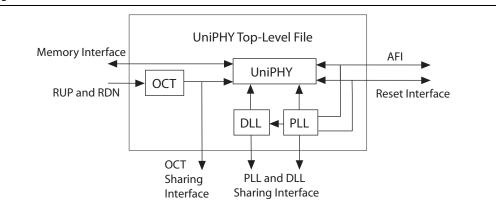

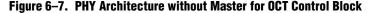

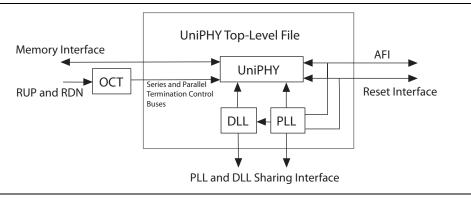

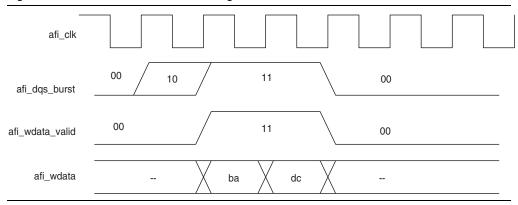

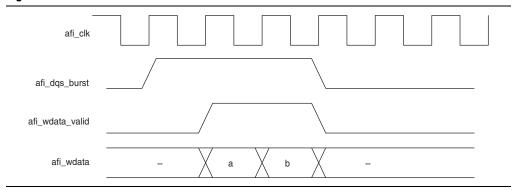

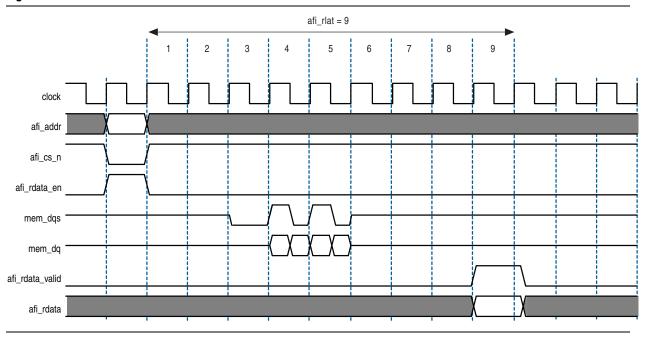

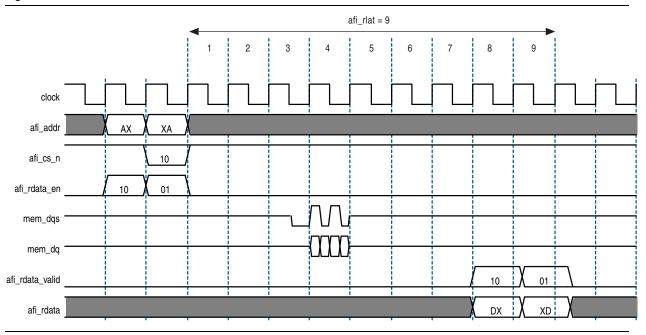

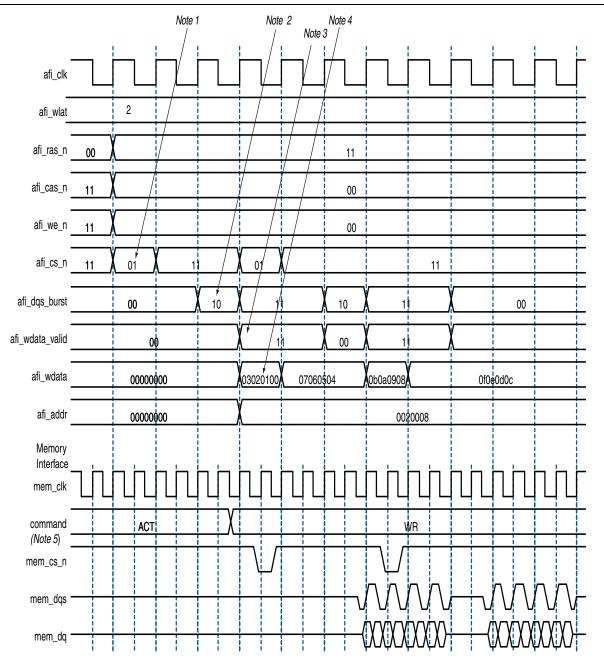

| Maximum Avalon-MM burst length | Specifies the maximum burst length on the Avalon-MM bus.                                                                                                                                    |