# 10-Gbps Ethernet Reference Design User Guide

101 Innovation Drive San Jose, CA 95134 www.altera.com IP Core Version: Document Date: 10.0 July 2010

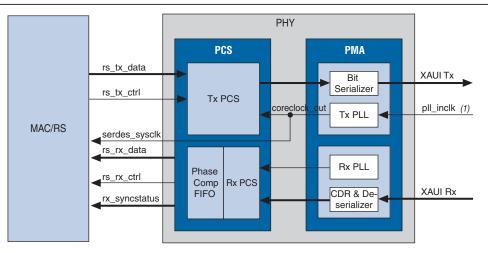

# 1. 10-Gbps Ethernet IP Datasheet

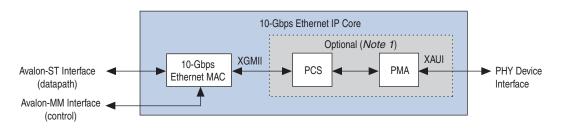

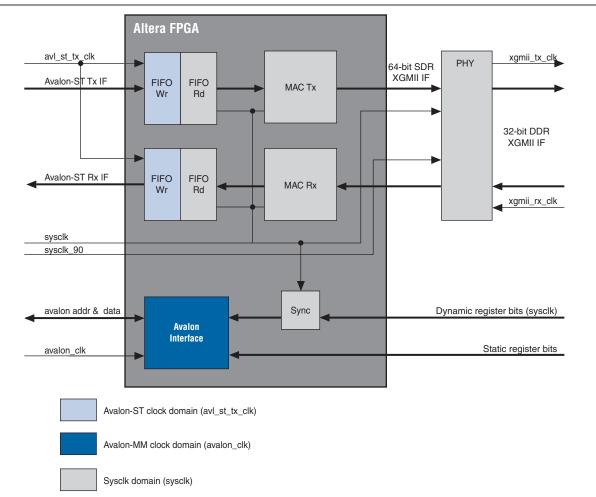

This datasheet describes the Altera<sup>®</sup> 10-Gbps Ethernet IP core which implements the IEEE 802.3 2005 and 802.1Q Ethernet standards. You can use the Quartus<sup>®</sup> II software to parameterize and implement this IP core in your design. The 10-Gbps Ethernet IP core is highly configurable. It includes an Ethernet Media Access Controller (MAC) with an Avalon<sup>®</sup> Streaming (Avalon-ST) interface on the client side, and a XAUI or a standard XGMII interface on the network side. The XAUI interface is implemented as hard IP in an Altera FPGA transceiver or as soft logic, which results in a soft 10GBASE-X XAUI PCS. Alternatively, you can choose to implement a 10-Gbps Ethernet IP core that includes only the MAC or the soft XAUI PCS. Figure 1–1 illustrates the top-level modules of this IP core.

Altera categorizes this IP core as a reference design, described on the Altera website on the 10-Gbps Ethernet Reference Design web page.

#### Figure 1–1. 10-Gbps Ethernet IP Core Block Diagram (Note 1)

#### Note to Figure 1–1:

(1) You can implement the optional XAUI PCS in an Altera device transceiver or as soft logic, which results in a soft 10GBASE-X XAUI PCS and PMA.

# **1.1. Supported Features**

- Flexible standard interfaces: SDR XGMII-like interface to connect to the internal 10GBASE-X (XAUI) PHY, standard XGMII interface to connect to the external PHY device, hard IP XAUI PCS and PMA to connect to an external optical module.

- Verified and tested in hardware with standard 10-Gbps Ethernet test equipment. The IP core has passed the University of New Hampshire Interoperability Lab (UNH-IOL) 10-Gbps Ethernet tests including MAC, 10GBASE-X physical coding sublayer (PCS), Reconciliation Sublayer, flow control, and XAUI physical media attachment (PMA).

- Management data I/O (MDIO) master interface for external PHY device management.

- Avalon-ST 64-bit wide client interface running at 156.25 MHz with 10-Gbps full-duplex throughput rate.

- Automatic or host-controlled flow control frame transmission can be initiated by either the host using explicit signals or by the host using configuration register. The xon\_req and xoff\_req signals can be controlled by either the MAC client or by the host via the configuration registers.

- Programmable pause quanta.

- Parameterizable FIFO size (64 bytes to 64 Kbytes) and programmable threshold levels.

- Programmable MAC addresses and receive packet filtering based on up to five unicast or multicast and broadcast destination MAC addresses.

- Programmable maximum receiving frame length up to 64 KBytes, including jumbo frames (1,519 to 9,618 bytes).

- Support for promiscuous (transparent) and non-promiscuous (filtered) modes of operation.

- Support for virtual LAN (VLAN) and stacked VLAN tagged frames according to the IEEE 802.1Q and 802.1ad (QinQ) standards, respectively.

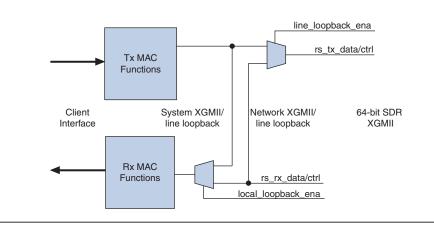

- Remote (Line) and Local (Client) loopback at XGMII for system test.

- Statistics counters supporting RMON (RFC 2819), Ethernet type MIB (RFC 3635), and interface group MIB (RFC 2863).

- Programmable filtering of received frames with CRC errors, length-check error, or oversized errors.

- Easy-to-use MegaWizard<sup>TM</sup> GUI for IP parameterization and generation.

- IP functional simulation models for use in Altera-supported VHDL and Verilog HDL simulators.

- Verilog HDL and VHDL testbench and verification environment.

- Deficit Idle Count (DIC) is supported

# **1.2. Performance and Resource Utilization**

Table 1–1 shows the typical expected device resource utilization for different IP configurations and parameters, using the Quartus II software version 9.1 targeting a Stratix II GX (EP2SGX30DF780C3) device.

For C4 and C5 device speed grades the  $f_{MAX}$  is 156.25 MHz.

|      | FIF0                      |      |                       |     |                        |                    |               | f <sub>max</sub> (MHz | )               | Mei | mory |

|------|---------------------------|------|-----------------------|-----|------------------------|--------------------|---------------|-----------------------|-----------------|-----|------|

| XAUI | (eight-<br>byte<br>words) | MDIO | Statistics<br>Counter | ECC | Combinational<br>ALUTs | Logic<br>Registers | Avalon<br>-MM | Avalon<br>-ST         | System<br>Clock | M4K | M512 |

| Yes  | No                        | No   | No                    | No  | 3,246                  | 3,238              | 156           | —                     | 202             | 0   | 0    |

| Yes  | 256                       | No   | No                    | No  | 3,652                  | 3,654              | 174           | 199                   | 179             | 8   | 0    |

| Yes  | 256                       | Yes  | No                    | No  | 3,803                  | 3,788              | 170           | 200                   | 187             | 8   | 0    |

| Yes  | 256                       | Yes  | Yes                   | No  | 5,666                  | 5,334              | 189           | 218                   | 204             | 8   | 0    |

Table 1-1. 10-Gbps Ethernet Performance and Resource Utilization—Stratix II GX Device

Table 1–2 shows the typical expected performance, using the Quartus II software v9.1 targeting a Stratix IV (EP4SGX70DF29C3) device.

|                | FIF0                      |      |                       |     |                        |                    |               | f <sub>max</sub> (MHz) |                 | Memory |

|----------------|---------------------------|------|-----------------------|-----|------------------------|--------------------|---------------|------------------------|-----------------|--------|

| XAUI           | (eight-b<br>yte<br>words) | MDIO | Statistics<br>Counter | ECC | Combinational<br>ALUTs | Logic<br>Registers | Avalon<br>-MM | Avalon<br>-ST          | System<br>Clock | M9K    |

| Yes            | 256                       | Yes  | Yes                   | No  | 5,666                  | 5,346              | 230           | 220                    | 197             | 4      |

| Yes            | 256                       | Yes  | Yes                   | Yes | 6,808                  | 6,119              | 187           | 175                    | 175             | 6      |

| Soft XAUI only | _                         | —    | —                     | No  | 2,545                  | 2,198              | _             | —                      | 156.25          | 6      |

| Soft XAUI      | 256                       | Yes  | Yes                   | No  | 8,136                  | 7,478              | 177           | 252                    | 188             | 10     |

| Soft XAUI      | 256                       | Yes  | Yes                   | Yes | 10,080                 | 8,409              | 180           | 175                    | 168             | 13     |

Table 1-2. 10-Gbps Ethernet Performance and Resource Utilization—Stratix IV Device

Table 1–3 shows the typical expected performance, using the Quartus II software v9.1 targeting a Arria<sup>®</sup> II GX (EP2AGX45CU17C5) device.

Table 1–3. 10-Gbps Ethernet Performance and Resource Utilization—Arria II GX Device

|      | FIFO<br>(eight-b |      |                       |     |                        |                    |               | f <sub>max</sub> (MHz) |                 | Memory |

|------|------------------|------|-----------------------|-----|------------------------|--------------------|---------------|------------------------|-----------------|--------|

| XAUI | yte<br>words)    | MDIO | Statistics<br>Counter | ECC | Combinational<br>ALUTs | Logic<br>Registers | Avalon-<br>MM | Avalon-<br>ST          | System<br>Clock | M9K    |

| Yes  | 256              | Yes  | Yes                   | No  | 5,670                  | 5,346              | 269           | 209                    | 199             | 4      |

# **1.3. Revision History**

Table 1-4 summarizes the new feature and device support history for this IP core.

| Release           | New Features                                                                                                                                                                              | Device Support<br>Added      | Device Support<br>Level        |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|--------------------------------|

| 10.0 July 2010    | <ul> <li>Added support for pause frame control (PFC). Frames can<br/>be passed to the user interface (no internal support for the<br/>pause control).</li> </ul>                          | _                            |                                |

| 9.1 December 2009 | <ul> <li>Added support for optional error correcting code (ECC) in<br/>memories in the Soft XAUI PC and the transmit (Tx) and<br/>receive (Rx) FIFOs on Stratix IV GX devices.</li> </ul> | HardCopy® III<br>HardCopy IV | Preliminary (1)<br>Preliminary |

|                   | <ul> <li>For the hard PCS, the local fault register is now asserted<br/>after reset until the link is up.</li> </ul>                                                                      |                              |                                |

|                   | <ul> <li>On the XGMII interface, the Tx now transmits with a clock<br/>shifted 90° and the Rx interface expects a clock that is<br/>shifted by 90°.</li> </ul>                            |                              |                                |

|                   | • Corrected address for linkFaultDetect register.                                                                                                                                         |                              |                                |

| Table 1–4. | New Features and Device Support History | (Part 1 of 2) |

|------------|-----------------------------------------|---------------|

|------------|-----------------------------------------|---------------|

| Release           | New Features                                                                                                            | Device Support<br>Added                                              | Device Support<br>Level                                |

|-------------------|-------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|--------------------------------------------------------|

| 9.0 March 2009    | <ul> <li>Added 2 input signals, xon_request and<br/>xoff_request that request XON and XOFF pause<br/>frames.</li> </ul> | Arria II GX                                                          | Preliminary                                            |

|                   | <ul> <li>Support for 1 primary and 4 supplemental addresses.</li> </ul>                                                 |                                                                      |                                                        |

|                   | <ul> <li>64-bit counters shadow upper 32 bits.</li> </ul>                                                               |                                                                      |                                                        |

|                   | <ul> <li>Soft XAUI and MAC-only options.</li> </ul>                                                                     |                                                                      |                                                        |

| 8.1 November 2008 | Initial release.                                                                                                        | Arria GX<br>Stratix II<br>Stratix II GX<br>Stratix III<br>Stratix IV | Full <i>(2)</i><br>Full<br>Full<br>Full<br>Preliminary |

#### Table 1-4. New Features and Device Support History (Part 2 of 2)

#### Notes to Table 1-4:

(1) *Preliminary support* means the IP core meets all functional requirements, but may still be undergoing timing analysis for the device family; it can be used in production designs with caution.

(2) *Full support* means the IP core meets all functional and timing requirements for the device family and can be used in production designs.

# 2. Getting Started with the 10-Gbps Ethernet IP

The chapter provides step-by-step instructions to help you get started using the Altera® 10-Gbps Ethernet IP core. It shows you how to install, generate, and simulate the 10-Gbps Ethernet IP core.

To use this document, you should already be familiar with the Ethernet protocol in general and 10-Gbps Ethernet in particular. You should also have some experience and familiarity with logic design using the Quartus<sup>®</sup> II software.

Refer to the Quartus II Development Software Literature page for information about the Quartus II design flow, including tutorials.

Altera categorizes this IP core as a reference design, described on the Altera website on the 10-Gbps Ethernet Reference Design web page.

This document describes the following development flow steps:

- 1. Licensing and Installation

- a. Free Time-Limited Evaluation Using OpenCore Plus Licensing

- b. Purchasing Full License for System Development

- c. Downloading and Installation

- 2. IP Core Parameterization

- a. Variation Options

- b. Design Flows

- 3. Functional Verification

- a. Testbench Files

- b. Testbench Utilities—Tasks and Procedures

- c. Running Tests

- 4. Implementation and Timing Analysis

- a. Synopsis Design Constraints

- b. Placement Constraints

- c. Timing Verification

# 2.1. Licensing and Installation

Depending on the phase of your design, the following licensing options are available.

# 2.1.1. Free Time-Limited Evaluation Using OpenCore Plus Licensing

You can use the OpenCore Plus feature to temporarily try out the IP core for free using one of Altera's development boards that include an Altera FPGA. There are two modes of operation:

- Untethered—the design runs for a limited time, typically one hour.

- *Tethered*—requires a connection between your board and the host computer. In tethered mode, the device can operate for a longer time or indefinitely.

- **For more information about the OpenCore Plus hardware evaluation, refer to** *AN 320: OpenCore Plus Evaluation of Megafunctions*.

# 2.1.2. Purchasing Full License for System Development

The use of this 10-Gbps Ethernet IP core is governed by, and is subject to, the terms and conditions of the Altera License Terms and Conditions for 10-Gbps Ethernet IP core.

Refer to License Terms and Conditions for 10-Gbps Reference Design for details about purchasing a full production license.

# 2.1.3. Downloading and Installation

Complete the following steps to download the 10-Gbps Ethernet IP core:

- 1. Go to the 10-Gbps Ethernet Reference Design web page.

- 2. To download the library, you must be a registered user. Click the **Download Reference Design** button to complete the registration steps.

- 3. To download the reference design, click the Proceed to Download Page button.

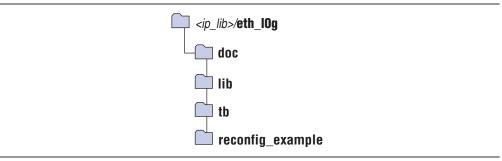

- 4. On the Download 10-Gbps Ethernet Reference Design page, click Download to save the compressed file to your working directory. Uncompress and extract the .zip file. These instructions refer to your project library directory as <ip\_lib>.

- Do not unzip to the standard Altera IP core directory altera \<version>\ip.

Figure 2–1 shows the directory structure.

The lib directory is required for all user designs. The other directories contain documentation and other files for an example design.

You can parameterize and instantiate the 10-Gbps Ethernet IP core using either the MegaWizard Plug-In Manager or SOPC Builder design flow. The MegaWizard Plug-In Manager allows you to customize and create RTL for the IP core and then integrate this variant into your overall design.

SOPC Builder allows you can add the 10-Gbps Ethernet IP core directly to a new or existing SOPC Builder system. Use this design flow if your design includes other SOPC Builder components. When you generate an SOPC Builder system, SOPC Builder automatically creates the HDL to connect components in your system design and generates simulation models.

**For more information on SOPC Builder, refer to** *Volume 4 of the Quartus II Handbook.*

#### 2.1.3.1. Install IP Core Library for MegaWizard Plug-In Manager Flow

Complete the following steps to install the design files for the MegaWizard Plug-In Manager design flow:

- 1. Choose **Programs > Altera > Quartus II>**<*version number*> (Windows Start menu) to run the Quartus II software.

- 2. To create a Quartus II project, complete the following steps:

- a. On the File menu, click New Project Wizard.

- b. In the New Project Wizard, follow the instructions to create a new Quartus II project. Navigation buttons at the bottom of the dialog wizard you through the steps. This user guide uses the project name tge\_91.qpf in the <project dir>/tge\_91 project design directory.

- 3. On the Assignments menu, click Settings.

- 4. In the Category list, click Library. Specify the following settings under Project libraries and Global libraries.

- a. In the Project library name, navigate to <ip\_lib>/eth\_10g/lib and double-click Open. You should see <ip\_lib>/eth\_10g/lib in the Project Library Name window.

- b. Click Add. The selected library appears under Libraries.

- c. Adapt steps a and b to include <ip\_lib>/eth\_10g/lib under Global libraries.

- d. Click OK.

- 5. On the File menu click Save Project. Type the project name tgb\_91.

You are now ready to create variations of the Altera 10-Gbps Ethernet design using the MegaWizard Plug-In Manager. You can locate the 10-Gbps Ethernet IP core in the MegaWizard Plug-In Manager by expanding Installed Plug-Ins > Interfaces > Ethernet.

#### 2.1.3.2. Install IP Core Libraries for the SOPC Builder Flow

Complete the following steps to install the design files for the system-on-a-programmable chip (SOPC) Builder design flow:

- 1. Install libraries for the MegaWizard Plug-In Manager as described in Section 2.1.3.1.

- 2. To start SOPC Builder, on the Tools menu, click SOPC Builder.

- 3. In the Create New System dialog box, click Cancel.

- 4. On the SOPC Builder Tools menu, click Options.

- 5. Under Category, click IP Search Path.

- 6. Click Add.

- 7. In the Open dialog box, navigate to <ip\_lib>/eth\_10g/lib/ip\_toolbench.

- 8. Click Open.

- 9. Click Finish. You can locate the 10G-Gbps Ethernet IP core in SOPC Builder by expanding: Interface Protocols -> Ethernet.

- For more information about SOPC Builder, refer to SOPC Builder which is volume 4 of the Quartus II Handbook.

# 2.2. IP Core Parameterization

This section provides an overview of the parameters that you can choose to customize your 10-Gbps Ethernet design. Figure 2–2 shows the MegaWizard Plug-In Manager.

#### Figure 2–2. 10-Gbps Ethernet Parameter Settings

| Parameter 2 EDA 3 Summary<br>Settings                        | )                                              | Parameters, EDA Tools<br>and Summary Tabs |

|--------------------------------------------------------------|------------------------------------------------|-------------------------------------------|

| -Variation Options<br>Variation: MAC + SOFT XAUI             | Soft XAUI TX PLL Type                          |                                           |

| FIFO Options                                                 |                                                |                                           |

| □ Include Avalon Streaming FIFO<br>Receiver FIFO size: 128 ∨ | (eight-byte words)   Store forward  Fill level |                                           |

| Transmitter FIFO size: 128 🗸                                 | (eight-byte words)                             |                                           |

| MAC Options                                                  | Transceiver Reconfiguration Options            |                                           |

| Enable MDIO                                                  | Use external reconfiguration block             |                                           |

| Clock divider: 64                                            | Starting channel number: 0                     |                                           |

| ECC Options                                                  | Default Register Value                         |                                           |

| ECC Protected RAMs                                           | Customer version number: 0000                  |                                           |

|                                                              |                                                |                                           |

Depending on the device and options that you choose, some of the parameters may not be available.

# 2.2.1. Variation Options

Table 2–1 describes the variation options available on the Parameter Settings tab.

Table 2–1. Variation Options (Part 1 of 2)

| Parameter Settings | Description                                                                                                                                                                                                                                                               |

|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MAC + XGMII        | Creates a IP core with a media access control (MAC) using an Avalon <sup>®</sup> Streaming (Avalon-ST) interface on the client side and 32-bit standard DDR XGMII interface operating at 156.25 MHz on the network side.                                                  |

| MAC + XAUI         | Creates a IP core that combines a MAC and a 10GBASE-X hard macro PHY with<br>an Avalon-ST interface on the client side and standard XAUI interface on the<br>network side.                                                                                                |

| MAC + Soft XAUI    | Creates a IP core that has the same functionality and external interfaces as a MAC with 10GBASE-X hard macro PHY; however, the physical coding sublayer (PCS) is implemented in soft logic instead of a hard macro. This option is only available for Stratix IV devices. |

| Parameter Settings    | Description                                                                                                                                                                                                                                                                                                                                                                       |

|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Soft XAUI only        | The <b>Soft XAUI only</b> option is only available on Stratix IV devices. It combines a 10GBASE-X XAUI soft PCS and a hard PMA. This configuration allows the design to use all the available transceivers. The soft XAUI PCS includes the transceiver megafunction and the reset sequence controller, which applies the transceiver reset signals with the required constraints. |

| Soft XAUI Tx PLL Type | These options are only available when you select <b>MAC + Soft XAUI</b> or <b>Soft XAUI Only.</b> These are two different PLLs:                                                                                                                                                                                                                                                   |

|                       | CMU–(clock multiplier unit) designed to achieve low Tx channel-to-channel skew                                                                                                                                                                                                                                                                                                    |

|                       | ATX-(auxiliary transmit) designed to improve jitter performance.                                                                                                                                                                                                                                                                                                                  |

|                       | For more information refer to <i>AN 578: Manual Placement of CMU PLLs and ATX PLLS in Stratix IV GX and GT Devices</i> and <i>Volume 3</i> of the <i>Stratix IV Device Handbook</i> .                                                                                                                                                                                             |

| MAC only              | Creates a IP core that includes the MAC with an Avalon-ST interface on the client side and 64-bit XGMII interface running at 156.25MHz on network side. This interface functions like an SDR interface.                                                                                                                                                                           |

| Table 2–1. Variation Options (Part 2 of 2 | Table 2–1. | Variation Options | (Part 2 of 2) |

|-------------------------------------------|------------|-------------------|---------------|

|-------------------------------------------|------------|-------------------|---------------|

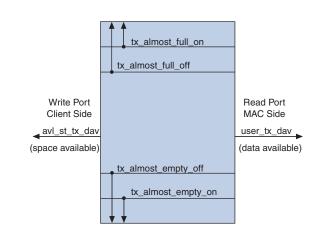

# 2.2.2. FIFO Options

In most applications, the client side interface of the IP core includes a FIFO between the client and the MAC. Table 2–2 describes the options that are available when you include the FIFO in the IP core.

Table 2–2. FIFO Options

| Parameter             | Value                | Description                                                                                                                                                                                                                                                                                                                                                              |

|-----------------------|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Receiver FIFO size    | 8,16,32,64,128,256,5 | Selects the depth of the FIFO in 8-byte words in each direction. The                                                                                                                                                                                                                                                                                                     |

| Transmitter FIFO size | 12,1024,4096,8192    | usable FIFO size is $\langle size \rangle - 1$ .                                                                                                                                                                                                                                                                                                                         |

| Mode                  | Store forward        | The packet information passes from the write side to the read side only<br>when the end of packet (EOP) is asserted on the write side. When you<br>select <b>Store forward</b> , you should select the FIFO size to accommodate the<br>longest possible frame in the system with some overhead. Altera<br>recommends twice the maximum possible frame size as a minimum. |

|                       |                      | In most cases, <b>Store forward</b> mode increases the latency and requires a deeper FIFO.                                                                                                                                                                                                                                                                               |

|                       | Fill level           | In <b>Fill level</b> mode, the FIFO begins passing data to the read side when a configurable number of bytes are available or an EOP is received.                                                                                                                                                                                                                        |

# 2.2.3. MAC Options

Table 2–3 describes the MAC options.

| Table 2-3. | MAC Options |

|------------|-------------|

|------------|-------------|

| Parameter                 | Values                   | Description                                                                                                                                                                                                     |

|---------------------------|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

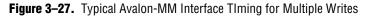

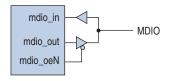

| Enable MDIO               | On/Off                   | When you turn this option <b>On</b> , the IP core instantiates an management data I/O (MDIO) master. The MDIO interface provides an Avalon Memory-Mapped (Avalon-MM) to MDIO bridge to control an external PHY. |

| Clock divider             | 4,8,16,32,<br>64,128,256 | The clock divider provides the division ratio for $sysclk$ to generate the preferred MDIO clock (MDC). The division factor must be defined such that the MDC frequency does not exceed 2.5 MHz.                 |

| Enable statistics counter | On/Off                   | When you turn this option <b>On</b> , the IP core includes registers to report statistics on frames transmitted and received.                                                                                   |

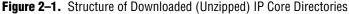

# 2.2.4. Transceiver Reconfiguration Options

Depending on the device and variant that you choose, reconfiguration of the transceiver may be an optional or required feature.

- If you select a Stratix II GX device and implement the MAC + XAUI variant, you can turn on Use external reconfig block, you can modify the properties of the transceiver using the ALTGX\_RECONFIG megafunction.

- If you select a Stratix IV GX or Arria II GX device with any variant that includes XAUI, you must include the ALTGX\_RECONFIG megafunction in your design; this option is always turned on.

- For Arria GX devices, this option is not available.

In any configuration that requires the ALTGX\_RECONFIG megafunction, you must instantiate it in your design and connect it to the 10-Gbps Ethernet IP core as shown in Figure 2–3.

#### Figure 2–3. Top-Level Block Diagram for 10-Gbps Ethernet, ALTGX Transceiver, and ALTGX\_RECONFIG Megafunction

• For more information on the ALT2GXB\_RECONFIG megafunction, refer to the *Stratix II GX ALT2GXB\_RECONFIG Megafunction User Guide*.

### 2.2.5. ECC Options

For Stratix IV devices, you can turn on ECC Protected RAMs option to configure single-bit error correction, double-bit error detection (SECDED) for data words up to 64 bits wide on the transmit and receive FIFOs and in the Soft XAUI PCS memory, for applications that require a highly-reliable 10-Gbps Ethernet solution. When you generate the IP core by clicking Finish in the MegaWizard interface, an ALTECC megafunction is automatically instantiated to implement this extra memory data protection.

If you turn on the ECC Protected RAMs, the IP core includes a set of error insertion registers to support ECC testing, and a set of ECC statistics counters that accumulate the counts of various types of ECC errors as they are detected, corrected, or both detected and corrected.

Turning on the ECC Protected RAMs affects the size and maximum achievable frequency of your IP core. For example, turning on this feature increases the widths of the ECC-protected FIFOs.

For information about the ALTECC megafunction, refer to the Error Correction Code (ALTECC\_ENCODER and ALTECC\_DECODER) Megafunctions User Guide.

# 2.3. Design Flows

The following sections explain how to customize your 10-Gbps Ethernet IP core using the MegaWizard Plug-in Manager and SOPB Builder design flows.

2-8

# 2.3.1. MegaWizard Plug-in Manager Design Flow

To customize you 10-Gbps Ethernet design using the MegaWizard Plug-In Manager design flow, complete the following steps.

- 1. Open your Quartus II project file, tge\_91.qpf.

- 2. Launch the MegaWizard Plug-in Manager from the Tools menu, and follow the prompts in the MegaWizard Plug-In Manager interface to create a custom megafunction variation. (The name you choose for your variation must not start with a number and should different from component names in the 10-Gbps Ethernet library that you installed.)

- 3. Specify the parameters on the Parameter Settings tab.

For detailed explanation of the parameters, refer to "IP Core Parameterization" on page 2–4.

4. On the EDA tab, turn on Generate simulation model to generate an IP functional simulation model for the IP core in the selected language.

An IP functional simulation model is a cycle-accurate VHDL or Verilog HDL model produced by the Quartus II software.

Some third-party synthesis tools can use a netlist that contains only the structure of the IP core, but not detailed logic, to optimize performance of the design that contains the IP core. If your synthesis tool supports this feature, turn on Generate netlist.

CAUTION

Use the simulation models only for simulation and not for synthesis or any other purposes. Using these models for synthesis creates a non-functional design.

- 5. On the **Summary** tab, select the files you want to generate. A grey checkmark indicates a file that is automatically generated. All other files are optional.

- 6. Click Finish to generate the IP core and supporting files.

You can now integrate the 10-Gbps Ethernet variant generated by the MegaWizard into your system design with other custom logic.

The MegaWizard generates a sample testbench, RTL files, SDC timing constraints, and placement and routing constraints. Their usage is explained in the following sections.

### 2.3.2. SOPC Builder Design Flow

In SOPC Builder you add the IP core directly to a new or existing SOPC Builder system. If your system includes other SOPC Builder components, such as the Nios II processor, external memory controllers, or scatter-gather DMA controllers, you can quickly create an SOPC Builder system with an Ethernet interface.

#### 2.3.2.1. Specify Parameters

Follow the steps below to specify 10-Gbps Ethernet parameters using the SOPC Builder flow.

- 1. Open your Quartus II project file.

- 2. Launch SOPC Builder from the Tools menu.

- 3. For a new system, specify the system name and language. This example uses the system name tge\_system and selects Verilog as the Target HDL.

- 4. Add 10-Gbps Ethernet to your system from the System Contents tab.

- You can find **10-Gbps Ethernet** by expanding **Interface Protocols** > **Ethernet** or by typing any string from the component name into the search field under the Component Library list.

- 5. Specify options on the Parameter Settings tab.

- For a detailed explanation of the parameters, refer to the "IP Core Parameterization" on page 2–4.

### 2.3.2.2. Complete the SOPC Builder System

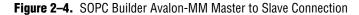

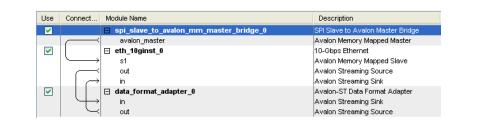

After you define the IP core parameters, you can integrate the core into a system design and connect the 10-Gbps interfaces. This document describes a very simple SOPC Builder system that includes two additional components, the SPI Slave to Avalon-MM Master Bridge and Data Format Adapter. The design creates a local loopback from the Tx to the Rx interfaces of the 10-Gbps Ethernet IP core. This example only demonstrates the SOPC Builder design flow; it is not a functional design.

**Refer to Application Note 588**, 10-*Gbps Ethernet Hardware Demonstration Reference Design* for a more complete design example.

Follow the steps below to complete the SOPC Builder system.

- 1. To add the SPI Slave to your system, expand Bridges and Adapters > Memory Mapped and double-click SPI Slave to Avalon Master Bridge. Click Finish to add this component to your system.

- As you add components to your system SOPC Builder reports errors in the console window. These errors disappear as you complete your system.

- 2. To add the Avalon-ST Data Format Adapter to your system, expand Bridges and Adapters > Streaming and double-click Avalon-ST Data Format Adapter.

- 3. On the **Parameter Settings** page, specify the following parameters shown in Table 2–4.

| Parameter                   | Value               |

|-----------------------------|---------------------|

| Data Symbols Per Beat       | 8                   |

| Include Empty Signal        | AUTO                |

| Channel Signal Width (bits) | 0                   |

| Max Channel                 | 0                   |

| Include Packet Support      | Turn this option on |

Table 2–4.

Avalon-ST Data Format Adapter Parameters (Part 2 of 2)

| Parameter                 | Value |  |  |  |  |

|---------------------------|-------|--|--|--|--|

| Error Signal Width (bits) | 1     |  |  |  |  |

| Ready Latency             | 1     |  |  |  |  |

| Data Bits Per Symbol      | 8     |  |  |  |  |

- 4. Click Finish to add this component to your system.

- 5. To complete this design, create the following connections:

- 6. Connectthespi\_slave\_to\_avalon\_mm\_master\_bridge\_0avalon\_masterAvalon master port to the eth\_10ginst\_0 s1 Avalon slave port using the following procedure:

- a. Click on the avalon\_master port then hover in the Connections column to display possible connections.

|                     |     | Use | Conne                                   | et .          | Module Na | ame              | Description                       | Clock  | Base         | End        | Tags | RC |

|---------------------|-----|-----|-----------------------------------------|---------------|-----------|------------------|-----------------------------------|--------|--------------|------------|------|----|

| Avalon-MM master    |     |     |                                         |               | E spr_st  | ave_to_avalon    | SPI Slave to Avaion Master Bridge |        |              |            |      |    |

| Avaion win master   | . ( |     |                                         |               |           |                  | Avaion Memory Mapped Master       | dk_0   |              |            |      |    |

| to slave connection |     |     |                                         |               | E eth_10  | lginst_0         | 10-Gbps Ethernet                  |        |              |            |      |    |

| to slave connection | 1   |     | <u> </u>                                | -             | 11        |                  | Avaion Memory Mapped Slave        | clk_0  | · 0x00000000 | 0x00000366 |      |    |

|                     |     |     | 6                                       |               | 0.4       |                  | Avalon Streaming Source           | clik_0 |              |            |      |    |

|                     |     |     | - ÷-                                    | $\rightarrow$ | in        |                  | Avalon Streaming Sink             | clik_0 |              |            |      |    |

|                     |     |     |                                         |               | 🛛 data 5  | format_adapter_0 | Avalon-ST Data Format Adapter     |        |              |            |      |    |

|                     |     |     | ~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~ | ≻             | in        |                  | Avaion Streaming Sink             | clk_0  |              |            |      |    |

|                     |     |     |                                         | 9             | 0.6       |                  | Avaion Streaming Source           |        |              |            |      |    |

- b. Click on the open dot at the intersection of the eth\_10ginst\_0 s1 port and the spi\_slave\_to\_avalon\_mm\_master\_bridge\_0 avalon\_master to create a connection.

- 7. Repeat step 6 to make the connections listed in Table 2–5.

#### Table 2–5. SOPC Builder Connections

| Make Connection From:  | To:                            |

|------------------------|--------------------------------|

| eth_10ginst_0 out port | data_format_adapter_0 in port  |

| eth_10ginst_0 in port  | data_format_adapter_0 out port |

Figure 2–5 shows the completed system.

Figure 2–5. SOPC Builder System Connections

- 8. Click the System Generation tab.

- 9. If you want to simulate your SOPC builder system, select **Simulate** on the **System Generation** tab to generate a functional simulation model for the system.

10. Click Generate to generate the system. The 10-Gbps Ethernet variant is eth\_10ginst\_0.v. A report file, *<variation\_name>*.html describes the HDL files that make up the design and the top-level signals.

# 2.4. Functional Verification

Altera provides a simple test infrastructure for basic functional verification of the customized IP core. This testbench is automatically generated when you generate your 10-Gbps Ethernet IP core. The details of the verification environment and how to use it is being described below.

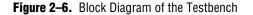

The testbench consists of the following components:

- An Avalon-ST client packet generator

- Avalon-ST client packet checker

- The 10-Gbps Ethernet device under test (DUT)

- An XGMII Ethernet packet generator

- An XGMII Ethernet packet checker

- An Avalon-MM configuration module

Figure 2–6 illustrates the top-level modules in the testbench. The testbench files are stored in clear text in <*ip\_lib*>/eth\_10g/tb.

The testbench sends and checks received Ethernet frames. The maximum supported frame size is 16 KBytes. It performs the following functions:

Generates Ethernet frames and checks their validity

- Generates Ethernet frames with CRC errors

- Generates frames on the Avalon-ST interface

- Provides access to the IP core registers via Avalon-MM interface

- Generates frames with virtual LAN (VLAN) or stacked VLAN tags

- Performs MDIO reads and writes

# 2.4.1. Testbench Files

Table 2–6 describes the files that implement the testbench.

| File Name                  | Description                                                                                                                                                                                                                                                                                                                               |

|----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| demo_hookup.iv             | The top-level testbench file. It includes the customized 10-Gbps Ethernet IP core which is the device under test (DUT), a client packet generator, and a client packet checker along with other logic blocks. This file ( <b>demo_hookup.iv</b> ) contains the DUT, packet generator, and packet checker, along with configuration logic. |

| demo_hutils.iv, tb_utils.v | These files include various test utilities to configure the DUT, the packet generator, and the packet checker. These utilities create tests such as <b>tb.v</b> .                                                                                                                                                                         |

| tb.v                       | This file includes tests that configure the testbench and transmit and receive packets via the MAC Tx and Rx ports.                                                                                                                                                                                                                       |

| demo_run_modelsim.tcl      | This is the simulation script that you can use to compile all files and run the test case.                                                                                                                                                                                                                                                |

# 2.4.2. Testbench Utilities—Tasks and Procedures

The tb\_utils.v file contains many tasks and functions to configure the components of the testbench. This section provides a description of some important Verilog HDL tasks. The VHDL functions are generally similar in structure and are not specifically listed below.

### 2.4.2.1. Avalon-MM Tasks

These tasks read and write the configuration and MDIO registers using the Avalon-MM protocol.

**For a more information about the Avalon-MM protocol refer to the** *Avalon Interface Specifications*.

#### write\_avalon

This command creates an Avalon-MM write command. You can use it to update registers.

| write_avalon |                                                                    |                                       |  |  |

|--------------|--------------------------------------------------------------------|---------------------------------------|--|--|

| Usage        | <pre>avalon_write(data_to_write, address_to_write)</pre>           |                                       |  |  |

| Arguments    | data_to_write The data to write at the specified address_to_write. |                                       |  |  |

|              | address_to_write                                                   | The address of the register to write. |  |  |

#### read\_avalon

This command creates an Avalon Memory-Mapped (Avalon-MM) read command. You can use it to read register values.

| read_avalon |                                                      |                                              |  |  |

|-------------|------------------------------------------------------|----------------------------------------------|--|--|

| Usage       | avalon_read(addre                                    | avalon_read(address_to_read, data_to_read)   |  |  |

| Arguments   | address_to_read The address of the register to read. |                                              |  |  |

|             | data_to_read                                         | The data to read from the specified address. |  |  |

#### write\_mdio

You can use this command to write the MDIO registers.

| write_mdio |                |                                                                                             |  |  |  |

|------------|----------------|---------------------------------------------------------------------------------------------|--|--|--|

| Usage      | write_mdio(cla | write_mdio(clause45, prtadr, devphyadr, regadr, data)                                       |  |  |  |

| Arguments  | clause45       | Set to 1 if the MDIO is for clause 45; set to 0 if the MDIO is for clause 22.               |  |  |  |

|            | prtadr         | Clause 45 PHY port address.                                                                 |  |  |  |

|            | devphyadr      | Clause 45 address of device (clause 45) or PHY (clause 22).                                 |  |  |  |

|            | regadr         | MDIO register address. It uses16 bits for clause 45 and the 5 low-order bits for clause 22. |  |  |  |

|            | data           | Write data for the MDIO register.                                                           |  |  |  |

#### read\_mdio

You can use this command to read the MDIO registers.

| read_mdio |               |                                                                                              |  |  |  |

|-----------|---------------|----------------------------------------------------------------------------------------------|--|--|--|

| Usage     | read_mdio(cla | read_mdio(clause45, prtadr, devphyadr, regadr, data)                                         |  |  |  |

| Arguments | clause45      | Set to 1 if the MDIO is for clause 45; set to 0 if the MDIO is for clause 22.                |  |  |  |

|           | prtadr        | Clause 45 PHY port address.                                                                  |  |  |  |

|           | devphyadr     | Clause 45 address of device (clause 45) or PHY (clause 22).                                  |  |  |  |

|           | regadr        | MDIO register address. It uses 16 bits for clause 45 and the 5 low-order bits for clause 22. |  |  |  |

|           | data_read     | Data read from the MDIO register.                                                            |  |  |  |

# 2.4.2.2. Avalon-ST Ethernet Frame Generation Tasks

You can use the following tasks to create ethernet frames to be sent on the Avalon-ST interface.

**For a more information about the Avalon-ST protocol refer to the** *Avalon Interface Specifications*.

#### gen\_valid\_frame

Creates a valid frame for transfer using the Avalon-ST protocol.

| gen_valid_frame |                                                           |                                                                                        |  |

|-----------------|-----------------------------------------------------------|----------------------------------------------------------------------------------------|--|

| Usage           | <pre>gen_valid_frame(pkt_length, pkt_type, min_ipg)</pre> |                                                                                        |  |

| Arguments       | pkt_length                                                | The length of the payload in bytes.                                                    |  |

|                 | pkt_type                                                  | Packet type. This the data that you entered in the length and type field of the frame. |  |

|                 | min_ipg                                                   | The minimum inter-packet gap (IPG) bytes to be generated.                              |  |

#### gen\_idles

Creates idles cycles on the Tx interface.

| gen_idles |                         |                                                                  |

|-----------|-------------------------|------------------------------------------------------------------|

| Usage     | gen_idles (idle_length) |                                                                  |

| Arguments | idle_length             | Number of idle cycles to be transmitted on the MAC Tx interface. |

### 2.4.2.3. Ethernet Frame Generation Tasks

You can use the following tasks to generate Ethernet frames which are sent over the Avalon-ST interface.

#### gen\_valid\_frame

Creates a valid frame for transfer using the Avalon-ST protocol.

| gen_valid_frame |                                                           |                                                                                                |

|-----------------|-----------------------------------------------------------|------------------------------------------------------------------------------------------------|

| Usage           | <pre>gen_valid_frame(pkt_length, pkt_type, min_ipg)</pre> |                                                                                                |

| Arguments       | pkt_length                                                | The physical size, which includes the payload only and must be greater than 4.                 |

|                 | pkt_type                                                  | Packet type.This is the 2 octet type of length.                                                |

|                 | min_ipg                                                   | The16-bit vector packet-inter packet gap, which you must specify. The minimum value is 8 bytes |

#### gen\_crc\_errored\_frame

Creates a valid frame for transfer using the Avalon-ST protocol.

| gen_crc_errored_frame |                                                                |                                                                                                |

|-----------------------|----------------------------------------------------------------|------------------------------------------------------------------------------------------------|

| Usage                 | <pre>gen_crc_errored_frame(pkt_length,pkt_type, min_ipg)</pre> |                                                                                                |

| Arguments             | pkt_length                                                     | The physical size, which includes the payload only and must be greater than 4.                 |

|                       | pkt_type                                                       | Packet type.This is the 2 octet type of length.                                                |

|                       | min_ipg                                                        | The16-bit vector packet-inter packet gap, which you must specify. The minimum value is 8 bytes |

# 2.4.3. Running Tests

You can use the **tb.v** as sample test to perform preliminary verification of the IP core. You can extend this example to create other tests to create a complete verification suite.

#### 2.4.3.1. Typical Test Sequence

A typical test case performs the following operations after a simulated power-on reset:

- 1. Initialize the 10-Gbps Ethernet IP core, which consists the following operations:

- a. Set the operation mode in the command\_config register.

- b. Set the address via the mac\_0 and mac\_1 registers.

- c. Set the IPG for transmit frames via the tx\_ipg\_length register.

- d. Set the Avalon-ST FIFO threshold registers.

- e. Set the supplemental unicast addresses.

- 2. Start transmission and clear the Rx and Tx FIFOs.

#### 2.4.3.2. Running sample test case

Before you can run the example tests, you must compile several RTL files and libraries. A script in the /tb directory performs these tasks. To run the script, complete the following tasks:

- 1. Change to the <project\_dir>/tge\_91/tb/verilog directory.

- 2. Launch ModelSim software.

- 3. Type the following command at the command prompt:

source demo\_run\_modelsim.tcl 🛩

4. Upon successful completion, the following text appears in the ModelSim transcript:

Example 2–1. Transcript from Successful Run in ModelSim

```

# DESC: Demonstration testbench

Time: 45 ns Instance: tb.DUT.nl1ii0ii.pll2

# 160005 Info: Avalon MM write at addr_hex=c, data_hex=34221400, time=160005

# 180005 Info: Avalon MM write at addr_hex=10, data_hex=80007bab, time=180005

# 200005 Info: Avalon MM write at addr_hex=300, data_hex=fe453681, time=200005

# 220005 Info: Avalon MM write at addr_hex=304, data_hex=8000c43c, time=220005

# 240005 Info: Avalon MM write at addr_hex=5c, data_hex=c, time=240005

# 260005 Info: Avalon MM write at addr hex=1c, data hex=3c0, time=260005

# 280005 Info: Avalon MM write at addr hex=20, data hex=40, time=280005

# 300005 Info: Avalon MM write at addr_hex=24, data_hex=3c0, time=300005

# 320005 Info: Avalon MM write at addr_hex=28, data_hex=40, time=320005

# 340005 Info: Avalon MM write at addr_hex=2c, data_hex=3c0, time=340005

# 360005 Info: Avalon MM write at addr_hex=30, data_hex=40, time=360005

# 380005 Info: Avalon MM write at addr_hex=34, data_hex=3c0, time=380005

# 400005 Info: Avalon MM write at addr_hex=38, data_hex=40, time=400005

# 420005 Info: Avalon MM write at addr_hex=8, data_hex=80000203, time=420005

# 742759 eth_gen generating packet pkt_type 100 -- pkt_size

100

# 851559 eth gen generating packet pkt type 101 -- pkt size

101

# 963559 eth gen generating packet pkt type 102 -- pkt size

102

# 1327247 avl_st_checker : received packet

# 1423247 avl_st_checker : received packet

# 1538447 avl_st_checker : received packet

```

```

#

#

Testbench tb.custdemo elapsed time 1000 ns

# 1075559 eth gen generating packet pkt type 103 -- pkt size

103

# 1128847 avl_st_checker : received packet

# 1187559 eth_gen generating packet pkt_type 104 -- pkt_size

104

# 1231247 avl_st_checker : received packet

Testbench tb.custdemo elapsed time 2000 ns

Testbench tb.custdemo elapsed time 3000 ns

# 3538447 avl_st_gen generating packet pkt_type 100 -- pkt_size

100

# 3634447 avl st gen generating packet pkt type 101 -- pkt size

101

# 3730447 avl_st_gen generating packet pkt_type 102 -- pkt_size

102

# 3826447 avl_st_gen generating packet pkt_type 103 -- pkt_size

# 3922447 avl_st_gen generating packet pkt_type 104 -- pkt_size

103

104

#

Testbench tb.custdemo elapsed time 4000 ns

#

Testbench tb.custdemo elapsed time 5000 ns

# DONECHECK #1: tb.custdemo, time: 5656 ns

*******

# ********

# $$$ End of testbench tb.custdemo at : 5666359

# chk_cnt = 1, exp_chk_cnt = 1

\# err cnt = 0, exp err cnt = 0

# $$$ Exit status for testbench tb.custdemo : TESTBENCH_STATUS: COMPLETED PASSED

```

# 2.5. Implementation and Timing Analysis

When you generate a custom 10-Gbps Ethernet IP core, the Quartus II software also generates files for timing constraints and place and route. When you instantiate your Ethernet IP core in a complete system design, you can use these scripts as a guide when creating the timing constraints for your complete system.

You can use the Tcl interface to add constraints to your design. In particular, the constraints in the tge\_91\_contraints.tcl file prevent shift registers from converting to memory, which is important if your design includes the optional ECC functionality. To add these constraints to your design, type the following command in the Quartus II Tcl Console window:

source tge\_91\_contraints.tcl

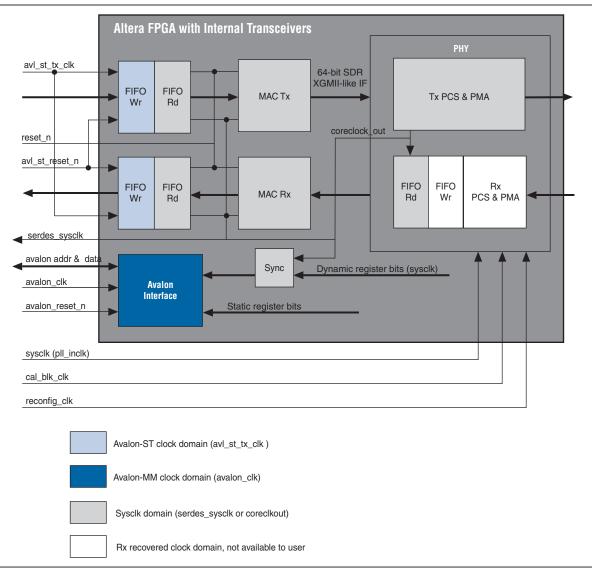

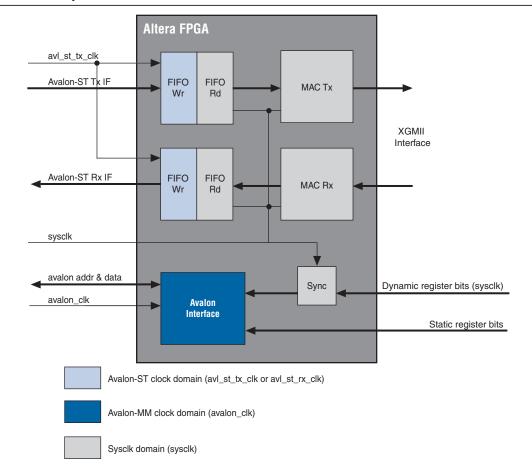

## 2.5.1. Clock Domains

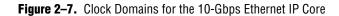

The 10-Gbps Ethernet IP core includes at least three clock domains. There is a fourth clock domain if your design includes the ALTGX\_RECONFIG megafunction discussed in "Transceiver Reconfiguration Options" on page 2–7. These clock domains are shown in Figure 2–7. The design logic synchronizes signals that cross clock boundaries. This logic is not shown in Figure 2–7.

# 2.5.2. Reset Synchronization

The IP core provides a separate reset pin for each clock domain. The design uses the following reset and clock pairs:

- reset\_n—resets the sysclk clock domain. sysclk connects to the MAC Tx and Rx and the MAC side of FIFO interfaces.

- avl\_st\_reset\_n—resets the avl\_st\_clk clock domain. The clock domain is

for the client side of the FIFO or MAC logic.

- avalon\_reset\_n—resets the avalon\_clk domain.

The reset pins are active low and must be synchronized by their respective clocks before use.

### 2.5.3. Synopsis Design Constraints

The timing constraints are provided by the Synopsis Design Constraints File (.sdc). In this example, tge\_91.sdc defines clocks and timing exceptions. The file specifies the following information:

- All clocks generated from PLLs

- Timing uncertainty from clock sources

- All clocks that are not generated from PLLs

- All asynchronous clock groups

Example 2–2 shows the constraints included in the .sdc for the 10-Gbps Ethernet IP core.

Example 2–2. Timing Constraints for the 10-Gbps Ethernet IP Core

```

// Create clocks other than generated clocks

create_clock -period 6.4 -name {sysclk} [get_ports *sysclk]

create_clock -period 10 -name {avalon_clk} [get_ports *avalon_clk]

create_clock -period 6.4 -name {av1_st_clk} [get_ports *av1_st_clk]

create_clock -period 20 -name {reconfig_clk} [get_ports *reconfig_clk]

// Create asynchronous clock groups

set_clock_groups -asynchronous -group {sysclk} -group {avalon_clk }

set_clock_groups -asynchronous -group {av1_st_clk} -group {avalon_clk}

set_clock_groups -asynchronous -group { avalon_clk } -group { avalon_clk }

set_clock_groups -asynchronous -group { avalon_clk } -group { avalon_clk } set_clock_groups -asynchronous -group { avalon_clk } -group { *eth_10g_inst|xaui_10g_genblk.xaui_10g|xaui_10g_serdes4_reconfig_genblk.xaui_10g_ser

des4_reconfig|xaui_10g_genblk.xaui_10g|xaui_10g_serdes4_reconfig_genblk.xaui_10g_ser

des4_reconfig|xaui_10g_genblk.xaui_10g|xaui_10g_serdes4_reconfig_genblk.xaui_10g_ser

des4_reconfig|xaui_10g_serdes4_reconfig_*|central_clk_div0|coreclkout }

```

Refer to "Clocks and Reset " on page 3–57 for more information about clocking.

# **2.5.4.** Placement Constraints

In this example, some global clocks and synthesis options are specified in tge\_constraints.tcl. Example 2–3 shows typical pin type and placement assignments.

**Example 2–3.** Pin Assignments in the .qsf File

```

set_instance_assignment -name IO_STANDARD "3.3-V LVCMOS" -to MYPIN

set_location_assignment PIN_G14 -to MYPIN

```

Refer to the appropriate Device Handbook, Pin-Out Files for Altera Devices, and Device Pin Connection Guidelines web pages for the targeted Altera device to determine available I/O standards and pin assignments for your design.

### 2.5.5. Timing Verification

Upon successful compilation, the Quartus II software generates output files that specify important features of your design. Table 2–7 lists the most important output files. All of the output files are described in *<variation\_name*.html.

| File Name                                 | Description                                                                                                   |

|-------------------------------------------|---------------------------------------------------------------------------------------------------------------|

| <variation_name>.pin</variation_name>     | Lists the pin location assignments in the final design.                                                       |

| <variation_name>.fit.rpt</variation_name> | Contains information on logic utilization, resource utilization, timing models, and other useful information. |

| <variation_name>.sta.rpt</variation_name> | Provides the timing analysis report and the results of the timing analysis including timing path slack.       |

Table 2–7. Quartus II Output Files

# **3. 10-Gbps Ethernet IP** Functional Description

This chapter provides a detailed description of Altera's 10-Gbps Ethernet IP core. It begins with a high-level overview of typical 10-Gbps Ethernet systems and then provides detailed descriptions of the MAC, transmit (Tx) and receive (Rx) datapaths, ECC, software programming model, register descriptions, PHY, clock domains, and reset. It includes the following sections:

- Typical 10-Gbps Ethernet Systems

- MAC Functional Description

- ECC Options

- Software Programming Interface

- Register Descriptions

- 10-Gbps Ethernet PHY

- Clocks and Reset

# 3.1. Typical 10-Gbps Ethernet Systems

This section provides top-level block diagrams of all of the variants that you can create when you to customize your 10-Gbps Ethernet IP core.

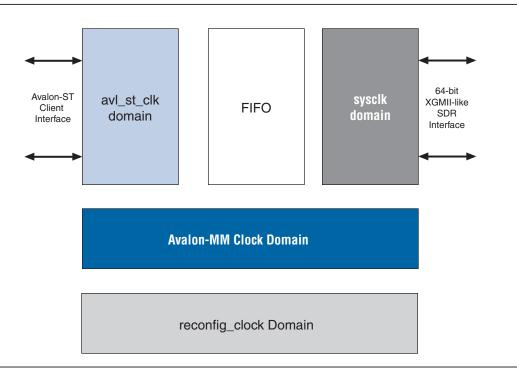

Figure 3–1 illustrates a system with a MAC connecting an external 10-Gbps Ethernet device over XAUI.

Altera categorizes this IP core as a reference design, described on the Altera website on the 10-Gbps Ethernet Reference Design web page.

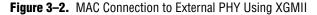

Figure 3–2 illustrates a system with a MAC connecting an external 10-Gbps Ethernet PHY over XGMII.

# **3.2. MAC Functional Description**

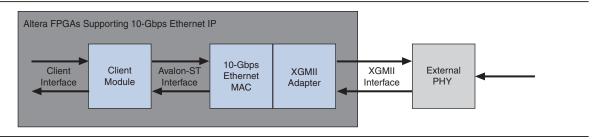

The Altera 10-Gbps Ethernet MAC implements the 10-Gbps Ethernet MAC in accordance with the IEEE 802.3 2005 specification. This module handles the flow of data between a client and Ethernet network via a 10-Gbps Ethernet PHY. In the Tx direction, the MAC accepts client frames, inserts an interpacket gap (IPG), preamble, start of frame delimiter (SFD), headers, and checksums before passing them to the PHY. The PHY encodes the MAC frame as required for reliable transmission over the media to the remote end. Similarly, in the receive direction, the MAC accepts frames via a PHY, performs checks, generates statistics, strips out the preamble and SFD, and passes the rest of the frame to the client.

The MAC includes the following interfaces:

- Data path interfaces

- Client side–Avalon-ST 64-bits wide

- PHY side–XAUI or XGMII

- Management interface

- Avalon-MM host slave interface

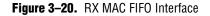

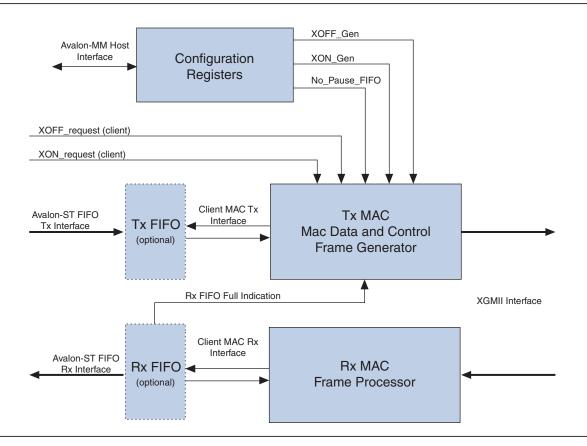

The Avalon-MM interface provides host access to the MAC and PHY configuration, status, MAC, statistics counters registers, and external PHY device registers via the MDIO interface. Figure 3–3 illustrates the top-level modules of the MAC. As Figure 3–3 illustrates, the MAC can be connected to the client directly or using an optional FIFO.

Figure 3–3. High-Level Block Diagram of the 10-Gbps Ethernet MAC

# 3.2.1. Transmit Datapath

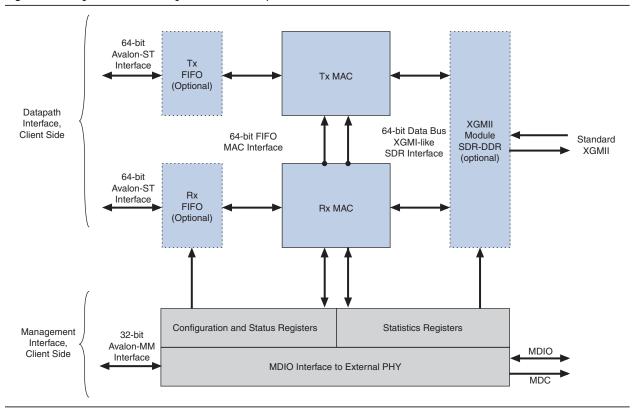

The Tx MAC module receives the client payload data with the destination and source addresses and then adds, appends, or updates various header fields in accordance with the configuration specified. The MAC does not modify the destination address or the payload received from client. However, the Tx MAC module adds a preamble, pads the payload to satisfy the minimum Ethernet frame payload of 64 bytes, and calculates the CRC over the entire MAC frame. (If padding is added, it is also included in CRC calculation.) The Tx MAC module can also modify the source address, and insert interpacket gap (IPG) bytes when necessary.

#### Figure 3-4 illustrates the changes that the Tx MAC makes to the client frame.

**Figure 3–4.** Typical Client Frame at the XGMII (Tx) Interface

#### Notes to Figure 3-4:

(1) = payload size = 0–1500 bytes, or 9600 bytes for jumbo frames.

- (2)  $\langle s \rangle$  = padding bytes = 0-46 bytes

- (3)  $\langle I \rangle$  = number of IPG bytes

The following sections describe the functions that the Tx module performs.

#### 3.2.1.1. Start, Preamble, and SFD Insertion

In the Tx datapath the MAC appends a one-byte START, 6-byte preamble, and 1-byte SFD to the client frame. (This MAC module also incorporates the functions of the reconciliation sublayer.)

#### 3.2.1.2. Address Insertion

The client provides the destination MAC address and the source address of the local MAC. However, if enabled by a Command\_Config Register bit, the source MAC address can be replaced by the primary address contained in two, 32-bit MAC registers: mac\_0 and mac\_1.

#### 3.2.1.3. Length/Type Field Processing

This two-byte header represents either the length of the payload or the type of MAC frame. When the value of this field is equal to or greater than 1536 (0x600) it indicates a type field. Otherwise, this field provides the length of the payload data that ranges from 0–1500 bytes. The Tx MAC does not modify this field and forwards it to the network.

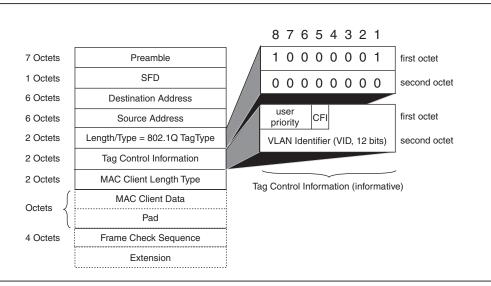

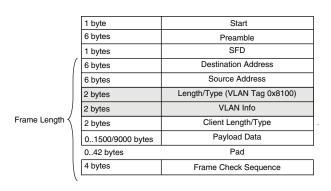

#### 3.2.1.4. VLAN and Stacked VLAN Frames Processing

The extension of a basic frame is a VLAN tagged frame, which contains an additional VLAN tag field between the source address and length/type fields as Figure 3–5 illustrates. VLAN tagging is defined by the IEEE 802.1Q standard. VLANs can identify and separate many groups' network traffic in enterprises and metro networks.VLAN tagged frames have a maximum length of 1522 bytes, excluding the preamble and the SFD bytes. In carrier Ethernet network applications based on IEEE 802.1ad provider bridge standard (QinQ) for scaling the network, frames can be tagged with two consecutive VLAN tags (stacked VLAN). Stacked VLAN frames

contain an additional 8-byte field between the source address and length/type fields. The Tx MAC forwards the VLAN or stacked VLAN tag and fields to the PHY as it would for other payload octets. Recently, the IEEE 802.1ah standard for Provider Backbone Bridge (PBB) and PBB traffic engineering (TE) or MAC-in-MAC is gaining traction which still can use this VLAN stacking for inner and outer VLAN tags.

Figure 3–5. MAC Frame Showing VLAN Fields

#### 3.2.1.5. Frame Padding

When the length of client frame is less than 64 bytes (meaning the payload is less than 46 bytes), the Tx MAC module inserts pad bytes (0x00) after the payload to create a frame length equal to the minimum size of 64 bytes.

#### 3.2.1.6. Frame Check Sequence (CRC-32) Insertion

The Tx MAC computes and inserts CRC32 checksum in the transmitted MAC frame. The frame check sequence (FCS) field contains a 32-bit CRC value. The MAC computes the CRC32 over the frame bytes that include the source address, destination address, length, data, and pad. The CRC checksum computation excludes the preamble, SFD, FCS, and extension. The encoding is defined by the following generating polynomial:

$FCS(X) = X^{32} + X^{26} + X^{23} + X^{22} + X^{16} + X^{12} + X^{11} + X^{10} + X^8 + X^7 + X^5 + X^4 + X^2 + X^1 + 1$

CRC bits are transmitted with MSB (X<sup>32</sup>) first. (Refer to "Byte Order on the Avalon-ST Interface Lanes" on page 3–14 and "Octet Transmission on the Avalon-ST SIgnals" on page 3–14 for illustrations of byte ordering.

#### 3.2.1.7. Interpacket Gap Generation and Insertion

The Tx MAC maintains the minimum interpacket gap (IPG) between transmitted frames required by the IEEE 802.3 Ethernet standard. The default minimum IPG minimum is maintained at 96 bit times (or 12 byte times). However, you can change the default IPG (in bytes) via the configuration register  $tx_ipg_length$ . You can configure the minimum IPG to any value between 8 bytes and 252 bytes times in the  $tx_ipg_length$  register.

The deficit idle counter maintains an average IPG. You can configure the average IPG value in the  $tx_ipg_length$  register (0x05c). The number is a multiple of 4 with a minimum of 8 and a maximum of 252. The default (IEEE required value) is 12.

To guarantee reliable PCS functionality, Altera recommends that you set the IPG to a minimum of 12 bytes. The IPG between successive frames varies and is the minimum that you specify ±3 bytes.

### 3.2.2. Tx Interfaces

This section describes the following Tx interfaces:

- "Tx Client Side Interfaces " on page 3–6

- "Tx FIFO Client Interface " on page 3–6

- "FIFO MAC Interface " on page 3–9

- SDR XGMII Tx Interface " on page 3–12

- "Standard DDR XGMII Interface" on page 3–11

#### **3.2.2.1. Tx Client Side Interfaces**

The client side of the interface depends on whether you included a FIFO in your design. If a FIFO is included, the client connects to the FIFO's client side interface, otherwise the client connects directly to the MAC's client interface.

The client Tx datapath employs the Avalon Streaming (Avalon-ST) protocol. The Avalon-ST protocol is a synchronous point-to-point, unidirectional interface that connects the producer of a data stream (source) to a consumer of data (sink). The key properties of this interface include:

- Frame transfers marked by startofpacket and endofpacket signals.

- Signals from source to sink are qualified by the valid signal.

- Errors marking a current packet, are aligned with endofpacket cycle.

- Use of the ready signal by the sink backpressure the source. The source must respond to the ready signal from sink by deasserting the valid signal after a fixed number of cycles defined by the ready\_latency.

The client acts as a source and the Tx FIFO/MAC acts as a sink in the transmit direction. If your design does not include the optional FIFO, the MAC does not buffer client data and it must receive data continuously between the assertions of the startofpacket and endofpacket signals.

For more information about the Avalon-ST interface refer to the Avalon Interface Specifications.

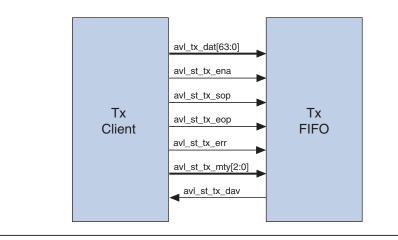

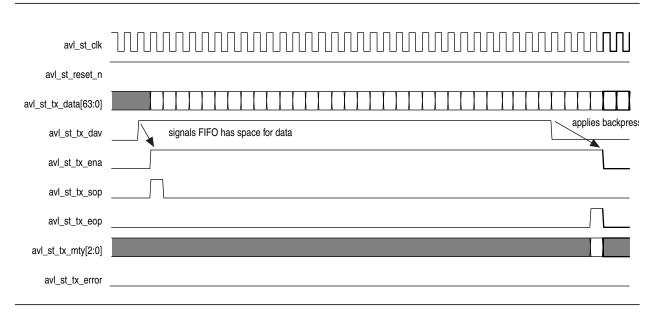

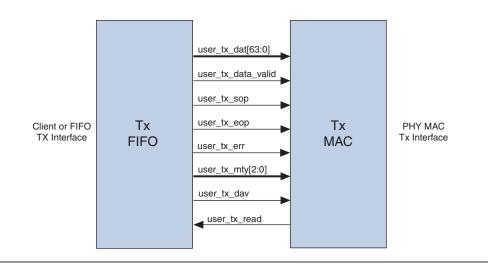

#### 3.2.2.2. Tx FIFO Client Interface

This is an Avalon-ST interface that provides backpressure from the MAC Tx sink to the client via Tx FIFO. The Tx FIFO receives data from the client and buffers it until the MAC is ready to consume it. Figure 3–6 illustrates this interface.

Table 3–1 describes the signals that comprise this interface.

Table 3–1. FIFO Client Interface Signals–AnAvalon-ST Interface

| Signal Name         | Dir | Description                                                                                                                                                                                                                                                                                                                                                                          |

|---------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| avl_st_tx_dat[63:0] | I   | 64-bit client (source) data.                                                                                                                                                                                                                                                                                                                                                         |

| avl_st_tx_ena       | I   | When asserted, Indicates that avl_st_tx_dat, avl_st_tx_sop,<br>avl_st_tx_eop, and avl_st_tx_mty are valid.                                                                                                                                                                                                                                                                           |

| avl_st_tx_sop       | I   | Asserted for one cycle to indicate the start of client/source data.                                                                                                                                                                                                                                                                                                                  |

| avl_st_tx_eop       | I   | Asserted for one cycle to indicate the end of client/source data.                                                                                                                                                                                                                                                                                                                    |

| avl_st_tx_mty[2:0]  | I   | Specifies how many bytes of avl_st_tx_dat[63:0] are empty when avl_st_tx_eop is asserted as follows:                                                                                                                                                                                                                                                                                 |

|                     |     | Value Valid Data Bits                                                                                                                                                                                                                                                                                                                                                                |

|                     |     | 0 avl_tx_dat[63:0]<br>1 avl_tx_dat[63:8]<br>2 avl_tx_dat[63:16]<br>3 avl_tx_dat[63:24]<br>4 avl_tx_dat[63:32]<br>5 avl_tx_dat[63:40]<br>6 avl_tx_dat[63:48]<br>7 avl_tx_dat[63:56]                                                                                                                                                                                                   |