# Farnell Order Code: 1538951

FOX MODEL: FXO-PC735R-312.5

FOX Part Number: 774-312.5-10 LVPECL, CERAMIC, SMD, OSCILLATOR

### **Specifications**

| Specifications                               |                    |  |  |

|----------------------------------------------|--------------------|--|--|

| Parameters                                   |                    |  |  |

| Frequency                                    | 312.5 MHz          |  |  |

| Frequency Stability <sup>1</sup>             | ±50PPM             |  |  |

| Temperature Range                            |                    |  |  |

| Operating (T <sub>OPR</sub> )                | -40°C ~ +85°C      |  |  |

| Storage (T <sub>STG</sub> )                  | -55°C ~ +125°C     |  |  |

| Supply Voltage (VDD)                         | 3.3V ± 5%          |  |  |

| Input Current (IDD)                          | 120 mA Max         |  |  |

| Output Voltage (V <sub>OL</sub> )            | 1.305V ~ 1.65V     |  |  |

| (V <sub>OH</sub> )                           | 2.055V ~ 2.405V    |  |  |

| Output Symmetry (50% V <sub>p-p</sub> Level) | 45% ~ 55%          |  |  |

| Rise Time (20% ~ 80% V <sub>p-p</sub> ) (TR) | 400 pS Max         |  |  |

| Fall Time (80% ~ 20% V <sub>p-p</sub> ) (TF) | 400 pS Max         |  |  |

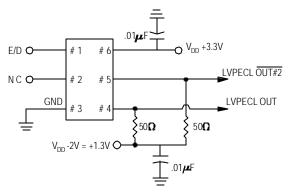

| Output Load (Recommended Circuit below)      | 50 ohms into +1.3V |  |  |

| Startup Time (T <sub>S</sub> )               | 10 ms Max          |  |  |

| Output Enable / Disable Time <sup>2</sup>    | 100 nS Max         |  |  |

| Phase Jitter (12kHz ~ 20MHz)                 | 0.98 pS Typ.       |  |  |

| Maximum Soldering Temp / Time                | 260°C / 10 Seconds |  |  |

| Moisture Sensitivity Level (MSL)             | 1                  |  |  |

| Termination Finish                           | Au                 |  |  |

<sup>&</sup>lt;sup>1</sup> Inclusive of 25°C tolerance, operating temperature range, input voltage change, load change, aging, shock, and vibration. <sup>2</sup>An internal pullup resistor from pin 1 to pin 6 allows active output if pin 1 is left open.

| ENABLE/DISABLE FUNCTION <sup>2</sup> |                   |  |  |  |

|--------------------------------------|-------------------|--|--|--|

| Pin 1                                | OUTPUT (Pin 4, 5) |  |  |  |

| OPEN <sup>2</sup>                    | ACTIVE            |  |  |  |

| '1' Level VIH ≥ 70%V <sub>DD</sub>   | ACTIVE            |  |  |  |

| '0' Level VIL ≤ 30%V <sub>DD</sub>   | High Z            |  |  |  |

NOTE A  $0.01\mu F$  bypass capacitor should be placed between V <sub>DD</sub> (Pin6) and GND (Pin 3) to minimize power supply line noise.

#### RoHS Compliance Status: Compliant

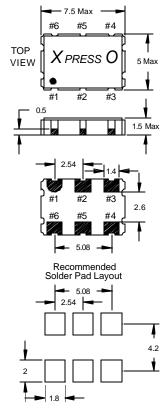

Drawing is for reference to critical specifications defined by size measurements.

Certain non-critical visual attributes, such as side castellations, reference pin shape, etc. may vary

## Mechanical / Dimensions (millimeters):

## **Pin Connections**

#1 E/D #4 Output 1 #2 NC #5 Output 2 #3 GND #6 V<sub>DD</sub>

#### **Recommended Circuit**

NOTE. The above specifications, having been carefully prepared and checked, is believed to be accurate at the time of publication; however, no responsibility is assumed by Fox Electronics for inaccuracies.

| Reference / Comments | Title / Description: P | Title / Description: Product Specifications |  |                  |  |  |

|----------------------|------------------------|---------------------------------------------|--|------------------|--|--|

|                      | Drawing Number: D\     | Drawing Number: DWG-4553-7 Rev: 1           |  | Size: A          |  |  |

|                      | Part Number: 774-      | Part Number: 774-312.5-10                   |  | Cage: 61429      |  |  |

|                      | Draftsperson: AR       | Draftsperson: AR Approved: BN               |  | Date: 01/15/2008 |  |  |

| Page 1 of 1          |                        |                                             |  |                  |  |  |