# Specification for BTHQ 128064AVE-FETF-06-LEDWHITE-COG

Version November 2003

NOV/2003

PAGE 2 OF 15

| DOCUMENT | DATE       | DESCRIPTION    | CHANGED   | CHECKE    |

|----------|------------|----------------|-----------|-----------|

| REVISION |            |                | BY        | BY        |

| FROM TO  |            |                |           |           |

| А        | 2003.11.28 | First Release. | SUNNY LEE | PRITT LEI |

|          |            |                |           |           |

|          |            |                |           |           |

|          |            |                |           |           |

|          |            |                |           |           |

|          |            |                |           |           |

|          |            |                |           |           |

|          |            |                |           |           |

|          |            |                |           |           |

|          |            |                |           |           |

|          |            |                |           |           |

|          |            |                |           |           |

|          |            |                |           |           |

|          |            |                |           |           |

|          |            |                |           |           |

|          |            |                |           |           |

|          |            |                |           |           |

|          |            |                |           |           |

|          |            |                |           |           |

|          |            |                |           |           |

|          |            |                |           |           |

|          |            |                |           |           |

|          |            |                |           |           |

|          |            |                |           |           |

|          |            |                |           |           |

|          |            |                |           |           |

|          |            |                |           |           |

|          |            |                |           |           |

|          |            |                |           |           |

|          |            |                |           |           |

|          |            |                |           |           |

|          |            |                |           |           |

|          |            |                |           |           |

|          |            |                |           |           |

|          |            |                |           |           |

# VL-FS-COG-BTHQ12864-03 REV. A (BTHQ 128064AVE-FETF-06-LEDWHITE-COG)

NOV/2003

PAGE 3 OF 15

# **CONTENTS**

Page No.

| 1.                      | GENERAL DESCRIPTION                                                                                         | 4                    |

|-------------------------|-------------------------------------------------------------------------------------------------------------|----------------------|

| 2.                      | MECHANICAL SPECIFICATIONS                                                                                   | 4                    |

| 3.                      | INTERFACE SIGNALS                                                                                           | 7                    |

| 4.<br>4.1<br>4.2        | ABSOLUTE MAXIMUM RATINGS<br>ELECTRICAL MAXIMUM RATINGS (Ta=25°C)<br>ENVIRONMENTAL CONDITION                 | 9<br>9<br>9          |

| 5.<br>5.1<br>5.2<br>5.3 | ELECTRICAL SPECIFICATIONS<br>TYPICAL ELECTRICAL CHARACTERISTICS<br>TIMING SPECIFICATIONS<br>INSTRUCTION SET | 10<br>10<br>11<br>14 |

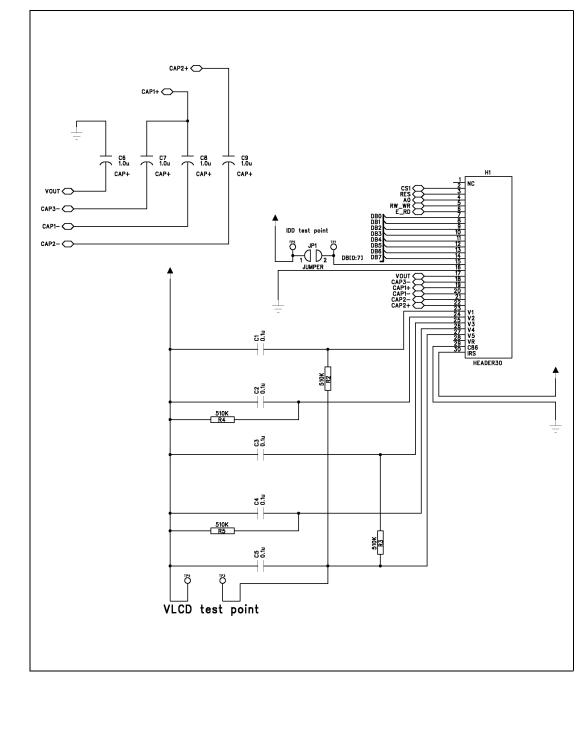

| 6.                      | REFERENCE APPLICATION CIRCUIT (8080) EXAMPLE                                                                | 15                   |

### VL-FS-COG-BTHQ12864-03 REV. A (BTHQ 128064AVE-FETF-06-LEDWHITE-COG)

NOV/2003

PAGE 4 OF 15

# Specification of LCD Module Type Model No.: COG-BTHQ12864-03

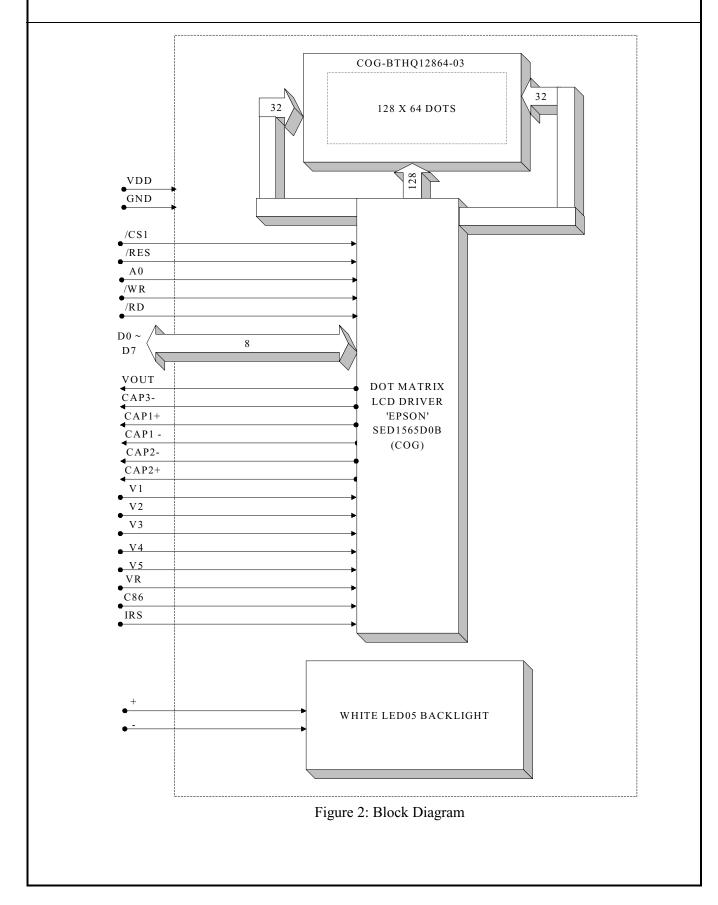

#### **1. General Description**

- 128 x 64 dots FSTN Positive Black & White Transflective Dot Matrix LCD Module.

- Viewing Angle: 6 o'clock direction.

- Driving duty: 1/65 duty, 1/7 bias.

- 'Epson' SED1565D0B (COG) Dot Matrix LCD Driver.

- 8080 Series MPU interface (default).

- 6800 Series MPU interface (Optional).

- FPC.

- White LED05 backlight.

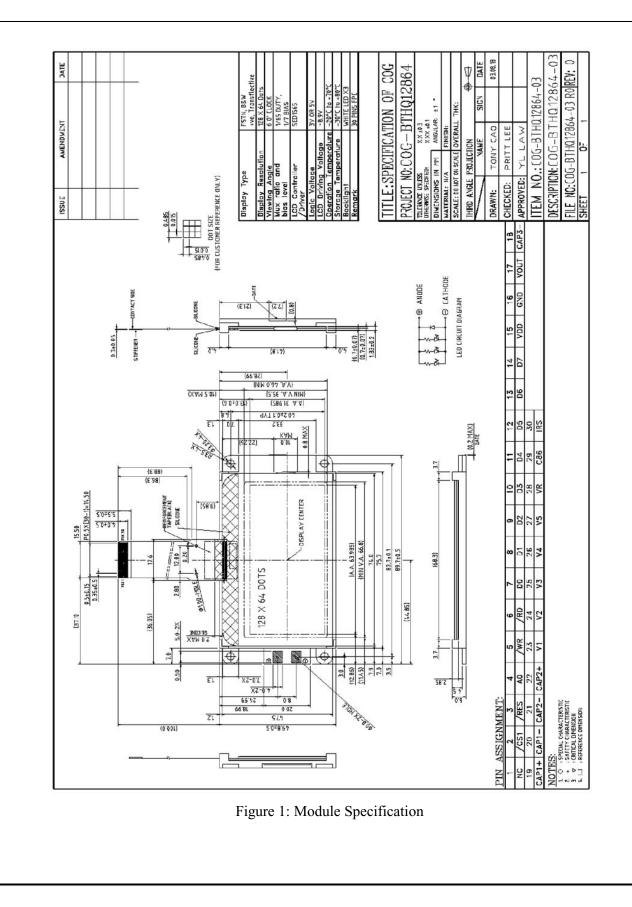

### 2. Mechanical Specifications

The mechanical detail is shown in Fig. 1 and summarized in Table 1 below.

#### Table 1

| Parameter          | Specifications                                         | Unit  |

|--------------------|--------------------------------------------------------|-------|

| Outline dimensions | 89.7(W) x 49.8(H) x 6.0(D)(Exclude FPC & gate)         | mm    |

|                    | 89.7(W) x 149.8(H) x 6.0(D)(Include FPC. Exclude gate) |       |

|                    | 89.7(W) x 150.0(H) x 6.0(D)(Include FPC and gate)      |       |

| View area          | 66.8 MIN.(W) x 35.5 MIN. (H)                           | mm    |

| Active area        | 63.985(W) x 31.985(H)                                  | mm    |

| Display format     | 128 (W) x 64(H)                                        | dots  |

| Dot size           | 0.485(W) x 0.485(H)                                    | mm    |

| Dot spacing        | 0.015(W) x 0.015(H)                                    | mm    |

| Dot pitch          | 0.500(W) x 0.500(H)                                    | mm    |

| Weight:            | TBD                                                    | grams |

### VL-FS-COG-BTHQ12864-03 REV. A (BTHQ 128064AVE-FETF-06-LEDWHITE-COG)

#### NOV/2003

PAGE 5 OF 15

### VL-FS-COG-BTHQ12864-03 REV. A (BTHQ 128064AVE-FETF-06-LEDWHITE-COG)

NOV/2003

PAGE 6 OF 15

### VL-FS-COG-BTHQ12864-03 REV. A (BTHQ 128064AVE-FETF-06-LEDWHITE-COG)

NOV/2003

PAGE 7 OF 15

#### 3. Interface signals

#### Table 2 (a)

| Pin | Symbol | Description                                                                                                                                                                                                                                                |

|-----|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| No. |        |                                                                                                                                                                                                                                                            |

| 1   | NC     | No connection.                                                                                                                                                                                                                                             |

| 2   | /CS1   | This is the chip select signal. When $/CS1 = "L"$ , then the chip select become active, and data/command I/O is enabled.                                                                                                                                   |

| 3   | /RES   | When /RES is set to "L," the settings are initialized. The reset operation is performed by the /RES signal level.                                                                                                                                          |

| 4   | A0     | This is connected to the least significant bit of the normal MPU address bus, and it determines whether the data bits are data or a command.<br>A0 = "H": Indicates that D0 to D7 are display data.<br>A0 = "L": Indicates that D0 to D7 are control data. |

| 5   | /WR    | When connected to an 8080 MPU, this is active LOW. This terminal connects to the 8080 MPU /WR signal. The signals on the data bus are latched at the rising edge of the /WR signal.                                                                        |

| 6   | /RD    | When connected to an 8080 MPU, this is active LOW.<br>This pin is connected to the /RD signal of the 8080 MPU, and the SED1565 series data<br>bus is in an output status when this signal is "L".                                                          |

| 7   | D0     | This is an 8-bit bi-directional data bus that connects to an 8-bit or 16-bit 8 standard                                                                                                                                                                    |

| 8   | D1     | MPU data bus.                                                                                                                                                                                                                                              |

| 9   | D2     |                                                                                                                                                                                                                                                            |

| 10  | D3     |                                                                                                                                                                                                                                                            |

| 11  | D4     |                                                                                                                                                                                                                                                            |

| 12  | D5     |                                                                                                                                                                                                                                                            |

| 13  | D6     |                                                                                                                                                                                                                                                            |

| 14  | D7     |                                                                                                                                                                                                                                                            |

| 15  | VDD    | Power supply. Shared with the MPU power supply terminal VCC.                                                                                                                                                                                               |

| 16  | GND    | Connection with ground.                                                                                                                                                                                                                                    |

| 17  | VOUT   | DC/DC voltage converter. Connect a capacitor between this terminal and GND.                                                                                                                                                                                |

| 18  | CAP3-  | DC/DC voltage converter. Connect a capacitor between this terminal and the CAP1+ terminal.                                                                                                                                                                 |

| 19  | CAP1+  | DC/DC voltage converter. Connect a capacitor between this terminal and the CAP1-terminal.                                                                                                                                                                  |

| 20  | CAP1-  | DC/DC voltage converter. Connect a capacitor between this terminal and the CAP1+ terminal.                                                                                                                                                                 |

| 21  | CAP2-  | DC/DC voltage converter. Connect a capacitor between this terminal and the CAP2+ terminal.                                                                                                                                                                 |

| 22  | CAP2+  | DC/DC voltage converter. Connect a capacitor between this terminal and the CAP2-terminal.                                                                                                                                                                  |

# VL-FS-COG-BTHQ12864-03 REV. A (BTHQ 128064AVE-FETF-06-LEDWHITE-COG)

NOV/2003

PAGE 8 OF 15

#### Table 2 (b)

| Pin<br>No. | Symbol                 | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|------------|------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 23~<br>27  | V1,V2,<br>V3,V4,<br>V5 | This is a multi-level power supply for the liquid crystal drive. The voltage applied is determined by the liquid crystal cell, and is changed through the use of a resistive voltage divided or through changing the impedance using an op. amp. Voltage levels are determined based on VDD, and must maintain the relative magnitudes shown below.<br>VDD (= V0) $\geq$ V1 $\geq$ V2 $\geq$ V3 $\geq$ V4 $\geq$ V5<br>Master operation: When the power supply turns ON, the internal power supply circuits produce the V1 to V4 voltages shown below. |

|            |                        | using the LCD bias set command.<br>For 1/7 bias: V1=(1/7)xV5, V2=(2/7)xV5, V3=(5/7)xV5, V4=(6/7)xV5.                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 28         | VR                     | Output voltage regulator terminal. Provides the voltage between VDD and V5<br>through a resistive voltage divider.<br>These are only enabled when the V5 voltage regulator internal resistors are not used<br>(IRS = "L").<br>These cannot be used when the V5 voltage regulator internal resistors are used (IRS =<br>"H").                                                                                                                                                                                                                           |

| 29         | C86                    | This is the MPU interface switch terminal.<br>C86 = "H": 6800 Series MPU interface.<br>C86 = "L": 8080 MPU interface.                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 30         | IRS                    | This terminal selects the resistors for the V5 voltage level adjustment.<br>IRS = "H": Use the internal resistors<br>IRS = "L": Do not use the internal resistors. The V5 voltage level is regulated by an<br>external resistive voltage divider attached to the VR terminal.<br>This pin is enabled only when the master operation mode is selected.<br>It is fixed to either "H" or "L" when the slave operation mode is selected.                                                                                                                   |

|            | +                      | Anode of backlight                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|            | -                      | Cathode of backlight.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

# VL-FS-COG-BTHQ12864-03 REV. A (BTHQ 128064AVE-FETF-06-LEDWHITE-COG)

#### NOV/2003

#### PAGE 9 OF 15

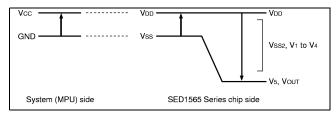

#### 4. Absolute Maximum Ratings

#### 4.1 Electrical Maximum Ratings (Ta = 25 °C)

| <u>Table 3</u>              |                    |            |       |         |      |  |  |

|-----------------------------|--------------------|------------|-------|---------|------|--|--|

| Paramete                    | r                  | Symbol     | Min.  | Max.    | Unit |  |  |

| Power Supply voltage (Logic | c)                 | VDD-GND    | -0.3  | +7.0    | V    |  |  |

|                             |                    | =VDD-VSS   |       |         |      |  |  |

| Power supply voltage        |                    | GND(=VSS2) | -7.0  | +0.3    | V    |  |  |

| (VDD standard)              | With Triple set-up |            | -6.0  | +0.3    | V    |  |  |

|                             | With Quad step-up  |            | -4.5  | +0.3    | V    |  |  |

| Power Supply voltage(V5,V   | OUT)               | V5,VOUT    | -18.0 | +0.3    | V    |  |  |

| (VDD standard)              | (VDD standard)     |            |       | !       |      |  |  |

| Power Supply voltage(V1~V   | V1,V2,V3,V4        | V5         | +0.3  | V       |      |  |  |

| (VDD standard)              |                    |            |       |         |      |  |  |

| Input voltage               |                    | Vin        | -0.3  | VDD+0.3 | V    |  |  |

Note: 1.)The modules may be destroyed if they are used beyond the absolute maximum ratings.

2.) Insure that the voltage levels of V1, V2, V3, and V4 are always such that

$VDD \ge V1 \ge V2 \ge V3 \ge V4 \ge V5.$

3.) The VSS2,V1 to V5 and VOUT are relative to VDD=0V reference.

. .

#### 4.2 Environmental Condition

|                         |                                                        | <u>Ta</u> | ble 4       |       |                 |

|-------------------------|--------------------------------------------------------|-----------|-------------|-------|-----------------|

|                         | Operating Storage                                      |           |             |       |                 |

| Item                    | Temperature                                            |           | Temperature |       | Remark          |

|                         | (To                                                    | pr)       | (Ts         | tg)   |                 |

|                         | Min.                                                   | Max.      | Min.        | Max.  |                 |

| Ambient Temperature     | -20°C                                                  | +70°C     | -30°C       | +80°C | Dry             |

| Humidity                | 95% max. RH for Ta $\leq$ 40°C                         |           |             |       | no condensation |

|                         | < 95% RH for Ta > 40°C                                 |           |             |       |                 |

| Vibration (IEC 68-2-6)  | Frequency: $10 \sim 55 \text{ Hz}$                     |           |             |       | 3 directions    |

| cells must be mounted   | Amplitude: 0.75 mm                                     |           |             |       |                 |

| on a suitable connector | Duration: 20 cycles in each direction.                 |           |             |       |                 |

| Shock (IEC 68-2-27)     | Pulse duration: 11 ms                                  |           |             |       | 3 directions    |

| Half-sine pulse shape   | Peak acceleration: $981 \text{ m/s}^2 = 100 \text{ g}$ |           |             |       |                 |

|                         | Number of shocks: 3 shocks in 3                        |           |             |       |                 |

|                         | mutually perpendicular axes.                           |           |             |       |                 |

NOV/2003

PAGE 10 OF 15

#### 5. Electrical Specifications

#### 5.1 Typical Electrical Characteristics

At Ta = 25 °C, VDD = 5V±5%, GND =0V.

| Table 5 |  |

|---------|--|

|         |  |

| _                 | ~                | ~               |         |      |         |      |

|-------------------|------------------|-----------------|---------|------|---------|------|

| Parameter         | Symbol           | Conditions      | Min.    | Тур. | Max.    | Unit |

| Supply voltage    | VDD-GND          |                 | 4.75    | 5.0  | 5.25    | V    |

| (Logic)           |                  |                 |         |      |         |      |

| Supply voltage    | VLCD             | VDD = +5.0V,    | 8.6     | 8.9  | 9.2     | V    |

| (LCD)             | =VDD-V5          | Note (1)        |         |      |         |      |

| Low-level input   | V <sub>ILC</sub> |                 | GND     | -    | 0.2xVDD | V    |

| signal voltage    |                  |                 |         |      |         |      |

| High-level input  | V <sub>IHC</sub> |                 | 0.8xVDD | -    | VDD     | V    |

| signal voltage    |                  |                 |         |      |         |      |

| Supply Current    | IDD              | VDD = 5V,       | -       | 0.5  | 0.7     | mA   |

| (Logic & LCD)     |                  | Character mode  |         |      |         |      |

|                   |                  | VDD = 5V,       | -       | 1.1  | 1.3     | mA   |

|                   |                  | Checker board   |         |      |         |      |

|                   |                  | mode            |         |      |         |      |

| Supply voltage of | VLED05           | Forward current | 4.8     | 5.0  | 5.2     | V    |

| white LED05       |                  | =45mA           |         |      |         |      |

| backlight         |                  |                 |         |      |         |      |

| -                 |                  | Number of LED   |         |      |         |      |

|                   |                  | dies            |         |      |         |      |

|                   |                  | =1x3=3          |         |      |         |      |

Note (1): There is tolerance in optimum LCD driving voltage during production and it will be within the specified range.

NOV/2003

PAGE 11 OF 15

5.2 Timing Specifications

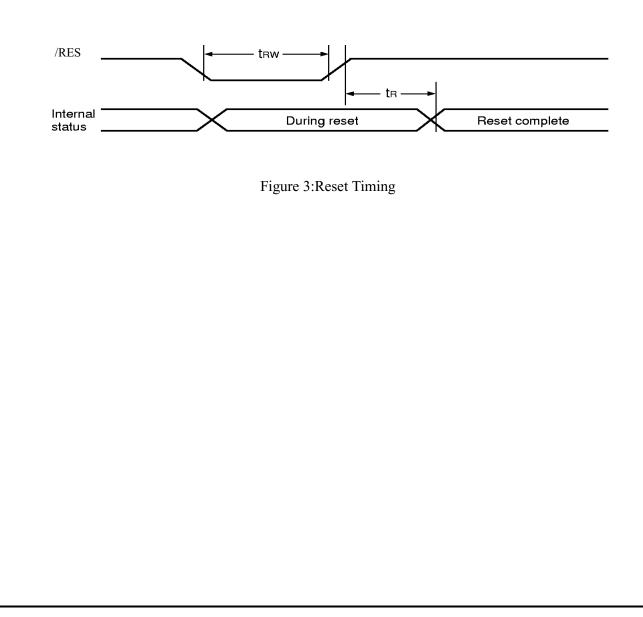

**Reset Timing**

At Ta = -20 °C to +70 °C, VDD = +5.0V±5%, GND = 0V.

| Item                  | Signal Symbo | Symbol | Condition | Rating |     |     | Units |

|-----------------------|--------------|--------|-----------|--------|-----|-----|-------|

| Item                  | Signal       | Symbol | Condition | Min    | Тур | Max | Units |

| Reset time            |              | tR     |           |        |     | 0.5 | μs    |

| Reset "L" pulse width | RES          | trw    |           | 0.5    | —   | —   | μs    |

Note: All timing is specified with 20% and 80% of VDD as the standard.

# VL-FS-COG-BTHQ12864-03 REV. A (BTHQ 128064AVE-FETF-06-LEDWHITE-COG)

NOV/2003

PAGE 12 OF 15

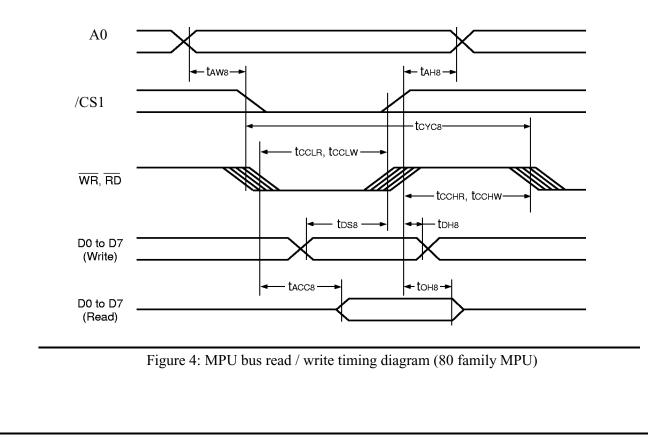

### System Bus Read/Write Characteristics (8080 Series MPU) At Ta = -20 °C to +70 °C, VDD = +5.0V±5%, GND = 0V.

| Table | 7 |

|-------|---|

|       |   |

| ltem                                                                                                                 | Signal    | Symbol                           | Condition   | Rating               |          | Units          |

|----------------------------------------------------------------------------------------------------------------------|-----------|----------------------------------|-------------|----------------------|----------|----------------|

|                                                                                                                      |           |                                  |             | Min                  | Max      | Units          |

| Address hold time<br>Address setup time                                                                              | A0        | tah8<br>taw8                     |             | 0<br>0               |          | ns<br>ns       |

| System cycle time                                                                                                    | A0        | tcycs                            |             | 166                  | _        | ns             |

| Control L pulse width (WR)<br>Control L pulse width (RD)<br>Control H pulse width (WR)<br>Control H pulse width (RD) | 레페<br>페 페 | tcclw<br>tcclr<br>tccHw<br>tccHR |             | 30<br>70<br>30<br>30 |          | ns<br>ns<br>ns |

| Data setup time<br>Address hold time                                                                                 | D0 to D7  | tDS8<br>tDH8                     |             | 30<br>10             |          | ns<br>ns       |

| RD access time<br>Output disable time                                                                                |           | taccs<br>tohs                    | CL = 100 pF | 5                    | 70<br>50 | ns<br>ns       |

\*1 The input signal rise time and fall time (tr, tf) is specified at 15 ns or less. When the system cycle time is extremely fast, (tr + tf) ≤ (tCYC8 - tCCLW - tCCHW) for (tr + tf) ≤ (tCYC8 - tCCLR - tCCHR) are specified.

\*2 All timing is specified using 20% and 80% of VDD as the reference.

\*3 tccLw and tccLR are specified as the overlap between  $\overline{CS1}$  being "L" (CS2 = "H") and  $\overline{WR}$  and  $\overline{RD}$  being at the "L" level.

NOV/2003

PAGE 13 OF 15

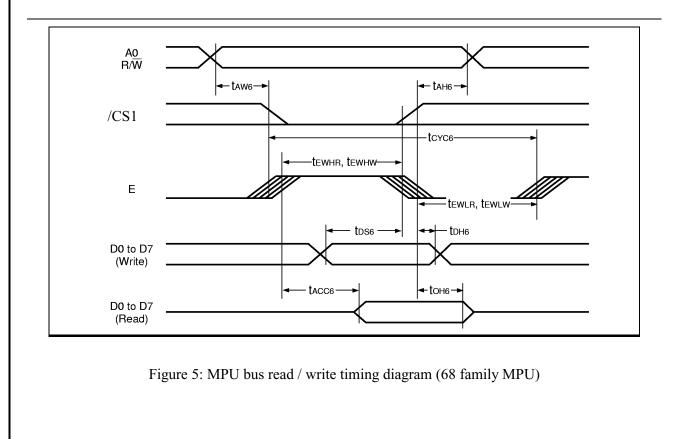

### System Bus Read/Write Characteristics (6800 Series MPU) At Ta = -20 °C to +70 °C, VDD = +5.0V±5%, VSS = 0V.

#### Table 8

| Item                                    |               | Signal   | Symbol         | Condition   | Rating   |          | Units    |

|-----------------------------------------|---------------|----------|----------------|-------------|----------|----------|----------|

|                                         |               |          |                |             | Min      | Max      | Units    |

| Address hold time<br>Address setup time |               | A0       | tah6<br>taw6   |             | 0<br>0   |          | ns<br>ns |

| System cycle time                       |               | A0       | tcyc6          |             | 166      |          | ns       |

| Data setup time<br>Data hold time       |               | D0 to D7 | tDS6<br>tDH6   |             | 30<br>10 | _        | ns<br>ns |

| Access time<br>Output disable time      |               |          | tacce<br>tohe  | CL = 100 pF | <br>10   | 70<br>50 | ns<br>ns |

| Enable H pulse<br>time                  | Read<br>Write | E        | tewhr<br>tewhw |             | 70<br>30 | _        | ns<br>ns |

| Enable L pulse<br>time                  | Read<br>Write | E        | tewlr<br>tewlw |             | 30<br>30 |          | ns<br>ns |

\*1 The input signal rise time and fall time (tr, tr) is specified at 15 ns or less. When the system cycle time is extremely fast,  $(tr + tf) \le (t_{CYC6} - t_{EWLW} - t_{EWHW})$  for  $(tr + tf) \le (t_{CYC6} - t_{EWLR} - t_{EWHR})$  are specified. All timing is specified using 20% and 80% of VDD as the reference. \*2

\*3 tewLw and tewLR are specified as the overlap between  $\overline{CS1}$  being "L" (CS2 = "H") and E.

### VL-FS-COG-BTHQ12864-03 REV. A (BTHQ 128064AVE-FETF-06-LEDWHITE-COG)

#### NOV/2003

PAGE 14 OF 15

#### 5.3 Instruction Set

#### Command Code WR RD D7 Command A0 D6 D5 D4 D3 D2 D1 D0 Function LCD display ON/OFF Display ON/OFF (1) 0 1 0 1 0 1 0 1 0 1 1 0: OFF, 1: ON Sets the display RAM display (2) Display start line set 0 1 0 0 1 Display start address start line address (3)Page address set 0 1 0 1 0 1 1 Page address Sets the display RAM page address (4) Column address 0 1 0 0 0 0 1 Most significant Sets the most significant 4 bits set upper bit column address of the display RĂM column address Sets the least significant 4 bits of Column address 0 1 0 0 0 0 0 Least significant the display RAM column address set lower bit column address Reads the status data (5) Status read 0 0 1 Status 0 0 0 0 Display data write 0 Write data Writes to the display RAM (6) 1 1 (7) Display data read 0 1 Read data Reads from the display RAM 1 (8) ADC select 0 0 0 0 0 0 0 0 Sets the display RAM address 1 1 1 SEG output correspondence 1 0: normal, 1: reverse 0 Sets the LCD display normal/ (9) Display normal/ 0 1 0 1 0 1 0 1 1 0 reverse 1 reverse 0: normal, 1: reverse (10) Display all points 0 1 0 1 0 1 0 0 1 0 0 Display all points ON/OFF 0: normal display 1 1: all points ON (11) LCD bias set Sets the LCD drive voltage 0 1 0 1 0 1 0 0 0 1 0 bias ratio SED1565\*\*\* ..... 0: 1/9, 1: 1/7 SED1566\*\*\* /SED1568\*\*\* /SED1569\*\*\* ..... 0: 1/8, 1: 1/6 SED1567\*\*\*\_..... 0: 1/6, 1: 1/5 (12) Read/modify/write 0 1 0 1 1 1 0 0 0 0 0 Column address increment At write: +1 At read: 0 (13) End 0 0 0 0 Clear read/modify/write 1 1 1 1 1 1 (14) Reset 0 0 0 0 0 1 0 Internal reset 1 1 1 1 Common output 0 0 0 0 0 Select COM output scan (15) mode select direction 1 0: normal direction, 1: reverse direction (16) Power control set 0 1 0 0 1 0 Operating Select internal power 0 1 mode supply operating mode (17) V5 voltage 0 0 0 0 0 0 Resistor ratio Select internal resistor ratio 1 1 regulator internal (Rb/Ra) mode resistor ratio set 0 (18) Electronic volume 0 1 0 1 0 0 0 ۵ 0 1 mode set Electronic volume 0 1 0 Electronic volume value Set the V5 output voltage register set electronic volume register (19) Static indicator 0 0 1 0 0 0 0 0: OFF, 1: ON 1 1 1 ON/OFF Static indicator 0 0 Mode Set the flashing mode 1 register set (20) Power saver Display OFF and display all points ON compound command (21) NOP 0 0 0 0 Command for non-operation 1 1 1 1 0 1 1 (22) Test 0 1 0 1 1 1 1 Command for IC test. Do not use this command (Note) \*: disabled data

Table 8

NOV/2003

PAGE 15 OF 15

#### 6. Reference Application Circuit (8080) Example