# Specification for BTHQ 128064AVD-FSTF-12-LEDMULTI-COG

**Version October 2004**

```

BTHQ 128064AVD-FSTF-12-LEDMULTI-COG

```

OCT/2004

PAGE 2 OF 16

#### **DOCUMENT REVISION HISTORY 1:**

| DOCUMENT DATE                     | DESCRIPTION                                                                                                                                                                                | CHANGED          | CHECKED          |

|-----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|------------------|

| REVISION                          |                                                                                                                                                                                            | BY               | BY               |

| REVISION   FROM TO   A 2004.10.13 | First Release.<br>Based on:<br>a.) VL-QUA-012B REV. W, 2004.03.20<br>(According to VL-QUA-012B, LCD<br>size is small because Unit Per<br>Laminate=24 which is more than<br>6pcs/Laminate.) | CHEN HUI<br>JUAN | TIAN JIAN<br>WEI |

BTHQ 128064AVD-FSTF-12-LEDMULTI-COG OCT/2004 PAGE 3 OF 16

# **CONTENTS**

Page No.

| 1.               | GENERAL DESCRIPTION                                                                             | 4              |

|------------------|-------------------------------------------------------------------------------------------------|----------------|

| 2.               | MECHANICAL SPECIFICATIONS                                                                       | 4              |

| 3.               | INTERFACE SIGNALS                                                                               | 8              |

| 4.<br>4.1<br>4.2 | ABSOLUTE MAXIMUM RATINGS<br>ELECTRICAL MAXIMUM RATINGS – FOR IC ONLY<br>ENVIRONMENTAL CONDITION | 10<br>10<br>10 |

| 5.<br>5.1<br>5.2 | ELECTRICAL SPECIFICATIONS<br>TYPICAL ELECTRICAL CHARACTERISTICS<br>TIMING SPECIFICATIONS        | 11<br>11<br>12 |

| 6.               | COMMAND TABLE                                                                                   | 15             |

| 7.               | LCD COSMETIC CONDITIONS                                                                         | 16             |

| 8.               | REMARK                                                                                          | 16             |

BTHQ 128064AVD-FSTF-12-LEDMULTI-COG OCT/2004 PAGE 4 OF 16

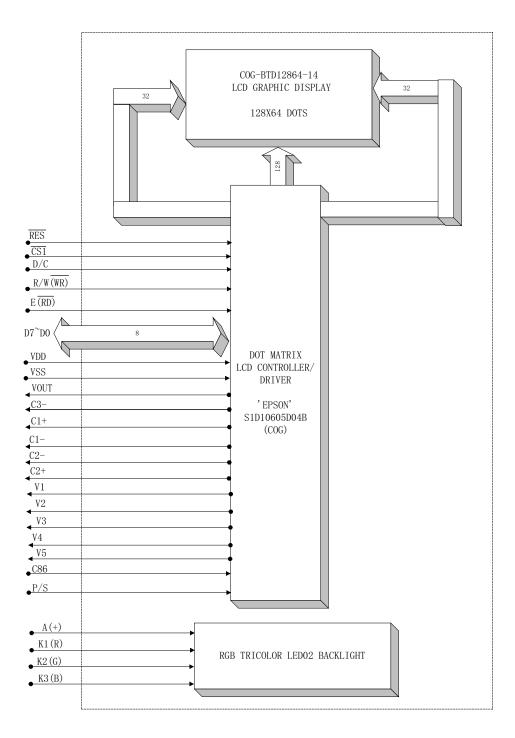

## Specification of LCD Module Type Model No.: COG-BTD12864-14

#### 1. General Description

- 128 x 64 Dots FSTN Positive Black & White Transflective Dot Matrix LCD Module.

- Viewing Angle: 12 o'clock direction.

- Driving duty: 1/65 Duty, 1/7 bias.

- 'Epson' S1D10605D04B (COG) Dot Matrix LCD Driver or equivalent.

- FPC connection.

- Red & Green & Blue Tricolor LED02 backlight.

#### 2. Mechanical Specifications

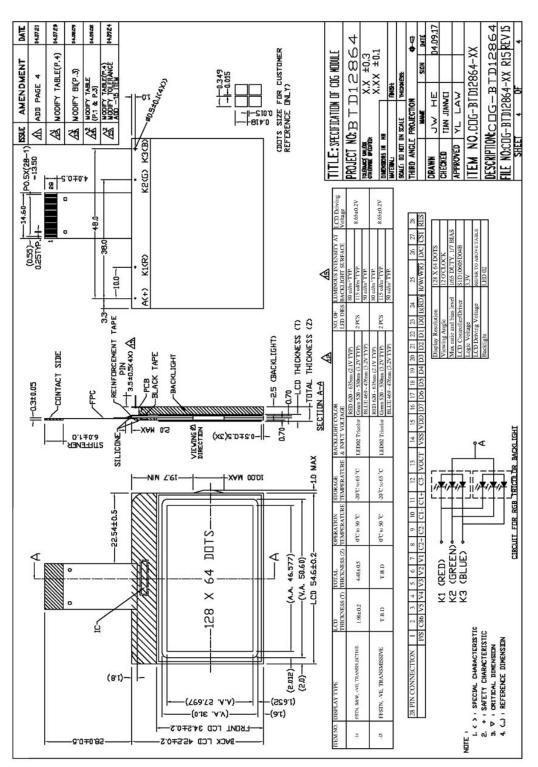

The mechanical detail is shown in Fig. 1 and summarized in Table 1 below.

| Parameter          | Specifications                                                  | Unit  |

|--------------------|-----------------------------------------------------------------|-------|

| Outline dimensions | 55.6(W) x 70.2(H) x 4.48(D) (Included FPC. Exclude terminals of | mm    |

|                    | backlight)                                                      |       |

| Viewing area       | 50.60(W) x 31.0(H)                                              | mm    |

| Active area        | 46.577(W) x 27.697(H)                                           | mm    |

| Display format     | 128(W) x 64(H)                                                  | dots  |

| Dot size           | 0.349(W) x 0.418(H)                                             | mm    |

| Dot spacing        | 0.015(W) x 0.015(H)                                             | mm    |

| Dot pitch          | 0.364(W) x 0.433(H)                                             | mm    |

| Weight             | TBD                                                             | grams |

#### Table 1

OCT/2004

PAGE 5 OF 16

Figure 1: Module Specification.

OCT/2004

PAGE 6 OF 16

Figure 2: Block Diagram.

OCT/2004

PAGE 7 OF 16

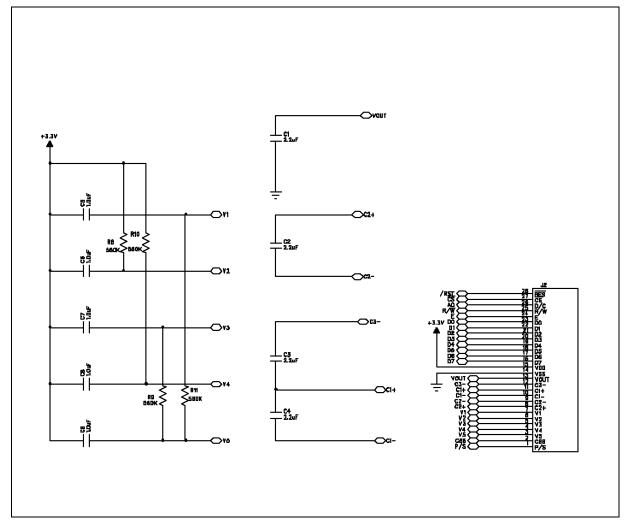

Figure 3: Reference Circuit

OCT/2004

PAGE 8 OF 16

### 3. Interface signals

#### Table 2(a): Pin Assignment

| Pin No. | Symbol    | Description                                                                                            |                                                                            |                          |                  |                      |  |  |  |  |  |

|---------|-----------|--------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|--------------------------|------------------|----------------------|--|--|--|--|--|

| 1       | P/S       | This is the paral                                                                                      | lel data input/                                                            |                          |                  | nal.                 |  |  |  |  |  |

|         |           | This is the parallel data input/serial data input switch terminal.<br>P/S = HIGH: Parallel data input. |                                                                            |                          |                  |                      |  |  |  |  |  |

|         |           | P/S = LOW: Serial data input.                                                                          |                                                                            |                          |                  |                      |  |  |  |  |  |

|         |           |                                                                                                        |                                                                            |                          |                  |                      |  |  |  |  |  |

|         |           |                                                                                                        | The following applies depending on the P/S status:                         |                          |                  |                      |  |  |  |  |  |

|         |           |                                                                                                        | P/S Data/Command Data Read/Write Serial Clock                              |                          |                  |                      |  |  |  |  |  |

|         |           |                                                                                                        | D/C(A0)                                                                    | D0 to D7                 | RD, WR           |                      |  |  |  |  |  |

|         |           | LOW I                                                                                                  | D/C(A0)                                                                    | SI (D7)                  | Write only       | SCL (D6)             |  |  |  |  |  |

|         |           | When $P/S = I O$                                                                                       | W D0 to D5                                                                 | are HZ_D0 to I           | )5 may be HIC    | GH, LOW or Open.     |  |  |  |  |  |

|         |           | $\overline{RD}(E)$ and $\overline{WR}(E)$                                                              |                                                                            |                          |                  | JII, LOW OF OPEN.    |  |  |  |  |  |

|         |           | With serial data                                                                                       |                                                                            |                          |                  | ported.              |  |  |  |  |  |

| 2       | C86       | This is the MPU                                                                                        |                                                                            |                          | <u> </u>         |                      |  |  |  |  |  |

|         |           | C86=HIGH: 68                                                                                           | 00 Series MPU                                                              | J interface.             |                  |                      |  |  |  |  |  |

|         |           | C86=LOW: 808                                                                                           |                                                                            |                          |                  |                      |  |  |  |  |  |

| 3       | V5        |                                                                                                        | This is multi-level power supply for liquid crystal drive.                 |                          |                  |                      |  |  |  |  |  |

| 4       | V4        |                                                                                                        | Voltage levels are determined based on VDD, and must maintain the relative |                          |                  |                      |  |  |  |  |  |

| 5       | V3        |                                                                                                        | magnitudes shown below.                                                    |                          |                  |                      |  |  |  |  |  |

| 6       | V2        | $VDD (=V0) \ge V$                                                                                      | $VDD (=V0) \ge V1 \ge V2 \ge V3 \ge V4 \ge V5$                             |                          |                  |                      |  |  |  |  |  |

| 7       | V1        | Master operatio                                                                                        | n When the no                                                              | war supply tur           | ns ON the inte   | ernal power supply   |  |  |  |  |  |

|         |           | circuits produce                                                                                       | -                                                                          |                          |                  | 1 11 5               |  |  |  |  |  |

|         |           | selected using th                                                                                      |                                                                            |                          |                  | ige setting are      |  |  |  |  |  |

|         |           | 8                                                                                                      |                                                                            |                          |                  |                      |  |  |  |  |  |

|         |           | For 1/7 bias: V1                                                                                       | =(1/7)xV5, V                                                               | $2 = (2/7) \times V5, V$ | 3=(5/7)xV5, V    | 74=(6/7)xV5.         |  |  |  |  |  |

| 8       | C2+       | •                                                                                                      | converter. Co                                                              | nnects a capaci          | tor between th   | is terminal and C2-  |  |  |  |  |  |

|         |           | terminal.                                                                                              |                                                                            |                          |                  |                      |  |  |  |  |  |

| 9       | C2-       | -                                                                                                      | converter. Co                                                              | nnects a capaci          | tor between th   | is terminal and C2+  |  |  |  |  |  |

| 10      | <u>C1</u> | terminal.                                                                                              |                                                                            |                          | 4 1 4            | is terminal and OI b |  |  |  |  |  |

| 10      | C1-       | DC/DC voltage terminal.                                                                                | converter. Co                                                              | nnects a capaci          | tor between th   | is terminal and C1+  |  |  |  |  |  |

| 11      | C1+       |                                                                                                        | converter Co                                                               | nnects a canaci          | tor between th   | is terminal and C1–  |  |  |  |  |  |

|         |           | terminal.                                                                                              |                                                                            | inicets a capaci         |                  |                      |  |  |  |  |  |

| 12      | С3-       |                                                                                                        | converter Co                                                               | nnects a canaci          | tor between th   | is terminal and C1+  |  |  |  |  |  |

|         |           | terminal.                                                                                              |                                                                            | a cupue                  |                  |                      |  |  |  |  |  |

| 13      | VOUT      |                                                                                                        | converter. Co                                                              | nnects a capaci          | tor between th   | is terminal and VSS. |  |  |  |  |  |

| 14      | VSS       |                                                                                                        |                                                                            |                          |                  | also the reference   |  |  |  |  |  |

|         |           | power supply fo                                                                                        | A                                                                          | <u> </u>                 | for the liquid c | rystal drive.        |  |  |  |  |  |

| 15      | VDD       | Power supply for                                                                                       | or logic $(+3.3)$                                                          | /).                      |                  |                      |  |  |  |  |  |

# BTHQ 128064AVD-FSTF-12-LEDMULTI-COG OCT/2004 PAGE 9 OF 16

#### Table 2(b): Pin Assignment

| 17<br>18    | D7<br>D6<br>D5     | This is an 8-bit bi-directional data bus that connects to an 8-bit standard MPU data bus.                 |

|-------------|--------------------|-----------------------------------------------------------------------------------------------------------|

| 18          |                    | data bus.                                                                                                 |

|             | D5                 |                                                                                                           |

| 19          | 20                 | When the serial interface is selected ( $P/S = LOW$ ), then D7 serves as the serial                       |

|             | D4                 | data input terminal (SI) and D6 serves as the serial clock input terminal (SCL).                          |

| 20          | D3                 | At this time, D0 to D5 are set to high impedance.                                                         |

| 21          | D2                 | When the chip select is inactive, D0 to D7 are set to high impedance.                                     |

| 22          | D1                 |                                                                                                           |

|             | D0                 |                                                                                                           |

| 24 E        | $\overline{(RD)}$  | When connected to an 8080 MPU, this is active LOW.                                                        |

|             |                    | This pin is connected to the RD signal of the 8080 MPU, and the S1D15605                                  |

|             |                    | series data bus is in an output status when this signal is LOW.                                           |

|             |                    |                                                                                                           |

|             |                    | When connected to a 6800 Series MPU, this is active HIGH.                                                 |

|             |                    | This is the 6800 Series MPU enable clock input terminal.                                                  |

| 25 R/W      | $W(\overline{WR})$ | When connected to an 8080 MPU, this is active LOW.                                                        |

|             |                    | This terminal connects to the 8080 MPU WR signal. The signals on the data                                 |

|             |                    | bus are latched at the rising edge of the WR signal.                                                      |

|             |                    |                                                                                                           |

|             |                    | When connected to an 6800 Series MPU:                                                                     |

|             |                    | This is the read/write control signal input terminal.<br>When $P(W = UICH)$ B and                         |

|             |                    | When $R/W = HIGH$ : Read.                                                                                 |

| 26 I        | D/C                | When R/W = LOW: Write.<br>This is connect to the least significant bit of the normal MPU address bus, and |

| 20 1        | D/C                | it determines whether the data bits are data or a command.                                                |

|             |                    | D/C(A0)="High": Indicates that D0 to D7 are display data.                                                 |

|             |                    | D/C(A0)="Low": Indicates that D0 to D7 are control data.                                                  |

| 27 0        | CS1                | This is the chip select signal for first chip.                                                            |

|             | 0.01               | When CS1=LOW and CS2=HIGH, then the chip select becomes active and the                                    |

|             |                    | data/commands I/O is enabled.                                                                             |

| 28 <b>H</b> | RES                | When RES is set to LOW, the settings are initialized.                                                     |

|             | ~~~~               | The reset operation is performed by the RES signal level.                                                 |

OCT/2004

PAGE 10 OF 16

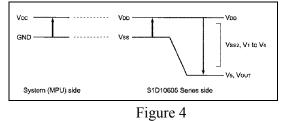

#### 4. Absolute Maximum Ratings

#### 4.1 Electrical Maximum Ratings – for IC Only

Table 3

| Parameter                                       | Symbol      | Min.  | Max.    | Unit |

|-------------------------------------------------|-------------|-------|---------|------|

| Power Supply voltage (Logic)                    | VDD-VSS     | -0.3  | +6.0    | V    |

| Power Supply voltage(VSS2)(VDD standard)        | VSS2        | -4.0  | +0.3    | V    |

| Power Supply voltage(V5,VOUT)(VDD standard)     | V5,VOUT     | -18.0 | +0.3    | V    |

| Power Supply voltage(V1,V2,V3,V4)(VDD standard) | V1,V2,V3,V4 | V5    | +0.3    | V    |

| Input voltage                                   | Vin         | -0.3  | VDD+0.3 | V    |

Note: 1.) The VSS2, V1 to V5 and VOUT are relative to the VDD=0V reference.

2.) The V1, V2, V3, and V4 voltages must always satisfy the condition of  $VDD \ge V1 \ge V2 \ge V3 \ge V4 \ge V5$ .

3.)The modules may be destroyed if they are used beyond the absolute maximum ratings.

#### 4.2 Environmental Condition

Table 4

| Item                                                                       | Operating<br>Temperature<br>(Topr) |                                                        | Storage<br>Temperature<br>(Tstg)            |                 | Remark |

|----------------------------------------------------------------------------|------------------------------------|--------------------------------------------------------|---------------------------------------------|-----------------|--------|

|                                                                            | Min.                               | Max.                                                   | Min.                                        | Max.            | -      |

| Ambient Temperature                                                        | 0°C                                | +50°C                                                  | -20°C                                       | +65°C           | Dry    |

| Humidity                                                                   |                                    | . RH for T<br>H for Ta >                               |                                             | no condensation |        |

| Vibration (IEC 68-2-6)<br>cells must be mounted<br>on a suitable connector | Amplitud                           | y: $10 \sim$<br>le: 0.75 r<br>20 cycles                | nm                                          | 3 directions    |        |

| Shock (IEC 68-2-27)<br>Half-sine pulse shape                               | Pulse dur<br>Peak acco<br>Number o | ation : 11<br>eleration: 9<br>of shocks :<br>perpendic | $\frac{ms}{281 m/s^2} = \frac{3 shocks}{2}$ | 3 directions    |        |

OCT/2004

PAGE 11 OF 16

#### 5. Electrical Specifications

#### 5.1 Typical Electrical Characteristics

#### At Ta = +25 °C, VDD = +3.3±5%, VSS = 0V.

|                                    | ,                 | Table 5                                                             |         |      |         |       |

|------------------------------------|-------------------|---------------------------------------------------------------------|---------|------|---------|-------|

| Parameter                          | Symbol            | Conditions                                                          | Min.    | Тур. | Max.    | Unit  |

| Supply voltage<br>(Logic)          | VDD-VSS           |                                                                     | 3.14    | 3.3  | 3.47    | V     |

| Supply voltage<br>(LCD) (built-in) | VLCD<br>=VDD-V5   | Ta = 0 °C,<br>Character mode<br>VDD = +3.3V, Note 1                 | -       | 8.90 | -       | V     |

|                                    |                   | Ta = 25 °C,<br>Character mode<br>VDD = +3.3V, Note 1                | 8.45    | 8.65 | 8.85    | V     |

|                                    |                   | Ta = $+50 \text{ °C}$ ,<br>Character mode<br>VDD = $+3.3$ V, Note 1 | -       | 8.10 | -       | V     |

| Low-level input signal voltage     | V <sub>ILC</sub>  | Note 2                                                              | VSS     | -    | 0.2xVDD | V     |

| High-level input<br>signal voltage | V <sub>IHC</sub>  | Note 2                                                              | 0.8xVDD | -    | VDD     | V     |

| Supply Current<br>(Logic & LCD)    | IDD               | VDD = +3.3V,Note 1,<br>Character mode                               | -       | 0.46 | 0.69    | mA    |

|                                    |                   | VDD = +3.3V,Note 1,<br>Checker board mode                           | -       | 0.78 | 1.2     | mA    |

| Supply voltage<br>of LED02         | RED VLED          |                                                                     | 1.8     | 2.1  | 2.3     | V     |

| backlight                          | GREEN VLED        |                                                                     | 2.9     | 3.2  | 3.5     |       |

|                                    | BLUE VLED         | Forward current                                                     | 2.9     | 3.2  | 3.5     |       |

| Wavelength of                      | $\lambda$ (RED)   | =40mA                                                               | 620     | 628  | 635     | nm    |

| LED02                              | $\lambda$ (GREEN) | Number of LED dice                                                  | 520     | 525  | 530     |       |

| backlight                          | λ (BLUE)          | =2dies.                                                             | 469     | 472  | 476     |       |

| Luminance (on                      | (RED)             |                                                                     | 55      | 80   | 104     | cd/m2 |

| the backlight<br>surface) of       | (GREEN)           |                                                                     | 80      | 115  | 150     |       |

| backlight                          | (BLUE)            |                                                                     | 35      | 50   | 65      |       |

Note 1: There is tolerance in optimum LCD driving voltage during production and it will be within the specified range.

Note 2: A0, D0 to D5,D6(SCL),D7(SI),E(RD),R/W(WR),CS1,C86,P/S,RES terminals.

BTHQ 128064AVD-FSTF-12-LEDMULTI-COG OCT/2004 PAGE 12 OF 16

#### 5.2 Timing Specifications

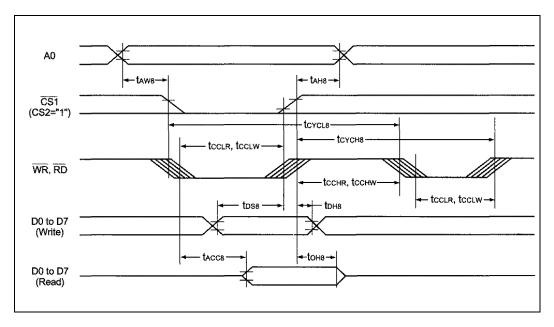

#### System Bus read/Write Characteristics 1 (For the 8080 Series MPU) At Ta = 0 °C to +50 °C, VDD = +3.3V±5%, VSS = 0V.

<u>Table 6</u>

| item                             | Sianol   | Granhal       | <b>^</b>    | Rat  | Units                                                                         |       |  |  |  |

|----------------------------------|----------|---------------|-------------|------|-------------------------------------------------------------------------------|-------|--|--|--|

| itern                            | Signal   | Symbol        | Condition   | Min. | ting<br>Max.<br>—<br>—<br>—<br>—<br>—<br>—<br>—<br>—<br>—<br>—<br>—<br>—<br>— | Units |  |  |  |

| Address hold time                | A0       | tans          |             | 0    |                                                                               | ns    |  |  |  |

| Address setup time               |          | taws          |             | 0    | —                                                                             | ns    |  |  |  |

| System cycle time 1              | A0       | tcycl8        |             | 300  |                                                                               | ns    |  |  |  |

| System cycle time 2              |          | tсусна        |             | 300  | —                                                                             | ns    |  |  |  |

| Control LOW pulse width (Write)  | WR       | tccLw         |             | 60   | <u>—</u> .                                                                    | ns    |  |  |  |

| Control LOW pulse width (Read)   | RD       | <b>t</b> CCLR |             | 120  | —                                                                             | ns    |  |  |  |

| Control HIGH pulse width (Write) | WR       | tcchw         |             | 60   | —                                                                             | ns    |  |  |  |

| Control HIGH pulse width (Read)  | RD       | <b>t</b> CCHR |             | 60   | —                                                                             | ns    |  |  |  |

| Data setup time                  | D0 to D7 | tosa          |             | 40   |                                                                               | ns    |  |  |  |

| Data hold time                   |          | tona          |             | 15   |                                                                               | ns    |  |  |  |

| RD access time                   |          | tACC8         | CL = 100 pF |      | 140                                                                           | ns    |  |  |  |

| Output disable time              |          | toн8          | r           | 10   | 100                                                                           | ns    |  |  |  |

\*1 The input signal rise time and fall time (tr, tf) is specified at 15 ns or less. When the system cycle time is extremely fast,

$(tr + tf) \le (tCYCL(H)8 - tCCLW - tCCHW)$  for  $(tr + tf) \le (tCYCL(H)8 - tCCLR - tCCHR)$  are specified.

\*2 All timing is specified using 20% and 80% of VDD as reference.

\*3 tCCLW and tCCLR are specified as the overlap between CS1 being LOW (CS2=HIGH) and WR and RD being at the LOW level.

Figure 5: The timing diagram of system bus read/write (For the 8080 Series MPU)

OCT/2004

PAGE 13 OF 16

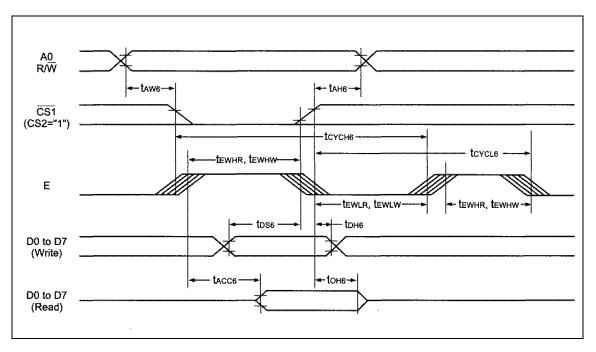

#### System Bus read/Write Characteristics 2 (For the 6800 Series MPU)

#### At Ta =-0 °C to +50 °C, VDD = +3.3V±5%, VSS = 0V.

| ltem                                       |               | Ciamal Car | Sumbal           | O           | Rat        | Units      |          |

|--------------------------------------------|---------------|------------|------------------|-------------|------------|------------|----------|

| Item                                       |               | Signal     | Symbol           | Condition   | Min.       | Max.       | Units    |

| Address hold time<br>Address setup time    |               | A0         | tah6<br>taw6     |             | 0<br>0     |            | ns<br>ns |

| System cycle time 1<br>System cycle time 2 | ł             | A0         | tcych6<br>tcycL6 |             | 300<br>300 |            | ns<br>ns |

| Data setup time<br>Data hold time          |               | D0 to D7   | tose<br>toнe     |             | 40<br>15   |            | ns<br>ns |

| Access time<br>Output disable time         |               |            | tacce<br>tohe    | C∟ = 100 pF | 10         | 140<br>100 | ns<br>ns |

| Enable HIGH pulse time                     | Read<br>Write | Е          | tewhr<br>tewhw   |             | 120<br>60  |            | ns<br>ns |

| Enable LOW pulse time                      | Read<br>Write | E          | tewlr<br>tewlw   |             | 60<br>60   |            | ns<br>ns |

#### Table 7

\*1 The input signal rise time and fall time (tr, tf) is specified at 15 ns or less. When the system cycle time is extremely fast, (tr + tf)  $\leq$  (tCYCH(L)6 - tEWLW - tEWHW) for (tr + tf)  $\leq$  (tCYCH(L)6 - tEWLR - tEWHR) are specified.

\*2 All timing is specified using 20% and 80% for VDD as the reference.

\*3 tEWLW and tEWLR are specified as the overlap between  $\overline{\text{CS1}}$  being LOW (CS2=HIGH) and E.

Figure 6: The timing diagram of system bus read/write (For the 6800 Series MPU)

OCT/2004

PAGE 14 OF 16

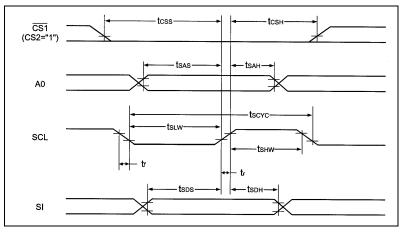

#### The serial interface

#### At Ta =0 °C to +50 °C, VDD = +3.3V±5%, VSS = 0V.

#### Table 8

| ltem                 | Signal | Ourse had    | 0         | Rat  |      |       |

|----------------------|--------|--------------|-----------|------|------|-------|

| Item                 | Signal | Symbol       | Condition | Min. | Max. | Units |

| Serial Clock Period  | SCL    | tscyc        |           | 250  | _    | ns    |

| SCL HIGH pulse width |        | tsнw         |           | 100  |      | ns    |

| SCL LOW pulse width  |        | ts∟w         |           | 100  |      | ns    |

| Address setup time   | A0     | tsas         |           | 150  | _    | ns    |

| Address hold time    |        | <b>t</b> SAH |           | 150  |      | ns    |

| Data setup time      | SI     | tsps         |           | 100  |      | ns    |

| Data hold time       |        | tspн         |           | 100  |      | ns    |

| CS-SCL time          | CS     | tcss         |           | 150  |      | ns    |

|                      |        | tcsH         |           | 150  |      | ns    |

Note 1: The input signal rise and fall (tr, tf) are specified at 15ns or less.

Note 2: All timing is specified using 20% and 80% of VDD as the standard.

Figure 7: The timing diagram of serial interface

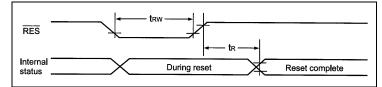

#### **Reset Timing**

At Ta =0 °C to +50 °C, VDD = +3.3V±5%, VSS = 0V.

Table 9

| ltem                  | Signal | Symbol | Condition |      | Units |      |       |

|-----------------------|--------|--------|-----------|------|-------|------|-------|

| nem                   | Signal | Symbol | Condition | Min. | Typ.  | Max. | Units |

| Reset time            |        | tR     |           |      |       | 1    | μs    |

| Reset LOW pulse width | RES    | trw    |           | 1    | —     | _    | μs    |

Note : All timing is specified with 20% and 80% of VDD as the standard.

Figure 8: Reset Timing

OCT/2004

PAGE 15 OF 16

#### 6. Command Table

#### Table 10

|      | Command                                                | Command Code |    |    |         |                                           |      |                       |                                    |                   |    |        |                                                                                                                                                           |

|------|--------------------------------------------------------|--------------|----|----|---------|-------------------------------------------|------|-----------------------|------------------------------------|-------------------|----|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

|      |                                                        | A0           | RD | WR | D7      | D6                                        | D5   | D4                    | D3                                 | D2                | D1 | D0     | Function                                                                                                                                                  |

| (1)  | Display ON/OFF                                         | 0            | 1  | 0  | 1       | 0                                         | 1    | 0                     | 1                                  | 1                 | 1  | 0<br>1 | LCD display ON/OFF<br>0: OFF, 1: ON                                                                                                                       |

| (2)  | Display start line set                                 | 0            | 1  | 0  | 0       | 1                                         |      | Display start address |                                    |                   |    |        | Sets the display RAM display start line address                                                                                                           |

| (3)  | Page address set                                       | 0            | 1  | 0  | 1       | 0                                         | 1    | 1                     | Page address                       |                   |    | s      | Sets the display RAM page address                                                                                                                         |

| (4)  | Column address<br>set upper bit                        | 0            | 1  | 0  | 0 0 0 1 |                                           |      |                       | Most significant<br>column address |                   |    |        | Sets the most significant 4 bits<br>of the display RAM column<br>address.                                                                                 |

|      | Column address<br>set lower bit                        | 0            | 1  | 0  | 0       | 0 0 0 Least significant<br>column address |      |                       |                                    |                   |    |        | Sets the least significant 4 bits of the display RAM column address                                                                                       |

| (5)  | Status read                                            | 0            | 0  | 1  |         | Sta                                       | atus |                       | 0                                  | 0                 | 0  | 0      | Reads the status data                                                                                                                                     |

| (6)  | Display data write                                     | 1            | 1  | 0  |         |                                           |      | Write data            |                                    |                   |    |        | Writes to the display RAM                                                                                                                                 |

| (7)  | Display data read                                      | 1            | 0  | 1  |         |                                           |      | Read data             |                                    |                   |    |        | Reads from the display RAM                                                                                                                                |

| (8)  | ADC select                                             | 0            | 1  | 0  | 1       | 0                                         | 1    | 0                     | 0                                  | 0                 | 0  | 0<br>1 | Sets the display RAM address<br>SEG output correspondence<br>0: normal, 1: reverse                                                                        |

| (9)  | Display normal/<br>reverse                             | 0            | 1  | 0  | 1       | 0                                         | 1    | 0                     | 0                                  | 1                 | 1  | 0<br>1 | Sets the LCD display normal/<br>reverse<br>0: normal, 1: reverse                                                                                          |

| (10) | Display all points<br>ON/OFF                           | 0            | 1  | 0  | 1       | 0                                         | 1    | 0                     | 0                                  | 1                 | 0  | 0<br>1 | Display all points<br>0: normal display<br>1: all points ON                                                                                               |

| (11) | LCD bias set                                           | 0            | 1  | 0  | 1       | 0                                         | 1    | 0                     | 0                                  | 0                 | 1  | 0<br>1 | Sets the LCD drive voltage<br>bias ratio<br>S1D10605***** 0: 1/9, 1: 1/<br>S1D10606*****<br>/S1D10609***** 0: 1/8, 1: 1//<br>S1D10609***** 0: 1/6, 1: 1// |

| (12) | Read/modify/write                                      | 0            | 1  | 0  | 1       | 1                                         | 1    | 0                     | 0                                  | 0                 | 0  | 0      | Column address increment<br>At write: +1<br>At read: 0                                                                                                    |

| (13) | End                                                    | 0            | 1  | 0  | 1       | 1                                         | 1    | 0                     | 1                                  | 1                 | 1  | 0      | Clear read/modify/write                                                                                                                                   |

| (14) | Reset                                                  | 0            | 1  | 0  | 1       | 1                                         | 1    | 0                     | 0                                  | 0                 | 1  | 0      | Internal reset                                                                                                                                            |

| (15) | Common output<br>mode select                           | 0            | 1  | 0  | 1       | 1                                         | 0    | 0                     | 0<br>1                             | *                 | *  | *      | Select COM output scan<br>direction<br>0: normal direction,<br>1: reverse direction                                                                       |

| (16) | Power control set                                      | 0            | 1  | 0  | 0       | 0                                         | 1    | 0                     | 1                                  | Operating<br>mode |    | ng     | Select internal power<br>supply operating mode                                                                                                            |

| (17) | V5 voltage<br>regulator internal<br>resistor ratio set | 0            | 1  | 0  | 0       | 0                                         | 1    | 0                     | 0                                  | Resistor ratio    |    | atio   | Select internal resistor ratio<br>(Rb/Ra) mode                                                                                                            |

| (18) | Electronic volume<br>mode set                          | 0            | 1  | 0  | 1       | 0                                         | 0    | 0                     | 0                                  | 0                 | 0  | 1      |                                                                                                                                                           |

|      | Electronic volume<br>register set                      | 0            | 1  | 0  | *       | *                                         |      | Electro               | onic vo                            | c volume value    |    |        | Set the V5 output voltage<br>electronic volume register                                                                                                   |

| (19) | Static indicator<br>ON/OFF                             | 0            | 1  | 0  | 1       | 0                                         | 1    | 0                     | 1                                  | 1                 | 0  | 0<br>1 | 0: OFF, 1: ON                                                                                                                                             |

|      | Static indicator<br>register set                       | 0            | 1  | 0  | *       | *                                         | *    | *                     | *                                  | *                 | Мо | de     | Set the flashing mode                                                                                                                                     |

| (20) | Power saver                                            |              |    |    |         |                                           |      |                       |                                    |                   |    |        | Display OFF and display all<br>points ON compound command                                                                                                 |

| (21) | NOP                                                    | 0            | 1  | 0  | 1       | 1                                         | 1    | 0                     | 0                                  | 0                 | 1  | 1      | Command for non-operation                                                                                                                                 |

| (22) | Test                                                   | 0            | 1  | 0  | 1       | 1                                         | 1    | 1                     | *                                  | *                 | *  | *      | Command for IC test. Do not use this command                                                                                                              |

(Note) \*: disabled data

BTHQ 128064AVD-FSTF-12-LEDMULTI-COG OCT/2004 PAGE 16 OF 16

#### 7. LCD Cosmetic Conditions

- a.) Reference document follow VL-QUA-012B.

- b.) LCD size of the product is small.

#### 8. Remark

- a.) Identification labels will be stuck on the module without obstructing the viewing area of display.

- b.) Data Modul does not responsible for any polarizer defect after the protective film has been removed from the display.