# HSMP-382x, 482x

# Surface Mount RF PIN Switch and Limiter Diodes

# **Data Sheet**

## **Description/Applications**

The HSMP-382x series is optimized for switching applications where ultra-low resistance is required. The HSMP-482x diode is ideal for limiting and low inductance switching applications up to 1.5 GHz.

A SPICE model is not available for PIN diodes as SPICE does not provide for a key PIN diode characteristic, carrier lifetime.

#### **Features**

- Diodes Optimized for: Low Current Switching Low Distortion Attenuating

- Power Limiting/Circuit Protection

- Surface Mount SOT-23 and SOT-323 Packages Single and Dual Versions Tape and Reel Options Available

- Low Failure in Time (FIT) Rate[1]

- Lead-free

Note:

For more information see the Surface Mount PIN Reliability Data Sheet.

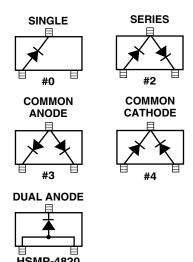

## Package Lead Code Identification, SOT-23 (Top View)

## Package Lead Code Identification, SOT-323 (Top View)

# Absolute Maximum Ratings $^{[1]}$ $T_c = +25^{\circ}$ C

| stgg                                                                                                   | Symbol         | Parameter                         | Unit | S0T-23     | SOT-323    |

|--------------------------------------------------------------------------------------------------------|----------------|-----------------------------------|------|------------|------------|

| $T_{\rm j}$ Junction Temperature °C 150 150 $T_{\rm stg}$ Storage Temperature °C -65 to 150 -65 to 150 | $I_f$          | Forward Current (1 µs Pulse)      | Amp  | 1          | 1          |

| T <sub>stg</sub> Storage Temperature °C -65 to 150 -65 to 15                                           | $P_{IV}$       | Peak Inverse Voltage              | V    | 50         | 50         |

|                                                                                                        | T <sub>j</sub> | Junction Temperature              | °C   | 150        | 150        |

|                                                                                                        | $T_{stg}$      | Storage Temperature               | °C   | -65 to 150 | -65 to 150 |

| $\theta_{jc}$ Thermal Resistance <sup>[2]</sup> °C/W 500 150                                           | $\theta_{jc}$  | Thermal Resistance <sup>[2]</sup> | °C/W | 500        | 150        |

#### Notes:

- 1. Operation in excess of any one of these conditions may result in permanent damage to the device.

- device. 2.  $T_c = +25^{\circ}\text{C}$ , where  $T_c$  is defined to be the temperature at the package pins where contact is made to the circuit board.

# Electrical Specifications $T_c = 25^{\circ}C$

| Package<br>Marking<br>Code | Lead<br>Code                      | Configuration               | Minimum<br>Breakdown<br>Voltage V <sub>BR</sub> (V)                       | Maximum Series Resistance $R_s\left(\Omega\right)$                                                                           | Maximum<br>Total Capacitance<br>C <sub>T</sub> (pF)   |

|----------------------------|-----------------------------------|-----------------------------|---------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|

| F0                         | 0                                 | Single                      | 50                                                                        | 0.6                                                                                                                          | 0.8                                                   |

| F2                         | 2                                 | Series                      |                                                                           |                                                                                                                              |                                                       |

| F3                         | 3                                 | Common Anode                |                                                                           |                                                                                                                              |                                                       |

| F4                         | 4                                 | Common Cathode              |                                                                           |                                                                                                                              |                                                       |

|                            |                                   |                             | $V_{R} = V_{BR}$                                                          | f = 100 MHz                                                                                                                  | f = 1 MHz                                             |

|                            |                                   |                             |                                                                           | $I_F = 10 \text{ mA}$                                                                                                        | $V_R = 20 \text{ V}$                                  |

|                            | Marking<br>Code<br>F0<br>F2<br>F3 | Marking Code  FO OF2 2 F3 3 | Marking<br>CodeLead<br>CodeConfigurationF00SingleF22SeriesF33Common Anode | Marking<br>CodeLead<br>CodeConfigurationBreakdown<br>Voltage V<br>BR (V)F00Single50F22SeriesF33Common AnodeF44Common Cathode | $\begin{array}{c ccccccccccccccccccccccccccccccccccc$ |

# High Frequency (Low Inductance, 500 MHz – 3 GHz) PIN Diodes

| Part<br>Number<br>HSMP- | Package<br>Marking<br>Code | Lead<br>Code | Configuration | Minimum<br>Breakdown<br>Voltage<br>V <sub>BR</sub> (V) | Maximum Series Resistance $R_s(\Omega)$ | Typical<br>Total<br>Capacitance<br>C <sub>T</sub> (pF) | Maximum<br>Total<br>Capacitance<br>C <sub>T</sub> (pF) | Typical<br>Total<br>Inductance<br>L <sub>r</sub> (nH) |

|-------------------------|----------------------------|--------------|---------------|--------------------------------------------------------|-----------------------------------------|--------------------------------------------------------|--------------------------------------------------------|-------------------------------------------------------|

| 4820                    | FA                         | Α            | Dual Anode    | 50                                                     | 0.6                                     | 0.75                                                   | 1.0                                                    | 1.0                                                   |

| 482B                    | FA                         | Α            | Dual Anode    |                                                        |                                         |                                                        |                                                        |                                                       |

| Test Con                | ditions                    |              |               | $V_{R} = V_{BR}$ Measure $I_{R} \le 10 \mu A$          | I <sub>F</sub> = 10 mA                  | f = 1  MHz<br>$V_R = 20 \text{ V}$                     | f = 1 MHz<br>$V_R = 0 V$                               | f= 500 MHz-<br>3 GHz                                  |

# Typical Parameters at $T_c = 25^{\circ}C$

| Part Number<br>HSMP- | Series Resistance $R_s(\Omega)$             | Carrier Lifetime $	au$ (ns) | Reverse Recovery Time<br>T <sub>rr</sub> (ns) | Total Capacitance<br>C <sub>T</sub> (pF) |  |

|----------------------|---------------------------------------------|-----------------------------|-----------------------------------------------|------------------------------------------|--|

| 382x                 | 1.5                                         | 70                          | 7                                             | 0.60 @ 20 V                              |  |

| Test Conditions      | $f = 100 \text{ MHz}$ $I_F = 10 \text{ mA}$ | I <sub>F</sub> = 10 mA      | $V_R = 10 \text{ V}$ $I_E = 20 \text{ mA}$    |                                          |  |

|                      | ·                                           |                             | 90% Recovery                                  |                                          |  |

# Typical Parameters at $T_c = 25^{\circ}$ C (unless otherwise noted), Single Diode

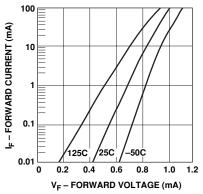

Figure 1. Forward Current vs. Forward Voltage.

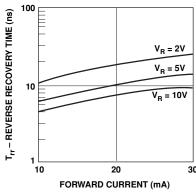

Figure 2. Reverse Recovery Time vs. Forward Current for Various Reverse Voltages.

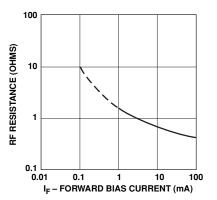

Figure 3. RF Resistance at 25C vs. Forward Bias Current.

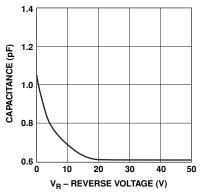

Figure 4. Capacitance vs. Reverse Voltage.

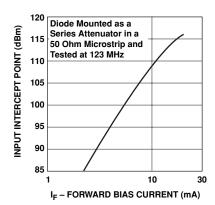

Figure 5. 2nd Harmonic Input Intercept Point vs. Forward Bias Current.

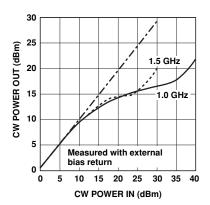

Figure 6. Large Signal Transfer Curve of the HSMP-482x Limiter.

# **Typical Applications for Multiple Diode Products**

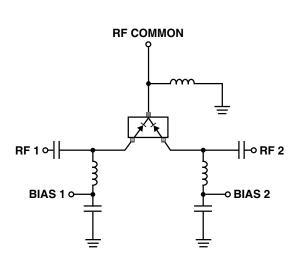

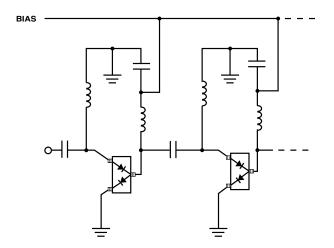

Figure 7. Simple SPDT Switch, Using Only Positive Current.

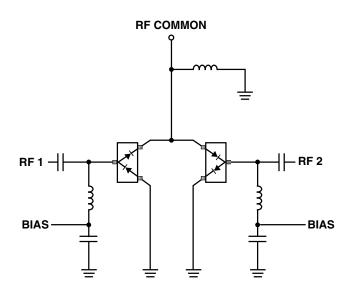

Figure 8. High Isolation SPDT Switch, Dual Bias.

# Typical Applications for Multiple Diode Products, continued

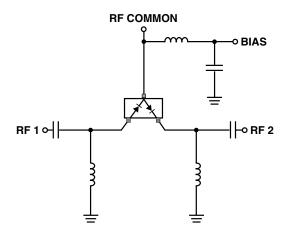

Figure 9. Switch Using Both Positive and Negative Bias Current.

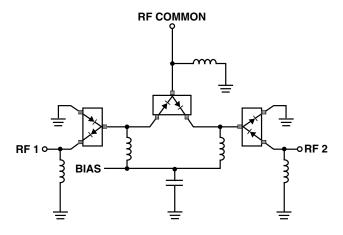

Figure 10. Very High Isolation SPDT Switch, Dual Bias.

Figure 11. High Isolation SPST Switch (Repeat Cells as Required.

Figure 12. Power Limiter Using HSMP-3822 Diode Pair. See Application Note 1050 for details.

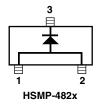

# Typical Applications for HSMP-482x Low Inductance Series

#### **Microstrip Series Connection for HSMP-482x Series**

In order to take full advantage of the low inductance of the HSMP-482x series when using them in series applications, both lead 1 and lead 2 should be connected together, as shown in Figure 14.

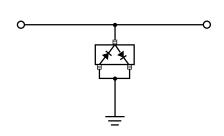

Figure 13. Internal Connections.

Figure 14. Circuit Layout.

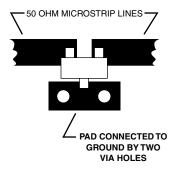

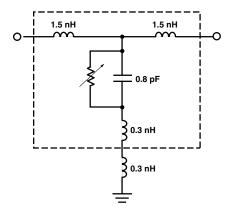

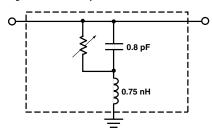

### **Microstrip Shunt Connections for HSMP-482x Series**

In Figure 15, the center conductor of the microstrip line is interrupted and leads 1 and 2 of the HSMP-482x diode are placed across the resulting gap. This forces the 0.5 nH lead inductance of leads 1 and 2 to appear as part of a low pass filter, reducing the shunt parasitic inductance and increasing the maximum available attenuation. The 0.3 nH of shunt inductance external to the diode is created by the via holes, and is a good estimate for 0.032" thick material.

Figure 15. Circuit Layout, HSMP-482x Limiter.

Figure 16. Equivalent Circuit.

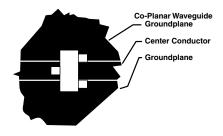

#### Co-Planar Waveguide Shunt Connection for HSMP-482x Series

Co-Planar waveguide, with ground on the top side of the printed circuit board, is shown in Figure 17. Since it eliminates the need for via holes to ground, it offers lower shunt parasitic inductance and higher maximum attenuation when compared to a microstrip circuit. See AN1050 for details.

Figure 17. Circuit Layout.

Figure 18. Equivalent Circuit.

# **Assembly Information**

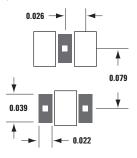

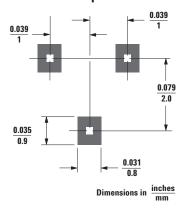

# **SOT-323 PCB Footprint**

A recommended PCB pad layout for the miniature SOT-323 (SC-70) package is shown in Figure 19 (dimensions are in inches). This layout provides ample allowance for package placement by automated assembly equipment without adding parasitics that could impair the performance.

Dimensions in inches

Figure 19. Recommended PCB Pad Layout for Avago's SC70 3L/SOT-323 Products.

# **SOT-23 PCB Footprint**

Figure 20. Recommended PCB Pad Layout for Avago's SOT-23 Products.

#### **SMT Assembly**

Reliable assembly of surface mount components is a complex process that involves many material, process, and equipment factors, including: method of heating (e.g., IR or vapor phase reflow, wave soldering, etc.) circuit board material, conductor thickness and pattern, type of solder alloy, and the thermal conductivity and thermal mass of components. Components with a low mass, such as the SOT-323/-23 package, will reach solder reflow temperatures faster than those with a greater mass.

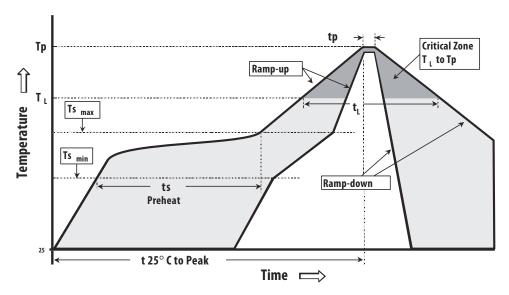

Avago's diodes have been qualified to the timetemperature profile shown in Figure 21. This profile is representative of an IR reflow type of surface mount assembly process.

After ramping up from room temperature, the circuit board with components attached to it (held in place with solder paste) passes through one or more preheat zones.

The preheat zones increase the temperature of the board and components to prevent thermal shock and begin evaporating solvents from the solder paste. The reflow zone briefly elevates the temperature sufficiently to produce a reflow of the solder.

The rates of change of temperature for the ramp-up and cool-down zones are chosen to be low enough to not cause deformation of the board or damage to components due to thermal shock. The maximum temperature in the reflow zone ( $T_{MAX}$ ) should not exceed 260°C.

These parameters are typical for a surface mount assembly process for Avago diodes. As a general guideline, the circuit board and components should be exposed only to the minimum temperatures and times necessary to achieve a uniform reflow of solder.

Figure 21. Surface Mount Assembly Profile.

#### Lead-Free Reflow Profile Recommendation (IPC/JEDEC J-STD-020C)

| Reflow Parameter Le                                                      |                                                                                                                          |  |  |  |  |

|--------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Average ramp-up rate (Liquidus Temperature (T <sub>S(max)</sub> to Peak) |                                                                                                                          |  |  |  |  |

| Temperature Min (T <sub>S(min)</sub> )                                   | 150°C                                                                                                                    |  |  |  |  |

| Temperature Max (T <sub>S(max)</sub> )                                   | 200°C                                                                                                                    |  |  |  |  |

| Time (min to max) (t <sub>s</sub> )                                      | 60-180 seconds                                                                                                           |  |  |  |  |

|                                                                          | 3°C/second max                                                                                                           |  |  |  |  |

| Temperature (T <sub>L</sub> )                                            | 217°C                                                                                                                    |  |  |  |  |

| Time (t <sub>L</sub> )                                                   | 60-150 seconds                                                                                                           |  |  |  |  |

|                                                                          | 260 +0/-5°C                                                                                                              |  |  |  |  |

| perature (t <sub>p</sub> )                                               | 20-40 seconds                                                                                                            |  |  |  |  |

|                                                                          | 6°C/second max                                                                                                           |  |  |  |  |

|                                                                          | 8 minutes max                                                                                                            |  |  |  |  |

|                                                                          | Temperature Min $(T_{S(min)})$ Temperature Max $(T_{S(max)})$ Time (min to max) $(t_s)$ Temperature $(T_L)$ Time $(t_L)$ |  |  |  |  |

Note 1: All temperatures refer to topside of the package, measured on the package body surface

# **Package Dimensions**

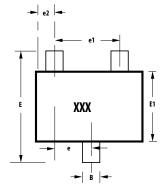

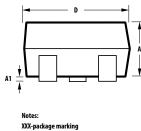

## Outline 23 (SOT-23)

|        | DIMENSIONS (MM) |       |  |  |

|--------|-----------------|-------|--|--|

| SYMBOL | MIN.            | MAX.  |  |  |

| A      | 0.79            | 1.20  |  |  |

| A1     | 0.000           | 0.100 |  |  |

| В      | 0.30            | 0.54  |  |  |

| C      | 0.08            | 0.20  |  |  |

| D      | 2.73            | 3.13  |  |  |

| E1     | 1.15            | 1.50  |  |  |

| e      | 0.89            | 1.02  |  |  |

| e1     | 1.78            | 2.04  |  |  |

| e2     | 0.45            | 0.60  |  |  |

| E      | 2.10            | 2.70  |  |  |

| L      | 0.45            | 0.69  |  |  |

|        |                 |       |  |  |

DIMENSIONS (mm)

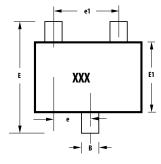

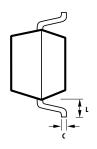

## Outline SOT-323 (SC-70)

| ŀ        | <b>→</b> D —                  | -       |

|----------|-------------------------------|---------|

|          |                               | $\prod$ |

| A1 ±     |                               |         |

| <b>†</b> |                               |         |

|          | lotes:<br>(XX-nackage marking |         |

Drawings are not to scale

|        | DIMENSIONS (mm) |      |  |  |  |

|--------|-----------------|------|--|--|--|

| SYMBOL | MIN.            | MAX. |  |  |  |

| Α      | 0.80 1.00       |      |  |  |  |

| A1     | 0.00 0.10       |      |  |  |  |

| В      | 0.15 0.40       |      |  |  |  |

| C      | 0.08            | 0.25 |  |  |  |

| D      | 1.80 2.25       |      |  |  |  |

| E1     | 1.10 1.40       |      |  |  |  |

| e      | 0.65 typical    |      |  |  |  |

| e1     | 1.30 typical    |      |  |  |  |

| E      | 1.80            | 2.40 |  |  |  |

| L      | 0.26 0.46       |      |  |  |  |

# **Package Characteristics**

Drawings are not to scale

| Lead Material                 | Copper (SOT-323); Alloy 42 (SOT-23) |

|-------------------------------|-------------------------------------|

| Lead Finish                   | Tin 100% (Lead-free option)         |

| Maximum Soldering Temperature | 260°C for 5 seconds                 |

|                               | 2 pounds pull                       |

| Typical Package Inductance    | 2 nH                                |

| Typical Package Capacitance   |                                     |

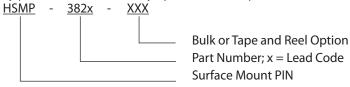

# **Ordering Information**

Specify part number followed by option. For example:

## **Option Descriptions**

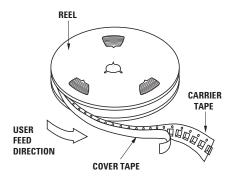

-BLKG = Bulk, 100 pcs. per antistatic bag

-TR1G = Tape and Reel, 3000 devices per 7" reel

-TR2G = Tape and Reel, 10,000 devices per 13" reel

Tape and Reeling conforms to Electronic Industries RS-481, "Taping of Surface Mounted Components for Automated Placement."

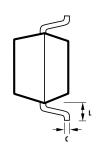

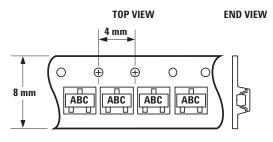

# **Device Orientation**

## For Outlines SOT-23/323

Note: "AB" represents package marking code.

"C" represents date code.

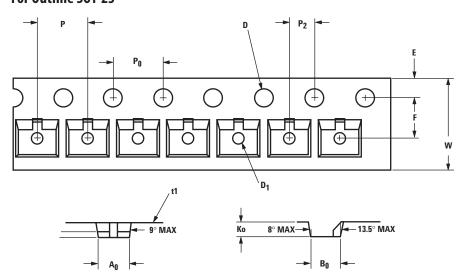

# Tape Dimensions and Product Orientation For Outline SOT-23

|                     | DESCRIPTION                              | SYMB0L         | SIZE (mm)                           | SIZE (INCHES)                       |

|---------------------|------------------------------------------|----------------|-------------------------------------|-------------------------------------|

| CAVITY              | LENGTH                                   | A <sub>0</sub> | $3.15 \pm 0.10$                     | $0.124 \pm 0.004$                   |

|                     | WIDTH                                    | B <sub>0</sub> | $\textbf{2.77} \pm \textbf{0.10}$   | $0.109 \pm 0.004$                   |

|                     | DEPTH                                    | K <sub>0</sub> | $\textbf{1.22} \pm \textbf{0.10}$   | $\textbf{0.048} \pm \textbf{0.004}$ |

|                     | PITCH                                    | P              | $4.00 \pm 0.10$                     | $\textbf{0.157} \pm \textbf{0.004}$ |

|                     | BOTTOM HOLE DIAMETER                     | D <sub>1</sub> | 1.00 + 0.05                         | $\textbf{0.039} \pm \textbf{0.002}$ |

| PERFORATION         | DIAMETER                                 | D              | 1.50 + 0.10                         | 0.059 + 0.004                       |

|                     | PITCH                                    | P <sub>0</sub> | $\textbf{4.00} \pm \textbf{0.10}$   | $\textbf{0.157} \pm \textbf{0.004}$ |

|                     | POSITION                                 | E              | $1.75 \pm 0.10$                     | $0.069 \pm 0.004$                   |

| CARRIER TAPE        | WIDTH                                    | w              | 8.00 + 0.30 - 0.10                  | 0.315+0.012-0.004                   |

|                     | THICKNESS                                | t1             | $\textbf{0.229} \pm \textbf{0.013}$ | $0.009 \pm 0.0005$                  |

| DISTANCE<br>BETWEEN | CAVITY TO PERFORATION (WIDTH DIRECTION)  | F              | $\textbf{3.50} \pm \textbf{0.05}$   | $0.138 \pm 0.002$                   |

| CENTERLINE          | CAVITY TO PERFORATION (LENGTH DIRECTION) | P <sub>2</sub> | $\textbf{2.00} \pm \textbf{0.05}$   | $\textbf{0.079} \pm \textbf{0.002}$ |

# Tape Dimensions and Product Orientation For Outline SOT-323

|              | DESCRIPTION                              | SYMBOL         | SIZE (mm)        | SIZE (INCHES)     |

|--------------|------------------------------------------|----------------|------------------|-------------------|

| CAVITY       | LENGTH                                   | A <sub>0</sub> | 2.40 ± 0.10      | $0.094 \pm 0.004$ |

|              | WIDTH                                    | В0             | $2.40 \pm 0.10$  | $0.094 \pm 0.004$ |

|              | DEPTH                                    | K <sub>0</sub> | 1.20 ± 0.10      | $0.047 \pm 0.004$ |

|              | PITCH                                    | P              | 4.00 ± 0.10      | $0.157 \pm 0.004$ |

|              | BOTTOM HOLE DIAMETER                     | D <sub>1</sub> | 1.00 + 0.25      | 0.039 + 0.010     |

| PERFORATION  | DIAMETER                                 | D              | 1.55 ± 0.05      | 0.061 ± 0.002     |

|              | PITCH                                    | P <sub>0</sub> | 4.00 ± 0.10      | $0.157 \pm 0.004$ |

|              | POSITION                                 | E              | 1.75 ± 0.10      | $0.069 \pm 0.004$ |

| CARRIER TAPE | WIDTH                                    | w              | 8.00 ± 0.30      | 0.315 ± 0.012     |

|              | THICKNESS                                | t <sub>1</sub> | $0.254 \pm 0.02$ | 0.0100 ± 0.0008   |

| COVER TAPE   | WIDTH                                    | С              | 5.4 ± 0.10       | 0.205 ± 0.004     |

|              | TAPE THICKNESS                           | T <sub>t</sub> | 0.062 ± 0.001    | 0.0025 ± 0.00004  |

| DISTANCE     | CAVITY TO PERFORATION (WIDTH DIRECTION)  | F              | 3.50 ± 0.05      | 0.138 ± 0.002     |

|              | CAVITY TO PERFORATION (LENGTH DIRECTION) | P <sub>2</sub> | 2.00 ± 0.05      | 0.079 ± 0.002     |

| ANGLE        | FOR SOT-323 (SC70-3 LEAD)                | An             | 8°C MAX          |                   |

|              | FOR SOT-363 (SC70-6 LEAD)                |                | 10°C MAX         |                   |

For product information and a complete list of distributors, please go to our web site: **www.avagotech.com**

Avago, Avago Technologies, and the A logo are trademarks of Avago Technologies in the United States and other countries. Data subject to change. Copyright © 2005-2009 Avago Technologies. All rights reserved. Obsoletes 5989-4026EN AV02-1395EN - June 2, 2009